**DRV8808**

SLVS857B - DECEMBER 2009 - REVISED JANUARY 2015

# DRV8808 Combination Motor Driver With DC-DC Converter

#### **Features**

- Three DC Motor Drivers

- Up to 2.5-A Current Chopping

- Low Typical ON Resistance ( $R_{DSON} = 0.5 \Omega$  at  $T_{.1} = 25^{\circ}C$

- Three Integrated DC-DC Converters

- ON/OFF Selectable Using CSELECT Pin and Serial Interface

- Outputs Configurable With External Resistor Network From 1 V to 90% of  $V_M$  Capability for All Three Channels

- 1.35-A Output Capability for All Three Channels

- One Integrated LDO Regulator

- Output Configurable With External Resistor Network from 1 V to 2.5 V

- 550-mA Output Capability

- 7-V to 40-V Operating Range

- Serial Interface for Communications

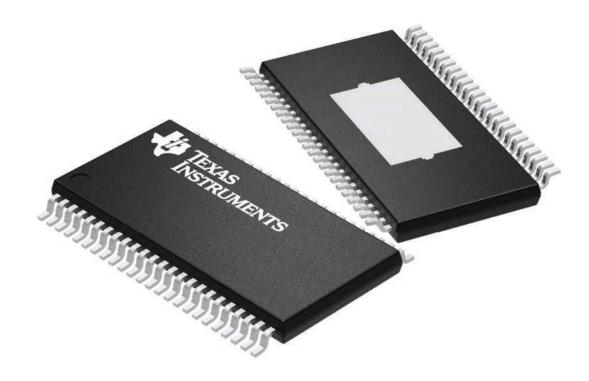

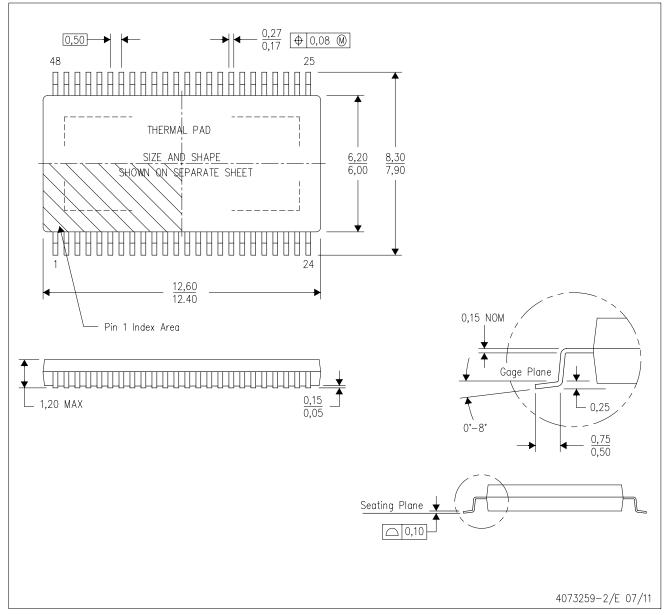

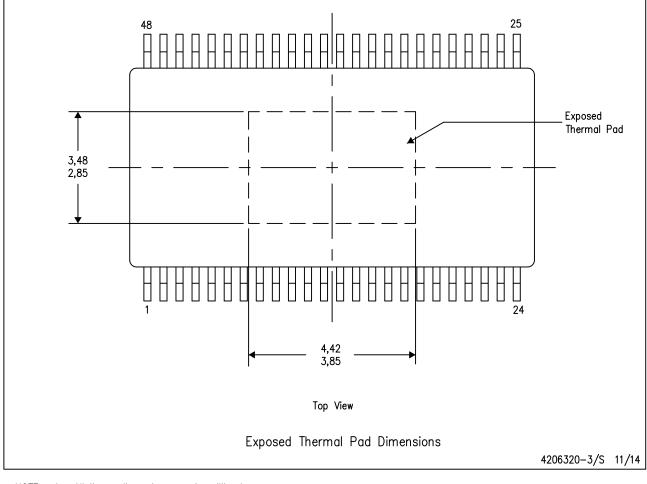

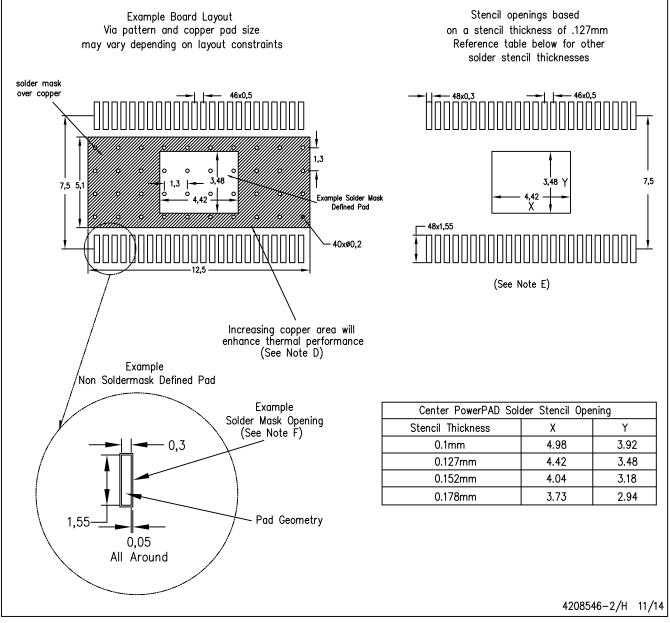

- Thermally Enhanced Surface-Mount Package 48-Pin HTSSOP With PowerPAD™ (Eco-Friendly: RoHS and No Sb/Br)

- Power-Down Function (Deep-Sleep Mode)

- Reset Signal Output (Active Low)

- Reset (All Clear) Control Input

## **Applications**

- **Printers**

- **Document Scanners**

- POS

- Copiers

# 3 Description

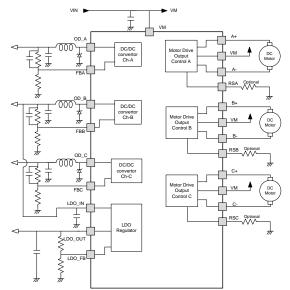

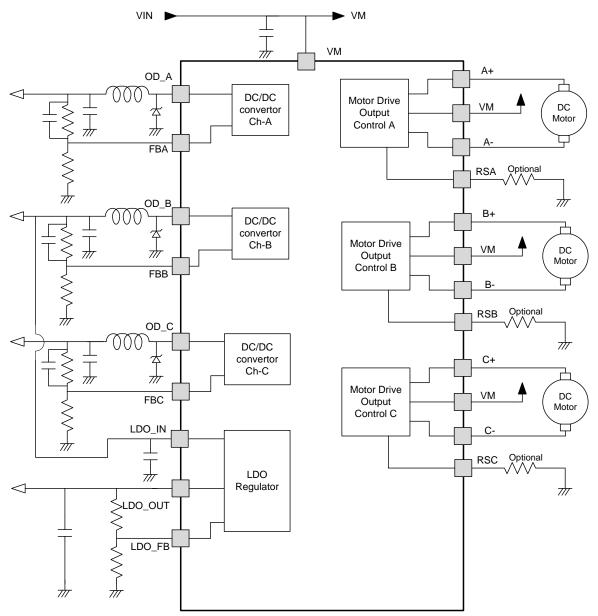

The DRV8808 device provides the integrated motor driver solution for printers. The chip has three full Hbridges and three buck DC-DC converters.

The output driver block for each consists of Nchannel power MOSFETs configured as full Hbridges to drive the motor windings. The device can be configured to use internal or external current sense for winding current control.

The SPI input pins are 3.3-V compatible and have inputs that are 5-V tolerant.

The DRV8808 has three DC-DC switched-mode buck converters to generate a programmable output voltage from 1 V up to 90% of  $V_{\rm M}$ , with up to 1.35-A load current capability.

The device is configured using the CSELECT terminal at start-up, and serial interface during run time.

An internal shutdown function is provided for protection, overcurrent short-circuit protection. undervoltage lockout, and thermal shutdown. Also, the device has the reset function at power on, and the input on the nReset pin.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)    |  |  |

|-------------|-------------|--------------------|--|--|

| DRV8808     | HTSSOP (48) | 12.50 mm x 6.10 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

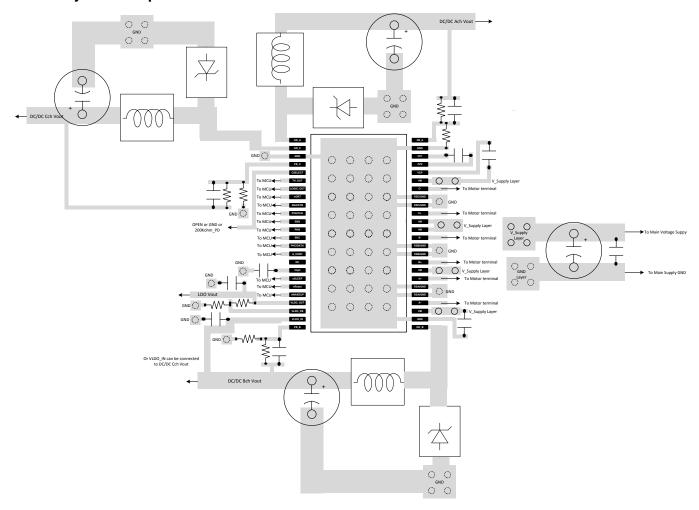

### **Typical Application Schematic**

# **Table of Contents**

| 1      | Features 1                           |    | 7.3 Feature Description                          | 14 |

|--------|--------------------------------------|----|--------------------------------------------------|----|

| 2      | Applications                         |    | 7.4 Device Functional Modes                      |    |

| 3      | Description 1                        |    | 7.5 Programming                                  | 32 |

| 4      | Revision History2                    | 8  | Application and Implementation                   |    |

| 5      | Pin Configuration and Functions      |    | 8.1 Application Information                      | 36 |

| 5<br>6 | Specifications6                      |    | 8.2 Typical Application                          | 36 |

| U      | 6.1 Absolute Maximum Ratings         | 9  | Power Supply Recommendations                     | 38 |

|        | 6.2 ESD Ratings                      | 10 | Layout                                           | 38 |

|        | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines                           |    |

|        | 6.4 Thermal Information              |    | 10.2 Layout Example                              | 38 |

|        | 6.5 Electrical Characteristics       | 11 | Device and Documentation Support                 | 39 |

|        | 6.6 Typical Characteristics          |    | 11.1 Trademarks                                  | 39 |

| 7      | Detailed Description 12              |    | 11.2 Electrostatic Discharge Caution             | 39 |

| •      | 7.1 Overview                         |    | 11.3 Glossary                                    | 39 |

|        | 7.2 Functional Block Diagram         | 12 | Mechanical, Packaging, and Orderable Information | 39 |

# 4 Revision History

#### Changes from Revision A (August 2011) to Revision B

**Page**

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN       |     |     |       | SHUNT |                                                  |  |  |

|-----------|-----|-----|-------|-------|--------------------------------------------------|--|--|

| NAME      | NO. | I/O | PU/PD | R     | DESCRIPTION                                      |  |  |

| A-        | 28  | 0   | _     | _     | Motor drive output for winding A-                |  |  |

| A+        | 31  | 0   | _     | _     | Motor drive output for winding A+                |  |  |

| A_CONT    | 15  | I   | Down  | 100k  | DC-DC A converter control (L = Enable)           |  |  |

| B-        | 36  | 0   | _     | _     | Motor drive output for winding B-                |  |  |

| B+        | 33  | 0   | _     | _     | Motor drive output for winding B+                |  |  |

| C-        | 42  | 0   | _     | _     | Motor drive output for winding C-                |  |  |

| C+        | 39  | 0   | _     | _     | Motor drive output for winding C+                |  |  |

| CP1       | 46  | 0   | _     | _     | Charge pump bucket capacitor output (low side)   |  |  |

| CP2       | 45  | 0   | _     | _     | Charge pump bucket capacitor output (high side)  |  |  |

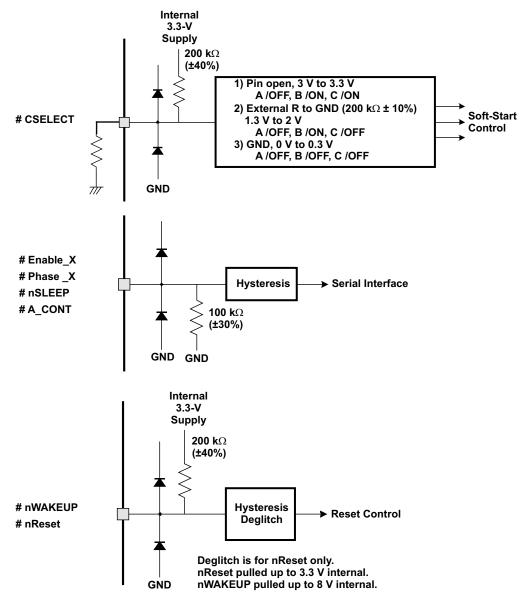

| CSELECT   | 5   | I   | Up    | 200k  | DC-DC converter startup selector                 |  |  |

| ENA / STB | 9   | I   | Down  | 100k  | Enable input for DC motor A control / SPI STROBE |  |  |

| ENB       | 11  | I   | Down  | 100k  | Enable input for DC motor B control              |  |  |

| ENC       | 13  | I   | Down  | 100k  | Enable input for DC motor C control              |  |  |

| FB_A      | 48  | I   | _     | _     | Feedback signal for DC-DC converter A            |  |  |

| FB_B      | 24  | I   | _     | _     | Feedback signal for DC-DC converter B            |  |  |

| FB_C      | 4   | I   | _     | _     | Feedback signal for DC-DC converter C            |  |  |

| GND       | 3   |     |       | _     | Ground                                           |  |  |

| GND       | 26  | _   | _     | _     | Ground                                           |  |  |

| GND       | 47  | _   | _     | _     | Ground                                           |  |  |

# Pin Functions (continued)

| PIN I/O    |     |     | SHUN  |      |                                                     |

|------------|-----|-----|-------|------|-----------------------------------------------------|

| NAME       | NO. | I/O | PU/PD | R    | DESCRIPTION                                         |

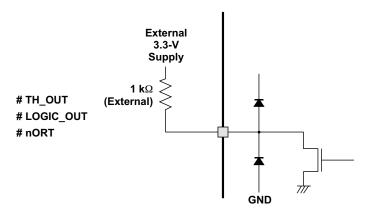

| LOGIC_OUT  | 7   | 0   | _     | _    | Information monitoring output (open drain)          |

| NC         | 16  | NC  | _     | _    | Do not connect                                      |

| nORT       | 8   | 0   | _     | _    | Reset output (open drain)                           |

| nReset     | 19  | I   | Up    | 200k | Reset input (L: reset, H/open: normal operation)    |

| nSLEEP     | 18  | I   | Down  | 100k | Enable/disable, SPI selector                        |

| nWAKEUP    | 20  | I   | Up    | 200k | Wake-up pin for DeepSleep mode (L = WAKEUP)         |

| OD_A       | 1   | 0   | _     | _    | Output for DC-DC switch mode regulator A            |

| OD_B       | 25  | 0   | _     | _    | Output for DC-DC switch mode regulator B            |

| OD_C       | 2   | 0   | _     | _    | Output for DC-DC switch mode regulator C            |

| PHA / CLK  | 10  | I   | Down  | 100k | Phase input for DC motor A control / SPI CLOCK      |

| PHB        | 12  | I   | Down  | 100k | Phase input for DC motor B control                  |

| PHC / DATA | 14  | I   | Down  | 100k | Phase input for DC motor C control / SPI DATA       |

| RSA / GND  | 30  | 0   | _     | _    | Motor drive current sensing resistor A / GND power  |

| RSKA / GND | 29  | 1   | _     | _    | Motor drive current sensing resistor A / GND Kelvin |

| RSB / GND  | 35  | 0   | _     | _    | Motor drive current sensing resistor B / GND power  |

| RSKB / GND | 34  | I   | _     | _    | Motor drive current sensing resistor B / GND Kelvin |

| RSC / GND  | 41  | 0   | _     | _    | Motor drive current sensing resistor C / GND power  |

| RSKC / GND | 40  | I   | _     | _    | Motor drive current sensing resistor C / GND Kelvin |

| TH_OUT     | 6   | 0   | _     | _    | Temperature warning output (open drain)             |

| V3p3       | 17  | 0   | _     | _    | Bypass for internal 3.3-V regulator                 |

| VCP        | 44  | 0   | _     | _    | Charge pump output                                  |

| VLDO_FB    | 22  | I   | _     | _    | LDO voltage regulator feed back                     |

| VLDO_IN    | 23  | I   | _     | _    | LDO voltage regulator input                         |

| VLDO_OUT   | 21  | 0   | _     | _    | LDO voltage regulator output                        |

| VM         | 27  | _   | _     | _    | Voltage supply for motors and regulators            |

| VM         | 32  | _   | _     |      | Voltage supply for motors and regulators            |

| VM         | 37  | _   | _     | _    | Voltage supply for motors and regulators            |

| VM         | 38  | _   | _     | _    | Voltage supply for motors and regulators            |

| VM         | 43  | _   | _     | _    | Voltage supply for motors and regulators            |

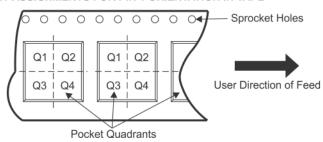

Figure 1. Input Pin Configuration

Figure 2. Open-Drain Output Pin Configuration

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                  |                                                                      | MIN  | MAX  | UNIT |

|------------------|----------------------------------------------------------------------|------|------|------|

| $V_{M}$          | Supply voltage                                                       |      | 40   | V    |

|                  | Logic input voltage, serial I/F, A_CONT, nReset, and so forth (2)    | -0.3 | 5.5  | V    |

|                  | TH_OUT, nORT, LOGIC_OUT, CSELECT                                     | -0.3 | 3.6  | V    |

|                  | nWAKEUP                                                              | -0.3 | 8    | V    |

|                  | Continuous total power dissipation (in case $\theta_{JA} = 20$ °C/W) |      | 4    | W    |

|                  | Continuous motor-drive output current for each H-bridge (100 ms)     |      | 2.5  | Α    |

|                  | Continuous DC-DC converter output current <sup>(3)</sup>             |      | 1.35 | Α    |

| $T_{J}$          | Operating junction temperature (1 hour)                              |      | 190  | °C   |

|                  | Lead temperature 1.6 mm (1/16 in) from case for 10 s                 |      | 260  | °C   |

| T <sub>stg</sub> | Storage temperature                                                  | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |  |                                                                                | VALUE | UNIT |

|--------------------|--|--------------------------------------------------------------------------------|-------|------|

|                    |  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> |  | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

|                                                            | MIN | NOM | MAX | UNIT |

|------------------------------------------------------------|-----|-----|-----|------|

| Supply voltage range, V <sub>M</sub> for motor control     | 18  | 27  | 38  | V    |

| Supply voltage range for DC-DC converter (V <sub>M</sub> ) | 7   | 27  | 38  | V    |

| Operating ambient temperature range                        | -10 |     | 85  | °C   |

| Operating junction temperature range                       | 0   |     | 135 | °C   |

#### 6.4 Thermal Information

|                        |                                              | DRV8808      |      |

|------------------------|----------------------------------------------|--------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | HTSSOP (DCA) | UNIT |

|                        |                                              | 48 PINS      |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 28.1         |      |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 15.6         |      |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 10.2         | 0000 |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.3          | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 10.1         |      |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 0.9          |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> The negative spike less than -5 V and narrower than 50-ns width should not cause any problem.

<sup>(3)</sup> May shut down due to regulator OCP.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.5 Electrical Characteristics

$T_1 = 0$ °C to 135°C.  $V_M = 7$  V to 38 V (unless otherwise noted)

|                         | PARAMETER                                  | TEST CO                               | ONDITIONS                         | MIN                 | TYP  | MAX                 | UNIT |

|-------------------------|--------------------------------------------|---------------------------------------|-----------------------------------|---------------------|------|---------------------|------|

| SUPPLY (SI              | LEEP) CURRENT                              | ·                                     |                                   |                     |      |                     |      |

| I <sub>SLEEP1</sub>     | Supply (sleep) current 1                   | nSLEEP = L,                           | DC-DC all off                     |                     | 3    | 5.5                 | mA   |

| I <sub>SLEEP2</sub>     | Supply (sleep) current 2                   | nSLEEP = L,<br>Regulators enabled     | V <sub>M</sub> = 8 V,<br>No load  |                     | 6    | 8                   | mA   |

| I <sub>SLEEP3</sub>     | Supply (sleep) current 3                   | nSLEEP = L,<br>Regulators enabled     | V <sub>M</sub> = 38 V,<br>No load |                     | 6    | 8                   | mA   |

| I <sub>DEEP_SL</sub>    | Supply (deep sleep) current <sup>(1)</sup> | V <sub>M</sub> = 38 V                 |                                   |                     | 0.7  | 1                   | mA   |

| DIGITAL IN              | TERFACE CIRCUIT                            |                                       |                                   | ·                   |      |                     |      |

| V <sub>IH</sub>         | Digital high-level input voltage           | Digital inputs                        |                                   | 2                   |      | 3.6                 | V    |

| I <sub>IH</sub>         | Digital high-level input current           | Digital inputs                        |                                   |                     |      | 100                 | μΑ   |

| V <sub>IL</sub>         | Digital low-level input voltage            | Digital inputs                        |                                   |                     |      | 0.8                 | V    |

| I <sub>IL</sub>         | Digital low-level input current            | Digital inputs                        |                                   |                     |      | 100                 | μΑ   |

| V <sub>hys</sub>        | Digital input hysteresis                   | Digital inputs                        |                                   |                     | 0.45 |                     | V    |

| T <sub>deg_nReset</sub> | nReset input deglitch time                 |                                       |                                   | 2.5                 |      | 7.5                 | μs   |

| T <sub>filt ACONT</sub> | A_CONT filter time <sup>(2)</sup>          |                                       |                                   | 30                  |      | 70                  | μs   |

| CHARGE-PI               | JMP VCP (CP = 0.1 μF to 0.47 μF,           | Cblk = 0.01 µF ±20%)                  |                                   | ·                   |      | *                   |      |

| V <sub>O</sub> (CP)     | Output voltage                             | $I_{LOAD} = 0 \text{ mA},$            | V <sub>M</sub> > 15 V             | V <sub>M</sub> + 10 | ,    | V <sub>M</sub> + 13 | V    |

| f(CP)                   | Switching frequency                        |                                       |                                   |                     | 1.6  |                     | MHz  |

| t <sub>start</sub>      | Start-up time                              | C <sub>Storage</sub> = 0.1 µF,        | V <sub>M</sub> ≥ 15 V             |                     | 0.5  | 2                   | ms   |

| V3P3 OUTP               | UT                                         |                                       |                                   |                     |      |                     |      |

| V <sub>3p3</sub>        | Output voltage (3)                         |                                       |                                   | 3                   | 3.3  | 3.6                 | V    |

| C <sub>bypass</sub>     | Output capacitor                           |                                       |                                   | 0.08                | 0.1  | 10                  | μF   |

|                         | CLOCK OSCI                                 | <u> </u>                              |                                   | -                   |      | ,                   |      |

| f <sub>OSCi</sub>       | System clock rrequency                     |                                       |                                   | 5.76                | 6.4  | 7.04                | MHz  |

|                         | OR DC-DC STARTUP SELECTION                 | 1                                     |                                   |                     |      |                     |      |

| V <sub>CS0</sub>        | DC-DC all off                              |                                       |                                   | 0                   |      | 0.3                 | V    |

| V <sub>CS1</sub>        | Turn ON ODB                                | Pull down by external                 | 200-kΩ resistor                   | 1.3                 |      | 2                   | V    |

| V <sub>CS2</sub>        | Turn ON ODB then ODC                       | As pin open                           |                                   | 3                   |      | 3.6                 | V    |

| VLDO REGI               | JLATOR (4)(5)(6)                           | <u> </u>                              |                                   | -                   |      | <u>'</u>            |      |

| VLDO <sub>IN</sub>      | LDO input voltage                          |                                       |                                   | 3                   |      | 3.6                 | V    |

| VLDO <sub>FB</sub>      | Feedback voltage                           |                                       |                                   |                     | 1    |                     | V    |

| \# BO                   |                                            | 1 V ≤ VLDO <sub>OUT</sub> ≤ 1.8       | V                                 |                     | ±5%  |                     |      |

| VLDO <sub>OUT</sub>     | Output voltage range                       | 1.8 V ≤ VLDO <sub>OUT</sub> ≤ 2       |                                   |                     | ±3%  |                     |      |

| I <sub>OUT</sub>        | Load capability                            |                                       |                                   |                     |      | 500                 | mA   |

| I <sub>OCP</sub>        | OCP current                                |                                       |                                   |                     | 725  | 1100                | mA   |

| t <sub>ldeg</sub>       | OCP deglitch                               |                                       |                                   | 3                   | 8    | 13                  | μs   |

| V <sub>ovp</sub>        | Overvoltage protection                     | % to nominal Voutx d (VFB increasing) | etected at VFB                    | 25%                 | 30%  | 35%                 |      |

| V <sub>uvp</sub>        | Undervoltage protection                    | % to nominal Voutx d (VFB decreasing) | etected at VFB                    | -25%                | -30% | -35%                |      |

<sup>(1)</sup> Deep Sleep shuts down majority of the device and runs minimal circuits (internal bias circuits and the nWAKEUP pin). Deep Sleep is entered by writing 1 to Setup Register, Bank 1, Bit 11. Device is restarted by pulling nWAKEUP pin low or power cycling V<sub>M</sub>. Deep Sleep functionality only available for V<sub>M</sub> > Vth<sub>VM+</sub>.

<sup>(2)</sup> A\_CONT is filtered for both high and low levels.

<sup>(3)</sup> V3p3 bypass pin is not meant to be used as a supply.

<sup>(4)</sup> LDO can be bypassed by either load configuration 1 or 2.

<sup>(5)</sup> Typical values for external components should be chosen such that when the tolerance is added to the typical, the values remain between the maximum and minimum specifications listed.

<sup>6)</sup> When LDO is not used, recommend connecting VLDO\_IN to GND, VLDO\_OUT to GND, and VLDO\_FB to FB\_B.

$T_J = 0$ °C to 135°C,  $V_M = 7$  V to 38 V (unless otherwise noted)

|                                  | PARAMETER                                                | TEST C                                               | ONDITIONS                                                       | MIN  | TYP            | MAX                     | UNIT           |

|----------------------------------|----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------|------|----------------|-------------------------|----------------|

| t <sub>Vdeg</sub>                | UVP/OVP deglitch time                                    |                                                      |                                                                 | 3    | 8              | 13                      | μs             |

| C <sub>L1</sub>                  |                                                          | Electrolytic load capa                               | acitance                                                        | 27   |                | 120                     | μF             |

| C <sub>ESR1</sub>                | Load bypass configuration 1                              | ESR of load capacita                                 | ance                                                            | 0.05 |                | 2                       | Ω              |

| C <sub>C1</sub>                  |                                                          | Ceramic load capaci                                  | tance                                                           | 0    |                | 0.4                     | μF             |

| C <sub>L2</sub>                  |                                                          | Electrolytic load capa                               | acitance                                                        | 80   | 100            | 120                     | μF             |

| C <sub>ESR2</sub>                | Load bypass configuration 2                              | ESR of load capacita                                 | ance                                                            | 0.05 |                | 0.2                     | Ω              |

| C <sub>C2</sub>                  |                                                          | Ceramic load capaci                                  | tance                                                           | 0    |                | 3                       | μF             |

| THREE DC-                        | DC CONVERTER                                             |                                                      |                                                                 |      |                |                         |                |

| V <sub>M OPE_X</sub>             | Operating supply voltage range ratio to V <sub>OUT</sub> | I <sub>O</sub> < 0.6 A                               | $Vth_{VM^-} < V_M < 7 V$                                        |      |                | 0.8 x<br>V <sub>M</sub> | V              |

|                                  |                                                          |                                                      | 20 V < V <sub>M</sub> < 38 V                                    |      |                | 0.9 x<br>V <sub>M</sub> |                |

| ODx                              | Regulator output voltage                                 | $20 \text{ V} < \text{V}_{\text{M}} < 40 \text{ V}$  | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}$ | -3%  | V <sub>O</sub> | 3%                      |                |

|                                  |                                                          |                                                      | 125°C < T <sub>J</sub> < 135°C                                  | -4%  | Vo             | 4%                      |                |

|                                  |                                                          | $6.5 \text{ V} < \text{V}_{\text{M}} < 20 \text{ V}$ |                                                                 | -5%  | Vo             | 5%                      |                |

|                                  |                                                          | $V_{M} = 7 \text{ V}, V_{O} = 5.5 \text{ V}$         | 1                                                               | -5%  | Vo             | 5%                      |                |

|                                  |                                                          | $V_{M} = 7 V, V_{O} = 1 V$                           | $0^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}$ | -3%  | V <sub>O</sub> | 3%                      |                |

|                                  |                                                          |                                                      | 125°C < T <sub>J</sub> < 135°C                                  | -4%  | $V_{O}$        | 4%                      |                |

|                                  |                                                          | $Vth_{VM^-} < V_M < 6.5 V$                           | , V <sub>O</sub> ≤ 3.3 V                                        | -5%  | Vo             | 5%                      |                |

| FBx                              | FBx pin voltage                                          |                                                      |                                                                 |      | 1              |                         | V              |

| $I_{O\ ODx}$                     | Output current (DC)                                      | V <sub>M</sub> > 15 V                                |                                                                 |      |                | 1.35                    | Α              |

| I <sub>O ODx2</sub>              | Output current (DC) at low $V_M$                         | $V_{M} = 7 \text{ V}, V_{O} = 5.5 \text{ V}$         | 1                                                               |      |                | 0.6                     | Α              |

| I <sub>O ODx3</sub>              | Output current (DC) at low V <sub>M</sub>                | $V_{M} = 7 \text{ V}, V_{O} = 3.3 \text{ V}$         |                                                                 |      |                | 1.2                     | Α              |

| R <sub>DSON</sub> <sup>(7)</sup> | FET on-resistance at 0.8 A for                           | T <sub>J</sub> = 70 °C                               |                                                                 |      | 0.85           | 1.05                    | Ω              |

|                                  | OD_x V <sub>M</sub> > 15 V                               | T <sub>J</sub> = 135 °C                              |                                                                 |      | 1              | 1.2                     |                |

| L                                | Inductor                                                 | V <sub>OUT</sub> = 1.0 V                             |                                                                 |      | 150            |                         | μΗ             |

|                                  |                                                          | V <sub>OUT</sub> ≥ 3.3 V                             |                                                                 |      | 330            |                         |                |

| С                                | Capacitor                                                | V <sub>OUT</sub> = 1.0 V                             |                                                                 | 270  |                | 330                     | μF             |

|                                  |                                                          | V <sub>OUT</sub> ≥ 3.3 V                             |                                                                 |      | 220            |                         |                |

| THREE DC-                        | DC CONVERTER PROTECTION                                  |                                                      |                                                                 |      |                |                         |                |

| I <sub>O DD ODx</sub>            | Overcurrent detect for OD_x source                       | Peak current in each                                 | ON cycle                                                        | 1.35 |                | 2.7                     | Α              |

| t <sub>ODXdeg</sub>              | Cycle by cycle Idetect deglitch                          |                                                      |                                                                 | 100  | 200            | 400                     | ns             |

| t <sub>ODXSD</sub>               | DC-DC shutdown filter                                    | Number of consecuti                                  | ive cycles with Idetect                                         |      | 4              |                         | chop<br>cycles |

| V <sub>ovpx</sub>                | Overvoltage protection                                   | % to nominal Voutx detected at VFB (VFB increasing)  |                                                                 | 25%  | 30%            | 35%                     |                |

| V <sub>uvpx</sub>                | Undervoltage protection                                  | % to nominal Voutx detected at VFB (VFB decreasing)  |                                                                 | -25% | -30%           | -35%                    |                |

| t <sub>VXdeg</sub>               | UVP/OVP deglitch time                                    |                                                      |                                                                 | 3    | 8              | 13                      | μs             |

| t <sub>sst</sub>                 | Start-up time with soft start                            |                                                      |                                                                 |      |                | 56                      | ms             |

| V <sub>stover</sub>              | Start-up overshoot                                       | Ratio to Vo                                          |                                                                 |      |                | 3%                      |                |

| V <sub>M</sub> SUPERV            | /ISORY <sup>(8) (9)</sup>                                |                                                      |                                                                 |      |                |                         |                |

| Vth <sub>VM</sub>                | nORT, for $V_M$ low threshold                            | V <sub>M</sub> decreasing                            |                                                                 | 4.5  | 5              | 6                       | V              |

| Vth <sub>VM+</sub>               | nORT, for V <sub>M</sub> high threshold                  | V <sub>M</sub> increasing                            |                                                                 | 5.5  | 6              | 6.79                    | V              |

$R_{DSON}$  at T = 135°C guaranteed by characterization. Production test will be done at T = 25°C/70°C.  $V_M$  must be  $V_M > Vth_{VM+}$  to start up internal DC-DC converter.

When V<sub>M</sub> goes down below Vth<sub>VM+</sub>, the VUVPx (undervoltage protection in DC-DC) are masked. The DC-DC converter is shut off by nORT assertion at Vth<sub>VM</sub> \_.

$T_J = 0$ °C to 135°C,  $V_M = 7$  V to 38 V (unless otherwise noted)

|                                | PARAMETER                                                   | TEST CONDITIONS                                                                        | MIN | TYP  | MAX  | UNIT |

|--------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|------|------|

| Vth <sub>VMh</sub>             | nORT, for V <sub>M</sub> detect hysteresis                  | $Vth_{VM+} - Vth_{VM-}$                                                                | 0.5 | 1    |      | V    |

| Vth <sub>VM2</sub>             | For motor driver off (10)                                   |                                                                                        |     |      | 15   | V    |

| t <sub>VMfilt</sub>            | Vth V <sub>M</sub> monitor filtering time                   | For Vth V <sub>M</sub> detect                                                          | 4   |      | 30   | μs   |

| t <sub>VM2filt</sub>           | Vth V <sub>M2</sub> monitor filtering time                  | For Vth V <sub>M2</sub> detect                                                         | 30  |      | 60   | ms   |

| THERMAL S                      | SHUTDOWN: TSD (11) (12)                                     |                                                                                        |     |      |      |      |

| T <sub>TSD</sub>               | Thermal shutdown set points                                 |                                                                                        | 150 | 170  | 190  | °C   |

| t <sub>TSDdeg</sub>            | TSD deglitch time                                           |                                                                                        | 30  | 60   | 90   | μs   |

|                                | URE WARNING: PRE-TSD <sup>(13)</sup> (12)                   | -                                                                                      |     |      |      |      |

| PreTSD                         | Temperature warning                                         | Assert at TH_OUT pin                                                                   | 115 | 135  | 155  | °C   |

| OPEN-DRA                       | IN OUTPUTS (NORT, LOGIC_OUT,                                | TH_OUT)                                                                                |     |      | "    |      |

| V <sub>OH</sub>                | High-state voltage                                          | RL = 1 $k\Omega$ to 3.3 V                                                              | 3   |      |      | V    |

| V <sub>OL</sub> (14)           | Low-state voltage                                           | RL = 1 $k\Omega$ to 3.3 V                                                              |     |      | 0.3  | V    |

| I <sub>OL</sub> (14)           | Low-state sink current                                      | Vo = 0.25 V                                                                            | 2   |      |      | mA   |

| t <sub>r</sub> <sup>(15)</sup> | Rise time                                                   | 10% to 90%                                                                             |     |      | 1    | μs   |

| t <sub>f</sub> (15)            | Fall time                                                   | 90% to 10%                                                                             |     |      | 50   | ns   |

| NORT DEL                       | AY: STARTUP SEQUENCE (16) (17)                              | 1                                                                                      |     |      |      |      |

| Tord1                          | nORT delay 1                                                | Reset deassertion from Vth <sub>VM+</sub> < V <sub>M</sub> , for DC/DC wake up failing | 200 | 300  | 390  | ms   |

| Tord3                          | DC-DC turn on delay                                         | From one DC-DC wake up to following DC-DC to go soft-start sequence                    | 5   | 10   | 15   | ms   |

| Tord4                          | nORT delay 4                                                | Reset deassertion from 2nd DC-DC wake up                                               | 60  | 120  | 180  | ms   |

| NRESET IN                      | PUT <sup>(16)</sup>                                         |                                                                                        |     |      |      |      |

| Treset                         | nReset assertion to nORT assertion delay                    | nReset falling to nORT failing                                                         |     | 5    | 10   | μs   |

| H-BRIDGE                       | DRIVERS (OUTX+ AND OUTX-) CO                                | ONDITION: V <sub>M</sub> = 15 V to 38 V <sup>(18)</sup>                                |     |      | ·    |      |

| I <sub>OUT1(max)</sub>         | Peak output current 1                                       | Less than 500-ns period                                                                |     |      | 6.8  | Α    |

| I <sub>OUT2(max)</sub>         | Peak output current 2                                       | Less than 100-ms period                                                                |     |      | 2.42 | Α    |

| R <sub>DSON</sub>              | FET ON resistance at 0.8 A                                  | $T_J = 70$ °C                                                                          |     | 0.55 | 0.65 | Ω    |

|                                |                                                             | T <sub>J</sub> = 135°C                                                                 |     | 0.7  | 0.85 |      |

| I <sub>CEX</sub>               | Output leakage current                                      | VOUTX = 0 V or 10                                                                      |     |      | 10   | μA   |

| I <sub>OC Motor</sub>          | Motor overcurrent threshold for each H-bridge (18)          |                                                                                        | 3   |      | 8    | Α    |

| Fchop                          | Motor chopping frequency = FOSCM/8                          |                                                                                        | 90  | 100  | 110  | kHz  |

| DC MOTOR                       | DRIVERS                                                     |                                                                                        |     |      |      |      |

| t <sub>r</sub>                 | Rise time                                                   | V <sub>M</sub> = 35 V<br>20% to 80%                                                    | 50  |      | 200  | ns   |

| t <sub>f</sub>                 | Fall time                                                   | V <sub>M</sub> = 35 V<br>20% to 80%                                                    | 50  |      | 200  | ns   |

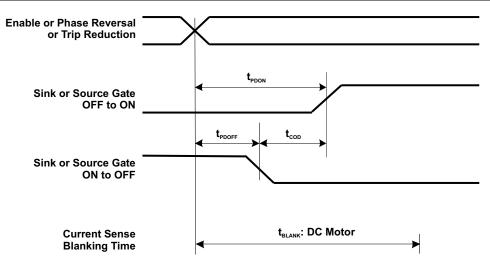

| t <sub>PDOFF</sub>             | Enable or strobe detection to sink or source gate OFF delay |                                                                                        | 50  | 150  | 400  | ns   |

<sup>(10)</sup> No nORT assertion to  $Vth_{VM2}$  detection. (11) TSD does not need thermal hysteresis.

<sup>(12)</sup> Parametric guaranteed by characterization. Not tested in production.

<sup>(13)</sup> PreTSD does not need thermal hysteresis.

<sup>(14)</sup> Production test only measures Vol and lol to ensure timing.

<sup>(15)</sup> t<sub>r</sub> and t<sub>f</sub> dominated by external capacitance, pullup resistance, and open-drain NMOS R<sub>DSON</sub>.

(16) This includes asynchronous timing deviation between the event to the timer clock.

<sup>(17)</sup> nORT assertion delay is configurable and defined in the serial register section.

<sup>(18)</sup> When the overcurrent is detected, all the H-bridges are shut down and assert nORT per shutdown configuration.

$T_J = 0$ °C to 135°C,  $V_M = 7$  V to 38 V (unless otherwise noted)

|                       | PARAMETER                                                  | TEST CONDITIONS      | MIN                 | TYP  | MAX  | UNIT |

|-----------------------|------------------------------------------------------------|----------------------|---------------------|------|------|------|

| t <sub>COD</sub>      | Crossover delay time to prevent shoot through              |                      | 100 <sup>(19)</sup> | 600  | 1000 | ns   |

| t <sub>PDON</sub>     | Enable or strobe detection to sink or source gate ON delay |                      |                     | 750  |      | ns   |

| t <sub>ldeg</sub>     | MISD BLANK                                                 | [00] <sup>(20)</sup> | 1.80                | 2.25 | 2.95 |      |

|                       |                                                            | [01] (21)            | 1.20                | 1.50 | 2.30 |      |

|                       |                                                            | [10] (22)            | 2.35                | 3.00 | 3.65 | μs   |

|                       |                                                            | [11] <sup>(23)</sup> | 2.95                | 3.75 | 4.30 |      |

| T <sub>blank</sub>    | TBLANK                                                     | [00] (24)            | 3.05                | 3.45 | 5.50 |      |

|                       |                                                            | [01] (25)            | 1.90                | 2.20 | 4.15 |      |

|                       |                                                            | [10] (26)            | 4.15                | 4.70 | 6.75 | μs   |

|                       |                                                            | [11] <sup>(27)</sup> | 5.30                | 5.95 | 8.25 |      |

| VRS <sub>TRIP</sub>   | Internal current trip                                      | 00                   | 1.18                | 1.4  | 1.62 |      |

|                       |                                                            | 01                   | 1.48                | 1.7  | 1.92 |      |

|                       |                                                            | 10                   | 1.68                | 1.9  | 2.12 | Α    |

|                       |                                                            | 11                   | 1.98                | 2.2  | 2.42 |      |

|                       | External resistor sense voltage trip threshold             | 00                   | 165                 | 185  | 205  |      |

|                       |                                                            | 01                   | 190                 | 210  | 230  |      |

|                       |                                                            | 10                   | 240                 | 260  | 280  | mV   |

|                       |                                                            | 11                   | 290                 | 310  | 330  |      |

| P <sub>minp</sub>     | Minimum pulse width (phase)                                | (19)                 |                     |      | 1    | μs   |

| P <sub>mine</sub>     | Minimum pulse width (enable)                               | (19)                 |                     |      | 1    | μs   |

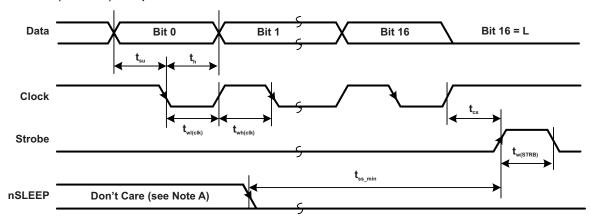

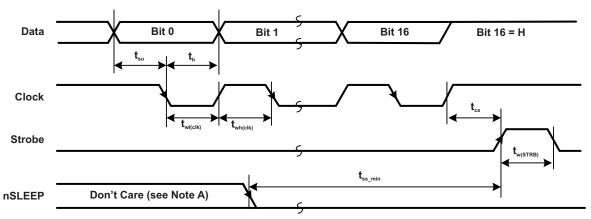

| SERIAL INT            | ERFACE <sup>(28)</sup>                                     |                      |                     |      |      |      |

| f(CLK)                | Clock frequency                                            |                      |                     |      | 25   | MHz  |

| t <sub>wh</sub> (CLK) | Minimum high-level pulse width                             |                      | 10                  |      |      | ns   |

| t <sub>wl</sub> (CLK) | Minimum low-level pulse width                              |                      | 10                  |      |      | ns   |

| t <sub>dcs</sub>      | Setup time, DATA to CLK↓                                   |                      | 10                  |      |      | ns   |

| t <sub>dch</sub>      | Hold time, CLK↓ to DATA                                    |                      | 10                  |      |      | ns   |

| t <sub>dss</sub>      | Setup time, DATA to STROBE↑                                |                      | 10                  |      |      | ns   |

| t <sub>dsh</sub>      | Hold time, STROBE↑ to DATA                                 |                      | 10                  |      |      | ns   |

| t <sub>css</sub>      | Setup time, CLK↓ to STROBE↑                                |                      | 20 <sup>(29)</sup>  |      |      | ns   |

| t <sub>csh</sub>      | Hold time, STROBE↑ to CLK↓                                 |                      | 20(29)              |      |      | ns   |

| t <sub>nss</sub>      | Setup time, nSLEEP↓ to STROBE↑                             |                      | 4 <sup>(30)</sup>   |      |      | μs   |

| t <sub>nsh</sub>      | Hold time, STROBE↑ to nSLEEP↑                              |                      | 10                  |      |      | ns   |

| t <sub>w</sub> (STRB) | Minimum strobe pulse width                                 |                      | 20                  |      |      | ns   |

- (19)  $t_{COD}$ ,  $P_{minp}$ , and  $P_{mine}$  not production tested. (20) 3 to 4 periods Fosc/4 + 1 Fosc

- (21) 2 to 3 periods Fosc/4 + 1 Fosc

- (22) 4 to 5 periods Fosc/4 + 1 Fosc

- (23) 5 to 6 periods Fosc/4 + 1 Fosc

- (24) 3 Fosc/8 (can add up to 1 additional Fosc/8 + 1.5 Fosc at phase or enable change due to asynchronous ambiguity)

- (25) 2 Fosc/8 (can add up to 1 additional Fosc/8 + 1.5 Fosc at phase or enable change due to asynchronous ambiguity)

- (26) 4 Fosc/8 (can add up to 1 additional Fosc/8 + 1.5 Fosc at phase or enable change due to asynchronous ambiguity)

- (27) 5 Fosc/8 (can add up to 1 additional Fosc/8 + 1.5 Fosc at phase or enable change due to asynchronous ambiguity)

- (28) Serial interface timing will not be tested parametrically in production.

(29) DATA value at STROBE is address bit for Setup and Extended Setup register so setup and hold times apply to DATA relative to STROBE. CLK and DATA also require setup and hold times relative to each other. Therefore, CLK and STROBE setup and hold timing is the summation of both.

- (30) Internal filter on nSLEEP to STROBE drives this specification.

Submit Documentation Feedback

Copyright © 2009-2015, Texas Instruments Incorporated

$T_J = 0$ °C to 135°C,  $V_M = 7$  V to 38 V (unless otherwise noted)

|                  | PARAMETER                                           | TEST CONDITIONS                                                                        | MIN | TYP | MAX  | UNIT |

|------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------|-----|-----|------|------|

| SERIAL           | INTERFACE: ID MONITOR FUNCTION                      | DE <sup>(31)</sup>                                                                     |     |     |      |      |

| t <sub>ODL</sub> | 0 data output delay bit 3 to 0 (ext-setup) = (1100) | From strobe rise to Logic_out $(1 \text{ k}\Omega \text{ to external } 3.3 \text{ V})$ |     |     | 4000 | ns   |

| t <sub>ODH</sub> | 1 data output delay bit 3 to 0 (ext-setup) = (1111) |                                                                                        |     |     | 4000 | ns   |

(31) Serial interface timing will not be tested parametrically in production.

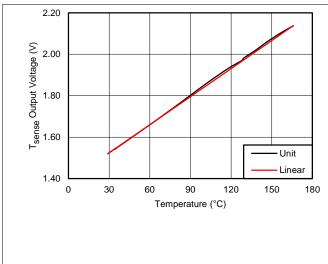

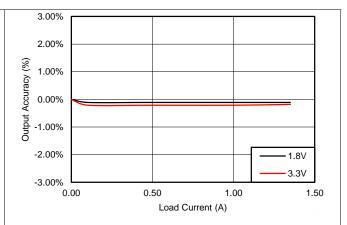

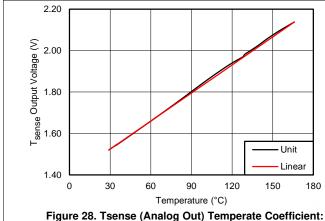

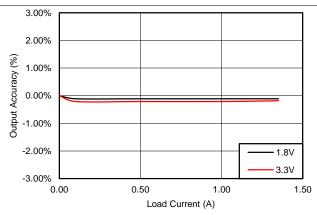

# 6.6 Typical Characteristics

Figure 3. Tsense (Analog Out) Temperate Coefficient: Voltage Plot Example (Typical)

Figure 4. DC-DC Converter - DC Load Regulation Example (Typical)

Copyright © 2009–2015, Texas Instruments Incorporated

Product Folder Links: DRV8808

# 7 Detailed Description

#### 7.1 Overview

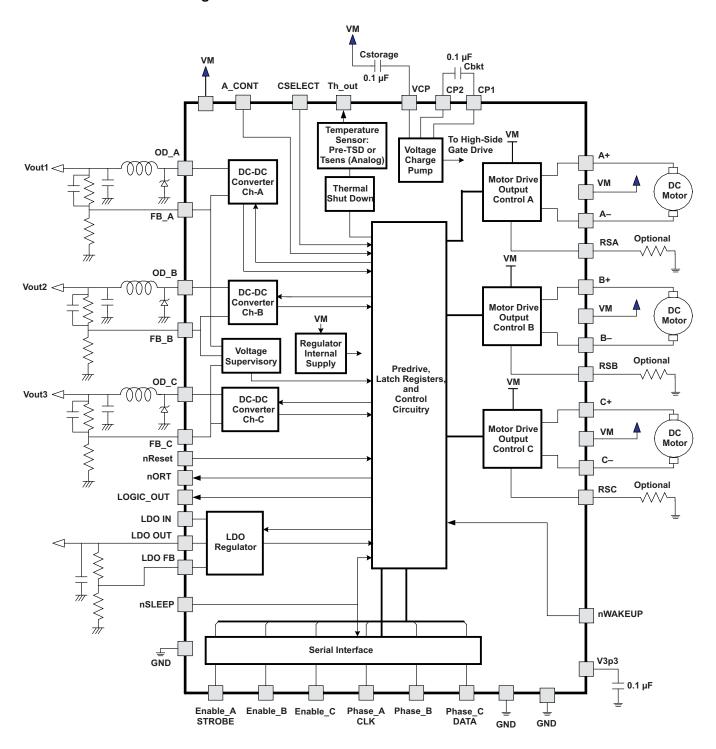

The Combo Motor Driver provides the integrated motor driver solution for printers and other applications. The chip has three full H-bridges and three Buck DC-DC converters, and one LDO.

The output driver block for each consists of N-channel power MOSFET's configured as full H-bridges to drive the motor windings. Device can be configured to utilize internal or external current sense for winding current control.

The SPI input pins are 3.3-V compatible and 5-V tolerant inputs.

The Combo Motor Driver has three, DC-DC switch mode buck converters to generate a programmable output voltage.

The device is configured using the CSELECT terminal at start up, and serial interface during run time.

An internal shutdown function is provided for over current protection, short circuit protection, under voltage lockout and thermal shutdown.

The device also has the reset function at power on, and the input on nReset pin.

## 7.2 Functional Block Diagram

Copyright © 2009–2015, Texas Instruments Incorporated

Submit Documentation Feedback

### 7.3 Feature Description

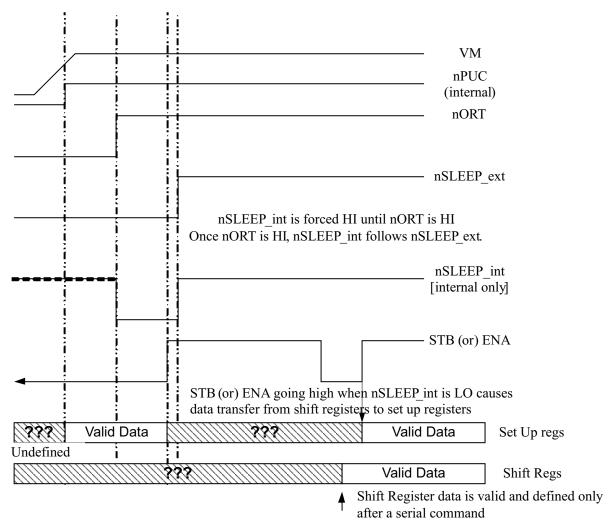

#### 7.3.1 Setup Mode, Extended Setup Mode, Power-Down Mode

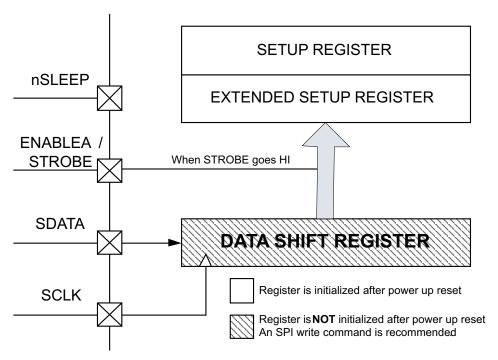

The motor output mode is configured through the SIP (DATA, CLK and STROBE) when nSLEEP = L. After set up, the nSLEEP pin must be pulled high for normal motor drive control. The value on the DATA line at the positive edge of STROBE when nSLEEP is low, selects whether the data is written to the Setup or Extended Setup registers. Setup is selected for DATA = L; Extended Setup is selected for DATA = H.

The condition, which the device requires for set up (initialize), is after the nORT (Reset) output goes H level from L level (power on, recovery from  $V_M < 7$  V). During nSLEEP in L level, all the motor-drive functions are shut down and their outputs are high-impedance state. This device forces motor-driver functions to shut down for the power-down mode, and is not damaged even if nSLEEP is asserted during motor driving.

Data is shifted at all times, regardless of nSLEEP. Care must be taken to ensure valid data has been shifted into the internal shift register, before the STROBE rising edge, occurs while nSLEEP is LO.

#### 7.3.1.1 Operation Setup Register Bit Assignment

Table 1. Setup Registers (1) (2) (3)

| BANK | BIT | FUNCTION            | DEFAULT | COMMENT                  |

|------|-----|---------------------|---------|--------------------------|

| _    | 0   | Tblank A 0          | 0       | 00: 3.75 μs, 01: 2.50 μs |

|      | 1   | Tblank A 1          | 0       | 10: 5.00 μs, 11: 6.25 μs |

|      | 2   | Tblank B 0          | 0       | 00: 3.75 μs, 01: 2.50 μs |

|      | 3   | Tblank B 1          | 0       | 10: 5.00 μs, 11: 6.25 μs |

|      | 4   | Tblank C 0          | 0       | 00: 3.75 μs, 01: 2.50 μs |

| 0    | 5   | Tblank C 1          | 0       | 10: 5.00 μs, 11: 6.25 μs |

|      | 6   | DC-DC A Minoff Time | 0       | 0: 2.2 μs, 1: 6.6 μs     |

|      | 7   | DC-DC A SW          | 1       |                          |

|      | 8   | DC-DC B SW          | CSELECT | 0: On<br>1: Off          |

|      | 9   | DC-DC C SW          | CSELECT | ৩                        |

|      | 10  | MOTOR CHOPPING 0    | 0       | 00: 100 kHz, 01: 50 kHz  |

|      | 11  | MOTOR CHOPPING 1    | 0       | 10: 133 kHz, 11: 200 kHz |

|      | 12  | RESET DELAY CONTROL | 0       | 0: Disable, 1: Enable    |

|      | 13  | LDO ENABLE          | Note 1  | 0: On, 1: Off            |

|      | 14  | DC-DC B Minoff Time | 0       | 0: 2.2 μs, 1: 6.6 μs     |

|      | 15  | Bank Change         | 0       | 0: Bank0, 1: Bank1       |

<sup>(1)</sup> The LDO default follows the DC/DC B default value based on CSELECT.

<sup>(2)</sup> All bits go to default for VM < Vth<sub>VM</sub>, nReset = L.

<sup>(3)</sup> RESET DELAY CONTROL set to 1 delays nORT assertion by 100 us typical. Range is 85 us to 125 us.

# **Feature Description (continued)**

Table 1. Setup Registers (1) (2) (3) (continued)

|      |     | rable 1. Setup riegisters | (continued) |                                                               |  |

|------|-----|---------------------------|-------------|---------------------------------------------------------------|--|

| BANK | BIT | FUNCTION                  | DEFAULT     | COMMENT                                                       |  |

|      | 0   | MISD BLANK AB 0           | 0           | 00: 2.25 μs, 01: 1.50 μs                                      |  |

|      | 1   | MISD BLANK AB 1           | 0           | 10: 3.00 µs, 11: 3.75 µs                                      |  |

|      | 2   | MISD BLANK C 0            | 0           | 00: 2.25 μs, 01: 1.50 μs                                      |  |

|      | 3   | MISD BLANK C 1            | 0           | 10: 3.00 µs, 11: 3.75 µs                                      |  |

|      | 4   | VRS A                     | 0           | 0: Disable, 1: Enable                                         |  |

|      | 5   | VRS A Level 0             | 0           | VRSA = 0:<br>00: 1.4 A, 01: 1.7 A<br>10: 1.9 A, 11: 2.2 A     |  |

|      | 6   | VRS A Level 1             | 0           | VRSA = 1:<br>00: 185 mV, 01: 210 mV<br>10: 260 mV, 11: 310 mV |  |

|      | 7   | DC-DC C Minoff Time       | 0           | 0: 2.2 μs, 1: 6.6 μs                                          |  |

|      | 8   | VRS B                     | 0           | 0: Disable, 1: Enable                                         |  |

| 1    | 9   | VRS B Level 0             | 0           | VRSB = 0:<br>00: 1.4 A, 01: 1.7 A<br>10: 1.9 A, 11: 2.2 A     |  |

|      | 10  | VRS B Level 1             | 0           | VRSB = 1:<br>00: 185 mV, 01: 210 mV<br>10: 260 mV, 11: 310 mV |  |

|      | 11  | DEEP SLEEP                | 0           | 0: Disable, 1: Enable                                         |  |

|      | 12  | VRS C                     | 0           | 0: Disable, 1: Enable                                         |  |

|      | 13  | VRS C Level 0             | 0           | VRSC = 0:<br>00: 1.4 A, 01: 1.7 A<br>10: 1.9 A, 11: 2.2 A     |  |

|      | 14  | VRS C Level 1             | 0           | VRSC = 1:<br>00: 185 mV, 01: 210 mV<br>10: 260 mV, 11: 310 mV |  |

|      | 15  | Bank Change               | 0           | 0: Bank0, 1: Bank1                                            |  |

### 7.3.1.2 Operation Extended Setup Register Bit Assignment

Table 2. Extended Setup Register (1) (2)

| BANK         | BIT | FUNCTION          | DEFAULT | COMMENT                      |

|--------------|-----|-------------------|---------|------------------------------|

| NA           | 0   | Signal Select 0   | 0       | See Logic_Out Table          |

|              | 1   | Signal Select 1   | 0       |                              |

|              | 2   | Signal Select 2   | 0       |                              |

|              | 3   | Signal Select 3   | 0       |                              |

|              | 4   | DCDC/LDO ISD Mask | 0       | 0: Disable, 1: Enable        |

|              | 5   | DCDC/LDO VSD Mask | 0       | 0: Disable, 1: Enable        |

|              | 6   | Motor ISD Mask    | 0       | 0: Disable, 1: Enable        |

| 7            |     | TSD Mask          | 0       | 0: Disable, 1: Enable        |

| 8<br>9<br>10 | 8   | Reset Mask C      | 0       | 0: Disable, 1: Enable        |

|              | 9   | Reset Mask B      | 0       | 0: Disable, 1: Enable        |

|              | 10  | Reset Mask A      | 0       | 0: Disable, 1: Enable        |

|              | 11  | Reset Mask SR     | 0       | 0: Disable, 1: Enable        |

|              | 12  | Pre TSD           | 0       | 0: TSD-20C, 1: Analog output |

|              | 13  | TSD Cont0         | 0       | See TSD Control Table        |

|              | 14  | TSD Cont1         | 0       |                              |

|              | 15  | MISD Cont         | 0       | See MISD Control Table       |

# Table 3. TSD Control - Operation After Detected TSD

| TSD<br>CONT1 | TSD<br>CONT0 | DC-DC | MOTORS | NORT  | LDO | RELEASED BY                                                |

|--------------|--------------|-------|--------|-------|-----|------------------------------------------------------------|

| 0            | 0            | OFF   | OFF    | LOW   | OFF | $V_M < Vth_{VM-}$ or nReset = L                            |

| 0            | 1            | ON    | OFF    | HIGH  | ON  | $V_M < Vth_{VM-}$ or nReset = L or nSLEEP L > H transition |

| 1            | 0            | ON    | OFF    | PULSE | ON  | $V_M < Vth_{VM-}$ or nReset = L or nSLEEP L > H transition |

| 1            | 1            | OFF   | OFF    | LOW   | OFF | $V_M < Vth_{VM-}$ or nReset = L                            |

#### Table 4. MISD Control – Operation After Detected Motor OCP

| MISD CONT | DC-DC | MOTORS | NORT      | LDO | RELEASED BY                                                                 |

|-----------|-------|--------|-----------|-----|-----------------------------------------------------------------------------|

| 0         | ON    | OFF    | PULSE (1) | ON  | V <sub>M</sub> < Vth <sub>VM</sub> or nReset = L or nSLEEP L > H transition |

| 1         | OFF   | OFF    | LOW       | OFF | $V_M < Vth_{VM-}$ or nReset = L                                             |

(1) PULSE in Control Tables is 40-ms duration.

<sup>(1)</sup> All bits go to default for V<sub>M</sub> < Vth<sub>VM</sub>., nReset = L.

(2) Bits [11:8] are selective shutdown bits. Setting to a 1 makes faults on the associated regulator only shutdown that regulator and allows restart on an nSLEEP L > H transition. Setting to 0 shuts everything down and restarts only for V<sub>M</sub> < Vth<sub>VM</sub> or nReset = L.

|  | Table | 5. | Logic_ | Out |

|--|-------|----|--------|-----|

|--|-------|----|--------|-----|

| SIGNAL SELECT | FUNCTION (LOGIC_OUT OUTPUT)                   |

|---------------|-----------------------------------------------|

| 0000          | Detect OCP/UVP/OVP on A, output L             |

| 0001          | Detect OCP/UVP/OVP on B, output L             |

| 0010          | Detect OCP/UVP/OVP on C, output L             |

| 0011          | Detect OCP on DC-DC/LDO regulator, output L   |

| 0100          | Detect UVP, output L                          |

| 0101          | Detect OVP, output L                          |

| 0110          | Detect OCP on motor, output L                 |

| 0111          | Detect TSD, output L                          |

| 1000          | Revision code bit 0                           |

| 1001          | Revision code bit 1                           |

| 1010          | Revision code bit 2                           |

| 1011          | Device code bit 0                             |

| 1100          | Device code bit 1                             |

| 1101          | N/A                                           |

| 1110          | Detect OCP/UVP/OVP on LDO regulator, output L |

| 1111          | Fix, output H                                 |

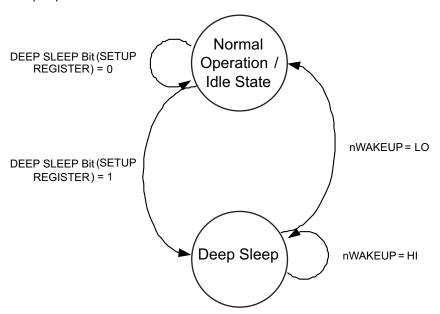

### 7.3.1.3 Deep Sleep Mode

Deep sleep mode can be entered by setting the deep sleep bit (bit 11) on the Setup register to HI. Once deep sleep mode is entered, every single subsystem is disabled, except the block necessary to regain power by making the nWAKEUP input pin LO.

Figure 5. Deep Sleep Mode

#### 7.3.1.4 DC Motor Drive

H-bridges A, B, and C can be controlled by using the ENABLE\_X and PHASE\_X control lines.

The H-bridge driver operation is available for  $V_M > 15 \text{ V}$ .

Internal current sense functionality is present by default. External sensing can be enabled through the serial interface. If enabled, the sense resistor must be placed externally.

#### NOTE

A capacitor, not larger than 2200 pF, can be placed between each H-bridge output to GND for EMI suppression purposes. It will increase the peak current but will have no impact on the operation.

Figure 6. Crossover and Blanking Timing for H-Bridge

The dc motor H-bridges include a t<sub>BLANK</sub> period to ignore huge current spike due to rush current to varistor capacitance.

#### 7.3.1.5 Short/Open for Motor Outputs

When a short/open situation happens, the protection circuit prevents device damage under certain conditions (short at start-up, etc).

Shutdown is released based on MISD Control in the Extended Setup register.

| FAULT<br>CONDITION | NSLEEP | ENABLEX | PHASEX | + HIGH SIDE | + LOW SIDE | – HIGH SIDE | - LOW SIDE |

|--------------------|--------|---------|--------|-------------|------------|-------------|------------|

| 0                  | 0      | X       | X      | OFF         | OFF        | OFF         | OFF        |

| 0                  | 1      | 0       | X      | OFF         | OFF        | OFF         | OFF        |

| 0                  | 1      | 1       | 0      | OFF         | ON         | ON          | OFF        |

| 0                  | 1      | 1       | 1      | ON          | OFF        | OFF         | ON         |

| Motor OCP          | X      | X       | X      | OFF         | OFF        | OFF         | OFF        |

| TSD                | Х      | Х       | Х      | OFF         | OFF        | OFF         | OFF        |

Table 6. DC Motor-Drive Truth Table (1)

(1) X = Don't care

#### 7.3.1.6 Charge Pump

The charge-pump voltage generator circuit utilizes, external storage, and bucket capacitors. It provides the necessary voltage to drive the high-side switches, for both DC-DC regulators and motor driver. The charge-pump circuit is driven at a frequency of 1.6 MHz (nom). Recommended bucket capacitance (connected from CP1 to CP2) is 10 nF, rated at 55 V (minimum), and storage capacitance is 0.1  $\mu$ F, at 16 V (minimum). The charge-pump storage capacitor, Cstorage, should be connected from the CP output to V<sub>M</sub>.

For power save in sleep mode, the charge pump is stopped when  $N_SLEEP = L$  and all three regulators are turned OFF. When the part is powered up, the charge pump is started first after the CSELECT capture and, 10 ms later from the CP startup, the first regulator is started up.

| Table 7. Charge P | ump <sup>(1)</sup> | (2) |

|-------------------|--------------------|-----|

|-------------------|--------------------|-----|

| FAULT CONDITION | DC-DC CH-A | DC-DC CH-B | DC-DC CH-C | NSLEEP | CHARGE PUMP |

|-----------------|------------|------------|------------|--------|-------------|

| X               | OFF        | OFF        | OFF        | 0      | OFF         |

| X               | ON         | X          | X          | X      | ON          |

| X               | X          | ON         | X          | X      | ON          |

| X               | X          | Χ          | ON         | X      | ON          |

| 0               | X          | Χ          | X          | 1      | ON          |

| Motor OCP       | X          | X          | X          | 1      | ON          |

| TSD             | OFF        | OFF        | OFF        | X      | OFF         |

<sup>(1)</sup> X = Don't care

#### 7.3.1.7 DC-DC Converters

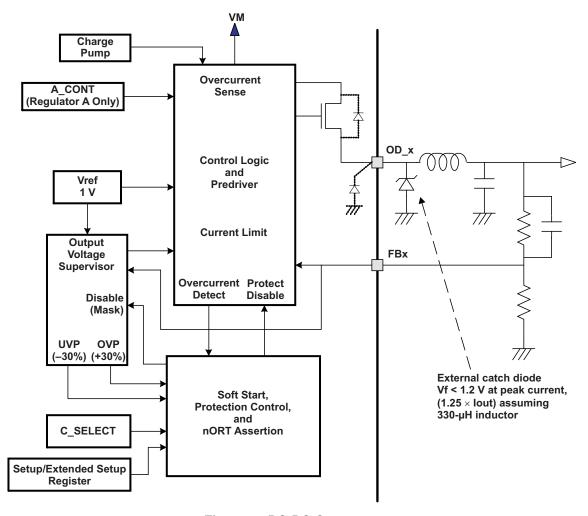

Figure 7. DC-DC Converter

This is a switch-mode regulator with integrated switches, to provide a programmed output set by the feedback terminal. The DC-DC converter has a variable duty cycle topology. External filtering (inductor and capacitor) and external catch diode are required. The output voltage is short circuit protected.

The regulator has a soft-start function to limit the rush current during start-up. It is achieved by using VFB ramp during soft start.

Product Folder Links: DRV8808

Submit Documentation Feedback

<sup>(2)</sup> DC=DC status in fault condition is determined by serial register settings, TSD Control table, and MISD Control table. These tables define status of charge pump.

For unused DC-DC converter channels, the external components can be removed if the channel is set to inactive by the CSELECT pin and register bits. Recommend connecting unused FB pin to GND or V3p3 (pin 17).

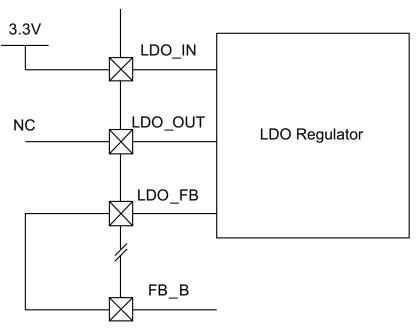

Figure 8. Unused LDO Recommended Connections

For proper termination, it is recommended that, if left unused, the LDO terminals be connected in the following fashion:

- 1. LDO IN must be powered by an input voltage greater than 1 V.

- 2. LDO OUT must be left disconnected.

LDO Feed Back must be connected to the DC/DC Converter Channel B Feed Back terminal.

Table 8. CSELECT for Start-Up (1) (2) (3)

| CSELECT                        | PIN VOLTAGE    | DCDC_A | DCDC_B | DCDC_C |

|--------------------------------|----------------|--------|--------|--------|

| Gnd                            | 0 V to 0.3 V   | OFF    | OFF    | OFF    |

| Pull down (by external 200 kΩ) | 1.3 V to 2.0 V | OFF    | ON     | OFF    |

| OPEN                           | 3.0 V to 3.3 V | OFF    | ON     | ON     |

- (1) The CSELECT pin is connected to internal 3.3-V supply through 200-k $\Omega$  resister.

- (2) This CSELECT pin control is valid after the PowerON Reset is initiated. Once the Setup Register is set, the DC-DC control follows the bits 7 to 9 on the Setup Register, bank 0, until the next PowerON Reset event occurred.

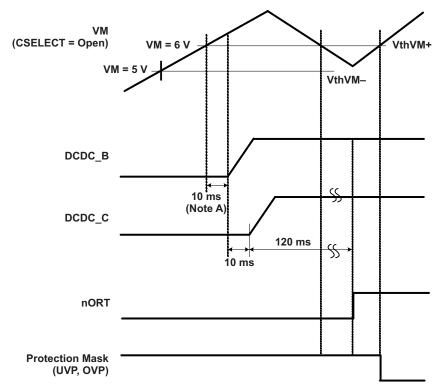

- (3) For OPEN case, B starts up 1st and C follows after 10-ms delay.

**Table 9. Regulator A Control**

| SETUP REGISTER BANK 0, BIT 7 | A_CONT | DCDC_A |

|------------------------------|--------|--------|

| 0                            | 0      | ON     |

| 0                            | 1      | OFF    |

| 1                            | 0      | OFF    |

| 1                            | 1      | OFF    |

#### 7.3.1.8 nReset: Input for System Reset

nReset pin assertion stops all the DC-DC converters and H-bridges. It also resets all the register contents to default values. After deassertion of input, device follows the initial start-up sequence. The CSELECT state is captured after the nReset deassertion (L > H).

The input is pulled up to internal 3.3 V by a 200- $k\Omega$  resistor. When the pin is H or left open, the reset function is released. Also it has deglitch filter of 2.5  $\mu$ s to 7.5  $\mu$ s.

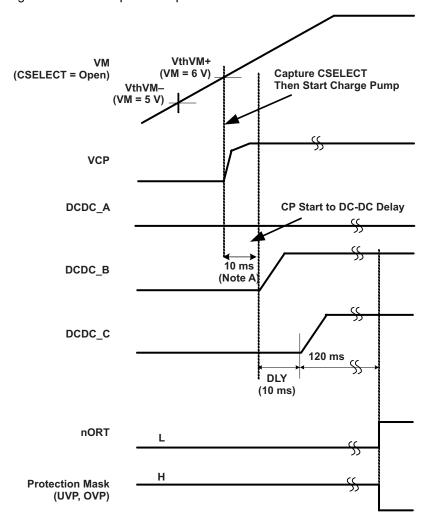

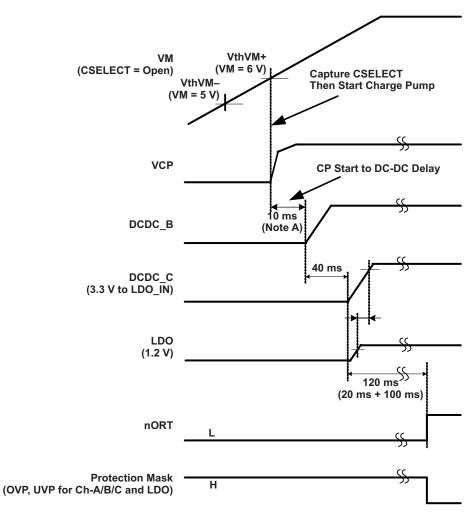

- A. Charge-pump wakeup delay, from 10 ms to 20 ms due to asynchronous event capture.

- B. When V<sub>M</sub> crosses the Vth<sub>VM+</sub> (about 6.0 V), the CSELECT state is captured. In case of the CSELECT being open (pulled up to internal 3.3 V), DC-DC regulator channels B and C are turned on.

- C. LDO OCP is masked during protection M\mask time.

- D. In order to avoid false SPI data latching caused by a rising edge on the STB signal, nSLEEP will remain high during the power up stage (VM rising) and until nORT is released.

- E. DC/DC Channel A follows the Regulator A Control table. During power up, DC/DC Channel A starts up disabled (SETUP BANK 0 [7] = 1).

Figure 9. Power-Up Timing (Power-Up With DC-DC Turnon by CSELECT)

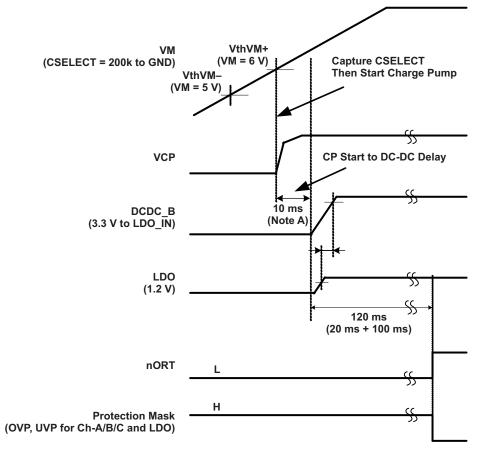

- A. Charge-pump wakeup delay, from 10 ms to 20 ms due to asynchronous event capture.

- B. LDO Enable follows DC/DC B Enable during power up and can be controlled using the SETUP register after power up.

Figure 10. Power-Up Timing (Power-Up With LDO, Supplied by DCDC\_B)

- A. Charge-pump wakeup delay, from 10 ms to 20 ms due to asynchronous event capture.

- B. LDO Enable follows DC/DC B Enable during power up and can be controlled using the SETUP register after power up. In this case, since LDO\_IN is driven by DC/DC Channel C, LDO\_OUT will follow DC/DC Channel C.

Figure 11. Power-Up Timing (Power-Up With LDO, Supplied by DCDC\_C)

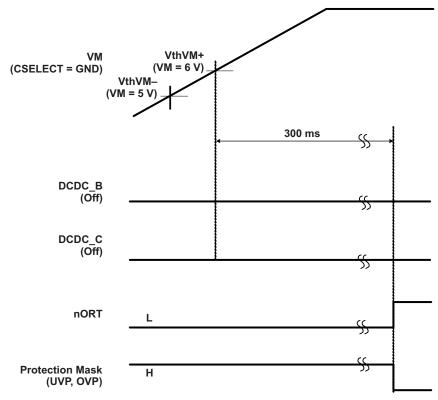

- A. When  $V_M$  crosses the Vth<sub>VM+</sub> (about 6 V) with CSELECT = GND, none of three regulators are turned ON. The nORT output is released to H after 300 ms from Vth<sub>VM+</sub> crossing.

- B. LDO OCP is masked during protection mask time.

Figure 12. Power-Up Timing (Power-Up Without DC-DC Turnon, CSELECT = GND)

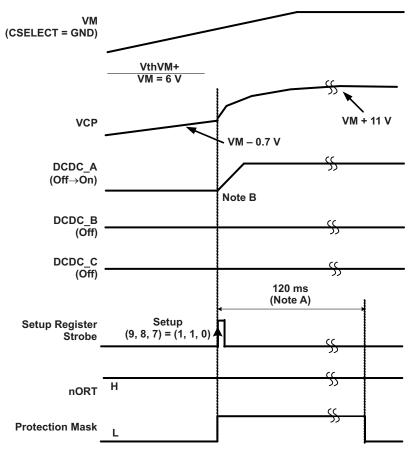

- A. The regulator is started from the strobe input, same as the charge pump. No 10-ms waiting, because the VCP pin already reached to  $V_M 0.7 \ V$ .

- B. LDO OCP is masked during protection mask time.

- C. A\_CONT must be LOW or OPEN for regulator A to turn on.

Figure 13. Power-Up Timing (DC-DC Regulator Wakeup by Setup Register)

Product Folder Links: DRV8808

Submit Documentation Feedback

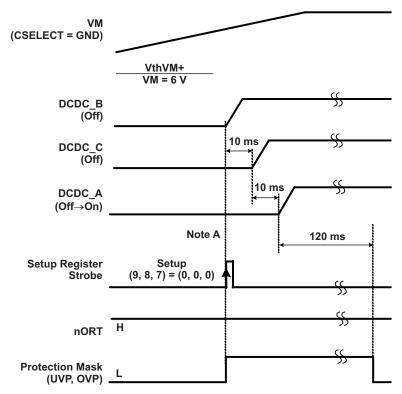

- A. A\_CONT must be LOW or OPEN for regulator A to turn on.

- B. LDO OCP is masked during protection mask time.

Figure 14. Power-Up Timing (DC-DC Regulator Wakeup by Setup Register, All Three Channels ON)

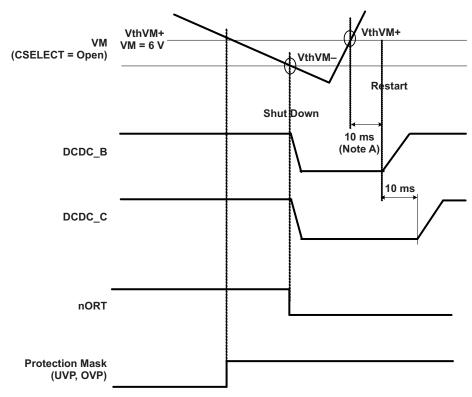

# 7.3.1.9 $V_M$ Start-up/Power-Down and Glitch Condition

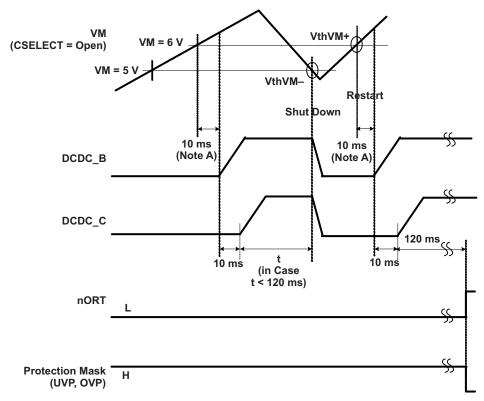

1. Start up with V<sub>M</sub> glitch (not below Vth<sub>VM</sub>-)

A. LDO OCP is masked during protection mask time.

Figure 15. Power-Up Timing With VM Glitch Condition (Not Below Vth\_VM-)

# 2. Start up with V<sub>M</sub> glitch (below Vth<sub>VM</sub>-)

A. LDO OCP is masked during protection mask time.

Figure 16. Power-Up Timing With VM Glitch Condition (Below Vth\_VM-)

Submit Documentation Feedback

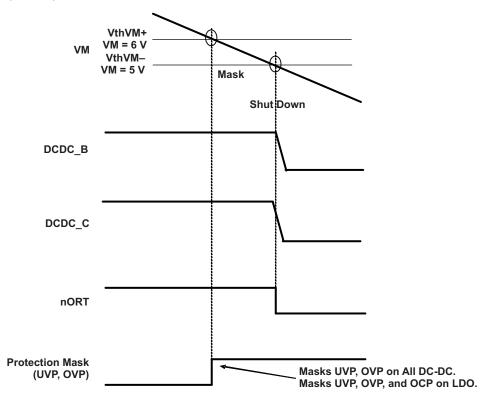

#### 3. Power down (normal)

Figure 17. Power-Down Timing

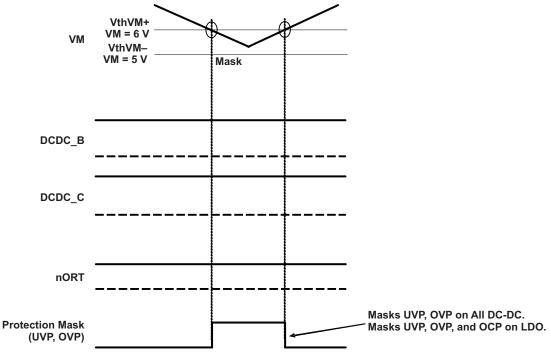

## 4. Power down (glitch on V<sub>M</sub>)

Figure 18. Power-Down Timing (With Glitch on VM)

Product Folder Links: DRV8808

Copyright © 2009-2015, Texas Instruments Incorporated

#### 5. Power down (glitch on V<sub>M</sub> below Vth<sub>VM</sub>)

A. LDO OCP is masked during protection mask time.

Figure 19. Power-Down Timing (With Glitch on VM Below VthVM-)

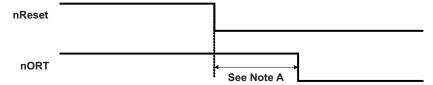

A.  $2.5 \mu s < (nReset Deglitch + Output Delay) < 10 \mu s$

Figure 20. Shut Down by nReset

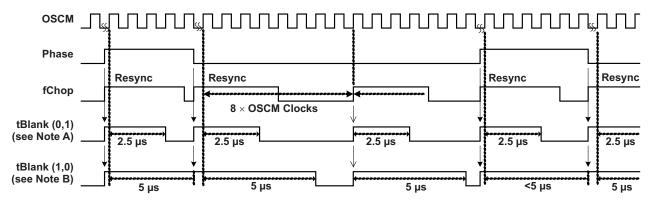

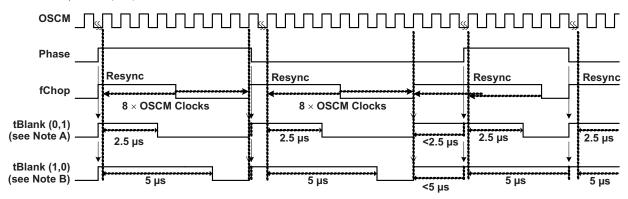

## 7.3.2 Blanking Time Insertion Timing for DC Motor Driving

For the dc motor-driving H-bridge, tBlank is inserted at each phase reversal and following each chopping cycle (once in every eight OSCM clocks).

For a large n number (5 or 6), tBlank setup may decrease the Itrip detect window. Care must be taken when optimizing this in the system.

Case A: Phase duty = 25%

- A\*1 for setup bit = (1,0)

- A\*2 for setup bit = (0,1)

30

- A. Setup register bit <1:0> = (1,0), tBlank = 5 µs (or bits <3:2>/<5:4> for H-bridge B/C channel)

- B. Setup register bit <1:0> = (0,1), tBlank = 2.5 \( \text{ps} \) (or bits <3:2>/<5:4> for H-bridge B/C channel)

Figure 21. Timing for Case A

Case B: Phase duty = 40%

- B\*1 for setup bit = (1,0)

- B\*2 for setup bit = (0,1)

- A. Setup register bit <1:0> = (1,0), tBlank = 5 µs (or bits <3:2>/<5:4> for H-bridge B/C channel)

- B. Setup register bit <1:0> = (0,1), tBlank = 2.5 \(\mu\)s (or bits <3:2>/<5:4> for H-bridge B/C channel)

Figure 22. Timing for Case B

## 7.3.3 Function Table in nORT, Power Down, V<sub>M</sub> Conditions

The following is valid only when the protection control bits (in Extended Setup register) are all 0.

Table 10. Block Conditions by Device Status

| DEVICE STATUS                          | CHARGE PUMP | OSCM     | nORT             | MODE SETTING         |  |

|----------------------------------------|-------------|----------|------------------|----------------------|--|

| nSleep                                 | Active      | Active   | Inactive         | Available            |  |

| nORT                                   | Inactive    | Active   | Active           | Depend on power down |  |

| V <sub>M</sub> < 6 V during power down | Active      | Active   | See timing chart | Depend on power down |  |

| 4.5 V < V <sub>M</sub>                 | Inactive    | Inactive | Active           | Unavailable          |  |

**Table 11. Shutdown Functions**

| FAULT CONDITION    | DCDC_A    | DCDC_B    | DCDC_C    | MOTOR     | nORT           |

|--------------------|-----------|-----------|-----------|-----------|----------------|

| DCDC_A UVP/OVP/OCP | Shut down | Shut down | Shut down | Shut down | Asserted (low) |

| DCDC_B UVP/OVP/OCP | Shut down | Shut down | Shut down | Shut down | Asserted (low) |

| DCDC_C UVP/OVP/OCP | Shut down | Shut down | Shut down | Shut down | Asserted (low) |

#### **Table 11. Shutdown Functions (continued)**

| FAULT CONDITION | DCDC_A           | DCDC_B           | DCDC_C           | MOTOR            | nORT             |

|-----------------|------------------|------------------|------------------|------------------|------------------|

| Motor OCP       | See MISD Control |

|                 | Table            | Table            | Table            | Table            | Table            |

| TSD             | See TSD Control  |

|                 | Table            | Table            | Table            | Table            | Table            |

- Table is valid when the Protection and Reset Mask bits in the Extended Setup register are all 0.

- If Reset Mask (selective shutdown) bits are set, shutdown and release description is in the note following the Extended Setup register definition.

- DC-DC regulators are released at  $V_M > Vth_{VM+}$  when  $V_M$  increasing. When  $V_M$  decreasing, regulators are shut down when  $V_M < Vth_{VM-}$ . When  $Vth_{VM+} > V_M > Vth_{VM-}$ , OVP and UVP are masked.

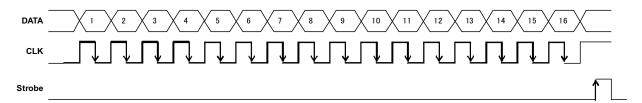

- Motor OCP shutdown release is specified in MISD Control Table.