### HIGH PERFORMANCE COMMUNICATION BUFFER

# ICS913051

### Description

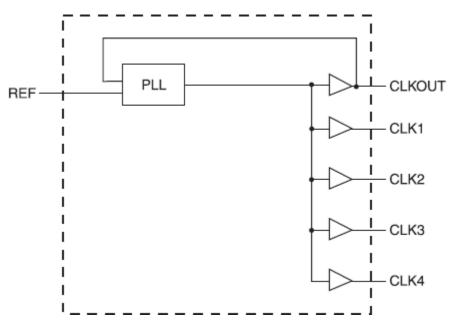

The ICS91305I is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the REF input with the CLKOUT signal. It is designed to distribute high speed clocks in communication systems operating at speeds from 10 to 133 MHz.

ICS91305I is a zero delay buffer that provides synchronization between the input and output. The synchronization is established via CLKOUT feed back to the input of the PLL. Since the skew between the input and output is less than +/- 350 pS, the part acts as a zero delay buffer.

The ICS91305I comes in an eight pin 150 mil SOIC package. It has five output clocks. In the absence of REF input, will be in the power down mode. In this mode, the PLL is turned off and the output buffers are pulled low. Power down mode provides the lowest power consumption for a standby condition.

#### **Features**

- · Zero input output delay

- Frequency range 10 133 MHz (3.3V)

- 5V tolerant input REF

- High loop filter bandwidth ideal for Spread Spectrum applications

- · Less than 200 ps Jitter between outputs

- · Skew controlled outputs

- Skew less than 250 ps between outputs

- Available in 8 pin 150 mil SOIC & 173 mil TSSOP packages

- 3.3V ±10% operation

- Supports industrial temperature range -40°C to 85°C

## **Block Diagram**

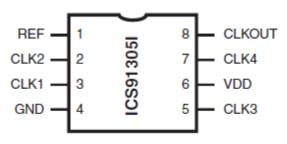

## **Pin Configuration**

# 8 pin SOIC & TSSOP

# **Pin Descriptions**

| PIN NUMBER | PIN NAME                   | TYPE | DESCRIPTION                                          |  |

|------------|----------------------------|------|------------------------------------------------------|--|

| 1          | REF <sup>2</sup>           | IN   | Input reference frequency, 5V tolerant input.        |  |

| 2          | CLK2 <sup>3</sup>          | OUT  | Buffered clock output                                |  |

| 3          | CLK1 <sup>3</sup>          | OUT  | Buffered clock output                                |  |

| 4          | GND                        | PWR  | Ground                                               |  |

| 5          | CLK3 <sup>3</sup>          | OUT  | Buffered clock output                                |  |

| 6          | VDD                        | PWR  | Power Supply (3.3V)                                  |  |

| 7          | CLK4 <sup>3</sup>          | OUT  | Buffered clock output                                |  |

| 8          | <b>CLKOUT</b> <sup>3</sup> | OUT  | Buffered clock output. Internal feedback on this pin |  |

Notes:

1. Guaranteed by design and characterization. Not subject to 100% test.

2. Weak pull-down

3. Weak pull-down on all outputs

# **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the ICS91305I. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Supply Voltage                | 7.0 V                           |

|-------------------------------|---------------------------------|

| Logic Inputs (Except REF)     | GND – 0.5 V to $V_{DD}$ + 0.5 V |

| Logic Input REF               | GND -0.5 V to GND + 5.5 V       |

| Ambient Operating Temperature | -40°C to +85°C                  |

| Storage Temperature           | -65°C to +150°C                 |

## **Electrical Characteristics at 3.3V**

|                                     | DC Characteristics |                                                                      |     |      |       |       |  |

|-------------------------------------|--------------------|----------------------------------------------------------------------|-----|------|-------|-------|--|

| PARAMETER                           | SYMBOL             | TEST CONDITIONS                                                      | MIN | ТҮР  | MAX   | UNITS |  |

| Input Low Voltage                   | V <sub>IL</sub>    |                                                                      |     |      | 0.8   | V     |  |

| Input High Voltage                  | V <sub>IH</sub>    |                                                                      | 2.0 |      |       | V     |  |

| Input Low Current                   | I <sub>IL</sub>    | V <sub>IN</sub> =0V                                                  |     | 19   | 100.0 | μA    |  |

| Input High Current                  | I <sub>IH</sub>    | V <sub>IN</sub> =V <sub>DD</sub>                                     |     | 0.10 | 250.0 | μA    |  |

| Output Low<br>Voltage <sup>1</sup>  | V <sub>OL</sub>    | $I_{OL} = 12mA$                                                      |     | 0.25 | 0.4   | V     |  |

| Output High<br>Voltage <sup>1</sup> | V <sub>OH</sub>    | I <sub>OH</sub> = -12mA                                              | 2.4 | 2.9  |       | V     |  |

| Power Down<br>Supply Current        | I <sub>DD</sub>    | REF = 0 MHz                                                          |     | 0.3  | 100.0 | μA    |  |

| Supply Current                      | I <sub>DD</sub>    | Unloaded oututs at 66.66 MHz<br>SEL inputs at V <sub>DD</sub> or GND |     | 30.0 | 80.0  | mA    |  |

Notes:

1. Guaranteed by design and characterization. Not subject to 100% test.

2.All Skew specifications are mesured with a  $50\Omega$  transmission line, load teminated with  $50\Omega$  to 1.4V.

3.Duty cycle measured at 1.4V.

4.Skew measured at 1.4V on rising edges. Loading must be equal on outputs.

# **Switching Characteristics**

| PARAMETER                                                          | SYMBOL            | CONDITION                                             | MIN            | TYP | MAX          | UNITS       |

|--------------------------------------------------------------------|-------------------|-------------------------------------------------------|----------------|-----|--------------|-------------|

| Output period                                                      | t1                | With CL=30pF                                          | 100.00<br>(10) |     | 7.5<br>(133) | ns<br>(MHz) |

| Input period                                                       | t1                | With CL=30pF                                          | 100.00<br>(10) |     | 7.5<br>(133) | ns<br>(MHz) |

| Duty Cycle <sup>1</sup>                                            | Dt1               | Measured at 1.4V; CL=30pF                             | 40.0           | 50  | 60           | %           |

| Duty Cycle <sup>1</sup>                                            | Dt2               | Measured at VDD/2 Fout<br><66.6MHz                    | 45             | 50  | 55           | %           |

| Rise Time <sup>1</sup>                                             | tr1               | Measured between 0.8V and 2.0V:<br>CL=30pF            |                | 1.2 | 1.5          | ns          |

| Fall Time <sup>1</sup>                                             | tf1               | Measured between 2.0V and 0.8V;<br>CL=30pF            |                | 1.2 | 1.5          | ns          |

| Delay, REF Rising<br>Edge to CLKOUT<br>Rising Edge <sup>1, 2</sup> | Dr1               | Measured at 1.4V                                      |                | 0   | ±350         | ps          |

| Output to Output<br>Skew <sup>1</sup>                              | Tskew             | All outputs equally loaded,<br>CL=20pF                |                |     | 250          | ps          |

| Device to Device<br>Skew <sup>1</sup>                              | Tdsk-Tdsk         | Measured at VDD/2 on the<br>CLKOUT pins of devices    |                | 0   | 700          | ps          |

| Cycle to Cycle<br>Jitter <sup>1</sup>                              | Тсус-Тсус         | Measured at 66.66 MHz, loaded outputs                 |                |     | 200          | ps          |

| PLL Lock Time <sup>1</sup>                                         | t <sub>LOCK</sub> | Stable power supply, valid clock presented on REF pin |                |     | 1.0          | ms          |

| Jitter; Absolute<br>Jitter <sup>1</sup>                            | Tjabs             | @ 10,000 cycles<br>C <sub>L</sub> = 30pF              | -200           | 70  | 200          | ps          |

| Jitter; 1 - Sigma <sup>1</sup>                                     | Tj1s              | @ 10,000 cycles<br>C <sub>L</sub> = 30pF              |                | 14  | 60           | ps          |

Notes:

1. Guaranteed by design and characterization. Not subject to 100% test.

2. REF input has a threshold voltage of 1.4V

3. All parameters expected with loaded outputs

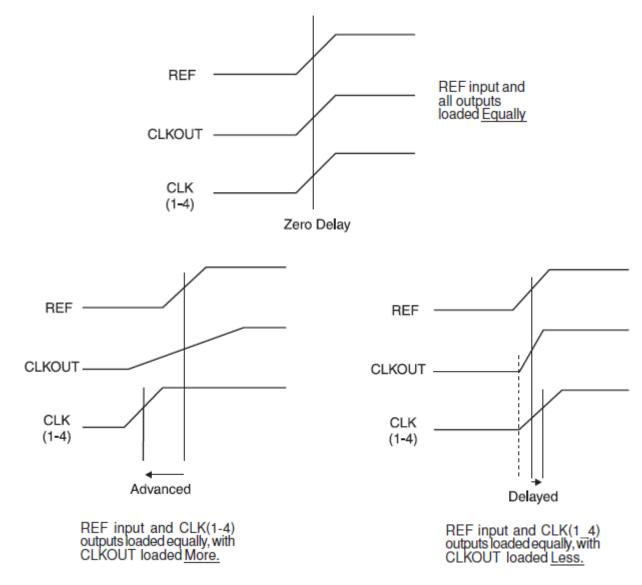

## Output to Output Skew

The skew between CLKOUT and the CLK(1-4) outputs is not dynamically adjusted by the PLL. Since CLKOUT is one of the inputs to the PLL, zero phase difference is maintained from REF to CLKOUT. If all outputs are equally loaded, zero phase difference will maintained from REF to all outputs.

If applications requiring zero output-output skew, all the outputs must equally loaded.

If the CLK(1-4) outputs are less loaded than CLKOUT, CLK(1-4) outputs will lead it; and if the CLK(1-4) is more loaded than CLKOUT, CLK(1-4) will lag the CLKOUT.

Since the CLKOUT and the CLK(1-4) outputs are identical, they all start at the same time, but different loads cause them to have different rise times and different times crossing the measurement thresholds.

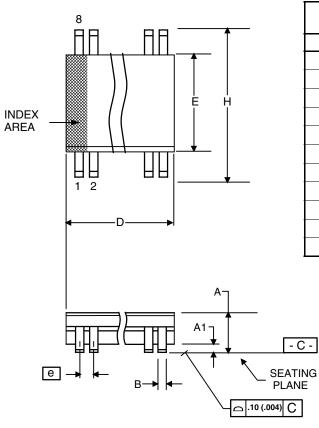

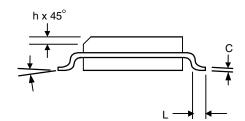

## Package Outline and Package Dimensions (8-pin SOIC, 150 Mil. Body)

Package dimensions are kept current with JEDEC Publication No. 95

|        | Millimeters |            | Inc         | hes        |

|--------|-------------|------------|-------------|------------|

| Symbol | Min         | Max        | Min         | Max        |

| А      | 1.35        | 1.75       | .0532       | .0688      |

| A1     | 0.10        | 0.25       | .0040       | .0098      |

| В      | 0.33        | 0.51       | .013        | .020       |

| С      | 0.19        | 0.25       | .0075       | .0098      |

| D      | 4.80        | 5.00       | .1890       | .1968      |

| E      | 3.80        | 4.00       | .1497       | .1574      |

| е      | 1.27 BASIC  |            | 0.050 BASIC |            |

| Н      | 5.80        | 6.20       | .2284       | .2440      |

| h      | 0.25        | 0.50       | .010        | .020       |

| L      | 0.40        | 1.27       | .016        | .050       |

| α      | <b>0</b> °  | <b>8</b> ° | <b>0</b> °  | <b>8</b> ° |

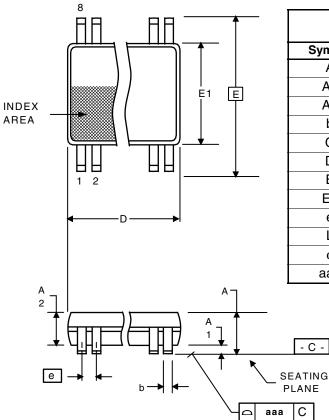

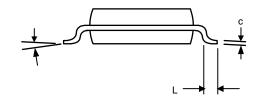

## Package Outline and Package Dimensions (8-pin TSSOP, 4.4 Mil. Body)

Package dimensions are kept current with JEDEC Publication No. 95

|        | Millimeters |            | Inc         | hes        |

|--------|-------------|------------|-------------|------------|

| Symbol | Min Max     |            | Min         | Мах        |

| A      |             | 1.20       |             | 0.047      |

| A1     | 0.05        | 0.15       | 0.002       | 0.006      |

| A2     | 0.80        | 1.05       | 0.032       | 0.041      |

| b      | 0.19        | 0.30       | 0.007       | 0.012      |

| С      | 0.09        | 0.20       | 0.0035      | 0.008      |

| D      | 2.90        | 3.10       | 0.114       | 0.122      |

| E      | 6.40 BASIC  |            | 0.252 BASIC |            |

| E1     | 4.30        | 4.50       | 0.169       | 0.177      |

| е      | 0.65 Basic  |            | 0.0256      | 8 Basic    |

| L      | 0.45        | 0.75       | 0.018       | 0.030      |

| α      | <b>0</b> °  | <b>8</b> ° | <b>0</b> °  | <b>8</b> ° |

| aaa    | -           | 0.10       | -           | 0.004      |

### **Ordering Information**

| Part / Order Number | Marking  | Shipping Packaging | Package     | Temperature   |

|---------------------|----------|--------------------|-------------|---------------|

| 91305AMILF          | 305AMILF | Tubes              | 8-pin SOIC  | -40 to +85° C |

| 91305AMILFT         | 305AMILF | Tape and Reel      | 8-pin SOIC  | -40 to +85° C |

| 91305AGILF          | 305IL    | Tubes              | 8-pin TSSOP | -40 to +85° C |

| 91305AGILFT         | 305IL    | Tape and Reel      | 8-pin TSSOP | -40 to +85° C |

- C -

С

"LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

"A" is the device revision designator (will not correlate with the datasheet revision).

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

#### **Revision History**

| Rev. | Originator | Date     | Description of Change                                                                                                                                                |

|------|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G    | D. Chan    | 09/06/12 | <ol> <li>Updated ordering information to inlclude "I" for industrial temp range in ordering<br/>scheme.</li> <li>Re-created datasheet in latest template.</li> </ol> |

|      |            |          |                                                                                                                                                                      |

|      |            |          |                                                                                                                                                                      |

|      |            |          |                                                                                                                                                                      |

|      |            |          |                                                                                                                                                                      |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>