PD-IM-7448E/A

# **Evaluation Board User Guide**

Document Issue: 1.2

Security Status: Restricted Date: April 2014

**PRODUCTION DATA:** Information contained in this document is proprietary to Microsemi and is current as of publication date. This document may not be modified in any way without the express written consent of Microsemi. Product processing does not necessarily include testing of all parameters. Microsemi reserves the right to change the configuration and performance of the product and to discontinue product at any time.

#### Reference Documents

- IEEE 802.3af-2003 Standard, DTE Power via MDI

- IEEE802.3at-draft1.0 Standard, DTE Power via MDI

- PD69012 Data Sheet, Catalogue Number 06-0069-058

- PD69000 Data Sheet, Catalogue Number 06-0070-058

- Application Note 175: Layout Design Guidelines for PoE Systems, Catalogue Number 06-0055-080

- Application Note 174: Designing a 48-port Enhanced PoE System (802.3af/802.3at Compliant, UART interface), Catalogue Number 06-0054-080

- Serial Communication Protocol User Guide, Catalogue Number 06-0032-056

- GUI installation User Guide, Catalogue Number 06-0037-056

The above documents can be obtained via Microsemi Customer Support. To access other documents, go to our web site at http://www.microsemi.com/ and under Tech Support\Documentation, and look up the relevant documents.

| T | able of | Contents                                           |   |

|---|---------|----------------------------------------------------|---|

| 1 | Abou    | It this Guide                                      | 4 |

|   | 1.1     | Objectives                                         | 4 |

|   | 1.2     | Audience                                           | 4 |

|   | 1.3     | Organization                                       | 4 |

| 2 | Intro   | duction                                            |   |

|   | 2.1     | Evaluation Board Ordering Information              |   |

|   | 2.2     | Evaluation Board Features                          |   |

|   | 2.3     | Evaluation Board Interfaces & Connections          | 6 |

|   | 2.4     | Physical Characteristics                           |   |

| 3 | Phys    | ical Description                                   |   |

|   | 3.1     | Package Contents                                   |   |

|   | 3.2     | Switches and Jumpers                               |   |

|   | 3.2.1   |                                                    |   |

|   | 3.2.2   | Reset Button                                       | 8 |

|   | 3.3     | Connectors                                         |   |

|   | 3.3.1   |                                                    |   |

|   | 3.3.2   |                                                    |   |

| 4 |         | rical Characteristics1                             |   |

| 5 |         | Ilation1                                           |   |

|   | 5.1     | Preliminary Considerations and Safety Precautions1 |   |

|   | 5.2     | Initial Configuration1                             |   |

|   | 5.3     | Hardware Setup1                                    |   |

|   | 5.4     | Auto-Mode Patch Burning1                           | 9 |

# 1 About this Guide

## 1.1 Objectives

This user guide provides both a description and operation procedures for Microsemi's PD-IM-7448 Evaluation Board. This board is used to evaluate the performance of the Enhanced and Auto Mode PoE applications based PD69012 managers.

## 1.2 Audience

This User Guide is intended for qualified personnel, meaning operators and technicians who have a background in basic electronics.

### 1.3 Organization

This Guide is divided into several sections:

| Chapter 1                                                                                            | About this guide describes the objectives audience organization.                                                    |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Chapter 2                                                                                            | Introduction gives an over view of the main functions, features, physical characteristics and ordering information. |

| Chapter 3                                                                                            | Physical description provides a physical description of the components (switches, jumpers, connectors).             |

| Chapter 4 Electrical characteristics list the electrical characteristics of the PoE evaluation board |                                                                                                                     |

| Chapter 5                                                                                            | Installation describes the installation process.                                                                    |

# 2 Introduction

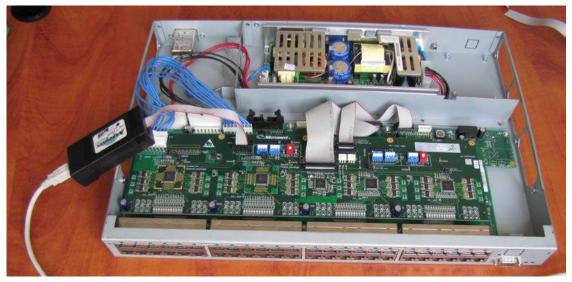

Microsemi's PD-IM-7448 evaluation board (see Figure 1 and 2) provides the designer with the needed environment to evaluate the performance and the implementation of PoE applications based on the PD69012 - PoE Manager and the PD69000 - PoE Controller. This board can be configured to support Enhanced and Autoc PoE operational modes. The PD-IM-7448 provides the customer with the ability to apply any PoE application while using different daughter boards (DB) connected to the top of the mother board (MB).

The document details the steps and connection instructions required to install and operate this board.

The Evaluation Board enables PoE designers to evaluate Microsemi's PoE solution with maximum flexibility and ease in configuration.

Figure 1: Mother Board - General View

Figure 2: Daughter Board - General View

## 2.1 Evaluation Board Ordering Information

The following table lists the EB ordering information.

| Ordering Number | Description                                                                                                            |

|-----------------|------------------------------------------------------------------------------------------------------------------------|

| PD-DB-7448      | 48 ports PoE application, four PD69012 managers with the PoE controller PD69000 operating at the Enhanced or Auto mode |

## 2.2 Evaluation Board Features

- Designed to support any PoE DB application (Auto/Enhanced mode, 12/24/48 ports)

- Four gangs (each contains 12 X RJ45 connectors)

- Vin connectors: DC in connector

- Port connection between MB to DB

- Communication and indication interface connection between MB to DB using flat cables

- Isolated USB to I2C interface

- Isolated USB to UART interface

- Isolated RS232 interface

- LED stream interface

- Daisy Chain option: MB can be cascaded to another MB in order to support eight PD69012 with single PoE controller

- External host interface

- External power supplies interface

- Reset push button

- There are no pulse transformers & common mode chocks per port

- Evaluation Board working temperature: 0° to +50° C

- ROHS compliant

## 2.3 Evaluation Board Interfaces & Connections

The board has several interfaces:

- **RJ45**: Running from the MB to the PD (powered device) (J29-J30)

- Ports interface: Ports connection between the MB to the DB

- Vin connectors: DC in (Vmain) connection (J6, J7, J15, J16 and J18)

- Communication and indication: Communication and indication signals transferred from the MB to the DB

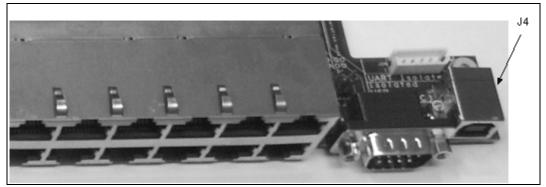

- External host: Control and indication signals running between the hosting system to the MB (J4)

- Isolated USB: USB to UART / USB to I2C communication between the hosting system to the MB (U7)

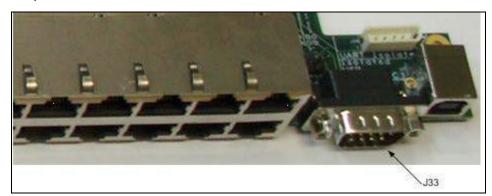

- Isolated RS232: Between the hosting system to the MB (J33)

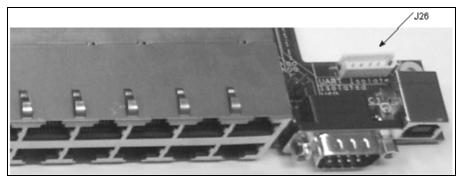

- Isolated UART: Between the hosting system to the MB (J26)

- LEDs: LED indication to the LED board (J16)

- Daisy chain: MB cascading option (J8)

- External power supplies: 'Power good' signals coming from the power supplies indicating operational/failed power supply (J1)

- Tester: Between the automatic tester and the MB

- BDM: PoE controller burning interface

### 2.4 Physical Characteristics

Table 1 lists the evaluation board's physical characteristics.

#### **Table 1: Physical Characteristics**

| Parameter             | Value                        |

|-----------------------|------------------------------|

| Mechanical dimensions | 420 x 168 x 30mm (l x w x h) |

# **3** Physical Description

## 3.1 Package Contents

Upon opening the Evaluation Board package, verify that all parts itemized in the packing list are included. If any part is missing or seems damaged, contact your local representative or Microsemi's Customer Service Department. Package contents for standard shipments are as follows:

- A GUI software CD

- Power supply cable (from the power supply unit to the MB)

- Power supply cable (from the MB to the DB)

- Two flat cables (16 pin and 30 pin)

### 3.2 Switches and Jumpers

The evaluation board comprises switches and jumpers used to select the desired configuration states of the board. Default configurations are indicated as 'default'.

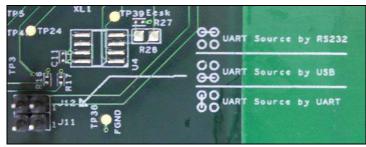

### 3.2.1 UART Communication Selection

There are three UART communication options:

- UART to USB (connecting USB cable to U7)

- UART to RS232 (connecting RS232 cable to J33)

- UART to UART(connecting UART cable to J26)

Using J11 and J12, these three options can be selected.

| Table 2: UART | Communication Selection |

|---------------|-------------------------|

|---------------|-------------------------|

| Switch/Jumper | UART to RS232             | UART to USB               | UART to UART |

|---------------|---------------------------|---------------------------|--------------|

| J11           | N.C                       | Short from pin "1" to "2" | N.C          |

| J12           | Short from pin "1" to "2" | N.C                       | N.C          |

Figure 3: UART Communication Selection (J11, J12)

#### 3.2.2 Reset Button

The dedicated Reset push button SW1 (see Figure 4) resets the following DB components:

- PoE controller PD69012

- PoE controller PD69000

Figure 4: Reset Push Button (SW1)

### 3.3 Connectors

The following sections provide a general and detailed description of the board connectors.

#### 3.3.1 Connectors Table

The Evaluation Board's connectors are listed in Table 3.

| Table 3: Connector List | Table | 3: | Connector List |

|-------------------------|-------|----|----------------|

|-------------------------|-------|----|----------------|

| Number | Connector                | Name                            | Description                                                                                                                                                                                                                  |

|--------|--------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | J29 - J30                | RJ45 connectors                 | 48 'RJ45' ports connecting the MB to the Powered<br>Device load                                                                                                                                                              |

| 2      | J22 - J25                | Port connection                 | Port connection (Vport_pos and Vport_neg)<br>between the MB and the DB implemented by using<br>four connectors                                                                                                               |

| 3      | J6, J7, J15, J16,<br>J18 | Vin connectors                  | DC in (Vmain) connection used to power the MB and DB Evaluation boards.                                                                                                                                                      |

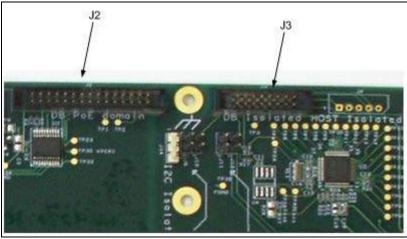

| 4      | J2, J3                   | Communication<br>and indication | Communication (UART, I <sup>2</sup> C and ESPI) and<br>indication signals (reset, disable etc) running<br>between the MB and the DB using flat cables<br>connected to the J2 (PoE domain) and J3 (Host<br>Domain) connectors |

| 5      | J4                       | Isolated External<br>HOST       | Control and indication signals running between the hosting system a the MB (isolation circuitry on the daughter board)                                                                                                       |

| 6      | U7                       | Isolated USB                    | The USB communication coming from the hosting system (U7), converted to UART or I <sup>2</sup> C communication and directed to the DB (Isolation circuitry on the daughter board)                                            |

| 7      | J33                      | Isolated RS232                  | RS232 signal levels coming from the hosting<br>system (J33) and converted to UART signal levels,<br>then directed to the DB (ilsolation circuitry on the<br>daughter board)                                                  |

| 8      | J26                      | Isolated UART                   | UART interface from the hosting system and the MB, then directed to the DB (isolation circuitry on the daughter board)                                                                                                       |

| 9      | J16                      | LEDs indication                 | Port's status presented via the LEDs indication<br>signals running to the LED board                                                                                                                                          |

| 10     | J8                       | Daisy Chaining                  | Connection between two MBs supporting eight<br>PD69012s using a single PoE Controller                                                                                                                                        |

| 11     | J1                       | External power                  | 'Power Good' indication signals coming from the                                                                                                                                                                              |

| Number | Connector | Name     | Description                                                                                                                                 |

|--------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|        |           | supplies | power supplies, indicating the operating/failed<br>power supply status. It is also a hot-swap signal<br>for hot swappable PoE applications. |

| 12     | J5        | Tester   | Interface between the automatic tester and the MB                                                                                           |

| 13     | J13       | BDM      | PoE Controller burning interface                                                                                                            |

#### 3.3.2 Connectors Detailed Explanation

The numbering is in reference to the numbers given in Table 3.

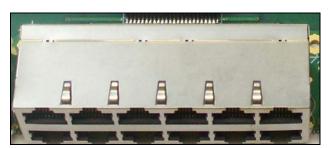

#### 1. RJ45 Connectors (see Figure 5)

There are four dedicated RJ45 connectors; each contains 12 RJ45 ports.

| Pin No. (Each RJ45) | Signal Name       | Description                   |

|---------------------|-------------------|-------------------------------|

| 4, 5                | SPARE - Vport_Pos | The PoE's Positive spare port |

| 7, 8                | SPARE - Vport_Neg | The PoE's Negative spare port |

| 1,2                 | DATA - Vport_neg  | The PoE's negative data port  |

| 3, 6                | DATA - Vport_neg  | The PoE's positive data port  |

- Manufacturer: FOXCONN

- Manufacture part number: JM371B3-KD10-4F

Figure 5: RJ45 Connectors

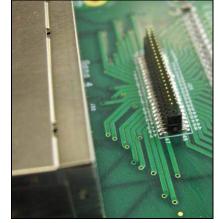

#### 2. Port Connection (see)

The Ports Connection (spare\_NEG, spare\_POS, data\_NEG and data\_POS) between the MB's RJ45 and the DB PoE circuitry is utilized by four connectors.

| Pin No.                                         | Signal Name | Description                   |

|-------------------------------------------------|-------------|-------------------------------|

| 1, 5, 9, 13, 17, 21, 25, 29, 33, 37,<br>41, 45  | spare_NEGx  | The PoE's negative spare port |

| 2, 6, 10, 14, 18, 22, 26, 30, 34, 38, 42, 46    | spare_POSx  | The PoE's positive spare port |

| 3, 7, 11, 15, 19, 23, 27,31, 35, 39,<br>43, 47  | data_NEGx   | The PoE's negative data port  |

| 4, 8, 12, 16, 20, 24, 28, 32, 36, 40,<br>44, 48 | data_POSx   | The PoE's positive data port  |

Manufacturer: CviLux

Manufacture part number: CH57482M100-PA

Figure 6: Port Connection

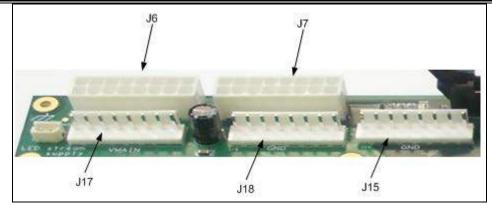

#### 3. Vin Connectors (see Figure 7)

DC in (Vmain) connection, used to power the MB and the DB Evaluation Boards. 44 VDC > Vmain> 57 V DC.

#### <u>J6</u>

| Pin No. | Signal Name   | Description                                    |

|---------|---------------|------------------------------------------------|

| 1-16    | Vmain (Vin +) | The positive main voltage (referenced to AGND) |

#### <u>J7</u>

| Pin No. | Signal Name  | Description   |

|---------|--------------|---------------|

| 1-16    | AGND (Vin -) | Analog ground |

Manufacturer: CviLux

Manufacture part number: CP01-316130

#### <u>J17</u>

| Pin No. | Signal Name   | Description                                    |

|---------|---------------|------------------------------------------------|

| 1-8     | Vmain (Vin +) | The positive main voltage (referenced to AGND) |

## <u>J15</u>

| Pin No. | Signal Name   | Description                                    |

|---------|---------------|------------------------------------------------|

| 1       | Vmain (Vin +) | The positive main voltage (referenced to AGND) |

| 2-8     | AGND (Vin -)  | Analog ground                                  |

### <u>J18</u>

| Pin No. | Signal Name   | Description                                    |

|---------|---------------|------------------------------------------------|

| 1       | Vmain (Vin +) | The positive main voltage (referenced to AGND) |

| 2-8     | AGND (Vin -)  | Analog ground                                  |

#### Manufacturer: CviLux

Manufacture part number: CI5208P1VOO

Figure 7: Vin Connectors

#### 4. Communication and Indication (see Figure 8)

The communication (UART, I<sup>2</sup>C and ESPI) and indication signals (reset, disable, etc.) run between the MB and the DB using flat cables connected to J2 (PoE domain) and J3 (Host Domain) connectors.

<u>J3</u>

| xReset_IN_isolated         | Reset signal sent from the hosting system                                                                                                                                              |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xDisable_ports_isolated    | Disable signal sent from the hosting system                                                                                                                                            |

| xSystem_ok_isolated        | System_ok signal sent from the hosting system                                                                                                                                          |

| RTS                        | Reserved                                                                                                                                                                               |

| xInt_out_isolated          | Int_out signal sent from the hosting system                                                                                                                                            |

| reserved                   | Reserved                                                                                                                                                                               |

| 3 3\/ico                   | 3.3 VDC sent from the hosting system (isolated from PoE                                                                                                                                |

| 5_5 180                    | domain), referenced to 'GND_Floating'                                                                                                                                                  |

| GND_Floating               | The hosting system ground (isolated from PoE domain)                                                                                                                                   |

| UART_Tx_isolated           | Tx signal (transmit), direction sent from the PoE controller (3.3V tolerate)                                                                                                           |

| UART_Rx_isolated           | Rx signal (receive), to the PoE controller (3.3V tolerate)                                                                                                                             |

| SDA_auto_mode_isolated     | I <sup>2</sup> C SDA: data I <sup>2</sup> C signal between the hosting system to PD69012                                                                                               |

| SCL_auto_mode_isolated     | I <sup>2</sup> C SCL: clock I <sup>2</sup> C signal between the hosting system to PD69012                                                                                              |

| SDA_enhanced_mode_isolated | I <sup>2</sup> C SDA: data I <sup>2</sup> C signal between the hosting system to PD69000                                                                                               |

| SCL_enhanced_mode_isolated | I <sup>2</sup> C SCL: clock I <sup>2</sup> C signal between the hosting system to PD69000                                                                                              |

|                            | xSystem_ok_isolated<br>RTS<br>xInt_out_isolated<br>reserved<br>3_3Viso<br>GND_Floating<br>UART_Tx_isolated<br>UART_Rx_isolated<br>SDA_auto_mode_isolated<br>SDA_enhanced_mode_isolated |

Manufacturer: CviLux

Manufacture part number: CH74162V100

<u>J2</u>

| Pin No.                                 | Signal Name    | Description                                                               |

|-----------------------------------------|----------------|---------------------------------------------------------------------------|

| 1                                       | PG0            | Power good signal, power supply status indication                         |

| 2                                       | PG1            | Power good signal, power supply status indication                         |

| 3                                       | PG2            | Power good signal, power supply status indication                         |

| 4                                       | PG3            | Power good signal, power supply status indication                         |

| 5                                       | xReset_IN      | Reset signal to the PoE application (used for cascading purposes)         |

| 6                                       | xDisable_ports | Disable_ports signal to the PoE application (used for cascading purposes) |

| 7                                       | xPoE_RESET     | Reset signal to the PD69012 ICs (used for cascading purposes)             |

| 8                                       | XHSWP          | Hot Swap control signal, used when the PoE application is hot swappable   |

| 9                                       | BKGD           | PoE controller burning signal                                             |

| 10, 11,<br>17, 18,<br>21, 23,<br>24, 29 | GND_D          | Digital ground at the PoE domain                                          |

| 12, 13                                  | Reserved       | Reserved                                                                  |

| Pin No. | Signal Name       | Description                                                                                                   |

|---------|-------------------|---------------------------------------------------------------------------------------------------------------|

| 12      | SDA_in_auto_mode  | I <sup>2</sup> C SDA_in - data I <sup>2</sup> C signal (used for cascading purposes)                          |

| 14      | SDA_out_auto_mode | I <sup>2</sup> C SDA_out - data I <sup>2</sup> C signal (used for cascading purposes)                         |

| 15      | SCL_auto_mode     | I <sup>2</sup> C SCL - clock I <sup>2</sup> C signal (used for cascading purposes)                            |

| 19      | LED_SCK           | Clock LED signal – running to LED indication board                                                            |

| 20      | LED_DATA          | Data LED signal – running to LED indication board                                                             |

| 22      | LED_Latch         | Latch LED signal – running to LED indication board                                                            |

| 25      | ESPI_CS           | ESPI 'chip select' signal (used for cascading purposes)                                                       |

| 26      | ESPI_MOSI         | ESPI 'master out slave in' signal (used for cascading purposes)                                               |

| 27      | ESPI_MISO         | ESPI 'master in' slave out' signal (used for cascading purposes)                                              |

| 28      | ESPI_SCK          | ESPI clock (used for cascading purposes)                                                                      |

| 30      | VPERI             | 3.3 VDC = Vperi, application's reference voltage (isolated from hosting system domain), referenced to 'GND_D' |

Figure 8: Communication and Indication Connectors

- Manufacturer: CviLux

- Manufacture part number: CH74302V100

- 5. Isolated External Host (see Figure 9)

This host transmits control and indication signals beween the hosting system to the MB.

| Pin No. | Signal Name             | Description                                          |

|---------|-------------------------|------------------------------------------------------|

| 1       | xReset_IN_isolated      | Reset signal from the hosting system                 |

| 2       | xDisable_ports_isolated | Disable signal from the hosting system               |

| 3       | xInt_out_isolated       | Int_out signal from the hosting system               |

| 4       | xSystem_ok_isolated     | System_ok signal from the hosting system             |

| 5       | GND_Floating            | The hosting system ground (isolated from PoE domain) |

- Manufacturer: CviLux

- Manufacture part number: CI25-05P1V00

Figure 9: Isolated External Host

### 6. Isolated USB Interface (see Figure 10)

This interface supplies USB communication coming from the hosting system (U7), converted to UART or I<sup>2</sup>C communication and directed to the DB (Isolation circuitry on the daughter board).

#### <u>U7</u>

| Pin No. | Signal Name | Description                     |

|---------|-------------|---------------------------------|

| 1       | Vbus        | Voltage supply from the USB bus |

| 2       | D-          | Dedicated USB signal            |

| 3       | D+          | Dedicated USB signal            |

| 4       | GND_F       | Floating ground                 |

- Manufacturer: Samtec

- Manufacture part number: USB-B-S-S-B-TH

Figure 10: Isolated USB Interface

### 7. Isolated RS232 (see Figure 11)

RS232 signals level comes from the hosting system and been converted to UART signals levels, then directed to the DB (Isolation circuitry on the daughter board)

| Pin No.             | Signal Name | Description                                                             |

|---------------------|-------------|-------------------------------------------------------------------------|

| 1, 4, 6,<br>7, 8, 9 | N.C         | Not connected                                                           |

| 2                   | Rx_RS232    | Rx RS232 level signal (receive), between the hosting system and the MB  |

| 3                   | Tx_RS232    | Tx RS232 level signal (transmit), between the hosting system and the MB |

| 5                   | GND_F       | Floating ground                                                         |

Manufacturer: Coxoc

Manufacture part number: 205A-09MGPBBA3

Figure 11: Isolated RS232

#### 8. Isolated UART Interface (see Figure 12)

UART interface from the hosting system and the MB, then directed to the DB (Isolation circuitry on the daughter board).

| Pin No. | Signal Name      | Description                                                                                     |

|---------|------------------|-------------------------------------------------------------------------------------------------|

| 1       | 3_3V_iso         | 3.3 VDC coming from the hosting system (isolated from PoE domain), referenced to 'GND_Floating' |

| 2       | UART_Rx_isolated | Rx UART level signal (receive), between the hosting system and the MB (3.3 VDC)                 |

| 3       | UART_Tx_isolated | Tx UART level signal (transmit), between the hosting system and the MB (3.3 VDC)                |

| 4       | GND_F            | Floating ground                                                                                 |

| 5       | N.C              | Not connected                                                                                   |

- Manufacturer: CviLux

- Manufacture part number: CI25-05P1V00

Figure 12: Isolated UART Interface

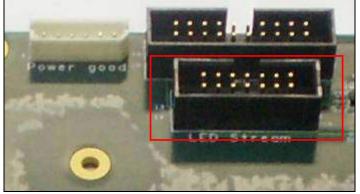

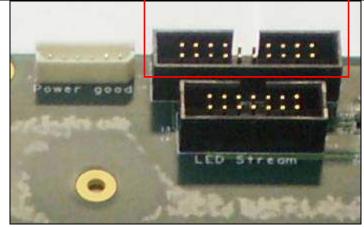

#### **9. LEDs Indication** (see Figure 13)

This interface controls the port status indication LEDs. Using four dedicated signals the LEDs indicate the ports status (on, off, and so on)

| Pin No. | Signal Name   | Description                                                              |

|---------|---------------|--------------------------------------------------------------------------|

| 1       | LED_reset     | Reset to the LED board                                                   |

| 2       | LED_Latch_b   | Latch LED signal running to LED indication board ('b' - buffered signal) |

| 7       | Vperi pull up | Vperi reference through a 10 Kohm resistor                               |

| 12      | GND_D         | Digital ground at the PoE domain                                         |

| 13      | LED_SCK_b     | Clock LED signal running to LED indication board ('b' - buffered signal) |

| 14      | LED_DATA_b    | Data LED signal running to LED indication board ('b' - buffered signal)  |

| 3, 4, 5,<br>6, 8, 9,<br>10, 11 | N.C | Not connected |

|--------------------------------|-----|---------------|

|--------------------------------|-----|---------------|

- Manufacturer: CviLux

- Manufacture part number: CH87-142V200

Figure 13: LEDs Indication

### 10. Daisy Chain (see Figure 14)

This interface enables a connection between two MBs destined to support eight PoE managers (PD69012) by a single PoE controller (PD69000).

| Pin No.                        | Signal Name       | Description                                                                           |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| 1                              | xDisable_ports    | Disable_ports signal to the PoE application (used for cascading purposes)             |

| 2                              | xPoE_RESET        | Reset signal to the PD69012 ICs (used for cascading purposes)                         |

| 3                              | PG0               | Power Good' signal, power supply status indication                                    |

| 4                              | PG1               | 'Power Good' signal, power supply status indication                                   |

| 5                              | PG2               | 'Power Good' signal, power supply status indication                                   |

| 6                              | PG3               | 'Power Good' signal, power supply status indication                                   |

| 7, 8, 10,<br>13, 14,<br>15, 19 | GND_D             | Digital ground at PoE domain                                                          |

| 9                              | SDA_in_auto_mode  | I <sup>2</sup> C SDA_in - data I <sup>2</sup> C signal (used for cascading purposes)  |

| 11                             | SDA_out_auto_mode | I <sup>2</sup> C SDA_out - data I <sup>2</sup> C signal (used for cascading purposes) |

| 12                             | SCL_auto_mode     | I <sup>2</sup> C SCL - clock I <sup>2</sup> C signal (used for cascading purposes)    |

| 16                             | ESPI_MISO         | ESPI 'master in' slave out' signal (used for cascading purposes)                      |

| 17                             | ESPI_MOSI         | ESPI 'master out slave in' signal (used for cascading purposes)                       |

| 18                             | ESPI_CS           | ESPI 'chip select' signal (used for cascading purposes)                               |

| 20                             | ESPI_SCK          | ESPI clock (used for cascading purposes)                                              |

Manufacturer: CviLux

Manufacture part number: CH87-142V200

Figure 14: Daisy Chain Interface

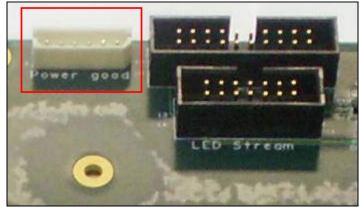

### 11. External Power Supplies (see Figure 15)

This interface supplies the 'Power Good' indication signals coming from the power supplies, indicating the operating/failed power supply's status and hot-swap signal for a hot swappable PoE application.

| Pin No. | Signal Name | Description                                                                   |

|---------|-------------|-------------------------------------------------------------------------------|

| 1       | PG0         | 'Power good' signal - power supply status indication                          |

| 2       | PG1         | 'Power good' signal - power supply status indication                          |

| 3       | PG2         | 'Power good' signal - power supply status indication                          |

| 4       | PG3         | 'Power good' signal - power supply status indication                          |

| 5       | GND_D       | Digital ground at the PoE domain                                              |

| 6       | xHSWP       | Hot Swap control signal, indicating that the PoE application is hot swappable |

- Manufacturer: CviLux

- Manufacture part number: CI25-06P1V00

Figure 15: External Power Supplies

# 4 Electrical Characteristics

The evaluation board's electrical characteristics are described below:

| Parameter                                | Symbol | Min. | Max. | Units |

|------------------------------------------|--------|------|------|-------|

| Main DC supply Vmain                     |        | 44   | 57   | V     |

| Port Isolation to chassis                |        | -    | 1.5  | kVrms |

| All communication's Isolation to chassis |        | -    | 1.5  | kVrms |

The MB's electrical characteristics depend on the daughter board to which it is connected.

# 5 Installation

This chapter describes the steps required to install and operate the MB Evaluation board with any DB PoE application.

## 5.1 Preliminary Considerations and Safety Precautions

- Verify that the board's power supply is turned on before the peripheral devices are turned on.

- Connect all the required peripherals prior to powering the board.

- Do not hot swap any components!

- Verify that the board is well configured prior to turning on the power supply.

## 5.2 Initial Configuration

It is highly important to verify that the Evaluation board is properly configured prior to starting any operation. Refer to the *Software GUI User Guide, catalogue number 06-0027-056* for detailed information related to the software and GUI used for Enhance Mode operation.

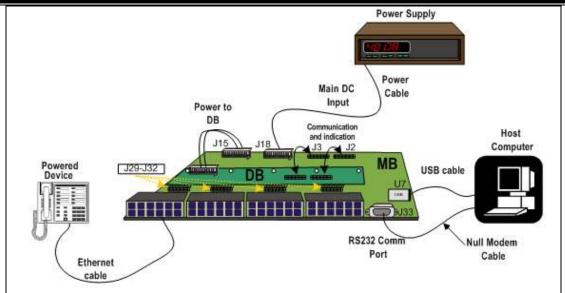

## 5.3 Hardware Setup

(See and Figure 17)

- 1. Connect DB port connectors to the MB's J29 to J32 connectors.

- 2. Place the DB on top of the MB in such a way that DB's holes are aligned with the appropriate MB spacers.

- 3. Tighten the five screws on top of the DB to the appropriate MB spacers.

- 4. Configure EVB according to required operation mode Auto/Enhanced mode:

| Annliegtion      | Comm                                   | Switches and jumpers                            |              |     |        |      |              |                  |         |

|------------------|----------------------------------------|-------------------------------------------------|--------------|-----|--------|------|--------------|------------------|---------|

| Application      | RS232/USB                              | I2C(Aardvark*)                                  | J3,5,7,8     | SW7 | SW2    | SW5  | SW6          | SW1              | SW4/SW3 |

| Enhanced<br>mode | Connect<br>RS232<br>cable to MB<br>J33 |                                                 | Short<br>1-2 | UP  | Normal | Down |              | EEPROM<br>normal | up      |

| Auto mode        |                                        | Connect<br>cable from<br>Aardvark* to<br>MB J14 | Short<br>1-2 | UP  | Debug  | Down | Auto<br>mode | EEPROM<br>normal | up      |

\*Aardvark – USB to I2C communication adaptor. Any other USB to I2C adaptor can be used.

- 5. Connect the power cable from J15 to the DB.

- 6. Connect the Communication and Indication flat cables as follows:

- From the MB's J2 flat cable to the DB.

- From MB's J3 flat cable to the DB.

- 7. Connect a power cable from the power supply to the MB (J18).

- 8. Connect the RS232 cable from the Host PC to the MB's J33 (for UART communication).

Figure 16: Test Setup

Figure 17: Auto Mode Communication Setup

## 5.4 Auto-Mode Patch Burning

Auto mode functionality can be modified using a patch. A relevant patch can be burnt into EEPROM prior to system power up according to the following procedure:

- 1. Connect Aardwark to connector JP1-(EEPROM)

- 2. Turn SW1 to EEPROM Burning Mode position.

- 3. Connect the Power Supply and open PD69012 E2GUI.

- 4. To burn patch file upload relevant patch file using E2 GUI:

- a. Choose E2 Structs tab.

- b. Click Load Tx Table button and browse for the relevant file (.xml format).

- c. Click GUI SEND button while pushing Reset Push button (SW1) on the DB (see Figure 18)

19

| Setup About                                           |                    |   |       |               |          |          |                          |                               |        |  |

|-------------------------------------------------------|--------------------|---|-------|---------------|----------|----------|--------------------------|-------------------------------|--------|--|

| 9 🗊 📰 🚯                                               |                    |   |       |               |          |          |                          |                               |        |  |

| 2 Structs E2 Comm                                     |                    |   |       |               |          |          |                          |                               |        |  |

| EEprom H                                              | leader             |   | E     | Eprom Data    | a        |          |                          |                               |        |  |

| E2 Header                                             | Value [Hex]        |   | Index | Address (Hex) | Chip Add | RAM Add  | Data                     | Description                   | ^      |  |

| EEprom ID                                             | 1910               | • | 1     | 64            | е        | 1332     | Offf                     | disable all ports             |        |  |

| Header Struct Version                                 | 1                  |   | 2     | 64            | е        | 31e      | ab                       | open protkey                  |        |  |

| Data Version                                          | a                  |   | 3     | 70            | e        | 80       | db49                     | patch 0 · Rise time exit      |        |  |

| Number of records                                     | 9C                 |   | 4     | 76            | е        | 82       | 1ca0                     | patch 0 - Rise time exit de   | est    |  |

| Enabled Patches                                       | 1f                 |   | 5     | 7C            | е        | 84       | e89f                     | patch 1 - class spike ex      | t      |  |

| Data Start Address                                    | 64                 |   | 6     | 82            | е        | 86       | 1c00                     | patch 1 - class spike exit d  | est    |  |

| Header CheckSum                                       | 1143               |   | 7     | 88            | e        | 88       | e8f5                     | patch 2 - cass threshold e    | xit    |  |

|                                                       |                    |   | 8     | 8E            | е        | 8a       | 1c30                     | patch 2 - class threshold exi | dest   |  |

|                                                       |                    | 9 | 94    | е             | 8c       | c897     | patch 3 - PM threshold e | cit                           |        |  |

|                                                       |                    |   | 10    | 94            | е        | 8e       | 1c50                     | patch 3 - PM threshold exit   | dest   |  |

|                                                       |                    |   | 11    | A0            | е        | 90       | de03                     | patch 4 - Static PM Startup   | exit   |  |

| rrent File 9_Alcatel EEPR                             | DM.xml             |   | 12    | A6            | е        | 92       | 1c70                     | patch 4 - Static PM Startup e | wit    |  |

|                                                       |                    |   | 13    | AC            | е        | 94       | fe3f                     | patch 5 - auto int out ex     | t exit |  |

| oad Tx Table                                          | Tx Table           |   | 14    | B2            | е        | 96       | 1d20                     | patch 5 - auto int out exit o | lest 💊 |  |

|                                                       | Data CheckSum      | 0 | )     | 0             | E491     | Checksum | Delete<br>selected row   | Delete last Cle<br>struct Tat |        |  |

|                                                       |                    |   |       |               |          |          |                          |                               |        |  |

| pecify Directory name:<br>:\Documents and Settings\te | stor amen' Deskton |   |       |               |          | Create H | Calculate<br>checksum    | Create Ser<br>Struct          | nd     |  |

| . AD ocuments and bettings te                         | ster_amsgybesktop  |   |       |               |          | File     |                          |                               |        |  |

Figure 18: E2 GUI

- 5. Verify proper burning:

- a. Choose the E2 Comm tab

- b. Click the Read button and make sure burnt data is correct.

- 6. Once verification is completed, return to Initial Configuration.

The information contained in the document is PROPRIETARY AND CONFIDENTIAL information of Microsemi and cannot be copied, published, uploaded, posted, transmitted, distributed or disclosed or used without the express duly signed written consent of Microsemi If the recipient of this document has entered into a disclosure agreement with Microsemi, then the terms of such Agreement will also apply. This document and the information contained herein may not be modified, by any person other than authorized personnel of Microsemi. No license under any patent, copyright, trade secret or other intellectual property right is granted to or conferred upon you by disclosure or delivery of the information, either expressly, by implication, inducement, estoppels or otherwise. Any license under such intellectual property rights must be approved by Microsemi in writing signed by an officer of Microsemi. Microsemi reserves the right to change the configuration, functionality and performance of its products at anytime without any notice. This product has been subject to limited testing and should not be used in conjunction with life-support or other mission-critical equipment or applications. Microsemi assumes no liability whatsoever, and Microsemi disclaims any express or implied warranty, relating to sale and/or use of Microsemi products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. The product is subject to other terms and conditions which can be located on the web at http://www.microsemi.com/legal/tnc.asp

#### **Revision History**

| Revision Level / Date | Para. Affected | Description                    |

|-----------------------|----------------|--------------------------------|

| 0.1 / 21 / 03/ 2008   |                | Initial revision               |

| 1.1 / 21 / 04 / 2011  |                | 5 Installation                 |

| 1.2 / March 04 2014   |                | Updating EVB P/N to PD-IM-7448 |

### © 2014 Microsemi Corp. All rights reserved.

Visit our web site at: <u>www.microsemi.com</u>

All rights reserved.

For support contact: sales AMSG@microsemi.com

Catalog Number: 06-0025-56