# HI5702

#### August 1997

# Features

- Sampling Rate ...... 40 MSPS

- 8.3 Bits Guaranteed at f<sub>IN</sub> = 10MHz

- Low Power

- Wide Full Power Input Bandwidth ..... 250MHz

- Sample and Hold Not Required

- Single-Ended or Differential Input

- Input Signal Range ..... 1.25V

- Single Supply Voltage .....+5V

- TTL Compatible Interface

# Applications

- Professional Video Digitizing

- Medical Imaging

- Digital Communication Systems

- High Speed Data Acquisition

# Description

The HI5702 is a monolithic, 10-bit, analog-to-digital converter fabricated in a BiCMOS process. It is designed for high speed applications where wide bandwidth and low power consumption are essential. Its 40 MSPS speed is made possible by a fully differential pipeline architecture which also eliminates the need for an external sample and hold circuit. The HI5702 has excellent dynamic performance while consuming <650mW power at 40 MSPS. Data output latches are provided which present valid data to the output bus with a latency of 7 clock cycles.

10-Bit, 40 MSPS A/D Converter

Refer to the HI5703, HI5746, or HI5767 data sheets for lower power consumption.

# **Ordering Information**

| PART<br>NUMBER | SAMPLE<br>RATE | TEMP.<br>RANGE ( <sup>O</sup> C) | PACKAGE          | PKG.<br>NO. |

|----------------|----------------|----------------------------------|------------------|-------------|

| HI5702KCB      | 40 MSPS        | 0 to 70                          | 28 Ld SOIC (W)   | M28.3       |

| HI5702JCB      | 36 MSPS        | 0 to 70                          | 28 Ld SOIC (W)   | M28.3       |

| HI5702-EV2     |                | 25                               | Evaluation Board | k           |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

### Absolute Maximum Ratings

| Supply Voltage, AV <sub>CC</sub> or DV <sub>CC</sub> to AGND or DGND | . +6V            |

|----------------------------------------------------------------------|------------------|

| DGND to AGND                                                         | . 0.3V           |

| Digital I/O Pins DGND to I                                           | ⊃V <sub>CC</sub> |

| Analog I/O Pins                                                      | AVCC             |

|                                                                      |                  |

#### **Operating Conditions**

Temperature Range

#### Thermal Information

| Thermal Resistance (Typical, Note 1)      | $\theta_{JA}$ ( <sup>o</sup> C/W)      |

|-------------------------------------------|----------------------------------------|

| SOIC Package                              | 70                                     |

| Maximum Junction Temperature              |                                        |

| Maximum Storage Temperature Range65       | 5 <sup>0</sup> C to 150 <sup>0</sup> C |

| Maximum Lead Temperature (Soldering, 10s) |                                        |

| (SOIC - Lead Tips Only)                   |                                        |

|                                           |                                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

9.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TEST CONDITIONS                 | MIN      | ТҮР  | МАХ  | UNITS                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                 | <u>I</u> |      |      | •                                                                                                                                                                           |

| Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                 | 10       | -    | -    | Bits                                                                                                                                                                        |

| Integral Linearity Error, INL                                                                                                                                                                                                                                                                                                                                                                                                                                        | f <sub>IN</sub> = DC            | -        | ±1   | ±2.0 | LSB                                                                                                                                                                         |

| Differential Linearity Error, DNL<br>(Guaranteed No Missing Codes)                                                                                                                                                                                                                                                                                                                                                                                                   | f <sub>IN</sub> = DC            | -        | ±0.5 | ±1   | LSB                                                                                                                                                                         |

| Offset Error, V <sub>OS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                        | f <sub>IN</sub> = DC            | -        | 3    | -    | LSB                                                                                                                                                                         |

| Full Scale Error, FSE                                                                                                                                                                                                                                                                                                                                                                                                                                                | f <sub>IN</sub> = DC            | -        | 2    | -    | LSB                                                                                                                                                                         |

| DYNAMIC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                               | •        |      |      |                                                                                                                                                                             |

| Minimum Conversion Rate                                                                                                                                                                                                                                                                                                                                                                                                                                              | No Missing Codes                | -        | 0.5  | -    | MSPS                                                                                                                                                                        |

| Maximum Conversion Rate                                                                                                                                                                                                                                                                                                                                                                                                                                              | No Missing Codes<br>HI5702KCB   | 40       | -    | -    | MSPS                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | HI5702JCB                       | 36       | -    | -    | MSPS                                                                                                                                                                        |

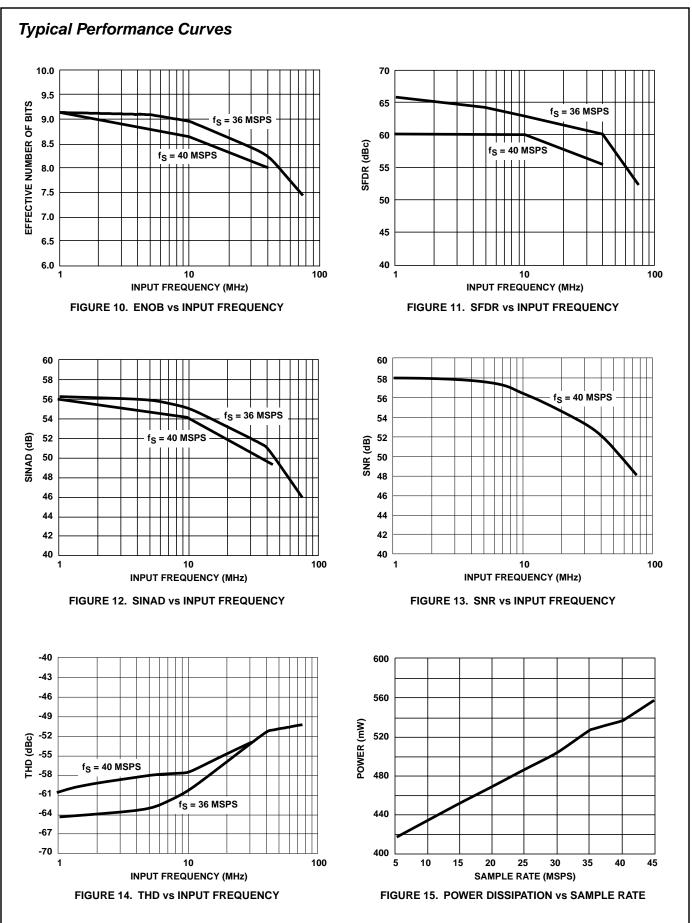

| Effective Number of Bits, ENOB                                                                                                                                                                                                                                                                                                                                                                                                                                       | f <sub>IN</sub> = 1MHz          | -        | 9.0  | -    | Bits                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 5MHz          | -        | 9.0  | -    | Bits                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 10MHz         | 8.3      | 8.8  | -    | Bits                                                                                                                                                                        |

| Signal to Noise and Distribution Ratio,                                                                                                                                                                                                                                                                                                                                                                                                                              | f <sub>IN</sub> = 1MHz          | -        | 57   | -    | dB                                                                                                                                                                          |

| SINAD<br>RMS Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f <sub>IN</sub> = 5MHz          | -        | 57   | -    | dB                                                                                                                                                                          |

| = RMS Noise + Distortion                                                                                                                                                                                                                                                                                                                                                                                                                                             | f <sub>IN</sub> = 10MHz         | 51       | 56   | -    | dB                                                                                                                                                                          |

| Signal to Noise Ratio, SNR                                                                                                                                                                                                                                                                                                                                                                                                                                           | f <sub>IN</sub> = 1MHz          | -        | 56   | -    | dB                                                                                                                                                                          |

| = RMS Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                         | f <sub>IN</sub> = 5MHz          | -        | 56   | -    | dB                                                                                                                                                                          |

| RMS NOISE                                                                                                                                                                                                                                                                                                                                                                                                                                                            | f <sub>IN</sub> = 10MHz         | 51       | 55   | -    | dB                                                                                                                                                                          |

| Total Harmonic Distortion, THD                                                                                                                                                                                                                                                                                                                                                                                                                                       | f <sub>IN</sub> = 1MHz          | -        | -64  | -    | ±2.0 LSB   ±1 LSB   - LSB   - LSB   - MSPS   - MSPS   - MSPS   - Bits   - Bits   - Bits   - dB   - dB |

| asolution<br>agral Linearity Error, INL<br>erential Linearity Error, DNL<br>arranteed No Missing Codes)<br>Set Error, V <sub>OS</sub><br>Scale Error, FSE<br>NAMIC CHARACTERISTICS<br>imum Conversion Rate<br>kimum Conversion Rate<br>Adv<br>and to Noise and Distribution Ratio,<br>(AD<br>RMS Signal<br>RMS Noise + Distortion<br>nal to Noise Ratio, SNR<br>RMS Signal<br>RMS Noise<br>al Harmonic Distortion, THD<br>Harmonic Distortion<br>Harmonic Distortion | f <sub>IN</sub> = 5MHz          | -        | -63  | -    | dBc                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 10MHz         | -        | -60  | -    | dBc                                                                                                                                                                         |

| 2nd Harmonic Distortion                                                                                                                                                                                                                                                                                                                                                                                                                                              | f <sub>IN</sub> = 1MHz          | -        | -75  | -    | dBc                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 5MHz          | -        | -75  | -    | dBc                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 10MHz         | -        | -73  | -    | dBc                                                                                                                                                                         |

| 3rd Harmonic Distortion                                                                                                                                                                                                                                                                                                                                                                                                                                              | f <sub>IN</sub> = 1MHz          | -        | -66  | -    | dBc                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 5MHz          | -        | -64  | -    | dBc                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 10MHz         | -        | -63  | -    | dBc                                                                                                                                                                         |

| Spurious Free Dynamic Range, SFDR                                                                                                                                                                                                                                                                                                                                                                                                                                    | f <sub>IN</sub> = 1MHz          | -        | 66   | -    | dBc                                                                                                                                                                         |

| . –                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f <sub>IN</sub> = 5MHz          | -        | 64   | - 1  | dBc                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f <sub>IN</sub> = 10MHz         | 54       | 63   | -    | dBc                                                                                                                                                                         |

| Intermodulation Distortion, IMD                                                                                                                                                                                                                                                                                                                                                                                                                                      | $f_1 = 1$ MHz, $f_2 = 1.02$ MHz | -        | -59  | -    | dBc                                                                                                                                                                         |

$\begin{array}{ll} \textbf{Electrical Specifications} & \text{AV}_{CC} = \text{DV}_{CC} = +5\text{V}; \ \text{V}_{REF} + = 3.25\text{V}; \ \text{V}_{REF} - = 2\text{V}; \ \text{f}_{S} = \text{Specified Clock Frequency at 50\% Duty Cycle}; \\ \text{C}_{L} = 20\text{pF}; \ \text{T}_{A} = 25^{\text{o}}\text{C}; \ \text{Unless Otherwise Specified} \ \textbf{(Continued)} \end{array}$

| PARAMETER                                                                     | TEST CONDITIONS                             | MIN   | ТҮР   | MAX   | UNITS  |  |

|-------------------------------------------------------------------------------|---------------------------------------------|-------|-------|-------|--------|--|

| Differential Gain Error                                                       | f <sub>S</sub> = 17.72MHz, 6 Step, Mod Ramp | -     | 0.5   | 1     | %      |  |

| Differential Phase Error                                                      | f <sub>S</sub> = 17.72MHz, 6 Step, Mod Ramp | -     | 0.25  | 0.5   | Degree |  |

| Transient Response                                                            |                                             | -     | 1     | -     | Cycle  |  |

| Overvoltage Recovery                                                          | 0.2V Overdrive                              | -     | 1     | -     | Cycle  |  |

| ANALOG INPUT                                                                  |                                             |       |       |       |        |  |

| Analog Input Resistance, R <sub>IN</sub>                                      | (Note 3)                                    | -     | 1     | -     | MΩ     |  |

| Analog Input Capacitance, CIN                                                 |                                             | -     | 7     | -     | pF     |  |

| Analog Input Bias Current, IB                                                 | (Note 3)                                    | -50   | -     | +50   | μΑ     |  |

| Full Power Input Bandwidth                                                    |                                             | -     | 250   | -     | MHz    |  |

| Analog Input Common Mode Range<br>(V <sub>IN</sub> + + V <sub>IN</sub> -) / 2 | Differential Mode (Note 2)                  | 0.625 | -     | 4.375 | V      |  |

| REFERENCE INPUT                                                               |                                             |       |       |       |        |  |

| Total Reference Resistance, RL                                                |                                             | 200   | 400   | -     | Ω      |  |

| Reference Current                                                             |                                             | -     | 3     | 6     | mA     |  |

| Positive Reference Input, VREF+                                               | (Note 2)                                    | -     | 3.25  | 3.3   | V      |  |

| Negative Reference Input, V <sub>REF</sub> -                                  | (Note 2)                                    | 1.95  | 2.0   | -     | V      |  |

| Reference Common Mode Voltage                                                 | (Note 2)                                    | 2.575 | 2.625 | 2.675 | V      |  |

| (V <sub>REF</sub> + + V <sub>REF</sub> -) / 2                                 |                                             |       |       |       |        |  |

| COMMOM MODE VOLTAGE                                                           |                                             |       |       |       | -      |  |

| Common Mode Voltage Output, V <sub>CM</sub>                                   |                                             | -     | 2.8   | -     | V      |  |

| Max Output Current                                                            |                                             | -     | -     | 1     | mA     |  |

| DIGITAL INPUTS                                                                |                                             |       |       |       |        |  |

| Input Logic High Voltage, V <sub>IH</sub>                                     |                                             | 2.0   | -     | -     | V      |  |

| Input Logic Low Voltage, VIL                                                  |                                             | -     | -     | 0.8   | V      |  |

| Input Logic High Current, IIH                                                 | $V_{IN} = 5V$                               | -     | -     | 10.0  | μΑ     |  |

| Input Logic Low Current, IIL                                                  | $V_{IN} = 0V$                               | -     | -     | 10.0  | μΑ     |  |

| Input Capacitance, CIN                                                        |                                             | -     | 7     | -     | pF     |  |

| DIGITAL OUTPUTS                                                               |                                             |       |       | •     | •      |  |

| Output Logic Sink Current, IOL                                                | $V_{O} = 0.4V$                              | 3.2   | -     | -     | mA     |  |

| Output Logic Source Current, IOH                                              | $V_{O} = 2.4 V$                             | -0.2  | -     | -     | mA     |  |

| Output Capacitance, C <sub>OUT</sub>                                          |                                             | -     | 5     | -     | pF     |  |

| TIMING CHARACTERISTICS                                                        |                                             |       |       | •     | •      |  |

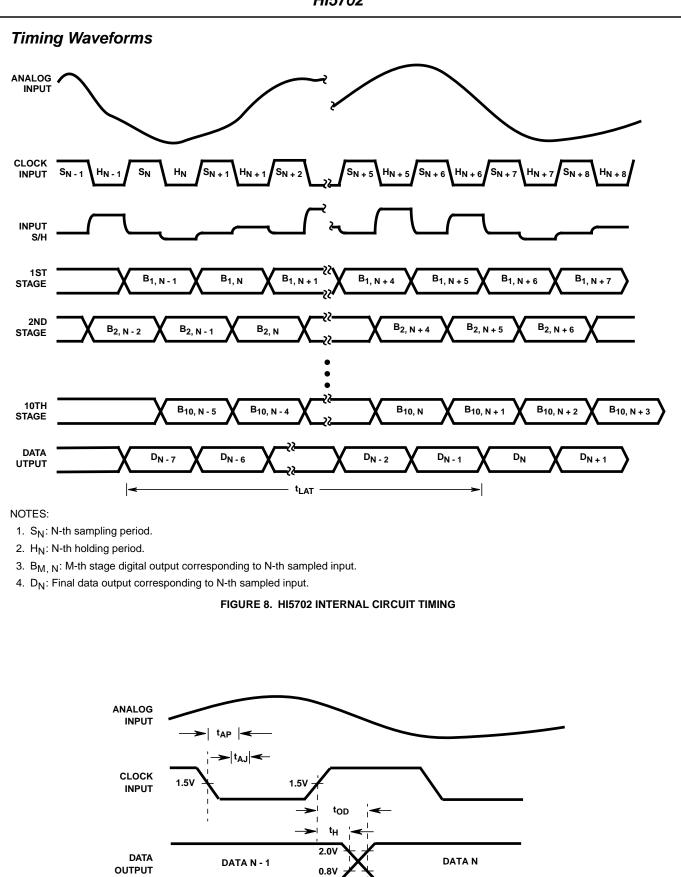

| Aperture Delay, t <sub>AP</sub>                                               |                                             | -     | 5     | -     | ns     |  |

| Aperture Jitter, t <sub>AJ</sub>                                              |                                             | -     | 5     | -     | ps     |  |

| Data Output Delay, t <sub>OD</sub>                                            |                                             | -     | 6     | -     | ns     |  |

| Data Output Hold, t <sub>H</sub>                                              |                                             | -     | 5     | -     | ns     |  |

| Data Latency, t <sub>LAT</sub>                                                | For a Valid Sample (Note 2)                 | -     | -     | 7     | Cycles |  |

| Power-Up Initialization                                                       | Data Invalid Time (Note 2)                  | -     | -     | 20    | Cycles |  |

| POWER SUPPLY CHARACTERISTICS                                                  |                                             |       |       | •     | . ·    |  |

| Supply Current, I <sub>CC</sub>                                               | V <sub>IN</sub> = 0V                        | -     | 120   | 130   | mA     |  |

| Power Dissipation                                                             | V <sub>IN</sub> = 0V                        | -     | 600   | 650   | mW     |  |

| Offset Error PSRR, $\Delta V_{OS}$                                            | $AV_{CC}$ or $DV_{CC} = 5V \pm 5\%$         | -     | 0.2   | -     | LSB    |  |

| Gain Error PSRR, ∆FSE                                                         | $AV_{CC} \text{ or } DV_{CC} = 5V \pm 5\%$  | -     | 1     | -     | LSB    |  |

NOTES:

10. Parameter guaranteed by design or characterization and not production tested.

11. With the clock off.

FIGURE 9. INPUT-TO-OUTPUT TIMING

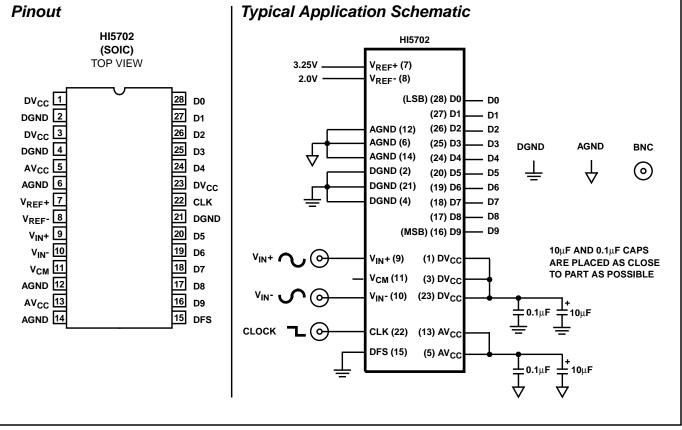

| PIN # | NAME               | DESCRIPTION               |

|-------|--------------------|---------------------------|

| 1     | DV <sub>CC</sub>   | Digital Supply.           |

| 2     | DGND               | Digital Ground.           |

| 3     | DV <sub>CC</sub>   | Digital Supply.           |

| 4     | DGND               | Digital Ground.           |

| 5     | AV <sub>CC</sub>   | Analog Supply.            |

| 6     | AGND               | Analog Ground.            |

| 7     | V <sub>REF</sub> + | Positive Reference.       |

| 8     | V <sub>REF</sub> - | Negative Reference.       |

| 9     | V <sub>IN</sub> +  | Positive Analog Input.    |

| 10    | V <sub>IN</sub> -  | Negative Analog Input.    |

| 11    | V <sub>CM</sub>    | DC Output Voltage Source. |

| 12    | AGND               | Analog Ground.            |

| 13    | AV <sub>CC</sub>   | Analog Supply.            |

| 14    | AGND               | Analog Ground.            |

| 15    | DFS                | Data Format Select.       |

| 16    | D9                 | Data Bit 9 Output (MSB).  |

| 17    | D8                 | Data Bit 8 Output.        |

| 18    | D7                 | Data Bit 7 Output.        |

| 19    | D6                 | Data Bit 6 Output.        |

| 20    | D5                 | Data Bit 5 Output.        |

| 21    | DGND               | Digital Ground.           |

| 22    | CLK                | Input Clock.              |

| 23    | DV <sub>CC</sub>   | Digital Supply.           |

| 24    | D4                 | Data Bit 4 Output.        |

| 25    | D3                 | Data Bit 3 Output.        |

| 26    | D2                 | Data Bit 2 Output.        |

| 27    | D1                 | Data Bit 1 Output.        |

| 28    | D0                 | Data Bit 0 Output (LSB).  |

####

# **Detailed Description**

#### **Theory of Operation**

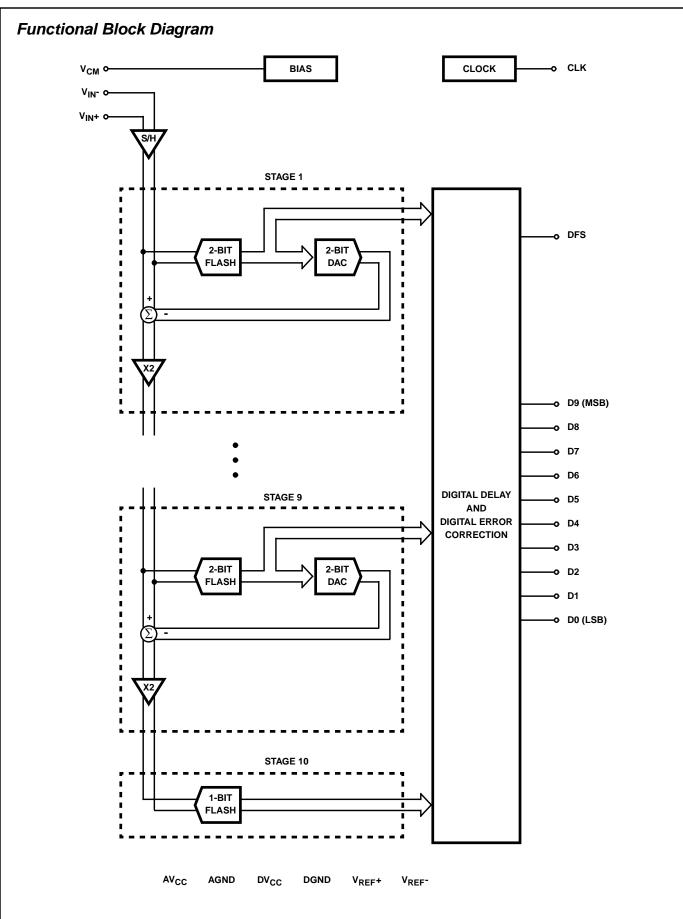

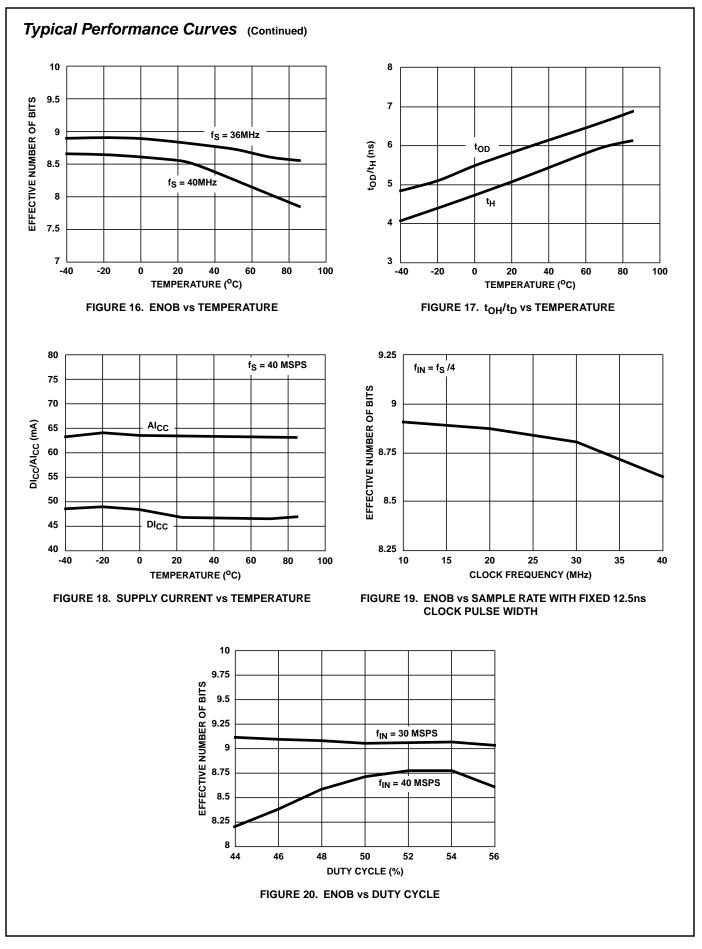

The HI5702 is a 10-bit fully differential sampling pipeline A/D converter with digital error correction. Figure 13 depicts the circuit for the front end differential-in-differential-out sampleand-hold (S/H). The switches are controlled by an internal clock which is a non-overlapping two phase signal,  $\phi_1$  and  $\phi_2$ , derived from the master clock. During the sampling phase,  $\phi_1$ , the input signal is applied to the sampling capacitors, CS. At the same time the holding capacitors, CH, are discharged to analog ground. At the falling edge of  $\phi_1$  the input signal is sampled on the bottom plates of the sampling capacitors. In the next clock phase,  $\phi_2$ , the two bottom plates of the sampling capacitors are connected together and the holding capacitors are switched to the op-amp output nodes. The charge then redistributes between CS and C<sub>H</sub> completing one sample-and-hold cycle. The output is a fully-differential, sampled-data representation of the analog input. The circuit not only performs the sample-and-hold function but will also convert a single-ended input to a fullydifferential output for the converter core. During the sampling

phase, the V<sub>IN</sub> pins see only the on-resistance of a switch and CS. The small values of these components result in a typical full power bandwidth of 250MHz.

FIGURE 21. ANALOG INPUT SAMPLE-AND-HOLD

As illustrated in the Functional Block Diagram and the Timing Diagram in Figure 1, nine identical pipeline subconverter stages, each containing a two-bit flash and a two-bit multiplying digital-to-analog converter, follow the S/H circuit with the tenth stage being a one bit flash converter. Each converter stage in the pipeline will be sampling in one phase and amplifying in the other clock phase. Each individual sub-converter clock signal is offset by 180 degrees from the previous stage clock signal with the result that alternate stages in the pipeline will perform the same operation.

The two-bit digital output of each stage is fed to a digital delay line controlled by the internal clock. The purpose of the delay line is to align the digital output data to the corresponding sampled analog input signal. This delayed data is fed to the digital error correction circuit which corrects the error in the output data with the information contained in the redundant bits to form the final 10-bit output for the converter.

Because of the pipeline nature of this converter, the data on the bus is output at the 7th cycle of the clock after the analog sample is taken. This delay is specified as the data latency. After the data latency time, the data representing each succeeding sample is output at the following clock pulse. The output data is synchronized to the external clock by a double buffered latching technique.

The output of the digital correction circuit is available in two's complement or binary format depending on the condition of the Data Format Select (DFS) input.

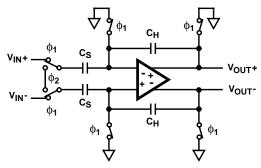

#### **Analog Input, Differential Connection**

The analog input to the HI5702 is a differential input that can be configured in various ways depending on the signal source and the required level of performance. A fully differential connection (Figure 15) will give the best performance for the converter.

FIGURE 22. AC COUPLED DIFFERENTIAL INPUT

Since the HI5702 is powered by a single +5V analog supply, the analog input is limited to be between ground and +5V, which implies the common mode voltage can range of 0.625V to 4.375V. The performance of the ADC does not change significantly with the value of the common mode voltage.

A DC voltage source,  $V_{CM}$ , about half way between the top and bottom reference voltages, is made available to the user to help simplify circuit design when using a differential input. This low output impedance voltage source is not designed to be a reference but makes an excellent bias source and stays within the common mode range over temperature. It has a temperature coefficient of about 200ppm.

Assume the difference between V<sub>REF</sub>+, typically 3.25V, and V<sub>REF</sub>-, typically 2V, is 1.25V in Figure 15. Fullscale is achieved when V<sub>IN</sub>+ and V<sub>IN</sub>- inputs are 1.25V<sub>P-P</sub>, with V<sub>IN</sub>-being 180 degrees out of phase with V<sub>IN</sub>+. The converter will be at positive fullscale when the V<sub>IN</sub>+ input is at V<sub>CM</sub> + 0.625V and V<sub>IN</sub>- is at V<sub>CM</sub> - 0.625V (V<sub>IN</sub>+ - V<sub>IN</sub>- = 1.25V). Conversely, the ADC will be at negative fullscale when the V<sub>IN</sub>+ input is equal to V<sub>CM</sub> - 0.625V and V<sub>IN</sub>- is at V<sub>CM</sub> + 0.625V (V<sub>IN</sub>+ - V<sub>IN</sub>- = -1.25V).

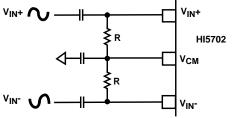

The analog input can be DC coupled as long as the inputs are within the common mode range, Figure 16.

FIGURE 23. DC COUPLED DIFFERENTIAL INPUT

The resistors, R, in Figure 16 are not absolutely necessary but will improve performance. Values of  $100\Omega$  or less are typical. A capacitor, C, connected from V<sub>IN</sub>+ to V<sub>IN</sub>- will help common mode any noise on the inputs, also improving performance. Values around 20pF are sufficient and can be used on AC coupled inputs as well.

#### **Analog Input, Single-Ended Connection**

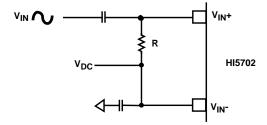

The configuration shown in Figure 17 may be used with a single ended AC coupled input.

FIGURE 24. AC COUPLED SINGLE ENDED INPUT

Sufficient headroom must be provided such that the input voltage never goes above +5V or below AGND.

Again, assume the difference between V<sub>REF</sub>+, typically 3.25V, and V<sub>REF</sub>-, typically 2V, is 1.25V. If V<sub>IN</sub> is a 2.5V<sub>P-P</sub>

sinewave riding on a positive voltage equal to V<sub>DC</sub>, the converter will be at positive fullscale when V<sub>IN</sub>+ is at V<sub>DC</sub> + 1.25V and will be at negative fullscale when V<sub>IN</sub> is equal to V<sub>DC</sub> - 1.25V. In this case, V<sub>DC</sub> could range between 1.25V and 3.75V without a significant change in ADC performance. The simplest way to produce V<sub>DC</sub> is to use the V<sub>CM</sub> output of the HI5702.

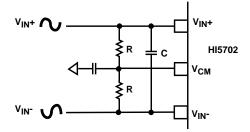

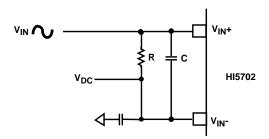

The analog input can be DC coupled as long as the input is within the common mode range, Figure 18.

FIGURE 25. DC COUPLED SINGLE ENDED INPUT

The resistor, R, in Figure 18 is not absolutely necessary but will improve performance. Values of 100 $\Omega$  or less are typical. A capacitor, C, connected from V<sub>IN</sub>+ to V<sub>IN</sub>- will help common mode any noise on the inputs, also improving performance. Values around 20pF are sufficient and can be used on AC coupled inputs as well.

A single ended source may give better overall system performance if it is first converted to differential before driving the HI5702. Also refer to the application note AN9413, "Driving the Analog Input of the HI5702". This application note describes several different ways of driving the analog differential inputs.

#### Reference Input, V<sub>REF</sub>- V<sub>REF</sub>+

The converter requires two reference voltages connected to the V<sub>REF</sub> pins. The voltage range of the part with a differential input will be V<sub>REF</sub>+ - V<sub>REF</sub>-. The HI5702 is tested with V<sub>REF</sub>-equal to 2V and V<sub>REF</sub>+ equal to 3.25V for an input range of 1.25V. V<sub>REF</sub>+ and V<sub>REF</sub>- can differ from the above voltages as long as the common mode voltage between the reference pins ((V<sub>REF</sub>+ + V<sub>REF</sub>-) / 2) does not exceed 2.65V ±50mV and the limits on V<sub>REF</sub>+ and V<sub>REF</sub>- are not exceeded.

In order to minimize overall converter noise it is recommended that adequate high frequency decoupling be provided at the reference input pin.

#### **Digital Control and Clock Requirements**

The HI5702 provides a standard high-speed interface to external TTL logic families.

In order to ensure rated performance of the HI5702, the duty cycle of the clock should be held at 50%. It must also have low jitter and operate at standard TTL levels.

A Data Format Select (DFS) pin is provided which will determine the format of the digital data. When at logic low the data will be output in offset binary format. When at a logic high the data will be output in a two's complement format. Refer to Table 2 for further information. Performance of the HI5702 will only be guaranteed at conversion rates above 1 MSPS. This ensures proper performance of the internal dynamic circuits. Similarly, when power is first applied to the converter, a maximum of 20 cycles at a sample rate above 1 MSPS will have to be performed before valid data is available.

#### **Supply and Ground Considerations**

The HI5702 has separate analog and digital supply and ground pins to keep digital noise out of the analog signal path. The part should be mounted on a board that provides separate low impedance connections for the analog and digital supplies and grounds. For best performance, the supplies to the HI5702 should be driven by clean, linear regulated supplies. The board should also have good high frequency decoupling capacitors mounted as close as possible to the converter. If the part is powered off a single supply then the analog supply and ground pins should be isolated by ferrite beads from the digital supply and ground pins.

Refer to the Application Note "Using Intersil High Speed A/D Converters" (AN9214) for additional considerations when using high speed converters.

#### **Increased Accuracy**

The V<sub>OS</sub> and FSE errors as reported on the data sheet can be decreased by further calibration of the ADC. It will be assumed that the converter has offset binary coding. See the A/D code table (Table 2) for the ideal code transitions.

The first step would be to center the analog input to the desired midscale voltage. This voltage would then be adjusted up or down in the circuitry driving one side of the input to the HI5702 until the 511 to 512 transition occurs on the digital output.

Next, set the analog input to the HI5702 to the desired positive fullscale voltage. Adjust one side of the reference circuit up or down until the 1022 to 1023 transition occurs on the digital output of the converter.

# Static Performance Definitions

#### Offset Error (V<sub>OS</sub>)

The midscale code transition should occur at a level  $^{1}/_{4}$  LSB above half-scale. Offset is defined as the deviation of the actual code transition from this point.

#### Full-Scale Error (FSE)

The last code transition should occur for a analog input that is  $1^{3}/_{4}$  LSBs below positive full-scale with the offset error removed. Full-scale error is defined as the deviation of the actual code transition from this point.

#### **Differential Linearity Error (DNL)**

DNL is the worst case deviation of a code width from the ideal value of 1 LSB.

#### Integral Linearity Error (INL)

INL is the worst case deviation of a code center from a best fit straight line calculated from the measured data.

#### Power Supply Rejection Ratio (PSRR)

Each of the power supplies are moved plus and minus 5% and the shift in the offset and gain error (in LSBs) is noted.

# **Dynamic Performance Definitions**

Fast Fourier Transform (FFT) techniques are used to evaluate the dynamic performance of the HI5702. A low distortion sine wave is applied to the input, it is coherently sampled, and the output is stored in RAM. The data is then transformed into the frequency domain with an FFT and analyzed to evaluate the dynamic performance of the A/D. The sine wave input to the part is -0.5dB down from full-scale for all these tests.

SNR and SINAD are quoted in dB. The distortion numbers are quoted in dBc (decibels with respect to carrier) and **DO NOT** include any correction factors for normalizing to full scale.

|                                                                                                            | (NOTE 1) | OFFSET BINARY OUTPUT CODE<br>(DFS LOW) |    |             |    |    |    |    |    |    |    | ٦  | TWO'S COMPLEMENT OUTPUT CODE<br>(DFS HIGH) |    |    |    |    |    |             |    |   |

|------------------------------------------------------------------------------------------------------------|----------|----------------------------------------|----|-------------|----|----|----|----|----|----|----|----|--------------------------------------------|----|----|----|----|----|-------------|----|---|

| DIFFERENTIAL       INPUT VOLTAGE       V <sub>REF</sub> + = 3.25V       CODE     V <sub>REF</sub> - = 2.0V |          | M<br>S<br>B                            |    | L<br>S<br>B |    |    |    |    |    |    |    |    |                                            |    |    |    |    |    | L<br>S<br>B |    |   |

| DESCRIPTION (V)                                                                                            | D9       | D8                                     | D7 | D6          | D5 | D4 | D3 | D2 | D1 | D0 | D9 | D8 | D7                                         | D6 | D5 | D4 | D3 | D2 | D1          | D0 |   |

| Full Scale (FS)                                                                                            | 1.25V    | 1                                      | 1  | 1           | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1                                          | 1  | 1  | 1  | 1  | 1  | 1           | 1  | 1 |

| FS - 1 <sup>3</sup> / <sub>4</sub> LSB                                                                     | 1.2479V  | 1                                      | 1  | 1           | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 1                                          | 1  | 1  | 1  | 1  | 1  | 1           | 1  | 0 |

| <sup>1</sup> / <sub>2</sub> FS + <sup>1</sup> / <sub>4</sub> LSB                                           | 0.3mV    | 1                                      | 0  | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0                                          | 0  | 0  | 0  | 0  | 0  | 0           | 0  | 0 |

| <sup>1</sup> / <sub>2</sub> FS - <sup>3</sup> / <sub>4</sub> LSB                                           | 2.1mV    | 0                                      | 1  | 1           | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1                                          | 1  | 1  | 1  | 1  | 1  | 1           | 1  | 1 |

| 1 <sup>1</sup> / <sub>4</sub> LSB                                                                          | -1.2485V | 0                                      | 0  | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0                                          | 0  | 0  | 0  | 0  | 0  | 0           | 0  | 1 |

| Zero                                                                                                       | -1.25V   | 0                                      | 0  | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0                                          | 0  | 0  | 0  | 0  | 0  | 0           | 0  | 0 |

#### TABLE 2. A/D CODE TABLE

NOTE:

1. The voltages listed above represent the ideal transition of each output code shown as a function of the reference voltage.

#### Signal-to-Noise Ratio (SNR)

SNR is the measured RMS signal to RMS noise at a specified input and sampling frequency. The noise is the RMS sum of all of the spectral components except the fundamental and the first five harmonics.

#### Signal-to-Noise + Distortion Ratio (SINAD)

SINAD is the measured RMS signal to RMS sum of all other spectral components below the Nyquist frequency excluding DC.

#### Effective Number of Bits (ENOB)

The effective number of bits (ENOB) is calculated from the SINAD data by

ENOB = (SINAD - 1.76 + V<sub>CORR</sub>) / 6.02

where:  $V_{CORR} = 0.5 dB$

$\mathsf{V}_{\text{CORR}}$  adjusts the ENOB for the amount the input is below fullscale.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the RMS sum of the first 5 harmonic components to the RMS value of the fundamental input signal.

#### 2nd and 3rd Harmonic Distortion

This is the ratio of the RMS value of the applicable harmonic component to the RMS value of the fundamental input signal.

#### Intermodulation Distortion (IMD)

Nonlinearities in the signal path will tend to generate intermodulation products when two tones,  $f_1$  and  $f_2$ , are present on the inputs. The ratio of the measured signal to the distortion terms is calculated. The terms included in the calculation are  $(f_1 + f_2)$ ,  $(f_1 - f_2)$ ,  $(2f_1)$ ,  $(2f_2)$ ,  $(2f_1 + f_2)$ ,  $(2f_1 - f_2)$ ,  $(f_1 + 2f_2)$ ,  $(f_1 - 2f_2)$ . The ADC is tested with each tone 6dB below full scale.

#### Spurious Free Dynamic Range (SFDR)

SFDR is the ratio of the fundamental RMS amplitude to the RMS amplitude of the next largest spur or spectral component in the spectrum below  $f_S/2$ .

#### **Transient Response**

Transient response is measured by providing a full scale transition to the analog input of the ADC and measuring the number of cycles it takes for the output code to settle within 10-bit accuracy.

#### **Overvoltage Recovery**

Overvoltage Recovery is measured by providing a full scale transition to the analog input of the ADC which overdrives the input by 200mV, and measuring the number of cycles it takes for the output code to settle within 10-bit accuracy.

#### Full Power Input Bandwidth (FPBW)

Full power bandwidth is the frequency at which the amplitude of the digitally reconstructed output has decreased 3dB below the amplitude of the input sine wave. The input sine wave has a peak-to-peak amplitude equal to the reference voltage. The bandwidth given is measured at the specified sampling frequency.

# Video Definitions

Differential gain and Differential Phase are two commonly found video specifications for characterizing the distortion of a chrominance (3.58MHz) signal as it is offset through the input voltage range of an ADC.

#### Differential Gain (DG)

Differential Gain is the peak difference in chrominance amplitude (in percent) at two different DC levels.

#### Differential Phase (DP)

Differential Phase is the peak difference in chrominance phase (in degrees) at two different DC levels.

# **Timing Definitions**

Refer to Figure 1 and Figure 2 for these definitions.

#### Aperture Delay (t<sub>AD</sub>)

Aperture delay is the time delay between the external sample command (the falling edge of the clock) and the time at which the signal is actually sampled. This delay is due to internal clock path propagation delays.

### Aperture Jitter (t<sub>AJ</sub>)

This is the RMS variation in the aperture delay due to variation of internal clock path delays.

#### Data Hold Time (t<sub>H</sub>)

Data hold time is the time to where the previous data (N - 1) is no longer valid.

#### Data Output Delay Time (t<sub>OD</sub>)

Data output delay time is the time to where the new data (N) is valid.

#### Data Latency (t<sub>LAT</sub>)

After the analog sample is taken, the data on the bus is output at 7th cycle of the clock. This is due to the pipeline nature of the converter where the data has to ripple through the stages. This delay is specified as the data latency. After the data latency time, the data representing each succeeding sample is output at the following clock pulse. The digital data lags the analog input by 7 cycles.

#### **Power-Up Initialization**

This time is defined as the maximum number of clock cycles that are required to initialize the converter at power-up. The requirement arises from the need to initialize the dynamic circuits within the converter.

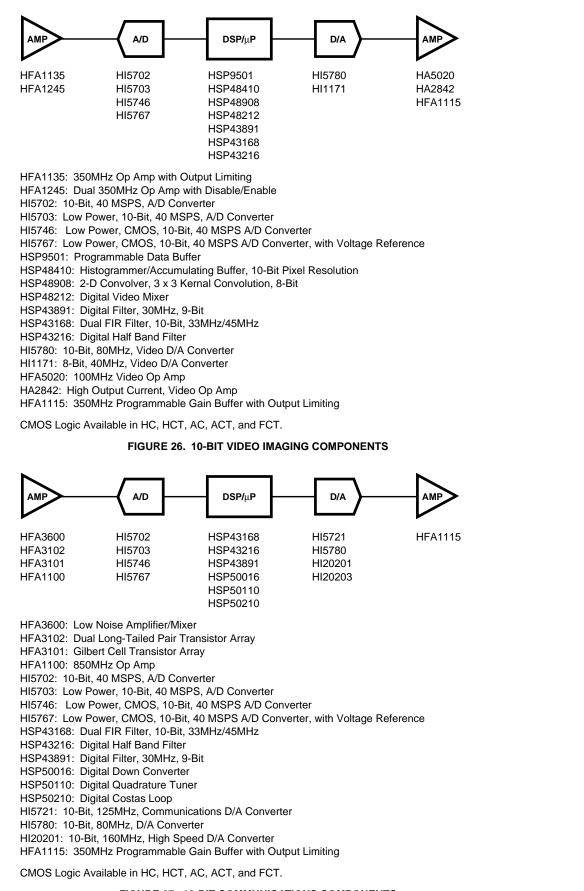

#### FIGURE 27. 10-BIT COMMUNICATIONS COMPONENTS

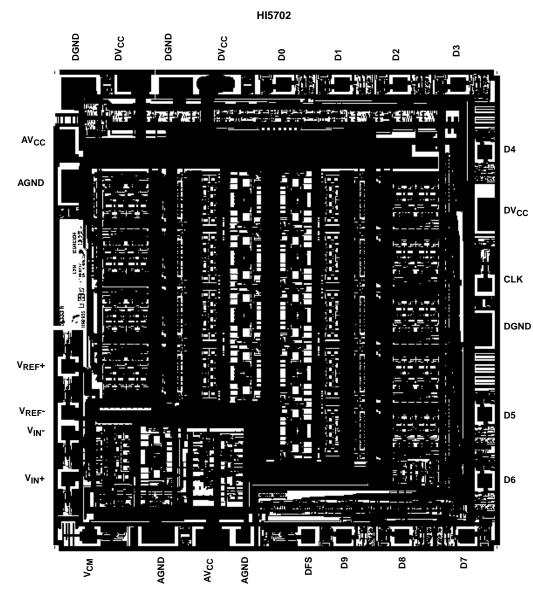

# **Die Characteristics**

## DIE DIMENSIONS:

159.4 mils x 175.2 mils x 19 mils  $\pm 1$  mil

# **METALLIZATION:**

Type: AlSiCu Thickness: 11kÅ ±1kÅ

# SUBSTRATE POTENTIAL (Powered Up):

GND (0.0V)

# PASSIVATION:

Type: Sandwich Passivation Nitride + Undoped Silicon Glass (USG) Thickness: Nitride 4.2kÅ, USG 8kÅ Total 12.2kÅ ±2kÅ

# Metallization Mask Layout

# WORST CASE CURRENT DENSITY:

1.6 x 10<sup>4</sup> A/cm<sup>2</sup>

# TRANSISTOR COUNT:

4514

# DIE DIMENSIONS:

Silver Filled Epoxy

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

# Sales Office Headquarters

#### NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (321) 724-7000 FAX: (321) 724-7240

### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### ASIA

Intersil (Taiwan) Ltd. Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029