# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## MITSUBISHI LINEAR IC'S M35500AFP/AGP

#### FLD CONTROLLER

#### **DESCRIPTION/FEATURES**

| High-breakdown-voltage output port 26                      |

|------------------------------------------------------------|

| Segment output 8 to 18                                     |

| • Digit output 7 to 10                                     |

| (Ports P0 to P7 are also used as ordinary output ports)    |

| Output breakdownVcc - 45 V                                 |

| <ul> <li>Output current –18 mA (DIGo to DIG17),</li> </ul> |

| -7 mA (SEG0 to SEG7)                                       |

| Pull-down resistorbuild-in                                 |

| Dimmer switch                                              |

| A-D converter                                              |

| Absolute accuracy ±3 LSB                                   |

| • Serial I/O                       | 4 (CS controller, external clock)          |

|------------------------------------|--------------------------------------------|

| Noise filter                       | build-in                                   |

| (in serial ir                      | put pin and clock pin, 2 MHz sampling)     |

| <ul> <li>FLD display</li> </ul>    | data input                                 |

| <ul> <li>A-D convers</li> </ul>    | ion data output                            |

| Command                            | input                                      |

| Package                            |                                            |

| Oscillating circuit C              | R oscillating cirucit (external capacitor) |

| <ul> <li>Oscillating fr</li> </ul> | equency4 MHz                               |

| • Power source voltage             | 4.0 to 5.5 V                               |

|                                    |                                            |

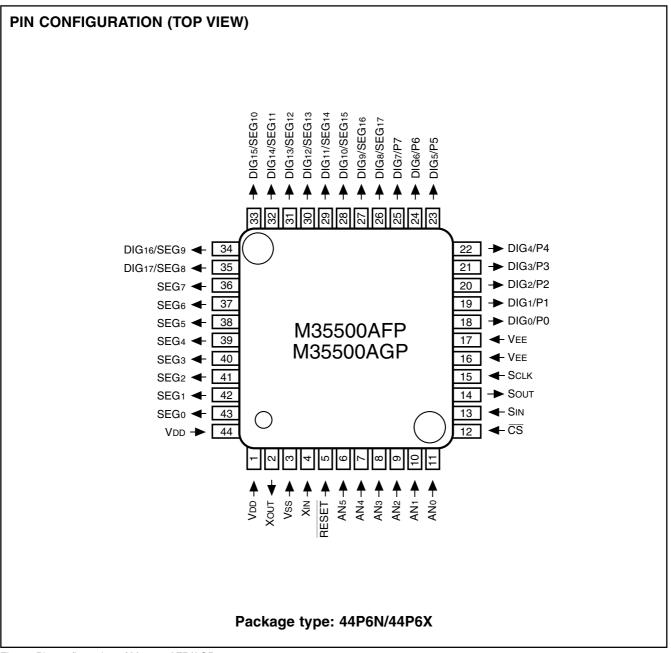

Fig. 1. Pin configuration of M35500AFP/AGP

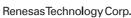

Fig. 2. Functional block diagram

### **FUNCTIONAL BLOCK**

**FLD CONTROLLER**

M35500AFP/AGP

MITSUBISHI LINEAR IC'S M35500AFP/AGP

FLD CONTROLLER

### **PIN DESCRIPTION**

| Pin                        | Name                      | Input                      | Output                  | Function                                                                                                                                         |

|----------------------------|---------------------------|----------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc, Vss                   | Power source              |                            |                         | Apply voltage of 5 V to Vcc, and 0 V to Vss.                                                                                                     |

| VEE                        | Pull-down<br>power source |                            |                         | Applies voltage supplied to pull-down resistors.                                                                                                 |

| XIN                        | Clock input               | Input                      |                         | CR oscillator pins for system clock.                                                                                                             |

| Хоит                       | Clock output              |                            | Output                  |                                                                                                                                                  |

| RESET                      | RESET input               | CMOS input                 |                         | <ul> <li>Reset input pin for active "L".</li> <li>Internal pull-up resistors connected between the RESET and VCC pins.</li> </ul>                |

| CS                         | Chip select               | CMOS input                 |                         | Serial transfer is possible by inputting "L" signal.                                                                                             |

| SCLK                       | Serial clock              | CMOS input<br>Noise filter |                         | <ul> <li>Clock for serial transfer is input.</li> <li>Read a clock twice with 2 MHz sampling clock and judge if it is a noise or not.</li> </ul> |

| Sout                       | Serial output             |                            | N-channel<br>open-drain | <ul><li>Serial data is output.</li><li>During reset it is in high-impedance state.</li></ul>                                                     |

| SIN                        | Serial input              | CMOS input<br>Noise filter |                         | <ul> <li>Serial data is input.</li> <li>Read a clock twice with 2 MHz sampling clock and judge if it is a noise or not.</li> </ul>               |

| DIG0/P0 –<br>DIG7/P7       | Digit/Port                |                            | P-channel<br>open-drain | <ul> <li>Pin for ordinary output or digit output.</li> <li>At reset this port is set to VEE level through a pull-down resistor.</li> </ul>       |

| DIG8/SEG17 –<br>DIG17/SEG8 | Digit/Segment             |                            | P-channel<br>open-drain | <ul> <li>Pin for digit output or segment output.</li> <li>At reset this port is set to VEE level through a pull-down resistor.</li> </ul>        |

| SEG0 – SEG7                | Segment                   |                            | P-channel<br>open-drain | <ul> <li>Pin for segment output.</li> <li>At reset this port is set to VEE level through a pull-down resistor.</li> </ul>                        |

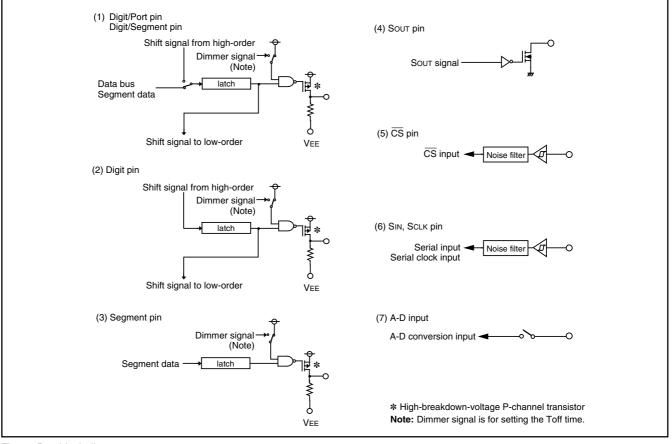

#### PORT BLOCK

Fig. 3. Port block diagram

FLD CONTROLLER

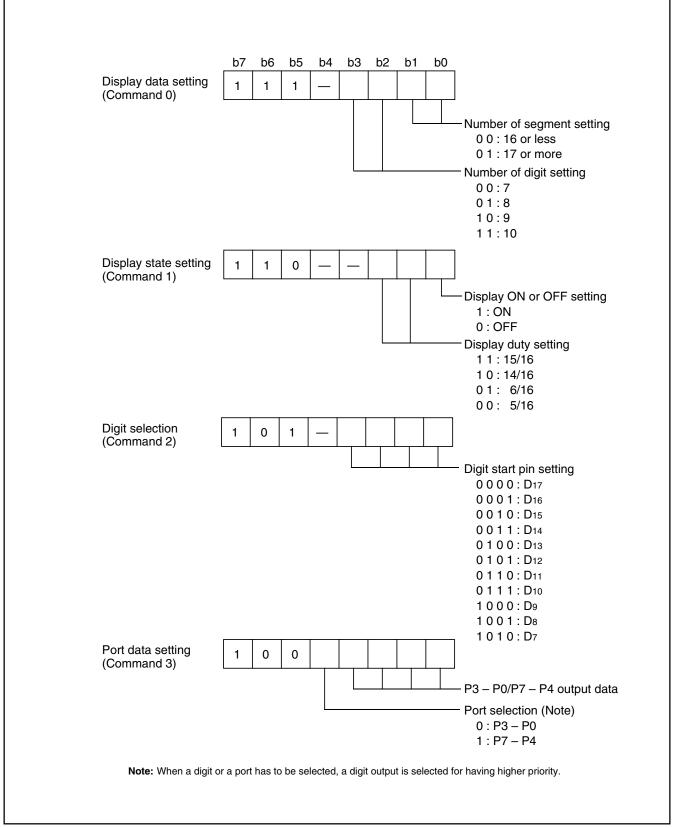

#### **COMMAND STYLE**

Fig. 4. Command style

## M35500AFP/AGP

FLD CONTROLLER

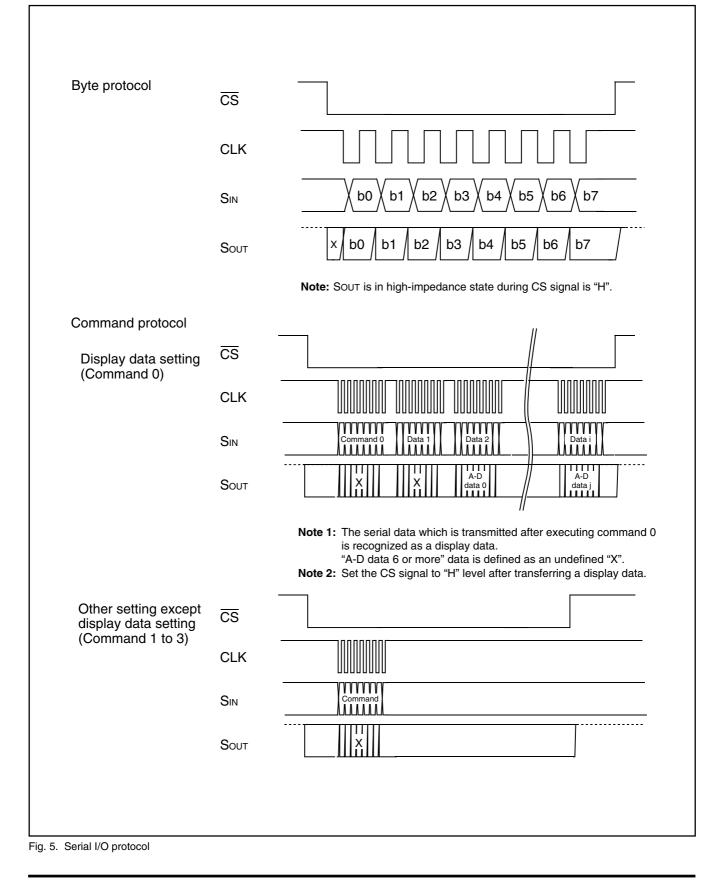

#### SERIAL I/O PROTOCOL

## M35500AFP/AGP

FLD CONTROLLER

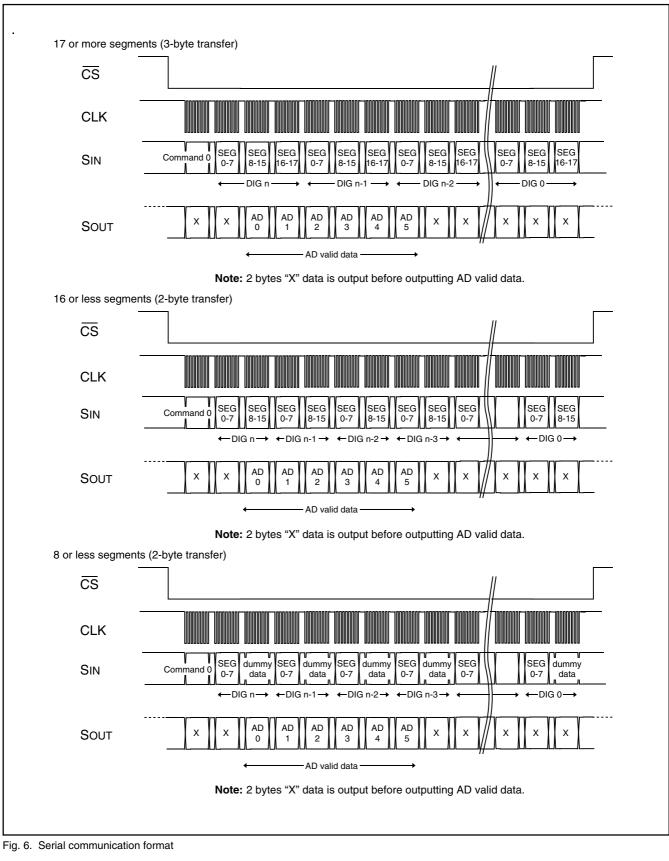

#### SERIAL COMMUNICATION FORMAT (DISPLAY DATA, A-D OUTPUT)

FLD CONTROLLER

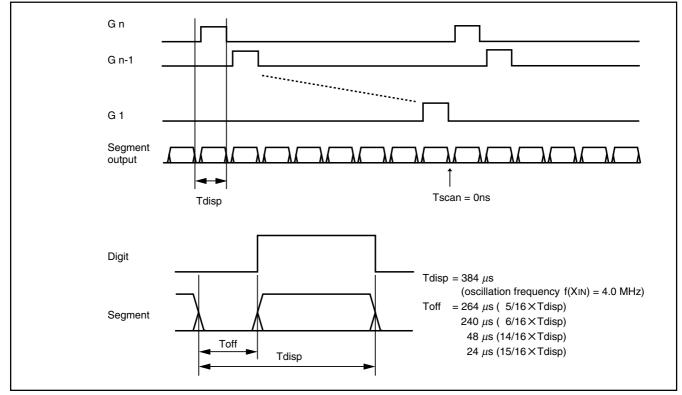

#### **FLD DISPLAY TIMING**

Fig. 7. FLD display timing diagram

#### SEGMENT/DIGIT SETTING EXAMPLE

|    | PORT | DIG   | SEG              | Grid : 7<br>Segment : 8 | Grid : 10<br>Segment : 8 | Grid : 10<br>Segment : 16 | Grid : 7<br>Segment : 18 |

|----|------|-------|------------------|-------------------------|--------------------------|---------------------------|--------------------------|

| 1  |      |       | SEG <sub>0</sub> | S1                      | S1                       | S1                        | S1                       |

| 2  |      |       | SEG1             | S2                      | S2                       | S2                        | S2                       |

| 3  |      |       | SEG2             | S3                      | S3                       | S3                        | S3                       |

| 4  |      |       | SEG3             | S4                      | S4                       | S4                        | S4                       |

| 5  |      |       | SEG4             | S5                      | S5                       | S5                        | S5                       |

| 6  |      |       | SEG5             | S6                      | S6                       | S6                        | S6                       |

| 7  |      |       | SEG6             | S7                      | S7                       | S7                        | S7                       |

| 8  |      |       | SEG7             | S8                      | S8                       | S8                        | S8                       |

| 9  |      | DIG17 | SEG8             | G7                      | G10                      | S9                        | S9                       |

| 10 |      | DIG16 | SEG9             | G6                      | G9                       | S10                       | S10                      |

| 11 |      | DIG15 | SEG10            | G5                      | G8                       | S11                       | S11                      |

| 12 |      | DIG14 | SEG11            | G4                      | G7                       | S12                       | S12                      |

| 13 |      | DIG13 | SEG12            | G3                      | G6                       | S13                       | S13                      |

| 14 |      | DIG12 | SEG13            | G2                      | G5                       | S14                       | S14                      |

| 15 |      | DIG11 | SEG14            | G1                      | G4                       | S15                       | S15                      |

| 16 |      | DIG10 | SEG15            |                         | G3                       | S16                       | S16                      |

| 17 |      | DIG9  | SEG16            |                         | G2                       | G10                       | S17                      |

| 18 |      | DIG8  | SEG17            |                         | G1                       | G9                        | S18                      |

| 19 | P7   | DIG7  |                  |                         |                          | G8                        | G7                       |

| 20 | P6   | DIG6  |                  |                         |                          | G7                        | G6                       |

| 21 | P5   | DIG5  |                  |                         |                          | G6                        | G5                       |

| 22 | P4   | DIG4  |                  |                         |                          | G5                        | G4                       |

| 23 | P3   | DIG3  |                  |                         |                          | G4                        | G3                       |

| 24 | P2   | DIG2  |                  |                         |                          | G3                        | G2                       |

| 25 | P1   | DIG1  |                  |                         |                          | G2                        | G1                       |

| 26 | P0   | DIGo  |                  |                         |                          | G1                        |                          |

Fig. 8. Segment/Digit setting example

## M35500AFP/AGP

| ADDRESS      | b7        |           |           |           |           |           |           | b0        | 1 |        |

|--------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|---|--------|

| 0916         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 0A16         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit0 |

| 0B16         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | ) |        |

| 0D16         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 0E16         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit1 |

| 0F16         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 1116         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 1216         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit2 |

| 1316         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 1516         |           |           | -         |           | -         |           | SEG<br>17 | SEG<br>16 | ) |        |

| 1616         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit3 |

| 1716         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 1916         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| <b>1</b> A16 | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit4 |

| 1B16         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 1D16         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 1E16         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit5 |

| 1F16         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 2116         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 2216         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit6 |

| 2316         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 2516         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 2616         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit7 |

| 2716         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 2916         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 2A16         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  |   | Digit8 |

| 2B16         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

| 2D16         |           |           |           |           |           |           | SEG<br>17 | SEG<br>16 | ) |        |

| 2E16         | SEG<br>15 | SEG<br>14 | SEG<br>13 | SEG<br>12 | SEG<br>11 | SEG<br>10 | SEG<br>9  | SEG<br>8  | } | Digit9 |

| 2F16         | SEG<br>7  | SEG<br>6  | SEG<br>5  | SEG<br>4  | SEG<br>3  | SEG<br>2  | SEG<br>1  | SEG<br>0  | J |        |

|              |           |           |           |           |           |           |           |           |   |        |

Fig. 9. Bit allocation for display RAM

M35500AFP/AGP

FLD CONTROLLER

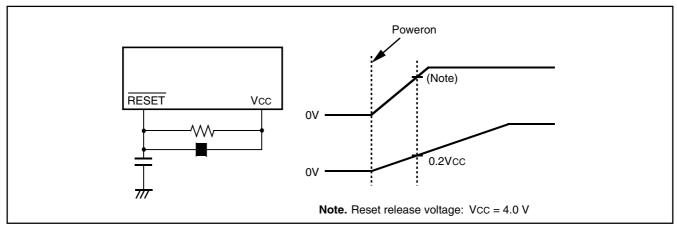

#### **RESET CIRCUIT**

To reset the controller, the  $\overrightarrow{\text{RESET}}$  pin should be held at a "L" level for 2  $\mu$ s or more. Then the  $\overrightarrow{\text{RESET}}$  pin is returned to an "H" level (the power source voltage should be between 4.0 V and 5.5 V, and XIN oscillation is stable), reset is released.

Make sure that the reset input voltage is 0.5 V or less for 4.0 V of Vcc.

Fig. 10. Reset circuit example

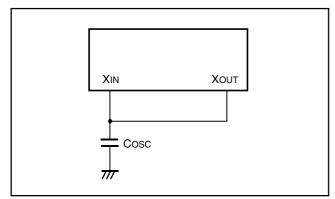

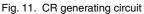

#### **CLOCK GENERATING CIRCUIT**

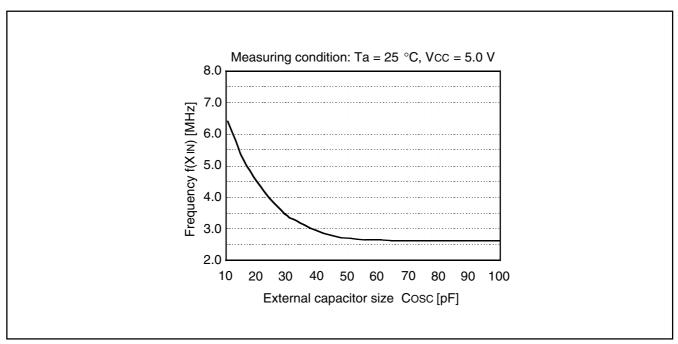

Oscillating circuit is built up by connecting pins XIN and XOUT as short as possible and connecting a capacitor between pins XIN (XOUT) and Vss.

When supplying a clock externally, input it to XIN pin and leave XOUT pin open.

#### HANDLING OF UNUSED PINS

Handle unused pins as the follow.

Table. 2. Handling of unused pins

Pin

Handling

Segment

Open

Digit

Open

Analog input

Connect to Vcc or Vss through a resistor.

FLD CONTROLLER

**ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                      | Conditions                                                                                                                                                                                                                 | Ratings           | Unit |

|--------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|

| Vcc    | Power source voltage           | All voltage are based on Vss.                                                                                                                                                                                              | -0.3 to 7.0       | v    |

| VEE    | Pull-down power source voltage | Output transistors are cut off.                                                                                                                                                                                            | Vcc-45 to Vcc+0.3 | V    |

| VI     | Input voltage AN0 – AN5        |                                                                                                                                                                                                                            | -0.3 to Vcc+0.3   | V    |

| VI     | Input voltage CS, SIN, SCLK    |                                                                                                                                                                                                                            | -0.3 to Vcc+0.3   | V    |

| VI     | Input voltage RESET            |                                                                                                                                                                                                                            | -0.3 to Vcc+0.3   | V    |

| Vo     | Output voltage DIG0 - DIG17    |                                                                                                                                                                                                                            | Vcc-45 to Vcc+0.3 |      |

|        | SEG0 – SEG17                   | <ul> <li>All voltage are based on VSS.</li> <li>Output transistors are cut off.</li> <li>A waveform: 450 μs or more frequency and 30 μs or less pulse width.</li> <li>Connect only capacitor load (CL = 200pF).</li> </ul> | Vcc-50 to Vcc+0.3 | v    |

| Vo     | Output voltage Sout            | All voltage are based on Vss.     Output transistors are cut off.                                                                                                                                                          | -0.3 to Vcc+0.3   | V    |

| Pd     | Power dissipation              | Ta = 25 °C                                                                                                                                                                                                                 | 600               | mW   |

| Topr   | Operating temperature          |                                                                                                                                                                                                                            | -20 to 85         | °C   |

| Tstg   | Storage temperature            |                                                                                                                                                                                                                            | -40 to 125        | °C   |

#### RECOMMENDED OPERATING CONDITIONS (Vcc = 4.0 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

| O: male al | Deventeday                      |         | Unit |         |      |

|------------|---------------------------------|---------|------|---------|------|

| Symbol     | Parameter                       | Min.    | Тур. | Max.    | Unit |

| Vcc        | Power source voltage            | 4.0     | 5.0  | 5.5     | V    |

| Vss        | Power source voltage            |         | 0    |         | V    |

| VEE        | Pull-down power source voltage  | Vcc-38  |      | Vcc     | V    |

| VIH        | "H" input voltage CS, SIN, SCLK | 0.75Vcc |      | Vcc     | V    |

| VIH        | "H" input voltage RESET         | 0.8Vcc  |      | Vcc     | V    |

| VIL        | "L" input voltage CS, SIN, SCLK | 0       |      | 0.25Vcc | V    |

| VIL        | "L" input voltage RESET         | 0       |      | 0.2Vcc  | V    |

#### RECOMMENDED OPERATING CONDITIONS (Vcc = 4.0 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

| Ormaliael          |                                  | Parameter                  |          |      | Limits |      | 11  |

|--------------------|----------------------------------|----------------------------|----------|------|--------|------|-----|

| Symbol             |                                  | Min.                       | Тур.     | Max. | Unit   |      |     |

| $\Sigma$ IOH(peak) | "H" total peak output current    | DIG0 – DIG17, SEG0 – SEG17 | (Note 1) |      |        | -240 | mA  |

| ΣIOH(avg)          | "H" total peak output current    | DIG0 – DIG17, SEG0 – SEG17 |          |      |        | -120 | mA  |

| IOH(peak)          | "H" peak output current          | DIG0 – DIG17               | (Note 2) |      |        | -40  | mA  |

| IOH(peak)          | "H" peak output current          | SEG0 – SEG7                | (Note 2) |      |        | -20  | mA  |

| IOL(peak)          | "L" peak output current          | Sout                       |          |      |        | 10   | mA  |

| IOH(avg)           | "H" peak output current          | DIG0 – DIG17               | (Note 3) |      |        | -18  | mA  |

| IOH(avg)           | "H" peak output current          | SEG0 – SEG7                | (Note 3) |      |        | -7   | mA  |

| IOL(avg)           | "L" peak output current          | Sout                       |          |      |        | 5.0  | mA  |

| f(XIN)             | Main clock input oscillation fre | quency                     | (Note 4) |      | 4.0    | 5.2  | MHz |

| f(SCLK)            | Serial I/O external clock frequ  | ency                       |          |      | 250    |      | kHz |

Notes 1: The total output current is the sum of all the currents flowing through all the applicable ports. The total average current is an average value measured over 100 ms. The total peak current is the peak value of all the currents.

2: The peak output current is the peak current flowing in each port.

3: The average output current is an average value measured over 100 ms.

4: When the oscillation frequency has a 50 % duty cycle.

#### FLD CONTROLLER

| 0 miles   |                     |               | To share a fifth         |         | Limits |      | 1.1  |

|-----------|---------------------|---------------|--------------------------|---------|--------|------|------|

| Symbol    | Para                | meter         | Test conditions          | Min.    | Тур.   | Max. | Unit |

| Vон       | "H" output voltage  | DIG output    | Iон = –18 mA             | Vcc-2.0 |        |      | V    |

|           |                     | SEG output    | Iон = -7 mA              | Vcc-2.0 |        |      | V    |

| Vol       | "L" output voltage  | SOUT          | IOL = 5 mA               |         |        | 2.0  | V    |

| Vt+ — Vt- | Hysteresis          | SIN, SCLK, CS | Vcc = 5.0 V              |         | 0.5    |      | V    |

|           |                     | RESET, XIN    |                          |         | 0.5    |      | V    |

| Іін       | "H" input voltage   | SIN, SCLK, CS | VI = VCC                 |         |        | 5.0  | μA   |

|           |                     | RESET         |                          |         |        | 5.0  | μA   |

|           |                     | XIN           |                          |         | 4.0    |      | μA   |

| lı∟       | "L" input voltage   | SIN, SCLK, CS | VI = VSS                 |         |        | -5.0 | μA   |

|           |                     | RESET         |                          |         | -150   |      | μA   |

|           |                     | XIN           |                          |         | -4.0   |      | μA   |

| ILOAD     | Output load current | DIG0 – DIG17  | VEE = VCC-36 V           |         |        |      |      |

|           |                     | SEG0 – SEG17  | VOL = VCC                | 250     | 500    | 750  | μA   |

|           |                     |               | Output transistors "off" |         |        |      |      |

| ILEAK     | Output leakage      | DIG0 – DIG17  | VEE = VCC-38 V           |         |        |      |      |

|           | current             | SEG0 – SEG17  | VOL = VCC-38 V           |         |        | -10  | μA   |

|           |                     |               | Output transistors "off" |         |        |      |      |

#### ELECTRICAL CHARACTERISTICS (Vcc = 4.0 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

#### ELECTRICAL CHARACTERISTICS (Vcc = 4.0 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

| O: make al | Parameter            | To at a set dition of                                                                 |      | Linit |      |      |

|------------|----------------------|---------------------------------------------------------------------------------------|------|-------|------|------|

| Symbol     |                      | Test conditions                                                                       | Min. | Тур.  | Max. | Unit |

| VRAM       | RAM hold voltage     | When clock is stopped                                                                 | 2.0  |       | 5.5  | V    |

| ICC        | Power source current | Vcc = 5 V, f(XIN) = 4.2 MHz<br>Output transistors "off" at<br>A-D converter operating |      | 0.5   | 1.0  | mA   |

#### A-D CONVERTER CHARACTERISTICS (Vcc = 4.0 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

| Currents al | Devemeter                                        | To at a smallting a |      | 1.1  |      |         |

|-------------|--------------------------------------------------|---------------------|------|------|------|---------|

| Symbol      | Parameter                                        | Test conditions     | Min. | Тур. | Max. | Unit    |

|             | Resolution                                       |                     |      |      | 8    | Bits    |

| _           | Absolute accuracy (excluding quantization error) | Vcc = 5.12 V        |      |      | ±3   | LSB     |

| Tconv       | Conversion time                                  |                     |      |      | 100  | tc(XIN) |

| VIA         | Analog input voltage                             |                     | 0    |      | Vcc  | V       |

| lia         | Analog port input current                        |                     |      | 0.5  | 5.0  | μA      |

| RLADDER     | Ladder resistor                                  |                     |      | 35   |      | kΩ      |

## MITSUBISHI LINEAR IC'S M35500AFP/AGP

FLD CONTROLLER

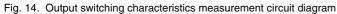

#### TIMING REQUIREMENTS (Vcc = 4.0 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

| Or mark all        | Descurator                                |            | Limits |      | 11   |

|--------------------|-------------------------------------------|------------|--------|------|------|

| Symbol             | Parameter                                 | Min.       | Тур.   | Max. | Unit |

| tw(RESET)          | Reset input "L" pulse width               | 2          |        |      | μs   |

| tc(XIN)            | Main clock input cycle time (XIN input)   | 238        |        |      | ns   |

| twH(XIN)           | Main clock input "H" pulse width          | 60         |        |      | ns   |

| twL(XIN)           | Main clock input "L" pulse width          | 60         |        |      | ns   |

| tc(SCLK)           | Serial clock input cycle time (Note)      | 4          |        |      | CLKs |

| twH(SCLK)          | Serial clock input "H" pulse width (Note) | 2          |        |      | CLKs |

| twL(SCLK)          | Serial clock input "L" pulse width (Note) | 2          |        |      | CLKs |

| tsu(SIN-SCLK)      | Serial input setup time (Note)            | 2          |        |      | CLKs |

| th(SCLK-SIN)       | Serial input hold time (Note)             | 3          |        |      | CLKs |

| tsu(\overline{CS}) | Serial input setup time                   | 50 tc(XIN) |        |      | ns   |

| th(CS)             | Serial input hold time                    | 50 tc(XIN) |        |      | ns   |

| tre(SCLK)          | Serial clock interval time                | 50 tc(XIN) |        |      | ns   |

Note: The unit means a number of noise filter sampling clock  $(2 \times tc(XIN))$ .

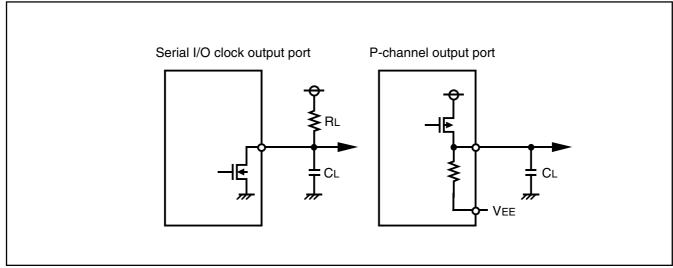

#### SWITCHING CHARACTERISTICS (Vcc = 4.0 to 5.5 V, Ta = -20 to 85 °C, unless otherwise noted)

| Symbol        | Parameter                                                         | Test conditions              | Limits |      |      | 11   |

|---------------|-------------------------------------------------------------------|------------------------------|--------|------|------|------|

|               |                                                                   |                              | Min.   | Тур. | Max. | Unit |

| td(SCLK-SOUT) | Serial I/O output delay time (Note 1)                             |                              |        |      | 3    | CLKs |

| tv(SCLK-SOUT) | Serial I/O output valid time                                      |                              | 0      |      |      | ns   |

| tr(Pch)       | High-breakdown-voltage P-channel<br>open-drain output rising time | CL = 100pF<br>VEE = VCC–36 V |        | 1.8  |      | μs   |

| Cosc          | External capacitor size (Note 2)                                  |                              |        | 22   |      | pF   |

Note 1: The unit means a number of noise filter sampling clock (2  $\times$  tc(XIN)).

2: An external capacitor size varies with a mounted condition.

Fig. 13. Standard characteristic example of f(XIN)-COSC

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change.

MITSUBISHI LINEAR IC's

## M35500AFP/AGP

FLD CONTROLLER

FLD CONTROLLER

PRELIMINARY Notice: This is not a final specification. Some parametric limits are subject to change.

### **MITSUBISHI LINEAR IC's** M35500AFP/AGP

**FLD CONTROLLER**

#### Keep safety first in your circuit designs!

Misubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- .

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party. Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts or circuit application examples contained in these materials. All information contained in these materials, and are subject to change by Mitsubishi

- The information contained in these materials, including product data, diagrams and charts, physical information on products are the united in publication on these materials, and are subject to charge by Mitsubish Electric Corporation or including by Control to the end of the contained in the end of publication of these materials, and are subject to charge by Mitsubish Electric Corporation without notice due to product information before purchasing a product listed herein. Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use. The prior written approval of Mitsubishi Electric Corporation of Mitsubishi Electric Corporation of Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use. The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the nervormed determined in the subject to the materials.

- - approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Р se contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.

© 1997 MITSUBISHI ELECTRIC CORP. New publication, effective Nov. 1997. Specifications subject to change without notice.

## **REVISION DESCRIPTION LIST**

## M35500AFP/AGP DATA SHEET

| Rev.<br>No. | Revision Description | Rev.<br>date |

|-------------|----------------------|--------------|

| 1.0         | First Edition        | 971115       |

| 1.0         |                      | 971113       |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |

|             |                      |              |