# 17V Input, 2A, ACOT<sup>®</sup> Buck Converter with Both FETs OC Protection

# **General Description**

The RT6252A/B is a simple, easy-to-use, 2A synchronous step-down DC-DC converter with an input supply voltage range of 4.5V to 17V. The device possesses an accurate reference voltage and integrates low R<sub>DS(ON)</sub> power MOSFETs to achieve high efficiency.

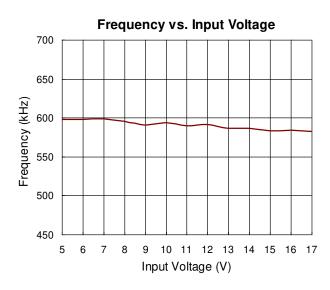

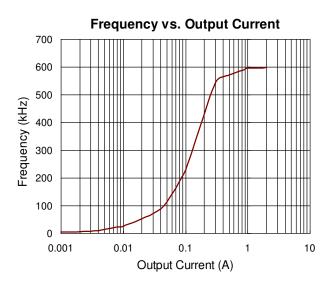

The RT6252A/B adopts Advanced Constant On-Time (ACOT®) control architecture to provide an ultrafast transient response with few external components and to operate in nearly constant switching frequency over the line, load, and output voltage range. The RT6252A operates in automatic PSM that maintains high efficiency during light load operation. The RT6252B operates in Forced PWM that helps meet tight voltage regulation accuracy requirements.

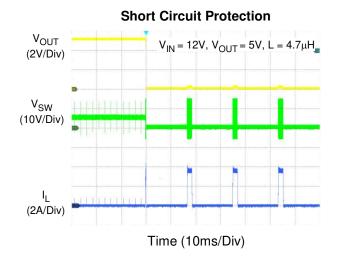

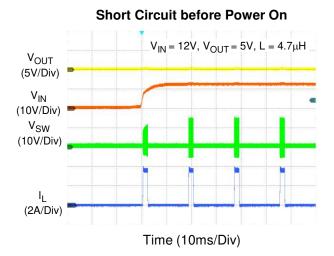

The RT6252A/B senses both FETs current for a robust over-current protection (OCP). The device features cycle-by-cycle current limit protection to prevent the device from the catastrophic damage in output short circuit, over-current or inductor saturation conditions. A built-in soft-start function prevents inrush current during start-up. The device also includes input under-voltage lockout, output under-voltage protection, and over-temperature protection (OTP) to provide safe and smooth operation in all operating conditions.

#### **Features**

- 2A Converter Integrated 140m $\Omega$  and 84m $\Omega$  FETs

- Input Supply Voltage Range: 4.5V to 17V

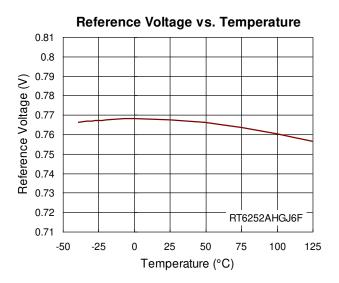

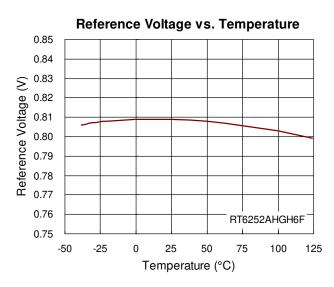

- Output Voltage Range: 0.765V to 7V

- Advanced Constant On-Time (ACOT®) Control

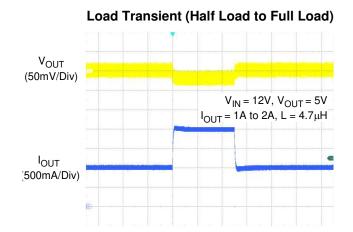

- **▶** Ultrafast Transient Response

- ► Optimized for Low-ESR Ceramic Output Capacitors

- High Accuracy Feedback Reference Voltage : Typ.

+ 1%

- Optional for Operation Modes :

- ► Automatically Power Saving Mode (PSM) (RT6252A)

- ► Forced PWM Mode (RT6252B)

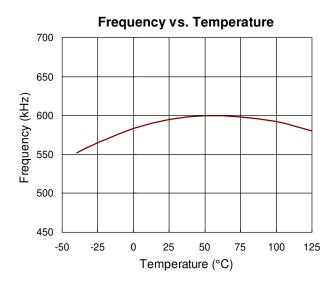

- Fixed Switching Frequency: 580kHz

- Enable Control and Internally Fixed Soft-Start

- Safe Start-Up from Pre-biased Output

- Input Under-Voltage Lockout (UVLO)

- Output Under-Voltage Protection (UVP) with Hiccup Mode

- High- /Low-side MOSFET OCP and OTP Function

- RoHS Compliant and Halogen Free

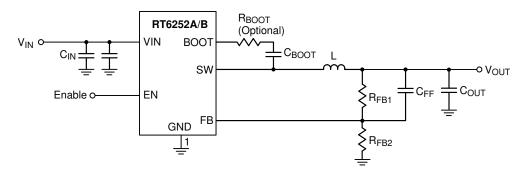

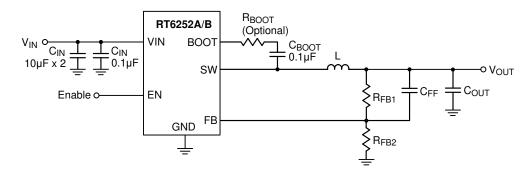

# **Simplified Application Circuit**

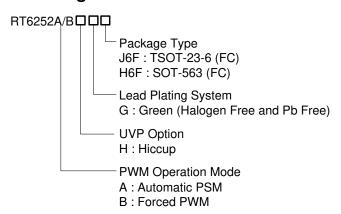

# **Ordering Information**

#### Note:

#### Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

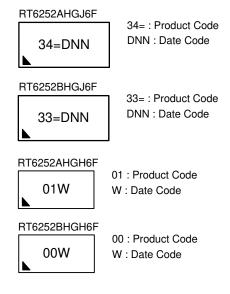

# **Marking Information**

# **Applications**

- Set-Top Boxes

- LCD TVs

- Home Networking Devices

- Surveillance

- General Purpose

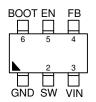

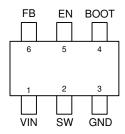

# **Pin Configuration**

(TOP VIEW)

TSOT-23-6 (FC)

SOT-563 (FC)

# **Functional Pin Description**

| Pin          | No.          | Din Nama | Din Function                                                                                                                                                                                                                                                         |

|--------------|--------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSOT23-6(FC) | SOT-563 (FC) | Pin Name | Pin Function                                                                                                                                                                                                                                                         |

| 1            | 3            | GND      | Power ground.                                                                                                                                                                                                                                                        |

| 2            | 2            | SW       | Switch node between the internal switch and the synchronous rectifier. Connect this pin to the inductor and bootstrap capacitor.                                                                                                                                     |

| 3            | 1            | VIN      | Power input. The input voltage range is from 4.5V to 17V. Connect input bypass capacitors directly to this pin and GND pins. The MLCC with capacitance higher than $20\mu F$ is recommended.                                                                         |

| 4            | 6            | FB       | Feedback voltage input. Connect this pin to the midpoint of the external feedback resistive divider to set the output voltage of the converter to the desired regulation level. The device regulates the FB voltage at feedback reference voltage, typically 0.765V. |

| 5            | 5            | EN       | Enable control input. Connect this pin to logic high enables the device and connect this pin to GND disables the device.                                                                                                                                             |

| 6            | 4            | воот     | Bootstrap capacitor connection node to supply the high-side gate driver. Connect a $0.1\mu F$ ceramic capacitor between this pin and the SW pin.                                                                                                                     |

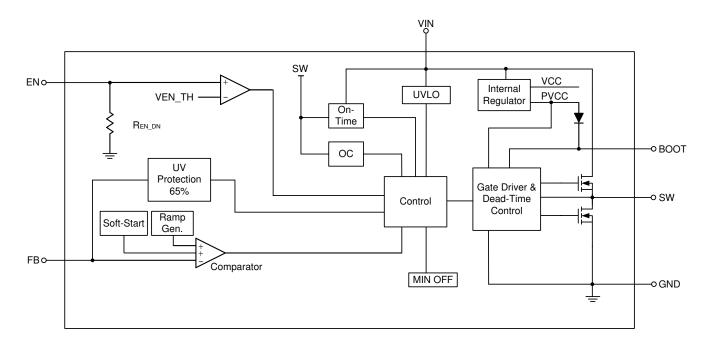

# **Functional Block Diagram**

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# Operation

The RT6252A/B is a high-efficiency, synchronous step-down DC-DC converter that can deliver up to 2A output current from a 4.5V to 17V input supply.

# Advanced Constant On-Time Control and PWM Operation

The RT6252A/B adopts ACOT® control for its ultrafast transient response, low external component counts and stable with low ESR MLCC output capacitors. When the feedback voltage falls below the feedback reference voltage, the minimum off-time one-shot (200ns, typ.) has timed out and the inductor current is below the current limit threshold, then the internal on-time one-shot circuitry is triggered and the high-side switch is turn-on. Since the minimum off-time is short, the device exhibits ultrafast transient response and enables the use of smaller output capacitance.

The on-time is inversely proportional to input voltage and directly proportional to output voltage to achieve pseudo-fixed frequency over the input voltage range. After the on-time one-shot timer expired, the high-side switch is turned off and the low-side switch is turned on until the on-time one-shot is triggered again. To achieve stable operation with low-ESR ceramic output capacitors, an internal ramp signal is added to the feedback reference voltage to simulate the output voltage ripple.

# Power Saving Mode (RT6252A Only)

The RT6252A automatically enters power saving mode (PSM) at light load to maintain high efficiency. As the load current decreases, the inductor current ripple valley eventually touches the zero current, which is the boundary between continuous conduction and discontinuous conduction modes. The low-side switch is turned off when the zero inductor current is detected. In this case, the output capacitor is only discharged by load current so that the switching frequency decreases. As the result, the light-load efficiency can be enhanced due to lower switching loss.

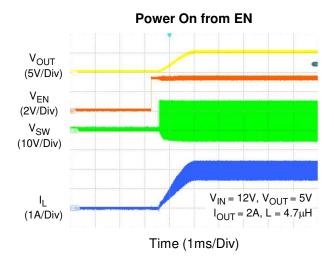

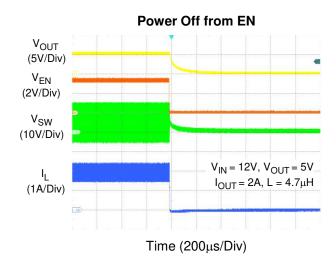

#### **Enable Control**

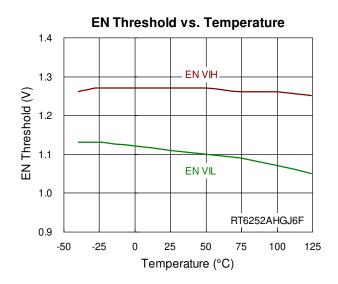

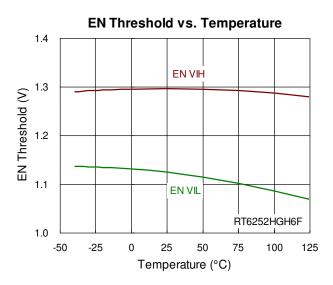

The RT6252A/B provides an EN pin, as an external chip enable control, to enable or disable the device. If

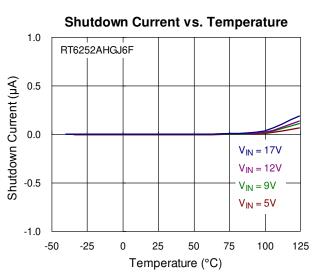

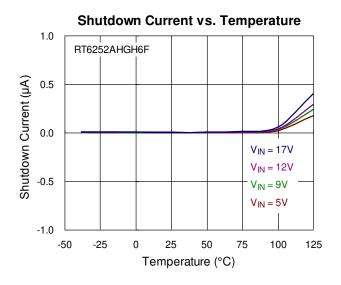

VEN is held below a logic-low threshold voltage (VEN\_L) of the enable input (EN), the converter will disable output voltage, that is, the converter is disabled and switching is inhibited even if the VIN voltage is above VIN under-voltage lockout threshold (VUVLO). During shutdown mode, the supply current can be reduced to ISHDN (10 $\mu$ A or below). If the EN voltage rises above the logic-high threshold voltage (VEN\_H) while the VIN voltage is higher than UVLO threshold, the device will be turned on, that is, switching being enabled and soft-start sequence being initiated. An internal resistor REN\_DN from EN to GND allows EN float to shutdown the chip.

# Soft-Start (SS)

The RT6252A/B provides an internal soft-start feature for inrush control, and the output voltage starts to rise in 0.3ms from EN rising edge. At power up, the internal capacitor is charged by an internal current source to generate a soft-start ramp voltage as a reference voltage to the PWM comparator. The device will initiate switching and the output voltage will smoothly ramp up to its targeted regulation voltage only after this ramp voltage is greater than the feedback voltage V<sub>FB</sub> to ensure the converter has a smooth start-up from pre-biased output.

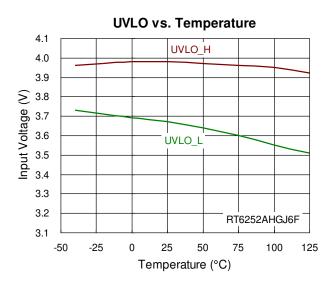

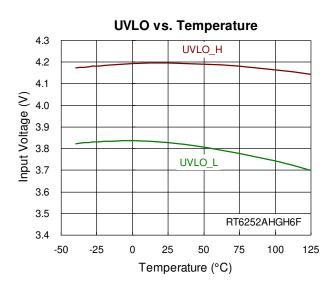

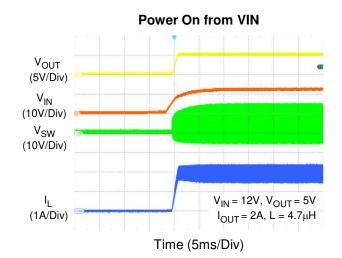

## Input Under-Voltage Lockout

In addition to the EN pin, the RT6252A/B also provides enable control through the VIN pin. It features an under-voltage lockout (UVLO) function that monitors the internal linear regulator (VCC). If  $V_{EN}$  rises above  $V_{EN\_H}$  first, switching will still be inhibited until the VIN voltage rises above  $V_{UVLO}$ . It is to ensure that the internal regulator is ready so that operation with not-fully-enhanced internal MOSFET switches can be

prevented. After the device is powered up, if the input voltage VIN goes below the UVLO falling threshold voltage ( $V_{UVLO} - \Delta V_{UVLO}$ ), this switching will be inhibited; if VIN rises above the UVLO rising threshold ( $V_{UVLO}$ ), the device will resume normal operation with a complete soft-start.

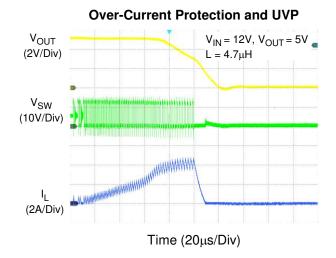

## **Output Under-Voltage Protection and Hiccup Mode**

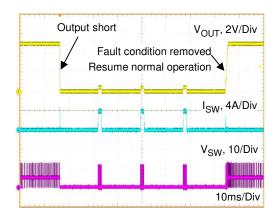

The RT6252A/B includes output under-voltage protection (UVP) against over-load or short-circuited condition by constantly monitoring the feedback voltage VFB. If VFB drops below the under-voltage protection trip threshold (typically 65% of the internal feedback reference voltage), the UV comparator will go high to turn off both the internal high-side and low-side MOSFET switches.

If the output under-voltage condition continues for a period of time, the RT6252A/B will enter output under-voltage protection with hiccup mode. During hiccup mode, the IC will shut down for thiccup\_off (15ms), and then attempt to recover automatically for thiccup\_on (1.8ms). Upon completion of the soft-start sequence, if the fault condition is removed, the converter will resume normal operation; otherwise, such cycle for auto-recovery will be repeated until the fault condition is cleared. The hiccup mode allows the circuit to operate safely with low input current and power dissipation, and then the converter resumes normal operation as soon as the over-load or short-circuit condition is removed.

#### **The Over-Current Protection**

The RT6252A/B features cycle-by-cycle current-limit protection on both the high-side and low-side

MOSFETs and prevents the device from the catastrophic damage in output short-circuit, over-current or inductor saturation conditions.

The high-side MOSFET over-current protection is achieved by an internal current comparator that monitors the current in the high-side MOSFET during each on-time. The switch current is compared with the high-side switch peak-current limit (I<sub>LIM\_H</sub>) after a certain amount of delay when the high-side switch being turned on each cycle. If an over-current condition occurs, the converter will immediately turns off the high-side switch and turns on the low-side switch to prevent the inductor current exceeding the high-side current limit.

The low-side MOSFET over-current protection is achieved by measuring the inductor current through the synchronous rectifier (low-side switch) during the low-side on-time. Once the current rises above the low-side switch valley current limit (I<sub>LIM\_L</sub>), the on-time one-shot will be inhibited until the inductor current ramps down to the current limit level (I<sub>LIM\_L</sub>), that is, another on-time can only be triggered when the inductor current goes below the low-side current limit. If the output load current exceeds the available inductor current (clamped by the low-side current limit), the output capacitor needs to supply the extra current such that the output voltage will begin to drop. If it drops below the output under-voltage protection trip threshold, the IC will stop switching to avoid excessive heat.

#### **Negative Over-Current Limit**

The RT6252B is the part which is forced to PWM and allows negative current operation.

In case of PWM operation, high negative current may be generated as an external power source is tied to output terminal unexpectedly. As the risk described above, the internal circuit monitors negative current in each on-time interval of low-side MOSFET and compares it with NOC threshold.

Once the negative current exceeds the NOC threshold, the low-side MOSFET is turned off immediately, and then the high-side MOSFET will be turned on to discharge the energy of output inductor. This behavior can keep the valley of negative current at NOC threshold to protect low-side MOSFET. However, the

negative current can't be limited at NOC threshold anymore since minimum off-time is reached.

#### **Thermal Shutdown**

The RT6252A/B includes an over-temperature protection (OTP) circuitry to prevent overheating due to excessive power dissipation. The OTP will shut down switching operation when junction temperature exceeds a thermal shutdown threshold (TsD). Once the junction temperature cools down by a thermal shutdown hysteresis ( $\Delta T_{SD}$ ), the IC will resume normal operation with a complete soft-start.

Note that the over-temperature protection is intended to protect the device during momentary overload conditions. The protection is activated outside of the absolute maximum range of operation as a secondary fail-safe and therefore should not be relied upon operationally. Continuous operation above the specified absolute maximum operating junction temperature may impair the reliability of the device or permanently damage the device.

# **Absolute Maximum Ratings** (Note 1)

| Supply Input Voltage, VIN                         | -0.3V to 20V   |

|---------------------------------------------------|----------------|

| Enable Voltage, EN                                | -0.3V to 20V   |

| Switch Voltage, SW                                | -0.3V to 20.3V |

| < 100ns                                           | -5V to 25V     |

| BOOT Voltage , BOOT                               | - 0.3V to 26V  |

| • BOOT to SW, V <sub>BOOT</sub> – V <sub>SW</sub> | -0.3V to 6V    |

| Feedback Voltage, FB                              | -0.3V to 6V    |

| Lead Temperature (Soldering, 10 sec.)             | 260°C          |

| Junction Temperature                              | 150°C          |

| Storage Temperature Range                         | –65°C to 150°C |

| ESD Ratings (Note 2)                              |                |

| ESD Susceptibility                                |                |

| HBM (Human Body Model)                            | 2kV            |

# **Recommended Operating Conditions** (Note 3)

• Supply Input Voltage ----- 4.5V to 17V

• Junction Temperature Range ----- -40°C to 125°C

# **Thermal Information** (Note 4 and Note 5)

|                     | Thermal Parameter                                       | TSOT-23-6 (FC) | SOT-563 (FC) | Unit |

|---------------------|---------------------------------------------------------|----------------|--------------|------|

| $\theta$ JA         | Junction-to-ambient thermal resistance (JEDEC standard) | 88.7           | 104.3        | °C/W |

| $\theta$ JC(Top)    | Junction-to-case (top) thermal resistance               | 76.9           | 62.1         | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 6              | 8.4          | °C/W |

| θJA(EVB)            | Junction-to-ambient thermal resistance (specific EVB)   | 63.3           | 82.3         | °C/W |

| ΨJC(Top)            | Junction-to-top characterization parameter              | 15.3           | 7.5          | °C/W |

| ΨЈВ                 | Junction-to-board characterization parameter            | 34.66          | 47.38        | °C/W |

DS6252A/B-02 August 2021 www.richtek.com

# **Electrical Characteristics**

# TSOT-23-6 (FC)

$(V_{IN} = 12V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                                     | Symbol                 | Test Conditions                                 | Min  | Тур  | Max  | Unit |

|-----------------------------------------------|------------------------|-------------------------------------------------|------|------|------|------|

| Supply Voltage                                |                        |                                                 |      | •    | •    |      |

| VIN Supply Input Operating Voltage            | V <sub>IN</sub>        |                                                 | 4.5  |      | 17   | V    |

| Under-Voltage Lockout<br>Threshold            | Vuvlo                  |                                                 | 3.7  | 4    | 4.3  | ٧    |

| Under-Voltage Lockout<br>Threshold Hysteresis | Δ <b>V</b> UVLO        |                                                 |      | 400  |      | mV   |

| Shutdown Current                              | ISHDN                  | V <sub>EN</sub> = 0V                            |      |      | 4    | μΑ   |

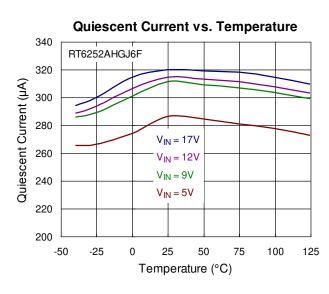

| Quiescent Current                             | IQ                     | $V_{EN} = 2V, V_{FB} = 0.8V$                    |      | 280  |      | μΑ   |

| Soft-Start                                    |                        |                                                 |      |      |      |      |

| Soft-Start Time                               | tss                    |                                                 |      | 1    |      | ms   |

| Enable Voltage                                |                        |                                                 |      |      |      |      |

| Facilia Valta va Thuashala                    | V <sub>EN_</sub> H     | EN high-level input voltage                     | 1.16 | 1.25 | 1.34 | V    |

| Enable Voltage Threshold                      | V <sub>EN_L</sub>      | EN low-level input voltage                      | 1.01 | 1.1  | 1.19 | V    |

| EN Pin Pull-Down<br>Resistance                | R <sub>EN_DN</sub>     | EN pin resistance to GND, V <sub>EN</sub> = 12V | 225  | 450  | 900  | kΩ   |

| Feedback Voltage and Discl                    | narge Resistar         | nce                                             |      |      |      |      |

| Feedback Threshold Voltage                    | V <sub>FB</sub>        | V <sub>OUT</sub> = 1.05V                        | 758  | 765  | 772  | mV   |

| Feedback Input Current                        | I <sub>FB</sub>        | VFB = 0.8V, TA = 25°C                           | -0.1 | 0    | 0.1  | μΑ   |

| Internal MOSFET                               |                        |                                                 |      |      |      |      |

| High-Side On-Resistance                       | R <sub>DS(ON)</sub> _H | $V_{BOOT} - V_{SW} = 4.8V$                      |      | 140  |      |      |

| Low-Side On-Resistance                        | RDS(ON)_L              |                                                 |      | 84   |      | mΩ   |

| Current Limit                                 | •                      |                                                 |      | •    | •    |      |

| High-Side Switch Current<br>Limit             | Ішм_н                  |                                                 |      | 5    |      |      |

| Low-Side Switch Valley<br>Current Limit       | ILIM_L                 |                                                 | 2.2  | 3.2  | 4.2  | Α    |

| Switching Frequency                           |                        |                                                 |      |      |      |      |

| Switching Frequency                           | fsw                    | V <sub>OUT</sub> = 1.05V, PWM mode              |      | 580  |      | kHz  |

| On-Time Timer Control                         | ı                      |                                                 |      | l .  | l .  |      |

| Minimum On-Time                               | ton_min                |                                                 |      | 60   |      | ns   |

| Minimum Off-Time                              | toff_min               | V <sub>FB</sub> = 0.5V                          |      | 200  | 260  | ns   |

| Output Under-Voltage Prote                    | ctions                 |                                                 |      |      |      |      |

| UVP Trip Threshold                            | V <sub>UVP</sub>       | Hiccup detect                                   |      | 65   |      | %    |

| Hiccup Power On-Time                          | tHICCUP_ON             |                                                 |      | 1.8  |      |      |

| Hiccup Power Off-Time                         | tHICCUP_OFF            |                                                 |      | 15   |      | ms   |

| Parameter                      | Symbol          | Test Conditions | Min | Тур | Max | Unit |

|--------------------------------|-----------------|-----------------|-----|-----|-----|------|

| Thermal Shutdown               |                 |                 |     |     |     |      |

| Thermal Shutdown<br>Threshold  | T <sub>SD</sub> |                 |     | 155 |     | °C   |

| Thermal Shutdown<br>Hysteresis | $\Delta T_{SD}$ |                 |     | 35  |     | °C   |

DS6252A/B-02 August 2021 www.richtek.com

# SOT-563 (FC)

$(V_{IN} = 12V, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter                                     | Symbol                | Test Conditions                                 | Min  | Тур  | Max  | Unit |

|-----------------------------------------------|-----------------------|-------------------------------------------------|------|------|------|------|

| Supply Voltage                                |                       |                                                 |      | •    | •    |      |

| VIN Supply Input Operating Voltage            | VIN                   |                                                 | 4.5  |      | 17   | ٧    |

| Under-Voltage Lockout<br>Threshold            | V <sub>UVLO</sub>     |                                                 | 3.9  | 4.2  | 4.5  | >    |

| Under-Voltage Lockout<br>Threshold Hysteresis | ΔV <sub>UVLO</sub>    |                                                 |      | 420  |      | mV   |

| Shutdown Current                              | ISHDN                 | V <sub>EN</sub> = 0V                            |      |      | 4    | μΑ   |

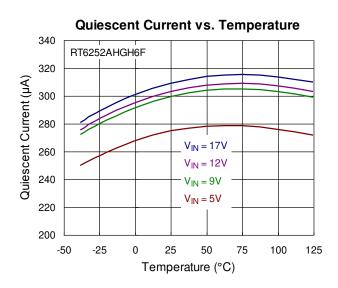

| Quiescent Current                             | IQ                    | $V_{EN} = 2V, V_{FB} = 0.85V$                   |      | 295  |      | μΑ   |

| Soft-Start                                    |                       |                                                 |      |      |      |      |

| Soft-Start Time                               | tss                   |                                                 |      | 0.95 |      | ms   |

| Enable Voltage                                |                       |                                                 |      |      |      |      |

| Frankla Valtaga Thyanhald                     | V <sub>EN_H</sub>     | EN high-level input voltage                     | 1.24 | 1.31 | 1.38 | V    |

| Enable Voltage Threshold                      | V <sub>EN_L</sub>     | EN low-level input voltage                      | 1.09 | 1.16 | 1.23 | V    |

| EN Pin Pull-Down<br>Resistance                | R <sub>EN_DN</sub>    | EN pin resistance to GND, V <sub>EN</sub> = 12V | 225  | 450  | 900  | kΩ   |

| Feedback Voltage and Disch                    | narge Resistan        | ce                                              |      |      |      |      |

| Feedback Threshold Voltage                    | V <sub>FB</sub>       | V <sub>OUT</sub> = 1.05V                        | 799  | 807  | 815  | mV   |

| Feedback Input Current                        | I <sub>FB</sub>       | VFB = 0.85V, TA = 25°C                          | -0.1 | 0    | 0.1  | μА   |

| Internal MOSFET                               |                       |                                                 |      | •    | •    |      |

| High-Side On-Resistance                       | R <sub>DS(ON)_H</sub> | $V_{BOOT} - V_{SW} = 4.8V$                      |      | 140  |      |      |

| Low-Side On-Resistance                        | R <sub>DS(ON)_L</sub> |                                                 |      | 84   |      | mΩ   |

| Current Limit                                 |                       |                                                 |      | •    | •    |      |

| High-Side Switch Current<br>Limit             | Ішм_н                 |                                                 |      | 5    |      |      |

| Low-Side Switch Valley<br>Current Limit       | I <sub>LIM_L</sub>    |                                                 | 2.5  | 3.35 | 4.2  | Α    |

| Switching Frequency                           |                       |                                                 |      |      |      |      |

| Switching Frequency                           | f <sub>SW</sub>       | V <sub>OUT</sub> = 1.05V, PWM mode              |      | 580  |      | kHz  |

| On-Time Timer Control                         |                       |                                                 |      | •    | •    |      |

| Minimum On-Time                               | ton_min               |                                                 |      | 60   |      | ns   |

| Minimum Off-Time                              | toff_min              | V <sub>FB</sub> = 0.5V                          |      | 190  | 250  | ns   |

| Output Under-Voltage Prote                    | ctions                | ,                                               |      | ı    | ı    | 1    |

| UVP Trip Threshold                            | V <sub>UVP</sub>      | Hiccup detect                                   |      | 65   |      | %    |

| Hiccup Power On-Time                          | tHICCUP_ON            |                                                 |      | 1.8  |      |      |

| Hiccup Power Off-Time                         | tHICCUP_OFF           |                                                 |      | 15   |      | ms   |

| <u> </u>                                      | UI TIME INICOUP_OFF   |                                                 |      |      |      |      |

| Parameter                      | Symbol          | Test Conditions | Min | Тур | Max | Unit |

|--------------------------------|-----------------|-----------------|-----|-----|-----|------|

| Thermal Shutdown               |                 |                 |     |     |     |      |

| Thermal Shutdown<br>Threshold  | T <sub>SD</sub> |                 |     | 155 |     | 00   |

| Thermal Shutdown<br>Hysteresis | $\Delta T_{SD}$ |                 |     | 35  |     | °C   |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution is recommended.

- Note 3. The device is not guaranteed to function outside its operating conditions.

- Note 4.  $\theta_{JA}$  and  $\theta_{JC}$  are measured or simulated at TA = 25°C based on the JEDEC 51-7 standard.

- Note 5.  $\theta_{JA(EVB)}$ ,  $\Psi_{JC(TOP)}$  and  $\Psi_{JB}$  are measured on a high effective-thermal-conductivity four-layer test board which is in size of 70mm x 50mm; furthermore, all layers with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

DS6252A/B-02 August 2021 www.richtek.com

# **Typical Application Circuit**

**Table 1. Recommended Components Selection**

| V (\( \)             | R <sub>FB1</sub> | ( <b>k</b> Ω) | D (kO)                | C (nE)               | 1 (                    | C(E)                  |

|----------------------|------------------|---------------|-----------------------|----------------------|------------------------|-----------------------|

| V <sub>OUT</sub> (V) | TSOT-23-6 (FC)   | SOT-563 (FC)  | R <sub>FB2</sub> (kΩ) | C <sub>FF</sub> (pF) | <b>L</b> (μ <b>H</b> ) | C <sub>OUT</sub> (μF) |

| 5.0                  | 54.9             | 52.3          | 10                    | 10 to 100            | 3.3 to 4.7             | 20 to 68              |

| 3.3                  | 33.2             | 30.9          | 10                    | 10 to 100            | 3.3 to 4.7             | 20 to 68              |

| 2.5                  | 22.6             | 21            | 10                    | 10 to 100            | 3.3 to 4.7             | 20 to 68              |

| 1.8                  | 13.7             | 12.4          | 10                    | 10 to 100            | 2.2 to 4.7             | 20 to 68              |

| 1.5                  | 9.53             | 8.66          | 10                    |                      | 2.2 to 4.7             | 20 to 68              |

| 1.2                  | 5.76             | 4.87          | 10                    |                      | 2.2 to 4.7             | 20 to 68              |

| 1.0                  | 3.09             | 2.4           | 10                    |                      | 2.2 to 4.7             | 20 to 68              |

## Note:

- (1) Please do not use a CFF higher than 100pF due to the noise coupling consideration.

- (2) Considering effective capacitance de-rating which is related to biased voltage level and size, the effective capacitance of C<sub>OUT</sub> at target output level should meet the value in above table to make converter operated in stable and normal.

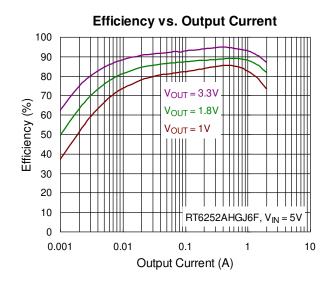

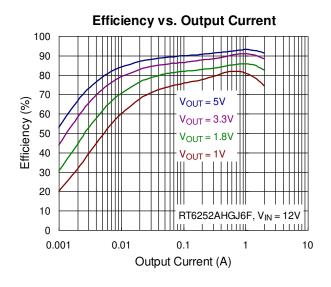

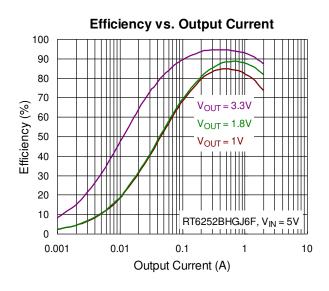

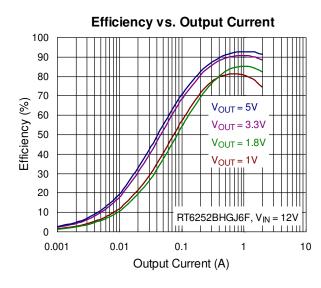

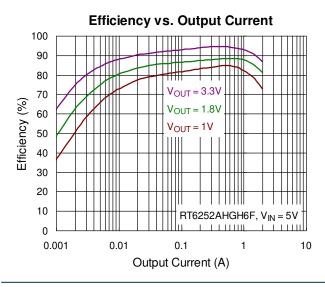

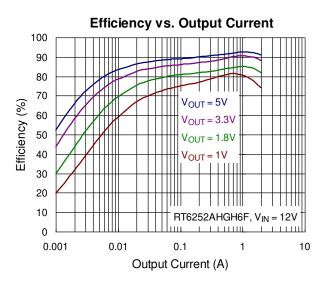

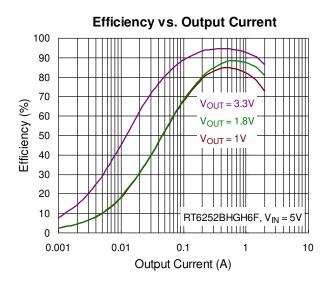

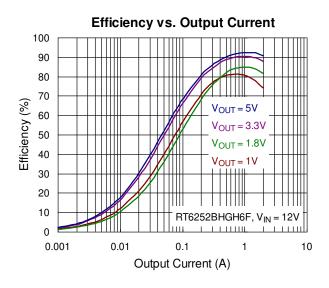

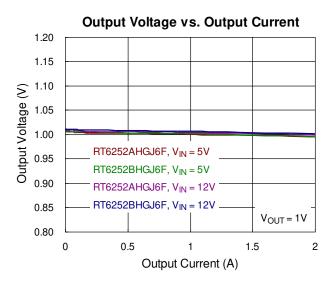

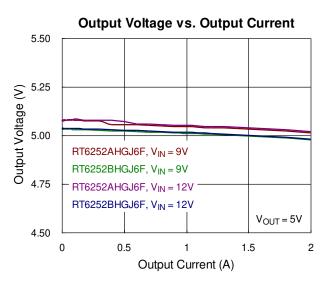

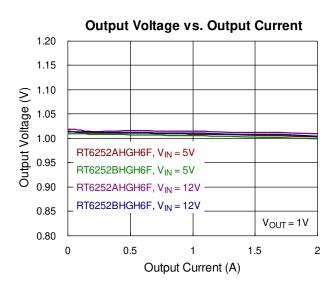

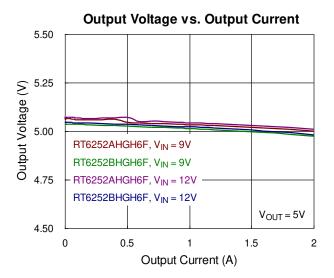

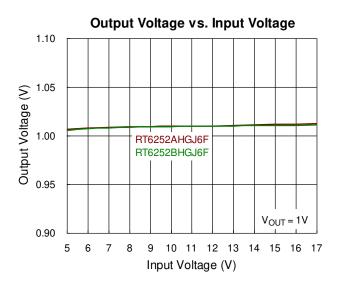

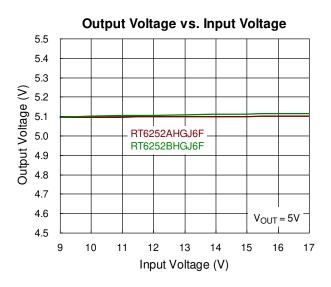

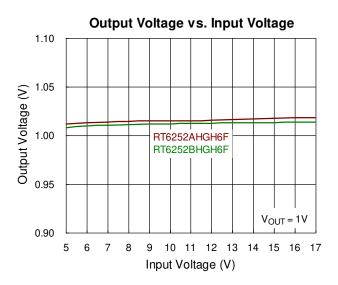

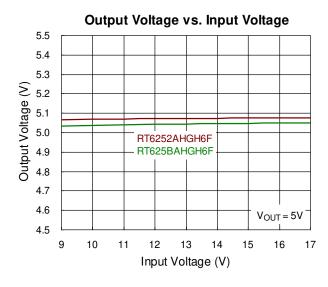

# **Typical Operating Characteristics**

L : WE-74404054022 (DCR =  $19m\Omega)$  for  $V_{OUT}$  = 1V and 1.8V.

L : WE-74404054047 (DCR =  $30m\Omega$ ) for  $V_{OUT} = 3.3V$  and 5V.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Time (400µs/Div)

# **Application Information**

The output stage of a synchronous buck converter is composed of an inductor and capacitor, which stores and delivers energy to the load, and forms a second-order low-pass filter to smooth out the switch node voltage to maintain a regulated output voltage.

#### **Inductor Selection**

The inductor selection trade-offs among size, cost, efficiency, and transient response requirements. Generally, three key inductor parameters are specified for operation with the device: inductance value (L), inductor saturation current (I<sub>SAT</sub>), and DC resistance (DCR).

A good compromise between size and loss is to choose the peak-to-peak ripple current equals to 20% to 50% of the IC rated current. The switching frequency, input voltage, output voltage, and selected inductor ripple current determines the inductor value as follows:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times \Delta I_L}$$

Once an inductor value is chosen, the ripple current  $(\Delta I_L)$  is calculated to determine the required peak inductor current.

$$\Delta I_L \!=\! \frac{V_{OUT} \times \! \left(V_{IN} - V_{OUT}\right)}{V_{IN} \times f_{SW} \times L} \; \text{ and } \; I_L(\text{PEAK}) \; = \; I_{OUT}(\text{MAX}) + \frac{\Delta I_L}{2}$$

I<sub>L(PEAK)</sub> should not exceed the minimum value of IC's upper current limit level. Besides, the current flowing through the inductor is the inductor ripple current plus the output current. During power up, faults, or transient load conditions, the inductor current can increase above the calculated peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify an inductor with a saturation current rating which is equal to or greater than the switch current limit rather than the peak inductor current.

Considering the Typical Application Circuit for 1.2V output at 2A and an input voltage of 12V, using an inductor ripple of 0.8A (40% of the IC rated current), the

calculated inductance value is:

$$L = \frac{1.2 \times \left(12 - 1.2\right)}{12 \times 580 \text{kHz} \times 0.8A} = 2.33 \mu H$$

For the typical application, a standard inductance value of  $2.2\mu H$  can be selected.

$$\Delta I_L = \frac{1.2 \times \left(12 - 1.2\right)}{12 \times 580 \text{kHz} \times 2.2 \mu H} = 0.85 \text{A (42.5\% of the IC rated current)}$$

and

$$I_{L(PEAK)} = 2A + \frac{0.85A}{2} = 2.425A$$

For the  $2.2\mu H$  value, the inductor's saturation and thermal rating should exceed at least 2.425A. For more conservative, the rating for inductor saturation current must be equal to or greater than switch current limit of the device rather than the inductor peak current.

For EMI sensitive application, choosing shielding type inductor is preferred.

### **Input Capacitor Selection**

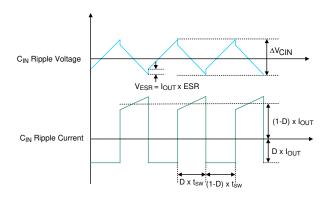

Input capacitance,  $C_{IN}$ , is needed to filter the pulsating current at the drain of the high-side power MOSFET.  $C_{IN}$  should be sized to do this without causing a large variation in input voltage. The waveform of  $C_{IN}$  ripple voltage and ripple current are shown in Figure 1. The peak-to-peak voltage ripple on input capacitor can be estimated as the equation below:

$$\Delta V_{CIN} = D \times I_{OUT} \times \left(\frac{1 - D}{C_{IN} \times f_{SW}}\right) + I_{OUT} \times ESR$$

where

$$D = \frac{V_{OUT}}{V_{IN} \times \eta}$$

For ceramic capacitors, the equivalent series resistance (ESR) is very low, the ripple which is caused by ESR can be ignored, and the minimum input capacitance can be estimated as the equation below:

$$C_{\text{IN\_MIN}} = I_{\text{OUT\_MAX}} \times \frac{D(1-D)}{\Delta V_{\text{CIN\_MAX}} \times f_{\text{SW}}}$$

where  $\Delta V_{CIN\_MAX} \leq 200 mV$

Figure 1.  $C_{\text{IN}}$  Ripple Voltage and Ripple Current In addition, the input capacitor needs to have a very low ESR and must be rated to handle the worst-case RMS input current of :

$$I_{RMS} \cong \ I_{OUT\_MAX} \times \frac{V_{OUT}}{V_{IN}} \times \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

It is common to use the worse  $I_{RMS} \cong I_{OUT}/2$  at  $V_{IN} = 2V_{OUT}$  for design. Note that ripple current ratings from capacitor manufacturers are often based on only 2000 hours of life which makes it advisable to further de-rate the capacitor, or choose a capacitor rated at a higher temperature than required.

Several capacitors may also be paralleled to meet size, height and thermal requirements in the design. For low input voltage applications, sufficient bulk input capacitance is needed to minimize transient effects during output load changes.

Ceramic capacitors are ideal for switching regulator applications because of its small size, robustness, and very low ESR. However, care must be taken when these capacitors are used at the input. A ceramic input capacitor combined with trace or cable inductance forms a high quality (under damped) tank circuit. If the RT6252A/B circuit is plugged into a live supply, the input voltage can ring to twice its nominal value, possibly exceeding the device's rating. This situation is easily avoided by placing the low ESR ceramic input capacitor in parallel with a bulk capacitor with higher ESR to damp the voltage ringing.

The input capacitor should be placed as close as possible to the VIN pins, with a low inductance connection to the GND of the IC. In addition to a larger bulk capacitor, a small ceramic capacitors of  $0.1 \mu F$  should be placed close to the VIN and GND pin. This

capacitor should be 0402 or 0603 in size.

# **Output Capacitor Selection**

The RT6252A/B are optimized for ceramic output capacitors and best performance will be obtained using them. The total output capacitance value is usually determined by the desired output voltage ripple level and transient response requirements for sag (undershoot on load apply) and soar (overshoot on load release).

#### **Output Ripple**

The output voltage ripple at the switching frequency is a function of the inductor current ripple going through the output capacitor's impedance. To derive the output voltage ripple, the output capacitor with capacitance ( $C_{OUT}$ ) and its equivalent series resistance ( $R_{ESR}$ ) must be taken into consideration. The output peak-to-peak ripple voltage ( $V_{RIPPLE}$ ) caused by the inductor current ripple ( $\Delta I_L$ ) is characterized by two components, which are ESR ripple ( $V_{RIPPLE(ESR)}$ ) and capacitive ripple ( $V_{RIPPLE(C)}$ ) and can be expressed as below:

$V_{RIPPLE} = V_{RIPPLE(ESR)} + V_{RIPPLE(C)}$

$V_{RIPPLE(ESR)} = \Delta I_{L} \times R_{ESR}$

$$V_{RIPPLE(C)} = \frac{\Delta I_L}{8 \times C_{OUT} \times f_{SW}}$$

As ceramic capacitors are used, both parameters should be estimated due to the extremely low ESR and relatively small capacitance. Refer to the RT6252A/B's typical application circuit of 1.2V application, the actual inductor current ripple ( $\Delta I_L$ ) is 0.85A, and the output capacitors are 2 x 22 $\mu$ F (Murata ceramic capacitor: GRM219R60J226ME47), VRIPPLE can be obtained as below.

The ripple caused by ESR  $(2m\Omega)$  can be calculated as :

$$V_{RIPPLE(ESR)} = 0.85A \times 2m\Omega = 1.7mV$$

Considering the capacitance derating, the effective capacitance is approximately  $18\mu F$  as the output voltage is 1.2V, and another parameter is :

$$V_{RIPPLE(C)} = \frac{0.85A}{8 \times 2 \times 18 \mu F \times 580 kHz} = 5.1 mV$$

$V_{RIPPLE} = 1.7 \text{mV} + 5.1 \text{mV} = 6.8 \text{mV}$

## **Output Transient Undershoot and Overshoot**

In addition to voltage ripple at the switching frequency, the output capacitor and its ESR also affect the voltage sag (undershoot) and soar (overshoot) when the load steps up and down abruptly. The ACOT<sup>®</sup> transient response is very quick and output transients are usually small. The following section shows how to calculate the worst-case voltage swings in response to very fast load steps.

Both undershoot voltage and overshoot voltage consist of two factors: the voltage steps caused by the output capacitor's ESR, and the voltage sag and soar due to the finite output capacitance and the inductor current slew rate. Use the following formulas to check if the ESR is low enough (typically not a problem with ceramic capacitors) and the output capacitance is large enough to prevent excessive sag and soar on very fast load step edges, with the chosen inductor value.

The amplitude of the ESR step up or down is a function of the load step and the ESR of the output capacitor :

VESR STEP =

$$\Delta$$

lout x Resr

The amplitude of the capacitive sag is a function of the load step, the output capacitor value, the inductor value, the input-to-output voltage differential, and the maximum duty cycle. The maximum duty cycle during a fast transient is a function of the on-time and the minimum off-time since the ACOT® control scheme will ramp the current using on-times spaced apart with minimum off-times, which is as fast as allowed. Calculate the approximate on-time (neglecting parasites) and maximum duty cycle for a given input and output voltage as:

$$t_{ON} = \frac{V_{OUT}}{V_{IN} \times f_{SW}} \text{ and } D_{MAX} = \frac{t_{ON}}{t_{ON} + t_{OFF\_MIN}}$$

The real on-time will slightly extend due to the voltage drop which is related to output current; however, this on-time compensation can be neglected. Besides, the minimum on-time is 60ns, typ. If the calculated on-time is smaller than minimum on-time, it and  $V_{OUT}$  will both be clamped. Calculate the output voltage sag as :

$$V_{SAG} = \frac{L \times (\Delta I_{OUT})^2}{2 \times C_{OUT} \times (V_{IN(MIN)} \times D_{MAX} - V_{OUT})}$$

The amplitude of the capacitive soar is a function of the

load step, the output capacitor value, the inductor value and the output voltage:

$$V_{SOAR} = \frac{L \times (\Delta I_{OUT})^2}{2 \times C_{OUT} \times V_{OUT}}$$

Because some modern digital loads can exhibit nearly instantaneous load changes, the amplitude of the ESR should be taken into consideration while calculating the V<sub>SAG</sub> & V<sub>SOAR</sub>.

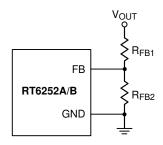

#### **Output Voltage Setting**

Set the desired output voltage using a resistive divider from the output to ground with the midpoint connected to FB, as shown in Figure 2. The output voltage is set according to the following equation:

$$V_{OUT} = 0.765 V \times (1 + R_{FB1} / R_{FB2})$$

Figure 2. Output Voltage Setting

Place the FB resistors within 5mm of the FB pin. Choose  $R_{FB2}$  between  $10k\Omega$  and  $100k\Omega$  to minimize power consumption without excessive noise pick-up and calculate  $R_{FB1}$  as follows :

$$R_{FB1} = \frac{R_{FB2} \times (V_{OUT} - V_{REF})}{V_{REF}}$$

For output voltage accuracy, use divider resistors with 1% or better tolerance.

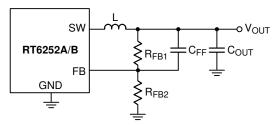

## Feed-Forward Capacitor Selection (CFF)

The RT6252A/B is optimized for low duty-cycle applications and the control loop is stable with low ESR ceramic output capacitors. In higher duty-cycle applications (higher output voltages or lower input voltages), the internal ripple signal will increase in amplitude. Before the ACOT® control loop can react to an output voltage fluctuation, the voltage change on the feedback signal must exceed the internal ripple amplitude. Because of the large internal ripple in this condition, the response may become slower and under-damped. This situation will result in ringing

RICHTEK

waveform at output terminal. In case of high output voltage application, the phenomenon described above is more visible because of large attenuation in feedback network. As shown in Figure 3, adding a feedforward capacitor (CFF) across the upper feedback resistor is recommended. This increases the damping of the control system.

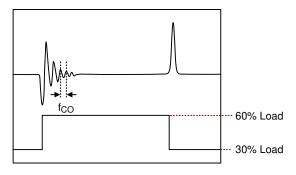

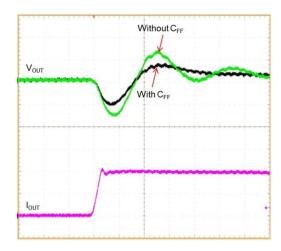

Figure 3. Feedback Loop with Feedforward Capacitor Loop stability can be checked by viewing the load transient response. A load step with a speed that exceeds the converter bandwidth must be applied. For ACOT®, loop bandwidth can be in the order of 100 to 200kHz, so a load step with 500ns maximum rising time (dl/dt  $\approx$  2A/ $\mu$ s) ensures the excitation frequency is sufficient. It is important that the converter operates in PWM mode, outside the light load efficiency range, and below any current limit threshold. A load transient from 30% to 60% of maximum load is reasonable which is shown in Figure 4.

Figure 4. Example of Measuring the Converter BW by Fast Load Transient

CFF can be calculated basing on below equation:

$$C_{FF} = \frac{1}{2\pi \times BW} \sqrt{\frac{1}{R_{FB1}} \times \left(\frac{1}{R_{FB1}} + \frac{1}{R_{FB2}}\right)}$$

Figure 5. shows the transient performance with and without feedfoward capacitor.

Note that, after defining the CFF please also check the load regulation, because feedforward capacitor might inject an offset voltage into  $V_{\text{OUT}}$  to cause  $V_{\text{OUT}}$

inaccuracy. If the output voltage is over spec caused by calculated  $C_{\text{FF}}$ , please decrease the value of feedforward capacitor  $C_{\text{FF}}$ .

Figure 5. Load Transient Response With and Without Feedforward Capacitor

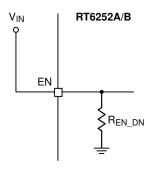

## **Enable Operation**

The RT6252A/B is enabled when the VIN pin voltage rises above  $V_{UVLO}$  while the EN pin voltage exceeds  $V_{EN\_H}$ . The RT6252A/B is disabled when the VIN pin voltage falls below  $V_{UVLO} - \Delta V_{UVLO}$  or when the EN pin voltage is below  $V_{EN\_L}$ . An internal pull-down resistor  $R_{EN\_DN}$ , which is connected form EN to GND, ensures that the chip still stays in shutdown even if EN pin is floated.

For automatic start-up, the EN pin, with high-voltage rating, can be connected to the input supply  $V_{\text{IN}}$  directly as shown in Figure 6.

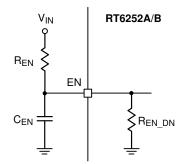

The built-in hysteresis band makes the EN pin useful for simple delay and timing circuits. The EN pin can be externally connected to  $V_{\text{IN}}$  by adding a resistor  $R_{\text{EN}}$  and a capacitor  $C_{\text{EN}}$ , as shown in Figure 7, to have an additional delay. The time delay can be calculated by the equation below with the EN's internal threshold, at which switching operation begins.

$$C_{EN} = \frac{t}{R_{th} \times ln \frac{V_{th}}{V_{th} - V_{EN\_H}}}$$

, where

$R_{th} = R_{EN} // R_{EN} DN$

$$V_{th} = V_{IN} \times \frac{R_{EN\_DN}}{R_{EN\_DN} + R_{EN}}$$

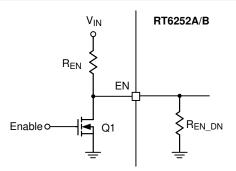

An external MOSFET can be used for logic control which is shown in Figure 8. In this case,  $R_{\text{EN}}$  is connected between VIN and the EN pin. The MOSFET Q1 will be under logic control to pull down the EN pin.

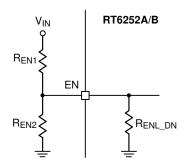

If the device is desired to be shut down by EN pin before VIN falls below the UVLO threshold, a resistive divider ( $R_{EN1}$  and  $R_{EN2}$ ) can be used to externally set the input under-voltage lockout threshold as shown in Figure 9. For a given  $R_{EN1}$ ,  $R_{EN2}$  can be found by the equation below for the desired  $V_{IN}$  stop voltage.

$$V_{IN\_STOP} \times \frac{R_{EN2} / / R_{EN\_DN}}{R_{EN1} + R_{EN2} / / R_{EN\_DN}} < V_{EN\_L}$$

After  $R_{\text{EN1}}$  and  $R_{\text{EN2}}$  are defined, the input voltage  $V_{\text{IN START}}$  is obtained from

$$V_{EN\_H} \times \frac{R_{EN1} + R_{EN2} /\!/ R_{EN\_DN}}{R_{EN2} /\!/ R_{EN\_DN}} = V_{IN\_START}$$

Figure 6. Automatic Start-Up Setting

Figure 7. External Timing Control

Figure 8. Digital Enable Control Circuit

Figure 9. Resistor Divider for Lockout Threshold

Setting

If  $V_{IN}$  shuts down faster than  $V_{OUT}$  and  $V_{OUT}$  is larger than 3.7V, buck converter becomes boost converter and generates negative current. To prevent these condition, EN should be shut down before  $V_{IN}$  falls below  $V_{OUT}$ . Therefore, the resistor divider for lockout threshold is recommended.

#### **Bootstrap Driver Supply**

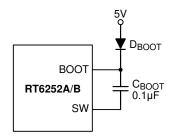

The bootstrap capacitor ( $C_{BOOT}$ ) between the BOOT pin and the SW pin is used to create a voltage rail above the applied input voltage, VIN. Specifically, the bootstrap capacitor is charged through an internal diode to a voltage equal to approximately PVCC each time the low-side switch is turned on. The charge on this capacitor is then used to supply the required current during the remainder of the switching cycle. For most applications, a  $0.1\mu F$ , 0603 ceramic capacitor with X5R is recommended and the capacitor should have a 6.3 V or higher voltage rating.

## **External Bootstrap Diode (Optional)**

A bootstrap capacitor of  $0.1\mu F$  low-ESR ceramic capacitor is connected between the BOOT and SW pins to supply the high-side gate driver. It is recommended to add an external bootstrap diode between an external 5V voltage supply and the BOOT pin as shown in Figure 10

to improve efficiency when the input voltage is below 5.5V. The bootstrap diode can be a low-cost one, such as 1N4148 or BAT54. The external 5V can be a fixed 5V voltage supply from the system, or a 5V output voltage generated by the RT6252A/B. Note that the BOOT voltage VBOOT must be lower than 5.5V.

Figure 10. External Bootstrap Diode

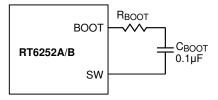

### **External Bootstrap Resistor (Optional)**

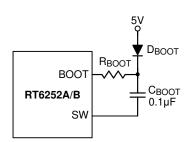

The gate driver of an internal power MOSFET, utilized as a high-side switch, is optimized for turning on the switch. The gate driver is not only fast enough for reducing switching power loss, but also slow enough for minimizing EMI. The EMI issue is worse when the switch is turned on rapidly due to the induced high di/dt noises. When the high-side switch is turned off, the discharging time on SW node is relatively slow because there's the presence of dead time, both high-side and low-side MOSFETs are turned off in this interval. In some cases, it is desirable to reduce EMI further, even at the expense of some additional power dissipation. The turn-on rate of the high-side switch can be slowed by placing a small bootstrap resistor RBOOT between the BOOT pin and the external bootstrap capacitor as shown in Figure 11. The recommended range for the RBOOT is several ohms to 47 ohms, and it could be 0402 or 0603 in size.

This will slow down the rates of the high-side switch turn on and the rise of  $V_{SW}$ . In order to improve EMI performance and enhancement of the internal MOSFET switch, the recommended application circuit is shown in Figure 12, which includes an external bootstrap diode for charging the bootstrap capacitor and a bootstrap resistor  $R_{BOOT}$  placed between the BOOT pin and the capacitor/diode connection.

Figure 11. External Bootstrap Resistor at the BOOT

Pin

Figure 12. External Bootstrap Diode and Resistor at the BOOT Pin

#### **Thermal Considerations**

In many applications, the RT6252A/B does not generate much heat due to its high efficiency and low thermal resistance of its TSOT-23-6 (FC) package. However, in applications which the RT6252A/B runs at a high ambient temperature and high input voltage, the generated heat may exceed the maximum junction temperature of the part.

The RT6252A/B includes an over-temperature protection (OTP) circuitry to prevent overheating due to excessive power dissipation. If the junction temperature reaches approximately 155°C, the RT6252A/B stops switching the power MOSFETs until the temperature is cooled down by 35°C.

Note that the over-temperature protection is intended to protect the device during momentary overload conditions. The protection is activated outside of the absolute maximum range of operation as a secondary fail-safe and therefore should not be relied upon operationally. Continuous operation above absolute maximum operating specified reliability temperature may impair device permanently damage the device.

The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = \left(T_{J(MAX)} - T_{A}\right) / \theta_{JA(EFFECTIVE)}$$

where  $T_{J(MAX)}$  is the maximum allowed junction temperature of the die. For recommended operating condition specifications, the maximum junction temperature is 125°C.  $T_A$  is the ambient operating temperature, and  $\theta_{JA(EFFECTIVE)}$  is the system-level junction to ambient thermal resistance. It can be estimated from thermal modeling or measurements in the system.

The thermal resistance of the device strongly depends on the surrounding PCB layout and can be improved by providing a heat sink of surrounding copper ground. The addition of backside copper with thermal vias, stiffeners, and other enhancements can also help reduce thermal resistance.

As an example, considering the RT6252A is used in application where V<sub>IN</sub> = 12V, I<sub>OUT</sub> = 2A, f<sub>SW</sub> = 580kHz, V<sub>OUT</sub> = 5V. The efficiency at 5V, 2A is 91.3% by using WE-74404054047 (4.7 $\mu$ H, 30m $\Omega$  DCR) as the inductor and measured at room temperature. The core loss can be obtained from its website, and it's 131mW. In this case, the power dissipation of the RT6252A is

$$P_{D, RT} = \frac{1-\eta}{\eta} \times P_{OUT} - \left(I_O^2 \times DCR + P_{CORE}\right) = 0.702W$$

Considering the system-level  $\theta_{JA(EFFECTIVE)}$  is 69.6°C /W (other heat sources are also considered), the junction temperature of the regulator operating in a 25°C ambient temperature is approximately :

$$T_{J} = 0.63W \times 76^{\circ}C/W + 25^{\circ}C = 73.9^{\circ}C$$

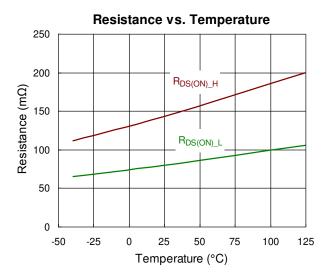

Figure 13 shows the RT6252A/B  $R_{DS(ON)}$  versus different junction temperatures. If the application requires a higher ambient temperature, the device power dissipation and the junction temperature of the device need to be recalculated based on a higher  $R_{DS(ON)}$  since it increases with temperature.

Using 60°C ambient temperature as an example. Due to the variation of junction temperature is dominated by the ambient temperature, the T'J at 60°C ambient temperature can be pre-estimated as

$$T_1' = 73.9^{\circ}C + (60^{\circ}C - 25^{\circ}C) = 108.9^{\circ}C$$

According to Figure 13, the increasing  $R_{DS(ON)}$  can be found as

$$\begin{split} &\Delta R_{DS(ON)\_H} = 190 m\Omega \; (at \; 108.9^{\circ}C) - 170 m\Omega \; \left(73.9^{\circ}C\right) = 20 m\Omega \\ &\Delta R_{DS(ON) \; L} = 101 m\Omega \; (at \; 108.9^{\circ}C) - 92 m\Omega \; \left(73.9^{\circ}C\right) = 9 m\Omega \end{split}$$

The external power dissipation caused by the increasing  $R_{DS(ON)}$  at higher temperature can be calculated as

$$\Delta P_{D,RDS(ON)} = \left(2A\right)^2 \times \frac{5}{12} \times 20 m\Omega + \left(2A\right)^2 \times \left(1 - \frac{5}{12}\right) \times 9 m\Omega = 0.054W$$

As a result, the new power dissipation is 0.756W due to the variation of  $R_{DS(ON)}$ . Therefore, the estimated new junction temperature is

$$T_J' = 0.756W \times 69.6^{\circ}C/W + 60^{\circ}C = 112.6^{\circ}C$$

If the application requires a higher ambient temperature and may exceed the recommended maximum junction temperature of 125°C, care should be taken to reduce the temperature rise of the part by using a heat sink or air flow.

Figure 13. RT6252A/B R<sub>DS(ON)</sub> vs. Temperature

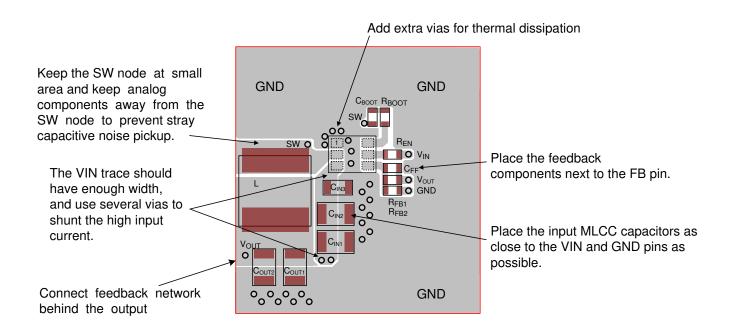

### **Layout Considerations**

Follow the PCB layout guidelines below for optimal performance of the device.

- ▶ Keep the high-current paths short, especially at the ground terminals. This practice is essential for stable and jitter-free operation. The high current path comprising of input capacitor, high-side FET, inductor, and the output capacitor should be as short as possible. This practice is essential for high efficiency.

- ▶ Place the input MLCC capacitors as close to the VIN and GND pins as possible. The major MLCC capacitors should be placed on the same layer as the RT6252A/B.

- ▶ SW node is with high frequency voltage swing and should be kept at small area. Keep analog components away from the SW node to prevent stray capacitive noise pickup.

- ► Connect feedback network behind the output capacitors. Place the feedback components next to the FB pin.

- ► For better thermal performance, design a wide and thick plane for GND pin or add a lot of vias to GND plane.

An example of PCB layout guide is shown in Figure 14.

Figure 14. Layout Guide

DS6252A/B-02 August 2021 www.richtek.com

27

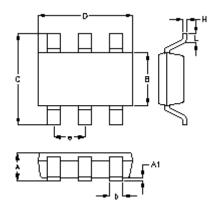

# **Outline Dimension**

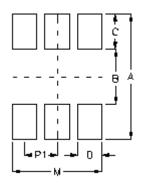

| Cumbal | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min. Max.    |               | Min.                 | Max.  |  |

| Α      | 0.700        | 1.000         | 0.028                | 0.039 |  |

| A1     | 0.000        | 0.100         | 0.000                | 0.004 |  |

| В      | 1.397        | 1.803         | 0.055                | 0.071 |  |

| b      | 0.300        | 0.559         | 0.012                | 0.022 |  |

| С      | 2.591        | 3.000         | 0.102                | 0.118 |  |

| D      | 2.692        | 3.099         | 0.106                | 0.122 |  |

| е      | 0.9          | 950           | 0.037                |       |  |

| Н      | 0.080        | 0.254         | 0.003                | 0.010 |  |

| L      | 0.300        | 0.610         | 0.012                | 0.024 |  |

TSOT-23-6 (FC) Surface Mount Package

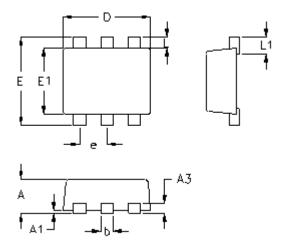

| Complete | Dimensions | In Millimeters | Dimension | s In Inches |

|----------|------------|----------------|-----------|-------------|

| Symbol   | Min        | Max            | Min       | Max         |

| Α        | 0.500      | 0.600          | 0.020     | 0.024       |

| A1       | 0.000      | 0.050          | 0.000     | 0.002       |

| A3       | 0.080      | 0.180          | 0.003     | 0.007       |

| b        | 0.150      | 0.300          | 0.006     | 0.012       |

| D        | 1.500      | 1.700          | 0.059     | 0.067       |

| E        | 1.500      | 1.700          | 0.059     | 0.067       |

| E1       | 1.100      | 1.300          | 0.043     | 0.051       |

| е        | 0.5        | 500            | 0.0       | 20          |

| L        | 0.100      | 0.300          | 0.004     | 0.012       |

| L1       | 0.200      | 0.400          | 0.008     | 0.016       |

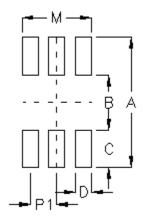

SOT-563 (FC) Surface Mount Package

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

DS6252A/B-02 August 2021

www.ri

# **Footprint Information**

|                                        | Number of |      | Footp | rint Din | nension | (mm) |      | Tolerance |

|----------------------------------------|-----------|------|-------|----------|---------|------|------|-----------|

| Package                                | Pin       | P1   | Α     | В        | С       | D    | М    | rolerance |

| TSOT-26/TSOT-26(FC)/SOT-26/SOT-26(COL) | 6         | 0.95 | 3.60  | 1.60     | 1.00    | 0.70 | 2.60 | ±0.10     |

| Dookogo     | Number of |      | Foo  | tprint Dim | nension (r | mm)  |           | Talaranaa |

|-------------|-----------|------|------|------------|------------|------|-----------|-----------|

| Package     | P1        | Α    | В    | С          | D          | М    | Tolerance |           |

| SOT-563(FC) | 6         | 0.50 | 2.42 | 1.02       | 0.70       | 0.30 | 1.30      | ±0.10     |

# **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.