## QorlQ<sup>™</sup> Communications Platforms

## **P2 Platform Series** Dual core performance in a single core power envelope

Ideal for networking infrastructure, telecom, industrial control, medical imaging, telehealth, aerospace and defense and test and measurement applications, Freescale QorlQ<sup>™</sup> communications platforms are the next-generation evolution of our leading PowerQUICC<sup>®</sup> communications processors. Based on high-performance e500 cores built on Power Architecture<sup>®</sup> technology, QorlQ platforms enable a new era of networking innovation that meets reliability, security and quality of service needs for the most demanding networking and industrial applications.

The QorIQ P2 platform series, which includes the P2020 and P2010 communications processors, delivers unprecedented performance per watt for a wide variety of applications at a low price point. The series delivers dual- and single-core frequencies from 800 MHz to 1.2 GHz.

The QorIQ P2 series is pin-compatible with the QorIQ P1 platform products, offering five interchangeable cost-effective solutions. Scaling from a single core at 533 MHz (P1011) to a dual core at 1.2 GHz (P2020), the two QorIQ platforms deliver an impressive 4.5x aggregate frequency range within the same pinout.

The devices in the P1 and P2 series are also software compatible, sharing the e500 core and peripherals, as well as being fully software compatible with existing PowerQUICC processors. This enables you to create a product with multiple performance points from a single board design, which provides great flexibility and scalability. Freescale provides highly integrated evaluation boards, software and drivers for the P2020 and P2010 as well as CodeWarrior<sup>™</sup> tools that will help speed your design to market. The P2020 family provides the horsepower, integration and scalability needed whether you are building a high-performance router or an industrial platform.

| QorlQ™ P2 Processors                                                                                        |                                                                                                                               |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Features                                                                                                    | Benefits                                                                                                                      |  |  |  |

| Comprehensive development tools including reference design boards, Linux <sup>®</sup> and third-party tools | Helps decrease time to revenue by getting designs up and running efficiently                                                  |  |  |  |

| Migration path                                                                                              | Improved performance/watt/cost migrating from PowerQUICC III and other Power Architecture-, x86- and MIPs-based architectures |  |  |  |

| High-performance e500 2.4 MIPS/MHz Power Architecture® core                                                 | High performance and efficient cores means fewer cores to get the job done                                                    |  |  |  |

| Best-in-class power                                                                                         | Enables fanless, energy-efficient designs for improved reliability and lower system costs                                     |  |  |  |

| Integrated Ethernet, USB, eSDHC flash controller, eSPI, eLBU, IEEE® 1588, PCI Express® and Serial RapidIO®  | Flexibility to address a wide range of applications and reduced system cost by eliminating the need for external bridge chips |  |  |  |

| 4.5x performance range in a single package                                                                  | Common hardware platform to enable a wide range of system performance                                                         |  |  |  |

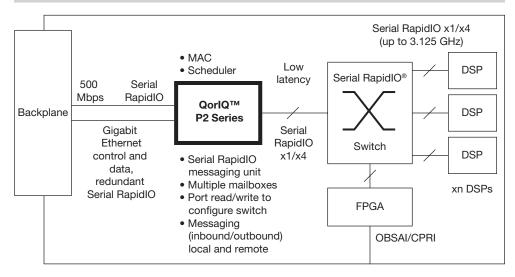

#### Telecom

Features for the market:

- Dual Gigabit Ethernet on SGMII (for redundancy) or Serial RapidIO<sup>®</sup> interface for implementing backhaul

- Serial RapidIO interface for direct connection to digital signal processors (DSPs)—for Layer 1 processing

- Security engine handles the secure network termination requirement

- Advanced quality of service (QoS) for Gigabit Ethernet to assist in scheduling Layer 2 baseband processing

## Applications:

- AdvancedMC<sup>™</sup> card

- Controller on AdvancedTCA® carrier card

- Channel and control card for 3G NodeB, 2G/2.5G BTS IP upgrades, WCDMA, 4G LTE and WiMAX

- General purpose compute blade

## LTE and WiMAX Baseband

## LTE and WiMAX Baseband

The P2020 and P2010 communications processors are well-suited for Long-Term Evolution (LTE) and WiMAX channel card applications. There are two factors that drive the need for dual-core performance without breaking out of a single-core power budget:

- Increased bandwidth per subscriber

- Flattening of the infrastructure hierarchy

Together, these factors increase the processing requirements of the channel card. P2 series processors, with dualcore performance in single-core power budgets, can increase performance in Layer 2 baseband processing and implementing network interfaces.

Layer 2 baseband processing implements the RLC layer that controls the base station and subscriber access to air interface resources. The advanced QoS features of the Gigabit Ethernet ports assist in scheduling these resources. This Layer 2 processing includes the medium access control (MAC), which controls the base station and subscriber access to air interface resources. Resources are scheduled according to QoS requirements using packet concatenation and segmentation, retransmission through automatic repeat request (ARQ) and hybrid automatic repeat request (HARQ) in combination with Layer 1.

Typically backhaul is implemented with either dual Gigabit Ethernet on SGMII (for redundancy) or Serial RapidIO interface, both of which are supported in the QorIQ P2 series processors. The Serial Rapid IO interface also allows direct connection to the DSPs—such as Freescale's MSC8144 and MSC8156 fourand six-core DSPs—that implement the Layer 1 processing. The security block handles the secure network termination requirement.

This solution performs network backhaul transport and interworking with internal interfaces. This includes processing the network layers up to OSI Layer 3, including IPsec secure network termination, header compression and traffic classification (QoS). The network interface card (NIC) can optionally support 3G LTE radio link encryption—however, depending upon the selected architecture, this could be partitioned to the channel card.

# NP

#### Compute Blades

#### Compute Blades

Blade servers have been widely adopted in data centers because they cost less to deploy and less to operate—due to savings in power and cooling—than rack-optimized servers. Blade servers are also more easily scaled than fixed-capacity monolithic servers to meet workload growth and are easier to service with their field-replaceable blades.

Blades process and move a large amount of data. Historically, designers have incorporated more processors and more processor types. Systems could include any number of CPUs, DSPs, microcontrollers, network processors and application-specific processors.

Embedding switches into blade servers provides further infrastructure integration, simplified management, greater scalability, improved power and cooling efficiency and increased application availability.

As enterprises begin to migrate to nextgeneration data centers, blade server switches are evolving to meet the new demands with advanced functions such as application-aware networking, low latency line-rate switching at Gigabit (Gb) speeds, advanced QoS, support for virtualization and advanced security features.

QorlQ processors can help designers reap the benefit of using highly integrated processors with the I/O needed for application/contentaware processing. Freescale partner companies such as 6WIND provide an open framework to ease the transition from a single core to many cores. Multicore-aware network middleware from 6WIND can boost performance, placing configuration and management at the heart of the software. This solves real business issues of time and cost savings associated with software integration, interface, configuration and network management of multicore machines.

The P2020 processor can manage control and dataplane functions in blade systems. This reduces the cost of integrating additional bridge chips to perform these functions.

#### Networking

Features for the Market:

- SD/MMC interface enables modularity by supporting booting from flash cards

- PCI Express interfaces enable multiple flexible I/O options

- USB port for front-panel code uploads when connecting directly to a PC for maintenance

- Triple Gigabit Ethernet (dual on SGMII for redundancy for backplane interconnect) and one Gigabit Ethernet interface for high-performance debug and maintenance

#### Applications:

- Line card controller

- Mid-range line card control plane

- Low-end line card combined control and data plane

- Shelf controller

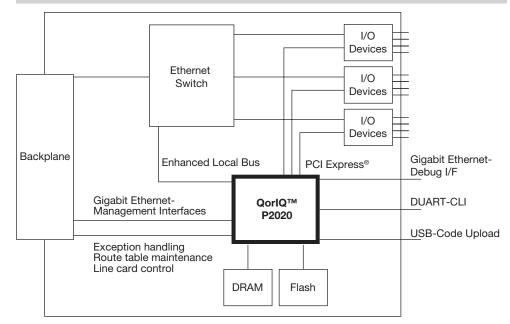

## Line Card Control Plane for Enterprise Routers

One of the primary applications for the QorIQ P2020 communications processor is as a line card control plane processor. Typically the P2020 will sit to the side of the main datapath, which has I/O processors on the front panel connected to a backplane interface device. The P2020 processor will communicate with these components using standard interfaces such as PCI Express or the local bus. The P2020 will often have front panel interfaces as well. One Gigabit Ethernet interface may be used for high-performance debug: the DUART can be used for a low-level command line interface and the USB port may be used for front-panel code uploads when connecting directly to a PC for maintenance. Redundant Gigabit Ethernet ports to the backplane are used as a management interface, which can be used to communicate with a centralized resource for receiving table updates, for instance. The eSDHC interface enables modularity by supporting booting from flash memory cards.

The primary functions of a linecard controller are:

- Exception handling: Packets that cannot be interpreted by the typically more hardwired datapath are kicked up to the control plane processor. These may be older or esoteric protocols which are not worth accommodating in ASICs, but can be handled with software with low performance impact because they occur infrequently.

- Board housekeeping: The control plane processor may be used to configure, provision and control other devices on the board. It also will collect statistics. It can implement a command line interface.

- Table maintenance: A line card controller may, especially in a distributed system, manage the forwarding tables. The tables are created by implementing a variety of interior routing protocols (such as Open Shortest Path First or Routing Information Protocol) and external routing protocols (such as Border Gateway Protocol). The tables are then exported to the forwarding path for per-packet access.

In the case of centralized processing, these functions are performed by a centralized processor, which can tolerate higher power and associated increased cooling costs because there are fewer of those cards per system. In these cases, the line card has little intelligence.

Implementing a line card in a distributed processing system provides several advantages. You may be able to forgo the costly centralized services card, which consumes a valuable slot in the chassis. You have the opportunity to perform local switching at the line card, thus conserving system resources. And the system becomes more scalable-as you add a line card, you automatically get the increased processing that it requires. However, in this system, the costs of high-volume line cards are critically important. Because of that, thermal budgets are very tight. The need for high performance at low power is a requirement that the P2 family fulfills.

Line Card Control Plane for Enterprise Routers

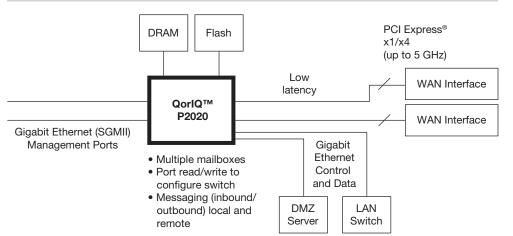

#### **Multiservice Routers**

A multiservice router or business gateway requires a combination of high performance and a rich set of peripherals to support the datapath throughputs and required system functionality. The P2 series of single- and dual-core devices offer a scalable platform to develop a range of products that can support the same feature set. Integrated 10/100/1000 Ethernet controllers with classification and QoS capabilities are ideal for managing the datapath traffic between the local area network (LAN) and wide area network (WAN) interface. PCI Express ports can provide connectivity to IEEE® 802.11n radio cards for wireless support and TDM for legacy phone interfaces to support voice. USB or eSDHC interfaces can be used to support local storage; the second USB interface is also available to support USB-attached printers or as a console port. The integrated security engine can provide encrypted secure communications for remote users with VPN support.

#### **Multiservice Routers**

#### Industrial

#### Features for the Market:

- IEEE<sup>®</sup> 1588 support for nanosecond level clock accuracy

- Virtualization support

- Double precision FPU

- Performance to 1500+ MIPS

- Memory management unit (MMU) for OS support

- <5W per processor to support fanless operation

- Memory L2 512 KB, DDR2/3 support support

#### Applications:

- Robotics

- Test/measurement, networking/telecom

- Multifunction printer (MFP)

- Single board computers

- Industrial applications

- Medical

## Industrial Networking

Disruptive technologies and trends are affecting the embedded market and providing device manufacturers in the industrial sector with a significant opportunity to improve both their devices and their businesses. Technical and industry trends in multicore processors and virtualization represent a significant opportunity for competitive advantage. Freescale's QorIQ multicore processors provide increased overall performance and improved performance per watt over single-core processors. Multicore processorbased systems can also improve application scalability and protect software investment by allowing processors with more cores to be substituted to meet future demand.

A dual-core processor can support networked communication from the factory floor on one processor while the other processor manages the lower field and data layer controlling the factory floor, linking sensors and actuators to controllers and ultimately to manufacturing equipment. Typically, this level requires equipment with very low power consumption. The P2020 typical power is less than five watts.

#### Test and Measurement

To continue realizing performance gains without increased clock rates, designers are integrating their test and measurement systems with dual and multicore devices. Test engineers can develop automated test applications capable of achieving the highest possible throughput through parallel processing with multicore processors.

When using traditional text-based programming languages, engineers who want to harness this computing power for developing advanced test, measurement and control applications regularly face the challenges of complex software primitives and programming models. However, engineers and scientists can capitalize on multithreaded application development by combining multicore support and software that supports parallelism. Using dual and multicore processors enables an application to distribute processing loads across multiple CPU cores simultaneously, which can significantly reduce test times for applications

that require intensive signal and data processing such as RF protocol testing and hardware in the loop (HIL) simulations. These applications also can replicate specific tests or processes to run on separate CPU cores and effectively double system throughput.

|                                      | P1011                              | P1020                                   | P2010                               | P2020                                    |

|--------------------------------------|------------------------------------|-----------------------------------------|-------------------------------------|------------------------------------------|

| CPU                                  | e500 V2, up to<br>800 MHz, 32K I/D | Dual e500 V2, up to<br>800 MHz, 32K I/D | e500 V2, up to<br>1200 MHz, 32K I/D | Dual e500 V2, up to<br>1200 MHz, 32K I/D |

| L2 Cache                             | 256 KB                             | 256 KB                                  | 512 KB                              | 512 KB                                   |

| DDR I/F Type/Width                   | DDR2/3, 32-bit                     | DDR2/3, 32-bit                          | DDR2/3, 32/64-bit                   | DDR2/3, 32/64-bit                        |

| 10/100/1000 Ethernet (IEEE® 1588 v2) | 3, with 2 SGMII                    | 3, with 2 SGMII                         | 3, with 2 SGMII                     | 3, with 2 SGMII                          |

| TDM                                  | Yes                                | Yes                                     | -                                   | -                                        |

| Enhanced Local Bus                   | Yes                                | Yes                                     | Yes                                 | Yes                                      |

| PCI Express <sup>®</sup> 1.0a        | 2 controllers with 4<br>SerDes     | 2 controllers with 4<br>SerDes          | 3 controllers with 4<br>SerDes      | 3 controllers with 4<br>SerDes           |

| Serial RapidIO <sup>®</sup> 1.2      | -                                  | -                                       | 2 x 1 or 1 x 4                      | 2 x 1 or 1 x 4                           |

| USB 2.0                              | 2                                  | 2                                       | 1                                   | 1                                        |

| Memory Card                          | eSDHC                              | eSDHC                                   | eSDHC                               | eSDHC                                    |

| Other Interfaces                     | eSPI, 2 x I²C, DUART               | eSPI, 2 x I²C, DUART                    | eSPI, 2 x I²C, DUART                | eSPI, 2 x I²C, DUART                     |

| Accelerators                         | SEC 3.3                            | SEC 3.3                                 | SEC 3.1                             | SEC 3.1                                  |

| Package                              | 689 TEPBGA II                      | 689 TEPBGA II                           | 689 TEPBGA II                       | 689 TEPBGA II                            |

#### Test and Measurement

The P2020DS-PA board and P2020RDB-PA board ship with Linux v2.6 and support for IEEE 1588. Both boards are supported by CodeWarrior v8.8, Wind River, Green Hills and MontaVista development environments. The P20220DS-PA is a highly integrated development system that can be utilized to bring your design to market. The P2020RDB-PA is a low-cost reference design board based on the mini-ITX form factor.

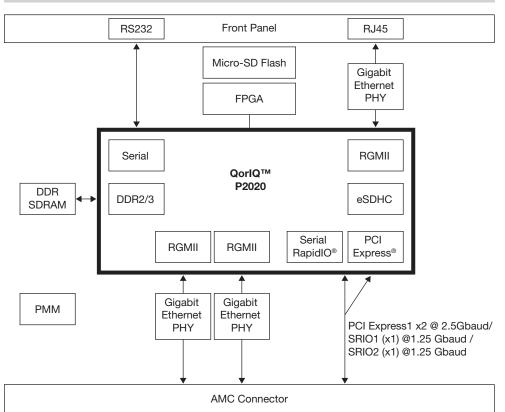

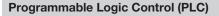

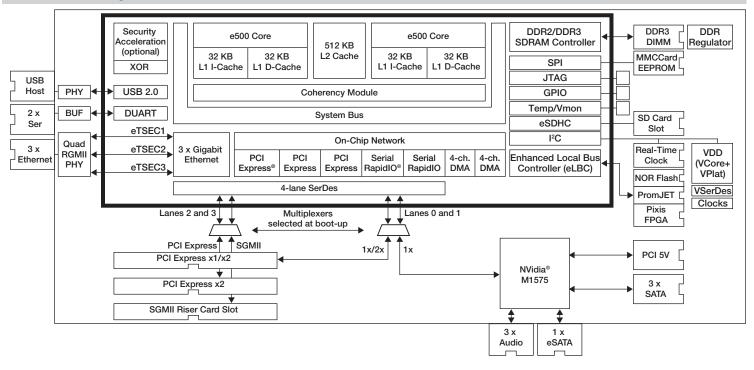

## P2020DS Block Diagram

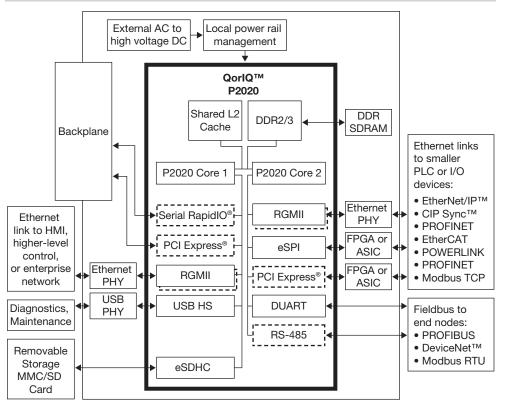

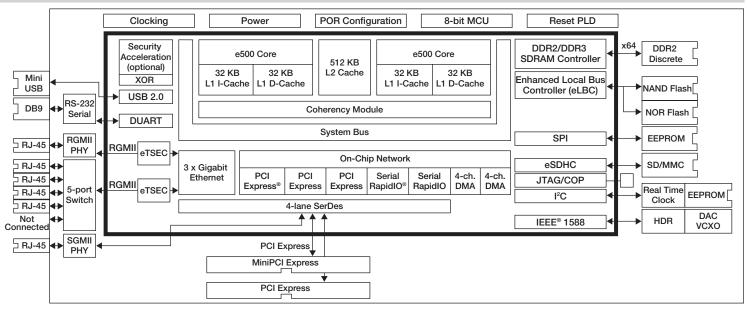

## P2020RDB Block Diagram

Learn More:

For current information about Freescale products and documentation, please visit **www.freescale.com/QorlQ**.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © Freescale Semiconductor, Inc. 2009. Document Number: P2PRDCTFMAPPBRCH

REV 0