# EVAL-AD7761FMCZ User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## Evaluation Board for the AD7761 16-Bit, 8-Channel, Simultaneous Sampling, 256 kSPS, Sigma-Delta ADC with Power Scaling

### **FEATURES**

Full featured evaluation board for the AD7761

PC control in conjunction with the SDP-H1

system demonstration platform (EVAL-SDP-CH1Z)

PC software control and data analysis

Time and frequency domain

Standalone hardware capability

### **ONLINE RESOURCES**

Evaluation kit contents

EVAL-AD7761FMCZ evaluation board

Evaluation software CD for the AD7761

Documents needed

AD7761 data sheet

EVAL-AD7761FMCZ user guide

Required software

AD7761 evaluation software

### **EQUIPMENT NEEDED**

EVAL-AD7761FMCZ evaluation board

EVAL-SDP-CH1Z system demonstration platform

External 7 V to 9 V bench top power supply

DC/ac signal source (Audio Precision® or similar high

performance signal source)

USB cable

PC running Windows with USB 2.0 port

### **GENERAL DESCRIPTION**

The EVAL-AD7761FMCZ evaluation kit features the AD7761 16-bit, 256 kSPS, analog-to-digital converter (ADC). A 7 V to 9 V external bench top supply is regulated to 5 V and 3.3 V to supply the AD7761 and support components. The EVAL-AD7761FMCZ board connects to the USB port of the PC via a connection to the EVAL-SDP-CH1Z motherboard.

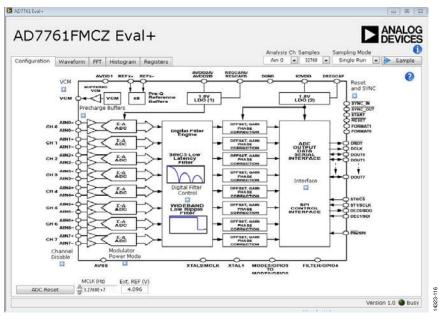

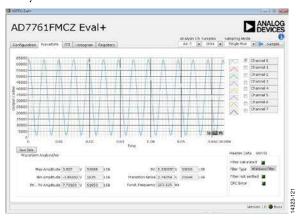

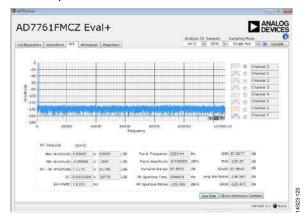

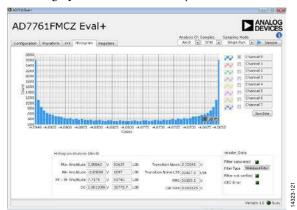

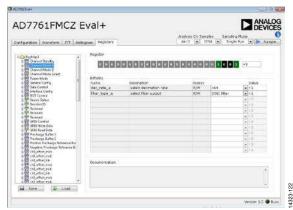

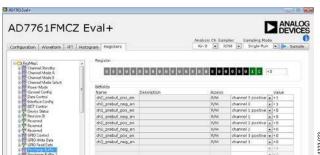

The AD7761 evaluation software fully configures the AD7761 device register functionality and provides dc and ac time domain analysis in the form of waveform graphs, histograms, and associated noise analysis for ADC performance evaluation.

The EVAL-AD7761FMCZ is an evaluation board that allows the user to evaluate the features of the ADC. The user PC software executable controls the AD7761 over a USB cable through the EVAL-SDP-CH1Z system demonstration platform (SDP).

Full specifications for the AD7761 are available in the product data sheet, which should be consulted in conjunction with this user guide when working with the evaluation board.

### UG-949

### **EVAL-AD7761FMCZ User Guide**

### **TABLE OF CONTENTS**

| Features                            | I |

|-------------------------------------|---|

| Online Resources                    | 1 |

| Equipment Needed                    | 1 |

| General Description                 | 1 |

| Revision History                    | 2 |

| EVAL-AD7761FMCZ Quick Start Guide   | 3 |

| Analog Inputs and Front-End Circuit | 4 |

| Evaluation Board Hardware           | 5 |

| Device Description                  | 5 |

| Hardware Link Options               | 5 |

| Power Supplies                      | 8 |

| Serial Data Interface                           |    |

|-------------------------------------------------|----|

| Serial Configuration Interface                  | 8  |

| Powering Down the System Demonstration Platform | 8  |

| Sockets/Connectors                              | 9  |

| Evaluation Board Setup Procedures               | 9  |

| Evaluation Board Software                       | 10 |

| Software Installation Procedures                | 10 |

| Setting up the System for Data Capture          | 13 |

| Software Operation                              | 14 |

### **REVISION HISTORY**

4/16—Revision 0: Initial Version

### **EVAL-AD7761FMCZ QUICK START GUIDE**

To begin using the EVAL-AD7761FMCZ evaluation board, take the following steps:

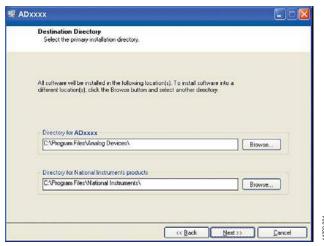

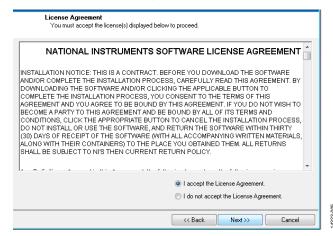

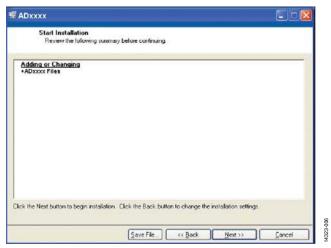

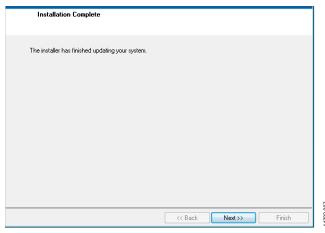

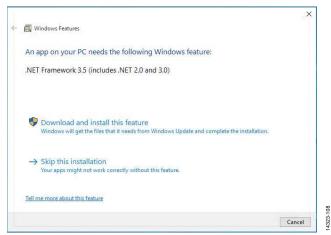

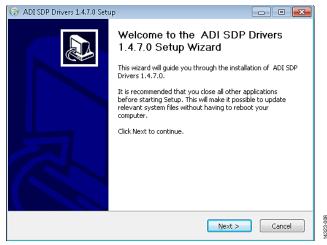

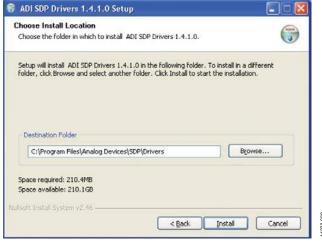

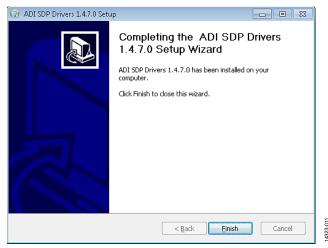

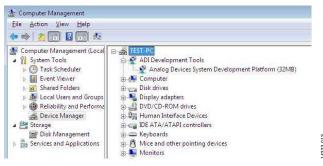

- Ensure that the EVAL-SDP-CH1Z board is disconnected from the USB port of the PC. Install the evaluation board software from the CD included in the evaluation board kit. Restart the PC after the software installation is complete. (For complete software installation instructions, see the Software Installation Procedures section.)

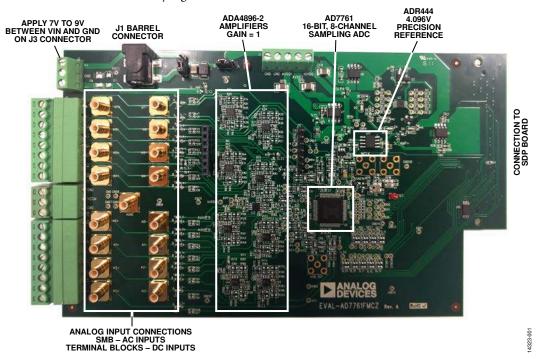

- Connect the EVAL-SDP-CH1Z board to the EVAL-AD7761FMCZ evaluation board (unpowered). Figure 1 illustrates the connection: J4 of the EVAL-SDP-CH1Z board adapts to the receiving socket on the EVAL-AD7761FMCZ printed circuit board (PCB).

- 3. Ensure that the boards are connected firmly together.

- 4. Apply power to the EVAL-AD7761FMCZ evaluation board via the supplied 9 V dc adapter at J1 (LK1 in Position B). Alternatively, supply an external voltage in the range of 7 V to 9 V from a bench top power supply using the J3 connector (LK1 in Position A).

- 5. Connect the 12 V dc supply to the EVAL-SDP-CH1Z board, and then connect to the PC using the supplied USB cable. For Windows® XP, the PC may need to search for the EVAL-SDP-CH1Z drivers. Choose to automatically search for the drivers for the EVAL-SDP-CH1Z board if prompted by the operating system.

- 6. Launch the AD7761 evaluation software from the **Analog Devices** subfolder in the **Programs** menu.

Figure 1. Evaluation Board

### ANALOG INPUTS AND FRONT-END CIRCUIT

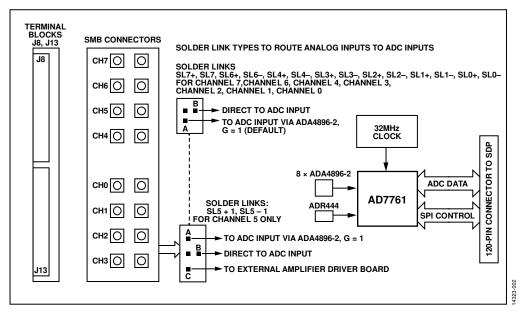

As shown in Figure 2, the AIN0± to AIN7± analog inputs are accessible through either the SMBs or the terminal blocks.

Figure 2 shows theses connectors and details the 16 main solder links that route the inputs from either the terminal blocks or the SMBs for each of the signals.

In the default board configuration, the input terminals are connected through to the ADA4896-2 on each of the ADC channels.

The ADR444 4.096 V low noise reference is used by default, allowing an absolute input range of 0||4.096 V on each input.

The ADA4896-2 amplifiers are not terminated at the inputs for any particular source impedances.

Use the on-board, common-mode voltage source on the AD7761 to bias the input signal. The default condition is  $V_{\text{CM}}$  = (AVDD1 – AVSS)/2.

Figure 2. Analog Inputs: Input Connectors, Solder Links, and Amplifiers

## EVALUATION BOARD HARDWARE DEVICE DESCRIPTION

The AD7761 is an 8-channel, simultaneously sampling,  $\Sigma$ - $\Delta$  ADC. The AD7761 offers an ADC per channel and synchronized sampling. The ADC power scaling is as required for the application, catered for by selecting one of the following modes of operation:

- Fast: 256 kSPS maximum, 110.8 kHz input bandwidth, 52 mW per channel

- Median: 128 kSPS maximum, 55.4 kHz input bandwidth, 28 mW per channel

- Focus: 32 kSPS maximum, 13.8 kHz input bandwidth,

9.5 mW per channel

The AD7761 offers extensive digital filtering:

- Wideband: low ripple, antialiasing, low-pass filter with sharp roll off, and full attenuation at Nyquist frequency.

- Sinc response: sinc5 filter, low latency path for dc measurements or control loops.

Within these filter options, the user can select a decimation rate of 32, 64, 128, 256, 512, or 1024.

Embedded analog functionality on each ADC channel simplifies system design. A precharge buffer on each analog input reduces analog input current.

Complete specifications for the AD7761 are provided in the product data sheet and should be consulted in conjunction with this user guide when using the evaluation board. Full details about the EVAL-SDP-CH1Z are available on the Analog Devices, Inc., website.

### HARDWARE LINK OPTIONS

The default link options are listed in Table 1. The board can be configured to operate from a bench top power supply via Connector J3, or from a 9 V dc adapter via Connector J1. The supply required for the AD7761 comes from the on-board low dropout regulators (LDOs), which generate their input voltage from J1 or J3, depending on the setting of LK1. Alternatively, the board can be powered by setting LK2 to Position A when used in conjunction with the EVAL-SDP-CH1Z (see Table 3 for details).

Table 1. Default Link and Solder Link Options

| Link No. Default Option |                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LK1                     | Α                     | LK1 selects the input voltage source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                         |                       | Position A: J3 is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                         |                       | Position B: J1 is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| LK2                     | В                     | LK2 selects the input from EVAL-SDP-CH1Z board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                         |                       | Position A: 12 V input from EVAL-SDP-CH1Z.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                         |                       | Position B: external power supply from either J1 or J3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SL1                     | Α                     | SL1 selects between pin mode and SPI mode operation of the AD7761.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                         |                       | Position A: SPI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                         |                       | Position B: pin mode (pin mode is not compatible with the evaluation software and currently untested on the evaluation board).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| SL2                     | В                     | FORMAT0 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                         |                       | Position A: IOVDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                         |                       | Position B: DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| SL3                     | A                     | FORMAT1 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                         |                       | Position A: DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                         |                       | Position B: IOVDD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| SL4                     | Α                     | Clock terminal source selection. To choose the Y1 crystal oscillator, do not populate SL4. R253,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                         |                       | R254, C46, and C45 must be populated. SL4A must be configured to the crystal oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                         |                       | Position A: selects CMOS Oscillator Y2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                         |                       | Position B: unpopulated terminals (J6 and J7).  Position C: SDP MCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| CLAA                    | Δ.                    | . This is a second of the seco |  |  |  |

| SL4A                    | A                     | Clock select (CLK_SEL) pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                         |                       | CMOS clock option on Pin 32.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| SL5                     | Soldered 0 Ω resistor | Crystal oscillator or LVDS option.  Shorts SYNC_OUT to SYNC_IN to allow sync pulses on START to be synchronously applied to SYNC_IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                         |                       | Pin 16: STO/CS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SL6                     | A                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                         |                       | Position A: chip select (CS) pin in SPI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                         |                       | Position B: Channel 0 to Channel 3 in standby mode (pin mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                         |                       | Position C: Channel 0 to Channel 3 enabled (pin mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

### UG-949

| Link No.   | <b>Default Option</b> | Description                                                                                            |  |  |

|------------|-----------------------|--------------------------------------------------------------------------------------------------------|--|--|

| SL7 A      |                       | Pin 17: ST1/SCLK.                                                                                      |  |  |

|            |                       | Position A: SCLK in SPI mode.                                                                          |  |  |

|            |                       | Position B: Channel 4 to Channel 7 in standby mode (pin mode).                                         |  |  |

|            |                       | Position C: Channel 4 to Channel 7 enabled (pin mode).                                                 |  |  |

| SL8        | Α                     | Pin 18: DEC1/SDI.                                                                                      |  |  |

|            |                       | Position A: SDI in SPI mode.                                                                           |  |  |

|            |                       | Position B: IOVDD.                                                                                     |  |  |

|            |                       | Position C: GND.                                                                                       |  |  |

| SL9        | A                     | Pin 19: DECO/SDO.                                                                                      |  |  |

|            |                       | Position A: SDO in SPI mode.                                                                           |  |  |

|            |                       | Position B: IOVDD.                                                                                     |  |  |

|            |                       | Position C: GND.                                                                                       |  |  |

| SL10       | A                     | Pin 12: MODE0/GPIO0.                                                                                   |  |  |

|            |                       | Position A: GPIO to SDP.                                                                               |  |  |

|            |                       | Position B: GND.                                                                                       |  |  |

|            |                       | Position C: IOVDD.                                                                                     |  |  |

| SL11       | Α                     | Pin 13: MODE1/GPIO1.                                                                                   |  |  |

|            |                       | Position A: GPIO to SDP.                                                                               |  |  |

|            |                       | Position B: GND.                                                                                       |  |  |

|            |                       | Position C: IOVDD.                                                                                     |  |  |

| SL12       | Α                     | Pin 14: MODE2/GPIO2.                                                                                   |  |  |

|            |                       | Position A: GPIO to SDP.                                                                               |  |  |

|            |                       | Position B: GND.                                                                                       |  |  |

|            |                       | Position C: IOVDD.                                                                                     |  |  |

| SL13       | A                     | Pin 15: MODE3/GPIO3.                                                                                   |  |  |

|            |                       | Position A: GPIO to SDP.                                                                               |  |  |

|            |                       | Position B: GND.                                                                                       |  |  |

|            |                       | Position C: IOVDD.                                                                                     |  |  |

| SL14       | A                     | Pin configuration mode. The AD7761 evaluation kit software runs from SPI mode; select the filter       |  |  |

|            |                       | via the register map. This link selects the filter mode (only available in pin mode).                  |  |  |

|            |                       | Position A: GPIO4.                                                                                     |  |  |

|            |                       | Position B: sinc5 fast settling filter.                                                                |  |  |

|            |                       | Position C: wideband low ripple filter.                                                                |  |  |

| SL15       | A                     | Select common-mode voltage to bias input signals to one of the following:.                             |  |  |

|            |                       | Position A: OP2177 buffered VCM output.                                                                |  |  |

|            |                       | Position B: VCM output from the AD7761.                                                                |  |  |

| SL16       | В                     | Select reference path from the ADR444 to REFX+.                                                        |  |  |

|            |                       | Position A: bypass the external reference buffer.                                                      |  |  |

|            |                       | Position B: ADR444 input into the ADA4841-1 reference buffer.                                          |  |  |

| SL17       | В                     | Select reference path from the ADR444 to REFX+.                                                        |  |  |

|            |                       | Position A: bypass the external reference buffer.                                                      |  |  |

|            |                       | Position B: select output from the ADA4841-1 reference buffer.                                         |  |  |

| SL18       | Unsoldered            | Shorts IOVDD to DREGCAP, only for IOVDD = 1.8 V operation; see the AD7761 data sheet.                  |  |  |

| SL19       | A                     | External common mode buffer input selection.                                                           |  |  |

|            |                       | Position A: AD7761 VCM pin.                                                                            |  |  |

|            |                       | Position B: AVDD1 is used for common-mode selection, R166 (0 $\Omega$ ) and R167 (not inserted) can be |  |  |

|            |                       | used as voltage dividers.                                                                              |  |  |

| SL22, SL23 |                       | Selects the output from Channel 5 amplifier driver option.                                             |  |  |

| ,          |                       | Position A: ADA4896-2.                                                                                 |  |  |

|            |                       | Position B: bypass the driver.                                                                         |  |  |

|            |                       | Position C: amplifier driver board header via the J11 and J12 connectors.                              |  |  |

| Link No.   | <b>Default Option</b> | Description                                                                                                                                                                                    |  |

|------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SLP1       | Α                     | AVDD1 input selector.                                                                                                                                                                          |  |

|            |                       | Position A: ADP7118ARDZ-5.0 5 V LDO.                                                                                                                                                           |  |

|            |                       | Position B: external AVDD1 input (J2, Pin 3).                                                                                                                                                  |  |

| SLP2       | Α                     | AVDD2 LDO selector.                                                                                                                                                                            |  |

|            |                       | Position A: ADP7118ARDZ-5.0 5 V LDO.                                                                                                                                                           |  |

|            |                       | Position B: external AVDD2 input (J2, Pin 4).                                                                                                                                                  |  |

| SLP4       | A                     | IOVDD input selector.                                                                                                                                                                          |  |