# 809XBH/839XBH/879XBH **ADVANCED 16-BIT MICROCONTROLLER** WITH 8- OR 16-BIT EXTERNAL BUS

**Automotive**

- Extended Automotive Temperature Range (-40°C to + 125°C Case)

- **High Performance NMOS Process**

- 8 Kbytes On-Chip ROM/EPROM

- 232 Byte Register RAM

- Register-to-Register Architecture

- 10-Bit A/D Converter with S/H

- **■** Five 8-Bit I/O Ports

- **20 Interrupt Sources**

- 8-Bit Pulse-Width Modulated Output

- Run-Time Programmable EPROM

- Full Duplex Serial Port

- High-Speed I/O Subsystem

- Full Duplex Serial Port

- Dedicated Baud Rate Generator

- 6.25 µs 16 x 16 Multiply

- 6.25 µs 32/16 Divide

- 16-Bit Watchdog Timer

- Four 16-Bit Software Timers

- Two 16-Bit Counters/Timers

- Available in 68-Pin PLCC, PFP and CFP; 48-Pin PDIP Package

(See Packaging Specifications, Order # 231369)

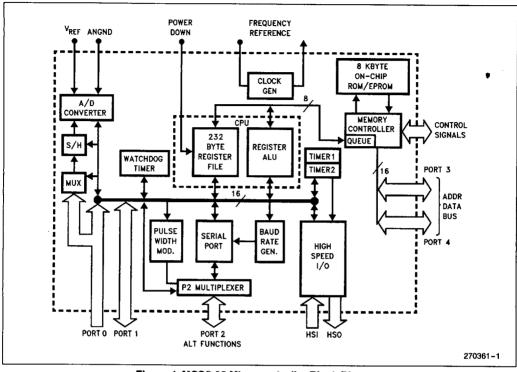

The 8X9XBH family of 16-bit microcontrollers consists of many members, all of which are designed for highspeed control functions. The 8X9XBH family members produced for the automotive environment, using Intel's HMOS-III process, with 8 Kbytes of ROM (or ROMless) and 232 total bytes of on-chip RAM, 256 bytes of register RAM are described in this datasheet.

The CPU supports bit, byte, and word operations. Thirty-two-bit double words are supported for a subset of the instruction set. With a 12 MHz input frequency the 8X9XBH can do a 16-bit addition in 1.0  $\mu s$  and a 16 x 16-bit multiply or 32/16 divide in 6.25 µs. Instruction execution times average 1 µs to 2 µs in typical applications.

Four high-speed capture inputs are provided to record the times at which external events occur stored in an eight-level FIFO. Rising, falling, rising and falling, or every eight rising edges can be recorded every 2.25 µs using 12 MHz clock. Interrupts can be programmed for every FIFO entry, or every 6th FIFO entry.

Up to 6 high-speed pulse generator outputs are provided to trigger external events at preset times. The highspeed output unit can simultaneously perform software timer functions, start A/D conversions, or pulse one or more outputs. Up to four 16-bit software timers can be in operation at once.

The on-chip A/D converter includes a Sample and Hold (S/H), and converts up to 8 multiplexed analog input channels to a 10-bit digital result. With a 12 MHz input frequency, each conversion takes as little as 22 µs. A/D conversions can be performed at preprogrammed times, or asynchronously.

Also provided on-chip are: a full duplex, double buffered receive serial port with 3 asynchronous and 1 synchronous modes; a 16-bit watchdog timer, and a 256 state pulse-width modulated output signal.

#### NOTICE:

This datasheet contains information on products in full production. Specifications within this datasheet are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

Figure 1. MCS® 96 Microcontroller Block Diagram

### PRODUCT/PACKAGING OPTIONS

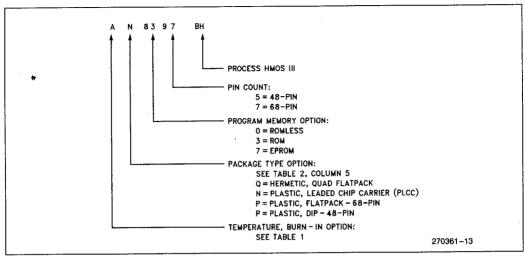

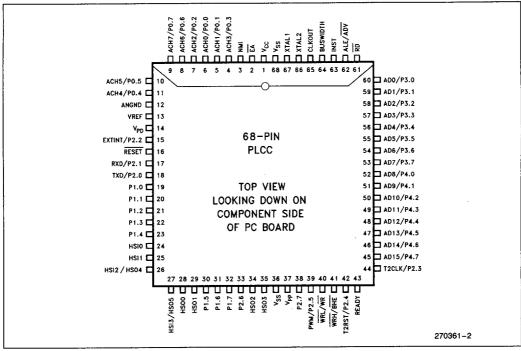

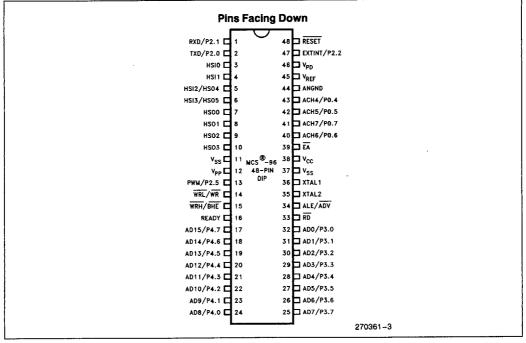

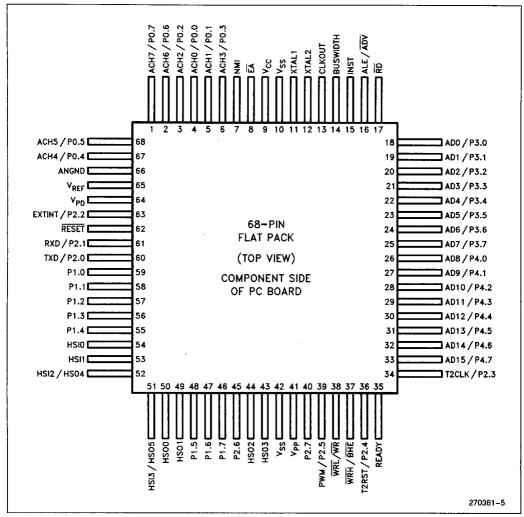

The 8X9XBH is available in 48 and 68-pin packages, with and without on-chip ROM or EPROM. The 8X9XBH nomenclature is shown in Figure 2. Figures 3, 4 and 6 show the pinouts for all available 68-pin packages: Plastic Leaded Chip Carrier (PLCC), Plastic Flatpack (PFP) and Ceramic Flatpack (CFP). Figure 5 shows the pinout for the 48-pin Plastic Dip Package (PDIP).

The 8X9XBH is also available in three temperature range options: Commercial (0°C to +70°C), Extended (-40°C to +85°C) and Automotive (-40°C to +125°C). Intel's extended and automotive temper-

ature range products are designed to meet the needs of those applications whose operating requirements exceed commercial standards.

The automotive, extended, and commercial temperature versions of the 8X9XBH product families are available with or without burn-in options as listed in Table 1.

As shown in Figure 2, temperature, burn-in and package options are indentified by a one- or two-letter prefix to the part number. It also illustrates the 8X9XBH family nomenclature for ROM/EPROM/ROMless, with/without A/D, and process.

Figure 2. The 8X9XBH Family Nomenclature

Table 1. Temperature — Burn-In Option

| Temperature    | Temperature | Operating              | Burn-In    |

|----------------|-------------|------------------------|------------|

| Classification | Designation | Temperature            | 125°C (Hr) |

| Commercial     | Null        | 0°C to +70°C Ambient   | 6          |

| Extended       | Т           | -40°C to +85°C Ambient | 6          |

| Automotive     | A           | -40°C to +125°C Case   | 6          |

|                | H           | -40°C to +125°C Case   | 6          |

## NOTES:

- 1. Burn-in is dynamic at  $\pm$  125°C,  $V_{CC} = 7.3V \pm 0.25V$ , for 6 hours.

- 2. Other burn-in durations are also available, but not standard.

Table 2. The 8X9XBH Family Packages

| ROMless             | 68-Pin<br>68-Pin<br>48-Pin | N8097BH-PLCC<br>P8097BH-PFP<br>P8095BH-P-DIP |

|---------------------|----------------------------|----------------------------------------------|

| ROM<br>(8 Kbytes)   | 68-Pin<br>68-Pin<br>48-Pin | N8397BH-PLCC<br>P8397BH-PFP<br>P8395BH-P-DIP |

| EPROM<br>(8 Kbytes) | 68-Pin<br>48-Pin           | Q8797BH-CFP<br>C8795BH-DIP                   |

| PFP/CFP | 48-Pin<br>P-DIP | 68-Pin<br>PLCC | Description     | PFP/CFP | 48-Pin<br>P-DIP | 68-Pin<br>PLCC | Description      |

|---------|-----------------|----------------|-----------------|---------|-----------------|----------------|------------------|

| 1       | 41              | 9              | ACH7/P0.7       | 35      | 16              | 43             | READY            |

| . 2     | 40              | 8              | ACH6/P0.6       | 36      |                 | 42             | T2RST/P2.4       |

| 3       | _               | 7              | ACH2/P0.2       | 37      | 15              | 41             | BHE/WRH          |

| 4       |                 | 6              | ACH0/P0.0       | 38      | 14              | 40             | WR/WRL           |

| 5       | _               | 5              | ACH1/P0.1       | 39      | 13              | 39             | PWM/P2.5         |

| 6       |                 | 4              | ACH3/P0.3       | 40      |                 | 38             | P2.7/T2CAPTURE   |

| 7       |                 | 3              | NMI             | 41      | 12              | 37             | $V_{PP}$         |

| 8       | 39              | 2              | ĒĀ              | 42      | 11              | 36             | V <sub>SS</sub>  |

| 9       | 38              | 1              | Vcc             | 43      | 10              | 35             | HSO.3            |

| 10      | 37              | 68             | V <sub>SS</sub> | 44      | 9               | 34             | HSO.2            |

| 11      | 36              | 67             | XTAL1           | 45      |                 | 33             | P2.6             |

| 12      | 35              | 66             | XTAL2           | 46      |                 | 32             | P1.7             |

| 13      | _               | 65             | CLKOUT          | 47      |                 | 31             | P1.6             |

| 14      | _               | 64             | BUSWIDTH        | 48      |                 | 30             | P1.5             |

| 15      | _               | 63             | INST            | 49      | 8               | 29             | HSO.1            |

| 16      | 34              | 62             | ALE/ADV         | 50      | 7               | 28             | HSO.0            |

| 17      | 33              | 61             | RD              | 51      | 6               | 27             | HSO.5/HSI.3      |

| 18      | 32              | 60             | AD0/P3.0        | 52      | 5               | 26             | HSO.4/HSI.2      |

| 19      | 31              | 59             | AD1/P3.1        | 53      | 4               | 25             | HSI.1            |

| 20      | 30              | 58             | AD2/P3.2        | 54      | 3               | 24             | HSI.0            |

| 21      | 29              | 57             | AD3/P3.3        | 55      | _               | 23             | P1.4             |

| 22      | 28              | 56             | AD4/P3.4        | 56      | _               | 22             | P1.3             |

| 23      | 27              | 55             | AD5/P3.5        | 57      | _               | 21             | P1.2             |

| 24      | 26              | 54             | AD6/P3.6        | 58      |                 | 20             | P1.1             |

| 25      | 25              | 53             | AD7/P3.7        | 59      | _               | 19             | P1.0             |

| 26      | 24              | 52             | AD8/P4.0        | 60      | 2               | 18             | TXD/P2.0         |

| 27      | 23              | 51             | AD9/P4.1        | 61      | 1               | 17             | RXD/P2.1         |

| 28      | 22              | 50             | AD10/P4.2       | 62      | 48              | 16             | RESET            |

| 29      | 21              | 49             | AD11/P4.3       | 63      | 47              | 15             | EXTINT/P2.2      |

| 30      | 20              | 48             | AD12/P4.4       | 64      | 46              | 14             | $V_{PD}$         |

| 31      | 19              | 47             | AD13/P4.5       | 65      | 45              | 13             | V <sub>REF</sub> |

| 32      | 18              | 46             | AD14/P4.6       | 66      | 44              | 12             | ANGND            |

| 33      | 17              | 45             | AD15/P4.7       | 67      | 43              | 11             | ACH4/P0.4        |

| 34      | _               | 44             | T2CLK/P2.3      | 68      | 42              | 10             | ACH5/P0.5        |

Figure 3. PFP/CFP, P-DIP and PLCC Functional Pinouts

Figure 4. 68-Pin PLCC Package

Figure 5. 48-Pin P-DIP Package

Figure 6. 68-Pin Package (Flat Pack—Top View)

# PIN DESCRIPTIONS

| Symbol           | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>  | Main supply voltage (5V).                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>SS</sub>  | Digital circuit ground (0V). There are two VSS pins, both of which must be connected.                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>PD</sub>  | RAM standby supply voltage (5V). This voltage must be present during normal operation. In a Power Down condition (i.e. $V_{CC}$ drops to zero), if RESET is activated before $V_{CC}$ drops below spec and $V_{PD}$ continues to be held within spec., the top 16 bytes in the Register File will retain their contents. RESET must be held low during the Power Down and should not be brought high until $V_{CC}$ is within spec and the oscillator has stabilized. |

| V <sub>REF</sub> | Reference voltage for the A/D converter (5V). $V_{REF}$ is also the supply voltage to the analog portion of the A/D converter and the logic used to read Port 0. Must be connected for A/D and Port 0 to function.                                                                                                                                                                                                                                                    |

| ANGND            | Reference ground for the A/D converter. Must be held at nominally the same potential as Vss.                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>PP</sub>  | Programming voltage for the EPROM parts. It should be $\pm$ 12.75V for programming. This pin is V <sub>BB</sub> on 8X9X-90 parts. Systems that have this pin connected to ANGND through a capacitance (required on 8X9X-90 parts) do not need to change. Otherwise, tie to V <sub>CC</sub> .                                                                                                                                                                          |

| XTAL1            | Input of the oscillator inverter and of the internal clock generator.                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL2            | Output of the oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKOUT           | Output of the internal clock generator. The frequency of CLKOUT is $\frac{1}{3}$ the oscillator frequency. It has a 33% duty cycle.                                                                                                                                                                                                                                                                                                                                   |

| RESET            | Reset input to the chip. Input low for at least 2 state times to reset the chip. The subsequent low-to-high transition re-synchronizes CLKOUT and commences a 10-state-time sequence in which the PSW is cleared, a byte read from 2018H loads CCR, and a jump to location 2080H is executed. Input high for normal operation. RESET has an internal pullup.                                                                                                          |

| BUSWIDTH         | Input for bus width selection. If CCR bit 1 is a one, this pin selects the bus width for the bus cycle in progress. If BUSWIDTH is high, a 16-bit bus cycle occurs. If BUSWIDTH is low, an 8-bit cycle occurs. If CCR bit 1 is a 0, the bus is always an 8-bit bus. This pin is the TEST pin on 8X9X-90 parts. Systems with TEST tied to V <sub>CC</sub> do not need to change. If this pin is left unconnected, it will rise to V <sub>CC</sub> .                    |

| NMI              | A positive transition causes a vector to external memory location 0000H. External memory from 00H through 0FFH is reserved for Intel development systems.                                                                                                                                                                                                                                                                                                             |

| INST             | Output high during an external memory read indicates the read is an instruction fetch. INST is valid throughout the bus cycle. INST is activated only during external memory accesses.                                                                                                                                                                                                                                                                                |

| ĒĀ               | Input for memory select (External Access). EA equal to a TTL-high causes memory accesses to locations 2000H through 3FFFH to be directed to on-chip ROM/EPROM. EA equal to a TTL-low causes accesses to these locations to be directed to off-chip memory. EA = +12.5V causes execution to begin in the Programming Mode. EA has an internal pulldown, so it goes low unless driven otherwise. EA is latched at reset.                                                |

# PIN DESCRIPTIONS (Continued)

| Symbol        | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE/ADV       | Address Latch Enable or Address Valid output, as selected by CCR. Both pin options provide a latch to demultiplex the address from the address/data bus. When the pin is $\overline{ADV}$ , it goes inactive high at the end of the bus cycle. $\overline{ADV}$ can be used as a chip select for external memory. ALE/ $\overline{ADV}$ is activated only during external memory accesses.                                                                                                                                                                                                                                                                                               |

| RD            | Read signal output to external memory. $\overline{\text{RD}}$ is activated only during external memory reads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WR/WRL        | Write and Write Low output to external memory, as selected by the CCR. WR will go low for every external write, while WRL will go low only for external writes where an even byte is being written. WR/WRL is activated only during external memory writes.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BHE/WRH       | Bus High Enable or Write High output to external memory, as selected by the CCR.  BHE low selects the bank of memory that is connected to the high byte of the data bus. A0 low selects the bank of memory that is connected to the low byte of the data bus. Thus accesses to a 16-bit wide memory can be to the low byte only (A0 low, BHE high), to the high byte only (A0 high, BHE low), or both bytes (A0 low, BHE low). If the WRH function is selected, the pin will go low if the bus cycle is writing to an odd memory location. BHE/WRH is activated only during external memory writes.                                                                                      |

| READY         | Ready input to lengthen external memory cycles, for interfacing to slow or dynamic memory, or for bus sharing. If the pin is high, CPU operation continues in a normal manner. If the pin is low prior to the falling edge of CLKOUT, the memory controller goes into a wait mode until the next positive transition in CLKOUT occurs with READY high. The bus cycle can be lengthened by up to 1 μs. When the external memory is not being used, READY has no effect. Internal control of the number of wait states inserted into a bus cycle held not ready is available through configuration of CCR. READY has a weak internal pullup, so it goes high unless externally pulled low. |

| HSI           | Inputs to High Speed Input Unit. Four HSI pins are available: HSI.0, HSI.1, HSI.2 and HSI.3. Two of them (HSI.2 and HSI.3) are shared with the HSO Unit. The HSI pins are also used as inputs by EPROM parts in Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| HSO           | Outputs from High Speed Output Unit. Six HSO pins are available: HSO.0, HSO.1, HSO.2, HSO.3, HSO.4 and HSO.5. Two of them (HSO.4 and HSO.5) are shared with the HSI Unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Port 0        | 8-bit high impedance input-only port. These pins can be used as digital inputs and/or as analog inputs to the on-chip A/D converter. These pins are also a mode input to EPROM parts in the Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Port 1        | 8-bit quasi-bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port 2        | 8-bit multi-functional port. Six of its pins are shared with other functions, the remaining 2 are quasi-bidirectional. These pins are also used to input and output control signals on EPROM parts in Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Ports 3 and 4 | 8-bit bidirectional I/O ports with open drain outputs. These pins are shared with the multiplexed address/data bus which has strong internal pullups. Ports 3 and 4 are also used as a command, address and data path by EPROM parts operating in the Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                  |

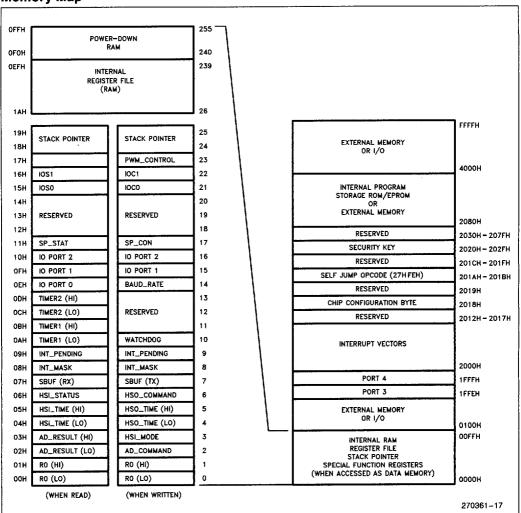

# **Memory Map**

## **ELECTRICAL CHARACTERISTICS**

## **ABSOLUTE MAXIMUM RATINGS\*\***

Case Temperature Under Bias... - 40°C to +125°C Storage Temperature .....-60°C to +150°C Voltage from Vpp to Vss or ANGND ..... -0.3V to +13.0V Voltage from Any Other Pin to  $V_{SS}$  or ANGND ...... -0.3V to  $+7.0V^{**}$

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### \*\*NOTE:

This includes VPP on ROM and CPU devices.

# **OPERATING CONDITIONS**

| Symbol           | Parameter                   | Min  | Max   | Units |

|------------------|-----------------------------|------|-------|-------|

| T <sub>C</sub>   | Case Temperature Under Bias | -40  | + 125 | °C    |

| V <sub>CC</sub>  | Digital Supply Voltage      | 4.50 | 5.50  | ٧     |

| V <sub>REF</sub> | Analog Supply Voltage       | 4.50 | 5.50  | ٧     |

| Fosc             | Oscillator Frequency        | 6.0  | 12.0  | MHz   |

| V <sub>PD</sub>  | Power Down Supply Voltage   | 4.50 | 5.50  | ٧     |

ANGND and VSS should be nominally at the same potential.

# **DC CHARACTERISTICS** Test Conditions: $V_{CC}$ , $V_{REF}$ , $V_{PD}$ , $V_{PP}$ , $V_{SS} = 5.0V \pm 0.5V$ ;

$E_{OCO} = 6.0 \text{ MHz}$  to 12.0 MHz:  $T_{O} = -40^{\circ}\text{C}$  to  $\pm 125^{\circ}\text{C}$ : Vec. ANGND = 0V

| Symbol           | Parameter                                                  | Min   | Max                   | Units | <b>Test Conditions</b>               |

|------------------|------------------------------------------------------------|-------|-----------------------|-------|--------------------------------------|

| lcc              | V <sub>CC</sub> Supply Current (-40°C ≤ +125°C Case)       |       | 240                   | mΑ    | All Outputs                          |

| I <sub>CC1</sub> | V <sub>CC</sub> Supply Current (T <sub>C</sub> = +125°C)   |       | 155                   | mΑ    | Disconnected                         |

| l <sub>PD</sub>  | V <sub>PD</sub> Supply Current                             |       | 1                     | mA    | Normal Operation<br>and Power Down   |

| REF              | V <sub>REF</sub> Supply Current                            |       | 10                    | mA    |                                      |

| V <sub>IL</sub>  | Input Low Voltage (Except RESET)                           | -0.3  | +0.8                  | ٧     |                                      |

| V <sub>IL1</sub> | Input Low Voltage, RESET                                   | -0.3  | + 0.8                 | ٧     |                                      |

| V <sub>IH</sub>  | Input High Voltage (Except RESET, NMI, XTAL1)              | 2.0   | $V_{CC} + 0.5$        | ٧     |                                      |

| V <sub>IH1</sub> | Input High Voltage, RESET Rising                           | 2.4   | V <sub>CC</sub> + 0.5 | ٧     |                                      |

| V <sub>IH2</sub> | Input High Voltage, RESET Falling Hysteresis               | 2.1   | $V_{CC} + 0.5$        | ٧     |                                      |

| V <sub>IH3</sub> | Input High Voltage, NMI, XTAL1                             | 2.3   | V <sub>CC</sub> + 0.5 | ٧     |                                      |

| ILI              | Input Leakage Current, All HSI, P3, P4 and P2.1.           |       | ±10                   | μΑ    | $V_{IN} = 0$ to $V_{CC}$             |

| I <sub>LI1</sub> | DC Input Leakage Current, All P0                           |       | +3                    | μΑ    | $V_{IN} = 0$ to $V_{CC}$             |

| ΊΗ               | Input High Current to EA                                   |       | 100                   | μΑ    | $V_{\rm IH}=2.4V$                    |

| ΙιL              | Input Low Current, All P1, P2.6 and P2.7.                  |       | - 150                 | μΑ    | $V_{IL} = 0.45V$                     |

| l <sub>IL1</sub> | Input Low Current to RESET                                 | -0.25 | -2                    | mA    | V <sub>IL</sub> = 0.45V              |

| l <sub>IL2</sub> | Input Low Current P2.2, P2.3, P2.4, READY, BUSWIDTH        |       | -50                   | μΑ    | V <sub>IL</sub> = 0.45V              |

| V <sub>OL</sub>  | Output Low Voltage,<br>All Quasi-Bidirectional I/O, P3, P4 |       | 0.45                  | ٧     | I <sub>OL</sub> = 0.8 mA<br>(Note 1) |

**DC CHARACTERISTICS** Test Conditions:  $V_{CC}$ ,  $V_{REF}$ ,  $V_{PD}$ ,  $V_{PP}$ ,  $V_{SS} = 5.0 V \pm 0.5 V$ ;  $F_{OSC} = 6.0 \text{ MHz}$  to 12.0 MHz;  $T_C = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ;  $V_{SS}$ , ANGND = 0V (Continued)

| Symbol                          | Parameter                                                  | Min | Max  | Units | Test Conditions                             |

|---------------------------------|------------------------------------------------------------|-----|------|-------|---------------------------------------------|

| V <sub>OL1</sub> <sup>(4)</sup> | Output Low Voltage,<br>All Quasi-Bidirectional I/O, P3, P4 |     | 0.75 | ٧     | I <sub>OL</sub> = 2.0 mA<br>(Notes 1, 2, 3) |

| V <sub>OL2</sub>                | Output Low Voltage on Standard I/O<br>Bus, Control Pins    |     | 0.45 | ٧     | I <sub>OL</sub> = 2.0 mA<br>(Notes 2, 3)    |

| V <sub>OH</sub>                 | Output High Voltage on<br>Quasi-Bidirectional I/O          | 2.4 |      | ٧     | l <sub>OH</sub> = -20 μA<br>(Note 1)        |

| V <sub>OH1</sub>                | Output High Voltage on Standard I/O<br>Bus, Control Pins   | 2.4 |      | ٧     | I <sub>OH</sub> = −200 μA<br>(Note 1)       |

| I <sub>ОНЗ</sub>                | Output High Current on RESET                               | -50 |      | μΑ    | V <sub>OH</sub> = 2.4V (Note 4)             |

| CS                              | Pin Capacitance (Any Pin to V <sub>SS</sub> )              |     | 10   | pF    | F <sub>TEST</sub> = 1.0 MHz (Note 4)        |

#### NOTES:

- 1. Quasi-bidirectional pins include those on P1, P2.6 and P2.7. Standard Output Pins include TXD, RXD (Mode 0 only), PWM, and HSO pins. Bus/Control pins include CLKOUT, ALE, BHE, RD, WR, INST and AD0-15.

- 2. Maximum current per pin must be externally limited to the following values if VOL is held above 0.45V.

IOL on quasi-bidirectional pins: 4.0 mA

IOL on standard output pins and RESET: 8.0 mA

IOL on Bus/Control pins: 2.0 mA

$I_{OL}$  on HSO.0, HSO.4, HSO.5 = 1.6 mA: @  $V_{OL}$  = 0.5V

3. During normal (non-transient) operation the following limits apply:

Total IOI on Port 1 must not exceed 4.0 mA.

Total IOL on P2.0, P2.6, RESET and all HSO pins must not exceed 17.0 mA.

Total IOI on P2.5, P2.7 must not exceed 4.0 mA.

4. These values are not tested in production, and are based on theoretical estimates and/or laboratory tests.

## **AC CHARACTERISTICS**

$V_{CC}$ ,  $V_{PD} = 5.0V \pm 0.5V$ ;  $T_{C} = -40^{\circ}C$  to  $+125^{\circ}C$ ;  $F_{OSC} = 6.0$  MHz to 12.0 MHz

Test Conditions: Load Capacitance on Output Pins = 80 pF

Oscillator Frequency = 12 MHz

## TIMING REQUIREMENTS (Other system components must meet these specifications)

| Symbol                | Parameter                         | Min                     | Max                      | Units |

|-----------------------|-----------------------------------|-------------------------|--------------------------|-------|

| T <sub>CLYX</sub>     | RÉADY Hold after CLKOUT Edge      | 0                       |                          | ns    |

| TLLYV                 | End of ALE/ADV to READY Valid     |                         | 2 T <sub>OSC</sub> - 70  | ns    |

| T <sub>LLYH</sub>     | End of ALE/ADV to READY High      | 2 T <sub>OSC</sub> + 40 | 4 T <sub>OSC</sub> - 80  | ns    |

| T <sub>YLYH</sub>     | Non-Ready Time                    |                         | 1000                     | ns    |

| T <sub>AVDV</sub> (1) | Address Valid to Input Data Valid | ·                       | 5 T <sub>OSC</sub> — 120 | ns    |

| T <sub>RLDV</sub>     | RD Active to Input Data Valid     |                         | 3 T <sub>OSC</sub> - 100 | ns    |

| T <sub>RHDX</sub>     | Data Hold after RD Inactive       | 0                       |                          | ns    |

| T <sub>RHDZ</sub>     | RD Inactive to Input Data Float   | . 0                     | T <sub>OSC</sub> - 25    | ns    |

| T <sub>AVGV</sub> (1) | Address Valid to BUSWIDTH Valid   |                         | 2 T <sub>OSC</sub> - 125 | ns    |

| T <sub>LLGX</sub>     | BUSWIDTH Hold after ALE/ADV Low   | T <sub>OSC</sub> + 40   |                          | ns    |

| TLLGV                 | ALE/ADV Low to BUSWIDTH Valid     |                         | T <sub>OSC</sub> - 95    | ns    |

1. The term "Address Valid" applies to AD0-AD15, BHE and INST.

# AC CHARACTERISTICS (Continued)

TIMING RESPONSES (MCS 96 parts meet these specifications)

| Symbol                | Parameter                                 | Min                      | Max                                  | Units |

|-----------------------|-------------------------------------------|--------------------------|--------------------------------------|-------|

| F <sub>XTAL</sub>     | Oscillator Frequency                      | 6.0                      | 12.0                                 | MHz   |

| Tosc                  | Oscillator Period                         | 83                       | 166                                  | ns    |

| Тонсн                 | XTAL1 Rising Edge to Clockout Rising Edge | 0                        | 120                                  | ns    |

| T <sub>CHCH</sub>     | CLKOUT Period <sup>(1)</sup>              | 3 T <sub>OSC</sub> (1)   | 3 T <sub>OSC</sub> (1) .             | ns    |

| T <sub>CHCL</sub>     | CLKOUT High Time                          | T <sub>OSC</sub> - 35    | T <sub>OSC</sub> + 10                | ns    |

| T <sub>CLLH</sub>     | LLH CLKOUT Low to ALE High -3             |                          | . 15                                 | ns    |

| TLLCH                 |                                           |                          | T <sub>OSC</sub> + 45                | ns    |

| T <sub>LHLL</sub>     | ALE/ADV High Time                         | T <sub>OSC</sub> - 30    | T <sub>OSC</sub> + 35(2)             | ns    |

| T <sub>AVLL</sub> (3) | Address Setup to End of ALE/ADV           | T <sub>OSC</sub> - 50    |                                      | ns    |

| T <sub>RLAZ</sub> (4) | RD or WR Low to Address Float             |                          | 10 <sup>(5)</sup>                    | ns    |

| T <sub>LLRL</sub>     | End of ALE/ADV to RD or WR Active         | T <sub>OSC</sub> - 40    |                                      | ns    |

| T <sub>LLAX</sub>     | Address Hold after End of ALE/ADV         | T <sub>OSC</sub> - 40    |                                      | ns    |

| T <sub>WLWH</sub>     | WR Pulse Width                            | 3 T <sub>OSC</sub> — 35  |                                      | ns    |

| TQVWH                 | Output Data Valid to End of WR/WRL/WRH    | 3 T <sub>OSC</sub> 60    |                                      | ns    |

| T <sub>WHQX</sub>     | Output Data Hold after WR/WRL/WRH         | T <sub>OSC</sub> - 50    |                                      | ns    |

| T <sub>WHLH</sub>     | End of WR/WRL/WRH to ALE/ADV High         | T <sub>OSC</sub> - 75    |                                      | ns    |

| T <sub>RLRH</sub>     | RD Pulse Width                            | 3 T <sub>OSC</sub> - 30  |                                      | ns    |

| TRHLH                 | End of RD to ALE/ADV High                 | T <sub>OSC</sub> - 45    |                                      | ns    |

| T <sub>CLLL</sub>     | CLOCKOUT Low to ALE/ADV Low               | T <sub>OSC</sub> - 40(5) | T <sub>OSC</sub> + 35 <sup>(5)</sup> | ns    |

| T <sub>RHBX</sub>     | RD High to INST, BHE, AD0-15 Inactive     | T <sub>OSC</sub> - 25    | T <sub>OSC</sub> + 30                | ns    |

| T <sub>WHBX</sub>     | WR High to INST, BHE, AD0-15 Inactive     | T <sub>OSC</sub> - 50    | T <sub>OSC</sub> + 100               | ns    |

| THLHH                 | WRL, WRH Low to WRL, WRH High             | 2 T <sub>OSC</sub> - 35  | 2 T <sub>OSC</sub> + 40              | ns    |

| TLLHL                 | ALE/ADV Low to WRL, WRH Low               | 2 T <sub>OSC</sub> - 30  | 2 T <sub>OSC</sub> + 55              | ns    |

| TQVHL                 | Output Data Valid to WRL, WRH Low         | T <sub>OSC</sub> - 60    |                                      | ns    |

## NOTES:

- 1. CLKOUT is directly generated as a divide by 3 of the oscillator. The period will be 3 Tosc ± 10 ns if Tosc is constant and the rise and fall times on XTAL1 are less than 10 ns.

- 2. Max spec applies only to ALE. Min spec applies to both ALE and ADV.

- 3. The term "Address" in this definition applies to AD0-15, BHE and INST.

4. The term "Address" in this definition applies to AD0-7 for 8-bit cycles, and AD0-15 for 16-bit cycles.

- 5. Typical values.

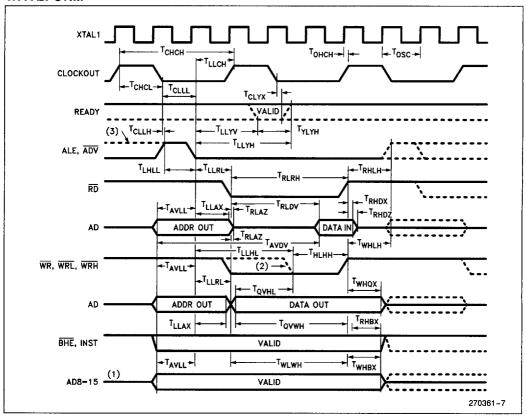

# **WAVEFORM**

## NOTES:

- 1. 8-bit bus only.

- 2. When write strobe mode selected.

- 3. When ADV selected.

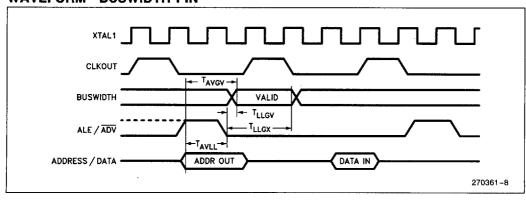

# **WAVEFORM—BUSWIDTH PIN**

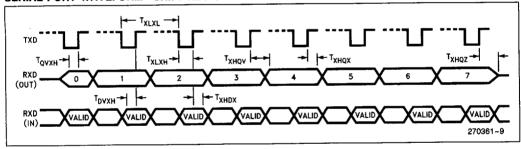

# AC CHARACTERISTICS—SERIAL PORT—SHIFT REGISTER MODE

# SERIAL PORT TIMING-SHIFT REGISTER MODE

Test Conditions:  $T_C = -40^{\circ}C$  to  $+125^{\circ}C$ ;  $V_{CC} = 5V \pm 10\%$ ;  $V_{SS} = 0V$ ; Load Capacitance = 80 pF

| Symbol            | Parameter                                      | Min                      | Max                     | Units |

|-------------------|------------------------------------------------|--------------------------|-------------------------|-------|

| T <sub>XLXL</sub> | Serial Port Clock Period                       | 8 Tosc                   |                         | ns    |

| T <sub>XLXH</sub> | Serial Port Clock Falling Edge to Rising Edge  | 4 T <sub>OSC</sub> - 50  | 4 T <sub>OSC</sub> + 50 | ns    |

| TovxH             | Output Data Setup to Clock Rising Edge         | 3 Tosc                   |                         | ns    |

| TXHQX             | Output Data Hold After Clock Rising Edge       | 2 T <sub>OSC</sub> - 70  |                         | ns    |

| T <sub>XHQV</sub> | Next Output Data Valid After Clock Rising Edge |                          | 2 T <sub>OSC</sub> + 50 | ns    |

| T <sub>DVXH</sub> | Input Data Setup to Clock Rising Edge          | 2 T <sub>OSC</sub> + 200 |                         | ns    |

| T <sub>XHDX</sub> | Input Data Hold After Clock Rising Edge        | 0                        |                         | ns    |

| T <sub>XHQZ</sub> | Last Clock Rising to Output Float              |                          | 5 Tosc                  | ns    |

# WAVEFORM-SERIAL PORT-SHIFT REGISTER MODE

# SERIAL PORT WAVEFORM-SHIFT REGISTER MODE

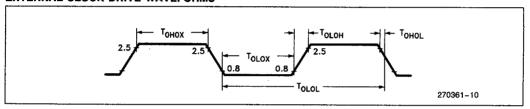

# **EXTERNAL CLOCK DRIVE**

| Symbol              | Parameter            | Min | Max  | Units |

|---------------------|----------------------|-----|------|-------|

| 1/T <sub>OLOL</sub> | Oscillator Frequency | 6   | 12   | MHz   |

| T <sub>OHOX</sub>   | High Time            | 30  |      | ns    |

| T <sub>OLOX</sub>   | Low Time             | 30  |      | ns    |

| T <sub>OLOH</sub>   | Rise Time            |     | . 15 | ns    |

| TOHOL               | Fall Time            |     | 15   | ns    |

## **EXTERNAL CLOCK DRIVE WAVEFORMS**

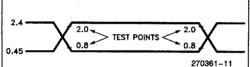

### AC TESTING INPUT, OUTPUT WAVEFORMS

AC Testing inputs are driven at 2.4V for a Logic "1" and 0.45V for a Logic "0". Timing measurements are made at 2.0V for a Logic "1" and 0.8V for a Logic "0".

#### **FLOAT WAVEFORMS**

For timing purposes a port pin is no longer floating when a 200 mV change from load voltage occurs, and begins to float when a 200 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs  $|_{\rm OL}/|_{\rm OH} \ge \pm 8$  mA.

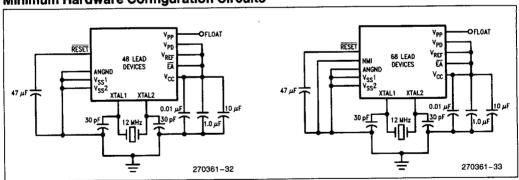

**Minimum Hardware Configuration Circuits**

# A/D CONVERTER SPECIFICATIONS

The absolute conversion accuracy is dependent on the accuracy of VREF. The specifications given below assume adherence to the Operating Conditions section of this datasheet. Testing is done at V<sub>RFF</sub> = 5.120V.

## **OPERATING CONDITIONS**

| V <sub>CC</sub> , V <sub>PD</sub> , V <sub>REF</sub> | 5.0V ±0.25V     |

|------------------------------------------------------|-----------------|

| V <sub>SS</sub> , ANGND                              |                 |

| T <sub>C</sub>                                       | -40°C to +125°C |

| F <sub>OSC</sub>                                     | 6.0 to 12.0 MHz |

| Test Conditions:                                     |                 |

| V <sub>REF</sub>                                     |                 |

| V <sub>CC</sub>                                      | 5.0V            |

| Parameter                                                                       | Typical*(1)             | Minimum                  | Maximum                  | Units**                    | Notes       |

|---------------------------------------------------------------------------------|-------------------------|--------------------------|--------------------------|----------------------------|-------------|

| Resolution                                                                      |                         | 1024<br>10               | 1024<br>10               | Levels<br>Bits             |             |

| Absolute Error                                                                  |                         | 0                        | ±4                       | LSBs                       |             |

| Full Scale Error                                                                | -0.5 ±0.5               |                          |                          | LSBs                       |             |

| Zero Offset Error                                                               | ±0.5                    |                          |                          | LSBs                       |             |

| Non-Linearity                                                                   |                         |                          | ±4                       | LSBs                       |             |

| Differential Non-Linearity                                                      |                         | 0                        | ±2                       | LSBs                       |             |

| Channel-to-Channel Matching                                                     |                         | 0                        | ±1                       | LSBs                       |             |

| Repeatability                                                                   | ± 0.25                  | 0                        |                          | LSBs                       | 1           |

| Temperature Coefficients:<br>Offset<br>Full Scale<br>Differential Non-Linearity | 0.009<br>0.009<br>0.009 |                          |                          | LSB/°C<br>LSB/°C<br>LSB/°C | 1<br>1<br>1 |

| Off Isolation                                                                   |                         | -60                      |                          | dB                         | 1, 2, 4     |

| Feedthrough                                                                     | -60                     |                          |                          | dB                         | 1, 2        |

| V <sub>CC</sub> Power Supply Rejection                                          | -60                     |                          |                          | dB                         | 1, 2        |

| Input Resistance                                                                |                         | 1K                       | 5K                       | Ω                          | 1           |

| DC Input Leakage                                                                |                         | 0                        | 3.0                      | μА                         |             |

| Sample Delay                                                                    |                         | 3 T <sub>OSC</sub> — 50  | 3 T <sub>OSC</sub> + 50  | ns                         | 1, 3        |

| Sample Time                                                                     |                         | 12 T <sub>OSC</sub> - 50 | 12 T <sub>OSC</sub> + 50 | ns                         | 1           |

| Sample Capacitance                                                              |                         |                          | 2                        | pF                         |             |

### NOTES:

- \* These values are expected for most parts at 25°C.

- \*\* An "LSB", as used here, is defined in the glossary which follows and has a value of approximately 5 mV.

- 1. These values are not tested in production and are based on theoretical estimates and laboratory tests.

- 2. DC to 100 KHz.

- 3. For starting the A/D with an HSO Command.

- 4. Multiplexer Break-Before-Make Guaranteed.

# **EPROM SPECIFICATIONS**

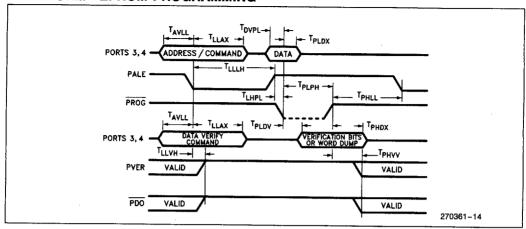

# AC EPROM PROGRAMMING CHARACTERISTICS

Operating Conditions: Load Capacitance = 150 pF,  $T_C = 25^{\circ}C$ ,  $\pm 5^{\circ}C$ ,  $V_{CC}$ ,  $V_{PD}$ ,  $V_{REF} = 5.0V \pm 0.5V$ ,  $V_{SS}$ , ANGND = 0V,  $V_{PP} = 12.75V \pm 0.25V$ ,  $\overline{EA} = 11V \pm 2.0V$ ,  $F_{OSC} = 6.0$  MHz

| Symbol            | Parameter                                | Min                  | Max                              | Units |

|-------------------|------------------------------------------|----------------------|----------------------------------|-------|

| TAVLL             | ADDRESS/COMMAND Valid to PALE Low        | 0                    |                                  | Tosc  |

| T <sub>LLAX</sub> | ADDRESS/COMMAND Hold After PALE Low      | 80                   |                                  | Tosc  |

| T <sub>DVPL</sub> | Output Data Setup Before PROG Low        | 0                    |                                  | Tosc  |

| T <sub>PLDX</sub> | Data Hold After PROG Falling             | 80                   |                                  | Tosc  |

| TLLLH             | PALE Pulse Width                         | 180                  |                                  | Tosc  |

| T <sub>PLPH</sub> | PROG Pulse Width                         | 250 T <sub>OSC</sub> | 100 μs +<br>144 T <sub>OSC</sub> |       |

| T <sub>LHPL</sub> | PALE High to PROG Low                    | 250                  |                                  | TOSC  |

| T <sub>PHLL</sub> | PROG High to Next PALE Low               | 600                  |                                  | Tosc  |

| T <sub>PHDX</sub> | Data Hold After PROG High                | 30                   |                                  | Tosc  |

| T <sub>PHVV</sub> | PROG High to PVER/PDO Valid              | 500                  |                                  | Tosc  |

| TLLVH             | PALE Low to PVER/PDO High                | 100                  |                                  | Tosc  |

| T <sub>PLDV</sub> | PROG Low to VERIFICATION/DUMP Data Valid | 100                  |                                  | Tosc  |

| TSHLL             | RESET High to First PALE Low (not shown) | 2000                 |                                  | Tosc  |

Run-time programming is done with F<sub>OSC</sub> = 6.0 MHz to 12.0 MHz,  $V_{CC}$ ,  $V_{PD}$ ,  $V_{REF}$  = 5V  $\pm 0.5$ V,  $T_{C}$  = 25°C  $\pm 5$ °C and  $V_{PP} = 12.75V \pm 0.25V$ . For run-time programming over a full operating range, contact the factory.

# DC EPROM PROGRAMMING CHARACTERISTICS

| [ | Symbol | Parameter                                             | Min | Max | Units |

|---|--------|-------------------------------------------------------|-----|-----|-------|

|   | lpp    | V <sub>PP</sub> Supply Current (Whenever Programming) |     | 100 | mA    |

Vpp must be within 1V of  $V_{CC}$  while  $V_{CC} < 4.5V$ .  $V_{PP}$  must not have a low impedance path to ground or  $V_{SS}$  while  $V_{CC} > 4.5V$ .

# WAVEFORM—EPROM PROGRAMMING

Reserved location warning: Intel Reserved addresses can not be used by applications which use 8X9XBH internal ROM/EPROM. The data read from a reserved location is not guaranteed, and a write to any reserved location could cause unpredictable results. When attempting to program Intel Reserved addresses, the data must be 0FFFFH to ensure a harmless result. A memory map indicating reserved locations on the 8X9XBH is shown in Figure 2.

Intel Reserved locations, when mapped to external memory, must be filled with 0FFFFH to ensure compatibility with future devices.

# POWER SUPPLY SEQUENCE WHILE PROGRAMMING

For any 879XBH that is in any programming mode, high voltages must be applied to the device. To avoid damaging the devices, the following rules must not be violated.

RULE #1-VPP must not have a low impedance path to ground when V<sub>CC</sub> is above 4.5V.

RULE #2--- V<sub>CC</sub> must be above 4.5V before V<sub>PP</sub> can be higher than 5.0V.

RULE #3—  $V_{PP}$  must be within 1V of  $V_{CC}$  while  $V_{CC}$ is below 4.5V.

RULE #4--- All voltages must be within tolerance and the oscillator stable before RESET rises.

RULE #5-EA must be brought high to place the devices in programming mode before Vpp is brought high.

To adhere to these rules, the following power up and power down sequences can be followed.

#### POWER UP

RESET = 0:

CLOCK ON; if using an external clock ; instead of an oscillator

$V_{CC} = V_{PP} = V_{EA} = 5V;$

PALE = PROG = PORT 34 = VIH;\*

SID AND PMODE VALID:

$\overline{EA} = 12.75V$ :

$V_{PP} = 12.75V;$

WAIT; wait for supplies and clock to ; settle

RESET = 5V:

WAIT Tshil; See datasheet

BEGIN:

### POWER DOWN

RESET = 0:

$V_{PP} = 5V;$

$\overline{EA} = 5V$ :

$PALE = \overline{PROG} = SID = PMODE = PORT34 =$ OV:

$V_{CC} = V_{PP} = V_{FA} = 0V$ ;

CLOCK OFF:

#### NOTE:

\*VIH = Logical "1", 2.4V Minimum

One final note on power up, power down. The maximum limit on V<sub>PP</sub> must never be violated, even for an instant. Therefore, an RC rise to the desired VPP is recommended. VPP is also sensitive to instantaneous voltage steps. This also can be avoided by using an RC ramp on Vpp.

## ADDITIONAL INFORMATION

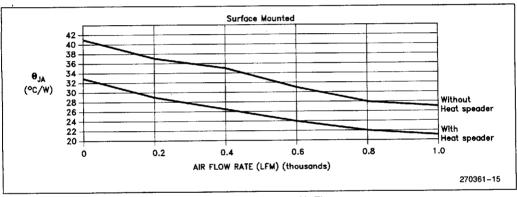

MCS-96 Thermal Characteristics

| Package                             | θ <sub>JA</sub><br>(°C/W) | θJC<br>(°C/W) |

|-------------------------------------|---------------------------|---------------|

| 68-Lead Plastic Leaded Chip Carrier | 36                        | 13.4          |

| 68-Lead Plastic Flatpack            | 36                        | 13.4          |

#### **NOTES:**

$\theta_{JA}$  = Thermal resistance between junction and the surrounding environment (ambient). Measurements are taken 1 ft. away from case in air flow environment.

$\theta_{\rm JC}$  = Thermal resistance between junction and package surface (case).

All values of  $\theta_{JA}$  and  $\theta_{JC}$  may fluctuate depending on the environment (with or without airflow, and how much air flow) and device power dissipation at temperature of operation. Typical variations are  $\pm 2^{\circ}$ C/W.

The graph below shows a typical  $\theta_{JA}$  vs. Air Flow rate for a PLCC package (with and without a heat speader).

Figure 7.  $\theta_{JA}$  vs Linear Air Flow

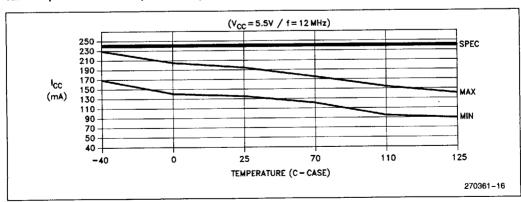

Figure 8 is an  $I_{CC}$  vs. temperature plot for the 8X9XBH products. Test conditions are stated and actuals may vary depending on speed, package,  $V_{CC}$  and temperature, but will not exceed maximum limit specified at any case temperature between specified temperature limits.

Figure 8. 8X9XBH I<sub>CC</sub> vs TEMP

## **FUNCTIONAL DEVIATIONS**

The following is a list of all known functional deviations for 8X9XBH devices.

# **CPU Section**

### 1. Indexed, 3 Operand Multiply (Note C. D. E)

In a three word multiply (MUL, MULB, MULU, MULUB) using indexed addressing mode, the displacement portion may not be in the range of 200H through 17FFH, inclusive. If the displacements in this range are necessary, the use of a two operand indexed multiply can be used with a move.

## 2. JBS and JBC Directly with Port Pins (Note C)

The JBS and JBC instructions when used directly with Port 2.1 or all pins of Port 0 cannot be used. If testing of these port pins is necessary, shadow the entire port data in a RAM register and test the bit in that RAM register.

# 3. BUSWIDTH and 8-Bit Bus (Note C)

If the BUSWIDTH pin is pulled high externally, or left to float, the internal pullup will pull this pin high. A high condition on this input equates to a 16-bit bus mode externally. During the CHIP CON-FIGURATION BYTE fetch cycle, the port circuitry changes the CCB address about 25 ns after RD goes low. If the CCB being read is trying to configure an 8-bit bus, the upper address lines (AD8-AD15) will NOT be latched during the CCB read. Therefore, if the read from the CCR (2018H) is in a x8 address space, the BUSWIDTH pin MUST be held low for this fetch, or the address lines AD8-AD15 must be latched (via a latched external EPROM or TTL latch).

## 4. FIFO/HSI Status Cleared (Note C, D)

It is possible to have a time value in the FIFO with no status bits set in the HSI\_STATUS register. When events are logged, the first event is loaded into the Holding Register, the next is loaded into slot #1 of the FIFO, the next in slot #2, etc. If the Holding Register is read after the #2 slot is loaded, the #1 slot will be moved into the Holding Register to be read next. If another event is logged, it will be placed in slot #3, not #1 (the one just vacated). There are 7 slots in the FIFO. If the FIFO is allowed to "roll over", that is a 9th event stored in the #1 slot again, before a cleared FIFO happens, the 9th event will have a valid time with a cleared status bits in the HSI\_ STATUS register (Bits 0, 2, 4 and 6 = 0).

If the HSI\_STATUS register status bits are cleared, there is no way of matching this time with an HSI input pin. It is important to note that in order to avoid this problem both interrupt routines and polling procedures which allow seven entries in the FIFO MUST clear all events from the FIFO before the next event is logged. If this is not possible, events will have cleared status bits and these routines should also handle that case.

To ensure proper operation of the High Speed Input FIFO, it is imperative that no more than seven FIFO entries be placed into an empty FIFO. This includes conditions that enter and clear multiple events but leave one or more entries in the FIFO (i.e., add three entries, read one out, add four more, read one out, is seven entries). All seven must be emptied before allowing further events to occur at the pins. The FIFO is empty even if there is an entry in the Holding Register. (An "event" is defined as a pin transition. An "entry" is defined as one or more pin events loaded into a single FIFO array location.)

Allowing more than seven FIFO entries to occur between cleared conditions will result in incorrect status information for either the eighth or ninth entry. This effectively limits the total number of entries to seven.

There is one exception that will allow the FIFO to correctly record eight entries. If the first two entries of a cleared FIFO and Holding Register are separated by greater than 16 state times, the ninth entry (rather than the eighth entry) will be recorded with incorrect status information. This is true even if the events following the first two entries were only separated by eight states.

# 5. RESET (Note C)

If the XTAL inputs are driven BEFORE V<sub>CC</sub> is stable (between 4.5 V<sub>DC</sub>-5.5 V<sub>DC</sub>), the state machine locks the device into a condition which floats the node in control of the pulldown gate on the RESET pin. The pulldown node will remain on until the floating node loses the stored charge and releases the pulldown. All subsequent RESET's after the Power-on-Reset will operate correctly. Make sure that V<sub>CC</sub> is stable before XTAL is driven.

Since RESET is asynchronous, it is possible to apply RESET during writes to quasi-bidirectional port pins. If this occurs, the QBD port pins may not RESET immediately to a logical one. Instead of the low impedance pullup being turned on, only the high impedance device is on, causing the signals on the QBD pins to rise more slowly than

## 6. Using T2CLK as source for Timer2 (Note C, D)

TIMER2 has two selectable clock sources, the T2CLK or HSI.1 pins, selectable by bit IOC0.3. When using T2CLK as the clock for TIMER2, writing to IOC0 may cause TIMER2 to increment. The user should only write to IOC0 once during initialization, and then immediately clear TIMER2 using the HSO command OEH. Effectively, the customer cannot reset TIMER2 with bit IOC0.1, and can only use the external reset sources or the HSO command when using T2CLK as the clock source. If the HSI.1 pin is the source for TIMER2, only the first write to IOC0 may cause TIMER2 to increment, further writes will not increment TIMER2.

# 7. HSI Resolution (Note E)

The HSI resolution has changed from 8 state times on the BH D-step to 9 state times on the BH E-step. This decreases the maximum HSI input speed from once every 8 state times to once every 9 state times.

### 8. Serial Port Flags (Note E)

Reading SP\_STAT may not clear the TI or RI flag if that flag was set within two state times prior to the read. In addition, the parity error bit (RPE/RB8) may not be correct if it is read within two state times after RI is set.

#### 9. Checksum on Reserved Locations (Note E)

This is a design consideration, not an errata. A test register was added to location 201Ch on the 8X9XBH E-step that controls the readability and writability of certain SFR's during testing. The addition of these bits affects the readability and writability of this reserved location when it is read. If this location is included in a checksum (which it should not), a checksum difference could occur between the E-step and previous steppings. The User Guide states that reserved locations should not be read or written, this statement includes checksum reads also.

# **AUTOMOTIVE 809XBH/839XBH/879XBH**

Note: C = present on C-step devices

D = present on D-step devices

E = present on E-step devices

E-step and later devices can be identified by a special mark following the eight digit FPO number on the top of the package. For E-step devices, this mark is an "E".

### DATASHEET REVISION HISTORY

The following are the key differences between this datasheet and the -005 version:

- The "preliminary" status was dropped and replaced with production status (no label).

- 2. Trademarks were updated.