# High-density power driver - high voltage full bridge with integrated gate driver

Datasheet - production data

#### **Features**

- Power system-in-package integrating gate drivers and high-voltage power MOSFETs

- Low  $R_{DS(on)}$  = 320 m $\Omega$

- BV<sub>DSS</sub> = 600 V

- · Suitable for operating as

- Full bridge

- Dual independent half bridges

- Wide driver supply voltage down to 6.5 V

- UVLO protection on supply voltage

- 3.3 V to 15 V compatible inputs with hysteresis and pull-down

- Interlocking function to prevent cross conduction

- Internal bootstrap diode

- Outputs in phase with inputs

- · Very compact and simplified layout

- Flexible, easy and fast design

#### **Applications**

- Motor drivers for industrial and home appliances

- Factory automation

- Fans and pumps

- HID, ballasts

- Power supply units

- DC-DC and DC-AC converters

#### **Description**

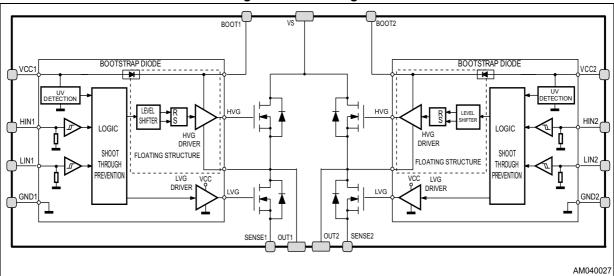

The PWD13F60 is a high-density power driver integrating gate drivers and four N-channel power MOSFETs in dual half bridge configuration.

The integrated power MOSFETs have low  $R_{DS(on)}$  of 320  $m\Omega$  and 600 V drain-source breakdown voltage, while the embedded gate drivers high side can be easily supplied by the integrated bootstrap diode. The high integration of the device allows to efficiently drive loads in a tiny space.

The PWD13F60 device accepts a supply voltage  $(V_{CC})$  extending over a wide range and is protected by means of low-voltage UVLO detection on the supply voltage.

The input pins extended range allows an easy interfacing with microcontrollers, DSP units or Hall effect sensors.

The device is available in a compact VFQFPN package.

# **Contents**

| 1  | Block diagram                                     | 3 |

|----|---------------------------------------------------|---|

| 2  | Pin connection diagram and description            | 4 |

|    | Pin list                                          | 5 |

| 3  | Electrical data                                   | 6 |

|    | 3.1 Absolute maximum ratings                      | ဝ |

|    | 3.2 Recommended operating conditions              | 7 |

|    | 3.3 Thermal data                                  | 7 |

| 4  | Electrical characteristics 8                      | 8 |

|    | 4.1 Driver 8                                      | 8 |

|    | 4.2 Power MOSFET                                  | 9 |

| 5  | Device characterization values                    | ) |

| 6  | Functional description                            | 5 |

|    | 6.1 Logic inputs                                  | 5 |

|    | 6.2 Bootstrap structure                           | 6 |

|    | 6.3 V <sub>CC</sub> supply pins and UVLO function | 3 |

| 7  | Typical application diagram 17                    | 7 |

| 8  | Package information                               | В |

|    | 8.1 VFQFPN 10 x 13 x 1.0 mm package information   | 8 |

| 9  | Suggested footprint                               | 3 |

| 10 | Ordering information                              | 5 |

| 11 | Revision history                                  | 5 |

PWD13F60 Block diagram

# 1 Block diagram

Figure 1. Block diagram

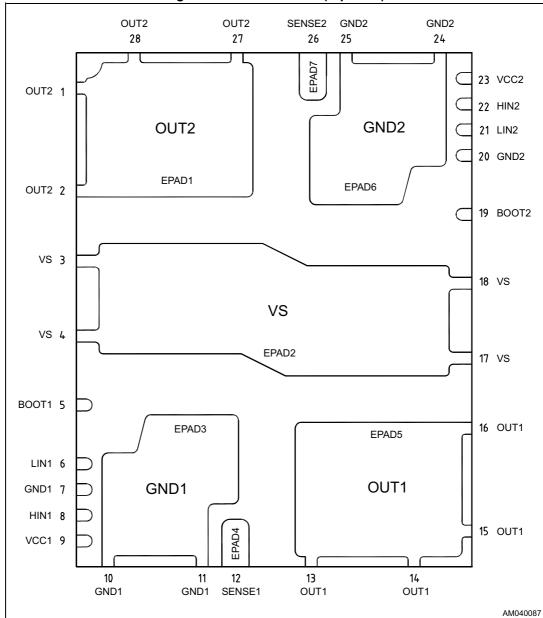

# 2 Pin connection diagram and description

Figure 2. Pin connection (top view)

# Pin list

Table 1. Pin description

|                       | N      |              |                                               |  |  |  |

|-----------------------|--------|--------------|-----------------------------------------------|--|--|--|

| No.                   | Name   | Туре         | Function                                      |  |  |  |

| 3, 4, 17, 18, EPAD2   | VS     | Power supply | High-voltage supply (high side MOSFET drains) |  |  |  |

| 13, 14, 15, 16, EPAD5 | OUT1   | Power output | Half bridge 1 output                          |  |  |  |

| 27, 28, 1, 2, EPAD1   | OUT2   | Power output | Half bridge 2 output                          |  |  |  |

| 12, EPAD4             | SENSE1 | Power supply | Half bridge 1 sense (low side MOSFET source)  |  |  |  |

| 26, EPAD7             | SENSE2 | Power supply | Half bridge 2 sense (low side MOSFET source)  |  |  |  |

| 5                     | BOOT1  | Power supply | Gate driver 1 high side supply voltage        |  |  |  |

| 19                    | BOOT2  | Power supply | Gate driver 2 high side supply voltage        |  |  |  |

| 9                     | VCC1   | Power supply | Gate driver 1 supply voltage                  |  |  |  |

| 23                    | VCC2   | Power supply | Gate driver 2 supply voltage                  |  |  |  |

| 7, 10, 11, EPAD3      | GND1   | Power supply | Gate driver 1 ground                          |  |  |  |

| 20, 24, 25, EPAD6     | GND2   | Power supply | Gate driver 2 ground                          |  |  |  |

| 6                     | LIN1   | Logic input  | Logic input of low side MOSFET 1              |  |  |  |

| 8                     | HIN1   | Logic input  | Logic input of high side MOSFET 1             |  |  |  |

| 21                    | LIN2   | Logic input  | Logic input of low side MOSFET 2              |  |  |  |

| 22                    | HIN2   | Logic input  | Logic input of high side MOSFET 2             |  |  |  |

Electrical data PWD13F60

## 3 Electrical data

## 3.1 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol                              | Parameter                                 | Test condition                                                                   | Value            | Unit |

|-------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------|------------------|------|

| V <sub>DS</sub>                     | MOSFET drain-to-<br>source voltage        | T <sub>J</sub> = 25 °C                                                           | 600              | V    |

| V <sub>CC1</sub> , V <sub>CC2</sub> | Drivers supply voltage                    | -                                                                                | -0.3 to 19       | V    |

| V <sub>CCx-SENSEx</sub>             | VCC to SENSE pin voltage                  | -                                                                                | -0.3 to 19       | V    |

| V <sub>BOOTx</sub>                  | Bootstrap voltage                         | -                                                                                | GNDx -0.3 to 600 | V    |

| V <sub>BO1</sub> , V <sub>BO2</sub> | BOOTx to OUTx pin voltage                 | -                                                                                | -0.3 to 19       | V    |

|                                     |                                           | DC at T <sub>CB</sub> = 25 °C <sup>(1)</sup>                                     | 8                | Α    |

| I <sub>D</sub>                      | Drain current (per MOSFET)                | DC at T <sub>CB</sub> = 100 °C <sup>(1)</sup> , <sup>(2)</sup>                   | 6.9              | Α    |

|                                     |                                           | Peak at T <sub>CB</sub> = 25 °C <sup>(1)</sup> , <sup>(2)</sup> , <sup>(3)</sup> | 32               | Α    |

|                                     | Source-drain diode                        | DC at T <sub>CB</sub> = 25 °C <sup>(1)</sup>                                     | 8                | Α    |

| I <sub>SD</sub>                     | current (per diode)                       | Peak at T <sub>CB</sub> = 25 °C <sup>(1)</sup> , <sup>(2)</sup> , <sup>(3)</sup> | 32               | Α    |

| SR <sub>out</sub>                   | Full bridge outputs slew rate (10% - 90%) | (2)                                                                              | 40               | V/ns |

| V <sub>i</sub>                      | Logic inputs voltage range                | -                                                                                | -0.3 to 15       | V    |

| $T_J$                               | Junction temperature                      | -                                                                                | -40 to 150       | °C   |

| T <sub>s</sub>                      | Storage temperature                       | -                                                                                | -40 to 150       | °C   |

| В                                   | Total power                               | T <sub>CB</sub> = 25 °C for each MOSFET                                          | 450              | W    |

| P <sub>tot</sub>                    | dissipation <sup>(4)</sup>                | T <sub>amb</sub> = 25 °C, JEDEC board <sup>(5)</sup> , <sup>(6)</sup>            | 6.9              | W    |

<sup>1.</sup>  $T_{CB}$  is temperature of case bottom pad.

<sup>2.</sup> Characterized, not tested in production.

<sup>3.</sup> The value specified by the design factor, pulse duration limited by max. junction temperature and SOA.

<sup>4.</sup> Value calculated basing on thermal resistance, power uniformly distributed over the four power MOSFETs, still air.

<sup>5.</sup> The device mounted on a FR4 2s2p board as JESD51-5/7.

<sup>6.</sup> Actual applicative board max. dissipation could be higher or lower depending on the layout and cooling techniques.

PWD13F60 Electrical data

# 3.2 Recommended operating conditions

Table 3. Recommended operating conditions

| Symbol                              | Parameter                 | Test condition | Min.               | Max. | Unit |

|-------------------------------------|---------------------------|----------------|--------------------|------|------|

| V <sub>CC1</sub> , V <sub>CC2</sub> | Driver supply voltage     | -              | 6.5 <sup>(1)</sup> | -    | V    |

| V <sub>BO1</sub> , V <sub>BO2</sub> | BOOTx to OUTx pin voltage | -              | 6.5 <sup>(1)</sup> | -    | V    |

| VS                                  | High-voltage supply       | -              | -                  | 480  | V    |

| TJ                                  | Junction temperature      | -              | -40                | 125  | °C   |

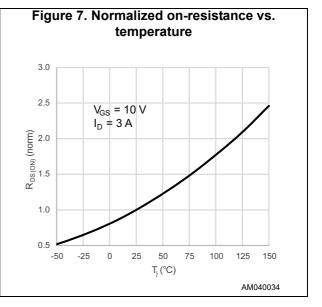

The integrated gate driver can work with V<sub>CC</sub> as low as V<sub>CC\_thON</sub>. Higher supply voltage allows decreasing the MOSFETs R<sub>DS(on)</sub>.

#### 3.3 Thermal data

Table 4. Thermal data

| Symbol                | Parameter                                                    | Value | Unit |

|-----------------------|--------------------------------------------------------------|-------|------|

| R <sub>th(J-CB)</sub> | Thermal resistance junction to each MOSFET exposed pad, typ. | 1.1   | °C/W |

| R <sub>th(J-A)</sub>  | Thermal resistance junction to ambient <sup>(1)</sup>        | 18    | °C/W |

The junction to ambient thermal resistance is obtained simulating the device mounted on a FR4 2s2p board as the JESD51-5/7 with power dissipation uniformly distributed over the four power MOSFETs.

Electrical characteristics PWD13F60

## 4 Electrical characteristics

#### 4.1 Driver

$V_{CCx}$  = 15 V;  $T_J$  = 25 °C, unless otherwise specified.

Table 5. Driver section electrical characteristics

| Symbol                | Parameter                                     | Test condition                                                          | Min. | Тур. | Max. | Unit |  |

|-----------------------|-----------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|--|

| Low supply            | Low supply voltage section                    |                                                                         |      |      |      |      |  |

| V <sub>CC_hys</sub>   | V <sub>CC</sub> UV hysteresis                 | -                                                                       | 0.2  | 0.4  | 0.6  | V    |  |

| V <sub>CC_thON</sub>  | V <sub>CC</sub> UV turn ON threshold          | -                                                                       | 5.7  | 6.1  | 6.5  | V    |  |

| V <sub>CC_thOFF</sub> | V <sub>CC</sub> UV turn OFF threshold         | -                                                                       | 5.3  | 5.7  | 6.1  | V    |  |

| I <sub>qccu</sub>     | Undervoltage quiescent supply current         | V <sub>CC</sub> = 4.5 V                                                 | -    | 140  | 190  | μА   |  |

| I <sub>qcc</sub>      | Quiescent current                             | HINx = GND; LINx = 5 V                                                  | -    | 270  | 350  | μА   |  |

| Bootstrapp            | ed supply voltage section                     |                                                                         | •    |      |      |      |  |

| I <sub>QBO</sub>      | V <sub>BO</sub> quiescent current             | V <sub>BO</sub> = 15 V<br>LINx = GND; HINx = 5 V                        | -    | 60   | 97   | μА   |  |

| I <sub>LK</sub>       | Bootstrap leakage current                     | $V_{OUTx} = V_{BOOTx} = VS = 600 \text{ V};$<br>VCC = LINx = HINx = GND | -    | -    | 1    | μА   |  |

| R <sub>BD(on)</sub>   | Bootstrap driver on-resistance <sup>(1)</sup> | LIN = 5 V                                                               | -    | 120  | -    | Ω    |  |

| Logic input           | s                                             |                                                                         |      |      |      |      |  |

| V <sub>il</sub>       | Logic level low threshold voltage             | -                                                                       | 0.80 | -    | 1.10 | V    |  |

| V <sub>ih</sub>       | Logic level high threshold voltage            | -                                                                       | 1.90 | -    | 2.30 | V    |  |

| I <sub>ih</sub>       | Logic '1' input bias current                  | LINx = HINx = 15 V                                                      | 30   | 40   | 65   | μΑ   |  |

| l <sub>il</sub>       | Logic '0' input bias current                  | LINx = HINx = GND                                                       | -    | -    | 1    | μΑ   |  |

<sup>1.</sup>  $R_{BD(on)}$  is tested in the following way:

$\mathsf{R}_{\mathsf{BD}(\mathsf{on})} = \left[ (\mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{BOOTa}}) - (\mathsf{V}_{\mathsf{CC}} - \mathsf{V}_{\mathsf{BOOTb}}) \right] / \left[ \mathsf{I}_{\mathsf{a}} - \mathsf{I}_{\mathsf{b}} \right]$

Where:  $I_a$  is the BOOT pin current when  $V_{BOOT} = V_{BOOTa}$ ;  $I_b$  is the BOOT pin current when  $V_{BOOT} = V_{BOOTb}$ .

## 4.2 Power MOSFET

$V_{CCx}$  = 15 V;  $T_J$  = 25 °C, unless otherwise specified.

**Table 6. Power MOSFET electrical characteristics**

| Symbol                | Parameter                                       | Test condition                                              | Min. | Тур. | Max.  | Unit |

|-----------------------|-------------------------------------------------|-------------------------------------------------------------|------|------|-------|------|

| MOSFET                | MOSFET on/off states                            |                                                             |      |      |       |      |

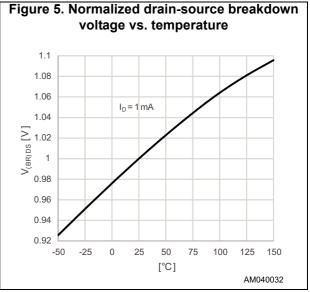

| V <sub>(BR)IDSS</sub> | Drain-source breakdown voltage                  | $I_D = 1 \text{ mA}^{(1)}$                                  | 600  | -    | -     | ٧    |

| I <sub>DSS</sub>      | Zero gate voltage drain current                 | V <sub>DS</sub> = 600 V                                     | -    | -    | 1     | μA   |

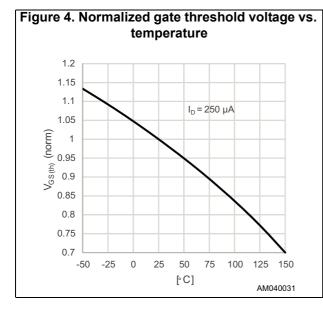

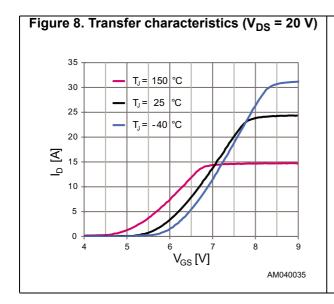

| V <sub>GS(th)</sub>   | Gate threshold voltage                          | $V_{DS} = V_{GS}, I_D = 250 \mu A^{(1)}$                    | 3    | 4    | 5     | V    |

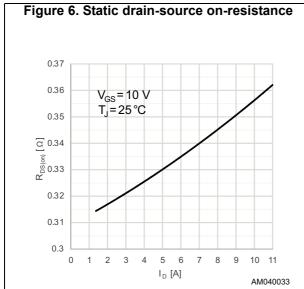

| R <sub>DS(on)</sub>   | Static drain-source on-<br>resistance           | I <sub>D</sub> = 3 A; V <sub>GS</sub> = 10 V                | -    | 0.32 | 0.425 | Ω    |

| MOSFET                | avalanche                                       |                                                             |      |      |       |      |

| I <sub>AS</sub>       | Avalanche current, repetitive or not repetitive | Pulse width limited by T <sub>J</sub> max. <sup>(1)</sup>   | -    | -    | 3     | А    |

| E <sub>AS</sub>       | Single pulse avalanche energy                   | Starting $T_J = 25$ °C, $I_D = I_{AS}$ , VDD = 50 $V^{(1)}$ | -    | -    | 162   | mJ   |

| Source-drain diode    |                                                 |                                                             |      |      |       |      |

| V <sub>SD</sub>       | Diode forward on voltage                        | LINx = GND;<br>HINx = GND;<br>I <sub>SD</sub> = 3 A         | -    | 0.8  | 1.25  | V    |

<sup>1.</sup> Tested at the wafer level before packaging.

## 5 Device characterization values

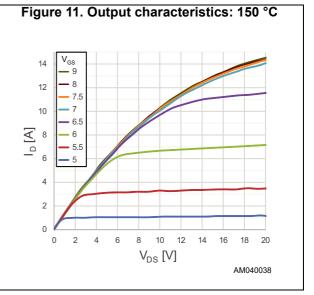

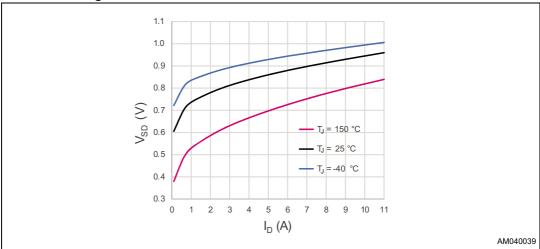

Table 7, Table 8 and electrical characteristics curves (from Figure 4 to Figure 12) contained in this section represent typical values based on characterization and simulation results.

**Table 7. Power MOSFET**

| Symbol             | Parameter                      | Test condition                                                                                  | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| MOSFET dynamic     |                                |                                                                                                 |      |      |      |      |

| Qg                 | Total gate charge              | V <sub>GS</sub> = 10 V, T <sub>J</sub> = 25 °C<br>V <sub>DS</sub> = 480 V, I <sub>D</sub> = 3 A | -    | 26   | -    | nC   |

| Source-drain diode |                                |                                                                                                 |      |      |      |      |

| t <sub>rr</sub>    | Diode reverse recovery time    | I <sub>SD</sub> = 3 A,                                                                          | -    | 93   | -    | ns   |

| Q <sub>rr</sub>    | Diode reverse recovery charge  | VS = 100 V,                                                                                     | -    | 376  | -    | nC   |

| I <sub>RRM</sub>   | Diode reverse recovery current | di/dt = 100 A/μs, T <sub>J</sub> = 25 °C                                                        | -    | 8.1  | -    | Α    |

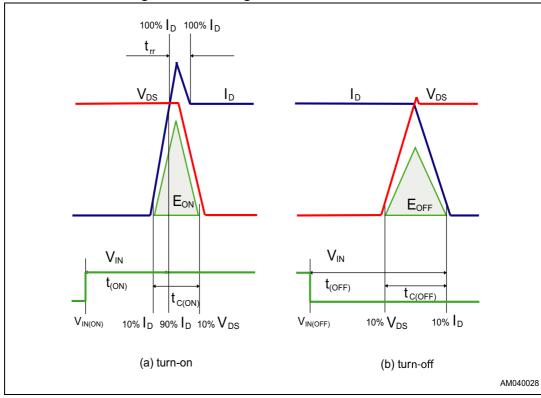

Table 8. Inductive load switching characteristics

| Symbol                             | Parameter                   | Test condition                                                                           | Min. | Тур. | Max. | Unit |

|------------------------------------|-----------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>(on)</sub> <sup>(1)</sup>   | Turn-on time                |                                                                                          | -    | 280  | -    | ns   |

| $t_{C(on)}^{(2)}$                  | Crossover time (on)         |                                                                                          | -    | 75   | -    | ns   |

| t <sub>(off)</sub> <sup>(1)</sup>  | Turn-off time               | VS = 300 V,                                                                              | -    | 360  | -    | ns   |

| t <sub>C(off)</sub> <sup>(2)</sup> | Crossover time (off)        | $V_{CC} = V_{BO} = 15 \text{ V},$<br>$I_{OUT} = 3 \text{ A}, T_J = 25 ^{\circ}\text{C},$ | -    | 105  | -    | ns   |

| E <sub>on</sub>                    | Turn-on switching losses    | see Figure 3                                                                             | -    | 115  | -    | μJ   |

| E <sub>off</sub>                   | Turn-off switching losses   |                                                                                          | -    | 35   | -    | μJ   |

| DT                                 | Suggested minimum dead time |                                                                                          | -    | -    | 270  | ns   |

<sup>1.</sup>  $t_{(on)}$  and  $t_{(off)}$  include the propagation delay time of the internal driver.

47/

<sup>2.</sup>  $t_{C(on)}$  and  $t_{C(off)}$  are the switching times of the MOSFET itself under the internally given gate driving conditions.

Figure 3. Switching time and losses definition

12/26 DocID030865 Rev 2

Figure 9. Output characteristics: 25 °C V<sub>GS</sub> 9 24 22 **-** 8 20 **-** 7.5 18 16 **-** 6.5  $\leq$ <del>-</del> 6 14 \_\_\_ 12 **-** 5.5 10 8 6 4 0 2 10 12 16 18  $V_{DS}[V]$ AM040036

Figure 10. Output characteristics: -40 °C 35 **-** 8 **-** 7.5 25 6.5  $\leq$ \_\_ 15 10 5 6 10 12 14 18  $V_{DS}[V]$ AM040037

Figure 12. Static source-drain diode forward characteristics

577

# 6 Functional description

## 6.1 Logic inputs

The PWD13F60 has four logic inputs to independently control the high side and low side internal MOSFETs.

An interlocking feature is offered to avoid undesired simultaneous turn on of of both HS and LS MOSFETs within the same channel (see *Table 9*).

Table 9. Truth table

| HINx | LINx | HSx | LSx |

|------|------|-----|-----|

| 0    | 0    | OFF | OFF |

| 0    | 1    | OFF | ON  |

| 1    | 0    | ON  | OFF |

| 1    | 1    | OFF | OFF |

The logic inputs have internal pull-down resistors. The purpose of these resistors is to pull logic inputs low in case, for example, there is an interruption in the logic lines or the controller outputs are in tri-state condition. In this case the gate driver outputs are set to the low level and the corresponding MOSFETs are turned off.

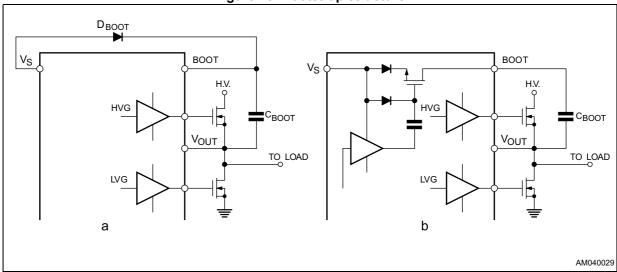

#### 6.2 Bootstrap structure

Bootstrap circuitry is typically used to supply the high-voltage section. This function is normally accomplished by a high-voltage fast recovery diode (see *Figure 13* a).

In the PWD13F60 a patented integrated structure replaces the external diode. It is realized by the series of the low-voltage diode and a high-voltage DMOS, driven synchronously with the low side driver (LVG), as shown in *Figure 13* b. An internal bootstrap provides the DMOS driving voltage. The integrated diode structure is actively turned on and guarantees the best performance when the low side driver is on.

In those applications whose control strategy requires recharging the bootstrap capacitor also when the low side driver is off, the use of an external bootstrap diode in parallel to the integrated structure is possible.

Figure 13. Bootstrap structure

# 6.3 V<sub>CC</sub> supply pins and UVLO function

The VCCx supply pin supplies the current to the low side section of the gate driver as well as to the integrated bootstrap diode used to charge the bootstrap capacitor. During outputs commutations the average current used to provide gate charge to the high side and low side MOSFETs flow through these pins.

The two pins VCC1 and VCC2 separately supply power to the two drivers even if usually are connected together at the power supply in the final application.

The PWD13F60 supply voltages ( $V_{CCx}$ ) are continuously monitored by an undervoltage lockout (UVLO) circuitry that turns the high side and low side MOSFETs off when the supply voltage goes below the  $V_{CC\_thOFF}$  threshold. The UVLO circuitry turns on the MOSFET, accordingly to the LIN and HIN status, as soon as the supply voltage goes above the  $V_{CC\_thON}$  voltage. A  $V_{CC\_hys}$  hysteresis is provided for the noise rejection purpose.

Two separate UVLO circuitries are provided to monitor  $V_{CC1}$  and  $V_{CC2}$ . When a UVLO occurs on a single rail, only the related half bridge MOSFETs are turned off.

16/26 DocID030865 Rev 2

# 7 Typical application diagram

Cbulk BOOT воот2 LIN2 From CONTROLLER From CONTROLLER DRIVER HIN2 From CONTROLLER DRIVER From CONTROLLER HIN1 CVCC1 GND1 SENSE1 SENSE2 To CONTROLLER (e.g. OC protection) Rsense Rsense AM040030

Figure 14. Typical application

Package information PWD13F60

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

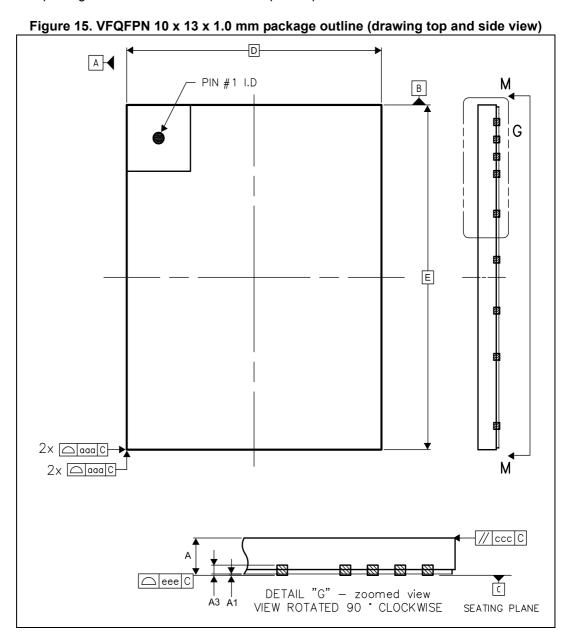

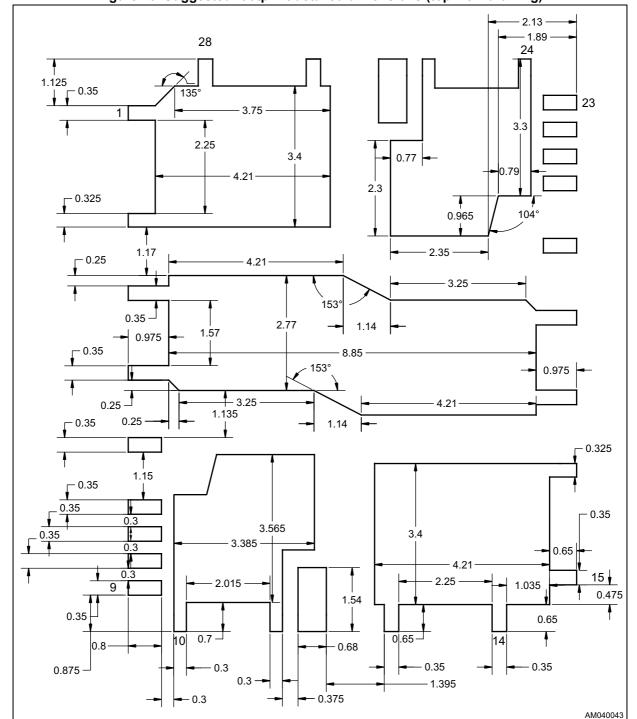

## 8.1 VFQFPN 10 x 13 x 1.0 mm package information

The package outline CAD file is available upon request.

PWD13F60 Package information

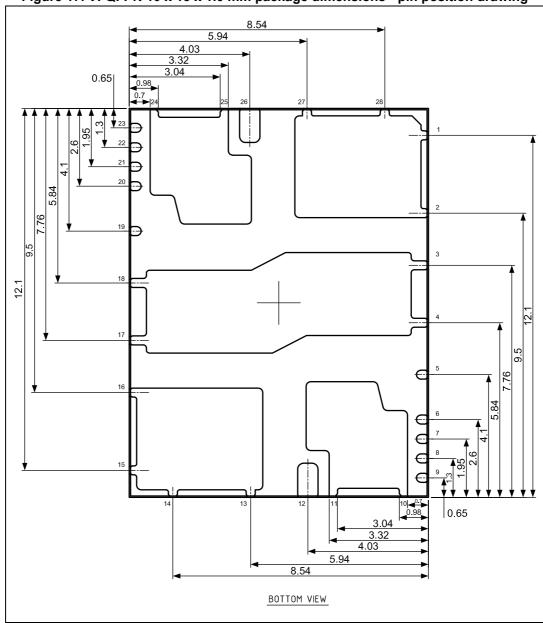

Figure 16. VFQFPN 10 x 13 x 1.0 mm package outline (bottom view drawing)

Package information PWD13F60

Table 10. VFQFPN 10 x 13 x 1.0 mm package mechanical data

| O. walk al       |       | Dimensions (mm) |       |

|------------------|-------|-----------------|-------|

| Symbol           | Min.  | Тур.            | Max.  |

| Α                | 0.80  | 0.85            | 0.90  |

| A1               | 0.00  | -               | 0.05  |

| A3               |       | 0.20            |       |

| b                | 0.15  | 0.25            | 0.35  |

| b1               | 0.20  | 0.30            | 0.40  |

| D                | 9.90  | 10.00           | 10.10 |

| E                | 12.90 | 13.00           | 13.10 |

| D1               |       | 0.70            |       |

| D2               | 2.52  | 2.62            | 2.72  |

| D3               | 3.29  | 3.39            | 3.49  |

| D4               |       | 0.25            |       |

| D5               | 4.12  | 4.22            | 4.32  |

| D6               |       | 0.58            |       |

| D7               | 3.40  | 3.50            | 3.60  |

| D8               | 3.59  | 3.69            | 3.79  |

| D9               |       | 0.68            |       |

| E1               |       | 0.30            |       |

| E2               | 2.50  | 2.60            | 2.70  |

| E3               | 3.47  | 3.57            | 3.67  |

| E4               |       | 0.25            | L     |

| E5               | 3.30  | 3.40            | 3.50  |

| E6               | 2.67  | 2.77            | 2.87  |

| E7               | 1.04  | 1.14            | 1.24  |

| E8               | 0.005 | -               | 0.09  |

| L                | 0.35  | 0.40            | 0.45  |

| е                |       | 0.65            |       |

| e1               |       | 3.45            |       |

| aaa              | 0.10  |                 |       |

| bbb              | 0.10  |                 |       |

| ccc              | 0.10  |                 |       |

| ddd              |       | 0.05            |       |

| eee              |       | 0.08            |       |

| N <sup>(1)</sup> |       | 28              |       |

<sup>1.</sup> N is the total number of terminals.

PWD13F60 Package information

Note: Dimensioning and tolerances conform to the ASME Y14.5-1994.

All dimensions are in millimeters.

The package is mechanically symmetrical by 180 degree rotation. Please refer to the pin1 identifier for the correct orientation.

A variable pitch is applied on leads. Please refer to Figure 17 for the detailed lead position.

The leads size is comprehensive of the thickness of the leads finishing material.

Dimensions do not include the mold protrusion, not to exceed 0.15 mm.

Package outline exclusive of metal burr dimensions.

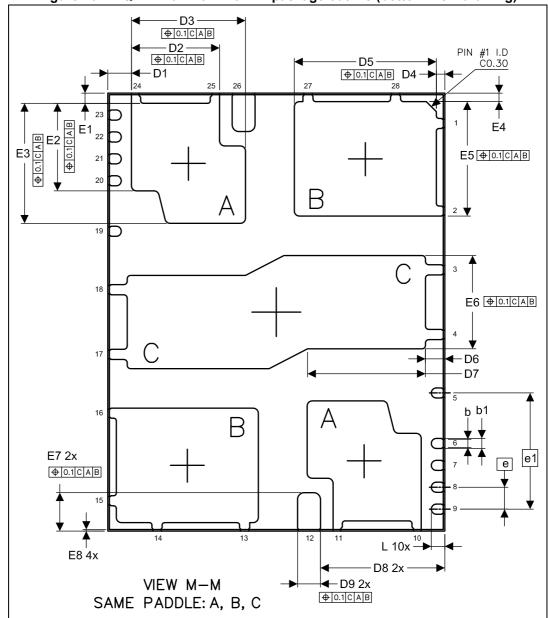

Figure 17. VFQFPN 10 x 13 x 1.0 mm package dimensions - pin position drawing

Package information PWD13F60

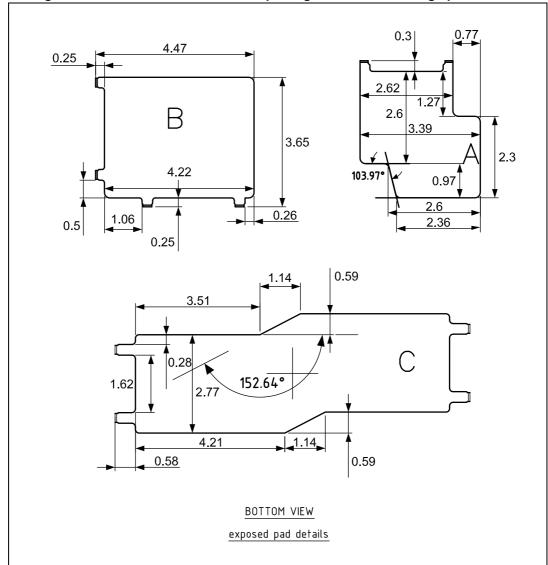

Figure 18. VFQFPN 10 x 13 x 1.0 mm package dimensions – large pads details

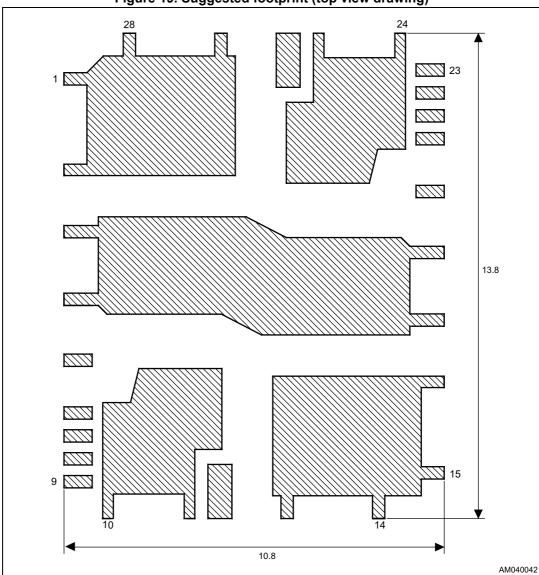

## 9 Suggested footprint

The PWD13F60 footprint for the PCB layout is usually defined based on several design factors as assembly plant technology capabilities and board component density. For easy device usage and evaluation, ST provides the following footprint design, which is suitable for the largest variety of PCBs.

The following footprint indicates the copper area which should be free from the solder mask, while the copper area shall extend beyond the indicated areas especially for the EPAD1, EPAD2, EPAD5. To aid thermal dissipation, it is recommended to add thermal vias under these EPADs to transfer and dissipate device heat to the other PCB copper layers. A PCB layout example is available with the PWD13F60 evaluation board.

As for the package outline, also the suggested footprint CAD file is available upon request.

Figure 19. Suggested footprint (top view drawing)

Suggested footprint PWD13F60

Figure 20. Suggested footprint detailed dimensions (top view drawing)

# 10 Ordering information

Table 11. Device summary

| Order code | Package                 | Packaging     |

|------------|-------------------------|---------------|

| PWD13F60   | VFQFPN 10 x 13 x 1.0 mm | Tray          |

| PWD13F60TR | VFQFPN 10 x 13 x 1.0 mm | Tape and reel |

# 11 Revision history

Table 12. Document revision history

| Date        | Revision | Changes                                                                                                                                                              |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Jul-2017 | 1        | Initial release.                                                                                                                                                     |

|             |          | Updated document status to Datasheet - production data.                                                                                                              |

| 02-Nov-2017 | 2        | Updated values and test conditions in <i>Table 3 on page 7</i> , <i>Table 5 on page 8</i> , and <i>Table 6 on page 9</i> .  Minor modifications throughout document. |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved