Features

# **Single-Chip Electricity Meter AFE**

## **General Description**

The MAX71020 is a single-chip analog front-end (AFE) for use in high-performance revenue meters. It contains the compute engine (CE) found in Maxim Integrated's fourth-generation meter system-on-chip (SoC) and an improved analog-to-digital converter (ADC), and interfaces to the host controller of choice over a SPI interface.

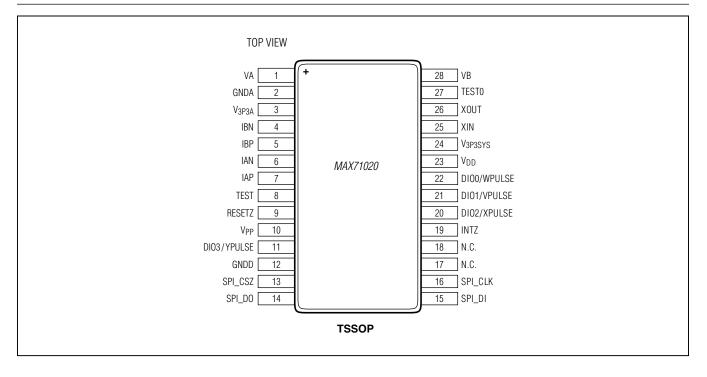

The MAX71020 comes in a 28-pin TSSOP package.

maxim integrated

### Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to <u>www.maximintegrated.com/MAX71020.related</u>.

## ♦ 0.1% Accuracy Over 2000:1 Current Range

- Exceeds IEC 62053/ANSI C12.20 Standards

- Two Differential Current Sensor Inputs

- Two Voltage Sensor Inputs

- Selectable Gain of 1 or 8.9 for One Current Input to Support a Shunt

- High-Speed Wh/VARh Pulse Outputs with Programmable Width

- Up to Four Pulse Outputs with Pulse Count

- Four-Quadrant Metering

- Digital Temperature Compensation

- Independent 32-Bit Compute Engine

- ♦ 45Hz to 65Hz Line Frequency Range with Same Calibration

- Phase Compensation (±10°)

- Four Multifunction DIO Pins

- SPI Interface

- ♦ -40°C to +85°C Industrial Temperature Range

- ♦ 28-Pin TSSOP Lead(Pb)-Free Package

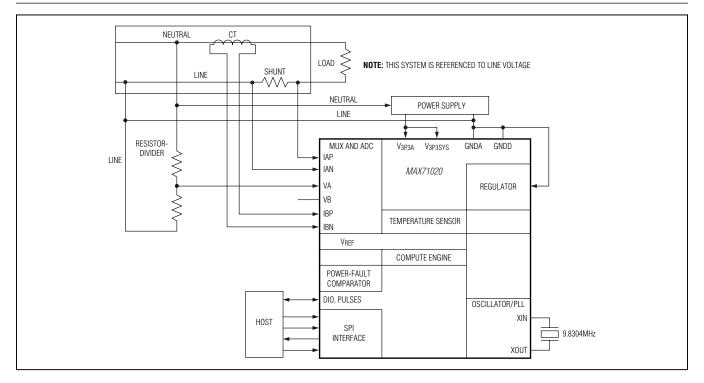

## **Typical Operating Circuit**

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

# **Single-Chip Electricity Meter AFE**

## **ABSOLUTE MAXIMUM RATINGS**

| (All voltages with respect to GNDA.)         | Digital Pins                                                      |

|----------------------------------------------|-------------------------------------------------------------------|

| Voltage and Current Supplies and Ground Pins | Inputs (-10mA to +10mA), (-0.5V to +6V)                           |

| V3P3SYS, V3P3A0.5V to +4.6V                  | Outputs (-10mA to +10mA), (-0.5V to (V <sub>3P3SYS</sub> + 0.5V)) |

| GNDD0.1V to +0.1V                            | Temperature and ESD Stress                                        |

| Analog Input Pins                            | Operating Junction Temperature (peak, 100ms)140°C                 |

| IAP, IAN, IBP, IBN, VA, VB(-10mA to +10mA),  | Operating Junction Temperature (continuous)125°C                  |

| (-0.5V to +0.5V)                             | Storage Temperature Range45°C to +165°C                           |

| XIN, XOUT (-10mA to +10mA), (-0.5V to +3.0V) | ESD Stress on All Pins±4kV, HBM                                   |

|                                              | Lead Temperature (soldering, 10s)                                 |

|                                              | Soldering Temperature (reflow)+250°C                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

TSSOP

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

# ELECTRICAL CHARACTERISTICS

| PARAMETER                                                       | CONDITIONS                             | MIN                           | ΤΥΡ | MAX  | UNITS |

|-----------------------------------------------------------------|----------------------------------------|-------------------------------|-----|------|-------|

| RECOMMENDED OPERATING                                           | CONDITIONS                             |                               |     |      |       |

| $V_{3P3SYS}$ and $V_{3P3A}$ Supply                              | Precision metering operation           | 3.0                           |     | 3.6  | V     |

| Voltage                                                         | Digital operation (Notes 2, 3)         | 2.8                           |     | 3.6  | V     |

| Operating Temperature                                           |                                        | -40                           |     | +85  | °C    |

| INPUT LOGIC LEVELS                                              |                                        |                               |     |      |       |

| Digital High-Level Input Voltage<br>(V <sub>IH</sub> )          |                                        | 2                             |     |      | V     |

| Digital Low-Level Input Voltage (V <sub>IL</sub> )              |                                        |                               |     | 0.8  | V     |

| Input Pullup Current (I <sub>IL</sub> )<br>RESETZ               | $V_{V3P3SYS} = 3.6V, V_{IN} = 0V$      | 41                            | 78  | 115  | μA    |

| Input Pullup Current (I <sub>IL</sub> ) Other<br>Digital Inputs | $V_{V3P3SYS} = 3.6V, V_{IN} = 0V$      | -1                            | 0   | +1   | μA    |

| Input Pulldown Current (I <sub>IH</sub> ) All<br>Pins           | V <sub>IN</sub> = V <sub>V3P3SYS</sub> | -1                            | 0   | +1   | μA    |

| OUTPUT LOGIC LEVELS                                             |                                        |                               |     |      |       |

| Digital High-Level Output                                       | I <sub>LOAD</sub> = 1mA                | V <sub>V3P3SYS</sub><br>- 0.4 |     |      | V     |

| Voltage (V <sub>OH</sub> )                                      | I <sub>LOAD</sub> = 15mA (Note 3)      | V <sub>V3P3SYS</sub><br>- 1.1 |     |      | V     |

| Digital Low-Level Output                                        | $I_{LOAD} = 1 mA$                      | 0                             |     | 0.4  |       |

| Voltage (V <sub>OL</sub> )                                      | I <sub>LOAD</sub> = 15mA (Note 3)      | 0                             |     | 0.96 | V     |

# **Single-Chip Electricity Meter AFE**

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                                         | CONDITIONS                                                    | MIN    | ТҮР                        | MAX   | UNITS  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------|--------|----------------------------|-------|--------|

| TEMPERATURE MONITOR                                                               |                                                               | 1      |                            |       | 1      |

| TNOM (Nominal Value at 22°C)                                                      | $V_{V3P3A} = 3.3V$                                            |        | 956                        |       | LSB    |

| Temperature Measurement<br>Equation                                               |                                                               | Temp = | = 0.33 x STE<br>21.77      | EMP + | °C     |

|                                                                                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                 | -6     |                            | +6    |        |

| Temperature Error (Note 4)                                                        | $T_A = -20^{\circ}C \text{ to } +60^{\circ}C$                 | -4.8   |                            | +4.8  | °C     |

| Duration of Temperature<br>Measurement After Setting<br>TEMP_START                | TEMP_PER = 0                                                  |        | 15                         | 60    | ms     |

| SUPPLY CURRENT PERFORM                                                            | ANCE SPECIFICATIONS                                           | •      |                            |       |        |

| V <sub>3P3A</sub> + V <sub>3P3SYS</sub> Current<br>(Note 4)                       | $V_{V3P3A} = V_{V3P3SYS} = 3.3V, CE_E = 1, ADC_E = 1$         |        | 3                          | 4.3   | mA     |

| INTERNAL POWER-FAULT CO                                                           | MPARATOR SPECIFICATIONS                                       |        |                            |       |        |

| Overall Response Time                                                             | 100mV overdrive, falling                                      | 20     |                            | 200   |        |

| Overall Response Time                                                             | 100mV overdrive, rising                                       | 8      |                            | 200   | μs     |

|                                                                                   | 3.0V comparator                                               | 2.83   | 2.93                       | 3.03  | V      |

| Falling Threshold                                                                 | 2.8V comparator                                               | 2.75   | 2.81                       | 2.89  | V      |

|                                                                                   | Difference 3.0V and 2.8V comparators                          | 50     | 136                        | 220   | mV     |

| Hysteresis (Rising Threshold -                                                    | 3.0V comparator, $T_A = +22^{\circ}C$                         | 17     | 45                         | 74    | mV     |

| Falling Threshold)                                                                | 2.8V comparator, $T_A = +22^{\circ}C$                         | 15     | 42                         | 70    |        |

| PLL PERFORMANCE SPECIFIC                                                          | CATIONS                                                       |        |                            |       |        |

| PLL Power-Up Settling Time                                                        | $V_{V3P3A} = 0$ to 3.3V step, measured from first edge of MCK |        | 75                         |       | μs     |

|                                                                                   | V <sub>V3P3A</sub> = 3.3V, PLL_FAST rise                      |        | 10                         |       |        |

| PLL_FAST Settling Time                                                            | V <sub>V3P3A</sub> = 3.3V, PLL_FAST fall                      |        | 10                         |       | μs     |

| PLL Lock Frequency at XOUT                                                        | V <sub>V3P3A</sub> = 3.3V, MCK frequency error < 1%           | 7      | 9.8                        | 13    | MHz    |

| VREF PERFORMANCE SPECIF                                                           | ICATIONS                                                      |        |                            |       |        |

| VREF Output Voltage, VREF (22)                                                    | $T_A = +22^{\circ}C$                                          | 1.200  | 1.205                      | 1.210 | V      |

| VREF Power-Supply Sensitivity<br>(DV <sub>REF</sub> /DV <sub>V3P3A</sub> )        | $V_{V3P3A} = 3.0V \text{ to } 3.6V$                           | -1.5   |                            | +1.5  | mV/V   |

| VNOM Definition                                                                   |                                                               |        | (T) = VREF(<br>22) + TC2(1 |       | V      |

| VNOM Temperature Coefficient<br>TC1                                               |                                                               | 29.32  | - 1.05 x TF                | RIMT  | µV/°C  |

| VNOM Temperature Coefficient<br>TC2                                               |                                                               | -0.56  | - 0.004 x TF               | RIMT  | µV/°C² |

| VREF(T) Deviation from<br>VNOM(T):<br>$\frac{VREF(T) - VNOM(T) 10^6}{VNOM(T) 62}$ | (Note 4)                                                      | -40    |                            | +40   | ppm/°C |

# **Single-Chip Electricity Meter AFE**

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                                                                      | CON                                                                                           | DITIONS                                                          | MIN  | TYP      | MAX              | UNITS |  |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------|------|----------|------------------|-------|--|

| ADC CONVERTER PERFORMA                                                                                         | NCE SPECIFICATIONS                                                                            |                                                                  |      |          |                  |       |  |

| Recommended Input Range<br>(with Respect to GNDA)                                                              | VA, VB, IBP, IBN                                                                              |                                                                  | -250 |          | +250             | mVpk  |  |

| Recommended Input Range                                                                                        | IAP, IAN: preamplifier en                                                                     | IAP, IAN: preamplifier enabled                                   |      |          | +27.78           |       |  |

| (with Respect to GNDA)                                                                                         | IAP, IAN: preamplifier dis                                                                    | IAP, IAN: preamplifier disabled                                  |      |          |                  | mVpk  |  |

| Input Impedance, No<br>Preamplifier                                                                            | $f_{IN} = 65Hz$                                                                               |                                                                  | 50   |          | 100              | kΩ    |  |

| ADC Gain Error vs Percentage<br>Power-Supply Variation                                                         |                                                                                               |                                                                  |      |          |                  |       |  |

| $\frac{10^{6} \Delta \text{Nout}_{\text{PK}} 357 \text{nV}/\text{V}_{\text{IN}}}{100 \Delta \text{V3P3A}/3.3}$ | V <sub>IN</sub> = 200mV peak, 65Hz                                                            | ;; V <sub>V3P3A</sub> = 3.0V, 3.6V                               |      |          | 81               | ppm/% |  |

| Input Offset                                                                                                   | IAP = IAN = GNDA                                                                              |                                                                  | -10  |          | +10              | mV    |  |

| Total Harmonic Distortion at 250mVpk                                                                           | V <sub>IN</sub> = 55Hz, 250mVpk, 64<br>Blackman Harris Window                                 |                                                                  |      | -85      |                  | dB    |  |

| Total Harmonic Distortion at 20mVpk                                                                            | V <sub>IN</sub> = 55Hz, 20mVpk, 64<br>Blackman Harris Window                                  |                                                                  |      | -90      |                  | dB    |  |

|                                                                                                                | V <sub>IN</sub> = 55Hz, 20mVpk,<br>64kpts FFT, Blackman-<br>Harris window, 10MHz<br>ADC clock | FIRLEN = 15                                                      |      | 120.46   |                  | nV    |  |

| LSB Size (LSB Values Do Not<br>Include the 9-Bit Left Shift at                                                 |                                                                                               | FIRLEN = 14                                                      |      | 146.20   |                  |       |  |

|                                                                                                                |                                                                                               | FIRLEN = 13                                                      |      | 179.82   |                  |       |  |

| the CE Input)                                                                                                  |                                                                                               | FIRLEN = 12                                                      |      | 224.59   |                  |       |  |

|                                                                                                                |                                                                                               | FIRLEN = 11                                                      |      | 285.54   |                  |       |  |

|                                                                                                                |                                                                                               | FIRLEN = 10                                                      |      | 370.71   |                  |       |  |

|                                                                                                                |                                                                                               | FIRLEN = 15                                                      |      | ±2621440 | 0                |       |  |

|                                                                                                                |                                                                                               | FIRLEN = 14                                                      |      | ±2160000 |                  | LSB   |  |

| Digital Full Scale                                                                                             | $V_{IN} = 55Hz$ , 400mVpk,                                                                    | FIRLEN = 13                                                      |      | ±1756160 |                  |       |  |

| Digital I uli Scale                                                                                            | 10MHz ADC clock                                                                               | FIRLEN = 12                                                      |      | ±1406080 |                  |       |  |

|                                                                                                                |                                                                                               | FIRLEN = 11                                                      |      | ±1105920 |                  |       |  |

|                                                                                                                |                                                                                               | FIRLEN = 10                                                      |      | ±851840  |                  |       |  |

| PREAMPLIFIER PERFORMANC                                                                                        | CE SPECIFICATIONS                                                                             |                                                                  |      |          |                  |       |  |

| Differential Gain,<br>(V <sub>IN</sub> = 28mV Differential)                                                    | T                                                                                             | 2) ( proceedifier eachlad                                        |      | 8.9      |                  | V/V   |  |

| Differential Gain<br>(V <sub>IN</sub> = 15mV Differential)                                                     | $T_A = +23 \text{ C},        $                                                                | $T_A = +25^{\circ}C$ , $V_{V3P3A} = 3.3V$ , preamplifier enabled |      | 0.9      |                  | V/V   |  |

| Gain Variation vs. V <sub>3P3A</sub><br>(V <sub>IN</sub> = 28mV Differential)                                  | V <sub>V3P3A</sub> = 3.0V, 3.6V                                                               |                                                                  | -72  |          | ppm/%            |       |  |

| Gain Variation vs. Temperature<br>(V <sub>IN</sub> = 28mV Differential)                                        | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                                               |                                                                  | -45  |          | ppm/°C           |       |  |

| Phase Shift (V <sub>IN</sub> = 28mV<br>Differential)                                                           | $T_A = +25^{\circ}C, V_{V3P3A} = 3.$                                                          | 0                                                                |      | 8        | milli-<br>degree |       |  |

| Preamplifier Input Current (I <sub>IAP</sub> )<br>Preamplifier Input Current (I <sub>IAN</sub> )               | Preamplifier enabled, IAE                                                                     | 9                                                                | 15   | 20       | μA               |       |  |

# **Single-Chip Electricity Meter AFE**

## **ELECTRICAL CHARACTERISTICS (continued)**

| PARAMETER                                                                                  | CONDITIONS                                        | MIN     | ТҮР                                                      | MAX    | UNITS |

|--------------------------------------------------------------------------------------------|---------------------------------------------------|---------|----------------------------------------------------------|--------|-------|

| Preamplifier and ADC Total<br>Harmonic<br>(V <sub>IN</sub> = 28mV Differential)            | $T_A = +25^{\circ}C; V_{V3P3A} = 3.3V, PRE_E = 1$ |         | -80                                                      |        | dB    |

| Preamplifier and ADC Total<br>Harmonic Distortion<br>(V <sub>IN</sub> = 15mV Differential) | $T_A = +25^{\circ}C; V_{V3P3A} = 3.3V, PRE_E = 1$ |         | -85                                                      |        | dB    |

| SPI SLAVE TIMING SPECIFIC                                                                  | ATIONS                                            |         |                                                          |        |       |

| SPI Setup Time                                                                             | SPI_DI to SPI_CK rise                             | 10      |                                                          |        | ns    |

| SPI Hold Time                                                                              | SPI_CLK rise to SPI_DI                            | 10      |                                                          |        | ns    |

| SPI Output Delay                                                                           | SPI_CLK fall to SPI_D0                            |         |                                                          | 40     | ns    |

| SPI Recovery Time                                                                          | SPI_CSZ fall to SPI_CLK                           | 10      |                                                          |        | ns    |

| SPI Removal Time                                                                           | SPI_CLK to SPI_CSZ rise                           | 15      |                                                          |        | ns    |

| SPI Clock High                                                                             |                                                   | 40      |                                                          |        | ns    |

| SPI Clock Low                                                                              |                                                   | 40      |                                                          |        | ns    |

| SPI Clock Frequency                                                                        |                                                   |         |                                                          | 10     | MHz   |

| SPI Transaction Space<br>(SPI_CSZ Rise to SPI_CSZ Fall)                                    |                                                   | 1       |                                                          |        | μs    |

| RESETZ TIMING                                                                              |                                                   | 1       |                                                          |        | 1     |

|                                                                                            | Following power-on                                | 1       |                                                          |        | ms    |

| Reset Pulse Width                                                                          | At all other times                                | 5       |                                                          |        | μs    |

| Reset Pulse Rise Time                                                                      | (Note 4)                                          |         |                                                          | 1      | μs    |

| VOLTAGE MONITOR                                                                            |                                                   |         |                                                          |        | ,     |

| Nominal Value at +22°C<br>(VNOM)                                                           | $V_{V3P3A} = 3.3V$                                |         | 130                                                      |        | LSB   |

| Voltage Measurement Equation                                                               |                                                   | (VSENSE | <sub>S</sub> (CALC) = 3<br>5 – 130) x 0.0<br>EMP x 242µ' | 025V + |       |

| Voltage Error                                                                              |                                                   |         |                                                          |        |       |

| 100×((100 × (100 - 1))<br>V <sub>üüü</sub> - 1)                                            |                                                   | -4      |                                                          | +4     | %     |

**Note 2:** V<sub>3P3SYS</sub> and V<sub>3P3A</sub> must be connected together. **Note 3:** GNDA and GNDD must be connected together.

**Note 4:** Guaranteed by design, not production tested.

# **Single-Chip Electricity Meter AFE**

| NAME | FROM                | то   | FUNCTION                                                                                                                     | VALUE      | UNITS |

|------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------|------------|-------|

| C1   | V <sub>3P3A</sub>   | GNDA | Bypass capacitor for 3.3V supply                                                                                             | ≥ 0.1 ±20% | μF    |

| CSYS | V <sub>3P3SYS</sub> | GNDD | Bypass capacitor for V <sub>3P3SYS</sub>                                                                                     | ≥ 1.0 ±30% | μF    |

| C1P8 | V <sub>DD</sub>     | GNDD | Bypass capacitor for V1P8 regulator                                                                                          | 0.1 ±20%   | μF    |

| XTAL | XIN                 | XOUT | At cut crystal specified for 18pF load                                                                                       | 9.8304     | MHz   |

| CXS  | XIN                 | GNDA | Load capacitor values for crystal depend on crystal specifications and board parasitics.                                     | 32 ±10%    | pF    |

| CXL  | XOUT                | GNDA | <ul> <li>Nominal values are based on 4pF board<br/>capacitance and include an allowance for<br/>chip capacitance.</li> </ul> | 32 ±10%    | pF    |

## **RECOMMENDED EXTERNAL COMPONENTS**

## **Pin Configuration**

# **Single-Chip Electricity Meter AFE**

## **Pin Description**

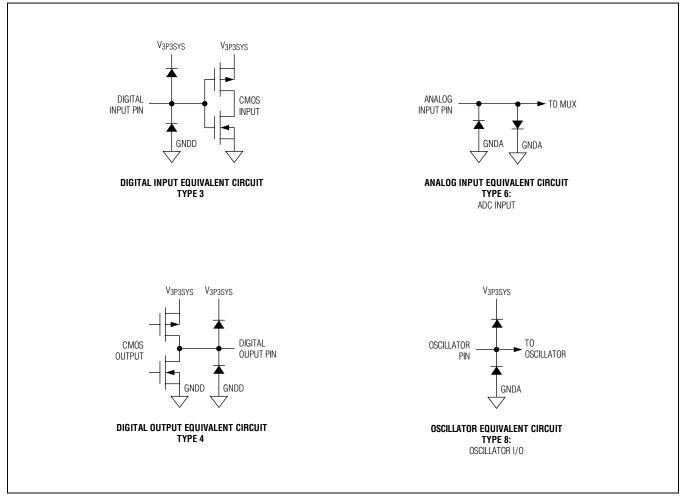

(Pin types: P = Power, O = Output, I = Input, I/O = Input/Output. The circuit number denotes the equivalent circuit, as specified under Figure 1).

| PIN          | NAME                | TYPE                         | CIRCUIT | DESCRIPTION                                                                                                                                                                                   |

|--------------|---------------------|------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER AND (  | GROUND PINS         |                              |         |                                                                                                                                                                                               |

| 2            | GNDA                | Р                            | _       | Analog Ground. GNDA should be connected directly to the ground plane.                                                                                                                         |

| 3            | V <sub>3P3A</sub>   | Р                            | _       | Analog Power Supply. A 3.3V power supply should be connected to $V_{3P3A}$ . $V_{3P3A}$ must be the same voltage as $V_{3P3SYS}$ .                                                            |

| 12           | GNDD                | Р                            | _       | Digital Ground. GNDD should be connected directly to the ground plane.                                                                                                                        |

| 23           | V <sub>DD</sub>     | 0                            | _       | Output of the 1.8V Regulator. A 0.1µF bypass capacitor to ground should be connected to this pin.                                                                                             |

| 24           | V <sub>3P3SYS</sub> | Р                            | _       | System 3.3V Supply. $V_{3P3SYS}$ should be connected to a 3.3V power supply.                                                                                                                  |

| ANALOG PINS  | ;                   |                              |         |                                                                                                                                                                                               |

| 7, 6         | IAP, IAN            |                              |         | Differential or Single-Ended Line Current-Sense Inputs. These pins are                                                                                                                        |

| 5, 4         | IBP, IBN            | Ι                            |         | voltage inputs to the internal ADC. Typically, these pins are connected to the outputs of current sensors. <b>Unused pins must be tied to GNDA</b>                                            |

| 1, 28        | VA, VB              | Ι                            | 6       | Line Voltage Sense Inputs. VA/VB are voltage inputs to the internal ADC. Typically, the pins are connected to the outputs of resistor-<br>dividers. <b>Unused pins must be tied to GNDA</b> . |

| 25           | XIN                 | I                            | 0       | Crystal Inputs. A 9.8304MHz crystal should be connected to XIN and                                                                                                                            |

| 26           | XOUT                | 0                            | - 8     | XOUT.                                                                                                                                                                                         |

| DIGITAL PINS |                     |                              |         |                                                                                                                                                                                               |

| 22           | DIO0/WPULSE         |                              |         | Multiple-Use Pins. Configurable as DIO. Alternative functions with                                                                                                                            |

| 21           | DIO1/VPULSE         | I/O                          | 3, 4    | proper selection of associated registers are:                                                                                                                                                 |

| 20           | DIO2/XPULSE         | XPULSE         DIOU = WPULSE |         |                                                                                                                                                                                               |

| 11           | DIO3/YPULSE         |                              |         | DIO1 = VPULSE                                                                                                                                                                                 |

| 8, 27        | TEST, TEST0         | I                            | 3       | Connect to GNDD                                                                                                                                                                               |

| 9            | RESETZ              | I                            | 3       | Active-Low Reset                                                                                                                                                                              |

| 13           | SPI_CSZ             | I                            | 3       |                                                                                                                                                                                               |

| 14           | SPI_DO              | 0                            | 4       |                                                                                                                                                                                               |

| 15           | SPI_DI              | I                            | 3       | SPI Interface                                                                                                                                                                                 |

| 16           | SPI_CLK             | I                            | 3       |                                                                                                                                                                                               |

| 19           | INTZ                | 0                            | 4       | Active-Low Interrupt Request                                                                                                                                                                  |

| OTHER PIN    |                     |                              |         |                                                                                                                                                                                               |

| 10           | V <sub>PP</sub>     | I                            | _       | Connect to GNDD                                                                                                                                                                               |

# **Single-Chip Electricity Meter AFE**

Figure 1. I/O Equivalent Circuits

# **Single-Chip Electricity Meter AFE**

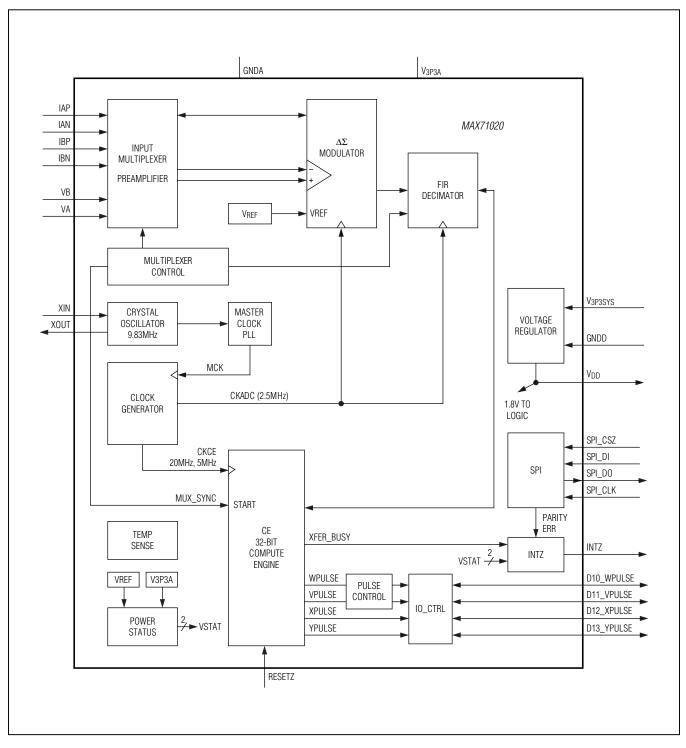

**Functional Diagram**

# **Single-Chip Electricity Meter AFE**

## **Hardware Description**

### **Hardware Overview**

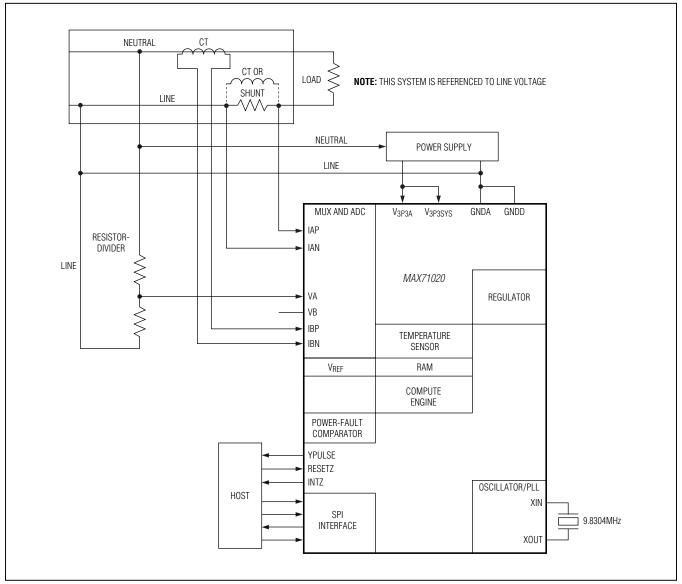

The MAX71020 energy meter analog front-end (AFE) integrates all primary functional blocks required to implement a solid-state residential electricity meter. Included on the chip are:

- An analog front-end (AFE) featuring a 22-bit secondorder sigma-delta ADC

- An independent 32-bit digital computation engine (CE) to implement DSP functions

- A precision voltage reference (VREF)

- A temperature sensor for digital temperature sensing and compensation

- Four I/O pins

- A zero-crossing detector with interrupt output

- Resistive shunt and current transformers are supported

- A SPI slave for connection to a host controller

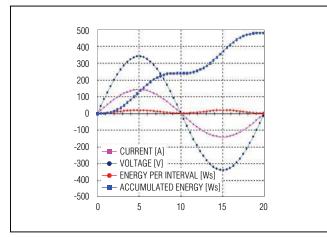

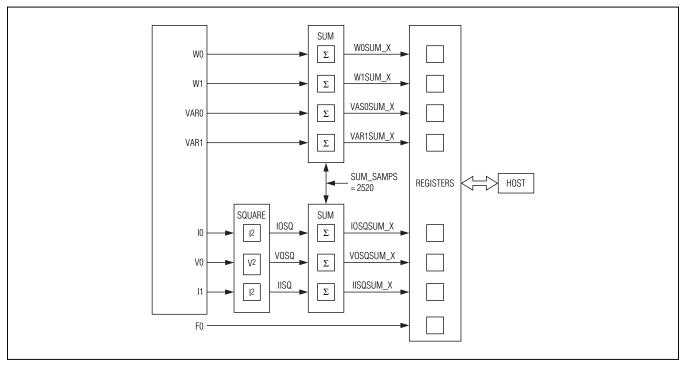

In a typical application, the 32-bit compute engine (CE) of the MAX71020 sequentially processes the samples from the voltage inputs on analog input pins and performs calculations to measure active energy (Wh) and reactive energy (VARh), as well as A<sup>2</sup>h, and V<sup>2</sup>h for four-quadrant metering. These measurements are then accessed by the host controller.

In addition to the temperature-trimmed ultra-precision voltage reference, the on-chip digital temperature compensation mechanism includes a temperature sensor and associated controls for correction of unwanted temperature effects on measurement, e.g., to meet the requirements of ANSI and IEC standards.

Temperature-dependent external components such as crystal oscillator, resistive shunts, current transformers (CTs) and their corresponding signal conditioning circuits can be characterized and their correction factors can be programmed to produce electricity meters with exceptional accuracy over the industrial temperature range.

Communications with the host is conducted over a SPI interface. The communications protocol between the host and the MAX71020 provides a redundant information transfer ensuring the correctness of commands transferred from the host to the AFE, and of data transferred from the AFE to the host.

In addition, the MAX71020 has one pin dedicated as an interrupt output to the host. This pin notifies the host of asynchronous events.

## Analog Section

### Signal Input Pins

The MAX71020 has four analog inputs: two single-ended inputs for voltage measurement, and two differential inputs for current measurement.

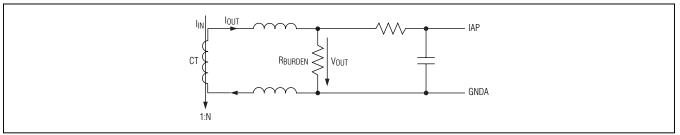

The IAP, IAN, IBP, and IBN pins are current sensor inputs. The differential inputs feature preamplifiers with a selectable gain of 1 or 9, and are intended for direct connection to a shunt resistor sensor or a current transformer (CT).

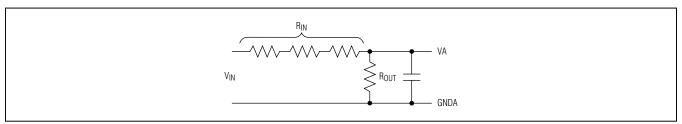

The voltage inputs in the MAX71020 are single-ended, and are intended for sensing the line voltage via resistive dividers. These single-ended inputs are referenced to the GNDA pin.

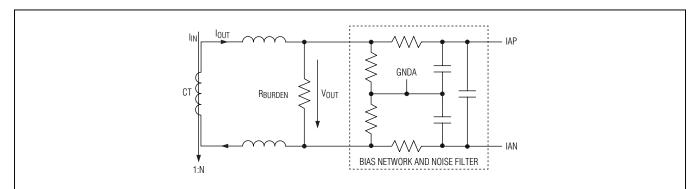

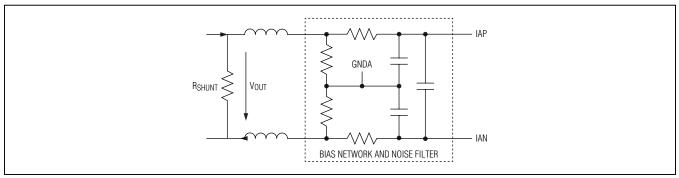

All analog signal input pins measure voltage. In the case of shunt current sensors, currents are sensed as a voltage drop in the shunt resistor sensor. In the case of Current Transformers (CT), the current is measured as a voltage across a burden resistor that is connected to the secondary winding of the CT. Meanwhile, line voltages are sensed through resistive voltage-dividers.

Some versions of the device implement a preamplifier with a fixed gain of 8.9 to enhance performance when using sensors with a low-amplitude output (for example, current shunts). When using a device with the preamplifier enabled, the input signal amplitude cannot be greater than 27.78mV peak.

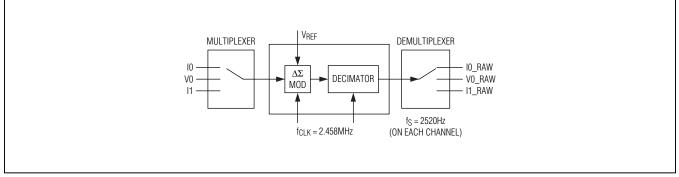

### Input Multiplexer

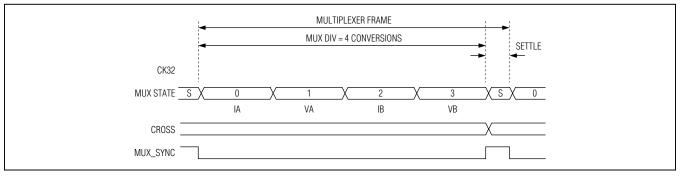

The input multiplexer sequentially applies the input signals from the analog input pins to the input of the ADC. One complete sampling sequence is called a multiplexer frame.

The IBP-IBN differential input may be used to sense the neutral current, and VB may be optionally used to sense a second voltage channel. This configuration implies that the multiplexer applies a total of four inputs to the ADC. For this configuration, the multiplexer sequence is as shown in Figure 2. In this configuration IAP-IAN, IBP-IBN, VA and VB are sampled. The physical current sensor for the neutral current measurement and the voltage sensor for VB may be omitted if not required.

## **Single-Chip Electricity Meter AFE**

For a standard single-phase application with tamper sensor in the neutral path, two current inputs are configured for differential mode, using the pin pairs IAP-IAN and IBP-IBN. The MAX71020 uses two locally connected current sensors via IAP-IAN and IBP-IBN for this configuration. The VA pin is typically connected to the phase voltage via resistor-dividers.

The MAX71020 adds the ability to sample a second phase voltage (applied at the VB pin), which makes it suitable for meters with two voltage and two current sensors, such as meters implementing Equation 2 for dual-phase operation ( $P = VA \times IA + VB \times IB$ ).

Table 1 summarizes the AFE input configuration.

### **Delay Compensation**

When measuring the energy of a phase (i.e., Wh and VARh) in a service, the voltage and current for that phase must be sampled at the same instant. Otherwise, the phase difference,  $\phi$ , introduces errors.

$$\phi = \frac{t_{delay}}{T} \times 360^{\circ} = t_{delay} \times f \times 360^{\circ}$$

where f is the frequency of the input signal, T = 1/f and  $t_{delay}$  is the sampling delay between current and voltage.

## Table 1. ADC Input Configuration

| PIN | COMMENT                                    |

|-----|--------------------------------------------|

| IAP | The ADC results are stored in register IA. |

| IAN | The ADC results are stored in register IA. |

| IBP | The ADC results are stored in register IB. |

| IBN | The ADC results are stored in register IB. |

| VA  | The ADC result is stored in register VA.   |

| VB  | The ADC result is stored in register VB.   |

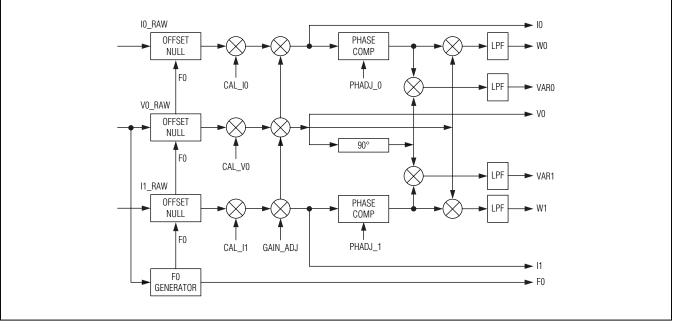

Traditionally, sampling is accomplished by using two ADCs per phase (one for voltage and the other one for current) controlled to sample simultaneously. Maxim Integrated's Single Converter Technology®, however, exploits the 32-bit signal processing capability of its CE to implement "constant delay" allpass filters. The allpass filter corrects for the conversion time difference between the voltage and the corresponding current samples that are obtained with a single multiplexed ADC.

The constant delay allpass filter provides a broadband delay  $360^{\circ}$  -  $\theta$ , which is precisely matched to the difference in sample time between the voltage and the current of a given phase. This digital filter does not affect the amplitude of the signal, but provides a precisely controlled phase response.

The ADC multiplexer samples the current first, immediately followed by sampling of the corresponding phase voltage, thus the voltage is delayed by a phase angle  $\phi$  relative to the current. The delay compensation implemented in the CE aligns the voltage samples with their corresponding current samples by first delaying the current samples by one full sample interval (i.e., 360°), then routing the voltage samples through the allpass filter, thus delaying the voltage samples by 360° -  $\theta$ , resulting in the residual phase error between the current and its corresponding voltage of  $\theta - \phi$ . The residual phase error is negligible, and is typically less than ±0.0015° at 100Hz, thus it does not contribute to errors in the energy measurements.

### ADC Preamplifier

The ADC preamplifier is a low-noise differential amplifier with a fixed gain of 8.9 available on the IAP and IAN current-sensor input pins. It is provided only in versions of the MAX71020 AFE configured for use with current shunts.

Figure 2. States in a Multiplexer Frame

Single Converter Technology is a registered trademark of Maxim Integrated Products, Inc.

#### Maxim Integrated

# **Single-Chip Electricity Meter AFE**

## Analog-to-Digital Converter (ADC)

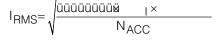

A single second-order delta-sigma ADC digitizes the voltage and current inputs to the device. The resolution of the ADC is dependent on several factors.

Initiation of each ADC conversion is automatically controlled by logic internal to the MAX71020. At the end of each ADC conversion, the FIR filter output data is stored into the register determined by the multiplexer selection. FIR data is stored LSB justified, but shifted left 9 bits.

### FIR Filter

The finite impulse response filter is an integral part of the ADC and it is optimized for use with the multiplexer. The purpose of the FIR filter is to decimate the ADC output to the desired resolution. At the end of each ADC conversion, the output data is stored into the register determined by the multiplexer selection.

### Voltage References

A bandgap circuit provides the reference voltage (VREF) to the ADC. Since the VREF bandgap amplifier is chopper stabilized, the DC offset voltage, which is the most significant long-term drift mechanism in the voltage reference (VREF), is automatically removed by the chopper circuit.

## **Digital Computation Engine (CE)**

The CE, a dedicated 32-bit signal processor, performs the precision computations necessary to accurately measure energy. The CE calculations and processes include:

- Multiplication of each current sample with its associated voltage sample to obtain the energy per sample (when multiplied with the constant sample time)

- Frequency-insensitive delay cancellation on all four channels (to compensate for the delay between samples caused by the multiplexing scheme)

- 90° phase shifter (for VAR calculations)

- Pulse generation

- Monitoring of the input signal frequency (for frequency and phase information)

- Monitoring of the input signal amplitude (for sag detection)

- Scaling of the processed samples based on calibration coefficients

- Scaling of samples based on temperature compensation information

- Gain and phase compensation

## Meter Equations

The MAX71020 provides hardware assistance to the CE in order to support various meter equations. This assistance is controlled through registers that are controlled by the CE code image. The CE firmware implements the equations listed in Table 2 or a subset thereof.

### **Pulse Generators**

The MAX71020 provides up to four pulse generators, VPULSE, WPULSE, XPULSE, and YPULSE, as well as hardware support for the VPULSE and WPULSE pulse generators. The pulse generators are used to output CE status indicators and energy usage. See <u>Table 3</u>.

The polarity of the pulses may be inverted with control bit PLS\_INV. When this bit is set, the pulses are active-high, rather than the more usual active-low. PLS\_INV inverts all four pulse outputs.

The function of each pulse generator is determined by the CE code. Standard configurations of the MAX71020 provide a mains zero-crossing indication on XPULSE and voltage sag detection on YPULSE.

A common use of the zero-crossing pulses is to generate interrupts in order to drive RTC software in places where the mains frequency is sufficiently accurate to do so and also to adjust for crystal aging. Zero-crossing can also be used to control PLC modems or cut-off relays. A common use for the SAG pulse is to generate an interrupt that alerts the host controller when mains power is about to fail, so that the host controller can store accumulated energy and other data to EEPROM before the board supply voltage drops below safe levels.

| Table 2 | . Inputs | Selected | in | Multiplexer | Cycles |

|---------|----------|----------|----|-------------|--------|

|---------|----------|----------|----|-------------|--------|

| FOU | DESCRIPTION                                  | Wh AND VAF  | Rh FORMULA |

|-----|----------------------------------------------|-------------|------------|

| EQU | DESCRIPTION                                  | ELEMENT 0   | ELEMENT 1  |

| 0   | 1 element, 2W, 1φ with neutral current sense | VA · IA     | VA · IB    |

| 1   | 1 element, 3-W, 1φ                           | VA(IA-IB)/2 | VA · IB/2  |

| 2   | 2 element, 3-W                               | VA · IA     | VB · IB    |

**Temperature Sensor**

# **Single-Chip Electricity Meter AFE**

## **Table 3. Pulse Output Function Assignments**

| OUTPUT | FUNCTION                                                   |  |  |  |

|--------|------------------------------------------------------------|--|--|--|

| XPULSE | Pulse output on each zero crossing on voltage input        |  |  |  |

| YPULSE | Pulse output when voltage sag detected                     |  |  |  |

| VPULSE | Pulse output when programmed VARh consumption has occurred |  |  |  |

| WPULSE | Pulse output when programmed Wh consumption has occurred   |  |  |  |

## XPULSE and YPULSE

Pulses generated by the CE may be exported to the XPULSE and YPULSE pulse output pins. Pins D2 and D3 are used for these pulses, respectively. The XPULSE and YPULSE outputs can be updated once on each pass of the CE code. See the <u>CE Interface Description</u> section for details.

## VPULSE and WPULSE

By default, WPULSE and VPULSE are negative pulses (i.e., low level pulses, designed to sink current through an LED). PLS\_MAXWIDTH[7:0] determines the maximum negative pulse width  $T_{MAX}$  in units of 2.458MHz clock cycles based on the pulse interval  $T_I$  according to the formula:

## $T_{MAX} = (2 \times PLS_MAXWIDTH[7:0] + 1) \times T_I$

$T_I$  is based on an internal value that determines the pulse interval and the ADC clock, both of which are determined by the particular characteristics of the CE code. In the MAX71020, the default value for  $T_I$  is 65.772µs, but this value may change in customized versions of this device.

If PLS\_MAXWIDTH = 255 no pulse-width checking is performed, and the pulses default to 50% duty cycle.  $T_{MAX}$ is typically programmed to 10ms ( $T_{MAX}$  = 76), which works well with most calibration systems.

The polarity of the pulses may be inverted with the control bit PLS\_INV. When PLS\_INV is set, the pulses are active-high. The default value for PLS\_INV is zero, which selects active-low pulses.

The WPULSE and VPULSE pulse generator outputs are available on pins D0/WPULSE and D1/VPULSE, respectively.

The MAX71020 includes an on-chip temperature sensor for determining the temperature of its bandgap reference. The primary use of the temperature data is to determine the magnitude of compensation required to offset the thermal drift in the system for the compensation of current, voltage, and energy measurement. See the *Metrology Temperature Compensation* section.

The temperature sensor is awakened on command from the host controller by setting the TEMP\_START control bit. The host controller must wait for the TEMP\_START bit to clear before reading STEMP[15:0] and before setting the TEMP\_START bit once again.

The result of the temperature measurement can be read from the STEMP[15:0] register. The 16-bit value is in two's complement form and ranges from -1024 to +1023 (decimal). The sensed temperature can be computed from the 16-bit STEMP[15:0] reading using the following formula:

$$Temp (^{\circ}C) = 0.33 \times STEMP + 21.77$$

An additional register, VSENSE[7:0], senses the level of the supply voltage. Table 4 shows the registers used for temperature measurement.

## Digital I/O

On reset or power-up, all DIO pins are configured as high impedance. DIO pins can be configured independently by the host controller by manipulating the D0, D1, D2, and D3 bit fields.

# **Single-Chip Electricity Meter AFE**

| NAME          | RST | WK | DIR | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                             |                                             |  |  |

|---------------|-----|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|

|               |     |    |     | Sets the period betw                                                                                                                                                                                                                                                                                                                                                    | een temperature measurements.               |  |  |

|               |     |    |     | TEMP_PER                                                                                                                                                                                                                                                                                                                                                                | TIME                                        |  |  |

|               |     |    |     | 0                                                                                                                                                                                                                                                                                                                                                                       | Manual updates (see TEMP_START description) |  |  |

| TEMP_PER[1:0] | 0   | _  | R/W | 1                                                                                                                                                                                                                                                                                                                                                                       | Every accumulation cycle                    |  |  |

|               |     |    |     | 2                                                                                                                                                                                                                                                                                                                                                                       | Continuous                                  |  |  |

|               |     |    |     | 3                                                                                                                                                                                                                                                                                                                                                                       | No updates                                  |  |  |

| TEMP_START    | 0   |    | R/W | TEMP_PER[1:0] must be zero in order for TEMP_START to function. If TEMP_         PER[1:0] = 0, then setting TEMP_START starts a temperature measurement.         Hardware clears         TEMP_START when the temperature measurement is complete. The host controller must wait for TEMP_START to clear before reading STEMP[10:0] and before setting TEMP_START again. |                                             |  |  |

| STEMP[15:0]   | _   |    | R   | The result of the temperature measurement.                                                                                                                                                                                                                                                                                                                              |                                             |  |  |

| VSENSE[7:0]   | _   | _  | R   | The result of the temperature measurement.           The result of the temperature measurement (see the formula listed in the <i>Electrical Characteristics</i> table).                                                                                                                                                                                                 |                                             |  |  |

## **Table 4. Temperature Measurement Registers**

## SPI Slave Port

The slave SPI port communicates directly with the host controller and allows it to read and write the device control registers. The interface to the slave port consists of the SPI\_CSZ, SPI\_CLK, SPI\_DI, and SPI\_DO pins. The host can also reset the MAX71020 through the SPI port by writing a data pattern to the RESET register (see Table 7).

## SPI Transactions

SPI transactions are configured to provide immunity to electrical noise through redundancy in the command segment and error checking in the data field. The MAX71020 SPI transaction is exactly 64 bits; transactions of any other length are rejected. Each SPI transaction has the following fields (see Table 5):

- A 24-bit setting packet, consisting of

- 11-bit address, MSB first

- 1-bit direction (1 means read)

- 11-bit inverted address, MSB first

- 1-bit inverted direction

- An 8-bit status, consisting of the following bits concerning the last transaction, starting from bit 7:

- Parity of the status byte (0 or 1 could be correct)

- FIFO overflow status bit (1 means error)

- FIFO underrun status bit (1 means error)

- Read or write data parity (0 or 1 could be correct) (never both read and write; address is not included in the parity)

- Address or direction mismatch error bit (1 means error) (1: error, 0 : no error)

- A bit indicating whether or not the bit count was exactly 64 (1 means error)

- Out of bounds address, most likely due to SPI safe bit or the memory manager (1 means error)

- A 32-bit packet of data, MSB first

If extra clocks are provided at the end during a read, all zero is output and the status continues to be updated, signaling an error. If extra clocks are provided at the end during a write, the write is aborted and the status is updated to signal an error.

- None of the fields above are optional.

- If an error is detected during the address or direction phase, no action is taken.

- SPI\_DO is high-Z while SPI\_CSZ is high.

- SPI safe mode is supported, and SPI is not locked out of this bit during SPI safe.

A typical SPI transaction is as follows. While SPI\_CSZ is high, the port is held in an initialized/reset state. During this state, SPI\_DO is held in high-Z state and all transitions on SPI\_CLK and SPI\_DI are ignored. When SPI\_CSZ falls, the port begins the transaction on the first rising edge of SPI\_CLK. A transaction consists of the fields shown in Table 5.

# **Single-Chip Electricity Meter AFE**

| 24-B                                                           | BIT SI                     | ETTING FIELD            |         | 8-BIT STATUS                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |                    |                            | 32-BIT DATA        |

|----------------------------------------------------------------|----------------------------|-------------------------|---------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------|----------------------------|--------------------|

| Address                                                        | Dir                        | Inv Address             | Inv Dir |                                                                          | St                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | atus from Pr | evious - | Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | : status[7:0                                         | 0]                 |                            | Data               |