### Description

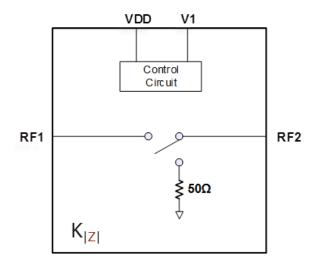

The F2910 is a high reliability, low insertion loss,  $50\Omega$  absorptive SPST RF switch designed for a multitude of wireless and RF applications. This device covers a broad frequency range from 30MHz to 8000MHz. In addition to providing low insertion loss, the F2910 also delivers excellent linearity and isolation performance while providing a  $50\Omega$  termination on RF2 in the isolation mode. The F2910 includes a patent pending constant impedance  $K_{|Z|}$  feature for the RF2 port.  $K_{|Z|}$  maintains near constant impedance when switching RF ports and improves hot switching ruggedness.  $K_{|Z|}$  minimizes VSWR transients and reduces phase and amplitude variations when switching.

The F2910 uses a single positive supply voltage supporting either 3.3V or 1.8V control logic.

### Competitive Advantage

The F2910 provides constant impedance for one RF port during transitions, improving a system's hot-switching ruggedness. The device also supports high power handling and high isolation.

- Constant impedance K<sub>|Z|</sub> during switching transition

- Low insertion loss

- High isolation

- Excellent linearity

- Extended temperature range: -55°C to +105°C

### Typical Applications

- Base Station 2G, 3G, 4G

- Portable Wireless

- Repeaters and E911 systems

- Digital Pre-Distortion

- Public Safety Infrastructure

- WIMAX Receivers and Transmitters

- Military Systems, JTRS radios

- RFID handheld and portable readers

- Cable Infrastructure

- Wireless LAN

- Test / ATE Equipment

#### **Features**

- Insertion Loss

- ✓ 0.55dB at 2GHz

- High Isolation

- ✓ 51dB at 2GHz

- High Linearity

- ✓ IIP3 of 65dBm

- Wide Single Positive Supply Voltage Range

- 3.3V and 1.8V compatible control logic

- Operating temperature -55°C to +105°C

- 2 x 2 mm 8-DFN package

#### Block Diagram

Figure 1. Block Diagram

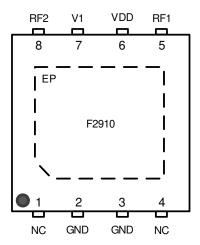

## Pin Assignments

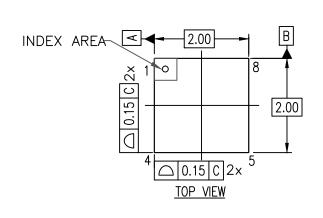

Figure 2. Pin Assignments for 2 mm x 2 mm x 0.9 mm 8-VFQFP-N - Top View

# Pin Descriptions

Table 1. Pin Descriptions

| Number | Name     | Description                                                                                                                                                                                                                                                                    |  |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 4   | NC       | This pin may be connected to the paddle and can be grounded.                                                                                                                                                                                                                   |  |

| 2, 3   | GND      | Ground. Also, internally connected to the ground paddle. Ground this pin as close to the device as possible.                                                                                                                                                                   |  |

| 5      | RF1      | RF1 Port. Matched to 50 $\Omega$ in the insertion loss state only. If this pin is not 0 V DC, then an external coupling capacitor must be used.                                                                                                                                |  |

| 6      | $V_{DD}$ | Power Supply. Bypass to GND with capacitors shown in the Typical Application Circuit as close as possible to pin.                                                                                                                                                              |  |

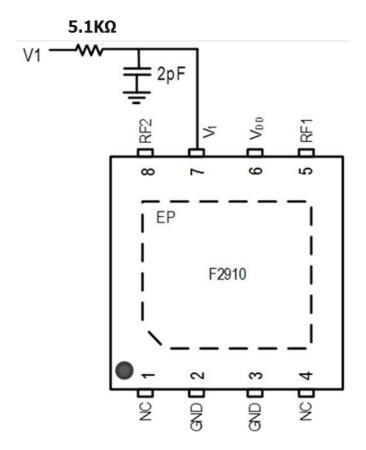

| 7      | V1       | Logic control pin. See Table 6 for proper logic setting.                                                                                                                                                                                                                       |  |

| 8      | RF2      | RF2 Port. Matched to 50 Ω. If this pin is not 0V DC, then an external coupling capacitor must be used.                                                                                                                                                                         |  |

|        | EP       | Exposed Pad. Internally connected to GND. Solder this exposed pad to a PCB pad that uses multiple ground vias to provide heat transfer out of the device and into the PCB ground planes. These multiple ground vias are also required to achieve the specified RF performance. |  |

# Absolute Maximum Ratings

Stresses beyond those listed below may cause permanent damage to the device. Functional operation of the device at these or any other conditions beyond those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                                                  | Symbol               | Minimum | Maximum                                 | Units |

|----------------------------------------------------------------------------|----------------------|---------|-----------------------------------------|-------|

| V <sub>DD</sub> to GND                                                     | $V_{DD}$             | -0.3    | +6.0                                    | ٧     |

| V1 to GND                                                                  | $V_{Logic}$          | -0.3    | Lower of (V <sub>DD</sub> + 0.3V, 3.6V) | ٧     |

| RF1, RF2 to GND                                                            | $V_{RF}$             | -0.3    | +0.3                                    | V     |

| RF Input Power Port 1 or 2. Other port terminated into 50 $\Omega$ [a]     | P <sub>RF12</sub>    |         | 33                                      |       |

| RF Input Power Port 1 in isolation. Port 2 terminated into 50 $\Omega$ [a] | P <sub>RF1_ISO</sub> |         | 23                                      | dBm   |

| RF Input Power Port 2 in isolation. Port 1 terminated into 50 $\Omega$ [a] | $P_{RF2\_ISO}$       |         | 30                                      |       |

| Maximum Junction Temperature                                               | $T_{jmax}$           |         | +140                                    | °C    |

| Storage Temperature Range                                                  | T <sub>ST</sub>      | -65     | +150                                    | °C    |

| Lead Temperature (soldering, 10s)                                          | $T_{LEAD}$           |         | +260                                    | °C    |

| ElectroStatic Discharge – HBM (JEDEC/ESDA JS-001-2012)                     | $V_{ESDHBM}$         |         | 2000<br>(Class 2)                       | V     |

| ElectroStatic Discharge – CDM (JEDEC 22-C101F)                             | $V_{ESDCDM}$         |         | 1000<br>(Class C3)                      | V     |

a.  $V_{DD}=2.7~V$  to 5.5 V, 30 MHz  $\leq$  F<sub>RF</sub>  $\leq$  8000 MHz,  $T_c=105^{\circ}C$ ,  $Z_S=Z_L=50$  ohms.

# Recommended Operating Conditions

Table 3. Recommended Operating Conditions

| Parameter                             | Symbol            | Condition                              |                                     | Minimum             | Typical | Maximum                          | Units |

|---------------------------------------|-------------------|----------------------------------------|-------------------------------------|---------------------|---------|----------------------------------|-------|

| Power supply voltage                  | $V_{DD}$          |                                        |                                     | 2.7                 |         | 5.5                              | V     |

| Logic Input High Threshold            | V <sub>IH</sub>   | 2.7 V ≤ V <sub>DD</sub> ≤ 5.5 V        |                                     | 1.1 [a]             |         | Lower of (V <sub>DD</sub> , 3.6) | ٧     |

| Logic Input Low Threshold             | V <sub>IL</sub>   |                                        |                                     | -0.3 <sup>[b]</sup> |         | 0.6                              | ٧     |

| Operating Temperature<br>Range        | T <sub>CASE</sub> | Exposed Paddle Temperature             |                                     | -55                 |         | +105                             | °C    |

| RF Frequency Range                    | F <sub>RF</sub>   |                                        |                                     | 30                  |         | 8000 <sup>[c]</sup>              | MHz   |

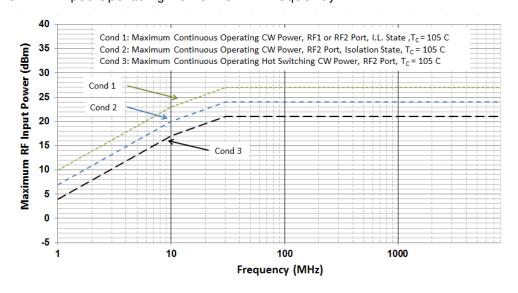

|                                       |                   | RF1 or RF2 as the input                | T <sub>c</sub> = 85 <sup>o</sup> C  |                     |         | 30                               |       |

|                                       |                   | (Insertion loss state)                 | T <sub>c</sub> = 105 <sup>o</sup> C |                     |         | 27                               | dBm   |

| RF Continuous                         |                   | RF1 as the input (Isolation state)     | T <sub>c</sub> = 85 <sup>o</sup> C  |                     |         | 20                               |       |

| Input CW Power (Non-Switched) [d]     | P <sub>RF</sub>   |                                        | T <sub>c</sub> = 105 <sup>o</sup> C |                     |         | 17                               |       |

| (                                     |                   | RF2 as the input (Isolation state)     | T <sub>c</sub> = 85 <sup>o</sup> C  |                     |         | 27                               |       |

|                                       |                   |                                        | T <sub>c</sub> = 105 <sup>o</sup> C |                     |         | 24                               |       |

| RF Continuous                         |                   | Applied to RF2 input switching between | T <sub>c</sub> = 85 <sup>o</sup> C  |                     |         | 24                               |       |

| Input Power (RF Hot Switching CW) [d] | P <sub>RFSW</sub> | Insertion loss to Isolation states     | T <sub>c</sub> = 105 <sup>o</sup> C |                     |         | 21                               | dBm   |

| RF1/2 Port Impedance                  | $Z_{RFx}$         | Insertion loss state                   |                                     |                     | 50      |                                  | Ω     |

| RF2 Port Impedance                    | $Z_{RFx}$         | Isolation state                        | Isolation state                     |                     | 50      |                                  | Ω     |

- a. Items in min/max columns in bold italics are Guaranteed by Test.

- b. Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

- c. To achieve best performance from 5 8 GHz, the use of bypass capacitors as described in the Applications Circuit section is required.tee

- d. Levels based on:  $V_{DD}$  = 2.7 V to 5.5 V, 30 MHz  $\leq$  F<sub>RF</sub>  $\leq$  8000 MHz,  $Z_{S}$  =  $Z_{L}$  = 50 ohms. See Figure 3 for power handling derating vs RF frequency.

Figure 3. Maximum RF Input Operating Power vs. RF Frequency

4

#### **Electrical Characteristics**

#### Table 4. Electrical Characteristics

Typical Application Circuit:  $V_{DD} = 3.3 \text{ V}$ ,  $T_{CASE} = +25 \,^{\circ}\text{C}$ ,  $F_{RF} = 2 \,^{\circ}\text{GHz}$ , Driven Port = RF2, Input power = 0 dBm,  $Z_S = Z_L = 50 \,^{\circ}\Omega$ . PCB board trace and connector losses are de-embedded unless otherwise noted. IIP2 / IIP3:  $P_{IN} = 13 \,^{\circ}\text{dBm}$  / tone, 50 MHz spacing. Performance beyond 5 GHz based on application circuit (Figure 20) using best RF PCB design practices. See note c for details.

| Parameter                                      | Symbol                            | Condition                   | Min | Тур                 | Max                 | Units |

|------------------------------------------------|-----------------------------------|-----------------------------|-----|---------------------|---------------------|-------|

| Logic Current                                  | I <sub>IH</sub> , I <sub>IL</sub> |                             | -1  |                     | +1                  | μΑ    |

|                                                |                                   | V <sub>DD</sub> =3.3 V      |     | 190                 | 304 <sup>[a]</sup>  |       |

| DC Current                                     | I <sub>DD</sub>                   | V <sub>DD</sub> =5.0 V      |     | 220                 | 374                 | μΑ    |

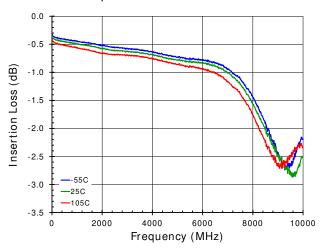

|                                                |                                   | 0.03 GHz                    |     | 0.38                |                     |       |

|                                                |                                   | 0.35 GHz                    |     | 0.44                |                     |       |

|                                                |                                   | 1.0 GHz                     |     | 0.50                | 0.70 <sup>[b]</sup> |       |

|                                                |                                   | 2.0 GHz                     |     | 0.55                | 0.80                |       |

| Incombine Land                                 | IL                                | 3.0 GHz                     |     | 0.60                | 0.85                | -10   |

| Insertion Loss                                 | IL IL                             | 4.0 GHz                     |     | 0.67                | 0.90                | dB    |

|                                                |                                   | 5.0 GHz                     |     | 0.75                | 1.00                |       |

|                                                |                                   | 6.0 GHz                     |     | 0.80 [c]            |                     |       |

|                                                |                                   | 7.0 GHz                     |     | 1.00 [c]            |                     |       |

|                                                |                                   | 8.0 GHz                     |     | 1.55 <sup>[c]</sup> |                     |       |

|                                                |                                   | 0.03 GHz                    |     | 85                  |                     |       |

|                                                |                                   | 0.35 GHz                    | 66  | 73                  |                     | dB    |

|                                                |                                   | 1.0 GHz                     | 55  | 61                  |                     |       |

|                                                |                                   | 2.0 GHz                     | 45  | 51                  |                     |       |

| Isolation                                      | ISO                               | 3.0 GHz                     | 40  | 46                  |                     |       |

| Isolation                                      | 150                               | 4.0 GHz                     | 35  | 41                  |                     |       |

|                                                |                                   | 5.0 GHz                     | 30  | 37                  |                     |       |

|                                                |                                   | 6.0 GHz                     |     | 33 <sup>[c]</sup>   |                     |       |

|                                                |                                   | 7.0 GHz                     |     | 29 <sup>[c]</sup>   |                     |       |

|                                                |                                   | 8.0 GHz                     |     | 26 <sup>[c]</sup>   |                     |       |

| Max RF2 Port                                   | VSWR                              | Insertion Loss to Isolation |     | 3.3:1               |                     |       |

| VSWR During Switching                          | VOVIN                             | Isolation to Insertion Loss |     | 2.0:1               |                     |       |

|                                                |                                   | 2.0 GHz                     |     | 27                  |                     |       |

|                                                |                                   | 3.0 GHz                     |     | 25                  |                     |       |

| DE4_DE0_Datum_1                                |                                   | 4.0 GHz                     |     | 20                  |                     |       |

| RF1, RF2 Return Loss<br>(Insertion Loss State) | RF <sub>RL</sub>                  | 5.0 GHz                     |     | 18                  |                     | dB    |

| (                                              |                                   | 6.0 GHz                     |     | 20 <sup>[c]</sup>   |                     |       |

|                                                |                                   | 7.0 GHz                     |     | 25 <sup>[c]</sup>   |                     |       |

|                                                |                                   | 8.0 GHz                     |     | 13 <sup>[c]</sup>   |                     |       |

a. Items in min/max columns in *bold italics* are Guaranteed by Test.

b. Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

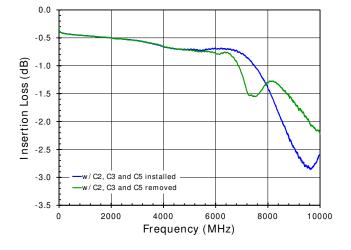

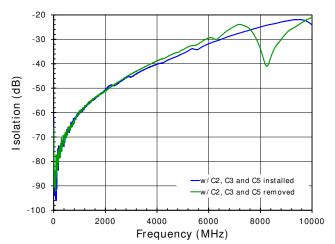

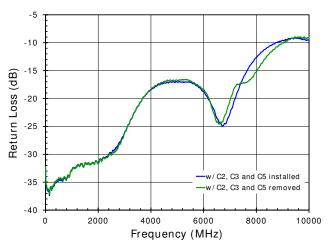

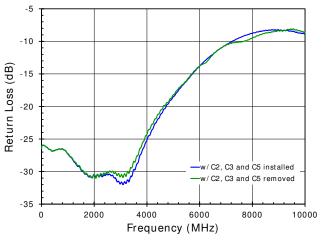

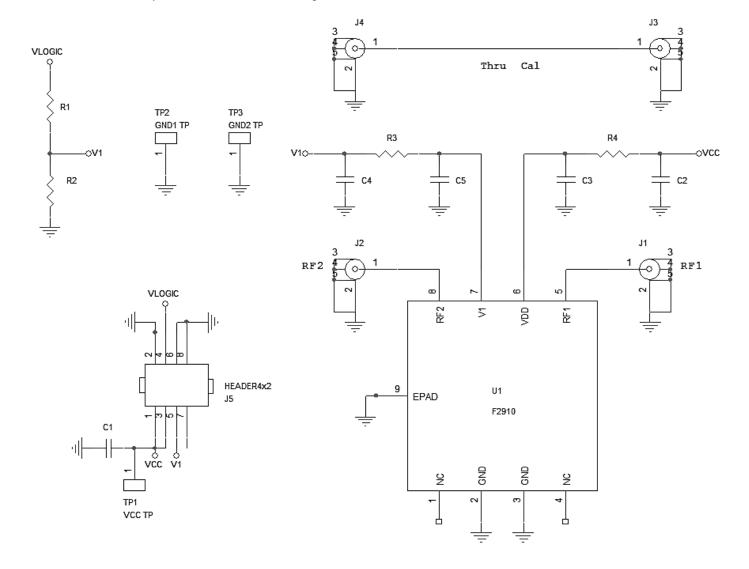

c. To achieve performance beyond 5 GHz, the use of bypass capacitors (BOM C2, C3, and C5) installed close to the device as embodied in the evaluation board per the application circuit (Figure 20) is required. See the appropriate Typical Operating Conditions graphs.

## Electrical Characteristics (Cont.)

Typical Application Circuit:  $V_{DD} = 3.3 \text{ V}$ ,  $T_{CASE} = +25 \,^{\circ}\text{C}$ ,  $F_{RF} = 2 \,\text{GHz}$ , Driven Port = RF2, Input power = 0 dBm,  $Z_S = Z_L = 50 \,\Omega$ . PCB board trace and connector losses are de-embedded unless otherwise noted. IIP2 / IIP3:  $P_{IN} = 13 \,\text{dBm}$  / tone, 50 MHz spacing. Performance beyond 5 GHz based on application circuit (Figure 20) using best RF PCB design practices. See note c for details.

| Parameter                         | Symbol               | Condition                                                              |                     | Minimum | Typical           | Maximum | Units |  |

|-----------------------------------|----------------------|------------------------------------------------------------------------|---------------------|---------|-------------------|---------|-------|--|

|                                   | 2.0 GHz              |                                                                        |                     |         | 27                |         |       |  |

|                                   |                      | 3.0 GHz                                                                |                     |         | 27                |         |       |  |

|                                   |                      | 4.0 GHz                                                                |                     |         | 25                |         |       |  |

| RF2 Return Loss (Isolation State) | RF <sub>RLT</sub>    | 5.0 GHz                                                                |                     |         | 20                |         | dB    |  |

| (1301ation State)                 |                      | 6.0 GHz                                                                |                     |         | 15 <sup>[c]</sup> |         |       |  |

|                                   |                      | 7.0 GHz                                                                |                     |         | 12 <sup>[c]</sup> |         |       |  |

|                                   |                      | 8.0 GHz                                                                |                     |         | 10 <sup>[c]</sup> |         |       |  |

|                                   |                      | 0.03 GHz                                                               |                     |         | 34                |         |       |  |

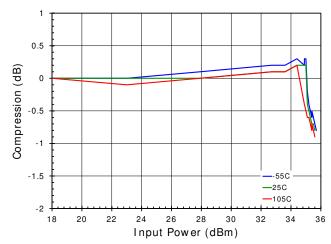

| Input 1dB Compression [d]         | ICP <sub>1dB</sub>   | 3.0 GHz                                                                |                     |         | 35                |         | dBm   |  |

|                                   |                      | 4.0 GHz                                                                |                     |         | 35                |         |       |  |

|                                   |                      | 0.03 GHz                                                               |                     |         | 33                |         | dBm   |  |

| Input 0.1dB Compression [d]       | ICP <sub>0.1dB</sub> | 3.0 GHz                                                                |                     |         | 34                |         |       |  |

|                                   |                      | 4.0 GHz                                                                |                     |         | 34                |         |       |  |

|                                   | IIP2                 | F1 = 0.35 GHz, F2 = 0.40 GHz                                           |                     |         | 123               |         |       |  |

| Input IP2 [e]                     |                      | F1 = 0.95 GHz, F2 = 1.00 GHz                                           |                     |         | 124               |         | dBm   |  |

|                                   |                      | F1 = 2.40 GHz, F2 = 2.45 GHz                                           |                     |         | 118               |         |       |  |

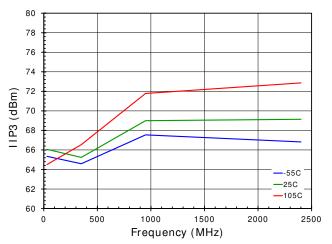

|                                   |                      | 0.03 GHz                                                               |                     |         | 65                |         |       |  |

| Input IP3 [e]                     | IIP3                 | 0.35 GHz                                                               |                     |         | 65                |         | dBm   |  |

| input ir 3 <sup>es</sup>          |                      | 1.00 GHz                                                               |                     |         | 68                |         |       |  |

|                                   |                      | 2.40 GHz                                                               |                     |         | 67                |         |       |  |

| Non-RF Driven Spurious [f]        | Spur <sub>MAX</sub>  | Any port when externally terminate                                     | ed into 50 $\Omega$ |         | -102              |         | dBm   |  |

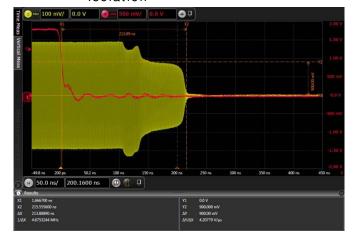

|                                   |                      | 50% control to 90% RF                                                  |                     |         | 265               | 500     |       |  |

| Switching Time                    | T <sub>SW</sub>      | 50% control to 10% RF                                                  |                     |         | 225               | 500     | - ns  |  |

|                                   | I SW                 | 50% control to RF settled to within +/- 0.1 dB of insertion loss value |                     |         | 280               |         |       |  |

| Maximum Switching Rate            | SW <sub>RATE</sub>   |                                                                        |                     |         | 25                |         | kHz   |  |

| Maximum Video Feed-through        | VID <sub>FT</sub>    | Peak transients during switching. Measured with 20 ns rise-time,       | Rise Time           |         | 25                |         | mVpp  |  |

| on RF Ports                       | VIDF                 | 0 to 3.3 V control pulse                                               | Fall Time           |         | 45                |         | шурр  |  |

- a. Items in min/max columns in bold italics are Guaranteed by Test.

- b. Items in min/max columns that are not bold/italics are Guaranteed by Design Characterization.

- c. To achieve performance beyond 5 GHz, the use of bypass capacitors (BOM C2, C3, and C5) installed close to the device as embodied in the evaluation board per the application circuit (Figure 20) is required. See the appropriate Typical Operating Conditions graphs.

- d. The input 0.1 and 1 dB compression point is a linearity figure of merit. Refer to Absolute Maximum Ratings section for the maximum RF input power.

- e. RF1 or RF2 driven IIP2 / IIP3 results when in insertion loss state. IP2 Frequency = F1 + F2.

- f. Spurious due to on-chip negative voltage generator. Spurious fundamental is approximately 5.7 MHz.

- g.  $F_{RF} = 1$  GHz.

#### Thermal Characteristics

#### Table 5. Package Thermal Characteristics

| Parameter                                                                    | Symbol                | Value | Units |

|------------------------------------------------------------------------------|-----------------------|-------|-------|

| Junction to Ambient Thermal Resistance.                                      | $\theta_{JA}$         | 159.5 | °C/W  |

| Junction to Case Thermal Resistance. (Case is defined as the exposed paddle) | $\theta_{	extsf{JC}}$ | 15.1  | °C/W  |

| Moisture Sensitivity Rating (Per J-STD-020)                                  |                       | MSL 1 |       |

# Typical Operating Conditions (TOC)

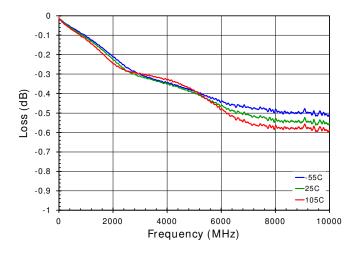

Unless otherwise noted:

- V<sub>DD</sub> = 3.3 V.

- $Z_L = Z_S = 50$  Ohms Single Ended.

- F<sub>BF</sub> = 2 GHz.

- $P_{IN} = 13 \text{ dBm} / \text{tone applied to RF2 port for two tone linearity tests.}$

- Two tone frequency spacing = 50 MHz.

- All temperatures are referenced to the exposed paddle.

- Evaluation Kit traces and connector losses are de-embedded.

- Performance beyond 5 GHz as listed in the Electrical Characteristics is based on the application circuit (Figure 20) with bypass capacitors (BOM C2, C3, and C5) installed. The capacitors must be installed in close proximity to the device as embodied in the evaluation board with best practices followed for PCB design. Performance above 5 GHz de-rated as shown in Typical Performance Characteristics plots Figure 10 to Figure 13 when application circuit with bypass capacitors is not utilized.

- Unless otherwise noted, C2, C3 and C5 are installed in following plots.

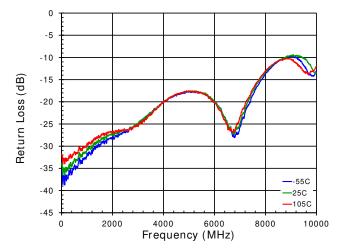

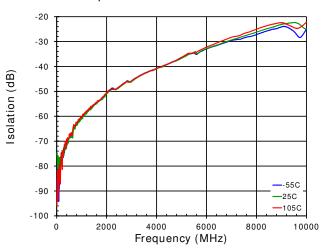

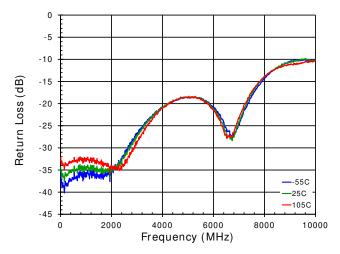

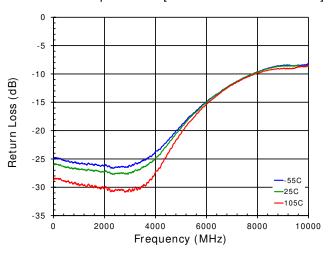

## Typical Performance Characteristics

Figure 4. Insertion Loss vs. Frequency over Temperature

Figure 6. Return Loss vs. Frequency over Temp [RF1 Insertion Loss State]

Figure 5. Isolation vs. Frequency over Temperature

Figure 7. Return Loss vs. Frequency over Temp [RF2 Insertion Loss State]

Figure 8. Return Loss vs. Frequency over

Temperature [RF2 Terminated State]

Figure 10. Insertion Loss vs. Frequency With and Without Capacitors

Figure 9. Evaluation Board Loss vs. Frequency

Figure 11. Isolation vs. Frequency With and Without Capacitors

Figure 12. Return Loss vs. Frequency With and Without Capacitors

Figure 14. Input IP3 vs. Frequency

Figure 16. Switching Time Isolation to Insertion loss

Figure 13. Return Loss vs. Frequency With and Without Capacitors [State 0]

Figure 15. 1 dB Compression at 3 GHz

Figure 17. Switching Time Insertion Loss to Isolation

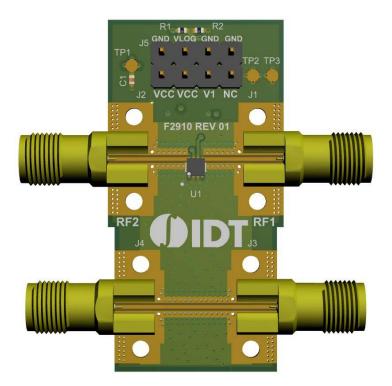

## **Evaluation Kit Picture**

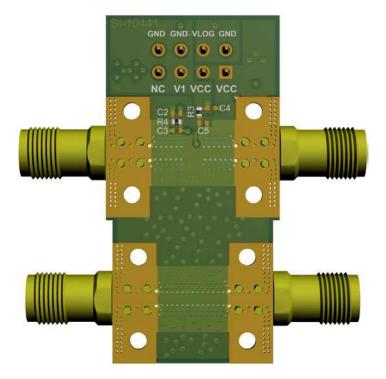

Figure 18. Top View

Figure 19. Bottom View

#### Control Mode

Table 6. Switch Control Truth Table

| V1<br>(Logic) | State          | Port Match                                            |

|---------------|----------------|-------------------------------------------------------|

| 0             | Isolation      | RF1 port reflective, RF2 port terminated into 50 ohms |

| 1             | Insertion Loss | RF1 and RF2 port matched to 50 ohm                    |

# Evaluation Kit / Applications Circuit

Figure 20. Electrical Schematic

Note: The use of bypass capacitors C2, C3, and C5 as listed in the BOM (Table 7) is required to achieve performance as listed in the Electrical Characteristics for frequencies beyond 5 GHz. The capacitors must be installed in close proximity to the device as embodied in the evaluation board with best practices followed for PCB design.

Table 7. Bill of Material (BOM)

| Part Reference | QTY                                              | Description                                        | Manufacturer Part # | Manufacturer       |

|----------------|--------------------------------------------------|----------------------------------------------------|---------------------|--------------------|

| C1             | 1                                                | 0.1 μF ±10%, 16V, X7R, Ceramic Capacitor (0402)    | GRM155R71C104KA88D  | Murata             |

| C2             | 1                                                | 0.5 pF ±0.1 pF, 50V, C0G, Ceramic Capacitor (0402) | GJM1555C1HR50BB01   | Murata             |

| C3             | 1                                                | 4.5 pF ±0.1 pF, 50V, C0G, Ceramic Capacitor (0402) | GJM1555C1H4R5BB01D  | Murata             |

| C4             | 0                                                | Not Installed (0402)                               |                     |                    |

| C5             | 1                                                | 4.9 pF ±0.1 pF, 50V, C0G, Ceramic Capacitor (0402) | GJM1555C1H4R9BB01   | Murata             |

| R1             | 1                                                | 15k $\Omega$ ±1%, 1/10W, Resistor (0402)           | ERJ-2RKF1502X       | Panasonic          |

| R2             | 1                                                | 18k Ω ±1%, 1/10W, Resistor (0402)                  | ERJ-2RKF1802X       | Panasonic          |

| R3, R4         | 2                                                | 0 $\Omega$ 1/10W, Jumper (0402)                    | ERJ-2GE0R00X        | Panasonic          |

| J1 – J4        | 4                                                | SMA Edge Mount                                     | 142-0761-881        | Cinch Connectivity |

| J5             | 1                                                | CONN HEADER VERT 4x2 POS GOLD                      | 67997-108HLF        | Amphenol FCI       |

| TP1            | 0                                                | Not Installed (Red Test Point Loop)                |                     |                    |

| TP2, TP3       | TP2, TP3 0 Not Installed (Black Test Point Loop) |                                                    |                     |                    |

| U1             | 1                                                | SPST Switch 2 mm x 2 mm 8 pin DFN                  | F2910NBGP/W         | IDT                |

|                | 1                                                | Printed Circuit Board                              | F2910 EVKIT REV 01  | IDT                |

### **Evaluation Kit Operation**

## Default Start-up

Control pins include no internal pull-down resistors to logic LOW or pull-up resistors to logic HIGH.

### Power Supplies

A common  $V_{CC}$  power supply should be used for all pins requiring DC power. All supply pins should be bypassed with external capacitors to minimize noise and fast transients. Supply noise can degrade noise figure and fast transients can trigger ESD clamps and cause them to fail. Supply voltage change or transients should have a slew rate smaller than 1 V / 20  $\mu$ s. In addition, all control pins should remain at 0 V ( $\pm$  0.3 V) while the supply voltage ramps or while it returns to zero.

#### Control Pin Interface

If control signal integrity is a concern and clean signals cannot be guaranteed due to overshoot, undershoot, ringing, etc., the following circuit at the input of each control pin is recommended. This applies to control pin 7 as shown in Figure 21. If bypass capacitor C5 as described in the application circuit (Figure 20) is used to achieve high frequency performance optimization, the use of an additional 2 pF capacitor as shown in Figure 21 is not necessary.

Figure 21. Control Pin signal integrity improvement circuit

## External Supply Setup

Set up a V<sub>CC</sub> power supply in the voltage range of 2.7 V to 5.5 V with the power supply output disabled.

#### Logic Control Setup

Using the EVKIT to manually set the control logic:

On connector J5, connect a 2-pin shunt from  $V_{CC}$  (pin 3) to  $V_{LOGIC}$  (pin 4). This connection provides the  $V_{CC}$  voltage supply to the Eval Board logic control pull-up network. Resistors R1 and R2 form a voltage divider to set the  $V_{IH}$  level over the 2.7 V to 5.5 V  $V_{CC}$  range for manual logic control.

Connector J5 has one logic input pin: V1 (pin 5). See Table 6 for Logic Truth Table. With the pull-up network enabled (as noted above) this pin can be left open to provide a logic high through pull-up resistor R1. To set a logic low for V1, connect a 2-pin shunt on J5 from  $V_{CTL}$  (pin 5) to GND (pin 6).

Note that when using the on board R1/R2 voltage divider, the current draw from the V<sub>CC</sub> supply will be higher by approximately V<sub>CC</sub> / 33 kΩ.

Using external control logic:

Pins 3, 4, 6, 7, and 8 of J5 should have no external connections. External logic control is applied to J5 V1 (pin 5). See Table 5 for the Logic Truth Table.

#### Turn On Procedure

Setup the supplies and EVKIT as noted in the External Supply Setup and Logic Control Setup sections above.

### Enable the Vcc Supply

Set the desired logic setting to achieve the desired Table 5 configuration. Note that external control logic should not be applied without  $V_{CC}$  being present.

#### Turn Off Procedure

Set the logic control to a logic low. Disable the  $V_{\text{CC}}$  supply.

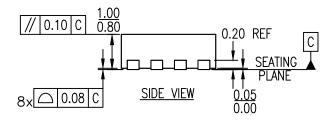

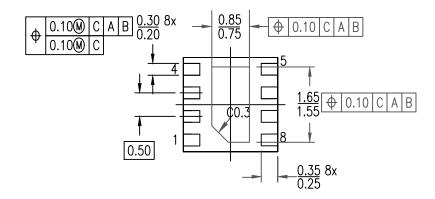

## Package Outline Drawings

The package outline drawings are appended at the end of this document and are accessible from the link below. The package information is the most current data available.

$\frac{\text{https://www.idt.com/document/psc/8-dfn-package-outline-drawing-20-x-20-x-09-mm-body-epad-08-x-16-mm-05mm-pitch-nbnbg8p3?language=en}{}$

## Ordering Information

| Orderable Part Number | Package                  | MSL Rating | Shipping Packaging | Orientation              | Temperature    |

|-----------------------|--------------------------|------------|--------------------|--------------------------|----------------|

| F2910NBGP             | 2 x 2 x 0.9 mm 8-VFQFP-N | MSL1       | Bulk               |                          | -55° to +105°C |

| F2910NBGP8            | 2 x 2 x 0.9 mm 8-VFQFP-N | MSL1       | Tape and Reel      | EIA-481-C <sup>[a]</sup> | -55° to +105°C |

| F2910EVBI             | Evaluation Board         |            |                    |                          |                |

a. Contact IDT for additional information on tape and reel orientation

### Marking Diagram

- 1. Line 1 is the part number.

- 2. Line 2 "6" is last digit of the year.

- 3. Line 2 "U" is the workweek code

- 4. Line 2 AG is the sequential code

# **Revision History**

| Revision Date Description of Change |                                                                      |

|-------------------------------------|----------------------------------------------------------------------|

| August 31, 2020                     | Updated the package outline drawings; however, no mechanical changes |

| October 25, 2020                    | Added orientation information and F2910NBGP/W part number.           |

| August 29, 2016                     | Initial release.                                                     |

**BOTTOM VIEW**

#### NOTE:

- 1. DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5-2009.

- 2. ALL DIMENSIONS ARE IN MMILLIMETERS.

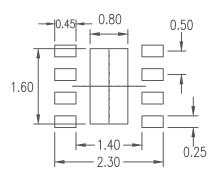

RECOMMENDED LAND PATTERN DIMENSION

#### NOTES:

- 1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW. AS VIEWED ON PCB.

- 3. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

| Package Revision History      |         |             |  |  |  |

|-------------------------------|---------|-------------|--|--|--|

| Date Created                  | Rev No. | Description |  |  |  |

| Oct 9, 2017 Rev 01 New Format |         |             |  |  |  |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/