# Smart Push-Button Reset with Two Discharge Paths

#### **Features**

- Operating Range: 2.2V~5.5V

- Supply Current in standby:  $< 1\mu A (V_{DD} = 4V)$

- Quiescent Current in Ship mode:  $< 1\mu A (V_{DD} = 4V)$

- Output Delay time (RST0 & 1 Input pins): 10s Typ.

- Reset Pulse Time (SRO, nSRO Output): 400ms Typ.

- Ship Mode Entry Delay Time (OFF Input): 15s

- Ship Mode Entry Command (OFF Input): 5 cycles

- Ship Mode Exit Delay Time (RST0 Input): Typ. 2s

- Output Discharge Time: 400ms Typ.

- Output Discharge Delay Time: 6ms Max

- ESD Protection

- ► Human Body Model: 2kV

- ► Charged Device Model: 1.5kV

- Over-Temperature Protection

- -40°C to +85°C Temperature Range

## **Applications**

- Mobile Phones & Tablets

- Wearable Devices

- Portable Instruments

- DSC, DVR, GPS

- Electronics with non-removable batteries

## **Brief Description**

The KTS1612 is a two input, two output Smart Push-Button Reset IC. A reset pulse is generated for a fixed discharge time (400ms typ) after both manual reset inputs have been held low for the reset request time of 10s.

The KTS1612 operates over the 2.2 V to 5.5V supply voltage range, consuming less than 10μA of supply current at 4V.

The reset and power sequence is controlled by RST0/RST1 and OFF signals and have the ability to drive an external P-channel MOSFET. The reset IC supports two discharge outputs DCHG0 and DCHG1.

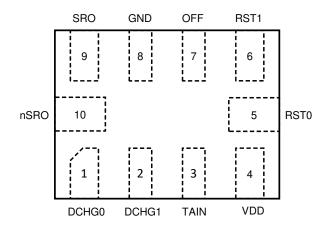

The KTS1612 is available in lead-free, fully green compliant, small 10-pin UQFN 2.0mm x 1.5mm package.

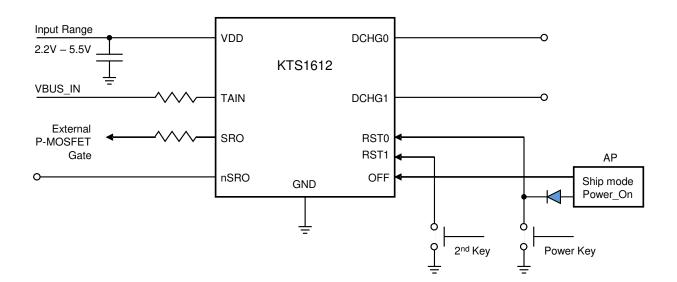

# **Typical Application**

## **Pin Descriptions**

| Pin# | Name  | Function                                      | IO Characteristics           |

|------|-------|-----------------------------------------------|------------------------------|

| 1    | DCHG0 | System supply discharge path input.           | Open-drain                   |

| 2    | DCHG1 | System supply discharge path input.           | Open-drain                   |

| 3    | TAIN  | Power input. Charger insert detection.        | R dividing circuit           |

| 4    | VDD   | Power supply input.                           | -                            |

| 5    | RST0  | Reset signal input 0.                         | Internal pull down (8MΩ)     |

| 6    | RST1  | Reset signal input 1.                         | No internal pull up resistor |

| 7    | OFF   | Digital input. Ship mode enter command input. | Internal pull down (1MΩ)     |

| 8    | GND   | GND                                           | -                            |

| 9    | SRO   | Digital output, active high (VDD)             | Push-Pull                    |

| 10   | nSRO  | Digital output, active low                    | Open-drain                   |

## UQFN2.0x1.5-10 (Top View)

10-Lead 2.0mm x 1.50mm x 0.55mm UQFN Package

$\label{eq:code} \mbox{Top Mark} \\ \mbox{KQ = Device ID Code, YY = Date Code, Z = Assembly Code}$

# **Ordering Information**

| Part Number   | Marking <sup>1</sup> | Operating<br>Temperature | Package        |

|---------------|----------------------|--------------------------|----------------|

| KTS1612EQU-TR | KQYYZ                | -40°C to +85°C           | UQFN2.0x1.5-10 |

<sup>1. &</sup>quot;KQYYZ" is the device code, date code and assembly code respectively.

# **Absolute Maximum Ratings<sup>2</sup>**

#### $(T_A = 25^{\circ}C \text{ unless otherwise noted})$

| Symbol                    | Description                                                  | Value               | Units |

|---------------------------|--------------------------------------------------------------|---------------------|-------|

| VDD,DCHG0,<br>DCHG1, RST0 | Power supply input, Discharge path input & Reset input pins. | -0.3 to +12<br>(DC) | V     |

| TAIN                      | Travel adaptor input pin.                                    | -0.3 to +30         | ٧     |

| RST1, SRO, nSRO, OFF      | Reset inputs, Digital outputs, Ship mode enter input pins    | -0.3 to +6          | ٧     |

| TJ                        | Maximum Junction Temperature Range                           | -40 to 150          |       |

| Ts                        | Storage Temperature Range                                    | -65 to 150          | °C    |

| T <sub>LEAD</sub>         | Maximum Soldering Temperature (at leads, 10sec)              | 300                 |       |

## Thermal Capabilities<sup>3</sup>

| Symbol              | Description                                        | Value | Units |

|---------------------|----------------------------------------------------|-------|-------|

| $\theta_{JA}$       | Thermal Resistance – Junction to Ambient           | 73    | °C/W  |

| P <sub>D</sub>      | Maximum Power Dissipation at T <sub>A</sub> ≤ 25°C | 1712  | mW    |

| ΔP <sub>D</sub> /°C | Derating Factor Above T <sub>A</sub> = 25°C        | 13.7  | mW/°C |

## Recommended Operating Range<sup>4</sup>

| Description                | Value        |

|----------------------------|--------------|

| VDD, DCHG0, DCHG1          | -0.3 to 5.5V |

| RST0, RST1, SRO, nSRO, OFF | -0.3 to 5V   |

| TAIN                       | -0.3 to 5.5V |

November 2018 - Revision 04d Page 3 Company Confidential

Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

<sup>3.</sup> Junction to Ambient thermal resistance is highly dependent on PCB layout. Values are based on thermal properties of the device when soldered to a PCB board.

<sup>4.</sup> The device is not guaranteed to function outside of recommended operating condition.

## Electrical Characteristics<sup>5</sup>

The *Min* and *Max* specs are applied over the full operation temperature range of -40°C to +85°C,  $V_{IN} = 2.2V$  to 5.5V unless otherwise noted, while *Typ* values are specified at  $V_{DD} = 4.0V$  and room temperature ( $T_A = 25$ °C) unless otherwise noted.

| Symbol           | Description                                    | Conditions                                                                                                    | Min                                              | Тур      | Max  | Units |

|------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------|------|-------|

| Basic Oper       | ation                                          |                                                                                                               |                                                  |          |      |       |

| VDD              | Input Voltage Range                            |                                                                                                               | 2.2                                              |          | 5.5  | V     |

| lα               | Quiescent supply current                       | Stand by when PMOS turn on (Exclude pull up/down resistor, Internal oscillator is off, V <sub>DD</sub> = 4V)  |                                                  |          | 1    | μА    |

| l <sub>OFF</sub> | Ship mode current                              | Stand by when PMOS turn off (Exclude pull up/down resistor, Internal oscillator is off, V <sub>DD</sub> = 4V) |                                                  |          | 1    | μА    |

| Iss              | Operation current                              | Active (Before reset signal output, Internal oscillator is on, $V_{DD} = 4V$ )                                |                                                  |          | 10   | μА    |

| Digital IO       |                                                |                                                                                                               |                                                  |          |      |       |

| V <sub>IL</sub>  | Digital input logic low level                  | RST0, RST1, OFF pin                                                                                           |                                                  |          | 0.4  | V     |

| VIH              | Digital input logic high level                 | $V_{DD} = 2.5V \text{ to } 4.6V$                                                                              | 1.0                                              |          |      | V     |

| V <sub>OL</sub>  | Digital output logic low level                 | SRO pin, I=1.2uA                                                                                              |                                                  |          | 0.3  | V     |

| Voh              | Digital output logic high level                | (V <sub>DD</sub> =4V)                                                                                         | 0.85*V <sub>DD</sub>                             | $V_{DD}$ |      | V     |

| IL               | RST0/RST1 input leakage current                |                                                                                                               | -                                                | -        | 1    | μΑ    |

| Vol              | Digital output logic low level                 | nSRO, lo=2mA                                                                                                  |                                                  |          | 0.3  | V     |

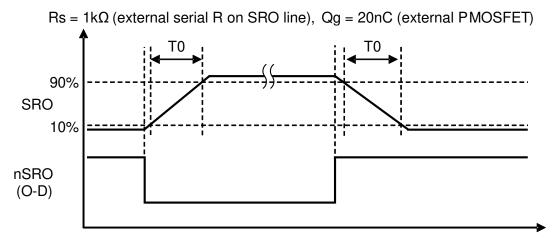

| To               | SRO rising and falling time                    | $(V_{DD} = 4V, R_S = 1k\Omega, Qg = 20nC)$                                                                    | 1                                                |          | 3    | ms    |

| TAIN             |                                                |                                                                                                               |                                                  |          |      | •     |

| VTA_detection    | R <sub>TA</sub> input active threshold voltage | Voltage before external 100K pull up resistor                                                                 | 3.8                                              | -        | 4.6  | V     |

| T <sub>TA</sub>  | Debounce time                                  | RST0,RST1,TAIN                                                                                                |                                                  | 10       |      | ms    |

| RESET            |                                                |                                                                                                               |                                                  |          |      |       |

| T <sub>R</sub>   | Reset request time                             | $V_{DD} = 4V$                                                                                                 | 8.5                                              | 10       | 11.5 | S     |

| T <sub>D</sub>   | Discharge time                                 |                                                                                                               | 340                                              | 400      | 460  | ms    |

| T <sub>dd</sub>  | Discharge delay time                           |                                                                                                               | 4                                                | 5        | 6    | ms    |

| I <sub>D</sub>   | DCHGx discharge current, V <sub>OUT</sub> = 4V |                                                                                                               | 30                                               | 52       | 67   | mA    |

| SHIP MODE        |                                                |                                                                                                               |                                                  |          |      |       |

| R_OFF            | OFF pin pull down resistor                     |                                                                                                               |                                                  | 1        |      | МΩ    |

| Tdo              | OFF pin debounce time                          |                                                                                                               |                                                  | 250      | 350  | μs    |

| _                | Ship mode enter delay                          |                                                                                                               | 12                                               | 15       | 18   | s     |

| Ts               | Command                                        |                                                                                                               | -                                                | 5        | -    | cycle |

| T <sub>1</sub>   | HIGH and LOW hold time                         | 50% duty cycle                                                                                                | 1                                                | 2        |      | ms    |

| T <sub>2</sub>   | Total 5 pulses time                            |                                                                                                               |                                                  |          | 100  | ms    |

| T <sub>3</sub>   | Time of RST keep L to exit ship mode           | $V_{DD} = 4V$                                                                                                 | 1.6                                              | 2        | 2.4  | s     |

| ESD PROTE        | ECTION                                         |                                                                                                               |                                                  | •        |      | •     |

|                  | Human Body Model (HBM)                         | All pins                                                                                                      |                                                  | ±2       |      | kV    |

| V <sub>ESD</sub> | IEC61000-4-2 Contact discharge                 | V <sub>DD</sub> pin                                                                                           |                                                  | ±8       |      | kV    |

|                  | IEC61000-4-2 Air gap discharge                 | V <sub>DD</sub> pin                                                                                           | 0.85*V <sub>DD</sub> - 1 3.8 8.5 340 4 30 12 - 1 | ±15      |      | kV    |

|                  | J-1 J-1 J-                                     | 1                                                                                                             |                                                  |          |      | 1     |

<sup>5.</sup> All specifications are 100% production tested at  $T_A = +25$ °C, unless otherwise noted. Specifications are over -40°C to +85°C and are guaranteed by design.

November 2018 - Revision 04d Page 4 Company Confidential

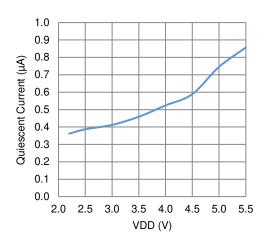

## **Typical Characteristics**

$V_{DD} = 4V$ ,  $T_A = 25$ °C unless otherwise specified.

#### **Quiescent Current vs. VDD**

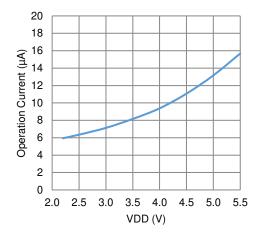

## Operation Current vs. VDD (before Reset pulse)

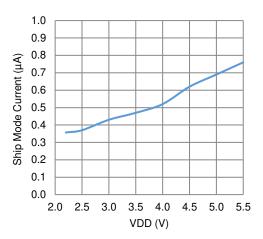

#### **Ship Mode Current vs. VDD**

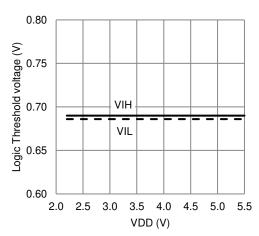

#### RST0/RST1 Digital Input Logic Threshold Vs. VDD

# **Typical Characteristics (continued)**

V<sub>DD</sub> = 4V, OFF = Low, TAIN = GND, T<sub>A</sub> = 25°C unless otherwise specified.

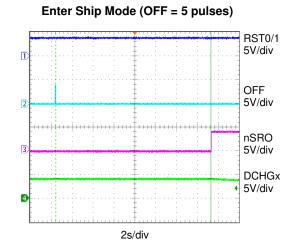

# Enter Reset Mode RST0/1 5V/div SRO 5V/div nSRO 5V/div DCHGX 5V/div

2s/div

#

100ms/div

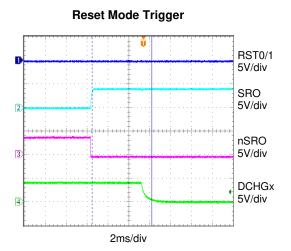

**Reset Mode Pulse**

## **Function Description**

#### **Real Value Table**

#### **Table 1. Logic Real Value Table**

("H" = High level, "L" = Low level, "OPEN" = internal FET is open, "↑" = rising edge, "↓" = falling edge)

| Pin   |       |      | Event | :0   |          |         | STATE | 0     | Event0        |          | State 1 Time between |          | Time<br>between      | State 2  |      |          |

|-------|-------|------|-------|------|----------|---------|-------|-------|---------------|----------|----------------------|----------|----------------------|----------|------|----------|

| State | AVDD  | RST0 | RST1  | TAIN | OFF      | SRO     | nSRO  | DCHGx | For<br>(in s) | SRO      | nSRO                 | DCHGx    | State 1 &<br>State 2 | SRO      | nSRO | DCHGx    |

| POR   | VDD ↑ | Х    | Х     | Х    | Х        | unknown | OPEN  | OPEN  | 20m           | Н        | Х                    | Х        | То                   | L        | OPEN | OPEN     |

| DEGET | VDD   | Н    | Н     | Х    | L        | L       | OPEN  | OPEN  | -             | L        | OPEN                 | OPEN     | -                    | L        | OPEN | OPEN     |

| RESET | VDD   | L    | L     | Х    | Х        | L       | OPEN  | OPEN  | 10            | <b>†</b> | <b>↓</b>             | <b>↓</b> | Td+2Tdd              | <b>↓</b> | †    | <b>†</b> |

| ENTER | VDD   | Х    | Х     | Х    | 5 pulses | L       | OPEN  | OPEN  | 15            | <b>†</b> | OPEN                 | OPEN     | 0                    | Н        | OPEN | OPEN     |

| SHIP  | VDD   | Н    | Н     | L    | L        | L       | OPEN  | OPEN  | Χ             | L        | OPEN                 | OPEN     | 0                    | L        | OPEN | OPEN     |

| EXIT  | VDD   | Х    | Х     | Н    | Х        | Н       | OPEN  | OPEN  | 10m           | Н        | OPEN                 | OPEN     | 0                    | L        | OPEN | OPEN     |

| SHIP  | VDD   | L    | Х     | Χ    | Х        | Н       | OPEN  | OPEN  | 2             | Н        | OPEN                 | OPEN     | 0                    | L        | OPEN | OPEN     |

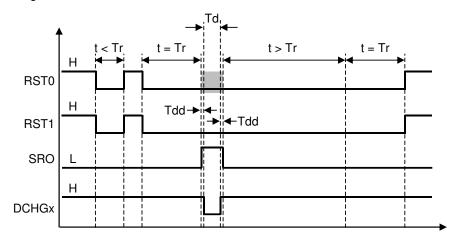

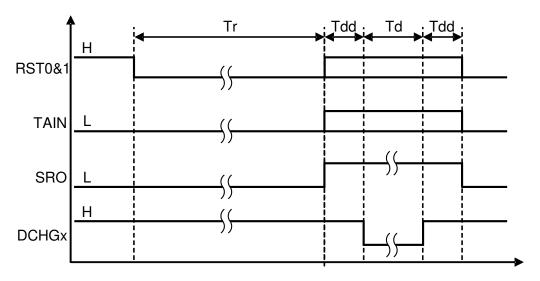

#### **Reset Timing**

Reset occurs only after both RST0 and RST1 stay low for Tr duration, SRO output goes high then the discharge paths DCHG0 and DCHG1 are turned on (pulled down to GND). After Td discharge time, the discharge paths are turned off then SRO output goes low.

If RST0 & RST1 stay low indefinitely, KTS1612 only resets one time.

RST0 & RST1 have highest priority. During Tr & Td time period, if there is an adaptor detection signal or enter ship mode signal, KTS1612 will continue the reset process. During Tr & Td time period, KTS1612 ignores the input signals including TAIN, OFF.

Figure 1. Reset Timing

November 2018 - Revision 04d Page 7 Company Confidential

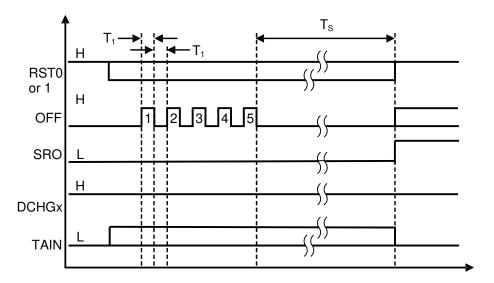

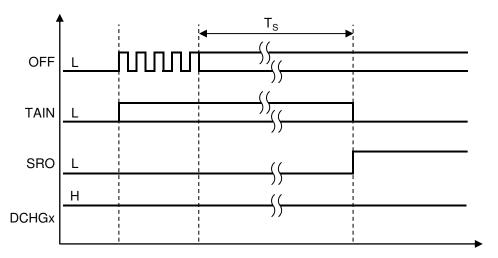

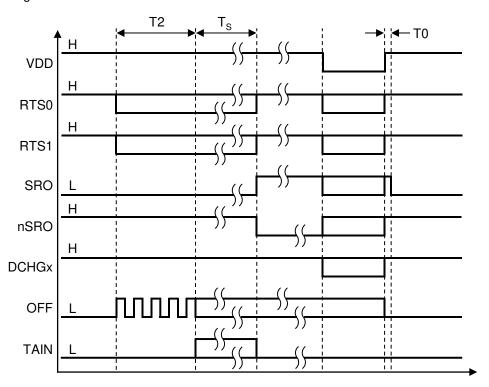

## **Ship Mode Enter and Exit Timing**

The ship mode enter command consists of 5 pulses in a square waveform with 50% duty and 4ms period. During Ts period, KTS1612 ignores all input signals.

Figure 2. Ship Mode Enter Timing

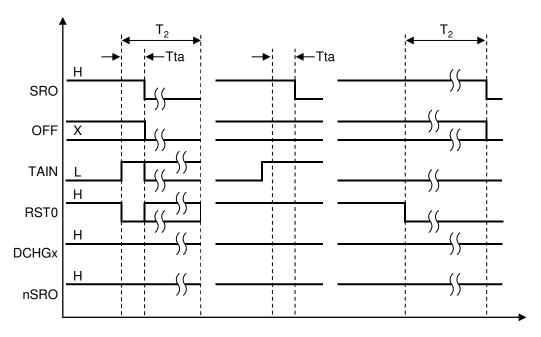

There are two triggers to exit ship mode: Adaptor is plugged in or RST0 input stays low for 2 seconds. If Adaptor in and RST0 input are low at same time, Adaptor detection has higher priority.

Figure 3. Ship Mode Exit Timing

November 2018 - Revision 04d Page 8 Company Confidential

#### Soft Turn ON and OFF

SRO output has soft turn on and turn off feature in order to reduce VBAT rising and falling overshoot. The output rising and falling time equal to 2ms typical.

nSRO is an open-drain output pin, there is no soft turn on & off feature for nSRO. The timing of SRO and nSRO is shown in Figure 4:

Figure 4. SRO Soft Turn ON and OFF Timing

## **VSYS Turn OFF and Discharge Timing**

#### 1) Reset

When a reset happens, KTS1612 first turns off the external MOSFET controlled by SRO to disconnect the battery, then starts the discharge with DCHGx.

Figure 5. Reset SRO and DCHGx Timing

2) Ship Mode Enter During ship mode enter process, DCHGx will not discharge.

November 2018 - Revision 04d Page 9 Company Confidential

Figure 6. Ship Mode Enter & SRO & DCHGx Timing

3) VDD falling and Power On Reset state.

Figure 7. Power ON Reset

November 2018 - Revision 04d Page 10 Company Confidential

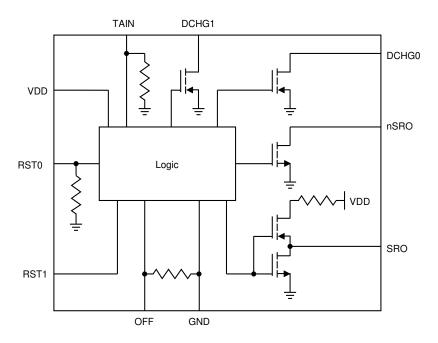

# **Functional Block Diagram**

Figure 8. Block Diagram

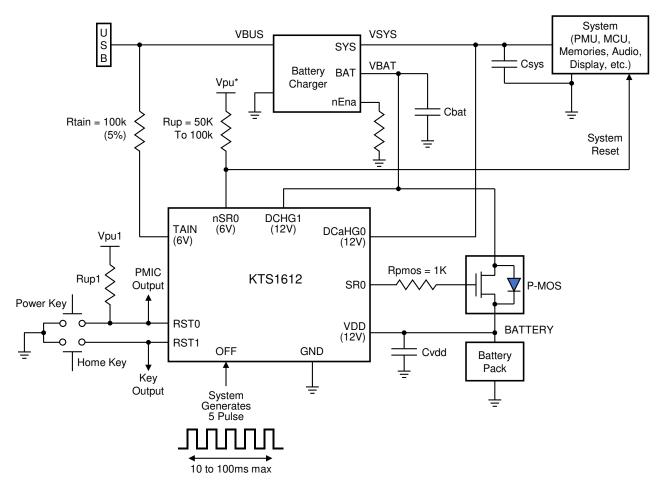

## **Application Circuit**

$Rup1 = 50 K^{\sim} 100 K\Omega$

Figure 9. Application Circuit

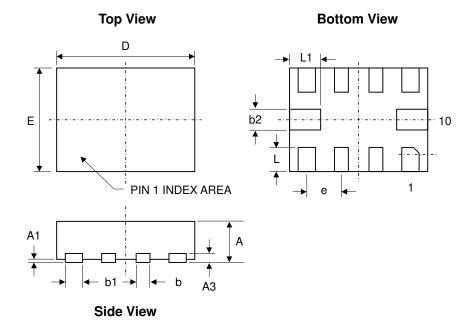

## **Packaging Information**

## UQFN2.0x1.5-10 (2.0mm x 1.50mm x 0.55mm)

| Dimension   |          | mm      |      |  |  |  |

|-------------|----------|---------|------|--|--|--|

| Dilliension | Min.     | Тур.    | Max. |  |  |  |

| Α           | 0.50     | 0.55    | 0.60 |  |  |  |

| A1          | 0.00     | -       | 0.05 |  |  |  |

| A3          | 0.       | 152 REF |      |  |  |  |

| b           | 0.15     | 0.20    | 0.25 |  |  |  |

| b1          | 0.20     | 0.25    | 0.30 |  |  |  |

| b2          | 0.25     | 0.30    | 0.35 |  |  |  |

| D           | 1.95     | 2.00    | 2.05 |  |  |  |

| D2          | -        | -       | -    |  |  |  |

| Е           | 1.45     | 1.50    | 1.55 |  |  |  |

| E2          | -        | -       |      |  |  |  |

| е           | 0.50 REF |         |      |  |  |  |

| L           | 0.30     | 0.35    | 0.40 |  |  |  |

| L1          | 0.40     | 0.45    | 0.50 |  |  |  |

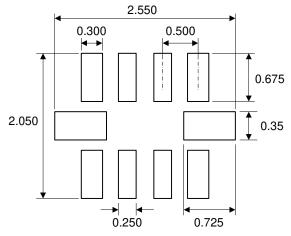

## **Recommended Footprint**

<sup>\*</sup> Dimensions are in millimeters.

Kinetic Technologies cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Kinetic Technologies product. No intellectual property or circuit patent licenses are implied. Kinetic Technologies reserves the right to change the circuitry and specifications without notice at any time.