## Intel<sup>®</sup> 82801CAM I/O Controller Hub 3 (ICH3-M)

**Datasheet**

July 2001

Document Number: 290716-001

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> I/O Controller Hub 3 (ICH3-M) component may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling

1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM.

Intel, Pentium, and Intel SpeedStep are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright© 2001, Intel Corporation

### **int**el<sup>®</sup>

# Intel<sup>®</sup> 82801CAM ICH3-M Features

- PCI Bus I/F

- Supports PCI Rev 2.2 Specification at 33 MHz

- 133 MByte/sec maximum throughput Supports up to 6 master devices on PCI

- One PCI REQ/GNT pair can be given higher arbitration priority (intended for external

- IEEE 1394 host controller)

- Integrated LAN Controller

- WfM 2.0 Compliant

- Interface to discrete LAN Connect component

- 10/100 Mbit/sec Ethernet support - 1 Mbit/sec HomePNA\* support

- Integrated IDE Controller

- New: Supports "Native Mode" Register and Interrupt support

- Independent timing of up to 4 drives, with separate IDE connections for Primary and Secondary cables

- Ultra ATA/100/66/33, BMIDE and PIO modes

- Tri-state modes to enable mobile swap bay

- USB

- New: Includes 3 UHCI Host Controllers, increasing the number of external ports to six

- Supports wake-up from sleeping states S1-S4

- Supports legacy Keyboard/Mouse software

- AC'97 Link for Audio and Telephony CODECs

- Audio Codec '97, Revision 2.2 compliant - Independent bus master logic for 5 channels (PCM

- In/Out, Mic Input, Modem In/Out) Separate independent PCI functions for Audio and Modem

- Support for up to six channels of PCM audio output (full AC3 decode)

- Supports wake-up events

- Interrupt Controller

- Support up to 8 PCI interrupt pins

- Supports PCI 2.2 Message Signaled Interrupts

- Two cascaded 82C59 with 15 interrupts

- Integrated I/O APIC capability with 24 interrupts

- Supports Serial Interrupt Protocol

- Supports Processor System Bus interrupt delivery

- 1.8 V operation with 3.3 V I/O

- 5V tolerant buffers on IDE, PCI, USB Overcurrent and Legacy signals

- Timers Based on 82C54 - System timer, Refresh request, Speaker tone output

- External Glue Integration

- Integrated Pull-up, Pull-down and Series Termination resistors on IDE, CPU I/F, and USB

- Power Management Logic ACPI 1.0 compliant

- ACPI-defined power states C1-C4, S1, S3-S5

- ACPI Power Management Timer

- Support for "Intel<sup>®</sup> SpeedStep<sup>™</sup> Technology" CPU power control

- New: Support for "Deeper Sleep" power state

- PCI CLKRUN# and PME# support

- SMI# generation

- All registers readable/restorable for proper resume from 0 V suspend states

- Support for APM-based legacy power management for non-ACPI implementations

- Firmware Hub (FWH) I/F supports BIOS Memory size up to 8 MB

- Low Pin count (LPC) I/F

- Allows connection of legacy ISA and X-Bus devices such as Super I/O

- Supports two Master/DMA devices.

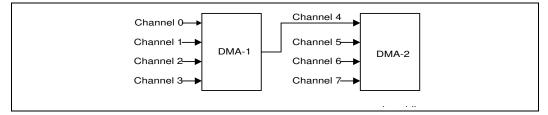

- Enhanced DMA Controller

- Two cascaded 8237 DMA controllers

- PCI DMA: Supports PC/PCI-Includes two PC/PCI REQ#/GNT# pairs

- Supports LPC DMA

- Supports DMA Collection Buffer to provide Type-F DMA performance for all DMA channels

- Real-Time Clock — 256-byte battery-backed CMOS RAM

- System TCO Reduction Circuits

- Timers to generate SMI# and Reset upon detection of system hang

- Timers to detect improper processor reset

- Integrated processor frequency strap logic

- New: Supports ability to disable external devices

- SMBus

- Host interface allows processor to communicate via SMBus

- Slave interface allows an external Microcontroller to access system resources

- Compatible with most 2-Wire components that are also I<sup>2</sup>C\* compatible

- New: Supports SMBus 2.0 Specification

- GPIO

- TTL, Open-Drain, Inversion

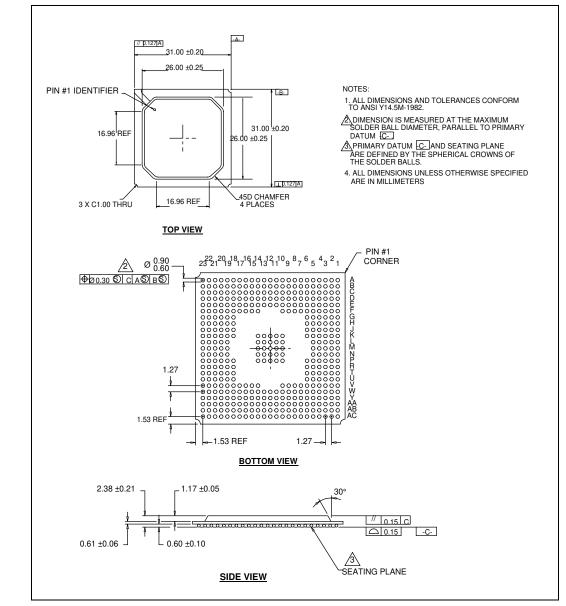

- New: Package 31x31 mm 421 BGA

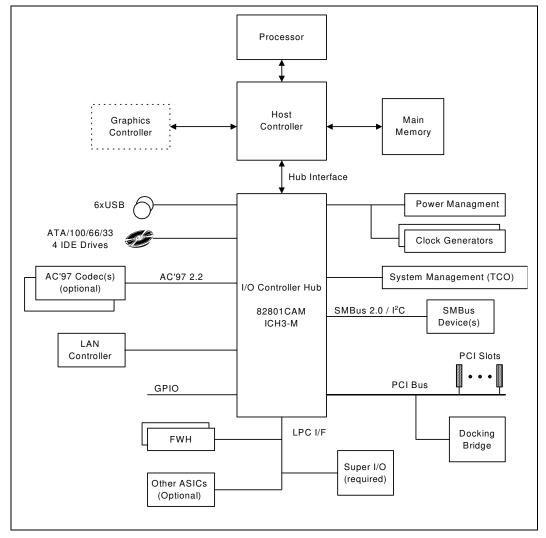

#### **System Configuration**

# int<sub>e</sub>l *Contents*

| 1 | Intro        | duction             |                                          | 1-1  |

|---|--------------|---------------------|------------------------------------------|------|

|   | 1.1          | About T             | his Datasheet                            | 1-1  |

|   | 1.2          | Overvie             | εw                                       | 1-3  |

| 2 | Sign         | al Desc             | ription                                  | 2-1  |

|   | 2.1          |                     | erface to Host Controller                |      |

|   | 2.2          |                     | LAN Connect                              |      |

|   | 2.3          |                     | OM Interface                             |      |

|   | 2.4          |                     | re Hub Interface                         |      |

|   | 2.5          |                     | erface                                   |      |

|   | 2.6<br>2.7   |                     | erface                                   |      |

|   | 2.7          |                     | t Interface                              |      |

|   | 2.0          |                     | terface                                  |      |

|   | 2.10         |                     | Vanagement Interface                     |      |

|   | 2.11         |                     | sor Interface                            |      |

|   | 2.12         |                     | Interface                                |      |

|   | 2.13         |                     | Management Interface                     |      |

|   | 2.14         |                     | me Clock Interface                       |      |

|   | 2.15         |                     | Clocks                                   |      |

|   | 2.16         |                     | aneous Signals                           |      |

|   | 2.17         |                     | Link                                     |      |

|   | 2.18<br>2.19 |                     | I Purpose I/O<br>and Ground              |      |

|   | 2.19         |                     | and Ground                               |      |

|   | 2.20         |                     | Functional Straps                        |      |

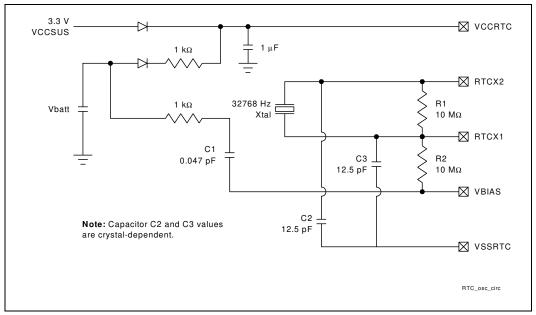

|   |              |                     | External RTC Circuitry                   |      |

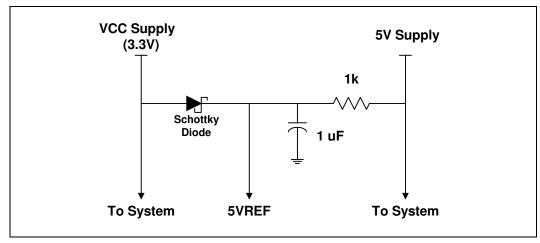

|   |              |                     | V5REF / Vcc3_3 Sequencing Requirements   |      |

|   |              |                     | Test Signals                             |      |

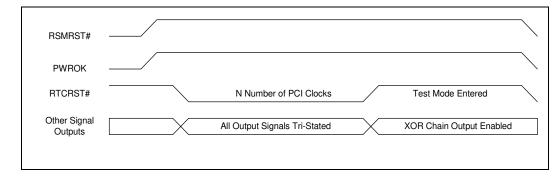

|   |              |                     | 2.20.4.1 Test Mode Selection             | 2-19 |

| 3 | Pow          | er Plane            | es and Pin States                        | 3-1  |

|   | 3.1          | Power I             | Planes                                   |      |

|   | 3.2          |                     | ed Pull-Ups and Pull-Downs               | -    |

|   | 3.3          |                     | egrated Series Termination Resistors     |      |

|   | 3.4          |                     | and I/O Signals Planes and States        |      |

|   | 3.5          | Power F             | Planes for Input Signals                 | 3-6  |

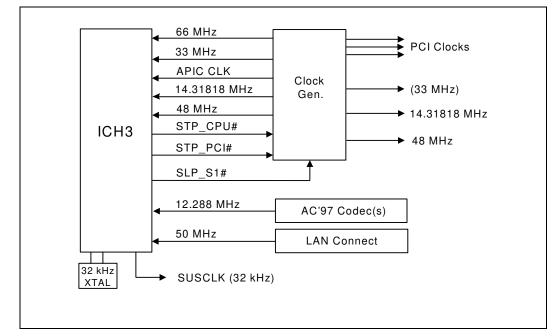

| 4 | Intel        | <sup>®</sup> ICH3 a | and System Clock Domains                 | 4-1  |

| 5 | Fund         | ctional D           | Description                              | 5-1  |

|   | 5.1          |                     | erface to PCI Bridge (D30:F0)            |      |

|   | ••••         | 5.1.1               | PCI Bus Interface                        |      |

|   |              | 5.1.2               | PCI-to-PCI Bridge Model                  |      |

|   |              | 5.1.3               | IDSEL to Device Number Mapping           |      |

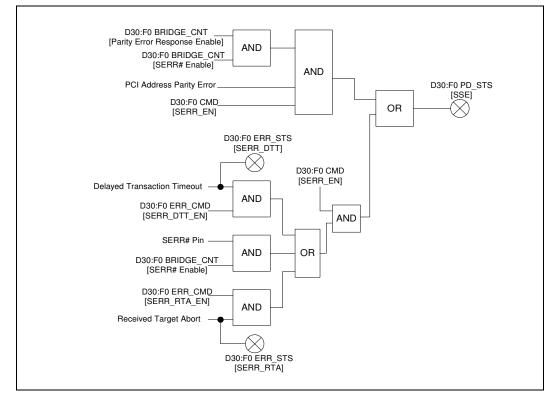

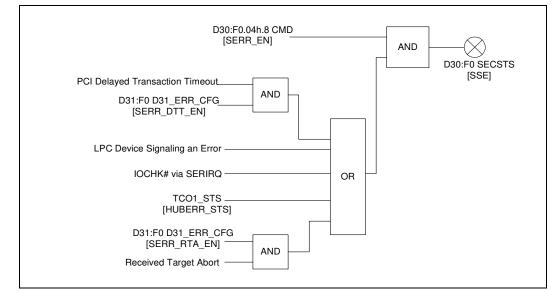

|   |              | 5.1.4               | SERR# Functionality                      | 5-2  |

|   |              | 5.1.5               | Parity Error Detection                   |      |

|   |              | 5.1.6               | Standard PCI Bus Configuration Mechanism | 5-5  |

|     |        | 5.1.6.1            | Type 0 to Type 0 Forwarding                            |      |

|-----|--------|--------------------|--------------------------------------------------------|------|

|     |        | 5.1.6.2            | Type 1 to Type 0 Conversion                            |      |

| 5.2 |        |                    | B1:D8:F0)                                              |      |

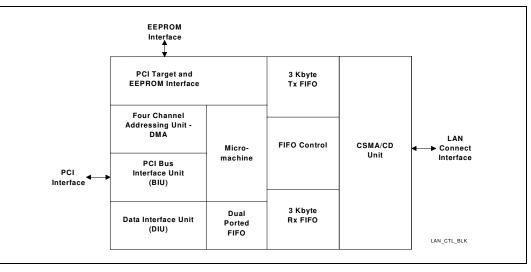

|     | 5.2.1  |                    | Summary                                                |      |

|     | 5.2.2  |                    | ntroller Architectural Overview                        |      |

|     |        | 5.2.2.1            | Parallel Subsystem                                     | 5-7  |

|     |        | 5.2.2.2<br>5.2.2.3 | FIFO Subsystem<br>Serial CSMA/CD Unit                  |      |

|     | 5.2.3  |                    | ntroller PCI Bus Interface                             |      |

|     | 5.2.5  | 5.2.3.1            | Bus Slave Operation                                    |      |

|     |        | 5.2.3.1            | Bus Master Operation                                   |      |

|     |        | 5.2.3.3            | CLOCKRUN# Signal                                       |      |

|     |        | 5.2.3.4            | PCI Power Management                                   |      |

|     |        | 5.2.3.5            | PCI Reset Signal                                       |      |

|     |        | 5.2.3.6            | Wake-Up Events                                         |      |

|     |        | 5.2.3.7            | Wake on LAN* (Preboot Wake-Up)                         | 5-16 |

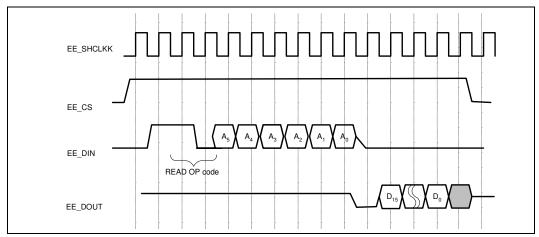

|     | 5.2.4  | Serial El          | EPROM Interface                                        |      |

|     | 5.2.5  | CSMA/C             | D Unit                                                 | 5-17 |

|     |        | 5.2.5.1            | Full Duplex                                            | 5-18 |

|     |        | 5.2.5.2            | Flow Control                                           | 5-18 |

|     |        | 5.2.5.3            | Address Filtering Modifications                        |      |

|     |        | 5.2.5.4            | VLAN Support                                           |      |

|     | 5.2.6  |                    | lanagement Interface                                   |      |

|     | 5.2.7  | TCO Fu             | nctionality                                            |      |

|     |        | 5.2.7.1            | Receive Functionality                                  |      |

|     |        | 5.2.7.2            | Transmit Functionality                                 |      |

| 5.3 |        |                    | System and Management Functions) (D31:F0)              |      |

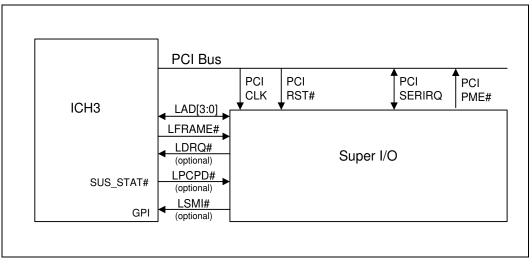

|     | 5.3.1  |                    | erface                                                 |      |

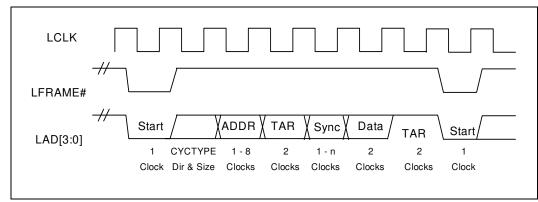

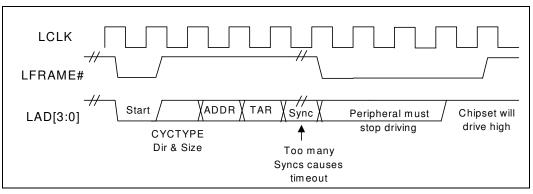

|     |        | 5.3.1.1            | LPC Cycle Types                                        |      |

|     |        | 5.3.1.2            | Start Field Definition                                 |      |

|     |        | 5.3.1.3            | Cycle Type / Direction (CYCTYPE + DIR)                 | 5-22 |

|     |        | 5.3.1.4            | SIZESYNC                                               |      |

|     |        | 5.3.1.5<br>5.3.1.6 | SYNC Time-out                                          |      |

|     |        | 5.3.1.7            | SYNC Error Indication                                  |      |

|     |        | 5.3.1.8            | LFRAME# Usage                                          |      |

|     |        | 5.3.1.9            | I/O Cycles                                             |      |

|     |        | 5.3.1.10           |                                                        |      |

|     |        | 5.3.1.11           | LPC Power Management                                   |      |

|     |        | 5.3.1.12           | Configuration and Intel <sup>®</sup> ICH3 Implications | 5-26 |

| 5.4 | DMA C  | Operation (        | (D31:F0)                                               | 5-26 |

|     | 5.4.1  | Channel            | Priority                                               | 5-27 |

|     |        | 5.4.1.1            | Fixed Priority                                         | 5-27 |

|     |        | 5.4.1.2            | Rotating Priority                                      | 5-28 |

|     | 5.4.2  | Address            | Compatibility Mode                                     | 5-28 |

|     | 5.4.3  | Summar             | y of DMA Transfer Sizes                                |      |

|     |        | 5.4.3.1            | Address Shifting When Programmed for 16-Bit I/         |      |

|     |        |                    | by Words                                               |      |

|     | 5.4.4  |                    | alize                                                  |      |

|     | 5.4.5  |                    | Commands                                               |      |

|     |        | 5.4.5.1            | Clear Byte Pointer Flip-Flop                           |      |

|     |        |                    | DMA Master Clear                                       |      |

|     |        |                    | Clear Mask Register                                    |      |

| 5.5 | PUI DI | VIA                |                                                        | 5-30 |

|     | 5.5.1                | PCI DMA Expansion Protocol                                    |       |

|-----|----------------------|---------------------------------------------------------------|-------|

|     | 5.5.2                | PCI DMA Expansion Cycles                                      | .5-32 |

|     | 5.5.3                | DMA Addresses                                                 | .5-32 |

|     | 5.5.4                | DMA Data Generation                                           | .5-32 |

|     | 5.5.5                | DMA Byte Enable Generation                                    | .5-33 |

|     | 5.5.6                | DMA Cycle Termination                                         | .5-33 |

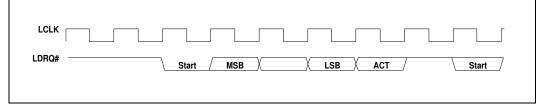

|     | 5.5.7                | LPC DMA                                                       | .5-33 |

|     | 5.5.8                | Asserting DMA Requests                                        |       |

|     | 5.5.9                | Abandoning DMA Requests                                       |       |

|     | 5.5.10               | General Flow of DMA Transfers                                 |       |

|     | 5.5.11               | Terminal Count                                                |       |

|     | 5.5.12               | Verify Mode                                                   | .5-35 |

|     | 5.5.13               | DMA Request Deassertion                                       |       |

|     | 5.5.14               | SYNC field / LDRQ# Rules                                      |       |

| 5.6 | Intel <sup>®</sup> 8 | 254 Timers (D31:F0)                                           | .5-37 |

|     | 5.6.1                | Counter 0, System Timer                                       |       |

|     | 5.6.2                | Counter 1, Refresh Request Signal                             |       |

|     | 5.6.3                | Counter 2, Speaker Tone                                       |       |

|     | 5.6.4                | Timer Programming                                             |       |

|     | 5.6.5                | Reading from the Interval Timer                               |       |

|     |                      | 5.6.5.1 Simple Read                                           |       |

|     |                      | 5.6.5.2 Counter Latch Command                                 |       |

|     |                      | 5.6.5.3 Read Back Command                                     |       |

| 5.7 | Intel® 8             | 3259 Interrupt Controllers (PIC) (D31:F0)                     | .5-41 |

|     | 5.7.1                | Interrupt Handling                                            |       |

|     |                      | 5.7.1.1 Generating Interrupts                                 |       |

|     |                      | 5.7.1.2 Acknowledging Interrupts                              |       |

|     |                      | 5.7.1.3 Hardware/Software Interrupt Sequence                  |       |

|     | 5.7.2                | Initialization Command Words (ICWx)                           |       |

|     | 5.7.3                | Operation Command Words (OCW)                                 |       |

|     | 5.7.4                | Modes of Operation                                            |       |

|     |                      | 5.7.4.1 Fully Nested Mode                                     |       |

|     |                      | 5.7.4.2 Special Fully Nested Mode                             |       |

|     |                      | 5.7.4.3 Automatic Rotation Mode (Equal Priority Devices)      |       |

|     |                      | 5.7.4.4 Specific Rotation Mode (Specific Priority)            |       |

|     |                      | 5.7.4.5 Poll Mode                                             |       |

|     |                      | 5.7.4.6 Cascade Mode<br>5.7.4.7 Edge and Level Triggered Mode |       |

|     |                      | 5.7.4.8 End of Interrupt Operations                           |       |

|     |                      | 5.7.4.9 Normal End of Interrupt                               | 5-46  |

|     |                      | 5.7.4.10 Automatic End of Interrupt Mode                      |       |

|     | 5.7.5                | Masking Interrupts                                            |       |

|     |                      | 5.7.5.1 Masking on an Individual Interrupt Request            |       |

|     |                      | 5.7.5.2 Special Mask Mode                                     |       |

|     | 5.7.6                | Steering PCI Interrupts                                       |       |

| 5.8 |                      | ed Interrupt Controller (APIC) (D31:F0)                       |       |

|     | 5.8.1                | Interrupt Handling                                            |       |

|     | 5.8.2                | Interrupt Mapping                                             |       |

|     | 5.8.3                | APIC Bus Functional Description                               |       |

|     |                      | 5.8.3.1 Physical Characteristics of APIC                      | .5-50 |

|     |                      | 5.8.3.2 APIC Bus Arbitration                                  | .5-50 |

|     |                      | 5.8.3.3 Bus Message Formats                                   |       |

|     | 5.8.4                | PCI Message-Based Interrupts                                  | .5-56 |

|     |                      |                                                               |       |

|      |                     |                    | Theory of Operation                                                               | 5-56 |

|------|---------------------|--------------------|-----------------------------------------------------------------------------------|------|

|      |                     | 5.8.4.2            | Registers and Bits Associated with PCI Interrupt                                  |      |

|      | <b>F</b> 0 <b>F</b> |                    | Delivery                                                                          |      |

|      | 5.8.5               |                    | or System Bus Interrupt Delivery                                                  |      |

|      |                     | 5.8.5.1<br>5.8.5.2 | Theory of Operation<br>Edge-Triggered Operation                                   | 5-57 |

|      |                     |                    | Level-Triggered Operation                                                         | 5-57 |

|      |                     | 5.8.5.4            | Registers Associated with Processor System Bus                                    |      |

|      |                     |                    | nterrupt Delivery                                                                 | 5-58 |

|      |                     | 5.8.5.5            | Interrupt Message Format                                                          | 5-58 |

| 5.9  | Serial I            | nterrupt (E        | D31:F0)                                                                           |      |

|      | 5.9.1               | Start Fra          | me                                                                                | 5-60 |

|      | 5.9.2               | Data Fra           | mes                                                                               | 5-60 |

|      | 5.9.3               | Stop Fra           | me                                                                                | 5-60 |

|      | 5.9.4               | Specific I         | nterrupts not Supported via SERIRQ                                                | 5-61 |

|      | 5.9.5               | Data Fra           | me Format                                                                         | 5-61 |

| 5.10 | Real Ti             | me Clock           | (D31:F0)                                                                          | 5-62 |

|      | 5.10.1              | Update C           | Cycles                                                                            | 5-62 |

|      | 5.10.2              | Interrupts         | 5                                                                                 | 5-63 |

|      | 5.10.3              | Lockable           | RAM Ranges                                                                        | 5-63 |

|      | 5.10.4              |                    | Rollover                                                                          |      |

|      | 5.10.5              |                    | Battery-Backed RTC RAM                                                            |      |

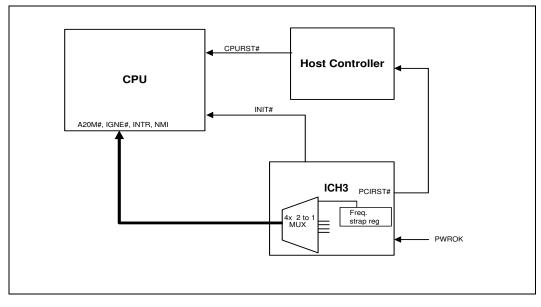

| 5.11 | Proces              |                    | ce (D31:F0)                                                                       |      |

|      | 5.11.1              |                    | or Interface Signals                                                              |      |

|      |                     | 5.11.1.1           | A20M#                                                                             | 5-65 |

|      |                     |                    | INIT#                                                                             |      |

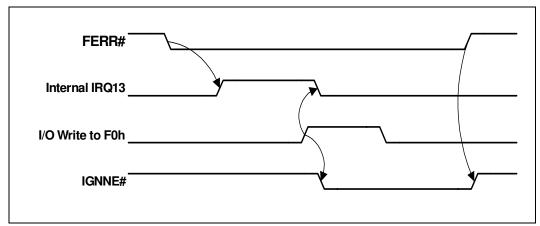

|      |                     |                    | FERR#/IGNNE# (Coprocessor Error)                                                  |      |

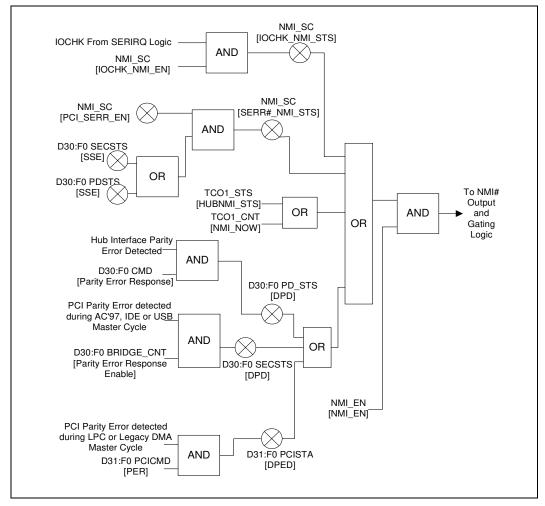

|      |                     |                    | NMI                                                                               |      |

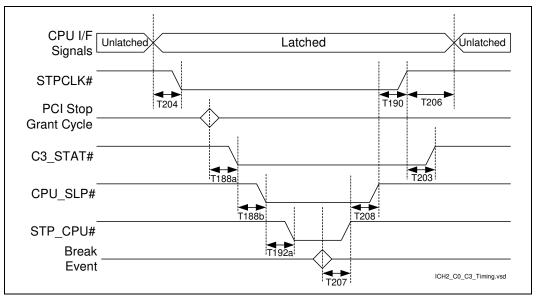

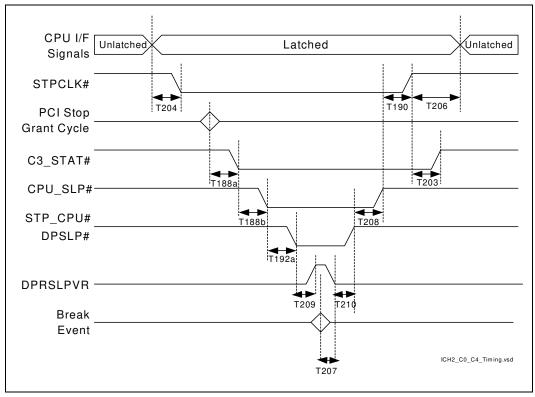

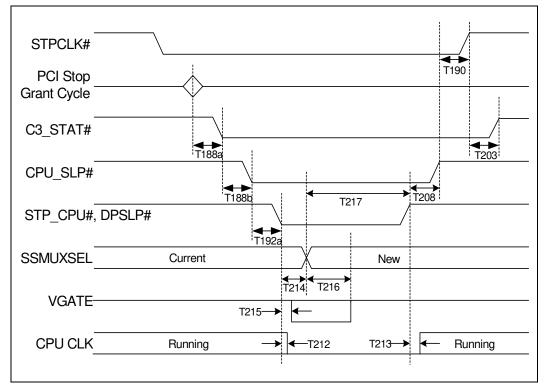

|      |                     | 5.11.1.5           | STPCLK# and CPUSLP# Signals                                                       | 5-67 |

|      |                     | 5.11.1.6           | CPUPWRGD Signal                                                                   | 5-67 |

|      |                     |                    | DPSLP#                                                                            |      |

| E 40 | 5.11.2              |                    | trapping for the Processor                                                        |      |

| 5.12 |                     |                    | ent (D31:F0)                                                                      |      |

|      | 5.12.1              |                    |                                                                                   |      |

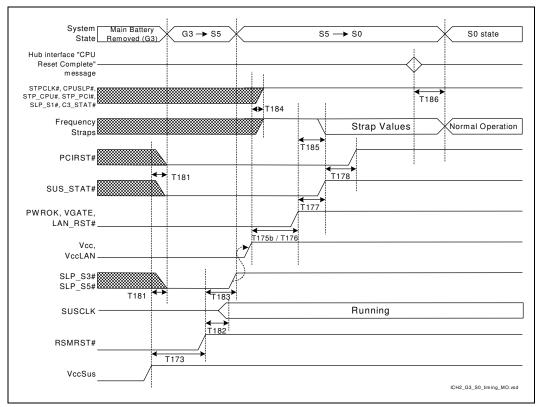

|      | 5.12.2              |                    | H3 and System Power States                                                        |      |

|      | 5.12.3              |                    | Power Planes                                                                      |      |

|      | 5.12.4              |                    | H3 Power Planes                                                                   |      |

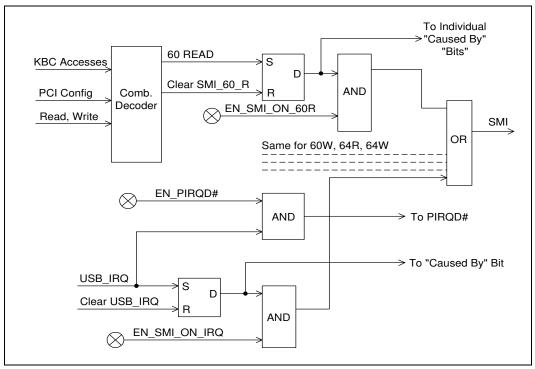

|      | 5.12.5              |                    | I Generation                                                                      |      |

|      | 5.12.6              |                    | Processor Clock Control                                                           |      |

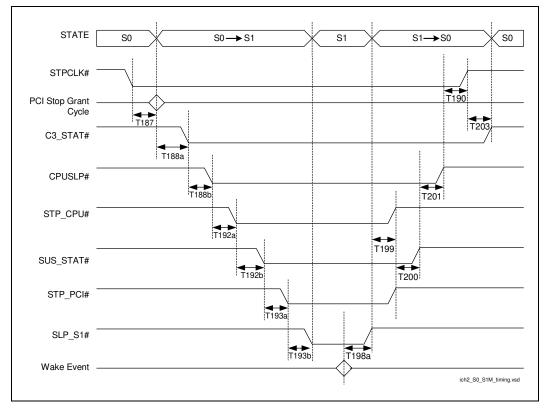

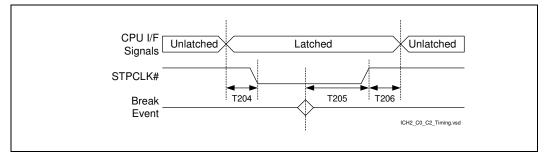

|      |                     | 5.12.6.1           | Throttling Using STPCLK#                                                          | 5-76 |

|      | F 10 7              |                    | Transition Rules Among S0/Cx and Throttling States                                |      |

|      | 5.12.7              |                    | PCI Clock Control                                                                 |      |

|      |                     |                    | Conditions for Stopping the PCI Clock                                             |      |

|      |                     | 5 12 7 3           | Conditions for Maintaining the PCI Clock<br>Conditions for Stopping the PCI Clock |      |

|      |                     |                    | Conditions for Re-Starting the PCI Clock                                          |      |

|      |                     | 5 12 7 5           | Other Causes of CLKRUN# Going Active                                              | 5-79 |

|      |                     | 5.12.7.6           | LPC Devices and CLKRUN#                                                           |      |

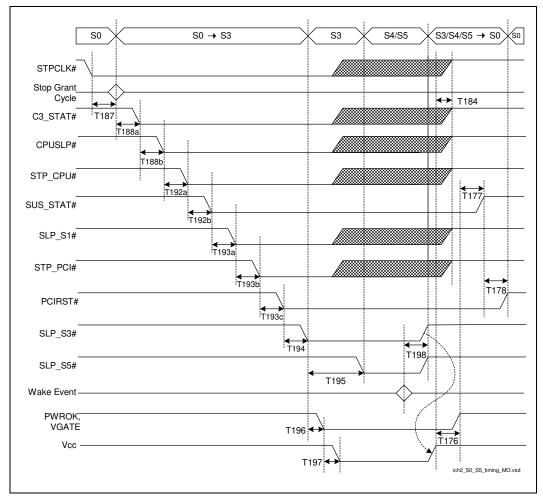

|      | 5.12.8              |                    | ates                                                                              |      |

|      |                     |                    | Initiating Sleep State                                                            |      |

|      |                     |                    | Exiting Sleep States                                                              |      |

|      |                     | 5.12.8.3           | Sx–G3–Sx, Handling Power Failures                                                 | 5-82 |

|      | 5.12.9              | Thermal            | Management                                                                        | 5-83 |

|       |                 | 5.12.9.1 THRM# Signal<br>5.12.9.2 THRM# Initiated Passive Cooling                    | 5-83  |

|-------|-----------------|--------------------------------------------------------------------------------------|-------|

|       |                 | 5.12.9.3 THRM# Override Software Bit                                                 |       |

|       |                 | 5.12.9.4 Processor Initiated Passive Cooling (Via Programmed                         |       |

|       |                 | Duty Cycle on STPCLK#)                                                               | 5-84  |

|       |                 | 5.12.9.5 Active Cooling                                                              | 5-84  |

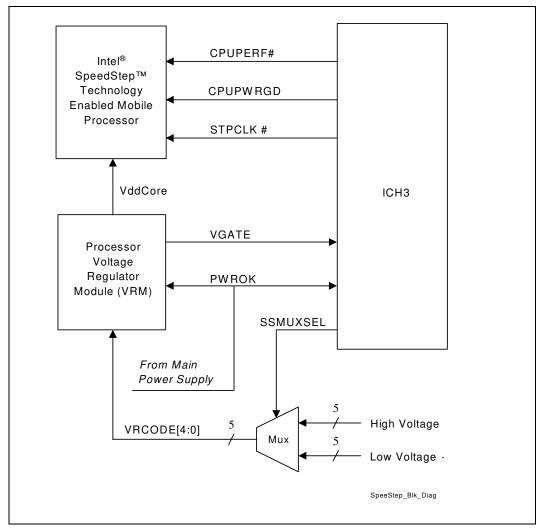

|       | 5.12.10         | Intel <sup>®</sup> SpeedStep™ Technology Protocol                                    | 5-84  |

|       |                 | 5.12.10.1 Intel <sup>®</sup> SpeedStep™ Technology Processor                         |       |

|       |                 | Requirements                                                                         | 5-85  |

|       |                 | 5.12.10.2 Intel <sup>®</sup> SpeedStep <sup>™</sup> Technology States                | 5-85  |

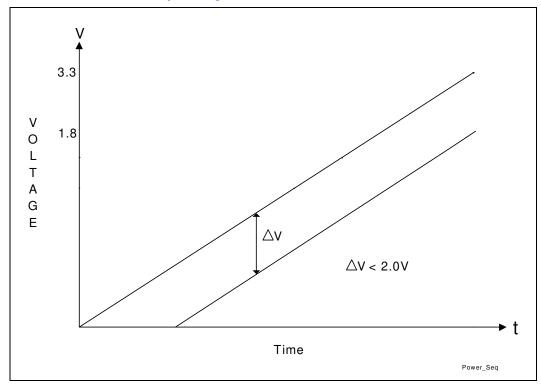

|       |                 | 5.12.10.3 Voltage Regulator Interface                                                |       |

|       | 5.12.11         | Event Input Signals and Their Usage                                                  |       |

|       |                 | 5.12.11.1 PWRBTN#–Power Button                                                       | 5-86  |

|       |                 | 5.12.11.2 RI#—Ring Indicate                                                          | 5-87  |

|       |                 | 5.12.11.3 PME#—PCI Power Management Event                                            |       |

|       |                 | 5.12.11.4 AGPBUSY#                                                                   | 5-87  |

|       | 5.12.12         | ALT Access Mode                                                                      | 5-88  |

|       |                 | 5.12.12.1 Write Only Registers with Read Paths in                                    |       |

|       |                 | ALT Access Mode                                                                      |       |

|       |                 | 5.12.12.2 PIC Reserved Bits                                                          | 5-91  |

|       |                 | 5.12.12.3 Read Only Registers with Write Paths in                                    |       |

|       |                 | ALT Access Mode                                                                      |       |

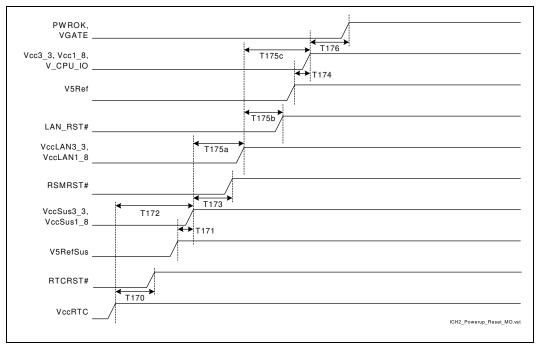

|       | 5.12.13         | System Power Supplies, Planes, and Signals                                           | 5-91  |

|       |                 | 5.12.13.1 Power Plane Control with SLP_S3# and SLP_S5#                               |       |

|       |                 | 5.12.13.2 SLP_S1# Signal                                                             |       |

|       |                 | 5.12.13.3 PWROK Signal                                                               |       |

|       |                 | 5.12.13.4 VRMPWRGD Signal                                                            |       |

|       |                 | 5.12.13.5 BATLOW#—Battery Low                                                        | 5-92  |

|       |                 | 5.12.13.6 Controlling Leakage and Power Consumption During                           | F 00  |

|       | <b>E 10 1 1</b> | Low-Power States                                                                     |       |

|       | 5.12.14         |                                                                                      | 5-93  |

|       |                 | 5.12.14.1 Clock Control Signals from Intel <sup>®</sup> ICH3 to<br>Clock Synthesizer | 5-93  |

|       | 5.12.15         | Legacy Power Management Theory of Operation                                          |       |

| 5.13  |                 | Management (D31:F0)                                                                  |       |

|       |                 | Theory of Operation                                                                  |       |

|       |                 | 5.13.1.1 Detecting a System Lockup                                                   |       |

|       |                 | 5.13.1.2 Handling an Intruder                                                        |       |

|       |                 | 5.13.1.3 Detecting Improper FWH Programming                                          |       |

|       |                 | 5.13.1.4 Handling an ECC Error or Other Memory Error                                 | 5-95  |

|       | 5.13.2          | Alert on LAN*                                                                        |       |

| 5.14  |                 | Il Purpose I/O                                                                       |       |

| ••••  |                 | GPIO Mapping                                                                         |       |

|       |                 | Power Wells                                                                          |       |

|       |                 | SMI# and SCI Routing                                                                 |       |

|       |                 | Power Wells                                                                          |       |

| 5 1 5 |                 | ntroller (D31:F1)                                                                    |       |

| 5.15  |                 |                                                                                      |       |

|       | 5.15.1          | PIO Transfers<br>5.15.1.1 IDE Port Decode                                            |       |

|       |                 | 5.15.1.1 IDE Port Decode<br>5.15.1.2 IDE Legacy Mode and Native Mode                 | 5-104 |

|       |                 |                                                                                      |       |

|       |                 | 5.15.1.3 PIO IDE Timing Modes<br>5.15.1.4 IORDY Masking                              |       |

|       |                 | 5.15.1.4 IORD Masking<br>5.15.1.5 PIO 32-Bit IDE Data Port Accesses                  | 5-100 |

|       |                 | 5.15.1.6 PIO IDE Data Port Prefetching and Posting                                   |       |

|       |                 |                                                                                      | 5 100 |

|      |        |                                                             | <b>F</b> 107 |

|------|--------|-------------------------------------------------------------|--------------|

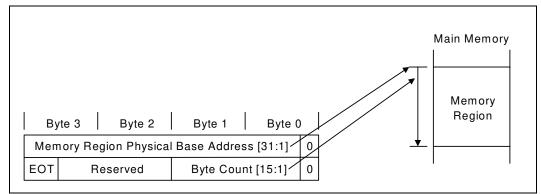

|      | 5.15.2 | Bus Master Function                                         |              |

|      |        | 5.15.2.1 Physical Region Descriptor Format                  |              |

|      |        | 5.15.2.2 Bus Master IDE Timings                             | 5-108        |

|      |        | 5.15.2.3 Interrupts                                         | 5-108        |

|      |        | 5.15.2.4 Bus Master IDE Operation                           | 5-109        |

|      |        | 5.15.2.5 Error Conditions                                   | 5-110        |

|      |        | 5.15.2.6 Intel <sup>®</sup> 8237-Like Protocol              | 5-110        |

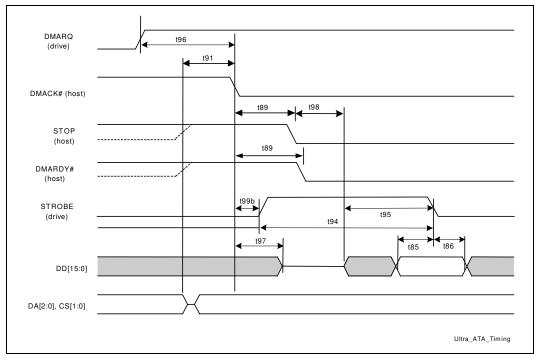

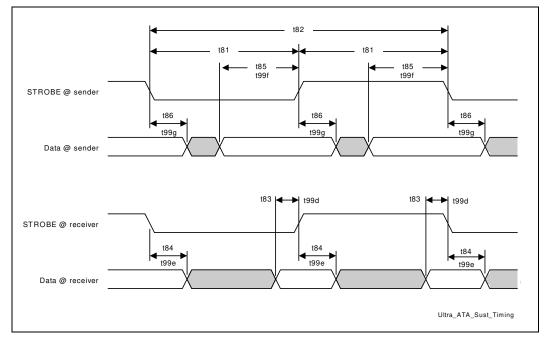

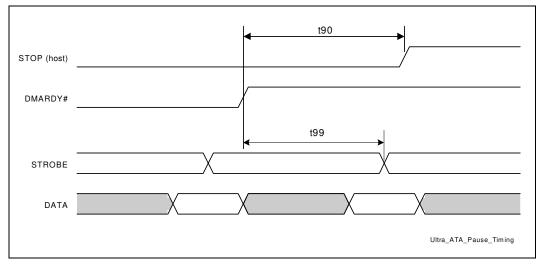

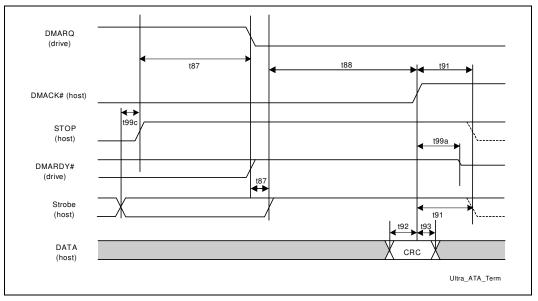

|      | 5.15.3 | Ultra ATA/33 Protocol                                       |              |

|      |        | 5.15.3.1 Signal Descriptions                                |              |

|      |        | 5.15.3.2 Operation                                          |              |

|      |        | 5.15.3.3 CRC Calculation                                    |              |

|      | 5.15.4 | Ultra ATA/66 Protocol                                       |              |

|      |        |                                                             |              |

|      | 5.15.5 | Ultra ATA/100 Protocol                                      |              |

|      | 5.15.6 | Ultra ATA/33/66/100 Timing                                  |              |

|      | 5.15.7 | Mobile IDE Swap Bay                                         |              |

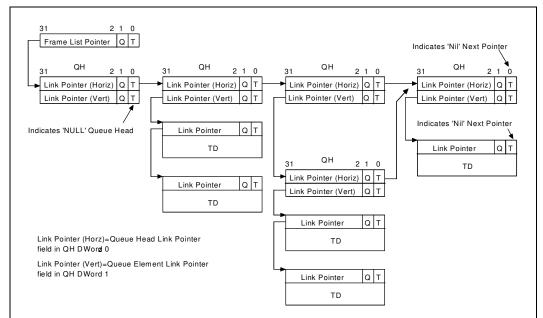

| 5.16 | USB 1. | 1 Controllers (D29:F0, F1 and F2)                           | 5-115        |

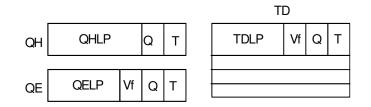

|      | 5.16.1 | Data Structures in Main Memory                              | 5-115        |

|      |        | 5.16.1.1 Frame List Pointer                                 |              |

|      |        | 5.16.1.2 Transfer Descriptor (TD)                           |              |

|      |        | 5.16.1.3 Queue Head (QH)                                    |              |

|      | 5 16 2 | Data Transfers to/from Main Memory                          |              |

|      | 0.10.2 | 5.16.2.1 Executing the Schedule                             |              |

|      |        | 5.16.2.2 Processing Transfer Descriptors                    |              |

|      |        |                                                             |              |

|      |        | 5.16.2.3 Command Register, Status Register, and TD Status I |              |

|      |        | Interaction                                                 |              |

|      |        | 5.16.2.4 Transfer Queuing                                   |              |

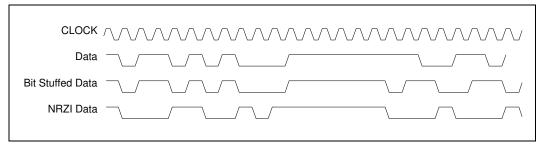

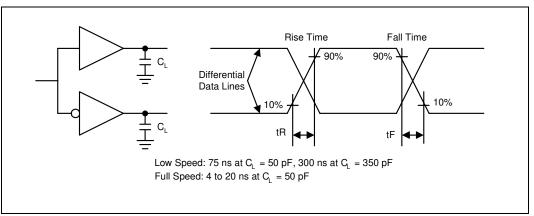

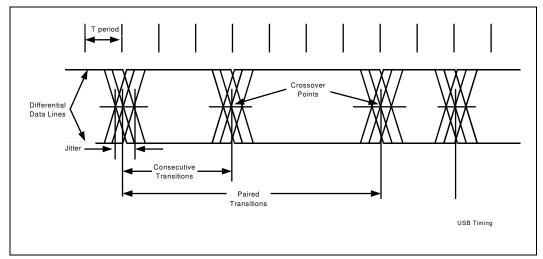

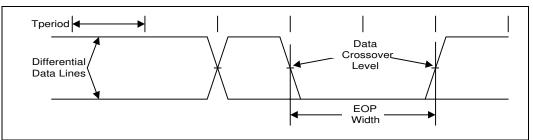

|      | 5.16.3 | Data Encoding and Bit Stuffing                              |              |

|      | 5.16.4 | Bus Protocol                                                |              |

|      |        | 5.16.4.1 Bit Ordering                                       | 5-128        |

|      |        | 5.16.4.2 SYNC Field                                         | 5-128        |

|      |        | 5.16.4.3 Packet Field Formats                               | 5-129        |

|      |        | 5.16.4.4 Address Fields                                     |              |

|      |        | 5.16.4.5 Frame Number Field                                 | 5-130        |

|      |        | 5.16.4.6 Data Field                                         |              |

|      |        | 5.16.4.7 Cyclic Redundancy Check (CRC)                      |              |

|      | 5.16.5 | Packet Formats                                              |              |

|      | 011010 | 5.16.5.1 Token Packets                                      |              |

|      |        | 5.16.5.2 Start of Frame Packets                             |              |

|      |        | 5.16.5.3 Data Packets                                       |              |

|      |        | 5.16.5.4 Handshake Packets                                  | 5-133        |

|      |        | 5.16.5.5 Handshake Responses                                |              |

|      | E 16 6 |                                                             |              |

|      | 0.01.0 | USB Interrupts                                              |              |

|      |        | 5.16.6.1 Transaction Based Interrupts                       |              |

|      |        | 5.16.6.2 Non-Transaction Based Interrupts                   |              |

|      |        | USB Power Management                                        |              |

|      |        | USB Legacy Keyboard Operation                               |              |

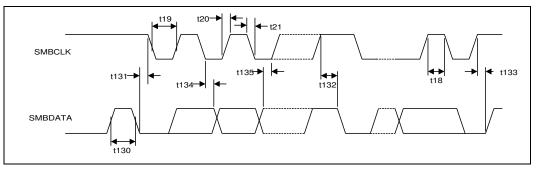

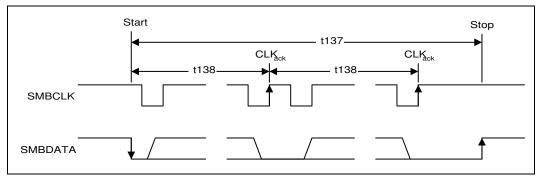

| 5.17 | SMBus  | 2.0 Controller Functional Description (D31:F3)              | 5-139        |

|      |        | Host Controller                                             |              |

|      |        | 5.17.1.1 Command Protocols                                  |              |

|      |        | 5.17.1.2 I <sup>2</sup> C Behavior                          |              |

|      |        | 5.17.1.3 Heartbeat for Use with the External LAN Controller | 5-149        |

|      | 5.17.2 | Bus Arbitration                                             |              |

|      |        |                                                             |              |

|      | 0.17.3 | Bus Timing                                                  |              |

|      |        | 5.17.3.1 Clock Stretching                                   | 5-150        |

|       |        | 5.17.3.2 Bus Time Out (Intel <sup>®</sup> ICH3 as SMBus Master)                                                          | .5-15 | 0  |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------|-------|----|

|       | 5.17.4 | Interrupts / SMI#                                                                                                        | .5-15 | 1  |

|       |        | SMBALERT#                                                                                                                |       |    |

|       | 5.17.6 | SMBus Slave Interface                                                                                                    |       |    |

|       |        | 5.17.6.1 Format of Slave Write Cycle                                                                                     | .5-15 | 3  |

|       |        | 5.17.6.2 Format of Read Command                                                                                          |       |    |

|       |        | 5.17.6.3 Format of Host Notify Command                                                                                   | .5-15 | 7  |

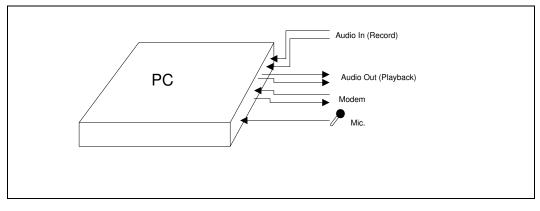

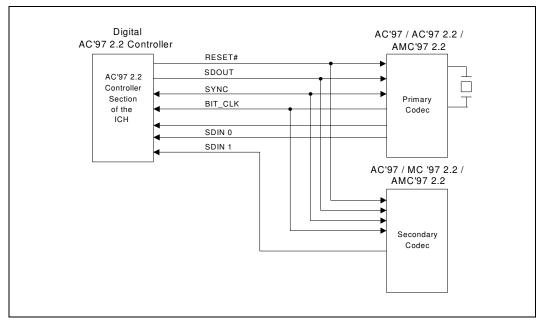

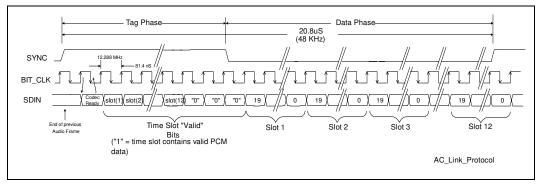

| 5.18  | AC '97 | Controller Functional Description<br>D31:F5, Modem D31:F6)                                                               | E 1 E | 0  |

|       |        |                                                                                                                          |       |    |

|       | 5.18.1 | AC-Link                                                                                                                  |       |    |

|       |        | 5.18.1.1 AC-Link Output Frame (SDOUT)<br>5.18.1.2 Output Slot 0: Tag Phase                                               |       |    |

|       |        | 5.18.1.3 Output Slot 1: Command Address Port                                                                             | 5-16  | 23 |

|       |        | 5.18.1.4 Output Slot 2: Command Data Port                                                                                |       |    |

|       |        | 5.18.1.5 Output Slot 3: PCM Playback Left Channel                                                                        |       |    |

|       |        | 5.18.1.6 Output Slot 4: PCM Playback Right Channel                                                                       | .5-16 | 3  |

|       |        | 5.18.1.7 Output Slot 5: Modem Codec                                                                                      | .5-16 | 3  |

|       |        | 5.18.1.8 Output Slot 6: PCM Playback Center Front Channel<br>5.18.1.9 Output Slots 7–8: PCM Playback Left and Right Rear |       |    |

|       |        | Channels                                                                                                                 |       |    |

|       |        | 5.18.1.10 Output Slot 9: Playback SubWoofer Channel                                                                      |       |    |

|       |        | 5.18.1.11 Output Slots 10–11: Reserved<br>5.18.1.12 Output Slot 12: I/O Control                                          |       |    |

|       |        | 5.18.1.13 AC-Link Input Frame (SDIN)                                                                                     |       |    |

|       |        | 5.18.1.14 Input Slot 0: Tag Phase                                                                                        |       |    |

|       |        | 5.18.1.15 Input Slot 1: Status Address Port / Slot Request Bits                                                          | .5-16 | 6  |

|       |        | 5.18.1.16 Input Slot 2: Status Data Port                                                                                 | .5-16 | 6  |

|       |        | 5.18.1.17 Input Slot 3: PCM Record Left Channel                                                                          | .5-16 | 7  |

|       |        | 5.18.1.18 Input Slot 4: PCM Record Right Channel                                                                         | .5-16 | 7  |

|       |        | 5.18.1.19 Input Slot 5: Modern Line                                                                                      | .5-16 | 1  |

|       |        | 5.18.1.20 Input Slot 6: Optional Dedicated Microphone<br>Record Data                                                     | 5-16  | 7  |

|       |        | 5.18.1.21 Input Slots 7–11: Reserved                                                                                     |       |    |

|       |        | 5.18.1.22 Input Slot 12: I/O status                                                                                      |       |    |

|       |        | 5.18.1.23 Register Access                                                                                                |       |    |

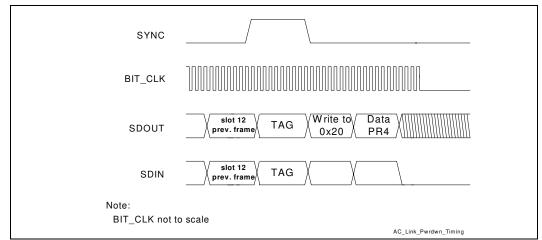

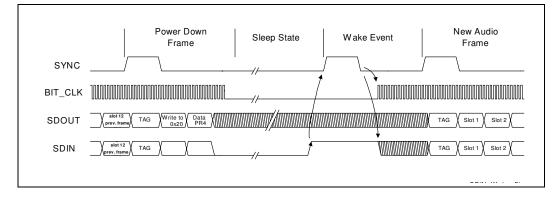

|       | 5.18.2 | AC-Link Low Power Mode                                                                                                   | .5-16 | 9  |

|       |        | 5.18.2.1 External Wake Event                                                                                             | .5-17 | 0  |

|       | 5.18.3 | AC '97 Cold Reset                                                                                                        | .5-17 | 0  |

|       | 5.18.4 | AC '97 Warm Reset                                                                                                        |       |    |

|       | 5.18.5 | System Reset                                                                                                             | .5-17 | 1  |

| Regis |        | d Memory Mapping                                                                                                         |       |    |

| 6.1   |        | vices and Functions                                                                                                      |       |    |

| 6.2   |        | nfiguration Map                                                                                                          |       |    |

| 6.3   |        | p                                                                                                                        |       |    |

|       | 6.3.1  | Fixed I/O Address Ranges                                                                                                 |       |    |

|       | 6.3.2  | Variable I/O Decode Ranges                                                                                               |       |    |

| 6.4   |        | у Мар                                                                                                                    |       |    |

|       | 6.4.1  | Boot-Block Update Scheme                                                                                                 |       |    |

| LAN ( |        | Iler Registers (B1:D8:F0)                                                                                                |       |    |

| 7.1   | PCI Co | nfiguration Registers (B1:D8:F0)                                                                                         | 7-    | 1  |

|       | 7.1.1  | VID—Vendor ID Register (LAN Controller—B1:D8:F0)                                                                         |       |    |

|       | 7.1.2  | DID—Device ID Register (LAN Controller—B1:D8:F0)                                                                         | 7-2   | 2  |

### 6

| 7.1.3         | PCICMD—PCI Command Register (LAN Controller—B1:D8:F0)                      | 7-3    |

|---------------|----------------------------------------------------------------------------|--------|

| 7.1.3         | PCISTS—PCI Status Register (LAN Controller—B1:D8:F0)                       |        |

| 7.1.4         | REVID—Revision ID Register (LAN Controller—B1:D8:F0)                       |        |

| 7.1.6         | SCC—Sub Class Code Register (LAN Controller—B1:D8:F0)                      |        |

| 7.1.7         | BCC—Base Class Code Register (LAN Controller—B1:D8:F0)                     |        |

| 7.1.7         | CLS—Cache Line Size Register (LAN Controller—B1:D8:F0)                     |        |

| 7.1.8         | PMLT—PCI Master Latency Timer Register                                     | .7-5   |

| 7.1.9         | (LAN Controller—B1:D8:F0)                                                  | 7-6    |

| 7.1.10        | HEADTYP—Header Type Register                                               | . / -0 |

| 7.1.10        | (LAN Controller—B1:D8:F0)                                                  | 7-6    |

| 7.1.11        | CSR_MEM_BASE CSR—Memory-Mapped Base Address Register                       |        |

| ,             | (LAN Controller—B1:D8:F0)                                                  | .7-6   |

| 7.1.12        | CSR_IO_BASE—CSR I/O-Mapped Base Address Register                           |        |

| ···· <b>_</b> | (LAN Controller—B1:D8:F0)                                                  | .7-7   |

| 7.1.13        | SVID—Subsystem Vendor ID Register                                          |        |

|               | (LAN Controller—B1:D8:F0)                                                  | .7-7   |

| 7.1.14        | SID—Subsystem ID Register (LAN Controller—B1:D8:F0)                        | .7-8   |

| 7.1.15        | CAP_PTR—Capabilities Pointer Register                                      |        |

|               | (LAN Controller—B1:D8:F0)                                                  | .7-8   |

| 7.1.16        | INT_LN—Interrupt Line Register                                             |        |

|               | (LAN Controller—B1:D8:F0)                                                  | .7-8   |

| 7.1.17        | INT_PN—Interrupt Pin Register (LAN Controller—B1:D8:F0)                    |        |

| 7.1.18        | MIN_GNT—Minimum Grant Register (LAN Controller—B1:D8:F0)                   | 7-9    |

| 7.1.19        | MAX_LAT—Maximum Latency Register                                           |        |

|               | (LAN Controller—B1:D8:F0)                                                  |        |

| 7.1.20        | CAP_ID—Capability ID Register (LAN Controller—B1:D8:F0)                    | .7-9   |

| 7.1.21        | NXT_PTR—Next Item Pointer Register<br>(LAN Controller—B1:D8:F0)            | - 10   |

| 7 1 00        | (LAN CONTROLLER—B1:D8:FU)                                                  | 7-10   |

| 7.1.22        | PM_CAP—Power Management Capabilities Register<br>(LAN Controller—B1:D8:F0) | 7 10   |

| 7102          | PMCSR—Power Management Control/Status Register                             | /-10   |

| 1.1.20        | (LAN Controller—B1:D8:F0)                                                  | 7_11   |

| 7 1 24        | PCIDATA—PCI Power Management Data Register                                 | , , ,  |

| 7.1.24        | (LAN Controller—B1:D8:F0)                                                  | 7-12   |

| LAN Co        | ontrol / Status Registers (CSR)                                            |        |

| 7.2.1         | System Control Block Status Word Register                                  |        |

| 7.2.2         | System Control Block Command Word Register                                 |        |

| 7.2.3         | System Control Block General Pointer Register                              |        |

| 7.2.4         | PORT                                                                       |        |

| 7.2.5         | EEPROM Control Register                                                    |        |

| 7.2.6         | Management Data Interface (MDI) Control Register                           |        |

| 7.2.7         | Receive DMA Byte Count Register                                            |        |

| 7.2.8         | Early Receive Interrupt Register                                           |        |

| 7.2.9         | Flow Control Register                                                      |        |

| 7.2.10        | Power Management Driver (PMDR) Register                                    |        |

| 7.2.11        | General Control Register                                                   |        |

| 7.2.12        | General Status Register                                                    |        |

| 7.2.13        | Statistical Counters                                                       |        |

|               |                                                                            |        |

7.2

8

| Hub | Interfac | ce to PCI Bridge Registers (D30:F0)                                  | 8-1     |

|-----|----------|----------------------------------------------------------------------|---------|

| 8.1 | PCI Co   | nfiguration Registers (D30:F0)                                       | 8-1     |

| -   | 8.1.1    | VID—Vendor ID Register (HUB-PCI—D30:F0)                              | 8-2     |

|     | 8.1.2    | DID—Device ID Register (HUB-PCI—D30:F0)                              |         |

|     | 8.1.3    | CMD—Command Register (HUB-PCI—D30:F0)                                |         |

|     | 8.1.4    | PD STS—Primary Device Status Register                                |         |

|     | •••••    | (HUB-PCI—D30:F0)                                                     | 8-4     |

|     | 8.1.5    | REVID—Revision ID Register (HUB-PCI—D30:F0)                          | 8-5     |

|     | 8.1.6    | SCC-Sub Class Code Register (HUB-PCI-D30:F0)                         |         |

|     | 8.1.7    | BCC-Base-Class Code Register (HUB-PCI-D30:F0)                        |         |

|     | 8.1.8    | PMLT—Primary Master Latency Timer Register<br>(HUB-PCI—D30:F0)       |         |

|     | 8.1.9    | HEADTYP—Header Type Register (HUB-PCI—D30:F0)                        | 8-6     |

|     | 8.1.10   | PBUS_NUM—Primary Bus Number Register<br>(HUB-PCI—D30:F0)             |         |

|     | 8.1.11   | SBUS NUM—Secondary Bus Number Register                               |         |

|     | 0 1 10   | (HUB-PCI—D30:F0)                                                     | 8-6     |

|     |          | SUB_BUS_NUM—Subordinate Bus Number Register<br>(HUB-PCI—D30:F0)      | 8-6     |

|     | 8.1.13   | SMLT—Secondary Master Latency Timer Register                         |         |

|     |          | (HUB-PCI—D30:F0)                                                     | 8-7     |

|     |          | IOBASE—I/O Base Register (HUB-PCI—D30:F0)                            |         |

|     |          | IOLIM—I/O Limit Register (HUB-PCI—D30:F0)                            |         |

|     |          | SECSTS—Secondary Status Register (HUB-PCI—D30:F0)                    |         |

|     |          | MEMBASE—Memory Base Register (HUB-PCI—D30:F0)                        |         |

|     |          | , , , , , , , , , , , , , , , , , , , ,                              | 8-9     |

|     | 8.1.19   | PREF_MEM_BASE—Prefetchable Memory Base Register<br>(HUB-PCI—D30:F0)  | 8-9     |

|     | 8.1.20   | PREF_MEM_MLT—Prefetchable Memory Limit Register (<br>HUB-PCI—D30:F0) | 8-10    |

|     | 8.1.21   | IOBASE_HI—I/O Base Upper 16 Bits Register                            |         |

|     |          | (HUB-PCI—D30:F0)                                                     | 8-10    |

|     |          | IOLIM_HI—I/O Limit Upper 16 Bits Register (HUB-PCI—D30:F             |         |

|     | 8.1.23   | INT_LINE—Interrupt Line Register (HUB-PCI—D30:F0)                    |         |

|     | 8.1.24   |                                                                      |         |

|     |          | BRIDGE_CNT2—Bridge Control Register 2 (HUB-PCI—D30:F                 | 0) 8-12 |

|     | 8.1.26   | DEVICE_HIDE—Secondary PCI Device Hiding Register                     |         |

|     |          | (HUB-PCI—D30:F0)                                                     |         |

|     | 8.1.27   | CNF—ICH3 Configuration Register (HUB-PCI—D30:F0)                     |         |

|     | 8.1.28   | MTT—Multi-Transaction Timer Register (HUB-PCI—D30:F0)                | 8-13    |

|     | 8.1.29   | PCI_MAST_STS—PCI Master Status Register<br>(HUB-PCI—D30:F0)          | 8-14    |

|     | 8.1.30   | ERR_CMD—Error Command Register (HUB-PCI—D30:F0)                      |         |

|     | 8.1.31   | ERR_STS—Error Status Register (HUB-PCI—D30:F0)                       |         |

| LPC |          | lge Registers (D31:F0)                                               |         |

| 9.1 | PCI Co   | onfiguration Registers (D31:F0)                                      | 9-1     |

|     | 9.1.1    | VID—Vendor ID Register (LPC I/F—D31:F0)                              |         |

|     | 9.1.2    | DID—Device ID Register (LPC I/F—D31:F0)                              |         |

|     | 9.1.3    | PCICMD—PCI COMMAND Register (LPC I/F—D31:F0)                         |         |

|     | 9.1.4    | PCISTA—PCI Device Status Register (LPC I/F—D31:F0)                   |         |

|     | 9.1.5    | REVID—Revision ID Register (LPC I/F—D31:F0)                          | 9-4     |

| 9.1.6   | PI—Programming Interface Register (LPC I/F—D31:F0)              | 9-5      |

|---------|-----------------------------------------------------------------|----------|

| 9.1.7   | SCC-Sub Class Code Register (LPC I/F-D31:F0)                    |          |

| 9.1.8   | BCC-Base Class Code Register (LPC I/F-D31:F0)                   |          |

| 9.1.9   | HEADTYP—Header Type Register (LPC I/F—D31:F0)                   |          |

| 9.1.10  | PMBASE—ACPI Base Address Register (LPC I/F—D31:F0)              |          |

| 9.1.11  | ACPI_CNTL—ACPI Control Register (LPC I/F—D31:F0)                |          |

| 9.1.12  | BIOS_CNTL Register (LPC I/F—D31:F0)                             |          |

| 9.1.13  | TCO_CNTL—TCO Control Register (LPC I/F—D31:F0)                  | 9-7      |

| 9.1.14  | GPIOBASE—GPIO Base Address Register (LPC I/F—D31:F0)            |          |

| 9.1.15  | GPIO_CNTL—GPIO Control Register (LPC I/F—D31:F0)                | 9-8      |

| 9.1.16  | PIRQ[n]_ROUT—PIRQ[A,B,C,D] Routing Control Register             |          |

|         | (LPC I/F—D31:F0)                                                |          |

| 9.1.17  | SERIRQ_CNTL—Serial IRQ Control Register (LPC I/F—D31:F0)        | 9-10     |

| 9.1.18  | PIRQ[n]_ROUT—PIRQ[E,F,G,H] Routing Control Register             | <b>.</b> |

|         | (LPC I/F—D31:F0)                                                | .9-11    |

| 9.1.19  | D31_ERR_CFG—Device 31 Error Configuration Register              | 0 1 1    |

| 0 1 00  | (LPC I/F—D31:F0)<br>D31_ERR_STS—Device 31 Error Status Register | .9-11    |

| 9.1.20  | (LPC I/F—D31:F0)                                                | 0-12     |

| 9.1.21  | PCI_DMA_CFG—PCI DMA Configuration Register                      | . 9-12   |

| 5.1.21  | (LPC I/F—D31:F0)                                                | 9-12     |

| 9122    | GEN_CNTL—General Control Register (LPC I/F—D31:F0)              |          |

|         | GEN_STA—General Status Register (LPC I/F—D31:F0)                |          |

| 9.1.24  | RTC_CONF—RTC Configuration Register (LPC I/F—D31:F0)            |          |

| 9.1.25  |                                                                 |          |

|         | (LPC I/F—D31:F0)                                                | .9-16    |

| 9.1.26  | FDD/LPT_DEC—LPC I/F FDD & LPT Decode Ranges Register            |          |

|         | (LPC I/F—D31:F0)                                                | .9-17    |

| 9.1.27  | SND_DEC—LPC I/F Sound Decode Ranges Register                    |          |

| 0 1 00  | (LPC I/F—D31:F0)                                                | .9-17    |

| 9.1.28  | FWH_DEC_EN1—FWH Decode Enable 1 Register<br>(LPC I/F—D31:F0)    | 0 10     |

| 9.1.29  | GEN1_DEC—LPC I/F Generic Decode Range 1 Register                | .9-10    |

| 9.1.29  | (LPC I/F—D31:F0)                                                | 9-19     |

| 9 1 30  | LPC_EN—LPC I/F Enables Register (LPC I/F—D31:F0)                | 9-19     |

| 9.1.31  |                                                                 | 9-21     |

| 9.1.32  |                                                                 |          |

| 00      | (LPC I/F—D31:F0)                                                | .9-22    |

| 9.1.33  | FWH_SEL2—FWH Select 2 Register (LPC I/F—D31:F0)                 |          |

| 9.1.34  |                                                                 |          |

|         | (LPC I/F—D31:F0)                                                |          |

| 9.1.35  | FUNC_DIS—Function Disable Register (LPC I/F—D31:F0)             | .9-24    |

| DMA I/0 | O Registers                                                     |          |

| 9.2.1   | DMABASE_CA—DMA Base and Current Address Registers               |          |

| 9.2.2   | DMABASE_CC—DMA Base and Current Count Registers                 |          |

| 9.2.3   | DMAMEM_LP—DMA Memory Low Page Registers                         |          |

| 9.2.4   | DMACMD—DMA Command Register                                     |          |

| 9.2.5   | DMASTA—DMA Status Register                                      |          |

| 9.2.6   | DMA_WRSMSK—DMA Write Single Mask Register                       |          |

| 9.2.7   | DMACH_MODE—DMA Channel Mode Register                            |          |

| 9.2.8   | DMA Clear Byte Pointer Register                                 |          |

| 9.2.9   | DMA Master Clear Register                                       | .9-31    |

9.2

|     | 9.2.10         | DMA_CLMSK—DMA Clear Mask Register                            | .9-31 |

|-----|----------------|--------------------------------------------------------------|-------|

|     | 9.2.11         | DMA_WRMSK—DMA Write All Mask Register                        | .9-31 |

| 9.3 | Timer I        | /O Registers                                                 | .9-32 |

|     | 9.3.1          | TCW-Timer Control Word Register                              | .9-32 |

|     |                | 9.3.1.1 RDBK CMD—Read Back Command                           |       |

|     |                | 9.3.1.2 LTCH CMD—Counter Latch Command                       |       |

|     | 9.3.2          | SBYTE_FMT—Interval Timer Status Byte Format Register         | .9-34 |

|     | 9.3.3          | Counter Access Ports Register                                |       |

| 9.4 |                | 3259 Interrupt Controller (PIC) Registers                    |       |

| ••• | 9.4.1          | Interrupt Controller I/O MAP                                 |       |

|     | 9.4.2          | ICW1—Initialization Command Word 1 Register                  |       |

|     | 9.4.3          | ICW2—Initialization Command Word 2 Register                  |       |

|     | 9.4.4          | ICW3—Master Controller Initialization Command Word 3         |       |

|     | 0              | Register                                                     | .9-37 |

|     | 9.4.5          | ICW3—Slave Controller Initialization Command Word 3 Register |       |

|     | 9.4.6          | ICW4—Initialization Command Word 4 Register                  |       |

|     | 9.4.7          | OCW1—Operational Control Word 1 (Interrupt Mask) Register    |       |

|     | 9.4.8          | OCW2—Operational Control Word 2 Register                     |       |

|     | 9.4.9          | OCW3—Operational Control Word 3 Register                     |       |

|     |                | ELCR1—Master Controller Edge/Level Triggered Register        |       |

|     | 9.4.10         | 5 55 F                                                       |       |

| 9.5 |                | zed Interrupt Controller (APIC)                              |       |

| 9.5 | 9.5.1          |                                                              |       |

|     | 9.5.1<br>9.5.2 | APIC Register Map                                            |       |

|     | 9.5.2<br>9.5.3 | IND—Index Register                                           |       |

|     | 9.5.3<br>9.5.4 | DAT—Data Register                                            |       |

|     |                | IRQPA—IRQ Pin Assertion Register                             |       |

|     | 9.5.5          | EOIR—EOI Register                                            |       |

|     | 9.5.6          | ID—Identification Register                                   |       |

|     | 9.5.7          | VER—Version Register                                         |       |

|     | 9.5.8          | ARBID—Arbitration ID Register                                |       |

|     | 9.5.9          | BOOT_CONFIG—Boot Configuration Register                      |       |

|     | 9.5.10         | Redirection Table                                            |       |

| 9.6 |                | me Clock Registers                                           |       |

|     | 9.6.1          | I/O Register Address Map                                     |       |

|     | 9.6.2          | Indexed Registers                                            |       |

|     |                | 9.6.2.1 RTC_REGA—Register A                                  |       |

|     |                | 9.6.2.2 RTC_REGB—Register B (General Configuration)          |       |

|     |                | 9.6.2.3 RTC_REGC—Register C (Flag Register)                  | .9-53 |

| 07  | <b>D</b>       | 9.6.2.4 RTC_REGD—Register D (Flag Register)                  |       |

| 9.7 |                | sor Interface Registers                                      |       |

|     | 9.7.1          | NMI_SC—NMI Status and Control Register                       |       |

|     | 9.7.2          | NMI_EN—NMI Enable (and Real Time Clock Index) Register       |       |

|     | 9.7.3          | PORT92—Fast A20 and Init Register                            |       |

|     | 9.7.4          | COPROC_ERR—Coprocessor Error Register                        |       |

|     | 9.7.5          | RST_CNT—Reset Control Register                               |       |

| 9.8 |                | Management Registers (D31:F0)                                |       |

|     | 9.8.1          | Power Management PCI Configuration Registers (D31:F0)        |       |

|     |                | 9.8.1.1 GEN_PMCON_1—General PM Configuration 1 Regist        |       |

|     |                | (PM—D31:F0)                                                  |       |

|     |                | 9.8.1.2 GEN_PMCON_2—General PM Configuration 2 Regist        |       |

|     |                | (PM—D31:F0)                                                  | .9-59 |

|            | 9.8.1.3 GEN_PMCON_3—General PM Configuration 3 Register<br>(PM—D31:F0)                                                 |       |

|------------|------------------------------------------------------------------------------------------------------------------------|-------|

|            | 9.8.1.4 STPCLK_DEL—Stop Clock Delay Register                                                                           |       |

|            | (PM—D31:F0)<br>9.8.1.5 GPI_ROUT—GPI Routing Control Register                                                           |       |

|            | (PM—D31:F0)<br>9.8.1.6 TRP_FWD_EN—I/O Monitor Trap Forwarding Enable                                                   |       |

|            | Register (PM—D31:F0)<br>9.8.1.7 MON[n]_TRP_RNG—I/O Monitor [4:7] Trap Range Reg                                        | ister |

|            | for Devices 4–7 (PM—D31:F0)<br>9.8.1.8 MON_TRP_MSK—I/O Monitor Trap Range Mask Regis<br>for Devices 4-7 (PM—D31:F0)    | ster  |

| 9.8.2      | APM I/O Decode                                                                                                         |       |

| 9.0.2      | 9.8.2.1 APM_CNT—Advanced Power Management Control Po                                                                   |       |

|            | Register                                                                                                               | 9-63  |

|            | 9.8.2.2 APM_STS—Advanced Power Management Status Port<br>Register                                                      | t     |

| 9.8.3      | Power Management I/O Registers                                                                                         |       |

| 0.0.0      | 9.8.3.1 PM1_STS—Power Management 1 Status Register                                                                     |       |

|            | 9.8.3.2 PM1_EN—Power Management 1 Enable Register                                                                      | 9-67  |

|            | 9.8.3.3 PM1_CNT—Power Management 1 Control Register                                                                    | 9-68  |

|            | 9.8.3.4 PM1_TMR—Power Management 1 Timer Register                                                                      |       |

|            | 9.8.3.5 PROC_CNT—Processor Control Register                                                                            |       |

|            | 9.8.3.6 LV2—Level 2 Register                                                                                           |       |

|            | 9.8.3.7 LV3—Level 3 Register                                                                                           | 9-70  |

|            | 9.8.3.8 LV3—Level 4 Register                                                                                           | 9-71  |

|            | 9.8.3.9 PM2_CNT—Power Management 2 Control Register                                                                    |       |

|            | 9.8.3.10 GPE0_STS—General Purpose Event 0 Status Register<br>9.8.3.11 GPE0_EN—General Purpose Event 0 Enables          | 9-72  |

|            | Register                                                                                                               | 9-74  |

|            | 9.8.3.12 GPE1_STS—General Purpose Event 1 Status Register                                                              | 9-75  |

|            | 9.8.3.13 GPE1_EN—General Purpose Event 1 Enable Register                                                               | 9-76  |

|            | 9.8.3.14 SMI_EN—SMI Control and Enable Register                                                                        |       |

|            | 9.8.3.15 SMI_STS—SMI Status Register<br>9.8.3.16 MON_SMI—Device Monitor SMI Status and Enable                          |       |

|            | Register                                                                                                               | 9-79  |

|            | 9.8.3.17 DEVACT_STS—Device Activity Status Register                                                                    | 9-80  |

|            | 9.8.3.18 DEVTRAP_EN— Device Trap Enable Register                                                                       | 9-81  |

|            | 9.8.3.19 BUS_ADDR_TRACK— Bus Address Tracker Register.                                                                 |       |

|            | 9.8.3.20 BUS_CYC_TRACK— Bus Cycle Tracker Register<br>9.8.3.21 SS_CNT— Intel <sup>®</sup> SpeedStep™ TechnologyControl |       |

| <b>0</b> 1 | Register                                                                                                               |       |

|            | Management TCO Registers (D31:F0)                                                                                      |       |

| 9.9.1      | TCO Register I/O Map                                                                                                   |       |

| 9.9.2      | TCO1_RLD—TCO Timer Reload and Current Value Register                                                                   |       |

| 9.9.3      | TCO1_TMR—TCO Timer Initial Value Register                                                                              |       |

| 9.9.4      | TCO1_DAT_IN—TCO Data In Register                                                                                       |       |

| 9.9.5      | TCO1_DAT_OUT—TCO Data Out Register                                                                                     |       |

| 9.9.6      | TCO1_STS—TCO1 Status Register                                                                                          |       |

| 9.9.7      | TCO2_STS—TCO2 Status Register                                                                                          |       |

| 9.9.8      | TCO1_CNT—TCO1 Control Register                                                                                         |       |

| 9.9.9      | TCO2_CNT—TCO2 Control Register                                                                                         |       |

| 9.9.10     | TCO_MESSAGE1 and TCO_MESSAGE2 Registers                                                                                |       |

| 9.9.11     | TCO_WDSTATUS—TCO2 Control Register                                                                                     | 9-89  |

9.9

10

|      | 9.9.12 SW_IRQ_GEN—Software IRQ Genera                      | ation Register9-90    | 0 |

|------|------------------------------------------------------------|-----------------------|---|

| 9.10 | General Purpose I/O Registers (D31:F0)                     | 9-9                   | 1 |

|      | 9.10.1 GPIO Register I/O Address Map                       |                       |   |

|      | 9.10.2 GPIO_USE_SEL—GPIO Use Select R                      |                       |   |

|      | 9.10.3 GP_IO_SEL—GPIO Input/Output Sele                    |                       |   |

|      | 9.10.4 GP_LVL—GPIO Level for Input or Out                  |                       |   |

|      | 9.10.5 GPO_BLINK—GPO Blink Enable Regi                     |                       |   |

|      | 9.10.6 GPI_INV—GPIO Signal Invert Register                 |                       |   |

|      | 9.10.7 GPIO_USE_SEL2—GPIO Use Select                       |                       |   |

|      | 9.10.8 GP_IO_SEL2—GPIO Input/Output Sel                    |                       |   |

|      | 9.10.9 GP_LVL2—GPIO Level for Input or Ou                  |                       |   |

| IDE  | Controller Registers (D31:F1)                              |                       |   |

| 10.1 |                                                            |                       |   |

|      | 10.1.1 CMD—Command Register (IDE—D31                       |                       |   |

|      | 10.1.2 STS—Device Status Register (IDE—D                   |                       |   |

|      | 10.1.3 PI—Programming Interface Register (I                |                       |   |