# EVAL-AD5755SDZ/EVAL-AD5755-1SDZ/ EVAL-AD5757SDZ User Guide UG-244

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# Evaluation Board for a Quad Channel, 16-Bit, Serial Input, 4 mA to 20 mA, Voltage Output DAC with Dynamic Power Control and HART Connectivity

#### **FEATURES**

Full-featured evaluation board for the AD5755, AD5755-1, and AD5757

**Link options**

PC control in conjunction with Analog Devices, Inc., system demonstration platform (SDP)

PC software for control

#### **GENERAL DESCRIPTION**

This user guide describes a full-featured evaluation board that is designed to allow the user to easily evaluate all features of the AD5755, AD5755-1, or AD5757, quad channel, 16-bit current source and voltage output DAC with dynamic power control and HART connectivity. The board can be controlled by two means: via the on-board connector (J11) or via the SDP connector (J9). The SDP board allows the evaluation board to be controlled through the USB port of a Windows\* XP (SP2 or later), Windows Vista (32-bit or 64-bit), or Windows 7 (32-bit or 64-bit) based PC using the AD575X evaluation software.

#### **DEVICE DESCRIPTION**

The AD5755 is a quad, voltage and current output DAC that operates with a power supply range from -26.4 V to +33 V. On-chip dynamic power control minimizes package power dissipation in current mode. This is achieved by regulating the voltage on the output driver from 7.4 V to 29.5 V.

The part uses a versatile 3-wire serial interface that operates at clock rates up to 30 MHz and is compatible with standard SPI, QSPI™, MICROWIRE™, DSP, and microcontroller interface standards. The interface also features optional CRC-8 packet error checking, as well as a watchdog timer that monitors activity on the interface.

The AD5757 is a current output-only version of the AD5755 and is HART compatible. The AD5755-1 is identical to the AD5755 except the -V<sub>SENSE\_x</sub> functionality has been removed and, instead, the device is HART compatible. For both the AD5757 and AD5755-1, each channel has a corresponding CHART pin so that HART signals can be coupled onto the current output.

#### **EVALUATION BOARD PHOTOGRAPH**

## **EVALUATION BOARD HARDWARE**

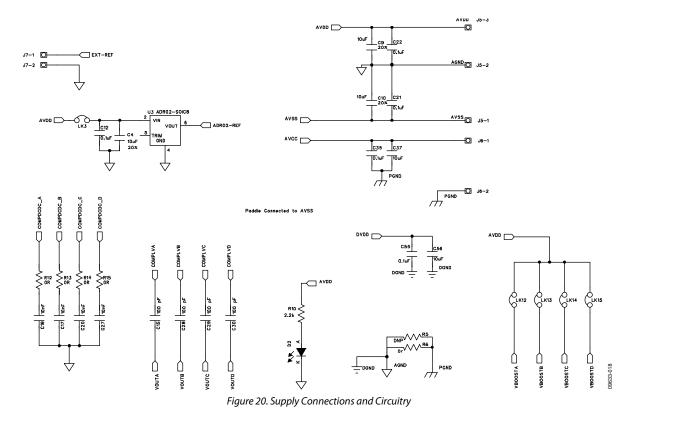

#### **POWER SUPPLIES**

The following power supplies are required.

**Table 1. Power Supply Connections**

| Connector        | Nominal        | Comment                                                                                                                                                                                                                                                      |

|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AV <sub>DD</sub> | 15 V           | Positive analog supply voltage.<br>10.8 V to 33 V range.<br>(Green LED D2 lights up when power is<br>supplied to AV <sub>DD</sub> .)                                                                                                                         |

| AV <sub>SS</sub> | -15 V/<br>+0 V | Negative analog supply voltage.  -10.8 V to -26.4 V range, or 0 V for the AD5757 or AD5755-1 in unipolar supply mode.                                                                                                                                        |

| AVcc             | 5 V            | DC-to-dc supply voltage. 4.5 V to 5.5 V range. The AV <sub>CC</sub> input supplies all four onboard dc-to-dc blocks and may draw as much as 0.8 A peak current per channel, depending on the configuration (see the device data sheet for more information). |

| $DV_{DD}$        | 3.3 V          | Supplied from the SDP connector.<br>2.7 V to 5.5 V range.                                                                                                                                                                                                    |

| REFIN            | 5 V            | See Table 4 for selecting the reference source: the DAC internal reference, the on-board ADR02 reference, or externally provided via the REFIN input.                                                                                                        |

Both analog AGND and PGND inputs are provided on the board. The PGND input is for the ground of the dc-to-dc converter circuitry, and a ground connection for the  $AV_{\text{CC}}$  supply should be made at this point. The AGND and PGND planes are connected at one location on the evaluation board. The AGND and DGND planes are connected at one location close to the AD5755, AD5755-1, or AD5757 device. Each supply is decoupled to the relevant ground plane with  $10~\mu\text{F}$  and  $0.1~\mu\text{F}$  capacitors. Each device supply pin is also decoupled with a  $10~\mu\text{F}$  and  $0.1~\mu\text{F}$  capacitor pair to the relevant ground plane.

#### **LINK OPTIONS**

The link options on the evaluation board should be set for the required operating setup before using the board. The functions of the link options are described in Table 4.

#### **Default Link Option Setup**

The default link options are listed in Table 2.

**Table 2. Default Link Options**

| Link | AD5755     | AD5755-1   | AD5757     |

|------|------------|------------|------------|

| No.  | Link Setup | Link Setup | Link Setup |

| LK0  | Removed    | Removed    | Removed    |

| LK1  | Removed    | Removed    | Removed    |

| LK2  | Inserted   | Inserted   | Inserted   |

| LK3  | Inserted   | Inserted   | Inserted   |

| LK4  | Inserted   | Inserted   | Removed    |

| LK5  | Inserted   | Removed    | Removed    |

| LK6  | Inserted   | Inserted   | Removed    |

| LK7  | Inserted   | Removed    | Removed    |

| LK8  | Inserted   | Inserted   | Removed    |

| LK9  | Inserted   | Removed    | Removed    |

| LK10 | Inserted   | Inserted   | Removed    |

| LK11 | Inserted   | Removed    | Removed    |

| LK12 | Removed    | Removed    | Removed    |

| LK13 | Removed    | Removed    | Removed    |

| LK14 | Removed    | Removed    | Removed    |

| LK15 | Removed    | Removed    | Removed    |

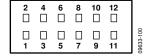

#### **Connector J11 Pin Descriptions**

Figure 2. Connector J11 Pin Configuration

Table 3. Connector J11 Pin Descriptions<sup>1</sup>

| Pin No. | Description               |

|---------|---------------------------|

| 1       | $DV_{DD}$                 |

| 2       | DGND                      |

| 3       | SYNC                      |

| 4       | SCLK                      |

| 5       | SDIN                      |

| 6       | SDO (output)              |

| 7       | LDAC                      |

| 8       | CLEAR                     |

| 9       | POC (AD5755 and AD5755-1) |

| 10      | RESET                     |

| 11      | FAULT (output)            |

| 12      | ALERT (output)            |

<sup>&</sup>lt;sup>1</sup> The SDP board must be disconnected when using the J11 connector.

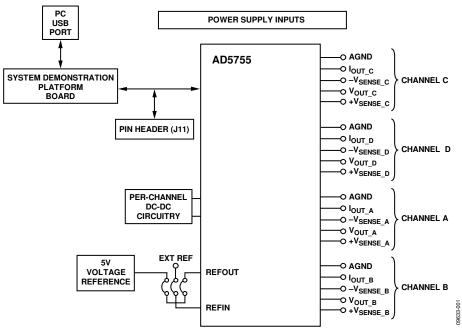

Figure 3. Evaluation Board Connection Diagram

**Table 4. Link Options**

| Link No.                  | Device              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LKO, LK1, LK2             | All models          | These links select the voltage reference source (only one of these should be inserted at any one time).  LKO selects the internal voltage reference of the DAC as the voltage reference source.  LK1 selects an external voltage reference source that can be applied at Connector J7.  LK2 selects the on-board ADRO2 as the voltage reference source. The ADRO2 is supplied by the AV <sub>DD</sub> supply and operates under the same input voltage range as the AV <sub>DD</sub> input of the DAC, that is 9 V to 33 V. |

| LK3                       | All models          | Powers the on-board ADR02 5 V reference by connecting the AV <sub>DD</sub> supply to the ADR02 supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                  |

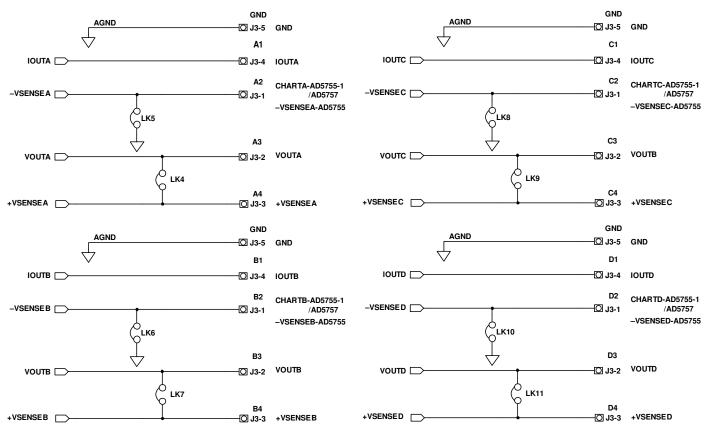

| LK4, LK6<br>LK10, LK8     | AD5755,<br>AD5755-1 | These links connect the $+V_{SENSE}$ input to $V_{OUT}$ for Channel A, Channel B, Channel C, and Channel D, respectively. When this link is inserted, the $+V_{SENSE}$ input is connected directly to the $V_{OUTx}$ pin. When this link is removed, the $+V_{SENSE}$ input is left floating and should be connected to the high-side of the load resistance external to the evaluation board.                                                                                                                              |

| LK5, LK7 LK9,<br>LK11     | AD5755              | These links connect the $-V_{SENSE}$ input to $V_{OUT}$ for Channel A, Channel B, Channel C, and Channel D, respectively. When this link is inserted, the $-V_{SENSE}$ input is connected directly to the $V_{OUT}$ pin.  When this link is removed, the $-V_{SENSE}$ input is left floating and should be connected to the high-side of the load resistance external to the evaluation board.                                                                                                                              |

| LK12, LK13,<br>LK14, LK15 | All models          | These links allow connection of an external $V_{BOOST}$ supply. (Remove Resistors R43, R44, R17, and R20 to use this feature.) When inserted, these connect the $V_{BOOST}$ pin of Channel A, Channel B, Channel C, and Channel D, respectively, to the $AV_{DD}$ supply.  When removed, the $V_{BOOST}$ supplies are controlled by the dc-to-dc converter circuitry.                                                                                                                                                       |

# EVALUATION BOARD SOFTWARE SOFTWARE INSTALLATION

The evaluation kit includes self-installing software on a CD. The software is compatible with Windows XP (SP2), Windows Vista (32-bit or 64-bit), and Windows 7 (32-bit or 64-bit). If the setup file does not run automatically, you can run **setup.exe** from the CD.

Install the evaluation software before connecting the evaluation board and SDP board to the USB port of the PC to ensure that the evaluation system is correctly recognized when connected to the PC.

- After installation from the CD is complete, power up the evaluation board as described in the Power Supplies section.

- 2. Next, connect the SDP board to the evaluation board and then to the USB port of your PC using the supplied cable.

- 3. When the evaluation system is detected, proceed through any dialog boxes that appear. This finishes the installation.

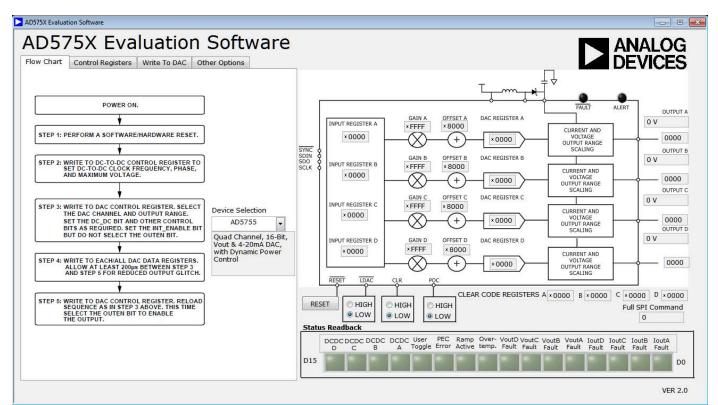

#### **SOFTWARE OPERATION**

To launch the software, complete the following steps:

From the Start menu, select Analog Devices –AD575X

Evaluation Software, and then select AD575X Evaluation

Software. The main window of the software opens (see

Figure 6).

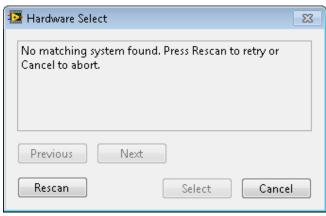

If the evaluation system is not connected to the USB port when the software is launched, a connectivity error is displayed (see Figure 5). Simply connect the evaluation board to the USB port of the PC, wait a number of seconds, and click Rescan. Follow the instructions. If you click Cancel, the software enters Demonstration Mode.

Figure 5. Connectivity Error Alert

Figure 6. Main Window

#### **DEMONSTRATION MODE**

Demonstration mode is accessible when the evaluation board is not connected to the PC. It allows the user to operate the software without the evaluation board. The user will have access to the majority of the software's features and the GUI will simulate the evaluation board. In demonstration mode, all communication to the SDP is disabled. Exit and restart the software to connect to the evaluation board.

Figure 7. Evaluation Mode

#### **SELECTING THE DEVICE**

In the flow chart tab, select the main device on the board, either AD5755, AD5755-1, or AD5757, from the drop-down list (see Figure 8) to adjust the available controls accordingly.

# AD5755 Quad Channel, 16-Bit, Vout & 4-20mA DAC, with Dynamic Power Control

Figure 8. Device Selection

#### **ENABLING THE OUTPUT CORRECTLY**

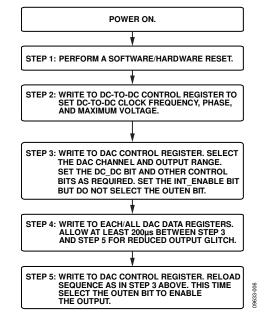

To correctly write to and set up the part from a power-on condition, use the following sequence.

- 1. Perform a hardware or software reset after initial power-on.

- The dc-to-dc converter supply block must be configured. Set the dc-to-dc switching frequency, maximum output voltage allowed, and the phase that the four dc-to-dc channels clock at.

- Configure the DAC control register on a per channel basis.

The output range is selected, and the dc-to-dc converter block is enabled (DC\_DC bit). Other control bits can be configured at this point. Set the INT\_ENABLE bit; however, the output enable bit (OUTEN) should not be set.

- Write the required code to the DAC data register. This

implements a full DAC calibration internally. Allow at

least 200 μs before Step 5 for reduced output glitch.

- 5. Write to the DAC control register again to enable the output (set the OUTEN bit).

A flowchart of enabling the output correctly is shown in Figure 9.

Figure 9. Programming Sequence for Enabling the Output Correctly

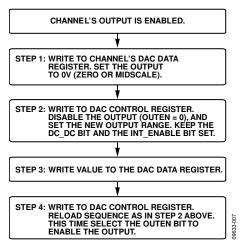

#### CHANGING AND REPROGRAMMING THE RANGE

When changing between ranges, the same sequence as described in the Enabling the Output Correctly section should be used. It is recommended to set the range to its zero point (can be midscale or zero scale) prior to disabling the output. Because the dc-to-dc converter switching frequency, maximum voltage, and phase have already been selected, there is no need to reprogram these.

A flowchart of changing and reprogramming the range is shown in Figure 10.

Figure 10. Steps for Changing the Output Range

#### **CLEAR COMMAND**

To clear an output, each relevant channel must have its clear code set in the relevant data register (default of 0x0000) and be enabled for clear operation via the DAC control registers. After these are set, assert the CLEAR pin to clear the selected channels.

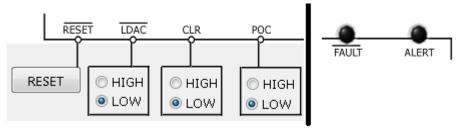

#### **CONTROL OF DIGITAL PINS**

The RESET, LDAC, POC, and CLR pins can all be controlled by selecting HIGH/LOW in the relevant boxes shown in Figure 11. The FAULT and ALERT lights display the status of their respective pins. The FAULT and ALERT pins of the device are polled by the evaluation software every ~100 ms. The FAULT pin is also connected to the reference LED, D1, on the evaluation board, and ALERT is connected to the orange LED, D14.

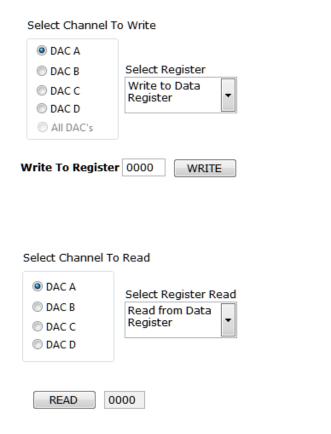

#### WRITING TO DATA REGISTERS

This function allows you to write to all the data registers. Select the register to write to from the pull-down menu, enter the 16-bit data-word to be written (in hexadecimal) and click **WRITE** to load data to the register (see Figure 12). Note that the effect of the gain and offset register values on the output is only seen once the data register is written to.

#### **READING FROM REGISTERS**

This function allows you to read from all the data registers, control registers, and the status register. Select the register to read from the pull-down menu and click **READ** (see Figure 12). The 16 bits of LSB data appear in the number box in hexadecimal format. This function is unavailable in demonstration mode.

Figure 11. Digital Pin Controls and Indicators in the Evaluation Software

Figure 12. Write to/Read From Data Register in the Evaluation Software

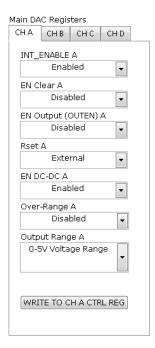

#### WRITING TO THE DAC CONTROL REGISTERS

This function allows you to write to and configure the DAC control register for a selected channel. Select the required DAC channel to be configured from the tab menu. After configuring the settings you require, click **WRITE TO CH A CTRL REG** to write to the device. The menu selection is shown in Figure 13.

**Table 9. DAC Control Register Functions**

| Table 9. DAC Control Register Functions |                                                                                                                                                                             |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Option                                  | Description                                                                                                                                                                 |  |  |

| INT_ENABLE                              | Powers up internal amplifiers. This should be done when enabling the output.                                                                                                |  |  |

| EN Clear                                | Selects if the channel clears when the CLEAR pin is activated.                                                                                                              |  |  |

| EN Output<br>(OUTEN)                    | Enables/disables the selected output channel.                                                                                                                               |  |  |

| Rset                                    | Selects whether internal or external sense resistor is used when using a current range.                                                                                     |  |  |

| EN DC-DC                                | Powers up/down the dc-to-dc converter on a selected channel. To correctly power down the dc-to-dc converter, <b>EN Output (OUTEN)</b> and INT_ENABLE must also be disabled. |  |  |

| Over-Range                              | Enables/disables 20% overrange. This is available on Vout ranges only.                                                                                                      |  |  |

| Output Range                            | Selects the output range for the specified channel.                                                                                                                         |  |  |

Figure 13. Write to the DAC Control Registers in the Evaluation Software

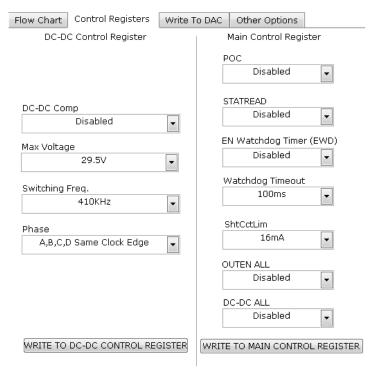

#### WRITING TO THE DC-TO-DC CONTROL REGISTER

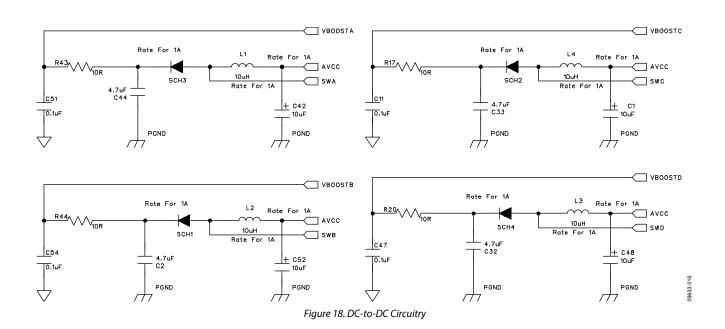

The dc-to-dc control register function is located in the **Control Registers** tab (Figure 14). This function allows you to write to and configure the dc-to-dc control register. Select the required clamp voltage, switching frequency, and phase from the pull-down menu and click the **WRITE TO DC-DC CONTROL REGISTER** button to write the selected data to the device. On the evaluation board, the dc-to-dc converter perform best at a 410 kHz switching frequency (see the DC-to-DC Boost section). See the device data sheet for information on the DC-DC Comp bit. If selecting an external compensation resistor, this can be placed at R12, R13, R14, and R15.

#### WRITING TO THE MAIN CONTROL REGISTER

This function allows you to write to and configure the main control register. After configuring the settings you require, click

the **WRITE TO MAIN CONTROL REGISTER** button to write to the device. See Table 11 for main control register functions.

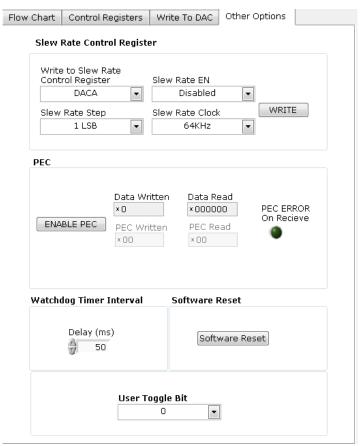

#### WRITING TO THE SLEW RATE CONTROL REGISTER

The slew rate control register can be accessed from the other options tab (see Figure 15). The slew rate control functions (Slew Rate Clock and Slew Rate Step) allow you to configure the slew rate on a per-channel basis. After configuring the setting you require, click WRITE to write to the device.

**Table 10. Slew Rate Register Functions**

| Option          | Description                                   |

|-----------------|-----------------------------------------------|

| Slew Rate EN    | Enable/disable the slew rate control feature. |

| Slew Rate Clock | Set the slew clock rate.                      |

| Slew Rate Step  | Set the step size when slewing.               |

Figure 14. Write to the DC-to-DC Control Register and Main Control Register in the Evaluation Software

**Table 11. Main Control Register Functions**

| Option                     | Description                                                                                                                    |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| POC                        | Determines the state of the V <sub>OUT</sub> channel when the voltage output channel is disabled during normal operation.      |

|                            | Disabled: disabled Vout channels goes to the function set by the POC pin.                                                      |

|                            | Enabled: disabled Vout channels goes to the opposite function of the POC pin.                                                  |

| STATREAD                   | Enable/disable status readback during a write (see the Status Readback section for details about using this feature).          |

| EN Watchdog Timer<br>(EWD) | Enable/disable the watchdog timer (see the Writing to the Main Control Register section for details about using this feature). |

| Watchdog Timeout           | Select timeout period for watchdog timer (using 100 ms or 200 ms with the evaluation software recommended).                    |

| ShtCctLim                  | Selects short-circuit current limit on the Vout channels.                                                                      |

| OUTEN ALL                  | Enables the output on all four DACs simultaneously.                                                                            |

|                            | Do not use <b>OUTEN ALL</b> when enabling channels via the DAC control registers.                                              |

| DC-DC ALL                  | When set, powers up the dc-to-dc converter on all four channels simultaneously.                                                |

|                            | To power down the dc-to-dc converters, all channels outputs must first be disabled.                                            |

|                            | Do not use the <b>DC-DC ALL</b> option when enabling the dc-to-dc converters via the DAC control registers.                    |

#### **OTHER OPTIONS**

Click the **Other Options** tab shown in Figure 15 to access this feature. From this tab, the user can set the slew rate register, PEC, and user toggle bit (AD5755/AD5757 only) that is contained in the status register. A software reset can also be performed.

This tab contains a feature for using the watchdog timer. By entering a value for **Delay (ms)**, the evaluation software attempts to send the SPI code required to the software register (0x195) in approximately the time specified. Note that, because the latency of the USB connection is not strictly defined, this time delay is only a rough estimate but can be far exceeded. It is recommended to use the 100 ms or 200 ms watchdog timeouts when using this feature.

#### PEC

In packet error checking mode, only 32-bit commands are accepted. This consists of the 24 data bits and an 8-bit frame check calculated using the polynomial:

$$C(x) = x_8 + x_2 + x_1 + 1$$

#### AD5755 and AD5757

The AD5755 and AD5757 PEC function is activated by writing 32-bits to the device. The frame check must match the 24 data bits or the command will be ignored.

To activate this feature in the software, ensure that the correct product is selected from the device selection menu (see Figure 8) then click **ENABLE PEC** (see Figure 15).

The software will now perform 32-bit writes to the device.

Clicking **ENABLE PEC** once again will return the software to 24-bit write mode. In this mode, the AD5755 and AD5757 will accept 24-bit writes once again.

#### AD5755-1

The AD5755-1 PEC function is activated by enabling the PEC enable bit (Bit 12 in the software register). Once enabled, each command must be 32 bits long.

To activate this feature in the software, ensure that the correct product is selected from the device selection menu (see Figure 8) then click **ENABLE PEC** (see Figure 15).

The PEC enable bit is enabled and software will now perform 32-bit writes to the device. The status of the PEC enable bit can be checked by reading the status register (Bit D11) or utilizing the STATREAD function (see the Status Readback section).

Clicking the PEC enable bit once again will return the software to 24-bit write mode. The PEC enable bit will also be disabled. In this mode, the AD5755-1 will accept 24-bit writes once again.

For more information, refer to the Packet Error Checking section of the respective device data sheets.

#### STATUS READBACK

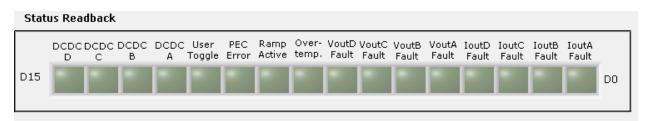

When **STATREAD** is enabled (see Figure 14), the status register is displayed shown in Figure 16. Note that the status register readback on a write operation reports any errors present immediately before the current write command.

#### **CLOSING THE SOFTWARE**

If the software is closed but the AD5755/AD5755-1/AD5757 and SDP remain powered, the evaluation board will retain the last state set by the software, with the exception of the PEC, which is disabled.

Figure 15. Other Options in the Evaluation Software (AD5755/AD5757 Device Selected)

Figure 16. Status Readback Indicator (AD5755/AD5757 Device Selected)

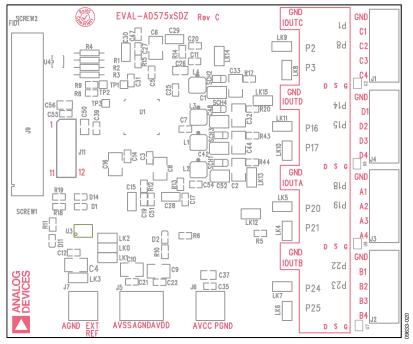

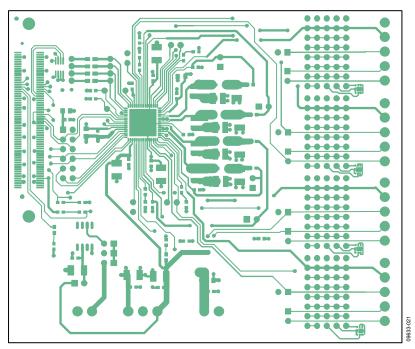

## **EVALUATION BOARD SCHEMATICS AND ARTWORK**

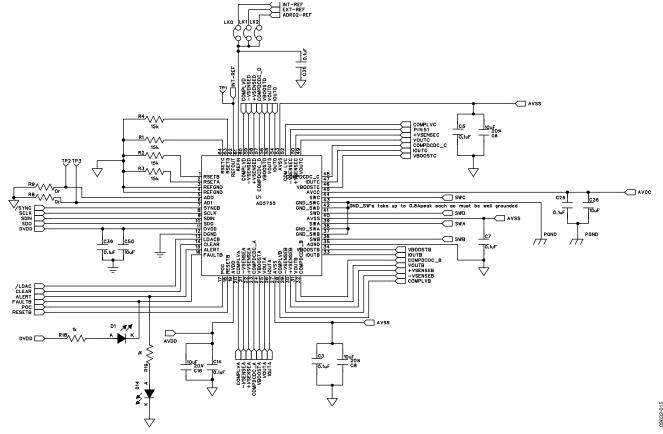

Figure 17. Main Device Circuitry

Figure 19. Output (Terminal Blocks) Circuitry

Rev. C | Page 14 of 19

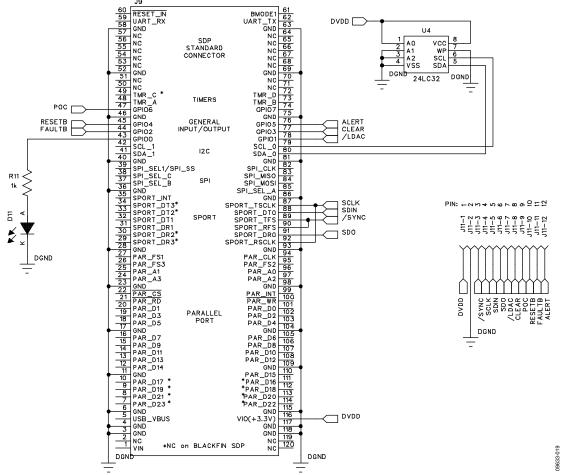

Figure 21. SDP Board Connector

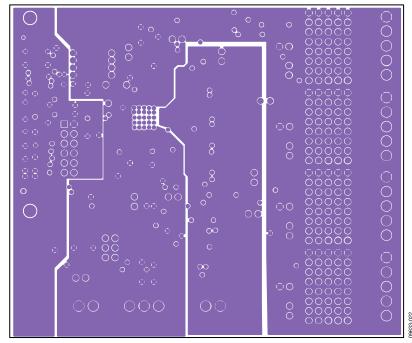

Figure 22. Component Placement

Figure 23. Top PCB Layer

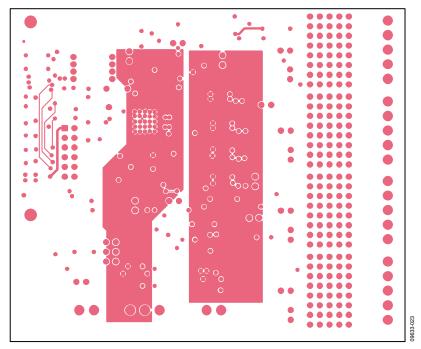

Figure 24. Inner First PCB Layer

Figure 25. Inner Second PCB Layer

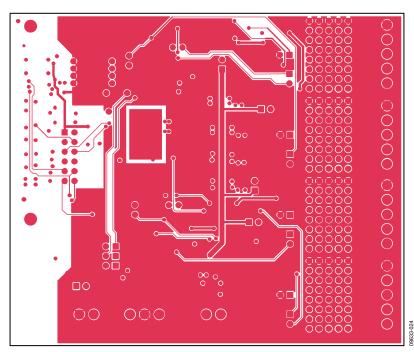

Figure 26. Bottom PCB Layer

# **ORDERING INFORMATION**

### **BILL OF MATERIALS**

#### Table 12.

| Qty | Reference Designator                                                                  | Part Description                                             | Part Number         | Stock Code                    |

|-----|---------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------|-------------------------------|

| 4   | C1, C42, C48, C52                                                                     | 10 μF, 10 V, SMD tantalum capacitor, Case A                  | TCJA106M010R0300    | FEC 1135234                   |

| 4   | C2, C32, C33, C44                                                                     | 4.7 μF, 50 V, X7R ceramic capacitor, 1210                    | GRM32ER71H475KA88L  | FEC 1404215                   |

| 5   | C4, C6, C8, C10, C16                                                                  | 10 μF, 50 V, X5R ceramic capacitor, 1210                     | UMK325BJ106MM-T     | FEC 1683595                   |

| 17  | C3, C5, C7, C9, C11, C12, C14, C21,<br>C22, C25, C31, C35, C39, C47, C51,<br>C54, C55 | 0.1 μF, 50 V, X7R ceramic capacitor, 0603                    | MCRR25101COGJ0100   | FEC 1288255                   |

| 4   | C15, C28 to C30                                                                       | 100 pF, 100 V, C0G ceramic capacitor, radial                 | B37979G1101J        | FEC 1216416                   |

| 4   | C17, C19, C20, C27                                                                    | 10 nF, 50 V, X7R ceramic capacitor, 0603                     | B37931K5103K60      | FEC 753622                    |

| 4   | C26, C37, C50, C56                                                                    | 10 μF, 16 V, X5R ceramic capacitor, 0805                     | GRM21BR61C106KE15L  | FEC 1762635                   |

| 1   | D1                                                                                    | Red, SMD LED, 0603                                           | SML-D12U8WT86       | FEC 1685094                   |

| 3   | D2, D11, D14                                                                          | Green, SMD LED, 0603                                         | SML-512MWT86R       | FEC 1685076                   |

| 4   | J1 to J4                                                                              | 5-pin terminal block (3.81 mm pitch)                         | 3704609             | FEC 3704609                   |

| 1   | J5                                                                                    | 3-pin terminal block (3.81 mm pitch)                         | 1727023             | FEC 3704580                   |

| 2   | J6, J7                                                                                | 2-pin terminal block (3.81 mm pitch)                         | 1727010             | FEC 3704579                   |

| 1   | J9                                                                                    | 120-way connector, 0.6 mm pitch                              | FX8-120S-SV(21)     | FEC 1324660                   |

| 1   | J11                                                                                   | 12-pin (2 × 6) 0.1" pitch header                             | M20-9980646         | FEC 1022238                   |

| 4   | L1 to L4                                                                              | Inductor                                                     | XAL4040-103         | Coilcraft XAL4040-103         |

| 16  | LK0 to L15                                                                            | 2-pin (0.1" pitch) header and jumper socket                  | M20-9990246         | FEC 1022247 and<br>FEC 150411 |

| 4   | R1, R2, R3, R4                                                                        | 15 kΩ, low drift, SMD resistor, 0805                         | PCF0805-13-15K-B-T1 | FEC 1108896                   |

| 1   | R5                                                                                    | 0 Ω, SMD resistor, 0603                                      | CRCW06030000Z0EA    | DNP                           |

| 7   | R6, R8, R9, R12, R13, R14, R15                                                        | 0 Ω, SMD resistor, 0603                                      | CRCW06030000Z0EA    | FEC 1469739                   |

| 1   | R10                                                                                   | 2.2 kΩ, SMD resistor, 0603                                   | CRCW06032K20JNEA    | FEC 1652868                   |

| 3   | R11, R18, R19                                                                         | 1 kΩ, SMD resistor, 0603                                     | CRCW06031K00JNEA    | FEC 1652851                   |

| 4   | R17, R20, R43, R44                                                                    | 10 Ω, SMD resistor, 0603                                     | CRCW060310R0FKEA    | FEC 1469751                   |

| 4   | SCH1 to SCH4                                                                          | 1 A, 60 V, Schottky diode, POWERDI323                        | PD3S160-7           | FEC 1843697                   |

| 3   | TP1 to TP3                                                                            | Test point                                                   |                     | DNP                           |

| 1   | U1                                                                                    | Quad 16-bit DAC with dynamic power control                   | AD5755              | AD5755BCPZ                    |

|     |                                                                                       |                                                              | AD5755-1            | AD5755-1ACPZ                  |

|     |                                                                                       |                                                              | AD5757              | AD5757ACPZ                    |

| 1   | U3                                                                                    | 5 V precision reference, 8-lead SOIC                         | ADR02BRZ            | ADR02BRZ                      |

| 1   | U4                                                                                    | 32 kB I <sup>2</sup> C serial EEPROM, 8-lead MSOP            | 24LC32A-I/MS        | FEC 1331330                   |

| 4   | U2, U5, U6, U7                                                                        | MOSFET P-channel, 30 V (only populate on EVAL-AD5757 boards) | FDMA530PZ           | Digi-Key<br>FDMA530PZCT-ND    |

#### **RELATED LINKS**

| Resource | Description                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------|

| AD5755   | Product Page, Quad Channel, 16-Bit, Serial Input, 4 mA to 20 mA and Voltage Output DAC, Dynamic Power Control                    |

| AD5757   | Product Page, Quad Channel, 16-Bit, Serial Input, 4 mA to 20 mA Output DAC, Dynamic Power Control, HART Connectivity             |

| AD5755-1 | Product Page, Quad Channel, 16-Bit, Serial Input, 4 mA to 20 mA and Voltage Output DAC, Dynamic Power Control, HART Connectivity |

| ADR02    | Product Page, Ultracompact, Precision 5.0 V Voltage Reference                                                                    |