# **RENESAS** FemtoClock<sup>®</sup> Crystal-to-LVDS Frequency Synthesizer

# 844008I-15

# DATASHEET

# **GENERAL DESCRIPTION**

FREQUENCY SELECT FUNCTION TABLE

The 844008I-15 is an 8 output LVDS Synthesizer optimized to generate PCI Express<sup>™</sup> reference clock frequencies and is a member of the high performance clock solutions from IDT. Using a 25MHz parallel resonant crystal, the following frequencies can be generated based on F\_SEL pin: 100MHz or 125MHz. The 844008I-15 uses IDT's 3<sup>rd</sup> generation low phase noise VCO technology and can achieve <1ps typical rms phase jitter, easily meeting PCI Express jitter requirements. The 844008I-15 is packaged in a 32-pin LQFP package.

# **F**EATURES

- Eight LVDS outputs

- · Crystal oscillator interface

- Supports the following output frequencies: 100MHz or 125MHz

- VCO: 500MHz

- RMS phase jitter @ 125MHz, using a 25MHz crystal (1.875MHz 20MHz): 0.42ps (typical)

- Full 3.3V supply modes

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

| Input<br>Frequency<br>(MHz) | F_SEL | M Divider<br>Value | N Divider<br>Value | M/N Divider<br>Value | Output<br>Frequency<br>(MHz) |

|-----------------------------|-------|--------------------|--------------------|----------------------|------------------------------|

| 25MHz                       | 0     | 20                 | 4                  | 5                    | 125                          |

| 25MHz                       | 1     | 20                 | 5                  | 4                    | 100 (default)                |

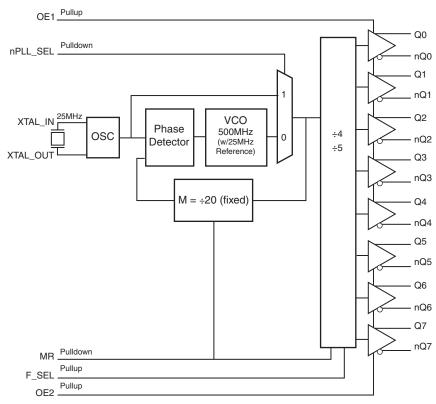

# BLOCK DIAGRAM

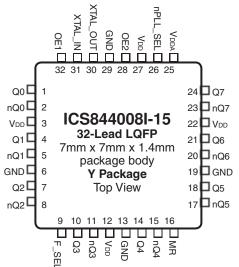

# **PIN ASSIGNMENT**

### TABLE 1. PIN DESCRIPTIONS

| Number           | Name                 | Т      | уре      | Description                                                                                                                                                                                                                                                 |

|------------------|----------------------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2             | Q0, nQ0              | Output |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 3, 12, 22,<br>27 | V                    | Power  |          | Core supply pin.                                                                                                                                                                                                                                            |

| 4, 5             | Q1, nQ1              | Ouput  |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 6, 13, 19,<br>29 | GND                  | Power  |          | Power supply ground.                                                                                                                                                                                                                                        |

| 7, 8             | Q2, nQ2              | Output |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 9                | F_SEL                | Input  | Pullup   | Frequency select pin LVCMOS/LVTTL interface levels.                                                                                                                                                                                                         |

| 10, 11           | Q3, nQ3              | Output |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 14, 15           | Q4, nQ4              | Output |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 16               | MR                   | Input  | Pulldown | Active HIGH Master Reset. When logic HIGH, the internal dividers are reset causing the true outputs Qx to go low and the inverted outputs nQx to go high. When logic LOW, the internal dividers and the outputs are enabled. LVCMOS/LVTTL interface levels. |

| 17, 18           | nQ5, Q5              | Output |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 20, 21           | nQ6, Q6              | Output |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 23, 24           | nQ7, Q7              | Output |          | Differential output pair. LVDS interface levels.                                                                                                                                                                                                            |

| 25               | V <sub>DDA</sub>     | Power  |          | Analog supply pin.                                                                                                                                                                                                                                          |

| 26               | nPLL_SEL             | Input  | Pulldown | Selects between the PLL and XTAL as input to the dividers. When LOW, selects PLL (PLL Enable). When HIGH, selects the XTAL (PLL Bypass). LVCMOS/LVTTL interface levels.                                                                                     |

| 28               | OE2                  | Input  | Pullup   | Output enable for Q5/nQ5:Q7/nQ7 outputs.<br>LVCMOS/LVTTL interface levels.                                                                                                                                                                                  |

| 30, 31           | XTAL_OUT,<br>XTAL_IN | Input  |          | Parallel resonant crystal interface. XTAL_OUT is the output, XTAL_IN is the input.                                                                                                                                                                          |

| 32               | OE1                  | Input  | Pullup   | Output enable for Q0/nQ0:Q4/nQ4 outputs.<br>LVCMOS/LVTTL interface levels.                                                                                                                                                                                  |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

### TABLE 2. PIN CHARACTERISTICS

| Symbol | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|--------|-------------------------|-----------------|---------|---------|---------|-------|

| C      | Input Capacitance       |                 |         | 4       |         | pF    |

|        | Input Pulldown Resistor |                 |         | 51      |         | kΩ    |

| R      | Input Pullup Resistor   |                 |         | 51      |         | kΩ    |

## TABLE 3A. OE1 FUNCTION TABLE

| Input | Outputs                      |

|-------|------------------------------|

| OE1   | Q0:Q4, nQ0:nQ4               |

| 0     | Places outputs in Hi-Z state |

| 1     | Normal operation             |

## TABLE 3B. OE2 FUNCTION TABLE

| Input | Outputs                      |

|-------|------------------------------|

| OE2   | Q5:Q7, nQ5:nQ7               |

| 0     | Places outputs in Hi-Z state |

| 1     | Normal operation             |

# RENESAS

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, $V_{_{DD}}$                                                                                            | 4.6V                        |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Inputs, V                                                                                                              | -0.5V to $V_{_{DD}}$ + 0.5V |

| Outputs, I <sub>o</sub><br>Continuous Current<br>Surge Current                                                         | 10mA<br>15mA                |

| Package Thermal Impedance, $\boldsymbol{\theta}_{_{\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | 65.7°C/W (0 mps)            |

| Storage Temperature, $T_{_{STG}}$                                                                                      | -65°C to 150°C              |

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

## **TABLE 4A. Power Supply DC Characteristics,** $_{DD} = V_{DDA} = 3.3V \pm 5\%$ , TA = -40°C to 85°C

| Symbol          | Parameter             | Test Conditions | Minimum            | Typical | Maximum | Units |

|-----------------|-----------------------|-----------------|--------------------|---------|---------|-------|

| V               | Core Supply Voltage   |                 | 3.135              | 3.3     | 3.465   | V     |

| V               | Analog Supply Voltage |                 | $V_{_{DD}} - 0.15$ | 3.3     | V       | V     |

|                 | Power Supply Current  |                 |                    |         | 150     | mA    |

| <b> </b><br>DDA | Analog Supply Current |                 |                    |         | 15      | mA    |

## **TABLE 4B. LVCMOS / LVTTL DC CHARACTERISTICS,** $_{DD} = V_{DDA} = 3.3V \pm 5\%$ , TA = -40°C to 85°C

| Symbol          | Parameter          |                 | Test Conditions                           | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------|-----------------|-------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage |                 | $V_{_{DD}} = 3.3V$                        | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| V               | Input Low Voltage  |                 | $V_{_{DD}} = 3.3V$                        | -0.3    |         | 0.8                   | V     |

|                 | Input              | MR, nPLL_SEL    | V <sub>DD</sub> = V <sub>IN</sub> = 3.465 |         |         | 150                   | μA    |

| н               | High Current       | OE1, OE2, F_SEL | $V_{_{DD}} = V_{_{IN}} = 3.465$           |         |         | 5                     | μA    |

| 1               | Input              | MR, nPLL_SEL    | $V_{_{DD}} = 3.465V, V_{_{IN}} = 0V$      | -5      |         |                       | μA    |

| L.              | Low Current        | OE1, OE2, F_SEL | $V_{_{DD}} = 3.465V, V_{_{IN}} = 0V$      | -150    |         |                       | μA    |

# Table 4C. LVDS DC Characteristics, $_{_{DD}} = V_{_{DDA}} = 3.3V \pm 5\%$ , Ta = -40°C to 85°C

| Symbol             | Parameter                                 | Test Conditions | Minimum | Typical | Maximum | Units |

|--------------------|-------------------------------------------|-----------------|---------|---------|---------|-------|

| V                  | Differential Output Voltage               |                 | 260     | 360     | 460     | mV    |

| $\Delta V_{_{OD}}$ | $V_{_{OD}}$ Magnitude Change              |                 |         |         | 50      | mV    |

| V <sub>os</sub>    | Offset Voltage                            |                 | 1.2     | 1.3     | 1.5     | V     |

| $\Delta V_{os}$    | V <sub>os</sub> Magnitude Change          |                 |         |         | 50      | mV    |

| I <sub>oz</sub>    | High Impedance Leakage Current            |                 | -10     | ±1      | 10      | μA    |

|                    | Power Off Leakage                         |                 | -20     | ±1      | 20      | μA    |

|                    | Differential Output Short Circuit Current |                 |         | -3.5    | -5      | mA    |

| I <sub>os</sub>    | Output Short Circuit Current              |                 |         | -3.5    | -5      | mA    |

### TABLE 5. CRYSTAL CHARACTERISTICS

| Parameter                          | Test Conditions | Minimum     | Typical | Maximum | Units |

|------------------------------------|-----------------|-------------|---------|---------|-------|

| Mode of Oscillation                |                 | Fundamental |         |         |       |

| Frequency                          |                 |             | 25      |         | MHz   |

| Parts per Million (ppm); NOTE 1    |                 |             |         | 100     | ppm   |

| Equivalent Series Resistance (ESR) |                 |             |         | 40      | Ω     |

| Shunt Capacitance                  |                 |             |         | 5       | pF    |

| Drive Level                        |                 |             |         | 100     | μW    |

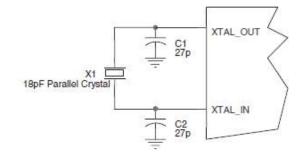

NOTE: Characterized using an18pF parallel resonant crystal.

NOTE 1: When used with recommended 50ppm crystal and external trim caps adjusted for user PC board.

| TABLE 6. AC CHARACTERISTICS, | $V_{DD} = V$ | $V_{_{DDA}}$ = 3.3V±5%, Ta = -40°C to 85°C |

|------------------------------|--------------|--------------------------------------------|

|------------------------------|--------------|--------------------------------------------|

| Symbol                            | Parameter                  | Test Conditions            | Minimum | Typical | Maximum | Units |

|-----------------------------------|----------------------------|----------------------------|---------|---------|---------|-------|

| f                                 | Output Frequency           | FSEL = 0                   |         | 125     |         | MHz   |

| OUT                               |                            | FSEL = 1                   |         | 100     |         | MHz   |

| tsk(o)                            | Output Skew; NOTE 1, 2     |                            |         |         | 110     | ps    |

| tsk(b) Bank Ske                   | Bank Skew; NOTE 2, 3       | Q0/nQ0:Q4/nQ4              |         |         | 50      | ps    |

| ISK(D)                            | Ballk Skew, NOTE 2, 3      | Q5/nQ5:Q7/nQ7              |         |         | 50      | ps    |

| tjit(cc)                          | Cycle-to-Cycle Jitter      |                            |         |         | 25      | ps    |

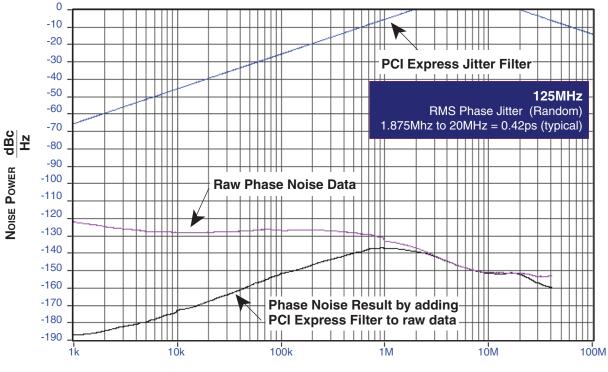

| +;;;+(0)                          | RMS Phase Jitter (Random); | 125MHz, (1.875MHz - 20MHz) |         | 0.42    |         | ps    |

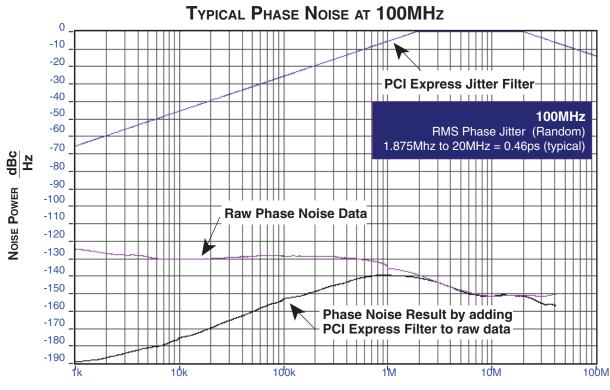

| $\pi\pi\pi\pi\nu$                 | NOTE 4                     | 100MHz, (1.875MHz - 20MHz) |         | 0.46    |         | ps    |

| t <sub>_R</sub> / t <sub>_F</sub> | Output Rise/Fall Time      | 20% to 80%                 | 100     |         | 600     | ps    |

| odc                               | Output Duty Cycle          |                            | 45      |         | 55      | %     |

Minimum and Maximum values are design target specs.

NOTE 1: Defined as skew between outputs at the same supply voltages and with equal load conditions. Measured at  $V_{p}/2$ .

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Defined as skew within a bank of outputs at the same voltages and with equal load conditions.

NOTE 4: Please refer to the Phase Noise Plot.

TYPICAL PHASE NOISE AT 125MHz

**OFFSET FREQUENCY (Hz)**

**OFFSET FREQUENCY (Hz)**

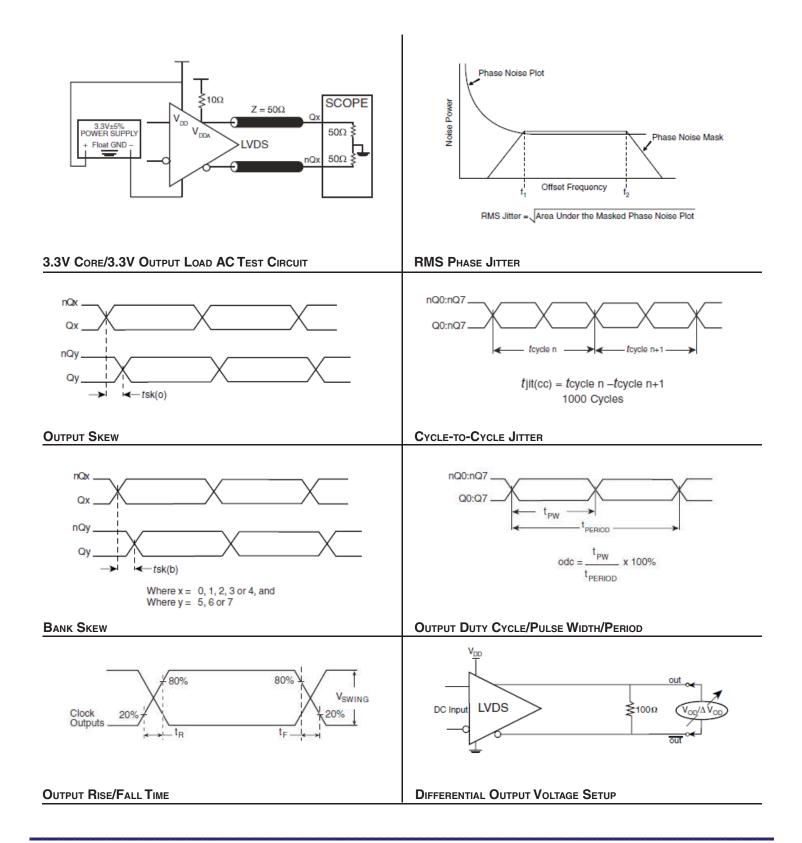

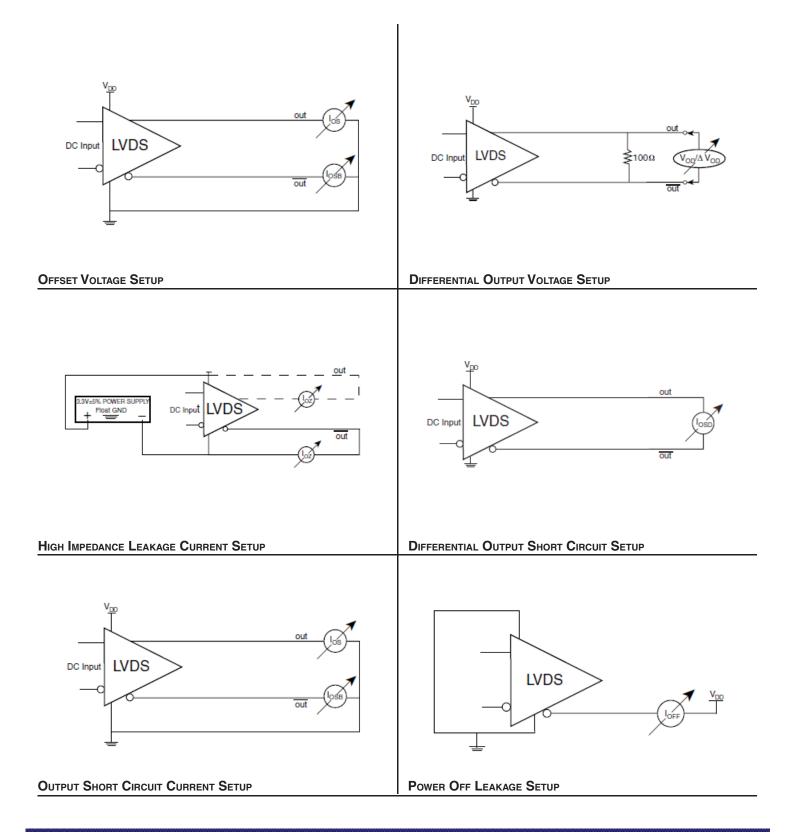

# **PARAMETER MEASUREMENT INFORMATION**

# **PARAMETER MEASUREMENT INFORMATION, CONTINUED**

# **APPLICATION** INFORMATION

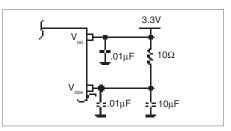

#### **POWER SUPPLY FILTERING TECHNIQUES**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. The 844008I-15 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL.  $V_{_{DD}}$  and  $V_{_{DDA}}$  should be individually connected to the power supply plane through vias, and bypass capacitors should be used for each pin. To achieve optimum jitter performance, power supply isolation is required. *Figure 1* illustrates how a  $10\Omega$  resistor along with a  $10\mu$ F and a  $0.01\mu$ F bypass capacitor should be connected to each  $V_{_{DDA}}$ .

FIGURE 1. POWER SUPPLY FILTERING

### **CRYSTAL INPUT INTERFACE**

The 844008I-15 has been characterized with an 18pF parallel resonant crystals. The capacitor values shown in

*Figure 2* below were determined using a 25MHz parallel resonant crystal and were chosen to minimize the ppm error.

FIGURE 2. CRYSTAL INPUT INTERFACE

## **RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS**

#### **INPUTS:**

#### LVCMOS CONTROL PINS:

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

### **OUTPUTS:**

#### LVDS

All unused LVDS outputs should be terminated with 100  $\!\Omega$  resistor between the differential pair.

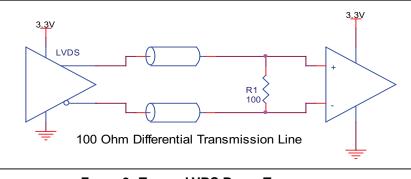

## **3.3V LVDS DRIVER TERMINATION**

A general LVDS interface is shown in *Figure 3*. In a 100 $\Omega$  differential transmission line environment, LVDS drivers require a matched load termination of 100 $\Omega$  across near the receiver input. For a

multiple LVDS outputs buffer, if only partial outputs are used, it is recommended to terminate the unused outputs.

FIGURE 3. TYPICAL LVDS DRIVER TERMINATION

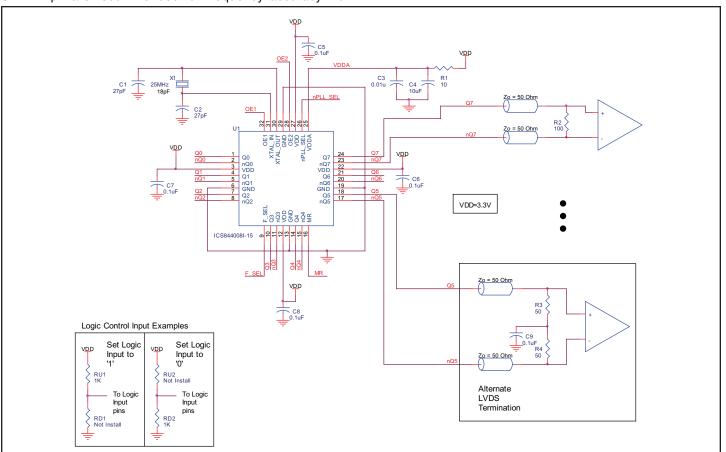

## SCHEMATIC EXAMPLE

*Figure 4* shows an example of 844008I-15 application schematic. In this example, the device is operated at V =3.3V. The 18pF parallel resonant 25MHz crystal is used. The C1 = 27pF and C2 = 27pF are recommended for frequency accuracy. For

different board layout, the C1 and C2 may be slightly adjusted for optimizing frequency accuracy. Two examples of LVDS for receiver without built-in termination are shown in this schematic.

# **Power Considerations**

This section provides information on power dissipation and junction temperature for the 844008I-15. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the 844008I-15 is the sum of the core power plus the power dissipated in the load(s). The following is the power dissipation for  $V_{nn} = 3.3V + 5\% = 3.465V$ , which gives worst case results.

Power (core)<sub>MAX</sub> = V<sub>DD,MAX</sub> \* (I<sub>DD,MAX</sub> + I<sub>DDA,MAX</sub>) = 3.465V \* (150mA + 15mA) = 571.73mW

#### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the device. The maximum recommended junction temperature for HiPerClockS<sup>™</sup> devices is 125°C.

The equation for Tj is as follows:  $Tj = \theta_{JA} * Pd_{total} + T_A$

Tj = Junction Temperature

$\theta_{JA}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

$T_{A} = Ambient Temperature$

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{JA}$  must be used. Assuming no air flow and a multi-layer board, the appropriate value is 65.7°C/W per Table 7 below.

Therefore, Tj for an ambient temperature of 85°C with all outputs switching is:  $85^{\circ}C + 0.572W * 65.7^{\circ}C/W = 122.5^{\circ}C$ . This is below the limit of  $125^{\circ}C$ .

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow, and the type of board (single layer or multi-layer).

#### TABLE 7. THERMAL RESISTANCE $\theta_{\text{JA}}$ for 32-Lead LQFP, Forced Convection

| θ <sub>JA</sub> by Velocity (Meters per Second) |          |          |          |  |

|-------------------------------------------------|----------|----------|----------|--|

|                                                 | 0        | 1        | 2.5      |  |

| Multi-Layer PCB, JEDEC Standard Test Boards     | 65.7°C/W | 55.9°C/W | 52.4°C/W |  |

# **R**ELIABILITY INFORMATION

# Table 8. $\theta_{_{JA}} \text{vs.}$ Air Flow Table for 32 Lead LQFP

| θ <sub>JA</sub> by Veloc                    | ity (Meters per | Second)  |          |

|---------------------------------------------|-----------------|----------|----------|

|                                             | 0               | 1        | 2.5      |

| Multi-Layer PCB, JEDEC Standard Test Boards | 65.7°C/W        | 55.9°C/W | 52.4°C/W |

### TRANSISTOR COUNT

The transistor count for 844008I-15 is: 2609

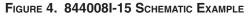

PACKAGE OUTLINE - Y SUFFIX FOR 32 LEAD LQFP

TABLE 9. PACKAGE DIMENSIONS

| JEDEC VARIATION<br>ALL DIMENSIONS IN MILLIMETERS |            |         |            |  |  |

|--------------------------------------------------|------------|---------|------------|--|--|

| CYMDOL                                           | BBA        |         |            |  |  |

| SYMBOL                                           | MINIMUM    | NOMINAL | MAXIMUM    |  |  |

| N                                                | 32         |         |            |  |  |

| Α                                                |            |         | 1.60       |  |  |

| A1                                               | 0.05       |         | 0.15       |  |  |

| A2                                               | 1.35       | 1.40    | 1.45       |  |  |

| b                                                | 0.30       | 0.37    | 0.45       |  |  |

| с                                                | 0.09       |         | 0.20       |  |  |

| D                                                | 9.00 BASIC |         |            |  |  |

| D1                                               | 7.00 BASIC |         |            |  |  |

| D2                                               | 5.60 Ref.  |         |            |  |  |

| Е                                                | 9.00 BASIC |         |            |  |  |

| E1                                               | 7.00 BASIC |         |            |  |  |

| E2                                               | 5.60 Ref.  |         |            |  |  |

| е                                                | 0.80 BASIC |         |            |  |  |

| L                                                | 0.45       | 0.60    | 0.75       |  |  |

| θ                                                | 0°         |         | <b>7</b> ° |  |  |

| ccc                                              |            |         | 0.10       |  |  |

Reference Document: JEDEC Publication 95, MS-026

### TABLE 10. ORDERING INFORMATION

| Part/Order Number | Marking      | Package                  | Shipping Packaging | Temperature   |

|-------------------|--------------|--------------------------|--------------------|---------------|

| 844008BYI-15LF    | ICS4008BI15L | 32 Lead "Lead-Free" LQFP | tube               | -40°C to 85°C |

| 844008BYI-15LFT   | ICS4008BI15L | 32 Lead "Lead-Free" LQFP | tape & reel        | -40°C to 85°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

### **REVISION HISTORY SHEET**

| Rev | Table | Page | Description of Change                                                                    | Date   |

|-----|-------|------|------------------------------------------------------------------------------------------|--------|

| A   | T10   |      | Ordering Information - Removed ICS from Part/Order number.<br>Updated data sheet format. | 7/2/15 |

|     |       |      |                                                                                          |        |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>