# MM74C945, MM74C947 4-Digit Up/Down Counter/Latch/Decoder Driver

## **General Description**

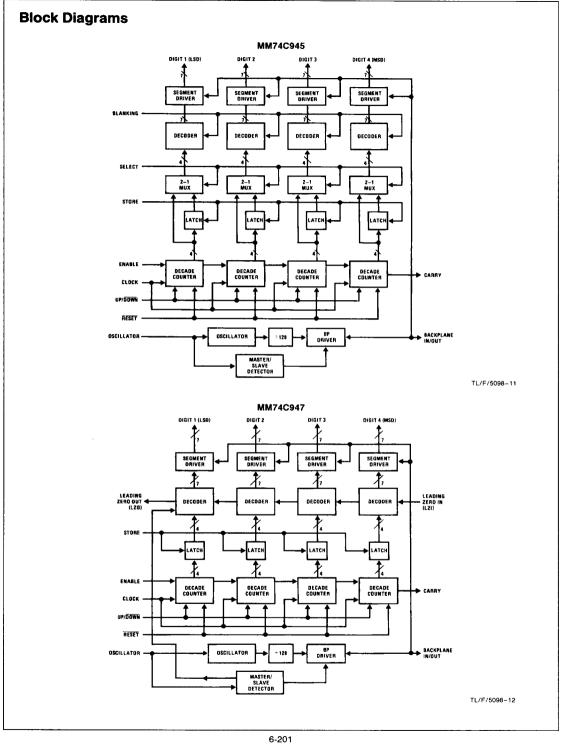

The MM74C945, MM74C947 are 4-digit counters for directly driving LCD displays. The MM74C945 contains a 4-decade up/down counter, output latches, counter/latch select multiplexer and 7-segment decoders. Also included are the backplane oscillator/driver, segment drivers and display blanking circuitry.

The MM74C947 differs from the MM74C945 in that it has no counter/latch multiplexer, but provides true leading zero blanking. All leading zeroes are automatically blanked except the least significant digit, which can be optionally blanked.

Both devices provide 28-segment outputs to drive a 4-digit display. Segment and backplane waveforms are generated internally, but can also be slaved to an external signal. This facilitates cascading of multiple displays.

#### **Features**

- 4-decade up/down count

- Direct 4-digit drive for high contrast and long display life

- Carry/borrow out for cascading counters

- Schmitt trigger clock input

- MM74C945 has display select to allow viewing of counter or latch

- Store and reset inputs allow operation as frequency or period counter

- MM74C947 has true ripple blanking; least significant digit may be optionally blanked

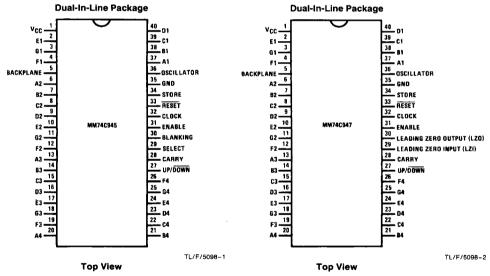

## **Connection Diagrams**

Order Number MM74C945\*

Order Number MM74C947\*

\*Please look into Section 8, Appendix D for availability of various package types.

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Voltage at Any Pin -0.3V to  $V_{CC} + 0.3V$

Operating Temperature Range (T<sub>A</sub>) MM74C945/MM74C947

-40°C to +85°C

Storage Temperature Range ( $T_S$ ) Power Dissipation ( $P_D$ ) Operating  $V_{CC}$  Range Absolute Maximum  $V_{CC}$ Lead Temperature ( $T_L$ ) (Soldering, 10 seconds) - 65°C to + 150°C 500 mW 3.0V to 6.0V 6.5V

300°C

# DC Electrical Characteristics Min/Max limits apply across temperature range, unless otherwise noted

| Parameter                                                            | Conditions                                                           | Min                    | Тур     | Max                   | Units |

|----------------------------------------------------------------------|----------------------------------------------------------------------|------------------------|---------|-----------------------|-------|

| MOS TO CMOS                                                          |                                                                      |                        |         |                       |       |

| V <sub>T+</sub> Positive Going Threshold<br>Voltage (Clock Only)     | $V_{CC} = 5V, V_{IN} (0 \rightarrow 5) V$                            | 2.5                    | 2.9     | 3.25                  | V     |

| V <sub>T</sub> Negative Going Threshold<br>Voltage (Clock Only)      | $V_{CC} = 5V, V_{IN} (0 \rightarrow 5) V$                            | 1.5                    | 2.2     | 2.4                   | >     |

| Hysteresis (V <sub>T+</sub> - V <sub>T-</sub> )<br>(Clock Only)      | V <sub>CC</sub> = 5V                                                 | 0.1                    | 0.7     | 1.75                  | >     |

| Logical "1" Input Voltage (V <sub>IN(1)</sub> )                      | V <sub>CC</sub> = 5V                                                 | 3.5                    |         |                       | >     |

| Logical "0" Input Voltage (VIN(0))                                   | V <sub>CC</sub> = 5V                                                 |                        |         | 1.5                   | >     |

| Logical "1" Output Voltage<br>(V <sub>OUT(1)</sub> ) (LZO and Carry) | $V_{CC} = 5V, I_{O} = -10 \mu\text{A}$                               | 4.5                    |         |                       | >     |

| Logical "0" Output Voltage (V <sub>OUT(0)</sub> ) (LZO and Carry)    | $V_{CC} = 5V, I_{O} = +10 \mu\text{A}$                               |                        |         | 0.5                   | >     |

| Clock Input Current IIN                                              | $V_{CC} = 5V, V_{IN} = 5V/0V$                                        |                        | 0.005   | 1.0                   | μΑ    |

| Input Current @ Pins 29, 31, 33<br>and 34 (Note 2)                   | V <sub>CC</sub> = 5V, V <sub>IN</sub> = 0V                           | -2.0                   | -12     | -25                   | μΑ    |

| Oscillator Input Current (IOSL)                                      | $V_{CC} = 5V, V_{IN} = 0V/5V$                                        |                        | ±1      | ± 10.0                | μΑ    |

| Supply Current (I <sub>CC</sub> ) (Note 3)                           | V <sub>CC</sub> = 5V, V <sub>IN</sub> = 0V/5V                        |                        | 10      | 60                    | μΑ    |

| Oscillator Input Voltage VIH (OSC) VIL (OSC)                         | When Driving Oscillator<br>Pin with External<br>Signal               | 0.2 V <sub>CC</sub>    |         | V <sub>CC</sub> - 0.2 | >>    |

| DC Offset Voltage (Note 4)                                           | V <sub>CC</sub> = 5V                                                 |                        |         | 25                    | m∨    |

| MOS/LPTTL INTERFACE                                                  |                                                                      |                        |         |                       |       |

| Logical "1" Input Voltage<br>(V <sub>IN(1)</sub> )                   | V <sub>CC</sub> = 4.75V                                              | V <sub>CC</sub> - 1.5V |         |                       | ٧     |

| Logical "0" Input Voltage<br>(V <sub>IN(0)</sub> )                   | V <sub>CC</sub> = 4.75V                                              |                        |         | 0.8                   | v     |

| Logical "1" Output Voltage<br>(V <sub>OUT(1)</sub> ) (LZO and Carry) | $V_{CC} = 4.75V, I_{O} = -360 \mu\text{A}$                           | 2.4                    |         |                       | V     |

| Logical "0" Output Voltage<br>(V <sub>OUT(0)</sub> ) (LZO and Carry) | $V_{CC} = 4.75V, I_{O} = 360 \mu A$                                  |                        |         | 0.4                   | ٧     |

| OUTPUT DRIVE (Short Circuit Curre                                    | ent)                                                                 |                        | · · · · |                       | •     |

| Output Source Current (ISOURCE) (LZO and Carry)                      | $V_{CC} = 5V, V_{OUT} = 0V$<br>$T_A = 25^{\circ}C$                   | 1.75                   | 2.7     |                       | mA    |

| Output Sink Current (I <sub>SINK</sub> ) (LZO and Carry)             | $V_{CC} = 5V$ , $V_{OUT} = 5V$<br>$T_A = 25$ °C                      | 1.75                   | 3.2     |                       | mA    |

| Output Source Current (ISOURCE) (Segment Outputs)                    | $V_{CC} = 5V$ , $V_{OUT} = 0V$<br>$T_A = 25$ °C                      | 1.4                    | 2.0     |                       | mA    |

| Output Sink Current<br>(I <sub>SINK</sub> ) (Segment Output)         | V <sub>CC</sub> = 5V, V <sub>OUT</sub> = 5V<br>T <sub>A</sub> = 25°C | 1.4                    | 2.2     |                       | mA    |

| Output Source Current (ISOURCE) (Backplane Output)                   | V <sub>CC</sub> = 5V, V <sub>OUT</sub> = 0V<br>T <sub>A</sub> = 25°C | 12.6                   | 15.0    |                       | mA    |

| Output Sink Current (ISINK) (Backplane Output)                       | $V_{CC} = 5V, V_{OUT} = 5V$<br>$T_A = 25^{\circ}C$                   | 12.6                   | 20.0    |                       | mA    |

# AC Electrical Characteristics\* $T_J = 25^{\circ}C, C_L = 50 \text{ pF}, \text{ unless otherwise specified}$

| Symbol                              | Parameter                        | Conditions                                 | Min | Тур | Max      | Units |

|-------------------------------------|----------------------------------|--------------------------------------------|-----|-----|----------|-------|

| t <sub>pd0</sub> , t <sub>pd1</sub> | Propagation Delay Clock to Carry | V <sub>CC</sub> = 5.0V                     |     | 375 | 600      | ns    |

| folk                                | Maximum Clock Frequency          | V <sub>CC</sub> = 5.0V                     | 2   | 3   |          | MHz   |

| t <sub>r</sub> , t <sub>f</sub>     | Clock Input Rise or Fall Time    | V <sub>CC</sub> = 5.0V                     |     |     | No Limit | MHz   |

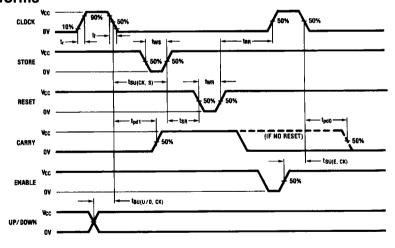

| t <sub>WR</sub>                     | Reset Pulse Width                | $V_{CC} = 5.0V$                            | 180 | 120 |          | ns    |

| tws                                 | Store Pulse Width                | V <sub>CC</sub> = 5.0V                     | 150 | 80  |          | ns    |

| tsu (CK, S)                         | Clock to Store Set-Up Time       | $V_{CC} = 5.0V$                            | 500 | 270 |          | ns    |

| t <sub>SR</sub>                     | Store to Reset Wait Time         | V <sub>CC</sub> = 5.0V                     | 280 | 170 |          | ns    |

| t <sub>SU</sub> (E, CK)             | Enable to Clock Set-Up Time      | V <sub>CC</sub> = 5.0V                     | 140 | 80  |          | ns    |

| t <sub>RR</sub>                     | Reset Removal                    | V <sub>CC</sub> = 5.0V                     | 50  | 0   |          | ns    |

| tsu (u/p, ck)                       | Up/Down to Clock Set-Up Time     | V <sub>CC</sub> = 5.0V                     | 300 | 190 |          | ns    |

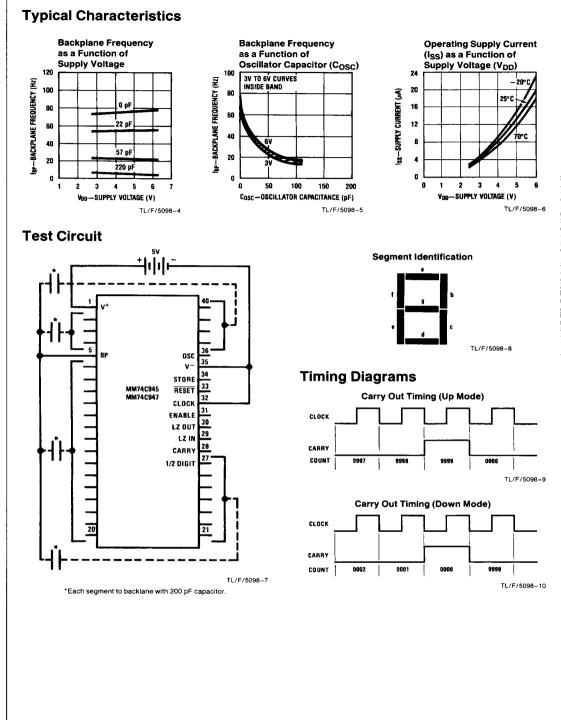

| f <sub>BP</sub>                     | Backplane Output Frequency       | Pin 36 Floating,<br>V <sub>CC</sub> = 5.0V |     | 85  |          | Hz    |

| C <sub>IN</sub>                     | Input Capacitance                | Logic Inputs (Note 2)                      |     | 5   |          | рF    |

| t <sub>rfs</sub>                    | Segment Rise/Fall Time           | C <sub>load</sub> = 200 pF                 |     | 0.5 |          | μs    |

| t <sub>rfb</sub>                    | Backplane Rise/Fall time         | C <sub>load</sub> = 5000 pF                |     | 1.5 |          | μs    |

| f <sub>osc</sub>                    | Oscillator Frequency             | Pin 36 Floating,<br>V <sub>CC</sub> = 5.0V |     | 11  |          | kHz   |

<sup>\*</sup>AC Parameters are guaranteed by DC correlated testing.

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Does not apply to backplane and oscillator pins.

Note 3: Display blanked. See Test Circuit.

Note 4: DC offset voltage is the effective DC voltage the LCD will have between any segment and the backplane.

#### **AC Waveforms**

TL/F/5098-3

### **Pin Description**

Backplane In/Out—When the oscillator input is grounded this pin is an input allowing an external device to generate a backplane waveform. When the oscillator input is left open this pin is an output supplying backplane drive for the display.

Oscillator—The oscillator frequency may be lowered by tying a capacitor (C<sub>OSC</sub>) to this pin. On the MM74C947, when the oscillator pin is open, the LSD is inhibited from blanking when leading zero blanking is enabled. If this pin is grounded, the backplanes on both parts become inputs, slaving the device to an external backplane.

Store—This input controls the on-chip latches. When low, the latches are in flow-through mode (latch outputs follow counter), but when taken high, the data on the counter outputs are stored in the latches.

Reset—When low, counters are reset to zero.

Clock-Advances counters on negative edge.

Enable—When low, halts counter operation.

Leading Zero Input (LZI)—(MM74C947) When high, enables leading zero blanking.

**Leading Zero Output (LZO)**—(MM74C947) This output goes high when the latch contents equal zero, LZI is high and the oscillator pin is open.

Blanking—(MM74C945) When high, blanks display.

**Select**—(MM74C945) When high, the contents of the counter are displayed. When low, the contents of the latch are displayed.

Carry—This outputs goes high when 9999 is reached (up) or 0000 is reached (down).

**Up/Down**—When high, the counter counts up. When low, the counter counts down.

A1-G1-Digit 1 segment outputs.

A2-G2-Digit 2 segment outputs.

A3-G3-Digit 3 segment outputs.

A4-G4-Digit 4 segment outputs.

# **Application Hints**

#### **DISPLAY CIRCUITRY DESCRIPTION**

The MM74C945 and MM74C947 have 28 segment outputs capable of directly driving 4 digits of 7 segments. Both the segment and backplane drivers are designed to provide matched rise and fall times eliminating possible DC components in the driving waveforms which could degrade display life (i.e., DC offset voltage).

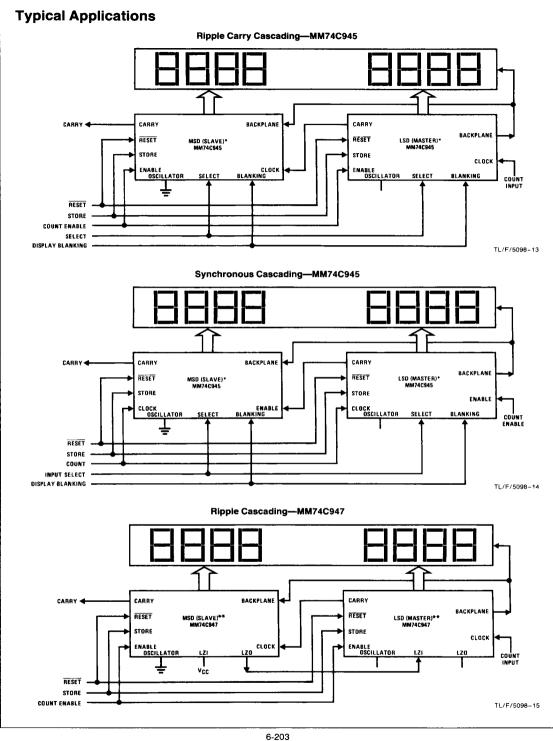

The backplane driver can be disabled by grounding the oscillator pin. This enables the segment output waveforms to be synchronized to an external signal applied to the backplane pin. Several devices can then be driven by a single master backplane waveform which can be generated by another MM74C945, MM74C947 or an external oscillator. Thus single backplane displays with 8, 12, 16, etc. digits can

be driven with several counters. The maximum fanout of a master backplane driver is limited by its total capacitive load, which is the sum of the slaved backplane input capacitances and the display backplane capacitance. (The MM74C947 oscillator pin controls the least significant digit blanking as well.)

An on-board oscillator/divider generates the segment/backplane waveforms. Its output frequency is typically 85 Hz, but may be lowered by connecting an external capacitor ( $C_{OSC}$ ) between the oscillator pin and ground. The oscillator pin may also be driven by an external waveform but the input low level must not go to ground or else the backplane pin will be put in the slave (input) mode (see  $V_{IH(OSC)}$  and  $V_{IL(OSC)}$  specifications).

#### COUNTER CIRCUITRY DESCRIPTION

The MM74C945, MM74C947 are 4-decade up/down counters. The direction of the count is controlled by the up/down input. A high level on this pin causes the counter to count up. The counter advances on the negative clock edge. The carry output is high for one clock period during a count of 9999 in up mode, or during a count of 0000 in down mode. The carry is designed to allow cascading of several circuits in either ripple carry or synchronous modes.

Reset and Enable controls are provided to allow period and frequency measurements. The Reset control clears the counter when low and the Enable control disables counting when taken low.

The counter chain feeds a series of 4-bit flow-through latches. These latches enable the display to follow the counter when the Store input is low. When the Store pin is taken high the data on the counter outputs at this time become latched and the display will remain unchanged. (Assuming the latch display is selected on MM74C945.)

On the MM74C945 the latch outputs feed a multiplexer which selects either the latch outputs or counter outputs for display. This allows an intermediate count to be stored in the latches while the counter continues to be displayed. This is equivalent to a stopwatch lap feature.

The output of the MM74C945's multiplexer feeds a decoder which converts 4-bit input to 7-segment outputs. A blanking control into these decoders blanks the display.

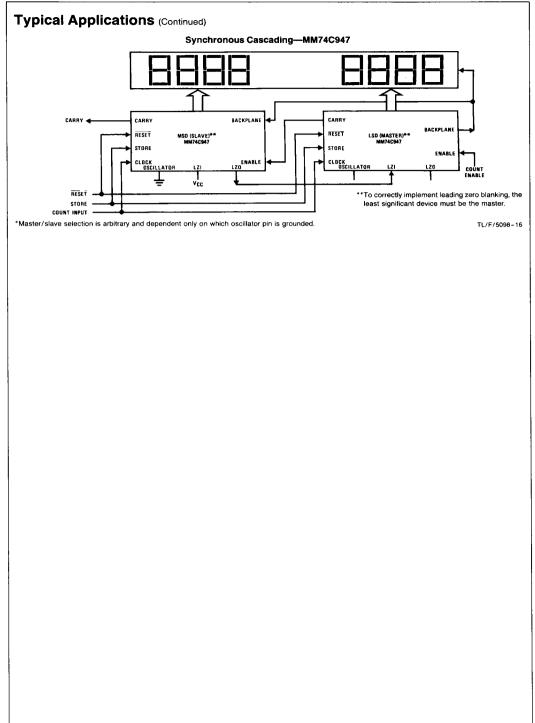

On the MM74C947 the latch outputs feed the decoders directly, but these decoders have a special ripple blanking capability that enables all leading zeroes except the least significant digit (LSD) to be blanked, even when counters are cascaded. Thus when the entire counter reads zero, instead of blanking all digits, the LSD will remain on. (When multiple counters are cascaded, all except the least significant counter will blank entirely on zeroes.) This feature is properly implemented by configuring the least significant device as the master (oscillator pin ungrounded) thereby inhibiting LSD blanking.

The outputs of the decoders for both devices control the segment drivers, which in turn enable display operation.