# onsemi

## **MOSFET** – N-Channel, POWERTRENCH<sup>®</sup>

## 100 V, 3.3 A, 100 m $\Omega$

# FDT86113LZ

## **General Description**

This N-Channel logic Level MOSFET is produced using **onsemi**'s advanced POWERTRENCH process that has been special tailored to minimize the on-state resistance and yet maintain superior switching performance. G-S zener has been added to enhance ESD voltage level.

## Features

- Max  $r_{DS(on)} = 100 \text{ m}\Omega$  at  $V_{GS} = 10 \text{ V}$ ,  $I_D = 3.3 \text{ A}$

- Max  $r_{DS(on)} = 145 \text{ m}\Omega$  at  $V_{GS} = 4.5 \text{ V}$ ,  $I_D = 2.7 \text{ A}$

- High Performance Trench Technology for Extremely Low rDS(on)

- High Power and Current Handling Capability in a Widely Used Surface Mount Package

- HBM ESD Protection Level > 3 kV Typical (Note 4)

- 100% UIL Tested

- This Device is Pb–Free and Halide Free

## Applications

• DC – DC Switch

## Specifications

#### **MOSFET MAXIMUM RATINGS** (T<sub>A</sub> = 25°C unless otherwise noted)

| Symbol                            | Para                                      | Ratings                         | Unit |   |

|-----------------------------------|-------------------------------------------|---------------------------------|------|---|

| V <sub>DS</sub>                   | Drain to Source Volta                     | 100                             | V    |   |

| V <sub>GS</sub>                   | Gate to Source Voltag                     | ±20                             | V    |   |

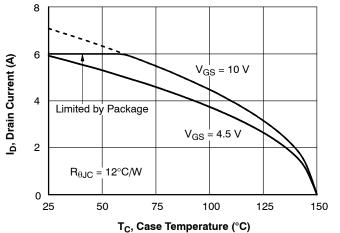

| Ι <sub>D</sub>                    | Drain Current                             | -Continuous                     | 3.3  | А |

|                                   |                                           | -Pulsed                         | 12   |   |

| E <sub>AS</sub>                   | Single Pulse Avalance                     | 9                               | mJ   |   |

| PD                                | Power Dissipation                         | T <sub>A</sub> = 25°C (Note 1a) | 2.2  | W |

|                                   |                                           | $T_A = 25^{\circ}C$ (Note 1b)   | 1.0  |   |

| T <sub>J</sub> , T <sub>STG</sub> | Operating and Storag<br>Temperature Range | -55 to +150                     | °C   |   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

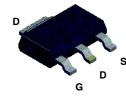

SOT-223 CASE 318H

## MARKING DIAGRAM

A = Assembly Location

= Year

Υ

W = Work Week

113LZ = Specific Device Code

= Pb-Free Package

(Note: Microdot may be in either location)

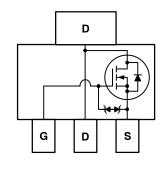

## PIN ASSIGNMENT

## **ORDERING INFORMATION**

See detailed ordering and shipping information on page 6 of this data sheet.

## THERMAL CHARACTERISTICS

| Symbol          | Parameter                                         | Ratings | Unit |

|-----------------|---------------------------------------------------|---------|------|

| $R_{\theta JC}$ | Thermal Resistance, Junction to Case              | 12      | °C/W |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient (Note 1a) | 55      |      |

## **ELECTRICAL CHARACTERISTICS** (T<sub>J</sub> = $25^{\circ}C$ unless otherwise noted)

| Symbol                                                             | Parameter                                                   | Test Conditions                                                                        | Min | Тур  | Max | Unit  |

|--------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|-----|-------|

| FF CHARA                                                           | ACTERISTICS                                                 |                                                                                        |     | •    |     |       |

| BV <sub>DSS</sub>                                                  | Drain to Source Breakdown Voltage                           | $I_D = 250 \ \mu A, \ V_{GS} = 0 \ V$                                                  | 100 |      |     | V     |

| $\frac{\Delta \text{BV}_{\text{DSS}}}{\Delta \text{T}_{\text{J}}}$ | Breakdown Voltage Temperature<br>Coefficient                | $I_D = 250 \ \mu\text{A}, \text{Referenced to } 25^\circ\text{C}$                      |     | 71   |     | mV/°C |

| I <sub>DSS</sub>                                                   | Zero Gate Voltage Drain Current                             | V <sub>DS</sub> = 80 V, V <sub>GS</sub> = 0 V                                          |     |      | 1   | μA    |

| I <sub>GSS</sub>                                                   | Gate to Source Leakage Current                              | $V_{GS}$ = ±20 V, $V_{DS}$ = 0 V                                                       |     |      | ±10 | μA    |

| N CHARA                                                            | CTERISTICS                                                  |                                                                                        |     |      |     |       |

| V <sub>GS(th)</sub>                                                | Gate to Source Threshold Voltage                            | $V_{GS} = V_{DS}, I_D = 250 \ \mu A$                                                   | 1.0 | 1.7  | 2.5 | V     |

| $\frac{\Delta V_{\text{GS(th)}}}{\Delta T_{\text{J}}}$             | Gate to Source Threshold Voltage<br>Temperature Coefficient | $I_D$ = 250 µA, Referenced to 25°C                                                     |     | -5   |     | mV/°C |

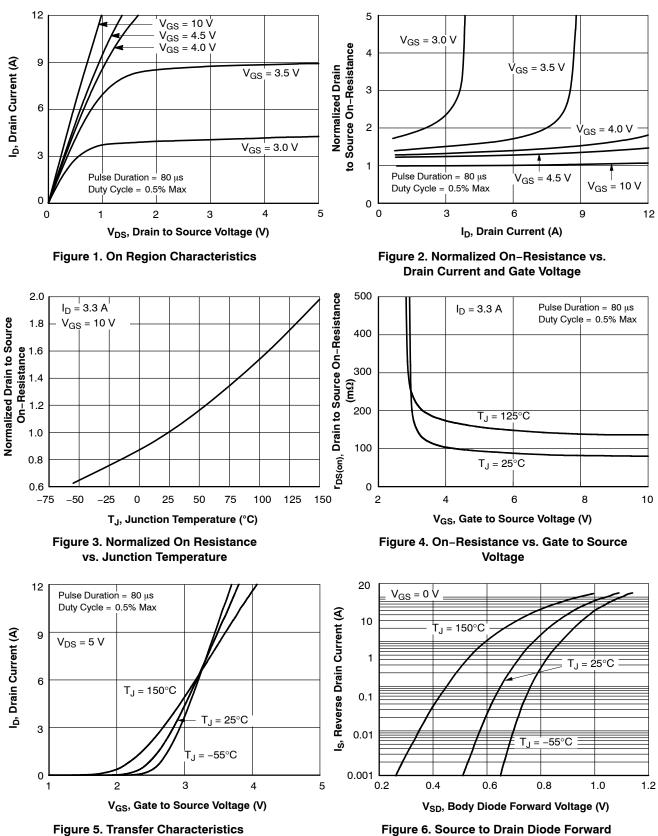

| r <sub>DS(on)</sub>                                                | Static Drain to Source On Resistance                        | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 3.3 A                                         |     | 75   | 100 | mΩ    |

|                                                                    |                                                             | $V_{GS}$ = 4.5 V, I <sub>D</sub> = 2.7 A                                               |     | 95   | 145 | 1     |

|                                                                    |                                                             | $V_{GS}$ = 10 V, I <sub>D</sub> = 3.3 A, T <sub>J</sub> = 125°C                        |     | 140  | 189 |       |

| 9FS                                                                | Forward Transconductance                                    | V <sub>DS</sub> = 10 V, I <sub>D</sub> = 3.3 A                                         |     | 8    |     | S     |

| YNAMIC C                                                           | HARACTERISTICS                                              | ·                                                                                      |     |      |     |       |

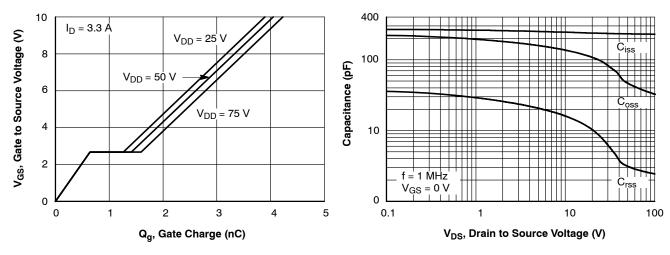

| C <sub>iss</sub>                                                   | Input Capacitance                                           | V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0 V, f = 1 MHz                               |     | 234  | 315 | pF    |

| C <sub>oss</sub>                                                   | Output Capacitance                                          |                                                                                        |     | 46   | 65  | pF    |

| C <sub>rss</sub>                                                   | Reverse Transfer Capacitance                                |                                                                                        |     | 3.1  | 5   | pF    |

| WITCHING                                                           | CHARACTERISTICS                                             |                                                                                        |     |      |     |       |

| t <sub>d(on)</sub>                                                 | Turn-On Delay Time                                          | $V_{DD} = 50 \text{ V}, \text{ I}_{D} = 3.3 \text{ A}, \text{ V}_{GS} = 10 \text{ V},$ |     | 3.8  | 10  | ns    |

| t <sub>r</sub>                                                     | Rise Time                                                   | $R_{GEN} = 6 \Omega$                                                                   |     | 1.3  | 10  | ns    |

| t <sub>d(off)</sub>                                                | Turn-Off Delay Time                                         |                                                                                        |     | 10   | 20  | ns    |

| t <sub>f</sub>                                                     | Fall Time                                                   |                                                                                        |     | 1.5  | 10  | ns    |

| Q <sub>g</sub> 1                                                   | Total Gate Charge                                           | $V_{GS}$ = 0 V to 10 V, $V_{DD}$ = 50 V, $I_{D}$ = 3.3 A                               |     | 4.1  | 6.8 | nC    |

|                                                                    |                                                             | $V_{GS}$ = 0 V to 5 V, $V_{DD}$ = 50 V, $I_{D}$ = 3.3 A                                |     | 2.3  | 3.9 | nC    |

| Q <sub>gs</sub>                                                    | Gate to Source Gate Charge                                  | V <sub>DD</sub> = 50 V, I <sub>D</sub> = 3.3 A                                         |     | 0.68 |     | nC    |

| Q <sub>gd</sub>                                                    | Gate to Drain "Miller" Charge                               | 1 1                                                                                    |     | 0.85 |     | nC    |

| RAIN-SOU                                                           | JRCE DIODE CHARACTERISTICS                                  |                                                                                        |     | •    |     | •     |

| V <sub>SD</sub>                                                    | Source to Drain Diode Forward                               | V <sub>GS</sub> = 0 V, I <sub>S</sub> = 3.3 A (Note 2)                                 |     | 0.86 | 1.3 | V     |

| V                                                                  | Voltage                                                     |                                                                                        |     | 0.77 | 10  | 1     |

| V <sub>SD</sub> | Voltage                 | $V_{GS} = 0 V, I_S = 3.3 A (Note 2)$                   | 0.86 | 1.3 | v  |

|-----------------|-------------------------|--------------------------------------------------------|------|-----|----|

|                 | Voltage                 | V <sub>GS</sub> = 0 V, I <sub>S</sub> = 1.0 A (Note 2) | 0.77 | 1.2 |    |

| t <sub>rr</sub> | Reverse Recovery Time   | I <sub>F</sub> = 3.3 A, di/dt = 100 A/μs               | 31   | 49  | ns |

| Q <sub>rr</sub> | Reverse Recovery Charge |                                                        | 21   | 34  | nC |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

NOTES:

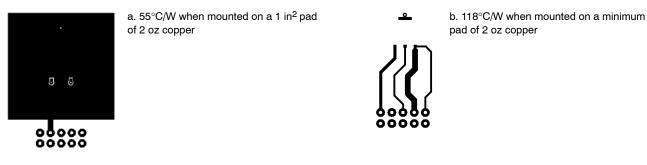

1. R<sub>0JA</sub> is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins.

$R_{\theta JC}$  is guaranteed by design while  $R_{\theta JA}$  is determined by the user's board design.

- Pulse Test: Pulse Width < 300 μs, Duty cycle < 2.0%.</li>

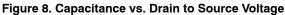

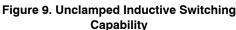

Starting T<sub>J</sub> = 25°C, L = 0.3 mH, I<sub>AS</sub> = 8 A, V<sub>DD</sub> = 90 V, V<sub>GS</sub> = 10 V.

The diode connected between the gate and source serves only as protection against ESD. No gate overvoltage rating is implied.

#### TYPICAL CHARACTERISTICS (T<sub>J</sub> = 25°C unless otherwise noted)

Voltage vs. Source Current

Figure 7. Gate Charge Characteristics

= 25°C

7

6

5

4

3

2

1

0.01

I<sub>AS</sub>, Avalanche Current (A)

0.1

T<sub>J</sub> = 125°C

Figure 10. Gate Leakage Current vs Gate to Source Voltage

35

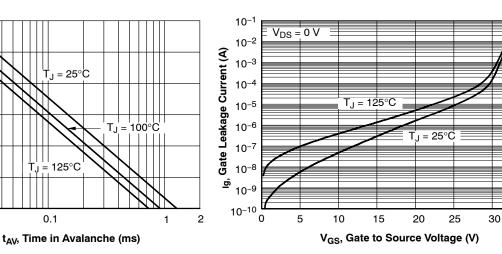

TYPICAL CHARACTERISTICS (T<sub>J</sub> = 25°C unless otherwise noted) (continued)

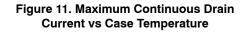

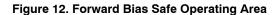

Figure 13. Single Pulse Maximum Power Dissipation

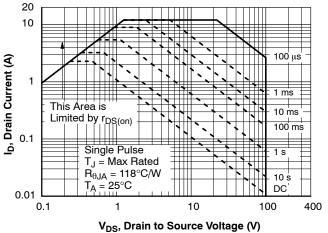

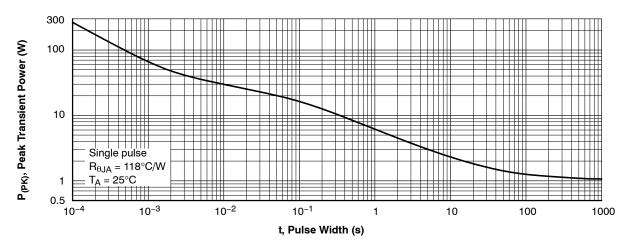

Figure 14. Junction-to-Ambient Transient Thermal Response Curve

#### **ORDERING INFORMATION**

| Device     | Device Marking | Package Type      | Shipping <sup>†</sup>    |

|------------|----------------|-------------------|--------------------------|

| FDT86113LZ | 113LZ          | SOT-223 (Pb-Free) | 4000 units / Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

POWERTRENCH is a registered trademark of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries.

SOT-223 CASE 318H ISSUE B DATE 13 MAY 2020 A NDTES SCALE 2:1 DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009. CONTROLLING DIMENSION: MILLIMETERS DIMENSIONS D & E1 ARE DETERMINED AT DATUM H. DIMENSIONS DO NOT INCLUDE MOLD FLASH, PROTRUSIONS DO NOT INCLUDE MOLD FLASH, PROTRUSIONS DO RGATE BURRS. SHALL NOT EXCEED 0.23mm PER SIDE. LEAD DIMENSIONS & AND b1 DO NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBBAR PROTRUSION IS 0.08mm PER SIDE. DATUMS A AND B ARE DETERMINED AT DATUM H. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT OF THE PACKAGE BODY. POSITIONAL TOLERANCE APPLIES TO DIMENSIONS & AND b1. DIMENSIONING AND TOLERANCING PER ASME 1. b1 2 з. В 4. 5. 6. 7. b AND b1. MILLIMETERS DIM MIN. NITM. MAX. e \_\_\_ \_\_\_ 1.80 k Α  $\oplus$  0.10  $\otimes$  C A B 0.02 0.06 0.11 A1 TOP VIEW NDTE 7 0.60 0.74 0.88 b 2.90 3.10 b1 3.00 DETAIL A 0.24 \_\_\_\_ 0.35 С H 6.70 D 6.30 6.50 Ε 6.70 7.00 7.30 E1 3.30 3.50 3.70 0.10 C 2.30 BSC e SIDE VIEW FND VIEW L 0.25 \_\_\_ i 10° 0° \_\_\_\_ -3.80 2.00 Α1 DETAIL A 8.30 3x= Assembly Location GENERIC A 2.00 **MARKING DIAGRAM\*** Y = Year = Work Week w XXXXX = Specific Device Code = Pb-Free Package 5'30 AYW 3x 1.50 (Note: Microdot may be in either location) XXXXX= PITCH \*This information is generic. Please refer to RECOMMENDED MOUNTING FOOTPRINT device data sheet for actual part marking. For additional information on our Pb-Free strategy Pb-Free indicator, "G" or microdot "•", may ж and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D. or may not be present. Some products may not follow the Generic Marking. Electronic versions are uncontrolled except when accessed directly from the Document Repository. **DOCUMENT NUMBER:** 98ASH70634A Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. **DESCRIPTION:** SOT-223 PAGE 1 OF 1

ON Semiconductor and use trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights nor the

**ON Semiconductor**<sup>®</sup>

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales