# Low Cost Variable OFF **Time Switched Mode Power Supply Controller**

The NCP1215A is a controller for low power off-line flyback Switched Mode Power Supplies (SMPS) featuring low size, weight and cost constraints together with a good low standby power performance. The operating principle uses switching frequency reduction at light load by increasing the OFF Time. Also, when OFF Time expands, the peak current is gradually reduced down to approximately 1/4 of the maximum peak current to prevent from exciting the transformer mechanical resonances. The risk of acoustic noise is thus greatly diminished while keeping good standby pov

A low power internal supply block also ensures very love current consumption at startup without hampering the stander of er performance.

A special primary current sensing technique mir vizes the im of SMPS switching on control IC operation. The pice of eak diss. i to be voltage across the current sense resistor 2' further reduced. The negative current nsing hnique offers advantages over a traditional approach by oiding t voltage drop incurred by traditional MOSFET sc sen. T' s, the IC drive capability is greatly improved.

Finally, the bulk input ripple en a na ral frequency Jithering which smooths the EMI sig

#### **Features**

- Variable OFF Time Cont. Me od

- Very Low Cv ent Cc ump on at Startup

- Natural Frequency Dith ing for Improved EMI Signature

- Current Mode peration

- Peak Current Compression Reduces Translorner Noise

- Programmable Current Sense Resistor Fight Voltage

- Undervoltage Lockout

- These are Pb-Free Devices

#### **Typical Applications**

- Auxiliary Power Supply

- Standby Power Supply

- AC-DC Adapter

- Off-line Battery Charger

### ON Semiconductor®

http://onsemi.com

TSOP-6 (SOT23-6, SC59-6) **SN SUFFIX CASE 318G**

= Specific Device Code = Assembly Location = Wafer Lot

= Year = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

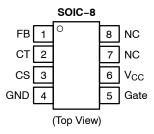

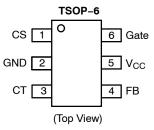

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.

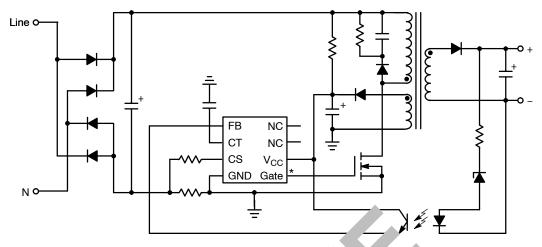

<sup>\*</sup>If your application requires a gate-source resistor, please refered & guider s in this document.

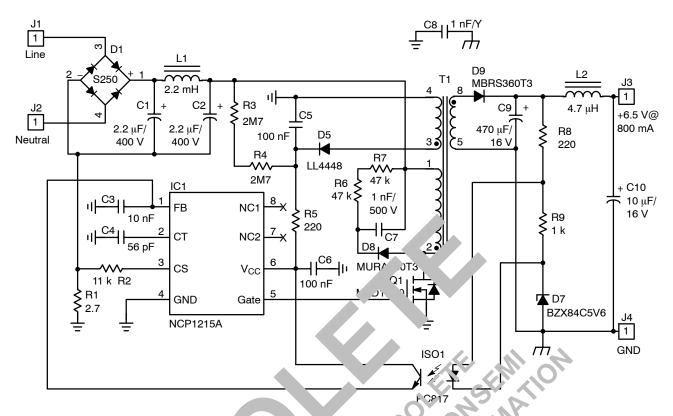

Figure 1. Typical A; iic. n

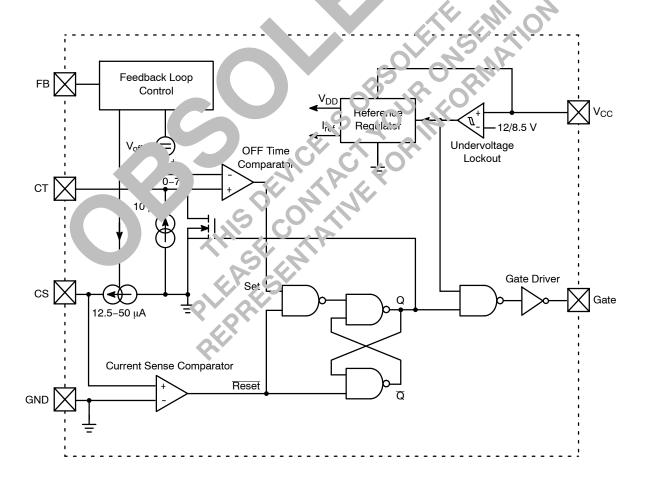

Figure 2. Representative Block Diagram

# **PIN FUNCTION DESCRIPTION**

| TSOP-6 | SO-8 | Symbol          | Description                                                                                                                                                                             |  |  |

|--------|------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4      | 1    | FB              | The FB pin provides voltage feedback loop. The current injected into the pin determines the primary switch OFF time interval. It also influences the peak value of the primary current. |  |  |

| 3      | 2    | CT              | Connection for an external timing programming capacitor.                                                                                                                                |  |  |

| 1      | 3    | CS              | The CS pin senses the power switch current.                                                                                                                                             |  |  |

| 2      | 4    | GND             | Primary and internal ground.                                                                                                                                                            |  |  |

| 6      | 5    | Gate            | Output drive for an external power MOSFET.                                                                                                                                              |  |  |

| 5      | 6    | V <sub>CC</sub> | Power supply voltage and Undervoltage Lockout.                                                                                                                                          |  |  |

| 7      | 7    | NC              | Unconnected pin.                                                                                                                                                                        |  |  |

| 8      | 8    | NC              | Unconnected pin.                                                                                                                                                                        |  |  |

#### **MAXIMUM RATINGS**

| Rating                                              |          | Symbol              | Value       | Unit |

|-----------------------------------------------------|----------|---------------------|-------------|------|

| Power Supply Voltage                                |          | V_c                 | 10          | V    |

| FB Pins Voltage Range                               |          | V:B                 | 1.3 to 18   | V    |

| CS and CT Pin Voltage Range                         |          | V <sub>in</sub>     | -u.3 to 10  | V    |

| Thermal Resistance, Junction-to-Air (SOIC-E ersion) | 02       | R <sub>θυΑ</sub>    | 178         | °C/W |

| Junction Temperature                                | 0        | ŤJ                  | 150         | °C   |

| Storage Temperature Range                           | (5) 10   | T.,                 | -60 to +150 | °C   |

| ESD Voltage Protection, Human Boo, uel (H           | 2014     | FSD-HBM             | 2.0         | kV   |

| ESD Voltage Protection, M line lodel (              | <u> </u> | V <sub>ESD-MM</sub> | 200         | V    |

Stresses exceeding Maxim. Brigs in y damage the doute. Maxim in Ratings are stress ratings only. Functional operation above the Recommended Operating Con. Ins is implied. Extende to exposite to stress above the Recommended Operating Conditions may affect device reliability.

# ORDERING INFORMATION

| Device        | (8, %) | Package             | Shipping <sup>†</sup> |

|---------------|--------|---------------------|-----------------------|

| NCP1215ADR2G  | O V OV | SOIC-8<br>(Pb-Free) | 2500 Units / Reel     |

| NCP1215ASNT1G | P.V    | TSOP-6<br>(Pb-Free) | 3000 Units / Reel     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 12 V, for typical values  $T_J$  = 25°C, for min/max values  $T_J$  = 0°C to +105°C, unless otherwise noted.)

| otherwise noted.)                                                                                                      |                       |      |      |      |      |

|------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|

| Characteristic                                                                                                         | Symbol                | Min  | Тур  | Max  | Unit |

| VOLTAGE FEEDBACK                                                                                                       |                       |      |      |      |      |

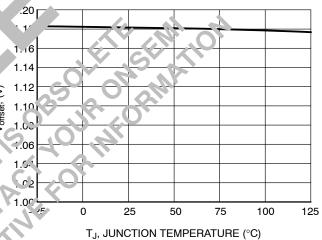

| Offset Voltage                                                                                                         | V <sub>offset</sub>   | 1.05 | 1.19 | 1.34 | V    |

| Maximum CT Pin Voltage at FB Current = 25 μA (Including V <sub>offset</sub> )                                          | V <sub>CT-25μ</sub> A | 2.4  | 3.1  | 4.3  | V    |

| Maximum CT Pin Voltage at FB Current = 50 μA (Including V <sub>offset</sub> )                                          | V <sub>CT-50μA</sub>  | 3.6  | 4.6  | 6.2  | V    |

| CT PIN - OFF TIME CONTROL                                                                                              |                       |      |      |      |      |

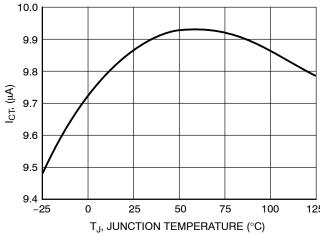

| Source Current (CT Pin Grounded)                                                                                       | I <sub>CT</sub>       | 8.0  | 9.8  | 11.5 | μА   |

| Source Current Maximum Voltage Capability                                                                              | V <sub>CT-max</sub>   | -    | 6.5  | -    | V    |

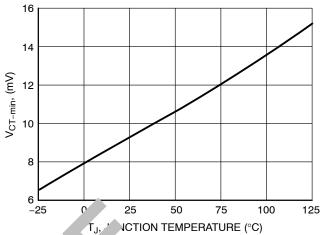

| Minimum CT Pin Voltage (Pin Unloaded, Discharge Switch Turned On)                                                      | V <sub>CT-mir</sub>   | -    | -    | 20   | mV   |

| CURRENT SENSE                                                                                                          |                       |      | •    |      |      |

| Minimum Source Current (I <sub>FB</sub> = 180 μA, CT Pin Grounded)                                                     | 3-m.                  | 8    | 12.5 | 16   | μΑ   |

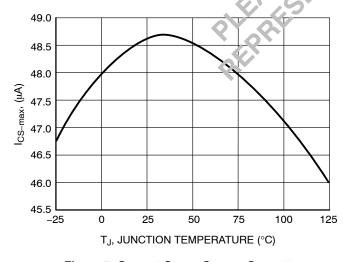

| Maximum Source Current (I <sub>FB</sub> = 0 μA, CT Pin Grounded)                                                       | ?S-max                | 40   | 49   | 58   | μΑ   |

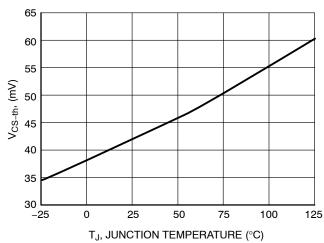

| Comparator Threshold Voltage                                                                                           |                       | 15   | 42   | 80   | mV   |

| Propagation Delay (CS Falling Edge to Gate Output)                                                                     | t <sub>dela</sub> ,   | -    | 215  | 310  | ns   |

| GATE DRIVE                                                                                                             |                       |      |      |      | •    |

| Sink Resistance (I <sub>sink</sub> = 30 mA)                                                                            | R <sub>OL</sub>       | 25   | 40   | 90   | Ω    |

| Source Resistance (I <sub>source</sub> = 30 mA)                                                                        | R <sub>OH</sub>       | 55   | 7.0  | 130  | Ω    |

| POWER SUPPLY                                                                                                           |                       | 7    | , D  |      |      |

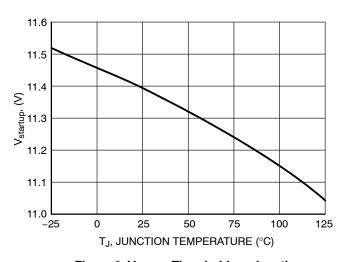

| V <sub>CC</sub> Startup Voltage                                                                                        | sturtup               | 0-7  | 12.5 | 14.2 | V    |

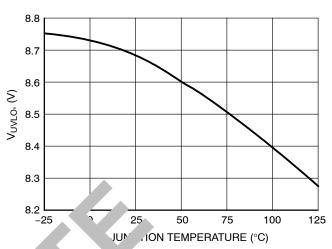

| Undervoltage Lockout Threshold Voltage                                                                                 | V <sub>UVLO</sub>     | .2   | 9.0  | -    | V    |

| Hysteresis (V <sub>startup</sub> – V <sub>UVLO</sub> )                                                                 | V <sub>h</sub> s      | 2.2  | 3.5  | -    | V    |

| V <sub>CC</sub> Startup Current Consumption ( V)                                                                       | ICC-strt              | _    | 2.8  | 6.5  | μΑ   |

| V <sub>CC</sub> Steady State Current C Sc. Stion (C <sub>GATE</sub> = 1.0 nF, f <sub>SW</sub> = J kH <sup>-</sup> Sen) | I <sub>O</sub> S=8 W  | 0.55 | 0.9  | 1.75 | mA   |

| V <sub>CC</sub> Startup Current Consumption ( V)  V <sub>CC</sub> Steady State Current C > > > > > > > > > > > > > > > |                       |      |      |      |      |

### **TYPICAL CHARACTERISTICS**

Figure 3. V<sub>startup</sub> Threshold vs. Junction Temperature

Figure 4. V<sub>UVLO</sub> Threshold vs. Junction Temperature

Figur 7. Oper ling Current Consumption vs.

Figure 6. Offset Voltage vs. Junction Temperature

Figure 7. Current Sense Source Current vs.

Junction Temperature

Figure 8. Current Sense Threshold vs. Junction Temperature

Figure 9. CT Pin Source Current vs. Junction **Temperature**

R<sub>source</sub>

$\mathsf{R}_{\mathsf{sink}}$

120

100

80

60

40

20

-25

$R_{source}$ - $R_{sink}$ ,  $(\Omega)$

100

istar ce 11. b. Si. and Source Pesistar ce vs. น าction Temperล\*นาษ

(°C)

T<sub>J</sub>, JUNC

10. C in Threshold vs. Junction **Temperature**

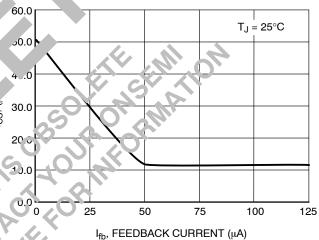

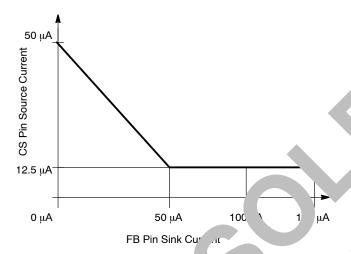

Figure 12. Current Sense Source Current vs. **Feedback Current**

#### APPLICATION INFORMATION

The NCP1215A implements a current mode SMPS with a variable OFF time dependant upon output power demand. It can be seen from the typical application that NCP1215A is designed to operate with a minimum number of external component. The NCP1215A incorporates the following features:

- Frequency Foldback: Since the switch-off time increases when power demand decreases, the switching frequency naturally diminishes in light load conditions. This helps to minimize switching losses and offers excellent standby power performance.

- Very Low Startup Current: The patented internal supply block is specially designed to offer a very low current consumption during startup. It allows the use of a very high value external startup resistor, greatly reducing dissipation, improving efficiency and minimizing standby power consumption.

- Natural Frequency Dithering: The quasi-fixed t<sub>on</sub>

mode of operation improves the EMI signature since

the switching frequency varies with the natural bulk

ripple voltage.

- Peak Current Compression: As the load by the search of the sudible range. To avoid exciting transform of the mechanical resonances, hence gending pustion noise, the NCP1215A includes patented technique, which reduces the peak current of the search of t

- Negative Primary Cu Sen Ig: By sensing the total current Sech. The Less not modify the MOSFET driving von (Ve) while switching.

Furthermore, the program ming resistor togather with the pin capacitant Sorms residual noise filter which blanks spurious spines. Also fixing primary current level to a maximum value sets the maximum now or limit

- Programmable Primary Current Sense: It offers a second peak current adjustment variable which improves the design flexibility.

- Secondary or Primary Regulation. The feedback loop arrangement allows simple secondary or primary side regulation without significant additional external components.

A detailed description of each internal block within the IC is given in the following text.

#### **Feedback Loop Control**

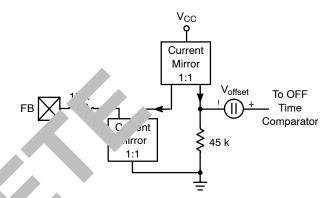

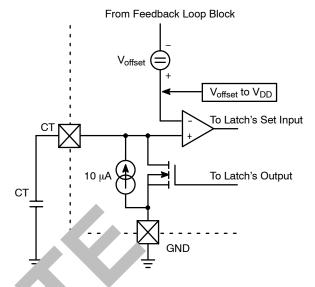

The main task of the Feedback Loop Block is to control the SMPS output voltage through the change of primary switch OFF time interval. It sets the peak voltage of the timing capacitor, which varies upon the output power demand. Figure 13 shows the simplified internal schematic:

Jure 13. Fee back Lcox - OFF Time Control

The voltage fer cloack signal is sensed as a current injected through the The pin.

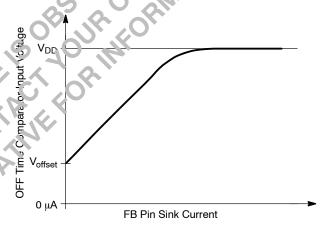

Figure 14. FB Loop Transfer Characteristic

The transfer characteristic (output voltage to input current) of the feedback loop control block can be seen in Figure 14.  $V_{DD}$  refers to the internal stabilized supply whereas the offset value sets the maximum switching frequency in lack of optocoupler current (e.g. an output short-circuit).

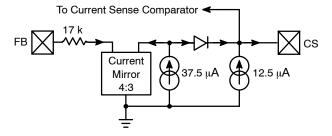

To keep the switching frequency above the audio range in light load condition the FB pin also regulates in certain range the peak primary current. The corresponding block diagram can be seen from Figure 15.

Figure 15. Feedback Loop - Current Sense Control

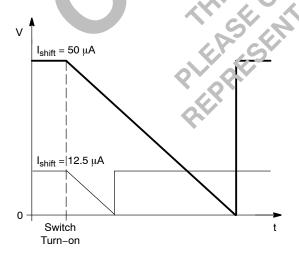

The resulting current sense regulation characteristic can be seen from Figure 16.

Figure 16. Current Sense Proguetton Chacteristic

When the load goes of the empression circuity decreases the peak current his to the effect of stigntly increasing the state. If the effect of stigntly increasing the state of the empression ratio is selected to not have enthe standby power.

# **OFF Time Contr**

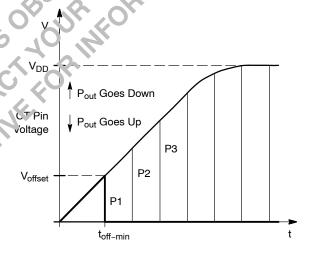

The loop signal together with the internal current source, via an external capacitor, controls the swite oracle time. This is portrayed in Figure 17.

Figure 17. OFF Time Control

uring the switch-ON time, the CT capacitor is kept tisches ed by a MOSFET switch. As soon as the latches the changes to class state the voltage across CT created by the internal current source, states to ramp-up until its value reaches the threshold given by the feedback loop demand

Figure 18. CT Pin Voltage ( $P_{out1} > P_{out2} > P_{out3}$ )

The voltage that can be observed on CT pin is shown in Figure 18. The **bold** waveform shows the maximum output power when the OFF time is at its minimum. The IC allows an OFF time of several seconds.

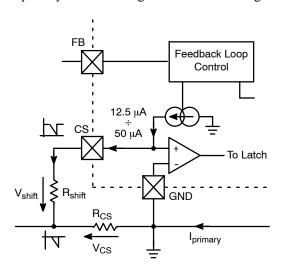

#### **Primary Current Sensing**

The primary current sensing circuit is shown in Figure 19.

Figure 19. Primary Current Sensing

When the primary switch is ON, the transformer current flows through the sense resistor  $R_{cs}$ . The current contest a voltage,  $V_{cs}$  which is negative with respect to GND. The the comparator connected to CS pin requires it voltage, the voltage  $V_{shift}$  is developed access the restor  $R_{shift}$  by a current source which level—shipped the negative voltage  $V_{cs}$ . The level—shift current is large  $r_{cs}$  and  $r_{cs}$  to 50  $\mu A$  depending on the Feedb at Lemma Control block signal (see more details in the research ack the pop Control section).

The peak primary cur it is the ruan to:

$$\frac{1}{RC} = \frac{1}{RC} \cdot \frac{1}{3}$$

(eq. 1)

A typical CS n voltage raveform is shown in Figure 20

Figure 20. CS Pin Voltage

Figure 20 also shows the effect of the inductor current of differing output power demand.

The primary current sensing method we described, brings the following benefits compared to the traditional approach:

- Maximum peak voltage across the current sense resistor is determined and can be optimized by the value of the shift resistor.

- CS pin is not exposed to negative voltage, which could induce a parasitic substrate current within the IC and distort the surrounding internal circuitry.

- The gate drive capability is improved because the current sense resistor is located out of the gate driver loop and does not deteriorate the turn-on and also turn-off gate drive amplitude.

#### **Gate Driver**

The Gate riv consists of a CMOS buffer designed to direct arive two AOSFET.

It is an unanced source and sink capabilities to optimize in ON and OFF performance without additional external continuous. Since the power MOSFET turns off at bind drain current, to minimize its turn-off losses the sink apability of the gate driver is increased for a faster turn-off opposite, the source continuity is lower to slow-down now wer MOSFET at turn-off product reduce the EMI noise.

Whenever the IC samply voltage is lower than the undervoltage threshold, the Cata Driver is low, pulling down the gate to ground. It eliminates the need for an external resistor.

#### Scartup Circuit

An external startup resistor is connected between high vertage potential of the input bulk capacitor and  $V_{CC}$  supply capacitor. The value of the resistor can be calculated as follows:

$$R_{\text{Startup}} = \frac{V_{\text{bulk}} - V_{\text{startup}}}{I_{\text{startup}}}$$

(eq. 2)

Where:

V<sub>startup</sub> V<sub>CC</sub> voltage at which IC starts operation

(see spec.)

I<sub>startup</sub> Startup current

V<sub>bulk</sub> Input bulk capacitor's voltage

Since the  $V_{bulk}$  voltage has obviously much higher value than  $V_{startup}$  the equation can be simplified in the following way:

$$R_{startup} = \frac{V_{bulk}}{I_{startup}}$$

(eq. 3)

The startup current can be calculated as follows:

$$I_{startup} = C_{Vcc} \frac{V_{startup}}{t_{startup}} + I_{CC-start}$$

(eq. 4)

Where:

C<sub>Vcc</sub> V<sub>CC</sub> capacitor value

t<sub>startup</sub> Startup time

I<sub>CC-start</sub> IC current consumption (see spec.)

If the IC current consumption is assumed constant during the startup phase, one can obtain resulting equation for startup resistor calculation:

$$R_{\text{startup}} = \frac{V_{\text{bulk}}}{C_{\text{Vcc}} \frac{V_{\text{startup}}}{t_{\text{startun}}} + I_{\text{CC-start}}}$$

(eq. 5)

# **Switching Frequency**

The switching frequency varies with the output load and input voltage. The highest frequency appears at highest input voltage and maximum output power.

Since the peak primary current is fixed, the on time portion of the switching period can be calculated:

$$t_{on} = L_p \frac{I_{pk}}{V_{bulk}}$$

(eq. 6)

Where:

L<sub>p</sub> Transformer primary inductance

I<sub>pk</sub> Peak primary current

Using equation for peak primary current estimation the switch—on time is:

$$t_{on} = L_p \frac{R_{shift}}{R_{cs} \cdot V_{bulk}} 50 \cdot 10^{-6}$$

(eq. 7)

Minimum switch-on time occurs at maximum . ut voltage:

$$t_{on-min} = L_p \frac{R_{shift}}{R_{cs} \cdot V_{bulk-max}} 5$$

10-6 ( $\epsilon$  8)

As it can be seen from the above quation the ...ch-on time linearly depends on the input with application to AC in voltage. Since this voltage has ripple to AC in voltage and input rectifier, it allows that the MF

The switch-off time is corminal by the charge of an external capacity connected to e CT pin. The minimum toff value can be computed by:

$$t_{\text{off-}\,\text{I}_{\text{II}}}$$

.  $\frac{v_{\text{offset}}}{v_{\text{CT}}} = c_{\text{T}} \frac{1.2}{10^{-5}}$  (eq. 9)

= 0.12 \cdot 10^6 CT

Where:

V<sub>offset</sub> Offset voltage (see spec.)

I<sub>CT</sub> CT pin source current (see spec.)

The maximum switching frequency than can be evaluated by:

$$\begin{split} f_{SW-\,max} &= \frac{1}{t_{on-\,min} + t_{off-\,min}} \\ &= \frac{1}{\frac{L_p \cdot R_{shift}}{V_{bulk} \cdot R_{cs}} \cdot 50 \cdot 10^{-6} + 0.12 \cdot 10^{6} \cdot C_T} \end{split}$$

(eq. 10)

As output power diminishes, the switching frequency decreases because the switch-off time prolongs upon feedback loop. The range of the frequency change is sufficient to keep output voltage regulation in any light load condition.

#### Application Design Example

An example of the typical wall adapter application is described hereafter.

As a wall adapter it should be able to operate properly with wide range of the input voltage from 90 VAC up to 265 VAC. The bulk capacitor voltage then can be calculated:

$$V_{bulk-min} = V_{AC-min}\sqrt{2} = 90 \cdot \sqrt{2} = 127 \text{ VDC}$$

(eq. 11)

$$V_{bulk-max} = V_{AC-max}\sqrt{2} = 265 \cdot \sqrt{2} = 375 \text{ VDC}$$

(eq. 12)

The requested output power is 5.2 Watts.

Assuming  $8^r$   $\sqrt{}$  efficiency the input power is equal to:

$$\Gamma_{i} = \frac{P_{out}}{P_{out}} = \frac{5.2}{0.8} = 6.5 \,\text{W}$$

(eq. 13)

The verage 1, of input current at minimum input verage

$$I_{in-vg} = \frac{P_{in}}{V_{bulk-min}} = \frac{6.5}{127} = 51.2 \text{ mA} \text{ (eq. 14)}$$

The itable reflected primary winding voltage for 600 V MOSFET switch is:

Vflbk

$$\sim 600 \text{ V} - \text{V}_{\text{bull}, -\text{n.ax}} - \text{V}_{\text{spike}}$$

=  $600 - 375 - 100 = 125 \text{ V}$  (eq. 15)

Using ca'culated flyback coltage the maximum duty cycle can be calcula ed:

$$\frac{V_{\text{flbk}}}{V_{\text{flbk}} + V_{\text{bulk-min}}}$$

$$= \frac{125}{125 + 127} = 0.496 = 0.5$$

(eq. 16)

Follo ing equation determines peak primary current:

$$I_{ppk} = \frac{2 \cdot I_{in-avg}}{\delta_{max}} = \frac{2 \cdot 51.2 \cdot 10^{-3}}{0.5}$$

(eq. 17)

= 204.7 mA

The desired maximum switching frequency at minimum input voltage is 75 kHz.

The highest switching frequency occurs at the highest input voltage and its value can be estimated as follows:

$$f_{max-high} = f_{max-low} \frac{V_{bulk-max}}{V_{bulk-min}} \delta_{max}$$

$$= 75 \cdot 10^3 \frac{375}{127} 0.5 = 110.7 \text{ kHz}$$

This frequency is much below 150 kHz, so that the desired operating frequency can be exploited for further calculation of the primary inductance:

$$L_{p} = \frac{V_{bulk-min} \cdot \delta_{max}}{I_{ppk} \cdot f_{sw-max}}$$

$$= \frac{127 \cdot 0.5}{0.2047 \cdot 75 \cdot 10^{3}} = 4.14 \text{ mH}$$

(eq. 19)

The EF16 core for transformer was selected. It has cross–section area  $A_e=20.1~\text{mm}^2$ . The N67 magnetic allows to use maximum operating flux density  $B_{max}=0.28~\text{Tesla}$ .

The number of turns of the primary winding is:

$$\begin{split} n_{p} &= \frac{L_{p} \cdot I_{ppk}}{B_{max} \cdot A_{e}} \\ &= \frac{4.14 \cdot 10^{-3} \cdot 0.2047}{0.28 \cdot 20.1 \cdot 10^{-6}} = 150 \text{ turns} \end{split}$$

(eq. 20)

The A<sub>L</sub> factor of the transformer's core can be calculated:

$$A_L = \frac{L_p}{(n_p)^2} = \frac{4.14 \cdot 10^{-3} \cdot}{(150)^2} = 184 \text{ nH} \quad \text{(eq. 21)}$$

For an adapter output voltage of 6.5 V, the number of turns of the secondary winding can be calculated accounting Schottky diode for output rectifier as follows:

$$\begin{split} n_S &= \frac{(V_S + V_{fwd})(1 - \delta_{max})n_p}{\delta_{max} \cdot V_{bulk-min}} \\ &= \frac{(6.5 + 0.7)(1 - 0.5)150}{0.5 \cdot 127} = 8.5 = 9 \text{ turns} \end{split}$$

The number of turns for auxiliary winding be calculated similarly:

$$\begin{split} n_{S} &= \frac{(V_{S} + V_{fwd})(1 - \delta_{max})n_{p}}{\delta_{max} \cdot V_{bulk-min}} \\ &= \frac{(12 + 1)(1 - 0.5)150}{0.5 \cdot 127} \quad 15.3^{\text{F}} \quad 15 \text{ turns} \end{split}$$

The peak primary currer is known from initial calculations. The current use who was choosing the voltage drop across the resistor. Let's use a value of 0.5 V. The value of the content sense resistor. Let's use a value of 0.5 V. The value of the content sense resistor. Can then be evaluated us to the value of 0.5 v.

n be evaluate as to.

$$vs$$

:

$$R_{CS} = \frac{V_C}{I_{pph}} = \frac{0.5}{0.20} = 2.442 \Omega = 1.7 \Omega \quad \text{(eq. 24)}$$

The voltage drop across the sense resistor needs to be recalculated:

$V_{CS} = R_{CS} \cdot I_{ppk} = 2.7 \cdot 0.2047 = 0.553 \,V$  (eq. 25)

Using the above results the value of the shift resistor is:

$$R_{\text{shift}} = \frac{V_{CS}}{I_{CS}} = \frac{0.553}{50 \cdot 10^{-6}} = 11.06 \text{ k}\Omega = 11 \text{ k}\Omega$$

(eq. 26)

The value of timing capacitor for the off time control has to be calculated for minimum bulk capacitor voltage since at these conditions the converter should be able to deliver specified maximum output power. The value of the timing capacitor is then given by the following equation:

$$C_{T} = \frac{\frac{1}{f_{e}} \frac{\frac{\text{LP \cdot lppk}}{V_{bi} \cdot \min}}{2.06}}{\frac{1}{75 \cdot 10^{5}} \frac{\frac{10 - 3 \cdot 0.2047}{127}}{127}} = 55.5 \text{ pF} = 56 \text{ pF}$$

The value  $\mathcal{L}$  the startup resistor for startup time of 200 ms  $\mathcal{L}$   $\mathcal{L}$  C capacitor of 200 nF is following:

R<sub>startup</sub> =

$$\frac{\frac{16 \text{ llk-n. i.}}{\text{OVcc} \frac{V_{\text{Si. i.}}}{r_{\text{str.tup}}} + \text{ICC-start MAX}}}{\frac{127}{200 \cdot 10^{-3}} \frac{\frac{127}{12} + 10 \cdot 10^{-6}}{\frac{12}{0.2} + 10 \cdot 10^{-6}}}$$

$$= 5.7 \text{ Vi}\Omega = 5.6 \text{ M}\Omega$$

(eq. 28)

The legal of an the calculations is the application schematic depicted in Figure 21.

Fi re 21. Application Schematic

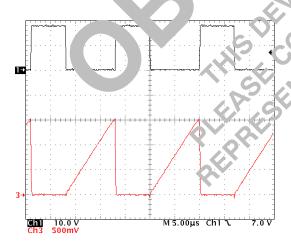

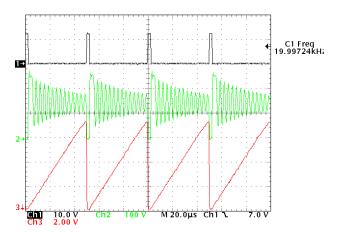

The following oscilloscope sr ots the operation of the working adap r. The Channel 3 in Figure 22 shows CT pin voltage and out it load. The Channel 1 is a gate driver of the channel 1 is a gate driver of the channel 1.

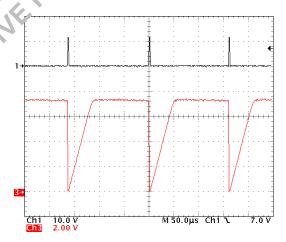

The CT voltage at no load condition is depicted in Figure 23.

Figure 22. CT Voltage at Full Load Condition

Figure 23. CT Voltage at No Load Condition

Figure 24 shows CT voltage and also by Channel 2 the switch's drain voltage at light load conditions.

Figure 24. CT and Drain at Light Load

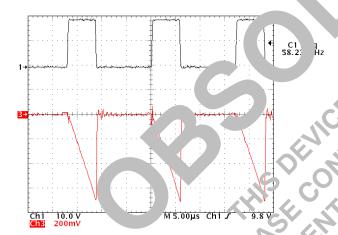

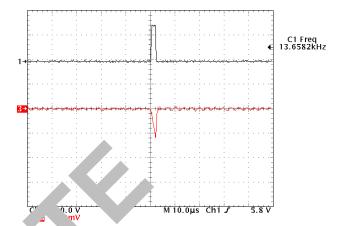

The waveform on the current sense pin at full load conditions can be observed from Channel 3 in Figure 25.

Figure 25. CS Pin at Full Load Condition

Figure 26 demonstrates the reduction of the peak primary current at light load conditions.

Fig 26. CS Pin at Light Load Condition

#### Rate Surce Resistor Design Guidelines

some applications, there is a new to wire a resistor between the MOSFET gair and source connections. This can preclude an evenual MCSTET destruction if, in the production stage, the converter is powered whilst the gate is left uses meeted. However, dealing with an extremely low sta tu) curren, implies a careful selection of the gate-source resistance. With the NCP1215A, the gate-source resistor must be calculated to allow the growth of the V<sub>CC</sub> capacitor to +.0 V in order to not interfere with the power-on socience. The following equation helps deriving Kgate-source, accounting for the minimum rectified input the startup volta, v and resistor: Vin<sub>min</sub>  $R_{\text{sate-source}}/(R_{\text{gate-source}} + R_{\text{startup}}) > 4.0 \text{ V}$ . If we take a Vin<sub>min</sub> of 100 VDC, a startup resistor of 4.0 M $\Omega$ , then  $R_{\text{gate-source}}$  equals 180 k $\Omega$  as a minimum normalized value.

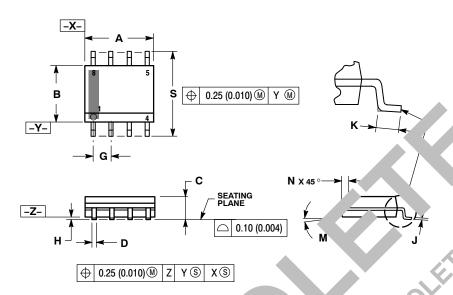

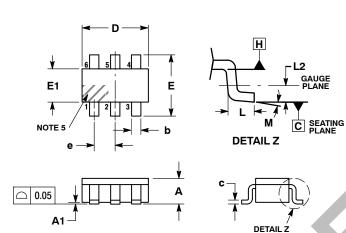

# **PACKAGE DIMENSIONS**

### SOIC-8 **D SUFFIX** CASE 751-07 **ISSUE AJ**

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.006) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. 751–01 THRU 751–06 ARE OBSOLETE. NEW STANDARD IS 751–07.

- STANDARD IS 751-07.

|   |     | MILLIN | IETERS   | INCHES |           |  |  |

|---|-----|--------|----------|--------|-----------|--|--|

|   | DIM | MIN    | MAX      | MIN    | MAX       |  |  |

|   | Α   | 4.80   | 5.00     | 0.189  | 0.197     |  |  |

|   | В   | 3.80   | 4.00     | 0.150  | 0.157     |  |  |

|   | С   | 1.35   | 1.75     | 0.053  | 0.069     |  |  |

|   | D   | 0.33   | 0.51     | 0.013  | 0.020     |  |  |

|   | G   | 1.27   | 1.27 BSC |        | 0.050 BSC |  |  |

|   | Н   | 0.10   | 0.25     | 0.004  | 0.010     |  |  |

|   | J   | 0.19   | 0.25     | 0.007  | 0.010     |  |  |

| J | K   | ( , 10 | 1.27     | 216    | 0.050     |  |  |

| 1 | M   | 10     | 8        | 0 °    | 8 °       |  |  |

|   | 1   | U.25   | 0.50     | 0.010  | 0.020     |  |  |

| Į | S   | 5.80   | 6.20     | 0.228  | 0.244     |  |  |

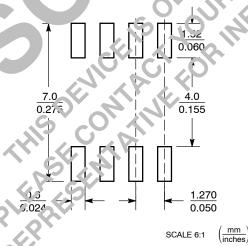

# RING FOOTPPOIT

\*For acdional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### PACKAGE DIMENSIONS

#### TSOP-6 CASE 318G-02 **ISSUE U**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- CONTROLLING DIMENSION: MILLIMETERS.

MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM

LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH,

- PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE, DIMENSIONS D AND E1 ARE DETERMINED AT DATUM H.

- 5. PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE.

|           | ILLIMETERS |       |      |  |

|-----------|------------|-------|------|--|

| DIM       |            | Mc    | MAX  |  |

| Α         | 90         | .00   | 1.10 |  |

| _A^       |            | 0.06  | 0.10 |  |

|           | 0.2        | 0.3°  | 0.50 |  |

| <b>G_</b> | 0.10       | 0     | 0.26 |  |

|           | 2.90       | 0ر _ا | 3.10 |  |

|           | 2.50       | 2.75  | 3.00 |  |

| E1        | 30         | 1.50  | 1.70 |  |

| е         | 5          | 0.95  | 1.05 |  |

| L         | 0.∠0       | 0.40  | 0.60 |  |

| L2        | 0.25 BSC   |       |      |  |

|           | 0°         |       | 10°  |  |

#### RECOMME \*RING FOOLPRINT\* SOL

DIMENSION'S MILLIMETERS

\*For addition Curformation on our Pb -Free strategy and soldering details, clease downloss the CN Semiconductor Soldering and Mounting rechniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 📖 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative