19-3644; Rev 2; 10/09

EVALUATION KIT

AVAILABLE

# 1.5V to 3.6V, 312.5ksps, 1-Channel True-Differential/ 2-Channel Single-Ended, 12-Bit, SAR ADCs

## **General Description**

The MAX1393/MAX1396 micropower, serial-output, 12bit, analog-to-digital converters (ADCs) operate with a single power supply from +1.5V to +3.6V. These ADCs feature automatic shutdown, fast wake-up, and a highspeed 3-wire interface. Power consumption is only 0.734 mW (V<sub>D</sub> = +1.5V) at the maximum conversion rate of 312.5ksps. AutoShutdown™ between conversions reduces power consumption at slower throughput rates.

The MAX1393/MAX1396 require an external reference VREF that has a wide range from 0.6V to VDD. The MAX1393 provides one true-differential analog input that accepts signals ranging from 0 to VREF (unipolar mode) or ±V<sub>RFF</sub>/2 (bipolar mode). The MAX1396 provides two single-ended inputs that accept signals ranging from 0 to VREF. Analog conversion results are available through a 5MHz 3-wire SPI™-/QSPI™-/ MICROWIRE<sup>™</sup>-/digital signal processor (DSP)-compatible serial interface. Excellent dynamic performance, low voltage, low power, ease of use, and small package sizes make these converters ideal for portable battery-powered data-acquisition applications, and for other applications that demand low power consumption and minimal space.

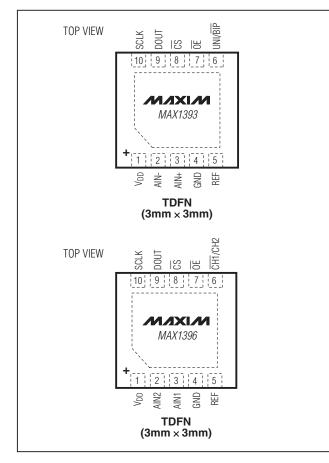

The MAX1393/MAX1396 are available in a space-saving (3mm x 3mm) 10-pin TDFN package. The parts operate over the extended (-40°C to +85°C) temperature range.

## **Applications**

Portable Datalogging Data Acquisition Medical Instruments **Battery-Powered Instruments Process Control**

## **Features**

- ♦ 312.5ksps, 12-Bit Successive-Approximation **Register (SAR) ADCs**

- ♦ Single True-Differential Analog Input Channel with Unipolar-/Bipolar-Select Input (MAX1393)

- Dual Single-Ended Input Channel with Channel-Select Input (MAX1396)

- ♦ ±1 LSB INL, ±1 LSB DNL, No Missing Codes

- ±2 LSB Total Unadjusted Error (TUE)

- 70dB SINAD at 75kHz Input Frequency

- External Reference (0.6V to VDD)

- Single-Supply Voltage (+1.5V to +3.6V)

- 0.915mW at 300ksps, 1.8V

- 0.305mW at 100ksps, 1.8V

- 3.1µW at 1ksps, 1.8V

- < 1µA Shutdown Current</p>

- AutoShutdown Between Conversions

- SPI-/QSPI-/MICROWIRE-/DSP-Compatible, 3- or 4-Wire Serial Interface

- Small (3mm x 3mm) 10-Pin TDFN Package

#### Typical Operating Circuit and Pin Configurations appear at end of data sheet.

AutoShutdown is a trademark of Maxim Integrated Products, Inc. SPI/QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

## **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE | ANALOG INPUTS | TOP MARK |

|-------------|----------------|-------------|---------------|----------|

| MAX1393ETB+ | -40°C to +85°C | 10 TDFN-EP* | 1-CH DIFF     | AOZ      |

| MAX1396ETB+ | -40°C to +85°C | 10 TDFN-EP* | 2-CH S/E      | APC      |

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

10-Pin TDFN (derate 18.5mW/°C above +70°C) ....1481.5mW

**Operating Temperature Ranges**

| MAX139_E                     | 40°C to +85°C  |

|------------------------------|----------------|

| Junction Temperature         | +150°C         |

|                              | 60°C to +150°C |

| Lead Temperature (soldering, | 10s)+300°C     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(VDD = +1.5V to +3.6V, VREF = VDD, CREF = 0.1 $\mu$ F, f<sub>SCLK</sub> = 5MHz, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                               | SYMBOL | CONDITIONS                                                        | MIN | ТҮР    | MAX | UNITS  |  |

|-----------------------------------------|--------|-------------------------------------------------------------------|-----|--------|-----|--------|--|

| DC ACCURACY (Note 1)                    |        |                                                                   | •   |        |     |        |  |

| Resolution                              |        |                                                                   | 12  |        |     | Bits   |  |

| Integral Nonlinearity                   | INL    |                                                                   |     |        | ±1  | LSB    |  |

| Differential Nonlinearity               | DNL    | No missing code overtemperature                                   |     |        | ±1  | LSB    |  |

| Offset Error                            |        |                                                                   |     | 0.5    | ±2  | LSB    |  |

| Gain Error                              |        | Offset nulled                                                     |     | 0.5    | ±2  | LSB    |  |

| Total Unadjusted Error                  | TUE    |                                                                   |     |        | ±2  | LSB    |  |

| Offset-Error Temperature<br>Coefficient |        |                                                                   |     | ±0.004 |     | LSB/°C |  |

| Gain-Error Temperature<br>Coefficient   |        |                                                                   |     | ±0.001 |     | LSB/°C |  |

| Channel-to-Channel Offset<br>Matching   |        | MAX1396 only                                                      |     | ±0.1   |     | LSB    |  |

| Channel-to-Channel Gain<br>Matching     |        | MAX1396 only                                                      |     | ±0.1   |     | LSB    |  |

| Input Common-Mode Rejection             | CMR    | $V_{CM} = 0$ to $V_{DD}$ , MAX1393 only                           |     | ±0.1   |     | mV/V   |  |

| DYNAMIC SPECIFICATIONS (No              | ote 2) |                                                                   |     |        |     |        |  |

|                                         |        | $V_{\text{REF}} = V_{\text{DD}} = 1.6$                            |     | 70     |     |        |  |

| Signal-to-Noise Plus Distortion         | SINAD  | V <sub>REF</sub> = V <sub>DD</sub> = 1.8–2.5                      | 69  |        |     | dB     |  |

|                                         |        | V <sub>REF</sub> = V <sub>DD</sub> = 2.5–3.6                      | 70  |        |     |        |  |

|                                         |        | $V_{\text{REF}} = V_{\text{DD}} = 1.6$                            |     | 70.5   |     |        |  |

| Signal-to-Noise Ratio                   | SNR    | V <sub>REF</sub> = V <sub>DD</sub> = 1.8–2.5                      | 70  | 71     |     | dB     |  |

|                                         |        | $V_{REF} = V_{DD} = 2.5 - 3.6$                                    | 71  |        |     |        |  |

| Total Harmonic Distortion               | THD    |                                                                   |     | -83    | -75 | dBc    |  |

| Spurious-Free Dynamic Range             | SFDR   |                                                                   |     | -85    | -76 | dBc    |  |

| Intermodulation Distortion              | IMD    | $f_{IN1} = 73$ kHz at -6.5dBFS,<br>$f_{IN2} = 77$ kHz at -6.5dBFS |     | -78    |     | dB     |  |

| Channel-to-Channel Crosstalk            |        | MAX1396 only                                                      |     | -70    |     | dB     |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>DD</sub> = +1.5V to +3.6V, V<sub>REF</sub> = V<sub>DD</sub>, C<sub>REF</sub> = 0.1 $\mu$ F, f<sub>SCLK</sub> = 5MHz, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                        | PARAMETER SYMBOL CONDITIONS |                                                                  | TIONS            | MIN                      | ТҮР                       | МАХ                       | UNITS |

|--------------------------------------------------|-----------------------------|------------------------------------------------------------------|------------------|--------------------------|---------------------------|---------------------------|-------|

| Full-Power Bandwidth                             |                             | -3dB point                                                       |                  |                          | 4                         |                           | MHz   |

| Full-Linear Bandwidth                            |                             | SINAD > 68dB MAX1393   MAX1396 MAX1396                           |                  |                          | 200                       |                           | kHz   |

|                                                  |                             |                                                                  |                  |                          | 150                       |                           | KI IZ |

| CONVERSION RATE                                  | 1                           | 1                                                                |                  |                          |                           |                           |       |

| Conversion Time                                  | tCONV                       | 13 clock cycles                                                  |                  | 2.6                      |                           |                           | μs    |

| Throughput Rate                                  |                             | 16 clock cycles per co<br>power-up, acquisition,                 |                  |                          |                           | 312.5                     | ksps  |

| Power-Up and Acquisition Time                    | tacq                        | Three SCLK cycles                                                |                  | 600                      |                           |                           | ns    |

| Aperture Delay                                   | t <sub>AD</sub>             |                                                                  |                  |                          | 8                         |                           | ns    |

| Aperture Jitter                                  | taj                         |                                                                  |                  |                          | 30                        |                           | ps    |

| Serial Clock Frequency                           | fclk                        |                                                                  |                  | 0.1                      |                           | 5.0                       | MHz   |

| ANALOG INPUTS (AIN+, AIN-, A                     | IN1, AIN2)                  |                                                                  |                  |                          |                           |                           |       |

| Input Voltago Passa                              | \/                          | Unipolar                                                         |                  | 0                        |                           | V <sub>REF</sub>          | V     |

| Input Voltage Range                              | V <sub>IN</sub>             | Bipolar, MAX1393 only                                            | /, (AIN+ - AIN-) | -V <sub>REF</sub> /2     |                           | +V <sub>REF</sub> /2      | V     |

| Common-Mode Input Voltage<br>Range               | VCM                         | Bipolar, MAX1393 only, [(AIN+) + (AIN-)] / 2                     |                  | 0                        |                           | V <sub>DD</sub>           | V     |

| Input Leakage Current                            |                             | Channel not selected, or conversion stopped, or in shutdown mode |                  |                          |                           | ±1                        | μA    |

| Input Capacitance                                |                             |                                                                  |                  |                          | 16                        |                           | рF    |

| REFERENCE INPUT (REF)                            |                             |                                                                  |                  |                          |                           |                           |       |

| REF Input Voltage Range                          | V <sub>REF</sub>            |                                                                  |                  | 0.6                      |                           | V <sub>DD</sub> +<br>0.05 | V     |

| REF Input Capacitance                            |                             |                                                                  |                  |                          | 24                        |                           | рF    |

| REF DC Leakage Current                           |                             |                                                                  |                  |                          | 0.025                     | ±2.5                      | μA    |

| REF Input Dynamic Current                        |                             | 312.5ksps                                                        |                  |                          | 20                        | 60                        | μA    |

| DIGITAL INPUTS (SCLK, CS, OE                     | , <del>CH</del> 1/CH2, U    |                                                                  |                  |                          |                           |                           |       |

| Input-Voltage Low                                | VIL                         |                                                                  |                  |                          |                           | 0.3 x<br>V <sub>DD</sub>  | V     |

| Input-Voltage High                               | VIH                         |                                                                  |                  | 0.7 x<br>V <sub>DD</sub> |                           |                           | V     |

| Input Hysteresis                                 |                             |                                                                  |                  |                          | 0.06 x<br>V <sub>DD</sub> |                           | V     |

| Input Leakage Current                            | IIL                         | Inputs at GND or V <sub>DD</sub>                                 |                  |                          |                           | ±1                        | μA    |

|                                                  |                             | CS, OE                                                           |                  |                          | 1                         |                           | -     |

| put Capacitance C <sub>IN</sub> CH1/CH2, UNI/BIP |                             |                                                                  | 12.5             |                          | pF                        |                           |       |

| DIGITAL OUTPUT (DOUT)                            |                             |                                                                  |                  |                          |                           |                           |       |

| Output-Voltage Low                               | V <sub>OL</sub>             | I <sub>SINK</sub> = 2mA                                          |                  |                          |                           | 0.1 x<br>V <sub>DD</sub>  | V     |

| Output-Voltage High                              | VOH                         | ISOURCE = 2mA                                                    |                  | 0.9 x                    |                           |                           | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>DD</sub> = +1.5V to +3.6V, V<sub>REF</sub> = V<sub>DD</sub>, C<sub>REF</sub> = 0.1 $\mu$ F, f<sub>SCLK</sub> = 5MHz, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                        | SYMBOL          | CONDITIONS                       |                        | MIN | ТҮР  | MAX   | UNITS |

|----------------------------------|-----------------|----------------------------------|------------------------|-----|------|-------|-------|

| Tri-State Leakage Current        | ILT             | $\overline{OE} = V_{DD}$         |                        |     |      | ±1    | μA    |

| Tri-State Output Capacitance     | Cout            | $\overline{OE} = V_{DD}$         |                        |     | 10   |       | рF    |

| POWER SUPPLY                     |                 |                                  |                        |     |      |       |       |

| Positive Supply Voltage          | V <sub>DD</sub> |                                  |                        | 1.5 |      | 3.6   | V     |

|                                  |                 | f <sub>SAMPLE</sub> = 100ksps    | $V_{DD} = 1.6V$        |     | 176  | 200   | μΑ    |

|                                  |                 |                                  | $V_{DD} = 3V$          |     | 225  | 260   |       |

|                                  |                 | fSAMPLE = 312.5ksps              | V <sub>DD</sub> = 1.6V |     | 520  | 600   |       |

| Positive Supply Current (Note 3) | IDD             |                                  | $V_{DD} = 3V$          |     | 710  | 800   |       |

|                                  |                 | Power-down mode (Note 4          | 1)                     |     | 5    | 10    |       |

|                                  |                 | Power-down mode (Note 5)         |                        |     | 0.2  | ±2.5  |       |

| Power-Supply Rejection           | PSR             | $V_{DD}$ = 1.5V to 3.6V, full-sc | ale input (Note 6)     |     | ±150 | ±1000 | μV/V  |

## TIMING CHARACTERISTICS

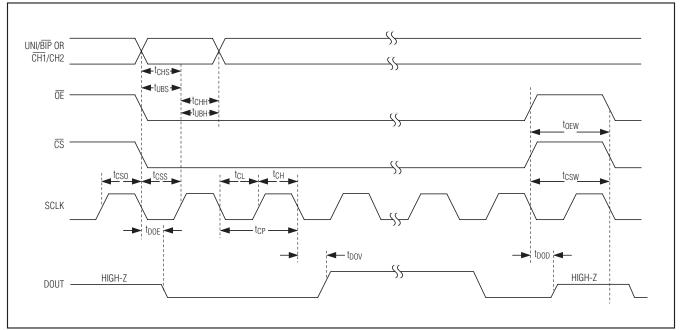

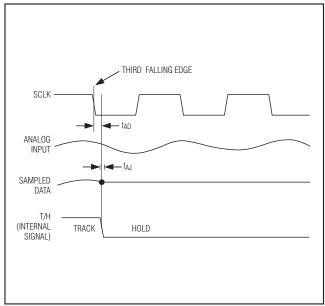

$(V_{DD} = +1.5V \text{ to } +3.6V, V_{REF} = V_{DD}, C_{REF} = 0.1 \mu\text{F}, f_{SCLK} = 5MHz, T_A = T_{MIN} \text{ to } T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C.}$ ) (Figure 1)

| PARAMETER                                | SYMBOL           | CONDITIONS             | MIN | ТҮР | MAX    | UNITS |

|------------------------------------------|------------------|------------------------|-----|-----|--------|-------|

| SCLK Clock Period                        | tCP              |                        | 200 |     | 10,000 | ns    |

| SCLK Pulse-Width High                    | tсн              |                        | 90  |     |        | ns    |

| SCLK Pulse-Width Low                     | tCL              |                        | 90  |     |        | ns    |

| CS Fall to SCLK Rise Setup               | tcss             |                        | 80  |     |        | ns    |

| SCLK Rise to $\overline{CS}$ Fall Ignore | tcso             |                        | 0   |     |        | ns    |

| SCLK Fall to DOUT Valid                  | t <sub>DOV</sub> | $C_{LOAD} = 0$ to 30pF | 10  |     | 80     | ns    |

| OE Rise to DOUT Disable                  | tdod             |                        |     | 6   | 20     | ns    |

| OE Fall to DOUT Enable                   | <b>t</b> DOE     |                        |     | 9   | 20     | ns    |

| CS Pulse-Width High or Low               | tcsw             |                        | 80  |     |        | ns    |

| OE Pulse-Width High or Low               | toew             |                        | 80  |     |        | ns    |

| CH1/CH2 Setup Time (to the First SCLK)   | tCHS             | MAX1396 only           | 10  |     |        | ns    |

| CH1/CH2 Hold Time (to the First SCLK)    | tСНН             | MAX1396 only           | 0   |     |        | ns    |

| UNI/BIP Setup Time (to the First SCLK)   | tubs             | MAX1393 only           | 10  |     |        | ns    |

| UNI/BIP Hold Time (to the First SCLK)    | tuвн             | MAX1393 only           | 0   |     |        | ns    |

Note 1:  $V_{DD} = 1.5V$ ,  $V_{REF} = 1.5V$ , and  $V_{AIN} = 1.5V$ .

Note 2:  $V_{DD}$  = 1.5V,  $V_{REF}$  = 1.5V,  $V_{AIN}$  = 1.5V<sub>P-P</sub>,  $f_{SCLK}$  = 5MHz,  $f_{SAMPLE}$  = 312.5ksps, and  $f_{IN}$  (sine wave) = 75kHz.

**Note 3:** All digital inputs swing between V<sub>DD</sub> and GND. V<sub>REF</sub> = V<sub>DD</sub>, f<sub>IN</sub> = 75kHz sine wave, V<sub>AIN</sub> = V<sub>REFP-P</sub>, C<sub>LOAD</sub> = 30pF on DOUT.

**Note 4:**  $\overline{CS} = V_{DD}$ ,  $\overline{OE} = UNI/\overline{BIP} = \overline{CH1}/CH2 = V_{DD}$  or GND, SCLK is active.

**Note 5:**  $\overline{CS} = V_{DD}$ ,  $\overline{OE} = UNI/\overline{BIP} = \overline{CH1}/CH2 = V_{DD}$  or GND, SCLK is inactive.

Note 6: Change in  $V_{AIN}$  at code boundary 4094.5.

Figure 1. Detailed Serial-Interface Timing Diagram

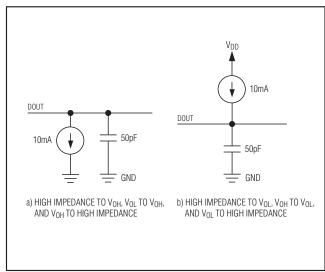

Figure 2. Load Circuits for Enable/Disable Times

M /X / M

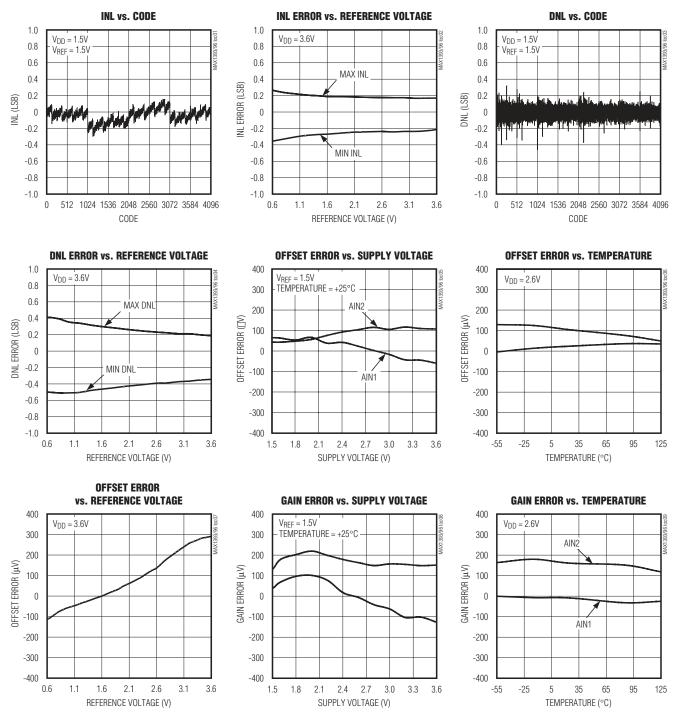

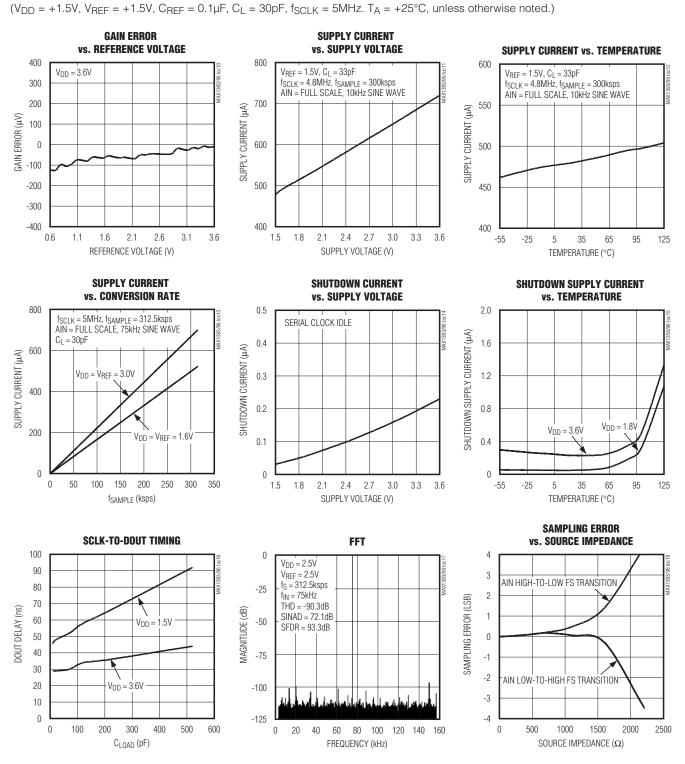

$(V_{DD} = +1.5V, V_{REF} = +1.5V, C_{REF} = 0.1\mu$ F, C<sub>L</sub> = 30pF, f<sub>SCLK</sub> = 5MHz. T<sub>A</sub> = +25°C, unless otherwise noted.)

6

**Typical Operating Characteristics (continued)**

7

## Pin Description

| PIN     |         |                 | FUNCTION                                                                                                                                                                                                                                                                              |  |  |  |  |

|---------|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MAX1393 | MAX1396 | NAME            | FUNCTION                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1       | 1       | V <sub>DD</sub> | Positive Supply Voltage. Connect $V_{DD}$ to a 1.5V to 3.6V power supply. Bypass $V_{DD}$ to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                           |  |  |  |  |

| 2       | _       | AIN-            | Negative Analog Input                                                                                                                                                                                                                                                                 |  |  |  |  |

| —       | 2       | AIN2            | Analog Input Channel 2                                                                                                                                                                                                                                                                |  |  |  |  |

| 3       | _       | AIN+            | Positive Analog Input                                                                                                                                                                                                                                                                 |  |  |  |  |

|         | 3       | AIN1            | Analog Input Channel 1                                                                                                                                                                                                                                                                |  |  |  |  |

| 4       | 4       | GND             | Ground                                                                                                                                                                                                                                                                                |  |  |  |  |

| 5       | 5       | REF             | External Reference Voltage Input. $V_{REF} = 0.6V$ to ( $V_{DD} + 0.05V$ ). Bypass REF to GND with a 0.1µF capacitor as close to the device as possible.                                                                                                                              |  |  |  |  |

| 6       | _       | UNI/BIP         | Input-Mode Select. Drive UNI/BIP high to select unipolar input mode. Pull UNI/BIP low to select bipolar input mode. In unipolar mode, the output data is in straight binary format. In bipolar mode, the output data is in two's complement format.                                   |  |  |  |  |

| _       | 6       | CH1/CH2         | Channel-Select Input. Pull $\overline{CH1}$ /CH2 low to select channel 1. Drive $\overline{CH1}$ /CH2 high to select channel 2.                                                                                                                                                       |  |  |  |  |

| 7       | 7       | ŌĒ              | Active-Low Output Enable. Pull $\overline{OE}$ low to enable DOUT. Drive $\overline{OE}$ high to disable DOUT. Connect to $\overline{CS}$ to interface with SPI, QSPI, and MICROWIRE devices or set low to interface with DSP devices.                                                |  |  |  |  |

| 8       | 8       | CS              | Active-Low Chip-Select Input. A falling edge on $\overline{\text{CS}}$ initiates power-up and acquisition.                                                                                                                                                                            |  |  |  |  |

| 9       | 9       | DOUT            | Serial-Data Output. DOUT changes state on the falling edge of SCLK. DOUT is high impedance when $\overline{\text{OE}}$ is high.                                                                                                                                                       |  |  |  |  |

| 10      | 10      | SCLK            | Serial-Clock Input. SCLK drives the conversion process and clocks data out. Acquisition ends on the 3rd falling edge after the $\overline{CS}$ falling edge. The LSB is clocked out on the SCLK 15th falling edge and the device enters AutoShutdown mode (see Figures 8, 9, and 10). |  |  |  |  |

| _       | _       | EP              | Exposed Pad. Not internally connected. Connect the exposed pad to GND or leave unconnected.                                                                                                                                                                                           |  |  |  |  |

## **Detailed Description**

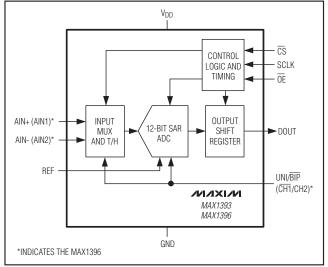

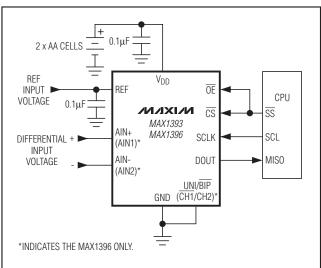

The MAX1393/MAX1396 use an input track and hold (T/H) circuit along with a SAR to convert an analog input signal to a serial 12-bit digital output data stream. The serial interface provides easy interfacing to microprocessors and DSPs. Figure 3 shows the simplified functional diagram for the MAX1393 (1 channel, true differential) and the MAX1396 (2 channels, single ended).

### True-Differential Analog Input T/H

The equivalent input circuit of Figure 4 shows the MAX1393/MAX1396 input architecture, which is composed of a T/H, a comparator, and a switched-capacitor DAC. The T/H enters its tracking mode on the falling edge of  $\overline{CS}$  (while  $\overline{OE}$  is held low). The positive input capacitor is connected to AIN+ (MAX1393), or to AIN1 or AIN2 (MAX1396). The negative input capacitor is connected to AIN- (MAX1393) or GND (MAX1396). The T/H enters its hold mode on the 3rd falling edge of SCLK

and the difference between the sampled positive and negative input voltages is converted. The time required for the T/H to acquire an input signal is determined by how quickly its input capacitance is charged. The required acquisition time lengthens as the input signal's source impedance increases. The acquisition time, tACQ, is the minimum time needed for the signal to be acquired. It is calculated by the following equation:

$$t_{ACQ} \ge 9 \times (R_{SOURCE} + R_{IN}) \times C_{IN} + t_{PU}$$

where:

RSOURCE is the source impedance of the input signal.

$R_{IN}$  = 500  $\Omega$  , which is the equivalent differential analog input resistance.

$C_{\text{IN}}$  = 16pF, which is the equivalent differential analog input capacitance.

tpu = 400ns.

Note:  $t_{ACQ}$  is never less than 600ns and any source impedance below  $400\Omega$  does not significantly affect the ADC's AC performance.

Figure 4. Equivalent Input Circuit

#### **Analog Input Bandwidth**

The ADC's input-tracking circuitry has a 4MHz fullpower bandwidth, making it possible to digitize highspeed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques.

Use anti-alias filtering to avoid high-frequency signals being aliased into the frequency band of interest.

#### **Analog Input Range and Protection**

The MAX1393/MAX1396 produce a digital output that corresponds to the analog input voltage as long as the analog inputs are within their specified range. When operating the MAX1393 in unipolar mode (UNI/BIP = 1), the specified differential analog input range is from 0 to VREF. When operating in bipolar mode (UNI/BIP = 0), the differential analog input range is from -V<sub>REF</sub>/2 to +V<sub>REF</sub>/2 with a common-mode range of 0 to V<sub>DD</sub>. The MAX1396 has an input range from 0 to V<sub>REF</sub>.

Internal protection diodes confine the analog input voltage within the region of the analog power input rails (V<sub>DD</sub>, GND) and allow the analog input voltage to swing from GND - 0.3V to V<sub>DD</sub> + 0.3V without damage. Input voltages beyond GND - 0.3V and V<sub>DD</sub> + 0.3V forward bias the internal protection diodes. In this situation, limit the forward diode current to less than 50mA to avoid damage to the MAX1393/MAX1396.

#### **Output Data Format**

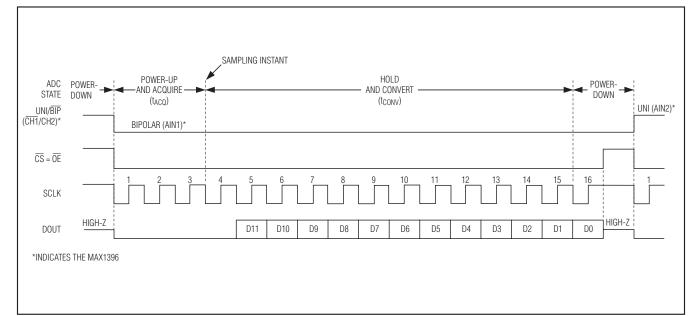

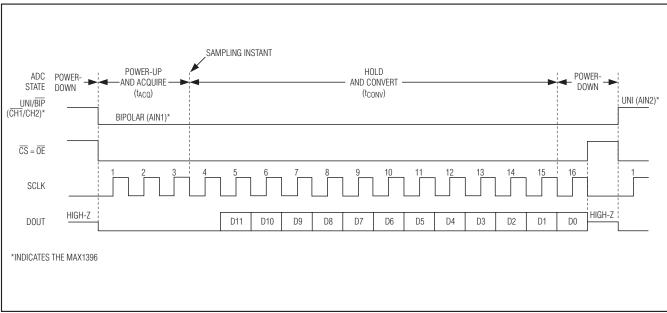

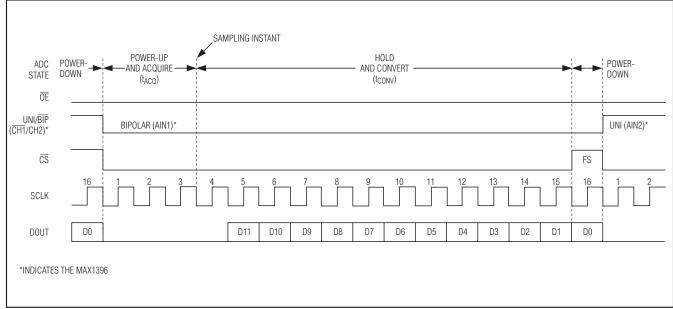

Figures 8, 9, and 10 illustrate the conversion timing for the MAX1393/MAX1396. Sixteen SCLK cycles are required to read the conversion result and data on DOUT transitions on the falling edge of SCLK. The conversion result contains 4 zeros, followed by 12 data bits with the data in MSB-first format. For the MAX1393, data is straight binary for unipolar mode and two's complement for bipolar mode. For the MAX1396, data is always straight binary.

#### **Transfer Function**

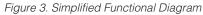

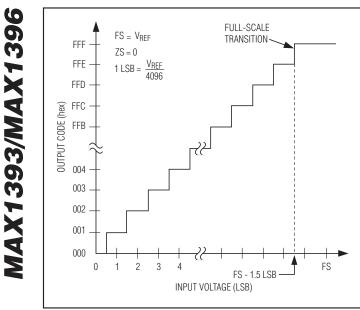

Figure 5 shows the unipolar transfer function for the MAX1393/MAX1396. Figure 6 shows the bipolar transfer function for the MAX1393. Code transitions occur halfway between successive-integer LSB values.

Figure 5. Unipolar Transfer Function

### **Applications Information**

#### Starting a Conversion

A falling edge on  $\overline{CS}$  initiates the power-up sequence and begins acquiring the analog input as long as  $\overline{OE}$  is also asserted low. On the 3rd SCLK falling edge, the analog input is held for conversion. The most significant bit (MSB) decision is made and clocked onto DOUT on the 4th SCLK falling edge. Valid DOUT data is available to be clocked into the master (microcontroller ( $\mu$ C)) on the following SCLK rising edge. The rest of the bits are decided and clocked out to DOUT on each successive SCLK falling edge. See Figures 8 and 9 for conversion timing diagrams.

Once a conversion has been initiated,  $\overline{\text{CS}}$  can go high at any time. Further falling edges of  $\overline{\text{CS}}$  do not reinitiate an acquisition cycle until the current conversion completes. Once a conversion completes, the first falling edge of  $\overline{\text{CS}}$ begins another acquisition/conversion cycle.

Figure 6. Bipolar Transfer Function

#### Selecting Unipolar or Bipolar Mode (MAX1393 Only)

Drive UNI/BIP high to select unipolar mode or pull UNI/BIP low to select bipolar mode. UNI/BIP can be connected to  $V_{DD}$  for logic high, to GND for logic low, or actively driven. UNI/BIP needs to be stable for tUBS prior to the first rising edge of SCLK after the CS falling edge (see Figure 1) for a valid conversion result when being actively driven.

### Selecting Analog Input AIN1 or AIN2 (MAX1396 Only)

Pull CH1/CH2 low to select AIN1 or drive CH1/CH2 high to select AIN2 for conversion. CH1/CH2 can be connected to V<sub>DD</sub> for logic high, to GND for logic low, or actively driven. CH1/CH2 needs to be stable for t<sub>CHS</sub> prior to the first rising edge of SCLK after the CS falling edge (see Figure 1) for a valid conversion result when being actively driven.

### AutoShutdown Mode

The ADC automatically powers down on the SCLK falling edge that clocks out the LSB. This is the falling edge after the 15th SCLK. DOUT goes low when the LSB has been clocked into the master ( $\mu$ C) on the 16th rising SCLK edge.

Alternatively, drive  $\overline{OE}$  high to force the MAX1393/ MAX1396 into power-down. Whenever  $\overline{OE}$  goes high, the ADC powers down and disables DOUT regardless of  $\overline{CS}$ , SCLK, or the state of the ADC. DOUT enters a high-impedance state after t<sub>DOD</sub>.

#### **External Reference**

The MAX1393/MAX1396 use an external reference between 0.6V and (V\_DD + 50mV). Bypass REF with a

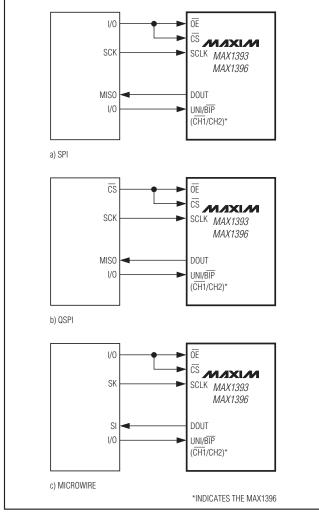

Figure 7. Common Serial-Interface Connections to the MAX1393/MAX1396

0.1µF capacitor to GND for best performance (see the *Typical Operating Circuit*).

#### **Serial Interface**

The MAX1393/MAX1396 serial interface is fully compatible with SPI, QSPI, and MICROWIRE (see Figure 7). If a serial interface is available, set the  $\mu$ C's serial interface in master mode so the  $\mu$ C generates the serial clock. Choose a clock frequency between 100kHz and 5MHz. CS and OE can be connected together and driven simultaneously. OE can also be connected to GND if the DOUT bus is not shared and driven independently.

#### SPI and MICROWIRE

When using SPI or MICROWIRE, make the  $\mu$ C the bus master and set CPOL = 0 and CPHA = 0 or CPOL = 1 and CPHA = 1. (These are the bits in the SPI or MICROWIRE control register.) Two consecutive 1-byte reads are required to get the entire 12-bit result from the ADC. DOUT transitions on SCLK's falling edge and is clocked into the  $\mu$ C on the SCLK's rising edge. See Figure 7 for connections and Figures 8 and 9 for timing diagrams. The conversion result contains 4 zeros, followed by the 12 data bits with the data in MSB-first format. When using CPOL = 0 and CPHA = 0 or CPOL = 1 and CPHA = 1, the MSB of the data is clocked into the  $\mu$ C on the SCLK's fifth rising edge. To be compatible with SPI and MICROWIRE, connect  $\overline{CS}$  and  $\overline{OE}$  together and drive simultaneously.

#### QSPI

Unlike SPI, which requires two 1-byte reads to acquire the 12 bits of data from the ADC, QSPI allows the minimum number of clock cycles necessary to clock in the data. However, the MAX1393/MAX1396 require 16 clock cycles from the  $\mu$ C to clock out the 12 bits of data. See Figure 7 for connections and Figures 8 and 9 for timing diagrams. The conversion result contains 4 zeros, followed by the 12 data bits with the data in MSB-first format. When using CPOL = 0 and CPHA = 0 or CPOL = 1 and CPHA = 1, the MSB of the data is clocked into the  $\mu$ C on the SCLK's fifth rising edge. To be compatible with QSPI, connect  $\overline{CS}$  and  $\overline{OE}$  together and drive simultaneously.

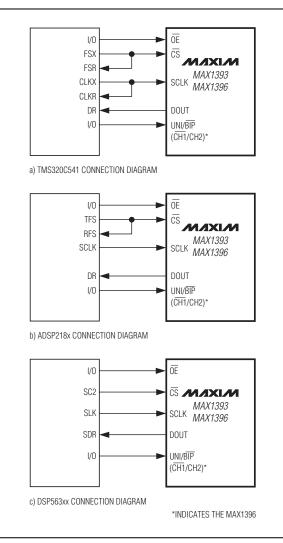

### **DSP** Interface

Figure 10 shows the timing for DSP operation. Figure 11 shows the connections between the MAX1393/ MAX1396 and several common DSPs.

Figure 8. Serial-Interface Timing for SPI/QSPI (CPOL = CPHA = 1) and MICROWIRE (G6 = 0, G5 = 1)

Figure 9. Serial-Interface Timing for SPI/QSPI (CPOL = CPHA = 0) and MICROWIRE (G6 = 0, G5 = 0)

Figure 10. DSP Serial-Timing Diagram

As shown in Figure 11, drive the MAX1393/MAX1396 chip-select input  $\overline{(CS)}$  with the DSP's frame-sync signal.  $\overline{OE}$  may be connected to GND or driven independently. For continuous conversion operation, keep  $\overline{OE}$  low and make the  $\overline{CS}$  falling edge coincident with the 16th falling edge of the SCLK.

#### Unregulated Two-Cell or Single Lithium LiMnO<sub>2</sub> Cell Operation

Low operating voltage (1.5V to 3.6V) and ultra-low-power consumption make the MAX1393/MAX1396 ideal for low cost, unregulated, battery-powered applications without the need for a DC-DC converter. Power the MAX1393/MAX1396 directly from two alkaline/NiMH/NiCd cells in series or a single lithium coin cell as shown in the *Typical Operating Circuit*.

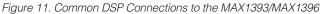

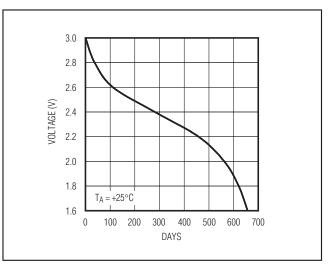

Fresh alkaline cells have a voltage of approximately 1.5V per cell (3V with 2 cells in series) and approach end of life at 0.8V (1.6V with 2 cells in series). A typical 2xAA alkaline discharge curve is shown in Figure 12a. A typical CR2032 lithium (LiMnO<sub>2</sub>) coin cell discharge curve is shown in Figure 12b.

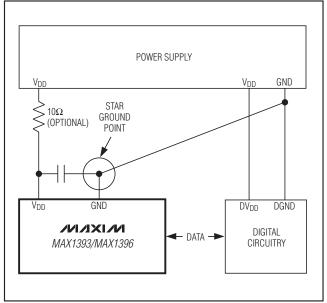

#### Layout, Grounding, and Bypassing

For best performance, use PC boards. Board layout must ensure that digital and analog signal lines are separated from each other. Do not run analog and digital (especially clock) lines parallel to one another, or digital lines underneath the ADC package. Figure 13 shows the recommended system ground connections. Establish a single-point analog ground (star ground point) at the MAX1393/MAX1396s' GND pin or use the ground plane.

High-frequency noise in the power supply (V<sub>DD</sub>) degrades the ADC's performance. Bypass V<sub>DD</sub> to GND with a 0.1µF capacitor as close to the device as possible. Minimize capacitor lead lengths for best supply noise rejection. To reduce the effects of supply noise, a 10 $\Omega$  resistor can be connected as a lowpass filter to attenuate supply noise.

#### Exposed Pad

The MAX1393/MAX1396 TDFN package has an exposed pad on the bottom of the package. This pad is not internally connected. Connect the exposed pad to the GND pin on the MAX1393/MAX1396 or leave unconnected for proper electrical performance.

### Definitions

#### Integral Nonlinearity (INL)

INL is the deviation of the values on an actual transfer function from a straight line. For the MAX1393/ MAX1396, this straight line is between the end points of the transfer function once offset and gain errors have been nullified. INL deviations are measured at every step and the worst-case deviation is reported in the *Electrical Characteristics* section.

#### **Differential Nonlinearity (DNL)**

DNL is the difference between an actual step width and the ideal value of 1 LSB. A DNL error specification of less than  $\pm$ 1 LSB guarantees no missing codes and a monotonic transfer function. For the MAX1393/ MAX1396, DNL deviations are measured at every step and the worst-case deviation is reported in the *Electrical Characteristics* section.

Figure 12a. Typical 2xAA Discharge Curve at 100ksps

Figure 12b. Typical CR2032 Discharge Curve at 100ksps

### Signal-to-Noise Plus Distortion (SINAD)

SINAD is computed by taking the ratio of the RMS signal to the RMS noise plus the RMS distortion. RMS noise includes all spectral components to the Nyquist frequency excluding the fundamental, the first five harmonics (HD2–HD6), and the DC offset. RMS distortion includes the first five harmonics (HD2–HD6):

$$SINAD = 20 \times \log \left( \frac{SIGNAL_{RMS}}{\sqrt{NOISE_{RMS}^2 + DISTORTION_{RMS}^2}} \right)$$

Figure 13. Power-Supply Grounding Connections

### Signal-to-Noise Ratio (SNR)

SNR is a dynamic figure of merit that indicates the converter's noise performance. For a waveform perfectly reconstructed from digital samples, the theoretical maximum SNR is the ratio of the full-scale analog input (RMS value) to the RMS quantization error (residual error). The ideal, theoretical minimum analog-to-digital noise is caused by quantization error only and results directly from the ADC's resolution (N bits):

$SNR_{dB[max]} = 6.02_{dB} \times N + 1.76_{dB}$

In reality, there are other noise sources such as thermal noise, reference noise, and clock jitter that also degrade SNR. SNR is computed by taking the ratio of the RMS signal to the RMS noise. RMS noise includes all spectral components to the Nyquist frequency excluding the fundamental, the first five harmonics, and the DC offset.

### **Total Harmonic Distortion (THD)**

THD is a dynamic figure of merit that indicates how much harmonic distortion the converter adds to the signal.

THD is the ratio of the RMS sum of the first five harmonics of the fundamental signal to the fundamental itself. This is expressed as:

THD = 20 × log

$$\left(\frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}\right)$$

where  $V_1$  is the fundamental amplitude, and  $V_2$  through  $V_6$  are the amplitudes of the 2nd- through 6th-order harmonics.

Spurious-Free Dynamic Range (SFDR)

SFDR is a dynamic figure of merit that indicates the lowest usable input signal amplitude. SFDR is the ratio of the RMS amplitude of the fundamental (maximum signal component) to the RMS value of the next-largest spurious component, excluding DC offset. SFDR is specified in decibels relative to the carrier (dBc).

### Intermodulation Distortion (IMD)

IMD is the ratio of the RMS sum of the intermodulation products to the RMS sum of the two fundamental input tones. This is expressed as:

IMD = 20 × log

$$\left(\frac{\sqrt{V_{IM1}^2 + V_{IM2}^2 + \dots + V_{IM3}^2 + V_{IMN}^2}}{\sqrt{V_1^2 + V_2^2}}\right)$$

The fundamental input tone amplitudes (V<sub>1</sub> and V<sub>2</sub>) are at -6.5dBFS. Fourteen intermodulation products (V<sub>IM</sub>) are used in the MAX1393/MAX1396 IMD calculation. The intermodulation products are the amplitudes of the output spectrum at the following frequencies, where f<sub>IN1</sub> and f<sub>IN2</sub> are the fundamental input tone frequencies:

- 2nd-order intermodulation products:  $f_{IN1} + f_{IN2}$ ,  $f_{IN2} f_{IN1}$

- 3rd-order intermodulation products: 2 x f<sub>IN1</sub> - f<sub>IN2</sub>, 2 x f<sub>IN2</sub> - f<sub>IN1</sub>, 2 x f<sub>IN1</sub> + f<sub>IN2</sub>, 2 x f<sub>IN2</sub> + f<sub>IN1</sub>

- 4th-order intermodulation products: 3 x f<sub>IN1</sub> - f<sub>IN2</sub>, 3 x f<sub>IN2</sub> - f<sub>IN1</sub>, 3 x f<sub>IN1</sub> + f<sub>IN2</sub>, 3 x f<sub>IN2</sub> + f<sub>IN1</sub>

- 5th-order intermodulation products: 3 x f<sub>IN1</sub> - 2 x f<sub>IN2</sub>, 3 x f<sub>IN2</sub> - 2 x f<sub>IN1</sub>, 3 x f<sub>IN1</sub> + 2 x f<sub>IN2</sub>, 3 x f<sub>IN2</sub> + 2 x f<sub>IN1</sub>

### **Channel-to-Channel Crosstalk**

Channel-to-channel crosstalk indicates how well each analog input is isolated from the others. The channel-tochannel crosstalk for the MAX1396 is measured by applying DC to channel 2 while an AC sine wave is applied to channel 1. An FFT is taken for channel 1 and channel 2 and the difference (in dB) is reported as the channel-to-channel crosstalk.

### **Aperture Delay**

The MAX1393/MAX1396 sample data on the falling edge of its third SCLK cycle (Figure 14). In actuality, there is a small delay between the falling edge of the sampling clock and the actual sampling instant. Aperture delay ( $t_{AD}$ ) is the time defined between the falling edge of the sampling clock and the instant when an actual sample is taken.

#### **Aperture Jitter**

Aperture jitter  $(t_{AJ})$  is the sample-to-sample variation in the aperture delay (Figure 14).

### **DC** Power-Supply Rejection Ratio (PSRR)

DC PSRR is defined as the change in the positive fullscale transfer function point caused by a full range variation in the analog power-supply voltage ( $V_{DD}$ ).

### Chip Information

TRANSISTOR COUNT: 9106 PROCESS: BICMOS

Figure 14. T/H Aperture Timing

### **Typical Operating Circuit**

## Pin Configurations

## Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 10 TDFN-EP   | T1033-1      | <u>21-0137</u> |

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                       | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------------------|------------------|

| 0                  | 5/05             | Initial release.                                                  | —                |

| 1                  | 11/05            | Removed the $\mu$ MAX package from the data sheet.                | 1, 2, 17         |

| 2                  | 10/09            | Removed the military grade package from the Ordering Information. | 1, 2             |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600