SNVS560E - MARCH 2008-REVISED OCTOBER 2017

LM2854

# LM2854 4-A 500-kHz / 1-MHz Synchronous Buck Regulator

## **Features**

- Input Voltage Range of 2.95 V to 5.5 V

- Maximum Load Current of 4 A

- Wide Bandwidth Voltage Mode Control Loop. Partial Internal Compensation

- Fixed Switching Frequency of 500 kHz or 1 MHz

- 35-mΩ Integrated MOSFET Switches

- Adjustable Output Voltage Down to 0.8 V

- Optimized Reference Voltage Initial Accuracy and Temperature Drift

- External Soft-Start Control With Tracking Capability

- **Enable Pin With Hysteresis**

- Low Standby Current of 230 µA

- Pre-Biased Load Start-up Capability

- Integrated UVLO, OCP, and Thermal Shutdown

- 100% Duty Cycle Capability

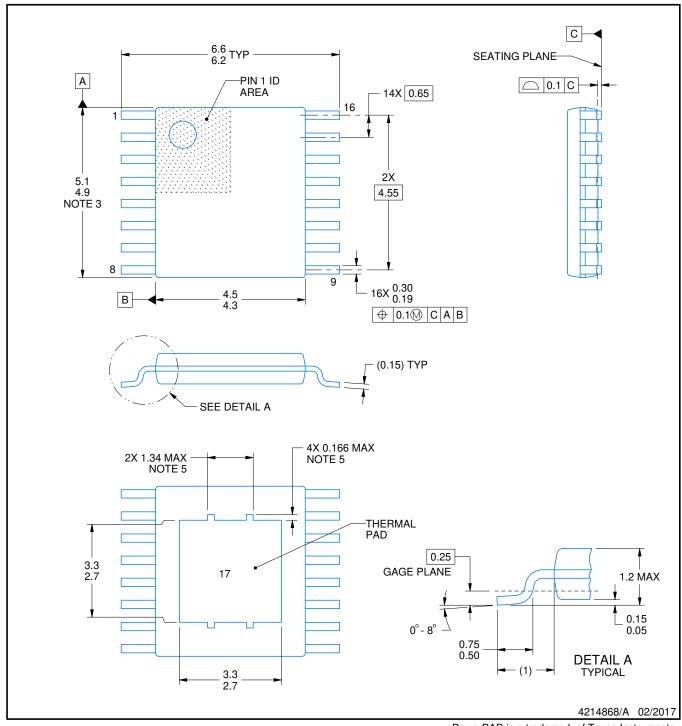

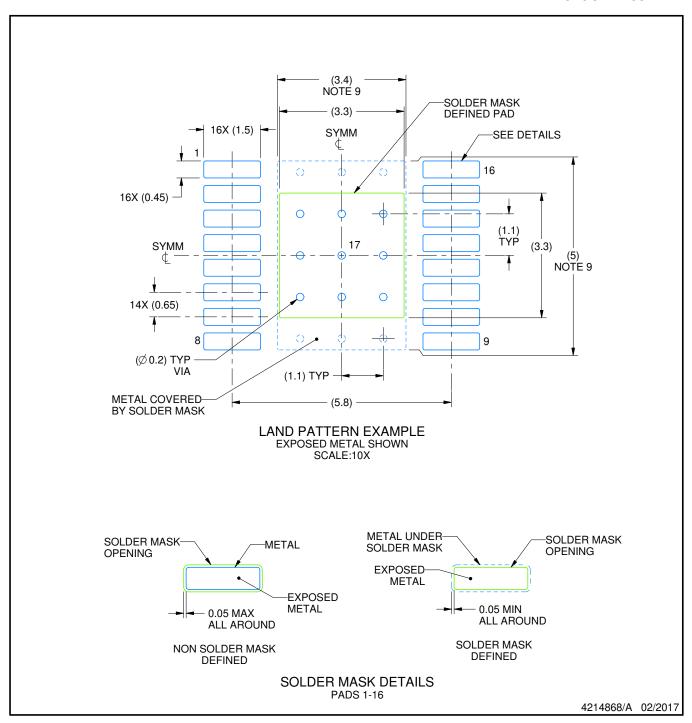

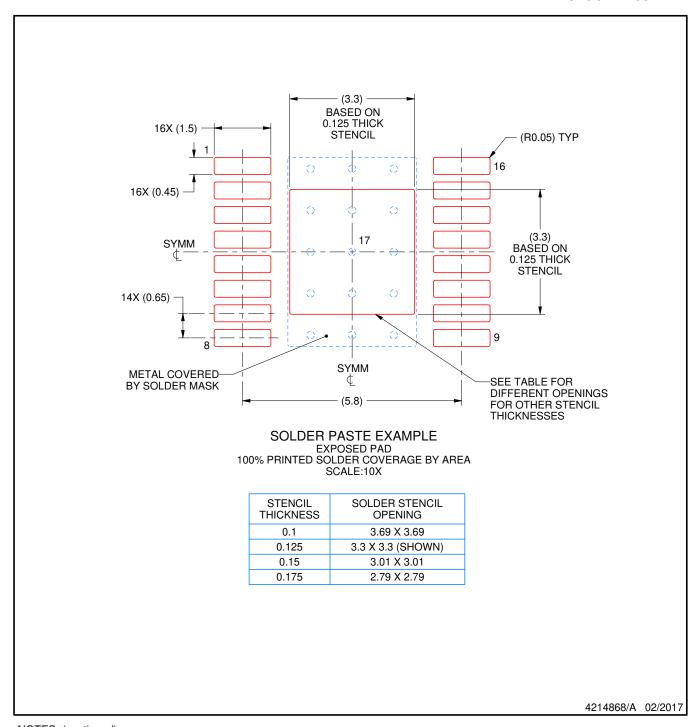

- HTSSOP-16 Exposed Pad Package

## **Applications**

- Low Voltage POL Regulation from 5-V or 3.3-V

- Local Solution for FPGA/DSP/ASIC/µP Core or I/O Power

- **Broadband Networking and Communications** Infrastructure

- Portable Computing

## 3 Description

The LM2854 PowerWise™ buck regulator is a 500kHz or 1-MHz step-down switching voltage regulator capable of driving up to a 4-A load with exceptional power conversion efficiency, line and load regulation, and output accuracy. The LM2854 can accept an input voltage rail between 2.95 V and 5.5 V, and deliver an adjustable and highly accurate output voltage as low as 0.8 V. Externally established softstart with a small capacitor facilitates controlled startup, and the LM2854 is capable of starting gracefully into a pre-biased output voltage. Partial internal compensation reduces the number of external passive components and PC board space typically necessary in a voltage mode buck converter application, yet preserving flexibility to deal with ceramic and/or electrolytic based load capacitors. Lossless cycle-by-cycle peak current limit is used to protect the load from an overcurrent or short-circuit fault. and enable comparator an sequencing applications. The LM2854 is available in an exposed pad HTSSOP-16 package that enhances the thermal performance of the regulator.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |  |  |

|-------------|-------------|-------------------|--|--|

| LM2854      | HTSSOP (16) | 4.40 mm × 5.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

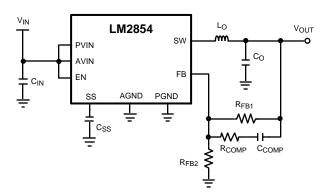

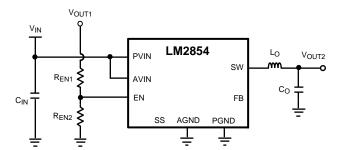

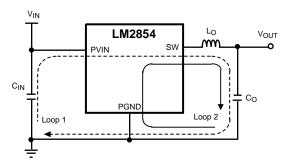

#### Typical Application Circuit

| 1 | Гa | h | عا | Ωf | Co           | nte | nte |

|---|----|---|----|----|--------------|-----|-----|

|   |    | _ |    | v  | $\mathbf{u}$ |     |     |

| 1 | Features 1                           |    | 7.3 Feature Description                          | 9               |

|---|--------------------------------------|----|--------------------------------------------------|-----------------|

| 2 | Applications 1                       |    | 7.4 Device Functional Modes                      | 11              |

| 3 | Description 1                        | 8  | Application and Implementation                   | 12              |

| 4 | Revision History2                    |    | 8.1 Application Information                      | 12              |

| 5 | Pin Configuration and Functions      |    | 8.2 Typical Application                          | 12              |

| 6 | Specifications4                      | 9  | Power Supply Recommendations                     |                 |

| U | 6.1 Absolute Maximum Ratings         | 10 | Layout                                           | 25              |

|   | 6.2 ESD Ratings                      |    | 10.1 Layout Guidelines                           |                 |

|   | 6.3 Recommended Operating Conditions |    | 10.2 Layout Example                              |                 |

|   | 6.4 Thermal Information              | 11 | Device and Documentation Support                 | 27              |

|   | 6.5 Electrical Characteristics 5     |    | 11.1 Documentation Support                       |                 |

|   | 6.6 Typical Characteristics          |    | 11.2 Trademarks                                  | <mark>27</mark> |

| 7 | Detailed Description9                |    | 11.3 Electrostatic Discharge Caution             | <mark>27</mark> |

| • | 7.1 Overview                         |    | 11.4 Glossary                                    |                 |

|   | 7.2 Functional Block Diagram         | 12 | Mechanical, Packaging, and Orderable Information |                 |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С        | Changes from Revision C (April 2013) to Revision D                                                                                                                                                                                                                                 | Page |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •        | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, a Mechanical, Packaging, and Orderable Information section. | nd   |

| •        | Removed Soldering and Infrared values from Absolute Maximum Ratings.                                                                                                                                                                                                               | 4    |

| •        | Added thermal information generated using TI standard methodology.                                                                                                                                                                                                                 | 4    |

| С        | Changes from Revision B (April 2013) to Revision C                                                                                                                                                                                                                                 | Page |

| <u>.</u> | Changed layout of National Data Sheet to TI format                                                                                                                                                                                                                                 | 24   |

| С        | Changes from Revision D (January 2016) to Revision E                                                                                                                                                                                                                               | Page |

|          | Deleted Simple Switcher from Description section, and Detailed Description section                                                                                                                                                                                                 | -    |

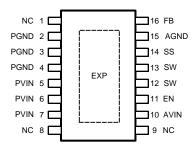

# 5 Pin Configuration and Functions

PWP Package 16-Pin HTSSOP Top View

## **Pin Functions**

| PIN                                                                                                                                                                                             |         | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                                                                                                                                                            | NO.     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| NC                                                                                                                                                                                              | 1, 8, 9 | _   | Reserved for factory use, this pin should be connected to GND to ensure proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PGND                                                                                                                                                                                            | 2, 3, 4 | _   | Power ground pins for the internal power switches. These pins should be connected together locally at the device and tied to the PC board ground plane.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| PVIN                                                                                                                                                                                            | 5, 6, 7 | _   | Input voltage to the power switches inside the device. These pins should be connected together at the device. A low ESR input capacitance should be located as close as possible to these pins.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Analog input voltage supply that get input from this pin also. Thus, if the internal FETs are turned off. TI record RC filter to minimize the influence of The series resistor should be 1 Ω at |         | _   | Analog input voltage supply that generates the internal bias. The UVLO circuit derives its input from this pin also. Thus, if the voltage on AVIN falls below the UVLO threshold, both internal FETs are turned off. TI recommends connecting PVIN to AVIN through a low pass RC filter to minimize the influence of input rail ripple and noise on the analog control circuitry. The series resistor should be 1 $\Omega$ and the bypass capacitor should be a X7R ceramic type 0.1 $\mu\text{F}$ to 1 $\mu\text{F}$ . |  |  |  |

| EN                                                                                                                                                                                              | 11      | 1   | Active high enable input for the device. Typically, turnon threshold is 1.23 V with 0.15-V hysteresis. An external resistor divider from PVIN can be used to effectively increase the UVLO turnon threshold. If not used, the EN pin should be connected to PVIN.                                                                                                                                                                                                                                                       |  |  |  |

| sw                                                                                                                                                                                              | 12, 13  | 0   | Switch node pins. This is the PWM output of the internal MOSFET power switches. These pins should be tied together locally and connected to the filter inductor.                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SS 14                                                                                                                                                                                           |         | I/O | Soft-start control pin. An internal 2-µA current source charges an external capacitor connected between this pin and AGND to set the output voltage ramp rate during start-up. This pin can also be used to configure the tracking feature.                                                                                                                                                                                                                                                                             |  |  |  |

| AGND                                                                                                                                                                                            | 15      | _   | Quiet analog ground for the internal bias circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| FB                                                                                                                                                                                              | 16 I    |     | Feedback pin is connected to the inverting input of the voltage loop error amplifier. An 0.8-V bandgap reference is connected to the noninverting input of the error amplifier.                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Exposed Pad                                                                                                                                                                                     |         | _   | Exposed metal pad on the underside of the package with a weak electrical connection to PGND. TI recommends connecting this pad to the PC board ground plane in order to improve thermal dissipation.                                                                                                                                                                                                                                                                                                                    |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                  | MIN  | MAX                | UNIT |

|--------------------------------------------------|------|--------------------|------|

| PVIN, AVIN, SW, EN, FB, SS to GND <sup>(3)</sup> | -0.3 | 6                  | V    |

| Power Dissipation                                |      | Internally Limited |      |

| Junction Temperature                             |      | 150                | °C   |

| Storage Temperature                              | -65  | 150                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|             |                         |                                                           | VALUE | UNIT |

|-------------|-------------------------|-----------------------------------------------------------|-------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)(2) | ±2000 | V    |

<sup>1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|                            | MIN  | MAX | UNIT |

|----------------------------|------|-----|------|

| PVIN to GND <sup>(1)</sup> | 2.95 | 5.5 | V    |

| AVIN to GND <sup>(1)</sup> | 2.95 | 5.5 | ٧    |

| Junction Temperature       | -40  | 125 | °C   |

<sup>(1)</sup> PGND and AGND are electrically connected together on the PC board and the resultant net is termed GND.

## 6.4 Thermal Information

|                      |                                              | LM2854       |      |

|----------------------|----------------------------------------------|--------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                      |                                              | 16 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 38.4         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 27.6         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 17.1         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.5          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 16.9         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.3          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, Semiconductor and IC Package Thermal Metrics.

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

<sup>(3)</sup> PGND and AGND are electrically connected together on the PC board and the resultant net is termed GND.

<sup>(2)</sup> The human body model is a 100-pF capacitor discharged through a 1.5-kΩ resistor into each pin. Test method is per JESD22-Al14.

#### 6.5 Electrical Characteristics

All Typical specifications are for  $T_J$  = 25°C only; all Maximum and Minimum limits apply over the operating junction temperature range  $T_J$  range of -40°C to 125°C. Minimum and maximum limits are ensured through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. AVIN = PVIN = EN = 5 V, unless otherwise indicated in the Test Conditions column.

|                               | PARAMETER                           | TEST CONDITIONS          | MIN <sup>(1)</sup> | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|-------------------------------|-------------------------------------|--------------------------|--------------------|--------------------|--------------------|------|

| SYSTEM PARAM                  | METERS                              |                          |                    |                    |                    |      |

| $V_{REF}$                     | Reference Voltage <sup>(3)</sup>    | Measured at the FB pin   | 0.790              | 0.8                | 0.808              | V    |

| $\Delta V_{REF}/\Delta AVIN$  | Line Regulation <sup>(3)</sup>      | ΔAVIN = 2.95 V to 5.50 V |                    | 0.04%              | 0.6%               |      |

| $\Delta V_{REF}/\Delta I_{O}$ | Load Regulation                     | Normal operation         |                    | 0.25               |                    | mV/A |

| M                             | LIVI O Threehold (AVINI)            | Rising                   |                    | 2.6                | 2.95               | V    |

| V <sub>ON</sub>               | UVLO Threshold (AVIN)               | Falling hysteresis       | 25                 | 170                | 375                | mV   |

| R <sub>DS(ON)-P</sub>         | PFET On Resistance                  | I <sub>SW</sub> = 4 A    |                    | 35                 | 65                 | mΩ   |

| R <sub>DS(ON)-N</sub>         | NFET On Resistance                  | I <sub>SW</sub> = 4 A    |                    | 34                 | 65                 | mΩ   |

| I <sub>SS</sub>               | Soft-Start Current                  |                          |                    | 2                  |                    | μΑ   |

| I <sub>CL</sub>               | Peak Current Limit Threshold        |                          | 4.5                | 6                  | 6.7                | Α    |

| IQ                            | Operating Current                   | Non-switching            |                    | 1.7                | 3                  | mA   |

| I <sub>SD</sub>               | Shut Down Quiescent Current         | EN = 0 V                 |                    | 230                | 500                | μΑ   |

| PWM SECTION                   |                                     |                          |                    |                    |                    |      |

|                               | Cuitabina Francisco                 | 1-MHz option             | 800                | 1050               | 1160               | kHz  |

| f <sub>SW</sub>               | Switching Frequency                 | 500-kHz option           | 400                | 525                | 580                | kHz  |

| D <sub>range</sub>            | PWM Duty Cycle Range                |                          | 0%                 |                    | 100%               |      |

| ENABLE CONTR                  | ROL                                 | •                        |                    |                    |                    |      |

| V <sub>IH</sub>               | EN Pin Rising Threshold             |                          | 0.8                | 1.23               | 1.65               | V    |

| V <sub>EN(HYS)</sub>          | EN Pin Hysteresis                   |                          |                    | 150                |                    | mV   |

| THERMAL CONT                  | rrol                                |                          |                    |                    |                    |      |

| T <sub>SD</sub>               | T <sub>J</sub> for Thermal Shutdown |                          |                    | 165                |                    | °C   |

| T <sub>SD-HYS</sub>           | Hysteresis for Thermal Shutdown     |                          |                    | 10                 |                    | °C   |

<sup>(1)</sup> Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

<sup>(2)</sup> Typical numbers are at 25°C and represent the most likely parametric norm.

<sup>(3)</sup> V<sub>REF</sub> measured in a non-switching, closed-loop configuration.

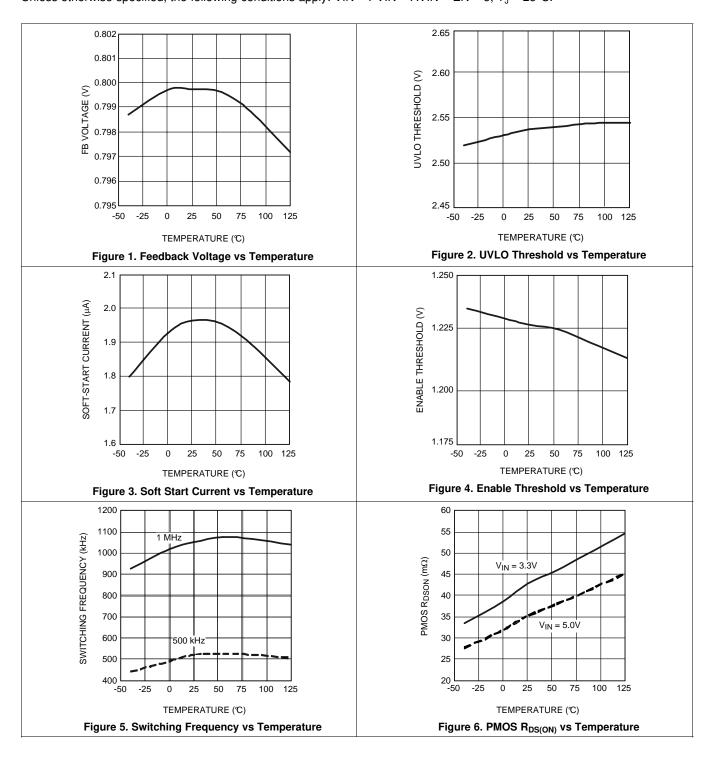

## 6.6 Typical Characteristics

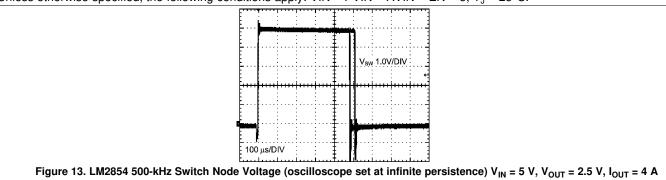

Unless otherwise specified, the following conditions apply: VIN = PVIN = AVIN = EN = 5,  $T_J = 25$ °C.

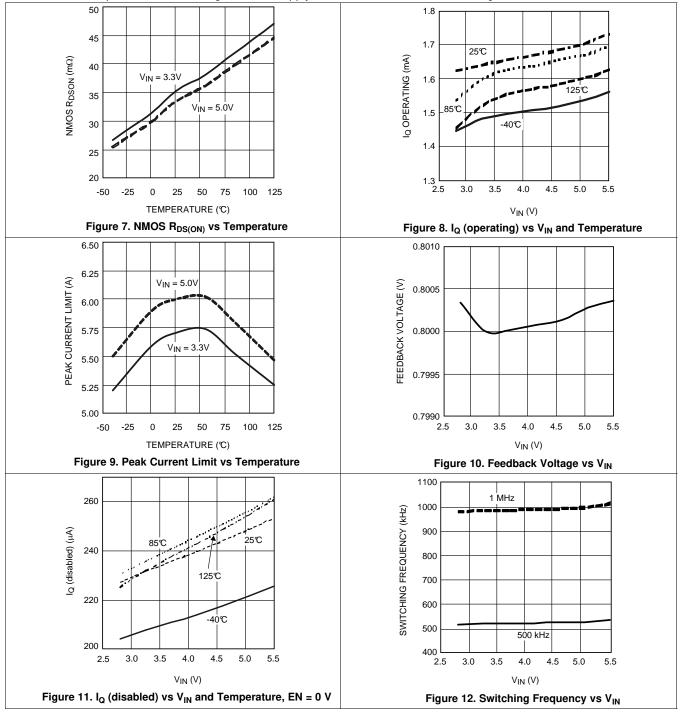

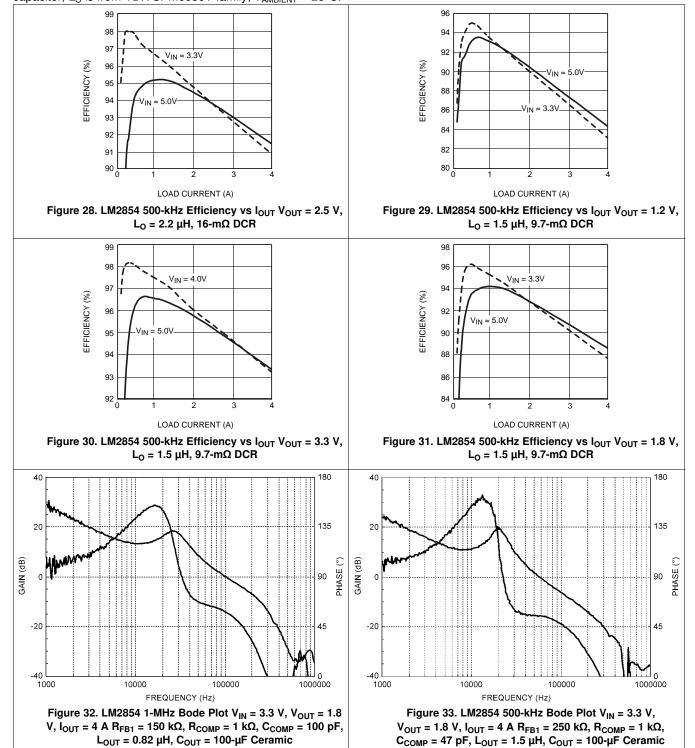

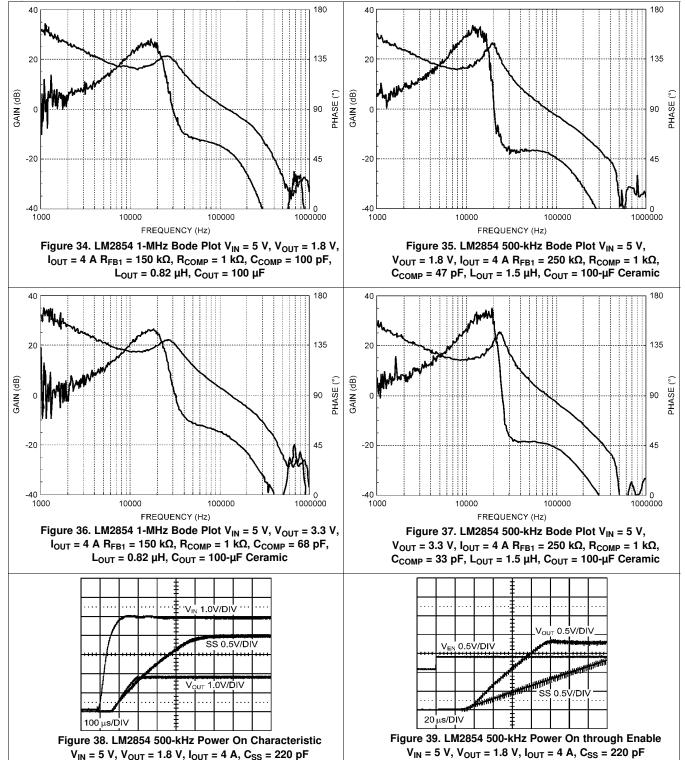

## **Typical Characteristics (continued)**

Unless otherwise specified, the following conditions apply: VIN = PVIN = AVIN = EN = 5,  $T_J = 25$ °C.

Copyright © 2008–2017, Texas Instruments Incorporated

Submit Documentation Feedback

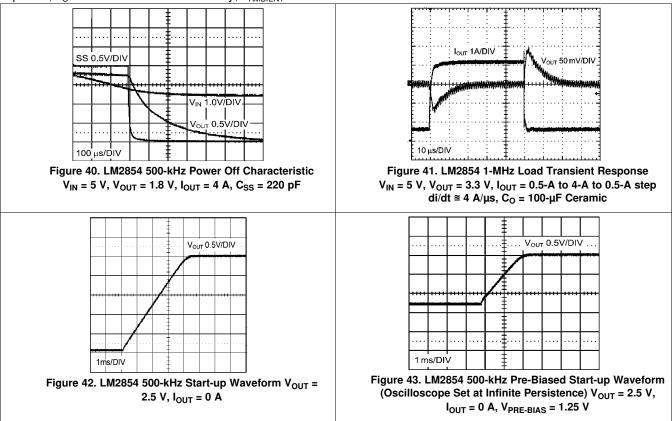

# **Typical Characteristics (continued)**

Unless otherwise specified, the following conditions apply: VIN = PVIN = AVIN = EN = 5,  $T_J = 25$ °C.

## 7 Detailed Description

#### 7.1 Overview

The LM2854 PowerWise synchronous DC-DC buck regulator belongs to the Texas Instruments family of switching regulators. Integration of the power MOSFETs and associated drivers, compensation component network, and the PWM controller reduces the number of external components necessary for a complete power supply design, without sacrificing performance.

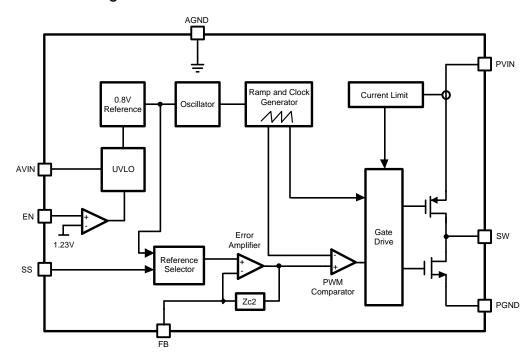

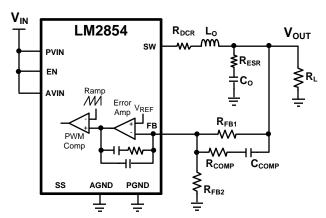

## 7.2 Functional Block Diagram

#### 7.3 Feature Description

## 7.3.1 Switching Frequency

The LM2854 is available in two switching frequency options, 500 kHz and 1 MHz. Generally, a higher switching frequency allows for faster transient response and a reduction in the footprint area and volume of the external power stage components, while a lower switching frequency affords better efficiency. These factors should be considered when selecting the appropriate switching frequency for a given application.

#### **7.3.2** Enable

The LM2854 features a enable (EN) pin and associated comparator to allow the user to easily sequence the LM2854 from an external voltage rail, or to manually set the input UVLO threshold. The turnon or rising threshold and hysteresis for this comparator are typically 1.23 V and 0.15 V, respectively. The precise reference for the enable comparator allows the user to ensure that the LM2854 will be disabled when the system demands it to be.

#### 7.3.3 Soft-Start

The LM2854 begins to operate when both the AVIN and EN voltages exceed the rising UVLO and enable thresholds, respectively. A controlled soft-start eliminates inrush currents during start-up and allows the user more control and flexibility when sequencing the LM2854 with other power supplies. An external soft-start capacitor is used to control the LM2854 start-up time. During soft-start, the voltage on the feedback pin is connected internally to the non-inverting input of the error amplifier. The soft-start period lasts until the voltage on the soft-start pin exceeds the LM2854 reference voltage of 0.8 V. At this point, the reference voltage takes over at the non-inverting amplifier input.

Draduat Folder Linker /

Copyright © 2008-2017, Texas Instruments Incorporated

## **Feature Description (continued)**

In the event of either AVIN or EN decreasing below the falling UVLO or enable threshold respectively, the voltage on the soft-start pin is collapsed by discharging the soft-start capacitor through a 5-k $\Omega$  transistor to ground.

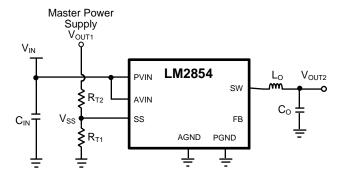

## 7.3.4 Tracking

The LM2854 can track the output of a master power supply during soft-start by connecting a resistor divider to the SS pin. In this way, the output voltage slew rate of the LM2854 will be controlled by a master supply for loads that require precise sequencing. When the tracking function is used, a small value soft-start capacitor can be connected to the SS pin to alleviate output voltage overshoot when recovering from a current limit fault.

Figure 14. Simplified Schematic Showing Use of Tracking

#### 7.3.5 Pre-Biased Start-up Capability

The LM2854 is in a pre-biased state when the device starts up with an output voltage greater than zero. This often occurs in many multi-rail applications such as when powering an FPGA, ASIC, or DSP. The output can be pre-biased in these applications through parasitic conduction paths from one supply rail to another. Even though the LM2854 is a synchronous converter, it will not pull the output low when a pre-bias condition exists. The LM2854 will not sink current during start up until the soft-start voltage exceeds the voltage on the FB pin. Since the device can not sink current it protects the load from damage that might otherwise occur if current is conducted through the parasitic paths of the load.

#### 7.3.6 Feedback Voltage Accuracy

The FB pin is connected to the inverting input of the voltage loop error amplifier and during closed loop operation its reference voltage is 0.8 V. The FB voltage is accurate to within -1.25% / +1% over temperature. Additionally, the LM2854 contains error nulling circuitry to substantially eliminate the feedback voltage over temperature drift as well as the long term aging effects of the internal amplifiers. In addition, the 1/f noise of the bandgap amplifier and reference are dramatically reduced. The manifestation of this circuit action is that the duty cycle will have two slightly different but distinct operating points, each evident every other switching cycle. The oscilloscope plot shown previously of the SW pin with infinite persistence set shows this behavior. No discernible effect is evident on the output due to LC filter attenuation. For further information, a Texas Instruments white paper is available on this topic.

#### 7.3.7 Positive Current Limit

The LM2854 employs lossless cycle-by-cycle high-side current limit circuitry to limit the peak current through the high-side FET. The peak current limit threshold, denoted  $I_{CL}$ , is nominally set at 6 A internally. When a current greater than  $I_{CL}$  is sensed through the PFET, its on-time is immediately terminated and the NFET is activated. The NFET stays on for the entire next four switching cycles (effectively four PFET pulses are skipped). During these skipped pulses, the voltage on the soft-start pin is reduced by discharging the soft-start capacitor by a current sink on the soft-start pin of nominally 6  $\mu$ A or 14  $\mu$ A for the 500-kHz or 1-MHz options, respectively. Subsequent overcurrent events will drain more and more charge from the soft-start capacitor, effectively decreasing the reference voltage as the output droops due to the pulse skipping. Reactivation of the soft-start circuitry ensures that when the overcurrent situation is removed, the part will resume normal operation smoothly.

## Feature Description (continued)

## 7.3.8 Negative Current Limit

The LM2854 implements negative current limit detection circuitry to prevent large negative current in the inductor. When the negative current sensed in the low-side NFET is below approximately -0.4 A, the present switching cycle is immediately terminated and both FETs are turned off. When both FETs are off, the negative inductor current originally flowing in the low-side NFET and into the SW pin commutates to the high-side PFET's body diode and ramps back to zero. At this point, the SW pin becomes a high impedance node and ringing can be observed on the SW node as the stored energy in the inductor is dissipated while resonating with the parasitic nodal capacitance.

## 7.3.9 Overtemperature Protection

When the LM2854 senses a junction temperature greater than 165°C, both switching FETs are turned off and the part enters a sleep state. Upon sensing a junction temperature below 155°C, the part will re-initiate the soft-start sequence and begin switching once again. This feature is provided to prevent catastrophic failure due to excessive thermal dissipation.

#### 7.3.10 Loop Compensation

The LM2854 preserves flexibility by integrating the control components around the error amplifier while using three small external compensation components from  $V_{\text{OUT}}$  to FB. An integrated type II (two pole, one zero) voltage-mode compensation network is featured. To ensure stability, an external resistor and small value capacitor can be added across the upper feedback resistor as a pole-zero pair to complete a type III (three pole, two zero) compensation network. For correct selection of these components, see *Detailed Design Procedure*.

#### 7.4 Device Functional Modes

#### 7.4.1 Shutdown Mode

If EN is less than  $V_{IH} - V_{EN(HSY)}$ , the LM2854 shuts down. Most internal circuitry is shut down, and the SW output is high-impedance. Once EN voltage exceeds  $V_{IH}$ , the LM2854 enters soft-start mode.

#### 7.4.2 Soft-Start and Track Mode

Once operation is initiated, the LM2854 starts charging its SS node. If a voltage is already present on the LM2854 circuit output, the LM2854 does not attempt to pull the circuit output low. If only a capacitor is connected to the SS pin, voltage on this pin rises, and once voltage exceeds 0.8 V, normal operating mode commences. If the high-side current limit is exceeded, the voltage on the SS pin is reduced, prolonging soft-start and track mode.

If a resistor divider is used to connect the SS pin to another power supply, Soft Start and Track mode can be used to cause the output of the LM2854 Buck to track this supply.

#### 7.4.3 Normal Operating Mode

If the EN input of the LM2854 is above  $V_{IH}$  and the SS pin is above 0.8 V, output is regulated normally. If EN is reduced to less than  $V_{IH} - V_{EN(HSY)}$ , the LM2854 enters shutdown mode. If the high-side current limit is activated or SS is pulled to below 0.8 V, the LM2854 enters soft-start and track mode.

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

The LM2854 is designed to convert voltage between 2.95 V and 5.5 V to a well-regulated voltage between input voltage and 0.8 V.

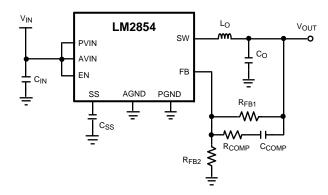

## 8.2 Typical Application

Figure 15. Typical Application Diagram

## 8.2.1 Design Requirements

Before starting a design, the following five design criteria should be considered. These criteria are the basic inputs into the detailed design procedure listed below.

- Output voltage: Choose an output voltage between 0.8 V and the lowest expected input voltage.

- Size vs efficiency: Choose 1 MHz for small physical size, and 500 kHz switching frequency for efficiency.

- Step load response and ripple: Use this criterion to select output capacitance. Also see compensation in Detailed Design Procedure.

- UVLO: Input UVLO voltage should be selected. A voltage divider connected to the EN input can be used to select input start-up voltage.

- Tracking: If tracking is desired, a voltage divider can be connected to the SS node.

## 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Input Filter Capacitor

Fast switching currents place a large strain on the input supply to a buck regulator. A capacitor placed close to the PVIN and PGND pins of the LM2854 helps to supply the instantaneous charge required when the regulator demands a pulse of current every switching cycle. In fact, the input capacitor conducts a square-wave current of peak-to-peak amplitude equal to I<sub>OUT</sub>. With this high AC current present in the input capacitor, the RMS current rating becomes an important parameter. The necessary RMS current rating of the input capacitor to a buck regulator can be estimated using Equation 1.

$$I_{Cin(RMS)} = I_{OUT}\sqrt{D(1-D)}$$

(1)

where the PWM duty cycle, D, is given in Equation 2.

$$D = \frac{V_{\text{OUT}}}{V_{\text{IN}}} \tag{2}$$

Neglecting capacitor ESR, the resultant input capacitor AC ripple voltage is a triangular waveform with peak-to-peak amplitude specified in Equation 3.

$$\Delta V_{in} = \frac{V_{OUT}D(1-D)}{f_{SW}C_{IN}}$$

(3)

The maximum input capacitor ripple voltage and RMS current occur at 50% duty cycle. A  $22-\mu F$  or  $47-\mu F$  high-quality dielectric (X5R, X7R) ceramic capacitor with adequate voltage rating is typically sufficient as an input capacitor to the LM2854. The input capacitor should be placed as close as possible to the PVIN and PGND pins to substantially eliminate the parasitic effects of any stray inductance or resistance on the PC board and supply lines. Additional bulk capacitance with higher ESR may be required to damp any resonance effects of the input capacitance and parasitic inductance.

## 8.2.2.2 AVIN Filtering Components

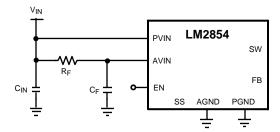

In addition to the large input filter capacitor, a smaller ceramic capacitor such as a 0.1  $\mu$ F or 1.0  $\mu$ F is recommended between AVIN and AGND to filter high frequency noise present on the PVIN rail from the quiet AVIN supply. For additional filtering in noisy environments, a small RC filter can be used on the AVIN pin as shown below.

Figure 16. Filtering of AVIN

In general,  $R_F$  is typically selected between 1  $\Omega$  and 10  $\Omega$  so that the steady state voltage drop across the resistor due to the AVIN bias current does not affect the UVLO level. Recommended filter capacitor,  $C_F$ , is 1  $\mu F$  in X5R or X7R dielectric.

#### 8.2.2.3 Soft-Start Capacitor

When the LM2854 is enabled, the output voltage will ramp up linearly in the time dictated by the relationship shown in Equation 4.

$$t_{SS} = \frac{C_{SS} \times V_{REF}}{I_{SS}}$$

(4)

where  $V_{REF}$  is the internal reference voltage (nominally 0.8V),  $I_{SS}$  is the soft-start charging current (nominally 2  $\mu$ A) and  $C_{SS}$  is the external soft-start capacitance. Rearranging this equation allows for the necessary soft-start capacitor for a given start-up time to be calculated as in Equation 5.

$$C_{SS} = \frac{t_{SS} \times 2 \,\mu\text{A}}{0.8\text{V}} \tag{5}$$

Thus, the required soft start capacitor per unit output voltage start-up time is given in Equation 6.

$$C_{SS} = 2.5 \text{ nF / ms} \tag{6}$$

For example, a 10 nF soft-start capacitor will yield a 4 ms soft-start time.

#### 8.2.2.4 Tracking - Equal Soft-Start Time

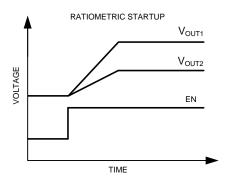

One way to use the tracking feature is to design the tracking resistor divider so that the master supply output voltage,  $V_{OUT1}$ , and the LM2854 output voltage,  $V_{OUT2}$ , both rise together and reach their target values at the same time. This is termed ratiometric start-up. For this case, the equation governing the values of tracking divider resistors  $R_{T1}$  and  $R_{T2}$  is given in Equation 7.

$$R_{T1} = \frac{R_{T2}}{V_{OUT1} - 1.0V} \tag{7}$$

The above equation includes an offset voltage to ensure that the final value of the SS pin voltage exceeds the reference voltage of the LM2854. This offset will cause the LM2854 output voltage to reach regulation slightly before the master supply. A value of 33 k $\Omega$  1% is recommended for R<sub>T2</sub> as a compromise between high precision and low quiescent current through the divider while minimizing the effect of the 2  $\mu$ A soft-start current source.

For example, If the master supply voltage  $V_{OUT1}$  is 3.3V and the LM2854 output voltage was 1.8V, then the value of  $R_{T1}$  needed to give the two supplies identical soft-start times would be 14.3 k $\Omega$ . A timing diagram for this example, the equal soft-start time case, is shown in Figure 17.

Figure 17. Simplified Start-up Waveforms When Using Proportional Tracking

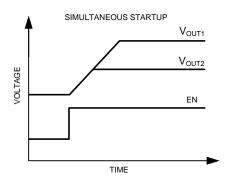

## 8.2.2.5 Tracking - Equal Slew Rates

Alternatively, the tracking feature can be used to have similar output voltage ramp rates. This is referred to as simultaneous start-up. In this case, the tracking resistors can be calculated using Equation 8.

$$R_{T1} = \frac{0.8V}{V_{OUT2} - 0.8V} R_{T2}$$

(8)

and to ensure proper overdrive of the SS pin as calculated in Equation 9.

$$V_{OUT2} < 0.8 V_{OUT1}$$

For the example case of  $V_{OUT1} = 5$  V and  $V_{OUT2} = 2.5$  V, with RT2 set to 33 k $\Omega$  as before,  $R_{T1}$  is calculated from the above equation to be 15.5 k $\Omega$ . A timing diagram for the case of equal slew rates is shown in Figure 18.

Figure 18. Simplified Start-up Waveforms, Showing Tracking Used to Achieve Equal Slew Rates

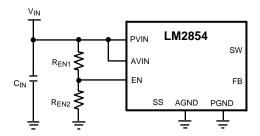

#### 8.2.2.6 Enable and UVLO

Using a resistor divider from VIN to EN as shown in the schematic diagram below, the input voltage at which the part begins switching can be increased above the normal input UVLO level as shown in Equation 10.

$$V_{IN(UVLO)} = 1.23V \frac{R_{EN1} + R_{EN2}}{R_{EN2}}$$

(10)

For example, suppose that the required input UVLO level is 3.69 V. Choosing  $R_{EN2}$  = 10 k $\Omega$ , then we calculate  $R_{EN1}$  = 20 k $\Omega$ .

Figure 19. Simplified Schematic Showing Use of EN as an Input UVLO

Alternatively, the EN pin can be driven from another voltage source to cater for system sequencing requirements commonly found in FPGA and other multi-rail applications. The following schematic shows an LM2854 that is sequenced to start based on the voltage level of a master system rail.

Figure 20. Simplified Schematic Showing EN Used to Cascade Power Supply Start-up

#### 8.2.2.7 Output Voltage Setting

A divider resistor network from  $V_{OUT}$  to the FB pin determines the desired output voltage as shown in Equation 11.

$$V_{OUT} = 0.8V \frac{R_{FB1} + R_{FB2}}{R_{FB2}}$$

(11)

$R_{\text{FB1}}$  is defined based on the voltage loop requirements and  $R_{\text{FB2}}$  is then selected for the desired output voltage. These resistors are normally selected as 0.5% or 1% tolerance.

#### 8.2.2.8 Compensation Component Selection

The power stage transfer function of a voltage mode buck converter has a complex double pole related to the LC output filter and a left half plane zero due to the output capacitor ESR, denoted R<sub>ESR</sub>. The locations of these singularities are given respectively in Equation 12.

$$f_{LC} = \frac{1}{2\pi\sqrt{L_{O}C_{O}\left(\frac{R_{ESR} + R_{L}}{R_{DCR} + R_{L}}\right)}} \cong \frac{1}{2\pi\sqrt{L_{O}C_{O}}}$$

$$f_{ESR} = \frac{1}{2\pi R_{ESR}C_{O}}$$

#### where

- C<sub>O</sub> is the output capacitance value appropriately derated for applied voltage and operating temperature

- R<sub>I</sub> is the effective load resistance

- R<sub>DCR</sub> is the series damping resistance associated with the inductor and power switches (12)

Figure 21. LM2854 Compensation Scheme

The conventional compensation strategy employed with voltage mode control is to use two compensator zeros to offset the LC double pole, one compensator pole located to cancel the output capacitor ESR zero and one compensator pole located between one third and one half switching frequency for high frequency noise attenuation.

The LM2854 internal compensation components are designed to locate a pole at the origin and a pole at high frequency as mentioned above. Furthermore, a zero is located at 8.8 kHz or 17.6 kHz for the 500 kHz or 1 MHz options, respectively, to approximately cancel the likely location of one LC filter pole.

The three external compensation components,  $R_{FB1}$ ,  $R_{COMP}$  and  $C_{COMP}$ , are selected to position a zero at or below the LC pole location and a pole to cancel the ESR zero. The voltage loop crossover frequency,  $f_{loop}$ , is usually selected between one tenth to one fifth of the switching frequency, as shown in Equation 13.

$$0.1f_{SW} \le f_{loop} \le 0.2f_{SW} \tag{13}$$

A simple solution for the required external compensation capacitor,  $C_{COMP}$ , with type III voltage mode control can be expressed as in Equation 14.

$$C_{COMP}(pF) = \alpha \frac{L_O(\mu H)C_O(\mu F)}{V_{IN}(V)} f_{loop}(kHz)$$

(14)

where the constant  $\alpha$  is nominally 0.038 or 0.075 for the 500 kHz or 1 MHz options, respectively. This assumes a compensator pole cancels the output capacitor ESR zero. Furthermore, since the modulator gain is proportional to  $V_{IN}$ , the loop crossover frequency increases with  $V_{IN}$ . Thus, it is recommended to design the loop at maximum expected  $V_{IN}$ .

The upper feedback resistor,  $R_{FB1}$ , is selected to provide adequate mid-band gain and to locate a zero at or below the LC pole frequency. The series resistor,  $R_{COMP}$ , is selected to locate a pole at the ESR zero frequency, as shown in Equation 15.

$$R_{\text{FB1}} = \frac{1}{2\pi C_{\text{COMP}} f_{\text{LC}}}$$

$$R_{\text{COMP}} = \frac{1}{2\pi C_{\text{COMP}} f_{\text{ESR}}}$$

(15)

Note that the lower feedback resistor,  $R_{FB2}$ , has no impact on the control loop from an AC standpoint since the FB pin is the input to an error amplifier and effectively at AC ground. Hence, the control loop can be designed irrespective of output voltage level. The only caveat here is the necessary derating of the output capacitance with applied voltage. Having chosen  $R_{FB1}$  as above,  $R_{FB2}$  is then selected for the desired output voltage.

Table 1 and Table 2 list inductor and ranges of capacitor values that work well with the LM2854, along with the associated compensation components to ensure stable operation. Values different than those listed may be used, but the compensation components may need to be recalculated to avoid degradation in phase margin. Note that the capacitance ranges specified refer to in-circuit values where the nominal capacitance value is adequately derated for applied voltage.

#### 8.2.2.9 Filter Inductor and Output Capacitor Selection

In a buck regulator, selection of the filter inductor and capacitor will affect many key system parameters, including stability, transient response and efficiency The LM2854 can accommodate relatively wide ranges of output capacitor and filter inductor values in a typical application and still achieve excellent load current transient performance and low output voltage ripple.

The inductance is chosen such that the peak-to-peak inductor current ripple,  $\Delta i_L$ , is approximately 25 to 40% of  $I_{OUT}$  as shown in Equation 16.

$$L_{O} = \frac{V_{OUT}(1-D)}{\Delta i_{L} f_{SW}} \cong \frac{V_{OUT}(1-D)}{0.3 I_{OUT} f_{SW}}$$

(16)

Note that the peak inductor current is the DC output current plus half the ripple current and reaches its highest level at lowest duty cycle (or highest  $V_{IN}$ ). It is recommended that the inductor should have a saturation current rating in excess of the current limit level.

When operating the LM2854 at input voltages above 5.2 V, the inductor should be sized to keep the minimum inductor current above -0.5 A. For most applications this should only occur at light loads or when the inductor is drastically undersized. To ensure the current never goes below -0.5 A for any application, the peak-to-peak ripple current ( $\Delta i_L$ ) in the inductor should be less than 1 A. Keeping the minimum inductor current above -0.5 A limits the energy storage in the inductor and helps prevent the switch node voltage from exceeding the absolute maximum specification when the low side FET turns off.

Table 3 lists examples of off-the-shelf powdered iron and ferrite based inductors that are suitable for use with the LM2854. The output capacitor can be of ceramic or electrolytic chemistry. The chosen output capacitor requires sufficient DC voltage rating and RMS ripple current handling capability.

The output capacitor RMS current and peak-to-peak output ripple are given respectively as in Equation 17.

$$I_{Cout(RMS)} = \frac{\Delta i_L}{\sqrt{12}}$$

$$\Delta V_{OUT} = \Delta i_L \sqrt{R_{ESR}^2 + \left(\frac{1}{8f_{SW}C_O}\right)^2}$$

(17)

In general,  $22 \mu F$  to  $100 \mu F$  of ceramic output capacitance is sufficient for both LM2854 frequency options given the optimal high frequency characteristics and low ESR of ceramic dielectric. It is advisable to consult the manufacturer's derating curves for capacitance voltage coefficient as the in-circuit capacitance may drop significantly with applied voltage.

Tantalum or organic polymer electrolytic capacitance may be suitable with the LM2854 500 kHz option, particularly in applications where substantial bulk capacitance per unit volume is required. However, the high loop bandwidth achievable with the LM2854 obviates the necessity for large bulk capacitance during transient loading conditions.

Table 4 lists some examples of commercially available capacitors that can be used with the LM2854.

Table 1. LM2854 500-kHz Compensation Component Values

| V 00                | 1 (-11)             | C <sub>O</sub> (μF) |     | ESR | ESR (mΩ) |                       | 0 (F)                  | D (1:0)                |

|---------------------|---------------------|---------------------|-----|-----|----------|-----------------------|------------------------|------------------------|

| V <sub>IN</sub> (V) | L <sub>O</sub> (μH) | MIN                 | MAX | MIN | MAX      | R <sub>FB1</sub> (kΩ) | C <sub>COMP</sub> (pF) | R <sub>COMP</sub> (kΩ) |

|                     | 1.5                 | 40                  | 100 | 2   | 10       | 150                   | 47                     | 1                      |

|                     | 1.5                 | 100                 | 200 | 1   | 5        | 150                   | 100                    | 1                      |

| 5                   | 1.5                 | 100                 | 220 | 15  | 25       | 150                   | 120                    | 25                     |

| 5                   | 2.2                 | 40                  | 100 | 2   | 10       | 150                   | 68                     | 1                      |

|                     | 2.2                 | 100                 | 200 | 1   | 5        | 150                   | 120                    | 1                      |

|                     | 2.2                 | 100                 | 220 | 15  | 25       | 120                   | 120                    | 15                     |

|                     | 1.5                 | 40                  | 100 | 2   | 10       | 150                   | 68                     | 1                      |

|                     | 1.5                 | 100                 | 200 | 1   | 5        | 100                   | 150                    | 1                      |

| 0.0                 | 1.5                 | 100                 | 220 | 15  | 25       | 100                   | 150                    | 15                     |

| 3.3                 | 2.2                 | 40                  | 100 | 2   | 10       | 150                   | 100                    | 1                      |

|                     | 2.2                 | 100                 | 200 | 1   | 5        | 100                   | 220                    | 1                      |

|                     | 2.2                 | 100                 | 220 | 15  | 25       | 100                   | 220                    | 10                     |

Table 2. LM2854 1-MHz Compensation Component Values

| V (V)               | I (LI\              | C <sub>O</sub> (μF) |     | ESR | ESR (mΩ) |                       | 0 (=5)                 | D (I+O)                |

|---------------------|---------------------|---------------------|-----|-----|----------|-----------------------|------------------------|------------------------|

| V <sub>IN</sub> (V) | L <sub>O</sub> (μH) | MIN                 | MAX | MIN | MAX      | R <sub>FB1</sub> (kΩ) | C <sub>COMP</sub> (pF) | R <sub>COMP</sub> (kΩ) |

|                     | 0.68                | 20                  | 60  | 2   | 10       | 120                   | 33                     | 1                      |

|                     | 0.68                | 60                  | 150 | 1   | 5        | 75                    | 100                    | 1                      |

| 5                   | 0.68                | 100                 | 220 | 15  | 25       | 100                   | 100                    | 20                     |

| 3                   | 1                   | 20                  | 60  | 2   | 10       | 100                   | 56                     | 1                      |

|                     | 1                   | 60                  | 150 | 1   | 5        | 75                    | 150                    | 1                      |

|                     | 1                   | 100                 | 220 | 15  | 25       | 75                    | 150                    | 15                     |

|                     | 0.68                | 20                  | 60  | 2   | 10       | 75                    | 56                     | 1                      |

|                     | 0.68                | 60                  | 150 | 1   | 5        | 50                    | 150                    | 1                      |

| 3.3                 | 0.68                | 100                 | 220 | 15  | 25       | 50                    | 150                    | 12                     |

| 3.3                 | 1                   | 20                  | 60  | 2   | 10       | 75                    | 82                     | 1                      |

|                     | 1                   | 60                  | 150 | 1   | 5        | 50                    | 220                    | 1                      |

|                     | 1                   | 100                 | 220 | 15  | 25       | 33                    | 330                    | 10                     |

**Table 3. Recommended Filter Inductors**

| INDUCTANCE (μH) | DCR (mΩ) | MANUFACTURER | MANUFACTURER P/N   | CASE SIZE (mm)                 |

|-----------------|----------|--------------|--------------------|--------------------------------|

| 0.47            | 14.5     | Vishay Dale  | IHLP1616BZERR47M11 | 4.06 × 4.45 × 2.00             |

| 1               | 24       | Vishay Dale  | IHLP1616BZER1R0M11 | 4.06 × 4.45 × 2.00             |

| 0.47            | 8.4      | Vishay Dale  | IHLP2525AHERR47M01 | 6.47 × 6.86 × 1.80             |

| 0.47            | 6        | Vishay Dale  | IHLP2525BDERR47M01 | $6.47 \times 6.86 \times 2.40$ |

| 0.68            | 8.7      | Vishay Dale  | IHLP2525BDERR68M01 | $6.47 \times 6.86 \times 2.40$ |

| 0.82            | 10.6     | Vishay Dale  | IHLP2525BDERR82M01 | 6.47 × 6.86 × 2.40             |

| 1               | 13.1     | Vishay Dale  | IHLP2525BDER1R0M01 | 6.47 × 6.86 × 2.40             |

| 1.5             | 18.5     | Vishay Dale  | IHLP2525BDER1R5M01 | 6.47 × 6.86 × 2.40             |

# Table 3. Recommended Filter Inductors (continued)

| INDUCTANCE (µH) | DCR (mΩ) | MANUFACTURER | MANUFACTURER P/N   | CASE SIZE (mm)            |

|-----------------|----------|--------------|--------------------|---------------------------|

| 2.2             | 15.7     | Vishay Dale  | IHLP2525CZER2R2M11 | 6.47 × 6.86 × 3.00        |

| 0.47            | 3.5      | Sumida       | CDMC6D28NP-R47M    | 6.50 × 7.25 × 3.00        |

| 0.68            | 4.5      | Sumida       | CDMC6D28NP-R68M    | 6.50 × 7.25 × 3.00        |

| 1               | 17.3     | Sumida       | CDMC6D28NP-1R0M    | 6.50 × 7.25 × 3.00        |

| 1.5             | 10.4     | Sumida       | CDMC6D28NP-1R5M    | 6.50 × 7.25 × 3.00        |

| 2.2             | 16.1     | Sumida       | CDMC6D28NP-2R2M    | 6.50 × 7.25 × 3.00        |

| 0.56            | 10       | Coilcraft    | DO1813H-561ML      | 6.10 × 8.89 × 5.00        |

| 0.47            | 3.3      | Coilcraft    | HA3619-471ALC      | 7 × 7 × 3                 |

| 0.68            | 4.8      | Coilcraft    | HA3619-681ALC      | $7 \times 7 \times 3$     |

| 1               | 7.5      | Coilcraft    | HA3619-102ALC      | $7 \times 7 \times 3$     |

| 1.2             | 9.4      | Coilcraft    | HA3619-122ALC      | 7 × 7 × 3                 |

| 1.5             | 11.5     | Coilcraft    | HA3619-152ALC      | 7 × 7 × 3                 |

| 1.8             | 16.5     | Coilcraft    | HA3619-182ALC      | $7 \times 7 \times 3$     |

| 0.47            | 3.3      | TDK          | SPM6530T-R47M170   | 7.1 × 6.5 × 3             |

| 0.68            | 4.9      | TDK          | SPM6530T-R68M140   | 7.1 × 6.5 × 3             |

| 1               | 7.1      | TDK          | SPM6530T-1R0M120   | 7.1 × 6.5 × 3             |

| 1.5             | 9.7      | TDK          | SPM6530T-1R5M100   | 7.1 × 6.5 × 3             |

| 0.47            | 14       | Cyntec       | PCMC042T-0R47MN    | 4 × 4.5 × 2               |

| 1.0             | 9        | Cyntec       | PCMC063T-1R0MN     | 6.5 × 6.9 × 3             |

| 1.5             | 14       | Cyntec       | PCMC063T-1R5MN     | $6.5 \times 6.9 \times 3$ |

# **Table 4. Recommended Filter Capacitors**

| CAPACITANCE (μF) | VOLTAGE (V), ESR (mΩ) | CHEMISTRY       | MANUFACTURER | MANUFACTURER P/N | CASE SIZE                  |

|------------------|-----------------------|-----------------|--------------|------------------|----------------------------|

| 22               | 6.3, < 5              | Ceramic, X5R    | TDK          | C3216X5R0J226M   | 1206                       |

| 47               | 6.3, < 5              | Ceramic, X5R    | TDK          | C3216X5R0J476M   | 1206                       |

| 47               | 6.3, < 5              | Ceramic, X5R    | TDK          | C3225X5R0J476M   | 1210                       |

| 47               | 10, < 5               | Ceramic, X5R    | TDK          | C3225X5R1A476M   | 1210                       |

| 100              | 6.3, < 5              | Ceramic, X5R    | TDK          | C3225X5R0J107M   | 1210                       |

| 100              | 6.3, 50               | Tantalum        | AVX          | TPSD157M006#0050 | D, 7.5 × 4.3 × 2.9 mm      |

| 100              | 6.3, 25               | Organic Polymer | Sanyo        | 6TPE100MPB2      | B2, 3.5 × 2.8 × 1.9 mm     |

| 150              | 6.3, 18               | Organic Polymer | Sanyo        | 6TPE150MIC2      | C2, 6 × 3.2 × 1.8 mm       |

| 330              | 6.3, 18               | Organic Polymer | Sanyo        | 6TPE330MIL       | D3L, 7.3 × 4.3 × 2.8<br>mm |

| 470              | 6.3, 23               | Niobium Oxide   | AVX          | NOME37M006#0023  | E, 7.3 × 4.3 × 4.1 mm      |

# **STRUMENTS**

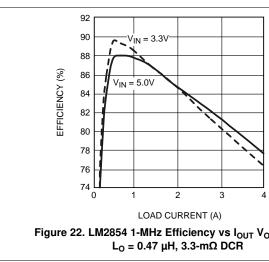

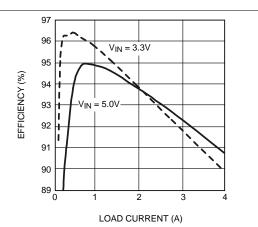

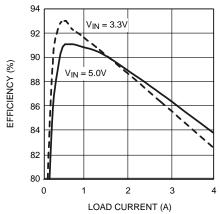

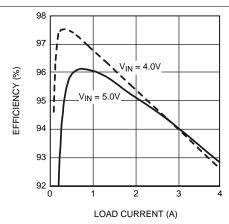

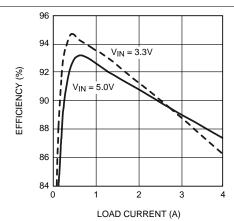

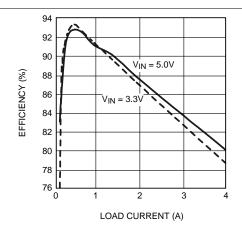

## 8.2.3 Application Curves

Unless otherwise specified, the following conditions apply:  $V_{IN}$  = PVIN = AVIN = EN = 5 V,  $C_{IN}$  is 47- $\mu$ F 10-V X5R ceramic capacitor, L<sub>O</sub> is from TDK SPM6530T family; T<sub>AMBIENT</sub> = 25°C.

Figure 22. LM2854 1-MHz Efficiency vs  $I_{OUT}$   $V_{OUT}$  = 0.8 V,

Figure 23. LM2854 1-MHz Efficiency vs  $I_{OUT}$   $V_{OUT}$  = 2.5 V,  $L_O$  = 1  $\mu H$ , 7.1-m $\Omega$  DCR

Figure 24. LM2854 1-MHz Efficiency vs  $I_{OUT}$   $V_{OUT}$  = 1.2 V,  $L_O$  = 0.68  $\mu H,\,4.9\text{-}m\Omega$  DCR

Figure 25. LM2854 1-MHz Efficiency vs I<sub>OUT</sub> V<sub>OUT</sub> = 3.3 V,  $L_O$  = 1  $\mu H$ , 7.1-m $\Omega$  DCR

Figure 26. LM2854 1-MHz Efficiency vs  $I_{OUT}$   $V_{OUT}$  = 1.8 V,  $L_{O}$  = 1  $\mu H,\,7.1\text{-}m\Omega$  DCR

Figure 27. LM2854 500-kHz Efficiency vs  $I_{OUT}$   $V_{OUT}$  = 0.8 V,  $L_{O}$  = 1  $\mu H,\,7.1\text{-}m\Omega$  DCR

Submit Documentation Feedback

Copyright © 2008-2017, Texas Instruments Incorporated

Copyright © 2008–2017, Texas Instruments Incorporated

Submit Documentation Feedback

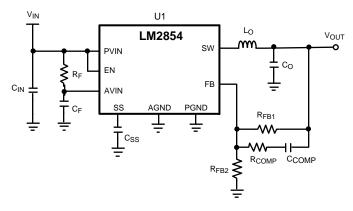

#### 8.2.4 System Examples

This section provides several application solutions with an associated bill of materials, listed in Table 5 to Table 7. All bill of materials reference the schematic in Figure 44. The compensation for each solution was optimized to work over the full input range. Many applications have a fixed input voltage rail. It is possible to modify the compensation to obtain a faster transient response for a given input voltage operating point.

Figure 44. LM2854 Application Circuit Schematic

Submit Documentation Feedback

Table 5. LM2854 500-kHz Bill of Materials,  $V_{IN}$  = 5 V,  $V_{OUT}$  = 3.3 V,  $I_{OUT(MAX)}$  = 4 A, Optimized for Efficiency

| REF DES           | DESCRIPTION                   | CASE SIZE          | MANUFACTURER      | MANUFACTURER P/N  |

|-------------------|-------------------------------|--------------------|-------------------|-------------------|

| U1                | Synchronous Buck<br>Regulator | HTSSOP-16          | Texas Instruments | LM2854MHX-500     |

| C <sub>IN</sub>   | 47 μF, X5R, 10 V              | 1210               | TDK               | C3225X5R1A476M    |

| Co                | 100 μF, X5R, 6.3 V            | 1210               | TDK               | C3225X5R0J107M    |

| Lo                | 1.5 μH, 9.7 mΩ, 10 A          | 7.1 × 6.5 × 3.0 mm | TDK               | SPM6530T-1R5M100  |

| R <sub>FB1</sub>  | 249 kΩ                        | 0603               | Vishay Dale       | CRCW06032493F-e3  |

| R <sub>FB2</sub>  | 80.6 kΩ                       | 0603               | Vishay Dale       | CRCW060328062F-e3 |

| R <sub>COMP</sub> | 1 kΩ                          | 0603               | Vishay Dale       | CRCW06031001F-e3  |

| $R_{F}$           | 1 Ω                           | 0603               | Vishay Dale       | CRCW06031R0F-e3   |

| C <sub>COMP</sub> | 33 pF, ±5%, C0G, 50 V         | 0603               | TDK               | C1608C0G1H330J    |

| C <sub>SS</sub>   | 10 nF, ±10%, X7R, 16 V        | 0603               | Murata            | GRM188R71C103KA01 |

| C <sub>F</sub>    | 1.0 μF, ±10%, X7R, 10 V       | 0603               | Murata            | GRM188R71A105KA61 |

Table 6. LM2854 1-MHz Bill of Materials,  $V_{IN}$  = 3.3 V to 5 V,  $V_{OUT}$  = 2.5 V,  $I_{OUT\ (MAX)}$  = 4 A, Optimized for Electrolytic Input and Output Capacitance

| REF DES           | DESCRIPTION                        | CASE SIZE               | MANUFACTURER      | MANUFACTURER P/N   |

|-------------------|------------------------------------|-------------------------|-------------------|--------------------|

| U1                | Synchronous Buck Regulator         | HTSSOP-16               | Texas Instruments | LM2854MHX-1000     |

| C <sub>IN</sub>   | 150 $\mu F$ , 6.3 V, 18 m $\Omega$ | C2, 6 × 3.2 × 1.8 mm    | Sanyo             | 6TPE150MIC2        |

| C <sub>O</sub>    | 330 $\mu F$ , 6.3 V, 18 m $\Omega$ | D3L, 7.3 × 4.3 × 2.8 mm | Sanyo             | 6TPE330MIL         |

| L <sub>O</sub>    | 2.2 μH, 16 m $\Omega$ , 7 A        | 6.47 × 6.86 × 3 mm      | Vishay Dale       | IHLP2525CZER2R2M11 |

| R <sub>FB1</sub>  | 100 kΩ                             | 0603                    | Vishay Dale       | CRCW06031003F-e3   |

| R <sub>FB2</sub>  | 47.5 kΩ                            | 0603                    | Vishay Dale       | CRCW060324752F-e3  |

| R <sub>COMP</sub> | 15 kΩ                              | 0603                    | Vishay Dale       | CRCW06031502F-e3   |

| $R_{F}$           | 1 Ω                                | 0603                    | Vishay Dale       | CRCW06031R0F-e3    |

| $C_{COMP}$        | 330 pF, ±5%, C0G, 50 V             | 0603                    | TDK               | C1608C0G1H331J     |

| C <sub>SS</sub>   | 10 nF, ±10%, X7R, 16 V             | 0603                    | Murata            | GRM188R71C103KA01  |

| C <sub>F</sub>    | 1 μF,±10%, X7R, 10 V               | 0603                    | Murata            | GRM188R71A105KA61  |

Table 7. LM2854 1-MHz Bill of Materials,  $V_{IN}$  = 3.3 V,  $V_{OUT}$  = 0.8 V,  $I_{OUT~(MAX)}$  = 4 A, Optimized for Solution Size and Transient Response

| REF DES           | DESCRIPTION                | CASE SIZE             | MANUFACTURER      | MANUFACTURER P/N    |

|-------------------|----------------------------|-----------------------|-------------------|---------------------|

| U1                | Synchronous Buck Regulator | HTSSOP-16             | Texas Instruments | LM2854MHX-1000      |

| C <sub>IN</sub>   | 47 μF, X5R, 6.3 V          | 1206                  | TDK               | C3216X5R0J476M      |

| Co                | 47 μF, X5R, 6.3 V          | 1206                  | TDK               | C3216X5R0J476M      |

| Lo                | 0.47 μH, 14.5 mΩ, 7 A      | 4.06 × 4.45 × 2.00 mm | Vishay Dale       | IHLP1616BZER0R47M11 |

| R <sub>FB1</sub>  | 110 kΩ                     | 0402                  | Vishay Dale       | CRCW04021103F-e3    |

| R <sub>COMP</sub> | 1 kΩ                       | 0402                  | Vishay Dale       | CRCW04021001F-e3    |

| $R_{F}$           | 1 Ω                        | 0402                  | Vishay Dale       | CRCW04021R0F-e3     |

| $C_COMP$          | 27 pF, ±5%, C0G, 50 V      | 0402                  | Murata            | GRM1555C1H270JZ01   |

| C <sub>SS</sub>   | 10 nF, ±10%, X7R, 16 V     | 0402                  | Murata            | GRM155R71C103KA01   |

| C <sub>F</sub>    | 1 μF, ±10%, X7R, 10 V      | 0402                  | Murata            | GRM155R61A105KE15   |

## 9 Power Supply Recommendations

The LM2854 is designed to operate from an input voltage supply range from 2.95 V to 5.5 V. This input supply should be able to source the maximum input current and maintain a voltage above either 2.95 V or the output voltage, whichever is higher. In cases where input supply is located at a distance (more than a few inches) from the device, drop due to traces and wires must be considered.

## 10 Layout

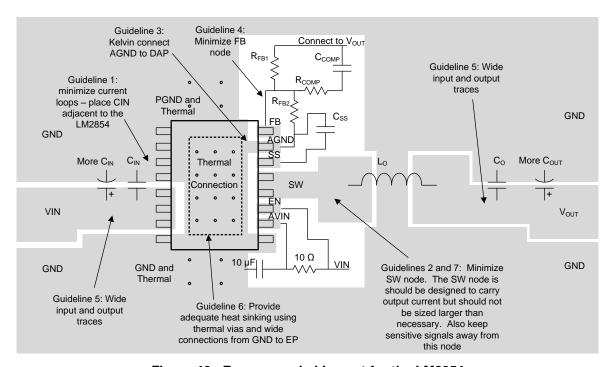

## 10.1 Layout Guidelines

PC board layout is an important part of DC-DC converter design. Poor board layout can disrupt the performance of a DC-DC converter and surrounding circuitry by contributing to EMI, ground bounce and resistive voltage drop in the traces. These can send erroneous signals to the DC-DC converter resulting in poor regulation or instability. Good layout can be implemented by following a few simple design rules.

## 1. Minimize area of switched current loops.

There are two loops where currents are switched at high di/dt slew rates in a buck regulator. The first loop represents the path taken by AC current flowing during the high side PFET on time. This current flows from the input capacitor to the regulator PVIN pins, through the high side FET to the regulator SW pin, filter inductor, output capacitor and returning via the PCB ground plane to the input capacitor. The second loop represents the path taken by AC current flowing during the low side NFET on time. This current flows from the output capacitor ground to the regulator PGND pins, through the NFET to the inductor and output capacitor. From an EMI reduction standpoint, it is imperative to minimize this loop area during PC board layout by physically locating the input capacitor close to the LM2854. Specifically, it is advantageous to place  $C_{\rm IN}$  as close as possible to the LM2854 PVIN and PGND pins. Grounding for both the input and output capacitor should consist of a localized top side plane that connects to PGND and the exposed die attach pad (DAP). The inductor should be placed close to the SW pin and output capacitor.

#### 2. Minimize the copper area of the switch node.

The LM2854 has two SW pins optimally located on one side of the package. In general the SW pins should be connected to the filter inductor on the top PCB layer. The inductor should be placed close to the SW pins to minimize the copper area of the switch node.

#### 3. Have a single point ground for all device analog grounds located under the DAP.

The ground connections for the Feedback, Soft-start, Enable and AVIN components should be routed to the AGND pin of the device. The AGND pin should connect to PGND under the DAP. This prevents any switched or load currents from flowing in the analog ground traces. If not properly handled, poor grounding can result in degraded load regulation or erratic switching behavior.

## 4. Minimize trace length to the FB pin.

Since the feedback (FB) node is high impedance, the trace from the output voltage setpoint resistor divider to FB pin should be as short as possible. This is most important as relatively high value resistors are used to set the output voltage. The FB trace should be routed away from the SW pin and inductor to avoid noise pickup from the SW pin. Both feedback resistors,  $R_{\text{FB1}}$  and  $R_{\text{FB2}}$ , and the compensation components,  $R_{\text{COMP}}$  and  $C_{\text{COMP}}$ , should be located close to the FB pin.

#### 5. Make input and output bus connections as wide as possible.

This reduces any voltage drops on the input or output of the converter and maximizes efficiency. To optimize voltage accuracy at the load, ensure that a separate feedback voltage sense trace is made to the load. Doing so will correct for voltage drops and provide optimum output accuracy.

## 6. Provide adequate device heat-sinking.

Use an array of heat-sinking vias to connect the DAP to the ground plane on the bottom PCB layer. If the PCB has a plurality of copper layers, these thermal vias can also be employed to make connection to inner layer heat-spreading ground planes. For best results use a 5 x 3 via array with minimum via diameter of 10 mils. Ensure enough copper area is used to keep the junction temperature below 125°C.

## **Layout Guidelines (continued)**

## 7. Keep sensitive system signals away from SW node.

SW is a high-voltage, rapidly changing signal which can couple to adjacent signal lines. Signal integrity of lines that have high impedances or are very sensitive to noise can be compromised by capacitive coupling to SW node.

## 10.2 Layout Example

Figure 45. High Current Loops

Figure 46. Recommended Layout for the LM2854

Submit Documentation Feedback

## 11 Device and Documentation Support

## 11.1 Documentation Support

#### 11.1.1 Related Documentation

For related documentation, see the following:

- AN-1786 LM2854 500 kHz Buck Regulator Evaluation Board (Rev. B), SNVA323

- AN-1880 LM2854 1MHz Buck Regulator Demo Board (Rev. B), SNVA358

- AN-1149 Layout Guidelines for Switching Power Supplies, SNVA021

- AN-1229 PCB Layout Guidelines, SNVA054

- Constructing Your Power Supply- Layout Considerations, SLUP230

- Low Radiated EMI Layout Made SIMPLE with LM4360x and LM4600x, SNVA721

- AN-2020 Thermal Design By Insight, Not Hindsight, SNVA419

- AN-1520 A Guide to Board Layout for Best Thermal Resistance for Exposed Pad Packages, SNVA183

- Semiconductor and IC Package Thermal Metrics, SPRA953

- Thermal Design made Simple with LM43603 and LM43602, SNVA719

- Using New Thermal Metrics, SBVA025

#### 11.2 Trademarks

PowerWise is a trademark of Texas Instrumetns, Inc. All other trademarks are the property of their respective owners.

## 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com 14-Sep-2023

#### PACKAGING INFORMATION

| Orderable Device    | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|---------------------|------------|--------------|--------------------|------|----------------|---------------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| LM2854MH-1000       | LIFEBUY    | HTSSOP       | PWP                | 16   | 92             | Non-RoHS<br>& Green | Call TI                       | Level-1-260C-UNLIM | -40 to 85    | LM2854<br>-1000         |         |

| LM2854MH-1000/NOPB  | ACTIVE     | HTSSOP       | PWP                | 16   | 92             | RoHS & Green        | SN                            | Level-1-260C-UNLIM | -40 to 85    | LM2854<br>-1000         | Samples |

| LM2854MH-500/NOPB   | ACTIVE     | HTSSOP       | PWP                | 16   | 92             | RoHS & Green        | SN                            | Level-1-260C-UNLIM | -40 to 85    | LM2854<br>-500          | Samples |

| LM2854MHX-1000/NOPB | ACTIVE     | HTSSOP       | PWP                | 16   | 2500           | RoHS & Green        | SN                            | Level-1-260C-UNLIM | -40 to 85    | LM2854<br>-1000         | Samples |

| LM2854MHX-500/NOPB  | ACTIVE     | HTSSOP       | PWP                | 16   | 2500           | RoHS & Green        | SN                            | Level-1-260C-UNLIM | -40 to 85    | LM2854<br>-500          | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

# PACKAGE OPTION ADDENDUM

www.ti.com 14-Sep-2023

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

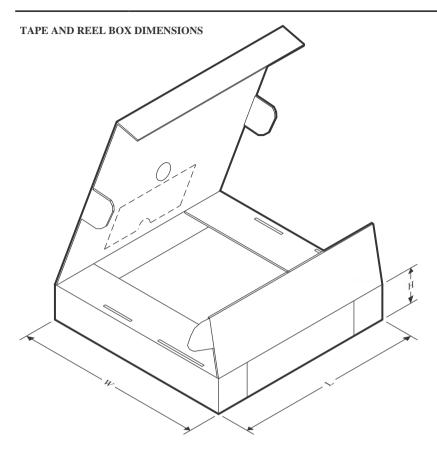

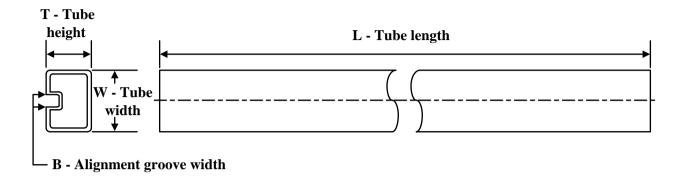

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

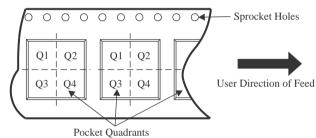

## TAPE AND REEL INFORMATION