#### CSD87355Q5D

SLPS575A - MARCH 2016 - REVISED SEPTEMBER 2017

# CSD87355Q5D Synchronous Buck NexFET™ Power Block

### 1 Features

Texas

Half-Bridge Power Block

INSTRUMENTS

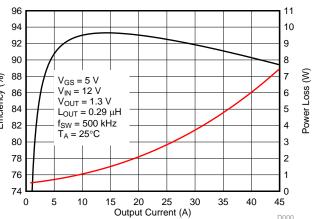

- 92.5% System Efficiency at 25 A

- Up to 45-A Operation

- High-Frequency Operation (Up to 1.5 MHz)

- High-Density SON 5-mm × 6-mm Footprint

- Optimized for 5-V Gate Drive

- Low Switching Losses

- Ultralow Inductance Package

- RoHS Compliant

- Halogen Free

- Pb-Free Terminal Plating

## 2 Applications

- Synchronous Buck Converters

- High-Frequency Applications

- High-Current, Low Duty Cycle Applications

- Multiphase Synchronous Buck Converters

- POL DC-DC Converters

- IMVP, VRM, and VRD Applications

## 3 Description

The CSD87355Q5D NexFET<sup>™</sup> power block is an optimized design for synchronous buck applications offering high-current, high-efficiency, and high-frequency capability in a small 5-mm × 6-mm outline. Optimized for 5-V gate drive applications, this product offers a flexible solution capable of offering a high-density power supply when paired with any 5-V gate drive from an external controller/driver.

#### Ordering Information<sup>(1)</sup>

| Device       | Media        | Qty  | Package         | Ship     |

|--------------|--------------|------|-----------------|----------|

| CSD87355Q5D  | 13-Inch Reel | 2500 | SON 5 mm × 6 mm | Tape and |

| CSD87355Q5DT | 7-Inch Reel  | 250  | Plastic Package | Reel     |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Typical Power Block Efficiency and Power Loss**

# **Table of Contents**

| 1 | Feat           | ures 1                                      |  |  |  |  |  |  |  |  |  |

|---|----------------|---------------------------------------------|--|--|--|--|--|--|--|--|--|

| 2 | Applications 1 |                                             |  |  |  |  |  |  |  |  |  |

| 3 | Des            | cription 1                                  |  |  |  |  |  |  |  |  |  |

| 4 | Rev            | ision History 2                             |  |  |  |  |  |  |  |  |  |

| 5 | Spe            | cifications 3                               |  |  |  |  |  |  |  |  |  |

|   | 5.1            | Absolute Maximum Ratings 3                  |  |  |  |  |  |  |  |  |  |

|   | 5.2            | Handling Ratings 3                          |  |  |  |  |  |  |  |  |  |

|   | 5.3            | Recommended Operating Conditions            |  |  |  |  |  |  |  |  |  |

|   | 5.4            | Thermal Information 3                       |  |  |  |  |  |  |  |  |  |

|   | 5.5            | Power Block Performance 3                   |  |  |  |  |  |  |  |  |  |

|   | 5.6            | Electrical Characteristics 4                |  |  |  |  |  |  |  |  |  |

|   | 5.7            | Typical Power Block Device Characteristics  |  |  |  |  |  |  |  |  |  |

|   | 5.8            | Typical Power Block MOSFET Characteristics7 |  |  |  |  |  |  |  |  |  |

| 6 | Арр            | lication and Implementation 10              |  |  |  |  |  |  |  |  |  |

|   | 6.1 | Application Information           | 10 |

|---|-----|-----------------------------------|----|

|   | 6.2 | Typical Application               | 13 |

| 7 | Lay | out                               | 15 |

|   | 7.1 | Layout Guidelines                 | 15 |

|   | 7.2 | Layout Example                    | 16 |

| 8 | Dev | ice and Documentation Support     | 17 |

|   | 8.1 | Community Resources               | 17 |

|   | 8.2 | Trademarks                        | 17 |

|   | 8.3 | Electrostatic Discharge Caution   | 17 |

|   |     | Glossary                          |    |

| 9 | Med | hanical, Packaging, and Orderable |    |

|   |     | rmation                           | 18 |

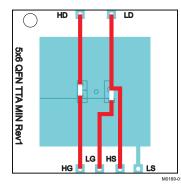

|   | 9.1 | Q5D Package Dimensions            | 18 |

|   | 9.2 | Land Pattern Recommendation       | 19 |

|   | 9.3 | Stencil Recommendation            | 19 |

|   |     |                                   |    |

# 4 Revision History

| CI | nanges from Original (March 2016) to Revision A                                        | Page |

|----|----------------------------------------------------------------------------------------|------|

| •  | Added footnote for Z <sub>DS(ON)</sub> in the <i>Electrical Characteristics</i> table. | 4    |

| •  | Deleted the Q5D Tape and Reel Information section                                      | 19   |

www.ti.com

#### CSD87355Q5D SLPS575A - MARCH 2016 - REVISED SEPTEMBER 2017

#### Specifications 5

#### 5.1 Absolute Maximum Ratings

$T_A = 25^{\circ}C$  (unless otherwise noted)<sup>(1)</sup>

|                                   |                                                | MIN  | MAX       | UNIT |  |

|-----------------------------------|------------------------------------------------|------|-----------|------|--|

|                                   | V <sub>IN</sub> to P <sub>GND</sub>            | -0.8 | 30        | V    |  |

|                                   | T <sub>G</sub> to T <sub>GR</sub>              | -8   | 10        | V    |  |

|                                   | -8                                             | 10   | V         |      |  |

| Pulsed current rating, ID         | (2)<br>M                                       |      | 120       | А    |  |

| Power dissipation, P <sub>D</sub> |                                                |      | 12        | W    |  |

| Auglanche energy E                | Sync FET, I <sub>D</sub> = 89 A, L = 0.1 mH    |      | 396       | mJ   |  |

| Avalanche energy $E_{AS}$         | Control FET, I <sub>D</sub> = 50 A, L = 0.1 mH |      | 125       | mJ   |  |

| Operating junction temp           | erature, T <sub>J</sub>                        | -55  | _55 150 ° |      |  |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings (1) only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability.

Pulse duration  $\leq$  50 µS. Duty cycle  $\leq$  0.01. (2)

#### 5.2 Handling Ratings

|                  |                           | MIN | MAX | UNIT |

|------------------|---------------------------|-----|-----|------|

| T <sub>stg</sub> | Storage temperature range | -55 | 150 | °C   |

#### 5.3 Recommended Operating Conditions

$T_A = 25^{\circ}$  (unless otherwise noted)

|                 |                                                   | MIN | MAX  | UNIT |

|-----------------|---------------------------------------------------|-----|------|------|

| $V_{GS}$        | Gate drive voltage                                | 4.5 | 10   | V    |

| V <sub>IN</sub> | Input supply voltage                              |     | 27   | V    |

| fsw             | Switching frequency $C_{BST} = 0.1 \ \mu F$ (min) | 200 | 1500 | kHz  |

|                 | Operating current                                 |     | 45   | А    |

| TJ              | Operating temperature                             |     | 125  | °C   |

### 5.4 Thermal Information

$T_A = 25^{\circ}C$  (unless otherwise stated)

|                 | THERMAL METRIC                                                            | MIN | TYP | MAX | UNIT |

|-----------------|---------------------------------------------------------------------------|-----|-----|-----|------|

| Р               | Junction-to-ambient thermal resistance (min Cu) <sup>(1)(2)</sup>         |     |     | 102 | °C/W |

| $R_{	hetaJA}$   | Junction-to-ambient thermal resistance (max Cu) <sup>(1)(2)</sup>         |     |     | 50  | °C/W |

| P               | Junction-to-case thermal resistance (top of package) <sup>(2)</sup>       |     |     | 20  | °C/W |

| $R_{\theta JC}$ | Junction-to-case thermal resistance (P <sub>GND</sub> pin) <sup>(2)</sup> |     |     | 2   | °C/W |

(1)

Device mounted on FR4 material with 1 inch<sup>2</sup> (6.45 cm<sup>2</sup>) Cu. R<sub> $\theta$ JC</sub> is determined with the device mounted on a 1 inch<sup>2</sup> (6.45 cm<sup>2</sup>), 2 oz. (0.071 mm thick) Cu pad on a 1.5 inches × 1.5 inches (2) (3.81 cm × 3.81 cm), 0.06 inch (1.52 mm) thick FR4 board. R<sub>0JC</sub> is specified by design while R<sub>0JA</sub> is determined by the user's board design.

#### 5.5 Power Block Performance

$T_A = 25^{\circ}$  (unless otherwise noted)

| PARAMETER                                            | TEST CONDITIONS                                    | MIN | TYP MA | X UNIT |

|------------------------------------------------------|----------------------------------------------------|-----|--------|--------|

| Power loss, P <sub>LOSS</sub> <sup>(1)</sup>         |                                                    |     | 2.8    | w      |

| V <sub>IN</sub> quiescent current, I <sub>QVIN</sub> | $T_G$ to $T_{GR}$ = 0 V , $B_G$ to $P_{GND}$ = 0 V |     | 10     | μA     |

Measurement made with six 10 µF (TDK C3216X5R1C106KT or equivalent) ceramic capacitors placed across V<sub>IN</sub> to P<sub>GND</sub> pins and (1)using a high current 5 V driver IC.

#### CSD87355Q5D

SLPS575A-MARCH 2016-REVISED SEPTEMBER 2017

www.ti.com

#### 5.6 Electrical Characteristics

$T_A = 25^{\circ}C$  (unless otherwise stated)

|                                    | DADAMETED                        | TEST CONDITIONS                                                        | Q1 C | Q1 CONTROL FET |      |      | SYNC F | ET   | UNIT |

|------------------------------------|----------------------------------|------------------------------------------------------------------------|------|----------------|------|------|--------|------|------|

|                                    | PARAMETER                        | TEST CONDITIONS                                                        | MIN  | ТҮР            | MAX  | MIN  | TYP    | MAX  | UNIT |

| STATIC CH                          | ARACTERISTICS                    |                                                                        |      |                |      |      |        |      |      |

| BV <sub>DSS</sub>                  | Drain-to-source voltage          | $V_{GS} = 0 V, I_{DS} = 250 \ \mu A$                                   | 30   |                |      | 30   |        |      | V    |

| I <sub>DSS</sub>                   | Drain-to-source leakage current  | $V_{GS} = 0 V, V_{DS} = 24 V$                                          |      |                | 1    |      |        | 1    | μA   |

| I <sub>GSS</sub>                   | Gate-to-source leakage current   | V <sub>DS</sub> = 0 V,<br>V <sub>GS</sub> = +10 / -8 V                 |      |                | 100  |      |        | 100  | nA   |

| V <sub>GS(th)</sub>                | Gate-to-source threshold voltage | $V_{DS} = V_{GS}$ , $I_{DS} = 250 \ \mu A$                             | 1.00 |                | 1.90 | 0.75 |        | 1.20 | V    |

| Z <sub>DS(ON)</sub> <sup>(1)</sup> | Drain-to-source ON impedance     |                                                                        |      | 3.9            |      |      | 0.9    |      | mΩ   |

| 9 <sub>fs</sub>                    | Transconductance                 | $V_{DS} = 3 V, I_{DS} = 20 A$                                          |      | 90             |      |      | 151    |      | S    |

| DYNAMIC (                          | CHARACTERISTICS                  |                                                                        |      |                |      |      |        |      |      |

| C <sub>ISS</sub>                   | Input capacitance                |                                                                        |      | 1430           | 1860 |      | 3570   | 4640 | pF   |

| C <sub>OSS</sub>                   | Output capacitance               | └ V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 15 V,<br>└ <i>f</i> = 1 MHz |      | 716            | 930  |      | 1730   | 2240 | pF   |

| C <sub>RSS</sub>                   | Reverse transfer capacitance     | - ) - I WH2                                                            |      | 25             | 32   |      | 52     | 67   | pF   |

| R <sub>G</sub>                     | Series gate resistance           |                                                                        |      | 0.6            | 1.2  |      | 0.7    | 1.4  | Ω    |

| Qg                                 | Gate charge total (4.5 V)        |                                                                        |      | 10.5           | 13.7 |      | 24.3   | 31.5 | nC   |

| Q <sub>gd</sub>                    | Gate charge – gate-to-drain      | V <sub>DS</sub> = 15 V,                                                |      | 2.3            |      |      | 4.1    |      | nC   |

| Q <sub>gs</sub>                    | Gate charge – gate-to-source     | I <sub>DS</sub> = 20 A                                                 |      | 3.2            |      |      | 5.6    |      | nC   |

| Q <sub>g(th)</sub>                 | Gate charge at V <sub>th</sub>   |                                                                        |      | 1.7            |      |      | 2.8    |      | nC   |

| Q <sub>OSS</sub>                   | Output charge                    | $V_{DS}=15~V,~V_{GS}=0~V$                                              |      | 18             |      |      | 40     |      | nC   |

| t <sub>d(on)</sub>                 | Turn on delay time               |                                                                        |      | 8              |      |      | 10     |      | ns   |

| t <sub>r</sub>                     | Rise time                        | V <sub>DS</sub> = 15 V, V <sub>GS</sub> = 4.5 V,                       |      | 18             |      |      | 14     |      | ns   |

| t <sub>d(off)</sub>                | Turn off delay time              | $I_{DS}$ = 20 A, $R_G$ = 2 $\Omega$                                    |      | 13             |      |      | 27     |      | ns   |

| t <sub>f</sub>                     | Fall time                        |                                                                        |      | 3              |      |      | 6      |      | ns   |

| DIODE CHA                          | ARACTERISTICS                    |                                                                        |      |                |      |      |        |      |      |

| V <sub>SD</sub>                    | Diode forward voltage            | $I_{DS} = 20 \text{ A}, V_{GS} = 0 \text{ V}$                          |      | 0.8            | 1.0  |      | 0.8    | 1.0  | V    |

| Q <sub>rr</sub>                    | Reverse recovery charge          | V <sub>dd</sub> = 17 V, I <sub>F</sub> = 20 A,                         |      | 43             |      |      | 82     |      | nC   |

| t <sub>rr</sub>                    | Reverse recovery time            | di/dt = 300 A/µs                                                       |      | 23.8           |      |      | 32.3   |      | ns   |

(1) Equivalent based on application testing. See *Application and Implementation* section for details.

$\begin{array}{l} Max \; R_{\theta JA} = 50^{\circ}C/W \\ when mounted on \\ 1 \; inch^2 \; (6.45 \; cm^2) \; of \\ 2 \; oz. \; (0.071 \text{-mm thick}) \\ Cu. \end{array}$

Max  $R_{\theta JA} = 102^{\circ}C/W$ when mounted on minimum pad area of 2 oz. (0.071-mm thick) Cu.

#### 5.7 Typical Power Block Device Characteristics

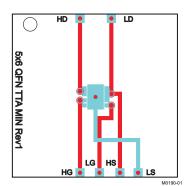

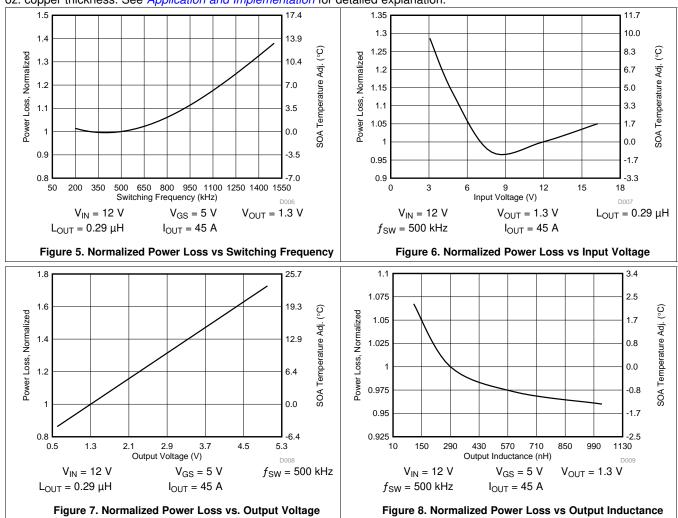

$T_J = 125^{\circ}$ C, unless stated otherwise. The Typical Power Block System Characteristic curves Figure 3, , and Figure 4 are based on measurements made on a PCB design with dimensions of 4" (W) × 3.5" (L) × 0.062" (H) and 6 copper layers of 1-oz. copper thickness. See *Application and Implementation* for detailed explanation.

### **Typical Power Block Device Characteristics (continued)**

$T_J = 125^{\circ}$ C, unless stated otherwise. The Typical Power Block System Characteristic curves Figure 3, , and Figure 4 are based on measurements made on a PCB design with dimensions of 4" (W) × 3.5" (L) × 0.062" (H) and 6 copper layers of 1-oz. copper thickness. See *Application and Implementation* for detailed explanation.

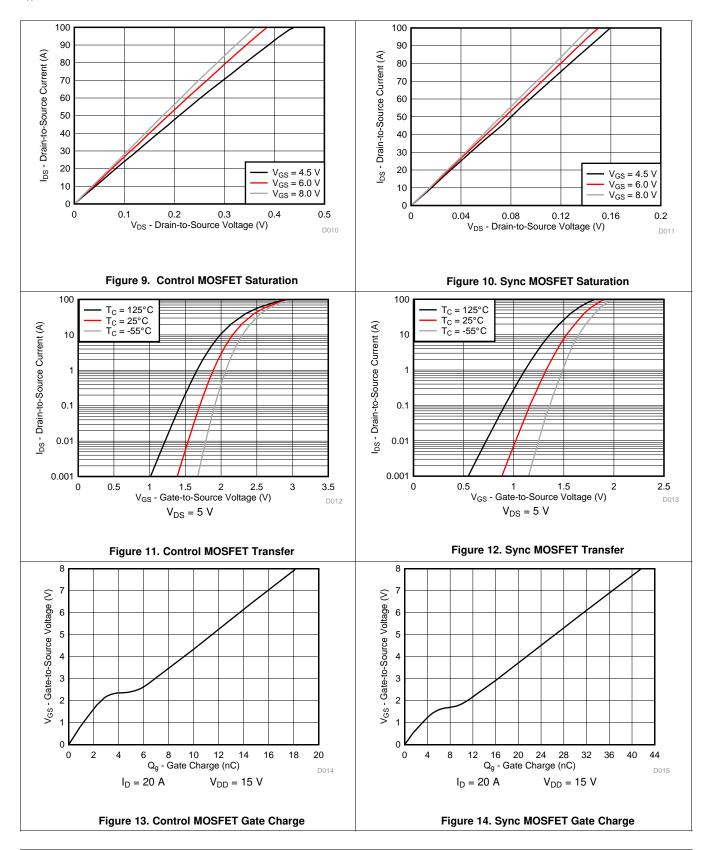

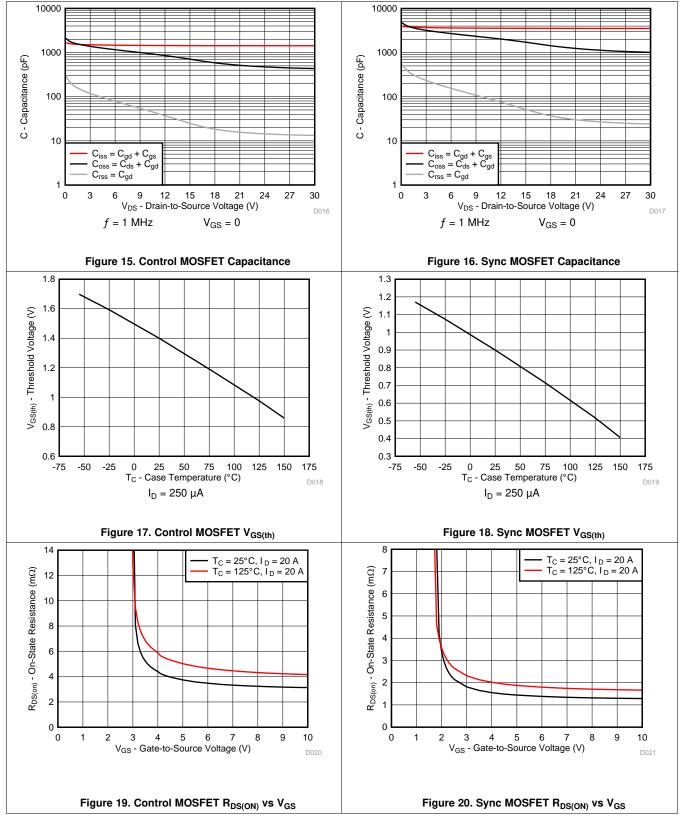

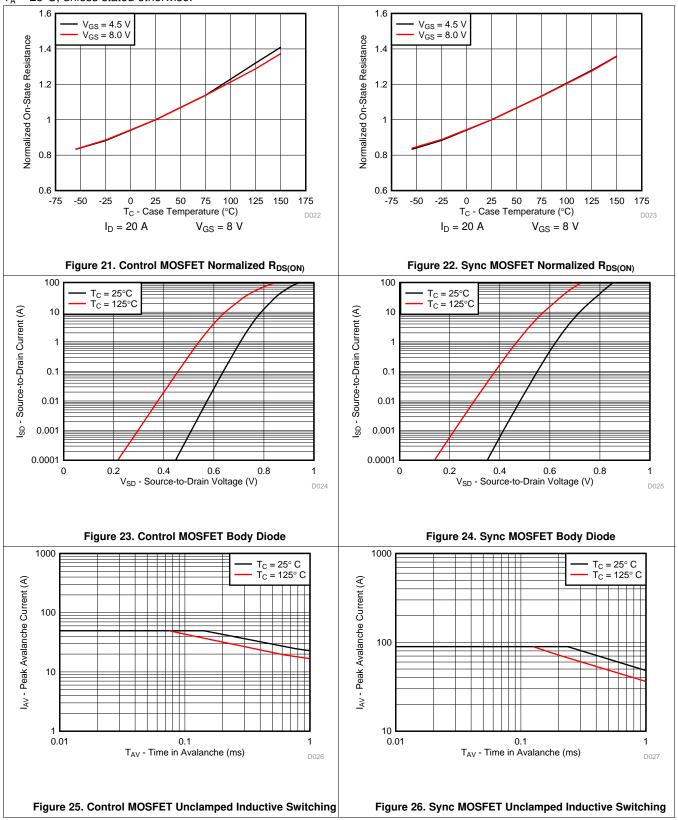

### 5.8 Typical Power Block MOSFET Characteristics

$T_A = 25^{\circ}C$ , unless stated otherwise.

## **Typical Power Block MOSFET Characteristics (continued)**

#### $T_A = 25^{\circ}C$ , unless stated otherwise.

#### **Typical Power Block MOSFET Characteristics (continued)**

$T_A = 25^{\circ}C$ , unless stated otherwise.

### 6 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

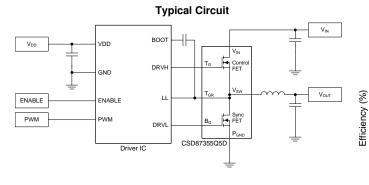

#### 6.1 Application Information

The CSD87355Q5D NexFET power block is an optimized design for synchronous buck applications using 5-V gate drive. The Control FET and Sync FET silicon are parametrically tuned to yield the lowest power loss and highest system efficiency. As a result, a new rating method is needed which is tailored towards a more systems centric environment. System level performance curves such as Power Loss, Safe Operating Area, and normalized graphs allow engineers to predict the product performance in the actual application.

#### 6.1.1 Equivalent System Performance

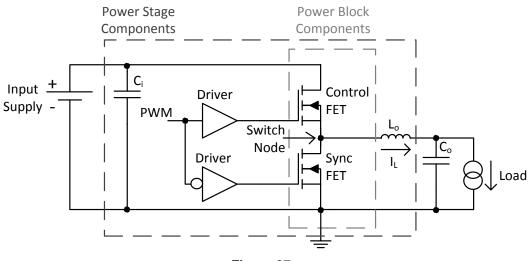

Many of today's high performance computing systems require low power consumption in an effort to reduce system operating temperatures and improve overall system efficiency. This has created a major emphasis on improving the conversion efficiency of today's Synchronous Buck Topology. In particular, there has been an emphasis in improving the performance of the critical Power Semiconductor in the Power Stage of this application (see Figure 27). As such, optimization of the power semiconductors in these applications, needs to go beyond simply reducing  $R_{DS(ON)}$ .

Figure 27.

#### **Application Information (continued)**

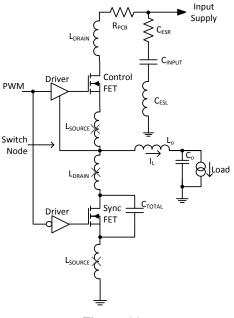

The CSD87355Q5D is part of TI's Power Block product family which is a highly optimized product for use in a synchronous buck topology requiring high current, high efficiency, and high frequency. It incorporates TI's latest generation silicon which has been optimized for switching performance, as well as minimizing losses associated with  $Q_{GD}$ ,  $Q_{GS}$ , and  $Q_{RR}$ . Furthermore, TI's patented packaging technology has minimized losses by nearly eliminating parasitic elements between the Control FET and Sync FET connections (see Figure 28). A key challenge solved by TI's patented packaging technology is the system level impact of Common Source Inductance (CSI). CSI greatly impedes the switching characteristics of any MOSFET which in turn increases switching losses and reduces system efficiency. As a result, the effects of CSI need to be considered during the MOSFET selection process. In addition, standard MOSFET switching loss equations used to predict system efficiency need to be modified in order to account for the effects of CSI. Further details behind the effects of CSI and modification of switching loss equations are outlined in TI's Application Note SLPA009.

Figure 28.

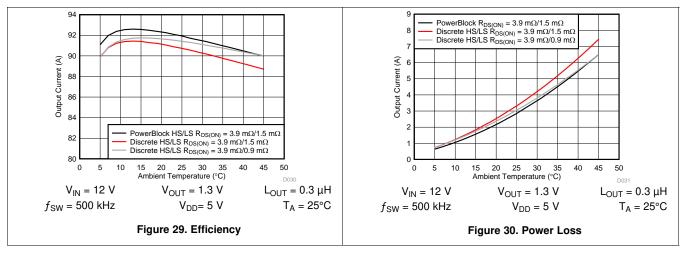

The combination of TI's latest generation silicon and optimized packaging technology has created a benchmarking solution that outperforms industry standard MOSFET chipsets of similar  $R_{DS(ON)}$  and MOSFET chipsets with lower  $R_{DS(ON)}$ . Figure 29 and Figure 30 compare the efficiency and power loss performance of the CSD87355Q5D versus industry standard MOSFET chipsets commonly used in this type of application. This comparison purely focuses on the efficiency and generated loss of the power semiconductors only. The performance of CSD87355Q5D clearly highlights the importance of considering the Effective AC On-Impedance ( $Z_{DS(ON)}$ ) during the MOSFET selection process of any new design. Simply normalizing to traditional MOSFET  $R_{DS(ON)}$  specifications is not an indicator of the actual in-circuit performance when using TI's Power Block technology.

#### CSD87355Q5D SLPS575A – MARCH 2016 – REVISED SEPTEMBER 2017

www.ti.com

#### **Application Information (continued)**

Table 1 compares the traditional DC measured  $R_{DS(ON)}$  of CSD87355Q5D versus its  $Z_{DS(ON)}$ . This comparison takes into account the improved efficiency associated with TI's patented packaging technology. As such, when comparing TI's Power Block products to individually packaged discrete MOSFETs or dual MOSFETs in a standard package, the in-circuit switching performance of the solution must be considered. In this example, individually packaged discrete MOSFETs or dual MOSFETs in a standard package would need to have DC measured  $R_{DS(ON)}$  values that are equivalent to CSD87355Q5D's  $Z_{DS(ON)}$  value in order to have the same efficiency performance at full load. Mid to light-load efficiency will still be lower with individually packaged discrete MOSFETs in a standard package.

#### Table 1. Comparison of R<sub>DS(ON)</sub> vs Z<sub>DS(ON)</sub>

| PARAMETER                                                      | HS  |     | LS  |     |      |

|----------------------------------------------------------------|-----|-----|-----|-----|------|

| PARAMETER                                                      | ТҮР | MAX | ТҮР | MAX | UNIT |

| Effective AC On-Impedance $Z_{DS(ON)}$ (V <sub>GS</sub> = 5 V) | 3.9 | -   | 0.9 | -   | mΩ   |

| DC Measured $R_{DS(ON)}$ (V <sub>GS</sub> = 4.5 V)             | 3.9 | 4.7 | 1.5 | 1.8 | mΩ   |

#### 6.1.2 Power Loss Curves

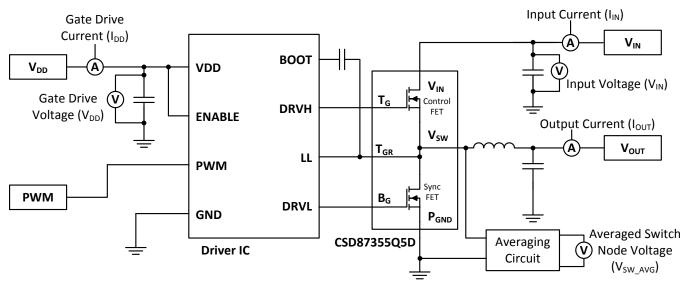

MOSFET centric parameters such as  $R_{DS(ON)}$  and  $Q_{gd}$  are needed to estimate the loss generated by the devices. In an effort to simplify the design process for engineers, Texas Instruments has provided measured power loss performance curves. Figure 1 plots the power loss of the CSD87355Q5D as a function of load current. This curve is measured by configuring and running the CSD87355Q5D as it would be in the final application (see Figure 31). The measured power loss is the CSD87355Q5D loss and consists of both input conversion loss and gate drive loss. Equation 1 is used to generate the power loss curve.

$$V_{IN} \times I_{IN}$$

+  $(V_{DD} \times I_{DD}) - (V_{SW_{AVG}} \times I_{OUT})$  = Power Loss

(1)

The power loss curve in Figure 1 is measured at the maximum recommended junction temperatures of 125°C under isothermal test conditions.

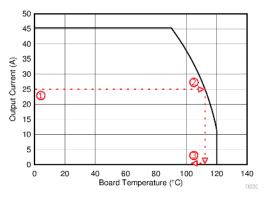

#### 6.1.3 Safe Operating Curves (SOA)

The SOA curves in the CSD87355Q5D data sheet provides guidance on the temperature boundaries within an operating system by incorporating the thermal resistance and system power loss. Figure 3 to Figure 4 outline the temperature and airflow conditions required for a given load current. The area under the curve dictates the safe operating area. All the curves are based on measurements made on a PCB design with dimensions of 4" (W)  $\times 3.5"$  (L)  $\times 0.062"$  (T) and 6 copper layers of 1-oz. copper thickness.

#### 6.1.4 Normalized Curves

The normalized curves in the CSD87355Q5D data sheet provides guidance on the Power Loss and SOA adjustments based on their application specific needs. These curves show how the power loss and SOA boundaries will adjust for a given set of system conditions. The primary Y-axis is the normalized change in power loss and the secondary Y-axis is the change is system temperature required in order to comply with the SOA curve. The change in power loss is a multiplier for the Power Loss curve and the change in temperature is subtracted from the SOA curve.

#### 6.2 Typical Application

Figure 31.

CSD87355Q5D

SLPS575A-MARCH 2016-REVISED SEPTEMBER 2017

www.ti.com

#### **Typical Application (continued)**

#### 6.2.1 Design Example: Calculating Power Loss and SOA

The user can estimate product loss and SOA boundaries by arithmetic means (see *Operating Conditions*). Though the Power Loss and SOA curves in this data sheet are taken for a specific set of test conditions, the following procedure will outline the steps the user should take to predict product performance for any set of system conditions.

#### 6.2.2 Operating Conditions

- Output Current = 25 A

- Input Voltage = 7 V

- Output Voltage = 1.4 V

- Switching Frequency = 800 kHz

- Inductor = 0.2 µH

#### 6.2.2.1 Calculating Power Loss

- Power Loss at 25 A = 3.62 W (Figure 1)

- Normalized Power Loss for input voltage ≈ 0.99 (Figure 6)

- Normalized Power Loss for output voltage ≈ 1.02 (Figure 7)

- Normalized Power Loss for switching frequency ≈ 1.06 (Figure 5)

- Normalized Power Loss for output inductor ≈ 1.03 (Figure 8)

- Final calculated Power Loss = 3.62 W × 0.99 × 1.02 × 1.06 × 1.03 ≈ 3.99 W

#### 6.2.2.2 Calculating SOA Adjustments

- SOA adjustment for input voltage ≈ -0.24<sup>o</sup>C (Figure 6)

- SOA adjustment for output voltage  $\approx 0.63^{\circ}$ C (Figure 7)

- SOA adjustment for switching frequency ≈ 2.12°C (Figure 5)

- SOA adjustment for output inductor ≈ 0.91°C (Figure 8)

- Final calculated SOA adjustment = -0.24 + 0.63 + 2.12 + 0.91 ≈ 3.42C

In the previous design example, the estimated power loss of the CSD87355Q5D would increase to 4 W. In addition, the maximum allowable board and/or ambient temperature would have to decrease by 3.4°C. Figure 32 graphically shows how the SOA curve would be adjusted accordingly.

- 1. Start by drawing a horizontal line from the application current to the SOA curve.

- 2. Draw a vertical line from the SOA curve intercept down to the board/ambient temperature.

- 3. Adjust the SOA board/ambient temperature by subtracting the temperature adjustment value.

In the design example, the SOA temperature adjustment yields a reduction in allowable board/ambient temperature of 3.4°C. In the event the adjustment value is a negative number, subtracting the negative number would yield an increase in allowable board/ambient temperature.

Figure 32. Power Block SOA

### 7 Layout

#### 7.1 Layout Guidelines

There are two key system-level parameters that can be addressed with a proper PCB design: electrical and thermal performance. Properly optimizing the PCB layout will yield maximum performance in both areas. The following sections provide a brief description on how to address each parameter.

#### 7.1.1 Electrical Performance

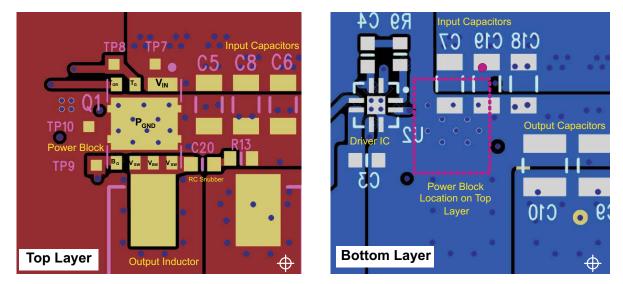

The Power Block has the ability to switch voltages at rates greater than 10 kV/µs. Take special care with the PCB layout design and placement of the input capacitors, Driver IC, and output inductor.

- The placement of the input capacitors relative to the Power Block's VIN and PGND pins should have the highest priority during the component placement routine. It is critical to minimize these node lengths. As such, ceramic input capacitors need to be placed as close as possible to the VIN and PGND pins (see Figure 33). The example in Figure 33 uses 6 × 10-µF ceramic capacitors (TDK Part # C3216X5R1C106KT or equivalent). Notice there are ceramic capacitors on both sides of the board with an appropriate amount of vias interconnecting both layers. In terms of priority of placement next to the Power Block, C5, C7, C19, and C8 should follow in order.

- The Driver IC should be placed relatively close to the Power Block Gate pins. T<sub>G</sub> and B<sub>G</sub> should connect to the outputs of the Driver IC. The T<sub>GR</sub> pin serves as the return path of the high-side gate drive circuitry and should be connected to the Phase pin of the IC (sometimes called LX, LL, SW, PH, etc.). The bootstrap capacitor for the Driver IC will also connect to this pin.

- The switching node of the output inductor should be placed relatively close to the Power Block VSW pins. Minimizing the node length between these two components will reduce the PCB conduction losses and actually reduce the switching noise level.

- In the event the switch node waveform exhibits ringing that reaches undesirable levels, the use of a Boost Resistor or RC snubber can be an effective way to reduce the peak ring level. The recommended Boost Resistor value will range between 1  $\Omega$  to 4.7  $\Omega$  depending on the output characteristics of Driver IC used in conjunction with the Power Block. The RC snubber values can range from 0.5  $\Omega$  to 2.2  $\Omega$  for the R and 330 pF to 2200 pF for the C. Refer to TI App Note SLUP100 for more details on how to properly tune the RC snubber values. The RC snubber should be placed as close as possible to the Vsw node and PGND see Figure 33. <sup>(1)</sup>

#### 7.1.2 Thermal Considerations

The Power Block has the ability to use the GND planes as the primary thermal path. As such, the use of thermal vias is an effective way to pull away heat from the device and into the system board. Concerns of solder voids and manufacturability problems can be addressed by the use of three basic tactics to minimize the amount of solder attach that will wick down the via barrel:

- Intentionally space out the vias from each other to avoid a cluster of holes in a given area.

- Use the smallest drill size allowed in your design. The example in Figure 33 uses vias with a 10 mil drill hole and a 16 mil capture pad.

- Tent the opposite side of the via with solder-mask.

In the end, the number and drill size of the thermal vias should align with the end user's PCB design rules and manufacturing capabilities.

<sup>(1)</sup> Keong W. Kam, David Pommerenke, "EMI Analysis Methods for Synchronous Buck Converter EMI Root Cause Analysis", University of Missouri – Rolla

TEXAS INSTRUMENTS

SLPS575A-MARCH 2016-REVISED SEPTEMBER 2017

www.ti.com

### 7.2 Layout Example

Figure 33. Recommended PCB Layout (Top View)

#### 8 Device and Documentation Support

#### 8.1 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 8.2 Trademarks

NexFET, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 8.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 8.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

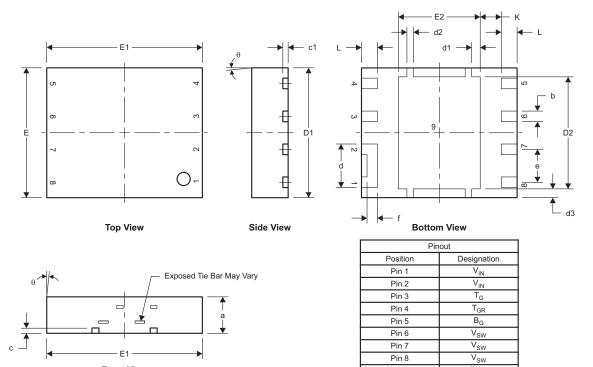

#### Mechanical, Packaging, and Orderable Information 9

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### 9.1 Q5D Package Dimensions

Pin 8

Pin 9

MILLIMETERS INCHES DIM MIN MAX MIN MAX 1.40 1.5 0.055 0.059 а 0.014 0.018 0.360 0.460 b с 0.150 0.250 0.006 0.010 0.250 0.010 c1 0.150 0.006 1.630 1.730 0.064 0.068 d 0.280 0.380 0.015 d1 0.011 d2 0.200 0.300 0.008 0.012 0.012 d3 0.291 0.391 0.015 4.900 5.100 0.201 D1 0.193 D2 4.269 4.369 0.168 0.172 Е 4.900 5.100 0.193 0.201 5.900 E1 6.100 0.232 0.240 3.106 E2 3.206 0.122 0.126 е 1.27 TYP 0.050 f 0.396 0.496 0.016 0.020 0.510 L 0.710 0.020 0.028 0.00 θ \_\_\_\_ \_\_\_\_ Κ 0.812 0.032

Front View

M0187-01

$\mathsf{P}_{\mathsf{GND}}$

18 Submit Documentation Feedback

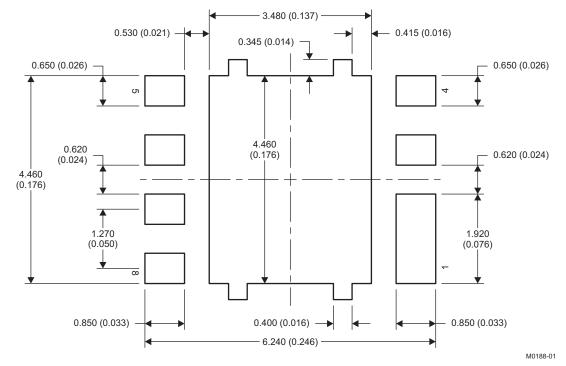

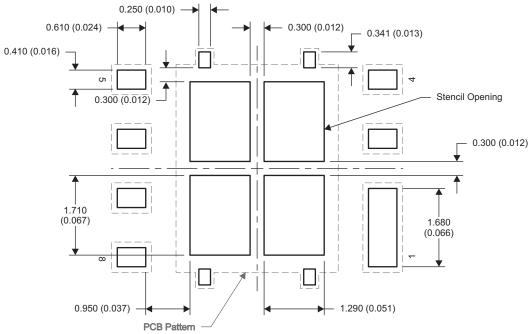

#### 9.2 Land Pattern Recommendation

NOTE: Dimensions are in mm (inches).

#### 9.3 Stencil Recommendation

M0208-01

NOTE: Dimensions are in mm (inches).

For recommended circuit layout for PCB designs, see application note SLPA005 – *Reducing Ringing Through PCB Layout Techniques*.

10-Dec-2020

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)        | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|------------------------|-------------------------------|----------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                        | (6)                           |                      |              |                         |         |

| CSD87355Q5D      | ACTIVE        | LSON-CLIP    | DQY                | 8    | 2500           | RoHS-Exempt<br>& Green | NIPDAU                        | Level-1-260C-UNLIM   | -55 to 150   | 87355D                  | Samples |

| CSD87355Q5DT     | ACTIVE        | LSON-CLIP    | DQY                | 8    | 250            | RoHS-Exempt<br>& Green | NIPDAU                        | Level-1-260C-UNLIM   | -55 to 150   | 87355D                  | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE OPTION ADDENDUM

10-Dec-2020

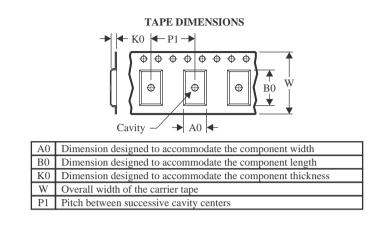

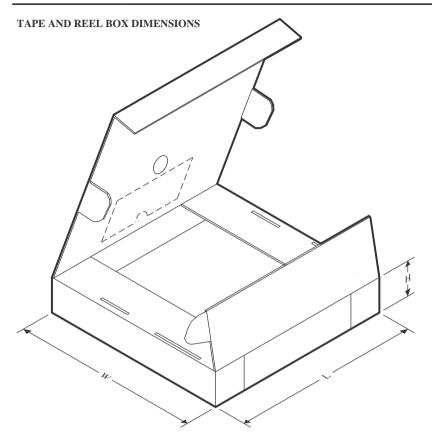

### TAPE AND REEL INFORMATION

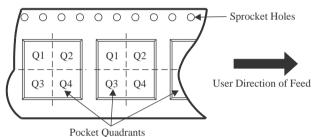

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           | t.               |

|-----------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| CSD87355Q5D                 | LSON-<br>CLIP   | DQY                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 6.3        | 1.8        | 8.0        | 12.0      | Q2               |

| CSD87355Q5DT                | LSON-<br>CLIP   | DQY                | 8 | 250  | 180.0                    | 12.4                     | 5.3        | 6.3        | 1.8        | 8.0        | 12.0      | Q2               |

# PACKAGE MATERIALS INFORMATION

20-Apr-2023

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CSD87355Q5D  | LSON-CLIP    | DQY             | 8    | 2500 | 346.0       | 346.0      | 33.0        |

| CSD87355Q5DT | LSON-CLIP    | DQY             | 8    | 250  | 182.0       | 182.0      | 20.0        |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated