# **AS3953B**

## 14443 High Speed Passive Tag Interface

## **General Description**

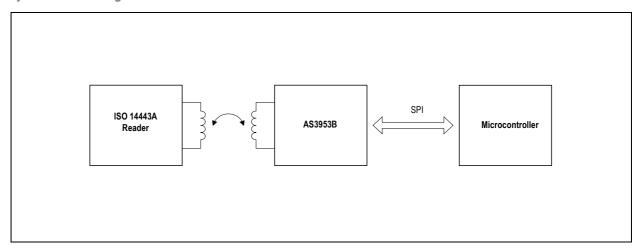

The AS3953B NFC interface IC (NFiC) delivers low cost, ultra low power NFC forum functionality to multiple different applications. The AS3953B is a analog front-end with integrated 14443A data framing and SPI interface. It is designed to create a fast data link between an ISO 14443A reader device (PCD) and a microcontroller. The AS3953B is **passively powered** meaning that it can be supplied from the PCD magnetic field, eliminating the need of a continual external supply. This makes the AS3953B perfect for wireless communication to a low-power battery powered device.

The AS3953B is used with an appropriate antenna coil connected to the terminals LC1 and LC2, and behaves as a normal passive ISO 144443A tag (PICC). After the anti-collision protocol is passed, the PCD sends a **Wake-Up** command, which wakes up the microcontroller by sending an interrupt. From this point onwards, the AS3953B serves as a data link between the microcontroller and the PCD. AS3953B can also operate as NFCIP-1 target at 106kbit/s.

The AS3953B includes an onboard EEPROM that can be accessed either from the PCD or from the microcontroller via the SPI interface. This built-in flexibility makes it ideal for two types of applications:

- Where personalization data is programmed by the PCD (even in case the SPI side is not powered) and it is later read by microcontroller through SPI interface.

- Where log data is stored periodically by the microcontroller and can then be read by the PCD even when the microcontroller is not powered.

A regulated power supply voltage extracted from the PCD field is also available on a pin and can be used as power supply for external circuitry. For example, an external microcontroller and a sensor could be powered from the PCD field combined with pass through data rates up to 848kbit/s, which means the AS3953B is ideal for contactless passive programming of MCU systems. The AS3953B can also operate as a stand-alone ISO 14443A tag.

The AS3953B supports ISO 14443A up to Level-4, meaning a contactless smart card or an NFC forum compatible tag (Tag Type 4) can be built. Having a NFC Forum compatible tag interface allows the AS3953B to be used in an application where a standard NFC enabled phone is used as a PCD.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of AS3953B,14443 High Speed Passive Tag Interface are listed below:

Figure 1: Added Value of Using AS3953B

| Benefits                                                                                                                                                      | Features                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| NFC Forum compliance for full interoperability                                                                                                                | ISO 14443A compliant to Level-4                                                     |

| Data rate transmission up to the<br>maximum allowed by ISO 14443A<br>compliance                                                                               | <ul><li>Bit rates from 106 kbit/s till 848 kbit/s</li><li>7 byte UID</li></ul>      |

| ECMA-340 / ISO/IEC_18092 compliance                                                                                                                           | NFCIP-1 target at 106 kbit/s                                                        |

| Internal user memory for standalone application                                                                                                               | 1k bit EEPROM (108 bytes of user memory)                                            |

| Allows zero-power standby                                                                                                                                     | Configurable wake-up interrupt (after tag is selected or using proprietary command) |

| Enables long battery life time, or<br>battery-less designs                                                                                                    | Powered from external magnetic field with the possibility to<br>draw up to 5mA      |

| Allows supply of external circuitry                                                                                                                           | User configurable regulated voltage extracted from external magnetic field          |

| Easy and fast antenna design and impedance matching                                                                                                           | Integrated resonant capacitor                                                       |

| Guarantees no reset during reader (PCD) modulation                                                                                                            | Integrated buffer capacitor                                                         |

| <ul> <li>Design flexibility, easy integration.</li> <li>Fits requirements for various embedded applications and manage of external microcontroller</li> </ul> | 4-wire Serial Peripheral Interface (SPI) with 32 byte FIFO                          |

| Fits supply requirements for various applications, including industrial                                                                                       | Wide SPI power supply range (1.65V to 3.6V)                                         |

| Flexibility for wide range of applications                                                                                                                    | • Wide temperature range: -40°C to 85°C                                             |

| Small outline, compatibility to common<br>inlay and card manufacturing lines,<br>surface-mount assembly                                                       | Available as sorted wafer and Thin Wafer Level Chip Scale Package                   |

Page 2ams DatasheetDocument Feedback[v1-04] 2016-Jan-07

## **Applications**

The device is ideal for applications like

- Passive wake-up

- Multipurpose HF interface to a controller

- Low power or passive programming

- Ultra low power data logger

- RFID programmable configuration EEPROM, ISO 14443A smart card, NFC Forum tag type 4

- Bluetooth and Wi-Fi pairing

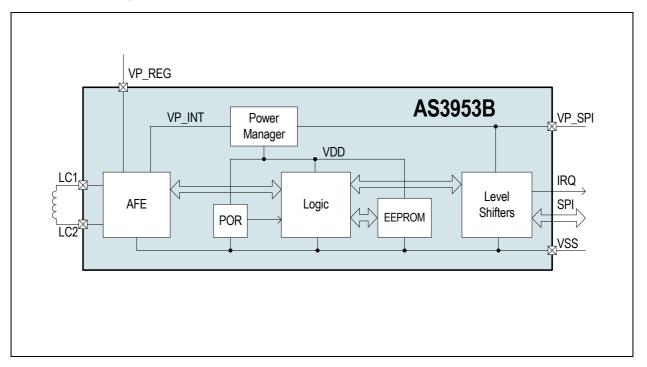

## **Block Diagram**

The functional blocks of this device are shown below:

Figure 2: AS3953B Block Diagram

ams Datasheet Page 3

[v1-04] 2016-Jan-07

Document Feedback

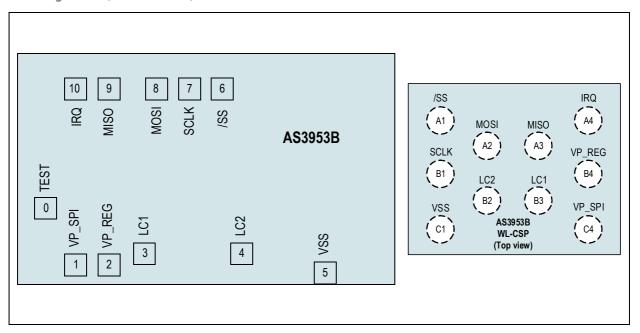

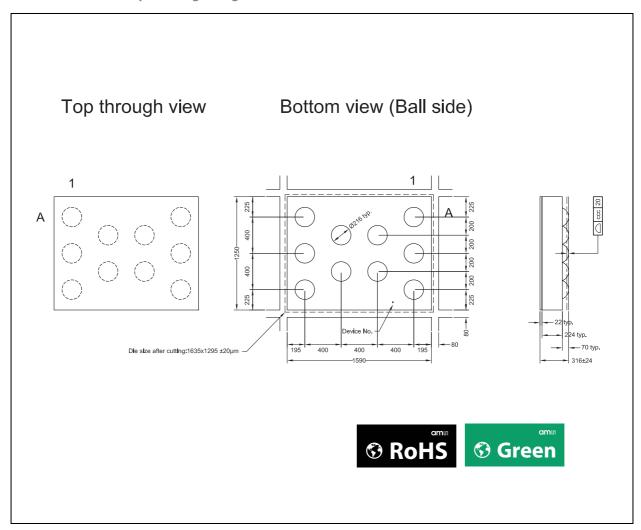

## **Pin Assignment**

Figure 3: Pin Assignment (Bottom View)

Figure 4: Pin Description

| Pin Number<br>Sorted Die | Pin Name    | Pin Type                     | Description                                      |  |  |  |  |

|--------------------------|-------------|------------------------------|--------------------------------------------------|--|--|--|--|

| 0                        | TEST        | Internal use                 | No connection                                    |  |  |  |  |

| 1                        | VP_SPI      | Supply pad                   | Positive supply of SPI interface                 |  |  |  |  |

| 2                        | VP_REG      | Analog output                | Regulator output                                 |  |  |  |  |

| 3                        | LC1         | Analog I/O                   | Connection to tag coil                           |  |  |  |  |

| 4                        | LC2         | Allalog I/O                  | Connection to tag con                            |  |  |  |  |

| 5                        | VSS         | Supply pad                   | Ground, die substrate potential                  |  |  |  |  |

| 6                        | /SS         |                              | Serial Peripheral Interface enable (active low)  |  |  |  |  |

| 7                        | SCLK        | Digital input                | Serial Peripheral Interface clock                |  |  |  |  |

| 8                        | MOSI        |                              | Serial Peripheral Interface data input           |  |  |  |  |

| 9                        | MISO        | Digital output /<br>tristate | Serial Peripheral Interface data output          |  |  |  |  |

| 10                       | IRQ         | Digital output               | Interrupt request output (active high)           |  |  |  |  |

| -                        | Exposed Pad | Supply                       | Exposed pad to be connected to ground (optional) |  |  |  |  |

Page 4ams DatasheetDocument Feedback[v1-04] 2016-Jan-07

## **Absolute Maximum Ratings**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5: Absolute Maximum Ratings

| Symbol                 | Parameter                                                                | Min         | Max         | Units     | Comments                                   |  |  |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------|-------------|-------------|-----------|--------------------------------------------|--|--|--|--|--|--|--|

|                        | Electrical Parameters                                                    |             |             |           |                                            |  |  |  |  |  |  |  |

| VDD                    | DC supply voltage                                                        | -0.5        | 5           | V         |                                            |  |  |  |  |  |  |  |

| Vin                    | Input pin voltage except LC1 and LC2                                     | -0.5        | 5           | V         |                                            |  |  |  |  |  |  |  |

|                        | Input pin voltage pins LC1 and LC2                                       | -0.5        | 6.5         | V         |                                            |  |  |  |  |  |  |  |

|                        | Peak current induced on pins<br>LC1 and LC2                              |             | 100         | mA        |                                            |  |  |  |  |  |  |  |

| I <sub>scr</sub>       | Input current<br>(latchup immunity)                                      | -100        | 100         | mA        | Norm: Jedec 78                             |  |  |  |  |  |  |  |

|                        | Elec                                                                     | trostatic [ | Discharge   |           |                                            |  |  |  |  |  |  |  |

| ESD <sub>HBM</sub>     | Electrostatic discharge<br>(human body model)                            | <u> </u>    | -2          | kV        | Norm: MIL 883 E method<br>3015             |  |  |  |  |  |  |  |

|                        | Temperature R                                                            | anges and   | l Storage C | onditions |                                            |  |  |  |  |  |  |  |

| T <sub>strg</sub>      | Storage temperature                                                      | -55         | 125         | ۰C        |                                            |  |  |  |  |  |  |  |

| RH <sub>NC</sub>       | Relative humidity non-condensing                                         | 5           | 85          | %         |                                            |  |  |  |  |  |  |  |

| MSL                    | Moisture sensitivity level                                               |             | 1           |           | Maximum floor life time of unlimited hours |  |  |  |  |  |  |  |

| t <sub>strg_DOF</sub>  | Storage time for DOF/dies or wafers on foil                              |             | 3           | months    | Refer to indicated date of packing         |  |  |  |  |  |  |  |

| T <sub>strg_DOF</sub>  | Storage temperature for DOF/dies or wafers on foil                       | 18          | 24          | °C        |                                            |  |  |  |  |  |  |  |

| RH <sub>open_DOF</sub> | Relative humidity for DOF/dies<br>or wafers on foil in open<br>package   |             | 15          | %         | Opened package                             |  |  |  |  |  |  |  |

| RH <sub>Unopen_</sub>  | Relative humidity for DOF/dies<br>or wafers on foil in closed<br>package | 40          | 60          | %         | Unopened package                           |  |  |  |  |  |  |  |

ams Datasheet Page 5

[v1-04] 2016-Jan-07 Document Feedback

## **Electrical Characteristics**

All in this specification defined tolerances for external components need to be assured over the whole operation conditions range and also over lifetime.

Figure 6: **Operating Conditions**

| Symbol              | Parameter              | Min  | Тур | Max | Units | Note                                              |

|---------------------|------------------------|------|-----|-----|-------|---------------------------------------------------|

| I <sub>lim</sub>    | Limiter current        |      |     | 30  | mA    | Till this current limiter clamps VLC1-LC2 to 5.0V |

| V <sub>VP_SPI</sub> | CDI manuar aumah       | 1.65 |     | 3.6 | V     | When logic powered from RFID interface            |

| * VP_SPI            | SPI power supply       | 1.8  |     | 3.6 | V     | When logic powered from VP_SPI interface          |

| Тамв                | Ambient<br>temperature | -40  |     | 85  | °C    |                                                   |

## DC/AC Characteristics for Digital Inputs and Outputs

Figure 7: **CMOS Inputs, Valid for Input Pins /SS, MOSI, SCLK**

| Symbol | Parameter                | Min          | Тур | Max              | Units | Note |

|--------|--------------------------|--------------|-----|------------------|-------|------|

| VIH    | High level input voltage | 0.7 * VP_SPI |     |                  | V     |      |

| VIL    | Low level input voltage  |              |     | 0.3 * VP_<br>SPI | V     |      |

| ILEAK  | Input leakage current    |              |     | 1                | μΑ    |      |

Page 6 ams Datasheet [v1-04] 2016-Jan-07

Figure 8: CMOS Outputs, Valid for Output Pins MISO, IRQ

| Symbol | Parameter                        | Min              | Тур | Max             | Units | Note                                                                                                                    |

|--------|----------------------------------|------------------|-----|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------|

| Vон    | High level output voltage        | 0.85 *<br>VP_SPI |     |                 | V     | Isource = 1mA                                                                                                           |

| Vol    | Low level output voltage         |                  |     | 0.15*<br>VP_SPI | V     | VP_SPI = 3V                                                                                                             |

| CL     | Capacitive load                  |                  |     | 50              | pF    |                                                                                                                         |

| Ro     | Output resistance                |                  | 200 | 400             | Ω     |                                                                                                                         |

| Rpd    | Pull-down resistance<br>pad MOSI |                  | 10  |                 | kΩ    | Pull-down can be<br>enabled while MISO<br>output is in tristate. The<br>activation is controlled<br>by register setting |

ams Datasheet Page 7

[v1-04] 2016-Jan-07

Document Feedback

## **Electrical Specification**

Figure 9: VP\_SPI = 3.0 V, Temperature 25°C (unless noted otherwise)

| Symbol               | Parameter                      | Min    | Тур | Max  | Units    | Note                                                                                                                                                                |

|----------------------|--------------------------------|--------|-----|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>SB_SPI</sub>  | Standby consumption            |        | 65  | 100  | nA       | @ 25°C; RF field not applied                                                                                                                                        |

| .2R <sup>-</sup> 251 | on VP_SPI                      | 1.8    | 2.2 | 2.7  | μΑ       | @ 25°C; RF field applied                                                                                                                                            |

| V <sub>LIM</sub>     | Limiter voltage                |        | 5.2 | 5.7  | V        | I <sub>LC</sub> = 30mA (DC)                                                                                                                                         |

| I <sub>S</sub>       | Supply current                 |        | 250 |      | μΑ       | Internal supply current<br>measured in test mode on<br>VREC, 13.56 MHz alternative<br>pulses with amplitude 2Vpp,<br>negative peak at VSS, forced<br>to LC1 and LC2 |

| V <sub>VP_REG</sub>  | Regulated supply voltage       | 1.65   | 1.8 | 2.01 | V        | Set to 1.8V in EEPROM<br>Configuration word                                                                                                                         |

| V <sub>HF_PON</sub>  | HF_PON threshold (rising VREG) |        | 2.3 |      | V        | Guaranteed by design only                                                                                                                                           |

| V <sub>POR_HY</sub>  | HF_PON hysteresis              |        | 0.8 |      | V        |                                                                                                                                                                     |

| V <sub>MOD</sub>     | Modulator ON voltage           |        | 1.2 |      | V        | I <sub>LC</sub> = 1mA                                                                                                                                               |

| ▼ MOD                | drop                           |        | 3.3 |      | <b>,</b> | I <sub>LC</sub> = 30mA                                                                                                                                              |

| C <sub>R</sub>       | Resonance capacitor            | 25.2   | 28  | 30.8 | pF       | Measured at 10MHz, 3.0Vpp<br>(2.5Vpp)                                                                                                                               |

| EE <sub>EN</sub>     | EEPROM endurance               | 100000 |     |      | cycles   | @ 125°C                                                                                                                                                             |

| EE <sub>RET</sub>    | EEPROM retention               | 10     |     |      | years    | 160,0                                                                                                                                                               |

Page 8ams DatasheetDocument Feedback[v1-04] 2016-Jan-07

## **Detailed Description**

Figure 10: System Block Diagram

#### Circuit

The AS3953B is composed of ISO 14443A PICC Analog Front-end (PICC AFE), the ISO 14443A PICC Logic (PICC Logic), EEPROM, SPI Interface, Level Shifters and Power Supply Manager Block (Power Manager).

The PICC AFE is connected to an external tag coil, which forms together with integrated resonant capacitor an LC tank with a resonance at the external electromagnetic field frequency of 13.56 MHz. The PICC AFE has a built in rectifier and regulators. Output of internal regulator is called VP\_INT. It is used to supply the PICC AFE and usually also the LOGIC and EEPROM (through Power Supply Manager). Output of external regulator VP\_REG is available on a pin to supply some external circuitry.

Power Manager is controlling power supply of Logic and EEPROM. The two blocks can be supplied either from VP\_INT or from VP\_SPI (SPI power supply). In order to save current on VP\_SPI, VP\_INT is used as power supply whenever it is available. VP\_SPI is only used when some activity is started over the SPI and the VP\_INT is too low to be used as a power supply.

The PICC Logic is responsible for PICC-to-PCD communication up to the Level-4 (block transmission) of ISO 14443A. This means that anti-collision and other low-level functionality are implemented there.

The SPI Interface logic contains a 32 byte FIFO for block transmission data which is exchanged on Level-4 of ISO 14443A communication. It also contains some control and display registers.

The EEPROM is used to store the UID, the housekeeping data (configuration and control bits) and user data. It can be accessed from both sides (RFID and SPI).

ams Datasheet Page 9

[v1-04] 2016-Jan-07 Document Feedback

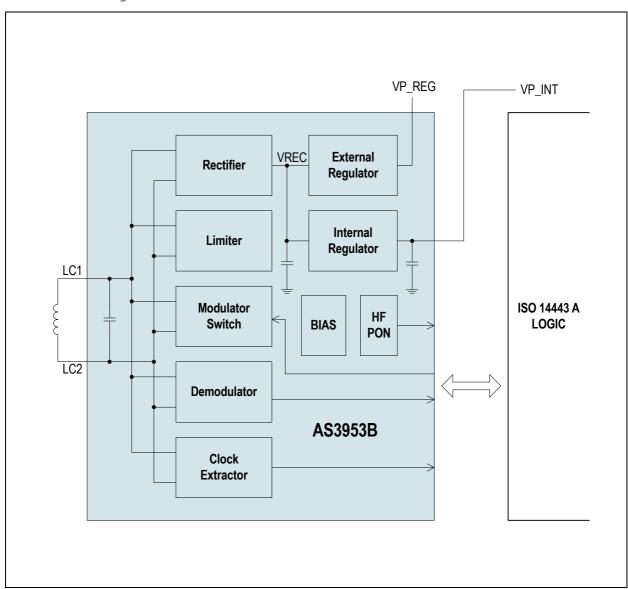

#### **PICC AFE**

Figure 11 depicts main PICC AFE building blocks.

The PICC AFE is connected to external tag coil, which together with the integrated resonant capacitor forms an LC tank with resonance at external electromagnetic field frequency (13.56 MHz). Figure 11 depicts the main PICC AFE building blocks.

**Rectifier**: Extracts DC power supply from AC voltage induced on coil terminals.

**Limiter**: Limits the maximum voltage on coil terminals to protect PICC AFE from destruction. At voltages that exceed limiter voltage it starts to absorb current (acts as some sort of shunt regulator).

**Modulator Switch**: Is used for communication PICC-to-PCD. When switched on, it will draw current from coil terminals. This mechanism is called load modulation. Variation of current in the modulator switch (ON and OFF state) is seen as modulation by the PCD.

**Demodulator**: Is used for communication PICC-to-PCD. It detects AM modulation of the PCD magnetic field. The demodulator is designed to accept modulation according to ISO 14443A; all standard bit rates from 106 kbit/s to 848 kbit/s are supported. The modulation for bit rate 106 kbit/s is 100%, whereas for other bit rates it may be less.

**Clock Extractor**: The clock extractor extracts a digital clock signal from the PCD carrier field frequency which is used as clock signal by logic blocks.

**HF\_PON**: Observes rectified regulated voltage VREC. When the supply voltage is sufficiently high it enables operation of the PICC AFE and the digital tag logic. A buffer capacitor and HF\_PON hysteresis guarantees that there is no reset during reader (PCD) modulation.

**Internal Regulator**: Provides regulated voltage VP\_INT to the PICC AFE and in most cases also to EEPROM and logic blocks. Typical regulated voltage VP\_INT is 2.0V. A buffer capacitor is also integrated.

**External Regulator**: Provides regulated voltage on external pin VP\_REG where it can be used to supply some external circuitry. The regulated voltage and output resistance can be adjusted using EEPROM settings (see Figure 36). Appropriate external buffer capacitor is needed in case VP\_REG is used in the application. The current to be provided depends on reader field strength, antenna size and Q factor, but it is limited to maximum 5mA

**Bias**: Provides bias currents and reference voltages to PICC AFE analog blocks.

Page 10

Document Feedback

[v1-04] 2016-Jan-07

Figure 11: PICC AFE Block Diagram

ams Datasheet Page 11

[v1-04] 2016-Jan-07 Document Feedback

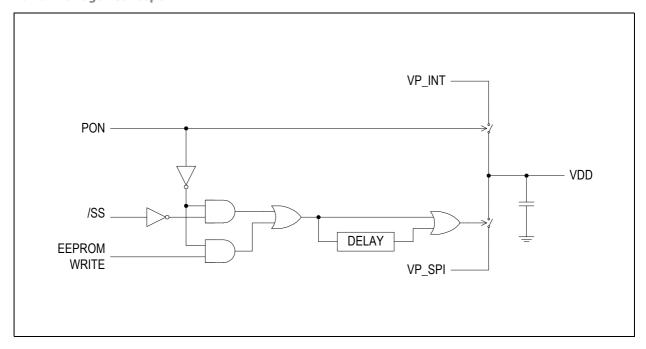

## **Power Manager**

Power manager is controlling the positive supply voltage of the PICC Logic, EEPROM and SPI Interface (VDD). Its inputs are VP\_INT (rectified and regulated supply extracted from PCD field) and the VP\_SPI (SPI power supply from external).

In standby mode, when the AS3953B is not in a PCD field (condition is that rectified supply voltage is below HF\_PON threshold) and the SPI is not active (/SS is high) the VDD supply is disconnected not to consume on VP\_SPI. The only consumption on VP\_SPI is leakage of level shifters and SPI pins.

When the AS3953B is placed in a PCD field the VDD is connected to VP\_INT. This happens once the VP\_INT level is above the HF\_PON threshold.

VP\_SPI is connected to VDD only when the AS3953B is not in the PCD field (rectified supply voltage is below HF\_PON threshold) and the SPI interface is activated by pulling /SS signal low. The switch to VP\_SPI is controlled by /SS signal. The deactivation is delayed by 0.7ms min., thus the switch stays on in case the time between successive SPI activations is short. During EEPROM writing, which is activated over the SPI, the switch is also active.

At activation of the switch the time between the falling edge of /SS signal and rising edge of SCLK has to be at least  $50\mu s$  to allow charging of internal VDD buffer capacitor and expiration of POR signal. Please note that the only SPI operations, which are allowed in this mode, are reading and writing of the EEPROM and registers.

Figure 12: Power Manager Concept

Page 12ams DatasheetDocument Feedback[v1-04] 2016-Jan-07

## ISO 14443A Framing Mode

When Framing mode is selected the PICC logic performs receive and transmit framing according to the selected ISO 14443A bit rate.

During reception it recognizes the SOF, EOF and data bits, performs parity and CRC check, organizes the received data in bytes and places them in the FIFO.

During transmit, it operates inversely, it takes bytes from FIFO, generates parity and CRC bits, adds SOF and EOF and performs data encoding.

Default bit rate in the Framing mode is fc/128 (~106 kbit/s). Higher data rates may be configured by controller by writing the Bit Rate Definition Register.

In order to respect the PCD-to-PICC frame delay according to ISO14443-3 at data rate fc/128 bit the PICC logic synchronizes the response to the beginning of the next response window, but not earlier than window with n=9.

In this mode the EEPROM can be accessed via SPI when the RF field is active.

#### ISO 14443A Level-4 Protocol Mode

When Level-4 Protocol mode is selected the PICC Logic autonomously execute complete ISO 14443A Level-3 communication and certain commands of Level-4. This also includes the anti-collision sequence during which the AS3953B UID number is read by the PCD (7 bytes UID is supported), the AS3953B is brought in the selected state (ISO14443-4) in which data exchange between the AS3953B and the PCD can start. On this level also a reading and writing of the AS3953B EEPROM is possible.

In case the configuration bit *irq\_I4* is set an interrupt is automatically sent to controller once the PICC Logic enters in ACTIVE(\*) state (after sending SAK on Cascade Level 2).

#### Support of ISO 14443A Level-4

ISO 14443A-4 commands **RATS**, **PPS** and **DESELECT** are implemented in the PICC Logic. **RATS** and **PPS** define communication parameters, which are going to be used in the following data exchange by using the block transmission protocol. The advantage of implementing *PPS* that defines the bit rate used for communication, is that all bit rate issues are handled by the PICC Logic. The MCU gets the information about the actual receive and transmit bit rate by reading a dedicated display register. It has to be fast enough to serve receive and transmit at the maximum bit rate.

Execution of the block transmission protocol is left to the controller. In case of receiving the block data from the PCD the PICC Logic provides support by detecting and removing start bit, stop bit, parity bits and CRC. Parity bits and CRC are also checked. When the block data is sent to the PCD the PICC Logic calculates and inserts start bit, parity bits, CRC and stop bit.

ams Datasheet Page 13

[v1-04] 2016-Jan-07 Document Feedback

**DESELECT** puts the PICC Logic in HALT state. An interrupt is sent to controller upon reception of **DESELECT** command to inform it that PCD stopped the Level-4 communication.

Additionally to supporting the ISO14443-4 transmitting protocol the PICC Logic accepts also proprietary commands. Proprietary commands are identified by setting the two MSB bits of first transmitted byte to '01' (This combination is not used by ISO 14443A Level-4 protocol). The following custom commands are implemented:

- Wake-Up: Sends a wake-up interrupt to controller

- Read EEPROM: Reads data from EEPROM

- Write EEPROM: Writes data to EEPROM

#### **Support of ISO 14443A Optional Features**

- CID is supported

- NAD is not supported

- · Historical bytes are not supported

- Power level indication is not supported

#### **Coding of UID**

Anti-collision procedure is based on Unique Identification Number (UID). The AS3953B supports double UID size (7 bytes). First three bytes of UID are hard-wired inputs to the PICC Logic (uid<23:0>). Last 4 bytes of UID are stored in EEPROM UID word.

#### First Byte of UID (uid0)

First byte of UID is according to [ISO3] ISO/IEC 7816-6 IC Manufacturer ID. It is coded on bits *uid*<7:0>. **ams** IC Manufacturer ID is 3F(hex).

## Second Byte of UID (uid1)

Second byte of UID – uid<15:8> is reserved for **ams** chip type (IC Type). Every **ams** RFID tag IC has its own chip type attributed. Therefore PCD which has read the RFID tag UID knows to which tag IC it is talking.

The AS3953B IC type is 10(hex).

#### Third Byte of UID (uid2)

Third byte of UID – *uid*<23:16> is set to 00(hex). Figure below defines the coding of the first three bytes of UID.

Figure 13: Coding of First Three Bytes of UID

| UID Byte | FL Signal Name | Value (hex) |

|----------|----------------|-------------|

| uid0     | uid<7:0>       | 3F          |

| uid1     | uid<15:8>      | 10          |

| uid2     | uid<23:16>     | 00          |

Page 14

Document Feedback

[v1-04] 2016-Jan-07

The last 4 bytes of UID are read from EEPROM (UID word). Figure below defines the last four bytes of UID.

Figure 14: **Coding of Last Four Bytes of UID**

| UID Byte | UID Word Bits |  |  |  |

|----------|---------------|--|--|--|

| uid3     | b7-b0         |  |  |  |

| uid4     | b15-b8        |  |  |  |

| uid5     | b23-b16       |  |  |  |

| uid6     | b31-b24       |  |  |  |

## Coding of ATQA, SAK and ATS

Several bits of responses ATQA, SAK and ATS are defined as "don't care" in the ISO 14443A standard. Some others are defined by optional choices in standard protocol. This section defines how these bits are set by the AS3953B.

#### **ATQA**

ATQA is response to **REQA** and **WUPA** commands. Figure below defines the ATQA coding.

Figure 15: **ATQA Coding**

| b16 | b15 | b14 | b13 | b12 | b11 | b10  | b9 | b8 | b7       | b6      | b5        | b4 | b3 | b2 | b1 |

|-----|-----|-----|-----|-----|-----|------|----|----|----------|---------|-----------|----|----|----|----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0  | 0  | 1        | 0       | 0         | 0  | 1  | 0  | 0  |

|     |     |     |     |     | UID | size |    | Е  | Bit fram | e anti- | collision | า  |    |    |    |

Bits b16 to b13 are RFU bits which must be set to '0'.

Bits b12 to b9 are proprietary coding and are set to '0'.

Bits b8 and b7 indicate double size UID.

Bit b6 is 'RFU' bit and is set to '0'.

For bit frame anti-collision, the code 00100 is chosen.

ams Datasheet Page 15 **Document Feedback**

#### SAK

SAK is response to **SELECT** command. AS3953B UID has double size, which defines SAK responses for Cascade Level 1 and Cascade Level 2.

**Cascade Level 1:** According to ISO 14443-3, all bits except *b3* are "don't care" for Cascade Level 1. Figure below defines Cascade Level 1 coding.

Figure 16: Cascade Level1 Coding

| b8<br>MSB | b7 | b6                  | b5 | b4 | b3 | b2 | b1<br>LSB | Description                       |

|-----------|----|---------------------|----|----|----|----|-----------|-----------------------------------|

| 0         | 0  | As b6 in<br>SAK CL2 | 0  | 0  | 1  | 0  | 0         | Cascade bit set: UID not complete |

Bit *b6* in Cascade Level 1 is always set as bit *b6* in Cascade Level 2. This is done in accordance to EMVCo Level – 1 Contactless Digital Test specifications.

**Cascade Level 2:** According to ISO 14443-3 all bits except *b6* and *b3* are "don't care" for Cascade Level 2.

If configuration *bit16* [*nl4*] is set to logic '0' (default state), the SAK on Cascade Level 2 reports that tag is compliant to level4 (see figure below).

Figure 17: Cascade Level 2 Coding (ISO/IEC14443-4 compliant)

| b8<br>MSB | b7 | b6 | b5 | b4 | b3 | b2 | b1<br>LSB | Description                                            |

|-----------|----|----|----|----|----|----|-----------|--------------------------------------------------------|

| 0         | 0  | 1  | 0  | 0  | 0  | 0  | 0         | UID complete, tag is<br>compliant to<br>ISO/IEC14443-4 |

If configuration *bit16* [*nl4*] is set to logic '1', the SAK on Cascade Level 2 reports that tag is NOT compliant to Level-4 (see figure below).

Figure 18: Cascade Level 2 Coding (NOT ISO/IEC14443-4 compliant)

| b8<br>MSB | b7 | b6 | b5 | b4 | b3 | b2 | b1<br>LSB | Description                                                 |

|-----------|----|----|----|----|----|----|-----------|-------------------------------------------------------------|

| 0         | 0  | 0  | 0  | 0  | 0  | 0  | 0         | UID complete, tag is <b>NOT</b> compliant to ISO/IEC14443-4 |

Page 16

Document Feedback

[v1-04] 2016-Jan-07

#### **ATS**

ATS is response to ISO 14443-4 command RATS. The content of the ATS is used to inform the PCD about PICC capability (like the maximum frame size, support of higher bit rates, etc.)

Several response fields of ATS are stored in EEPROM configuration word. The AS3953B ATS is composed of following 5 bytes according to [ISO4]: TL, T0, TA(1), TB(1) and TC(1).

**TL:** This is the length byte. Since ATS is composed of 5 bytes, its content is 0x05. Figure below defines the coding of the TL byte.

Figure 19: **TL Byte Coding**

| b8<br>MSB | b7 | b6 | b5 | b4 | b3 | b2 | b1<br>LSB | Description           |

|-----------|----|----|----|----|----|----|-----------|-----------------------|

| 0         | 0  | 0  | 0  | 0  | 1  | 0  | 1         | Coding of ATS byte TL |

**T0:** This is the format byte. Figure below defines the coding of the T0 byte.

Figure 20: **T0 Byte Coding**

| b8<br>MSB | b7    | b6    | b5    | b4      | b3      | b2      | b1<br>LSB | Description           |

|-----------|-------|-------|-------|---------|---------|---------|-----------|-----------------------|

| 0         | 1     | 1     | 1     | fsci<3> | fsci<2> | fsci<1> | fsci<0>   | Coding of ATS byte T0 |

|           | TC(1) | TB(1) | TA(1) | FCSI    |         |         |           |                       |

Bit *b8* is set to '0'.

Bits b7 to b5 indicate presence of bytes TA(1), TB(1) and TC(1) and hence are all set to '1'.

Bits b4 to b1 are called FCSI and codes FCS. The FCS is maximum size of a frame defined by PICC. It is defined by configuration bits fsci<3:0>.

TA(1): This codes the bit rate capability of PICC. Supported higher bit rates of AS3953B are 212, 424 and 848 kbit/s. However in specific applications, it is advised to report lower capability to PCD (for example, due to the usage of slow controller or low power application). Due to this reason the TA(1) response is configurable using configuration bits.

ams Datasheet Page 17 **Document Feedback**

Figure 21: TA(1) Byte Coding

| b8<br>MSB | b7               | b6            | b5            | b4               | b3           | b2           | b1<br>LSB    | Description              |

|-----------|------------------|---------------|---------------|------------------|--------------|--------------|--------------|--------------------------|

| dr_sdr    | dr_<br>picc_8    | dr_<br>picc_4 | dr_<br>picc_2 | 0                | dr_<br>pcd_8 | dr_<br>pcd_4 | dr_<br>pcd_2 | Coding of ATS byte TA(1) |

|           | DS (PICC to PCD) |               |               | DR (PCD to PICC) |              | CC)          |              |                          |

Bit b8 set to '0' codes possibility of having different data rates for each direction.

**TB(1):** The interface byte TB(1) conveys information to define the frame waiting time and the start-up frame guard time. The interface byte TB(1) consists of two parts:

- The most significant half-byte b8 to b5 is called FWI and codes frame waiting time (FWT).

- The least significant half byte b4 to b1 is called SFGI and codes a multiplier value used to define the SFGT. The SFGT defines a specific guard time needed by the PICC before it is ready to receive the next frame after it has sent the ATS. SFGI is coded in the range from 0 to 14. The value of '0' indicates 'No SFGT needed'.

- The SFGT bits are fixed to default value which is 0x0, while the FWI bits are defined by configuration bits fwi<3:0>. Figure below defines the coding of the TB(1) byte.

Figure 22: TB(1) Byte Coding

| b8<br>MSB | b7     | b6     | b5     | b4   | b3 | b2 | b1<br>LSB | Description              |

|-----------|--------|--------|--------|------|----|----|-----------|--------------------------|

| fwi<3>    | fwi<2> | fwi<1> | fwi<0> | 0    | 0  | 0  | 0         | Coding of ATS byte TB(1) |

|           | FWI    |        |        | SFGI |    |    |           |                          |

- TC(1): The interface byte TC(1) specifies a parameter of the protocol. The interface byte TC(1) consists of two parts:

- The most significant bits b8 to b3 are set to 000000, all other values are 'RFU'.

- The bits b2 and b1 define which optional fields in the prologue field are supported by the PICC. The PCD is allowed to skip fields that are supported by the PICC. Bit b2 indicates support of CID and b1 indicates support of NAD. The AS3953B value is '10' indicating "CID supported" and "NAD not supported".

Page 18 ams Datasheet

Figure below defines the coding of the TC(1) byte.

Figure 23: TC(1) Byte Coding

| b8<br>MSB | b7 | b6 | b5 | b4 | b3 | b2  | b1<br>LSB | Description              |

|-----------|----|----|----|----|----|-----|-----------|--------------------------|

| 0         | 0  | 0  | 0  | 0  | 0  | 1   | 0         | Coding of ATS byte TC(1) |

|           |    |    |    |    |    | CID | NAD       |                          |

## **Proprietary Commands**

Proprietary commands have the same format as blocks defined in ISO 14443-4 with the difference that optional NAD field is abandoned since NAD is not supported by the AS3953B. The same format is used for commands sent by PCD and AS3953B responses. Figure below defines the coding of the Proprietary commands.

Figure 24: **Proprietary Commands Coding**

| Prologi | ue Field | Information<br>Field | Epilogue<br>Field |

|---------|----------|----------------------|-------------------|

| PCB     | [CID]    | INF                  | EDC               |

| 1 byte  | 1 byte   |                      | 2 bytes           |

Prologue field consists of the mandatory Protocol Control Byte and an optional Card Identifier Byte. Card identifier byte is according to ISO 14443-4 definition. Epilogue field contains CRC over transmitted block.

ams Datasheet Page 19 [v1-04] 2016-Jan-07 **Document Feedback**

#### **Prologue Field for Proprietary Commands**

Figure below defines the coding of Prologue field for Proprietary commands.

Figure 25:

**Prologue Field (proprietary commands)**

| Bit | Value | Function                                           |  |  |  |

|-----|-------|----------------------------------------------------|--|--|--|

| b8  | 0     | 01 indicates proprietary command                   |  |  |  |

| b7  | 1     | or indicates proprietary command                   |  |  |  |

| b6  | 0     | Shall be set to this value, other                  |  |  |  |

| b5  | 1     | values are 'RFU'                                   |  |  |  |

| b4  |       | CID following if bit is set to '1'                 |  |  |  |

| b3  | 1     |                                                    |  |  |  |

| b2  | 0     | Shall be set to this value, other values are 'RFU' |  |  |  |

| b1  | 1     |                                                    |  |  |  |

The following proprietary commands are implemented:

- Wake-Up: Sends a wake-up interrupt to controller

- Read EEPROM: Reads data from EEPROM

- Write EEPROM: Writes data to EEPROM

## **Wake-Up Command**

Information field of **Wake-Up** command consists of one byte only (see figure below). The AS3953B echoes back the same information field.

Figure 26:

**Wake-Up Command**

| 01h   |

|-------|

| 1byte |

Figure below defines the coding of the AS3953B reply INF to **Wake-Up** command.

Figure 27:

Wake-Up Reply

| 01h   |

|-------|

| 1byte |

Page 20ams DatasheetDocument Feedback[v1-04] 2016-Jan-07

#### **Word Address Byte**

Both proprietary commands related to EEPROM (Read and Write) use Word Address byte to define the address of EEPROM word that is accessed. Seven MSB bits of the Address Byte are used to define the address, while the last bit is "don't care".

**Note(s):** The valid range for the Word Address byte is from 0000 000xb to 0011 111xb (EEPROM words from 00h to 1Fh).

#### **Read EEPROM**

The **Read EEPROM** command is used to read data from the EEPROM. The request information field contains the following three bytes:

- Command code byte (02h)

- · Address of the first word to be read

- Number of words to be read

Figure below defines coding of **Read EEPROM** command information field.

Figure 28: Read EEPROM Command

| 02h   | Address of First<br>Word to Be Read | Number of Words<br>(≤ 8) to Be Read |

|-------|-------------------------------------|-------------------------------------|

| 1byte | 1byte                               | 1byte                               |

If the request is normally processed, the reply information field contains the status word *90h* followed by the data. In case of error, the information field only contains the error status byte. The following rules apply:

- In case the number of words to be read is higher than 8, first eight words are read.

- In case the read protected word (its read lock bit is set) is accessed, an all '0' data is sent out.

- In case the reading starts at valid address and the number of words to read is such that the reading would be done beyond the EEPROM addressing space, all '0' data is returned for non-existing addresses.

- In case the reading starts at non-existing address, error information field is returned.

ams Datasheet Page 21

[v1-04] 2016-Jan-07 Document Feedback

Figure below defines the coding of the AS3953B reply information field to **Read EEPROM** command, if command is normally processed.

Figure 29:

Read EEPROM Reply (successful)

| 90h   | Data          |

|-------|---------------|

| 1byte | 4 to 32 bytes |

Figure below defines the coding of the AS3953B reply information field to **Read EEPROM** command, in case of an error.

#### Figure 30:

Read EEPROM Reply (error code)

| Information Field | Comment               |  |  |

|-------------------|-----------------------|--|--|

| 61h               | Error (no diagnostic) |  |  |

#### Write EEPROM

The **Write EEPROM** command is used to write one EEPROM word (32 bits). The request information field contains 6 bytes:

- Command code byte (04h)

- Address of the word to be written

- Four bytes (32 bits) of data to be written

Figure below defines coding of **Write EEPROM** command information field.

### Figure 31:

**Write EEPROM Command**

| 04h    | Address of Word to Be Written | Data    |

|--------|-------------------------------|---------|

| 1 byte | 1 byte                        | 4 bytes |

The AS3953B reply contains one byte informing whether the writing of EEPROM was executed or whether there was an error. Prior to actual programming of data in EEPROM, the control logic checks whether there is enough power available. This is done by performing so called power check during which a dummy EEPROM programming is started. If the power check fails, EEPROM programming is not performed and an error code is sent. The EEPROM programming is a time consuming operation.

Page 22

Document Feedback

[v1-04] 2016-Jan-07

Therefore, if the EEPROM programming is executed, the AS3953B reply comes after 8ms typical. Figure below defines the coding of the AS3953B reply to **Write EEPROM** command.

Figure 32: Write EEPROM Reply

| Information Field | Comment                                                                             |

|-------------------|-------------------------------------------------------------------------------------|

| 90h               | Writing is normally processed                                                       |

| 61h               | Writing is not done due to coding error (error in parity, CRC, nonexistent address) |

| 62h               | Writing is not done since the word is locked                                        |

| 64h               | Writing is not done due to power check fail                                         |

## **Passing of Block Data to Controller**

After the PICC Logic has passed the anti-collision procedure and replied with SAK on Cascade Level 2 it passes in ACTIVE(\*) state. On this level it expects that blocks received from the PCD have the format according to ISO 14443A-4. The ISO 144443A Logic recognizes the command by observing the first received byte. Based on content of this byte command is either processed by the AS3953B or the complete block data is put in the FIFO for further processing by the controller. The figure below displays the decision criteria.

ams Datasheet Page 23 **Document Feedback**

Figure 33: First Byte of the ISO 14443-4 PCD Block

| First Byte      | Comment                                | Action of PICC Logic                                                 |  |  |

|-----------------|----------------------------------------|----------------------------------------------------------------------|--|--|

| 1110 0000       | RATS                                   | Replies with ATS <sup>(1)</sup>                                      |  |  |

| 1110 not(0000)  |                                        | Block is put in FIFO                                                 |  |  |

| 1101 xxxx       | PPS                                    | Replies with PPS response (second character is CID) <sup>(1)</sup>   |  |  |

| 1100 x 010      | DESELECT                               | Replies and go to Halt                                               |  |  |

| 1100 x not(010) | See note (2)                           | Block is put in FIFO                                                 |  |  |

| 1111 xxxx       | WTX, S(PARAMETERS), RFU <sup>(1)</sup> | Block is put in FIFO since controller needs it to implement chaining |  |  |

| 01xx xxxx       | Proprietary command                    | Proprietary command is processed                                     |  |  |

| 00xx xxxx       | I-block                                | Block is put in FIFO                                                 |  |  |

| 10xx xxxx       | R-block                                |                                                                      |  |  |

#### Note(s):

- 1. RATS and PPS are only processed by the AS3953B logic in case they are sent according to the ISO 14443-4 specification (RATS is first command sent after entry in ACTIVE(\*) state, optionally followed by PPS). In case RATS or PPS are sent once the AS3953B logic is in PROTOCOL state the information received is saved into FIFO and not acted upon.

- 2. Compatible with old and new S(PARAMETERS) definition: Old: 1100 x000 is S(PARAMETERS) block according to the ISO 14443-4/AM2. **New**: 1111 x000 is S(PARAMETERS) block according to the modification SC17/WG8.

As shown in Figure 33, the block data is put in the FIFO whenever the two MSB bits are 00 or 10 and also in the case when the four MSB bits are 1111. Therefore the implemented communication between the PCD and a tag implemented by the AS3953B and a controller does not need to follow the Block transmission protocol defined in the ISO 14443-4.

#### **Use of CID**

As mentioned above the AS3953B decides depending on content of the first byte of received message to either execute received message as a command or to put it in the FIFO. The second byte of the message comprises a CID number which is attributed by PCD. PCD will use CID number in case more PICCs are brought to Level-4 of communication at the same time.

CID is only checked for messages (commands) that are executed by the AS3953B. In case CID does not match such a command is rejected (no action is taken).

Messages that are based on first byte are put in FIFO and are not filtered by CID. It is left to controller to check for the CID and decide whether or not to reply (CID number is stored in the RATS Register).

Page 24

Document Feedback

[v1-04] 2016-Jan-07

#### ISO 14443A Level-3 Protocol Mode

Level-3 Protocol mode is intended for implementation of custom protocols for which coding on Level-4 of ISO 14443A communication according to Figure 33 is not appropriate. In this mode Level-2 and Level-3 behavior of the PICC logic is identical to ISO 14443A Level-4 Protocol mode, while on Level-4 all received data blocks are put in FIFO.

In case the configuration bit *irq\_I4* is set an interrupt is automatically sent to controller once the PICC Logic enters in ACTIVE(\*) state (after sending SAK on Cascade Level 2).

In this mode the EEPROM can be accessed via SPI when the RF field is active.

## **Transparent Mode**

In the Transparent Mode the AS3953B logic is bypassed, AFE input and output signals are directly available on SPI interface pins when /SS signal is high.

- Modulator switch is controlled by pin MOSI (high is modulator on)

- Clock extractor output is sent to pin MISO

- Demodulator output is sent to pin IRQ

When /SS signal is low the SPI interface pins resume its normal functionality. In this mode the EEPROM can be accessed via SPI when the RF field is active.

ams Datasheet Page 25

[v1-04] 2016-Jan-07 Document Feedback

#### **EEPROM**

The AS3953B contains an EEPROM block which can be accessed from both RFID and SPI interface. EEPROM contains 1024 bits (128 bytes) organized in 32 words of 32 bits. Words in EEPROM are number from 0 to 31(1F[hex]). Bits in a word are numbered from 0 to 31.

Most of the EEPROM is used to store user data (27 words – 864 bits), five words are used to store some housekeeping information (part of the AS3953B UID, configuration bits which define the AS3953B operating options, lock bits, which control the possibility to write EEPROM words).

Figure 34: EEPROM Organization

| Word Address [hex] | Content            | Access Properties |

|--------------------|--------------------|-------------------|

| 0                  | UID                | RO                |

| 1                  | Fabrication Data   | RO                |

| 2                  | Configuration Word | RW                |

| 3                  | Write Lock Word    | ОТР               |

| 4                  | Read Lock Word     | ОТР               |

| 5: 1F              | User Data          | RW                |

#### **Access Properties:**

RO: Read only, writing to this word is not possible

**RW:** Reading and writing to this word is possible, writing is disabled once the lock bit is set

**OTP:** One time programmable. A bit of this word once set to '1' cannot be set back to '0'.

#### **UID Word**

The UID word contains four LSB bytes of 7 byte UID which is used during anti-collision and selection process. Every IC is programmed by a unique number during fabrication process at **ams**. For details on UID, please refer to Coding of UID.

#### **Fabrication Data Word**

This word stores some IC manufacturer data which is programmed and locked during fabrication process at **ams**.

#### **Configuration Word**

The Configuration word is used to define the AS3953B operating options. It is delivered by **ams** with default setting.

Page 26

Document Feedback

[v1-04] 2016-Jan-07

Figure 35: Configuration Word (Bits 31 to 16)

| Configuration Bit | Name      | Default | Function                                                                                           |

|-------------------|-----------|---------|----------------------------------------------------------------------------------------------------|

| b31               | fsci<3>   | 0       | FSCI. Default value (2h) codes maximum size of                                                     |

| b30               | fsci<2>   | 0       | frame accepted by PICC to 32 bytes which is the size of the FIFO. Please note that the AS3953B can |

| b29               | fsci<1>   | 1       | support larger frame sizes in case FIFO is read during the receiving.                              |

| b28               | fsci<0>   | 0       | during the receiving.                                                                              |

| b27               | fwi<3>    | 0       |                                                                                                    |

| b26               | fwi<2>    | 1       | FWI (default value (6h) defines frame waiting time                                                 |

| b25               | fwi<1>    | 1       | of ~19.3ms)                                                                                        |

| b24               | fwi<0>    | 0       |                                                                                                    |

| b23               | dr_sdr    | 0       | 1: Only the same bit rate for both directions supported (TA(1) of ATS)                             |

| b22               | dr_picc_8 | 0       | 1: DR=8 PICC-to-PCD supported (848kbit/s) (TA(1) of ATS)                                           |

| b21               | dr_picc_4 | 0       | 1: DR=4 PICC-to-PCD supported (424kbit/s) (TA(1) of ATS)                                           |

| b20               | dr_picc_2 | 0       | 1: DR=2 PICC-to-PCD supported (212kbit/s) (TA(1) of ATS)                                           |

| b19               | dr_pcd_8  | 0       | 1: DR=8 PCD-to-PICC supported (848kbit/s) (TA(1) of ATS)                                           |

| b18               | dr_pcd_4  | 0       | 1: DR=4 PCD-to-PICC supported (424kbit/s) (TA(1) of ATS)                                           |

| b17               | dr_pcd_2  | 0       | 1: DR=2 PCD-to-PICC supported (212kbit/s) (TA(1) of ATS)                                           |

| b16               | nl4       | 0       | 1: SAK on Cascade Level 2 reports that tag is not ISO 14443-4 compatible                           |

| b15               | nfc       | 0       | 1: SAK on Cascade Level 2 reports that tag is NFC passive target                                   |

### Note(s):

- 1. Configuration bits b31 to b15 define AS3953B response to **SAK** and **ATS** command in ISO 14443A Protocol modes, while bits b14 to *b0* actually change performance.

- 2. Incase both *nl4* and *nfc* are set, the *nl4* setting prevails.

ams Datasheet Page 27 Document Feedback

Figure 36: Configuration Word (Bits 14 to 0)

| Configuration Bit | Name    | Default | Function                                                                                                     |

|-------------------|---------|---------|--------------------------------------------------------------------------------------------------------------|

| b14               | irq_pu  | 0       | 1: Send a power-up IRQ (after power-up initialization is finished)                                           |

| b13               | irq_l4  | 0       | 1: Send an IRQ at entry in ACTIVE(*) state (after sending SAK on Cascade Level 2) (2)                        |

| b12               | mod_1   | 0       | 00: ISO 14443A Level-4 Protocol mode                                                                         |

| b11               | mod_0   | 0       | <ul><li>01: ISO 14443A Level-3 Protocol mode</li><li>10: Framing mode</li><li>11: Transparent mode</li></ul> |

| b10               | rxncrc  | 0       | <b>1:</b> Rx – CRC is not checked, CRC part of message is also put in FIFO (3)                               |

| b9                | rxbs    | 0       | <b>1:</b> Rx – Bit stream mode, received bits are put in FIFO (no parity and CRC check) (3)                  |

| b8                | txncrc  | 0       | 1: Tx – Do not generate CRC (3)                                                                              |

| b7                | txbs    | 0       | <b>1:</b> Tx – Bit stream mode, bits put in FIFO are sent without parity and CRC generation (3)              |

| b6                | fdel<1> | 0       | DCD to DICC dolove division and (4)                                                                          |

| b5                | fdel<0> | 0       | PCD-to-PICC delay adjustment (4)                                                                             |

| b4                | vreg<1> | 0       | 00: 1.8V<br>10: 2.7V External Regulated voltage (VP_                                                         |

| b3                | vreg<0> | 0       | <b>11:</b> 3.3V External Regulated Voltage (VP_<br><b>11:</b> 3.3V                                           |

| b2                | rreg<1> | 0       | <b>00:</b> disabled<br><b>10:</b> $50Ω$ External Regulator enable and                                        |

| b1                | rreg<0> | 0       | 10: $50Ω$ External Regulator enable and<br>output resistance setting11: $25Ω$                                |

| b0                | dr8     | 0       | Reserved for internal use                                                                                    |

#### Note(s):

- 1. Configuration bits *b31* to *b15* define AS3953B response to **SAK** and **ATS** command in ISO 14443A Protocol mode, while bits *b14* to *b0* actually change performance.

- 2. Applicable in ISO 14443A Level-3 and Level-4 Protocol modes.

- 3. Applicable in ISO 14443A Level-3 Protocol mode and Framing mode, in Protocol mode applicable for frames which are put in FIFO.

- 4. Configuration bits *fdel<1:0>* are used to adjust frame delay time PCD-to-PICC. Delays caused by reader and tag resonant tanks and AFE processing are compensated by PICC logic. Figure below defines PCD-to-PICC frame delay compensation using *fdel* bits.

Page 28ams DatasheetDocument Feedback[v1-04] 2016-Jan-07

Figure 37: **PCD-to-PICC Frame Delay Compensation**

| fdel<1:0> | Delay [ns] | Delay [number of 13.56 MHz periods] |

|-----------|------------|-------------------------------------|

| 00        | 442.5      | 6                                   |

| 01        | 295.0      | 4                                   |

| 10        | 147.5      | 2                                   |

| 11        | 590.0      | 8                                   |

#### **OTP Words**

Write and Read Lock Words are OTP (One Time Programmable). This means that once they are set to '1', they cannot be reset back to '0'. Since setting of OTP bits is an irreversible operation, it is strongly recommended to perform it in controlled environment.

#### Write Lock Word

The Write Lock Word contains write lock bits. Each EEPROM word has a corresponding lock bit in the Write Lock Word. Once a certain lock bit is set to '1', the content of corresponding word cannot be modified any more (it becomes read only), EEPROM write commands issued either through PICC interface or through SPI interface are rejected. The lock bit of a certain number protects the word with the same number (e.g. b5 of lock word protects word 5). Since lock bits are OTP they cannot be reset back to '0' once they are set to '1'. Therefore once a certain word is locked it cannot be unlocked any more. The lock bits for page 0 is "don't care" since word 0 is always read only. Please note that setting lock bit *b2* locks the Lock Word itself, therefore once this bit is set the lock configuration cannot be modified any more.

#### Read Lock Word

The Read Lock Word contains read lock bits. Each EEPROM word has a corresponding lock bit in the Read Lock Word. Once a certain lock bit is set to '1', the content of corresponding word cannot be read through PICC interface, it can only be read through SPI interface. The lock bit of a certain number protects the word with the same number (e.g. b5 of lock word protects word 5). Since lock bits are OTP they cannot be reset back to '0' once they are set to '1'. Therefore once a certain word is locked it cannot be unlocked any more. The lock bits for pages 0 to 4 are "don't care"; these pages can be read through PICC interface even in case their corresponding lock bits are set.

ams Datasheet Page 29 **Document Feedback**

## **Application Information**

#### **SPI Interface**

Communication between the AS3953B and controller is done through a 4-wire Serial Peripheral Interface (SPI) and additional interrupt signal. The AS3953B is an SPI slave device; it requests controller attention by sending an interrupt (IRQ pin).

Figure 38: SPI and Interrupt Signals

| Name | Signal                       | Signal Level | Description                    |

|------|------------------------------|--------------|--------------------------------|

| /SS  | Digital input with pull-up   | CMOS         | SPI enable (active low)        |

| MOSI | Digital input                | CMOS         | Serial data input              |

| MISO | Digital output with tristate | CMOS         | Serial data output             |

| SCLK | Digital input                | CMOS         | Clock for serial communication |

| IRQ  | Digital output               | CMOS         | Interrupt output pin           |

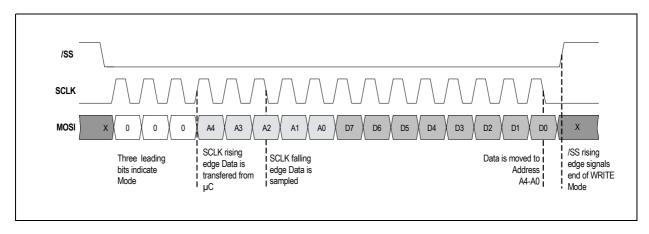

While signal /SS is high the SPI interface is in reset, while it is low the SPI interface is enabled. It is recommended to keep signal /SS high whenever the SPI interface is not in use. MOSI is sampled at the falling edge of SCLK. All communication is done in blocks of 8 bits (bytes). First three bits of first byte transmitted after high to low transition of /SS define SPI operation mode. MSB bit is always transmitted first (valid for address and data). Read and Write modes support address auto incrementing, which means that in case after the address and first data byte some additional data bytes are sent (read), they are written to (read from) addresses incremented by '1'.

SPI interface supports the following modes:

- Read and write of the SPI Interface internal registers

- · Read and write of the EEPROM

- Read and write of the FIFO

- Sending direct commands

Please note that the only SPI operations, which are allowed when logic and EEPROM are supplied from VP\_SPI, are reading and writing of EEPROM and registers (see also Power Manager)

Page 30

Document Feedback

[v1-04] 2016-Jan-07

Figure 39: SPI Modes

|                   |      | MOD | E Patte |         |    |    |    |    |                                                        |                                                                                     |  |

|-------------------|------|-----|---------|---------|----|----|----|----|--------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| MODE              | MODE |     |         | Trailer |    |    |    |    | MODE Related Data                                      |                                                                                     |  |

|                   | M2   | M1  | MO      | C4      | C3 | C2 | C1 | C0 |                                                        |                                                                                     |  |

| Register<br>Write | 0    | 0   | 0       | A4      | А3 | A2 | A1 | A0 | Data byte (or n<br>case of auto in                     | •                                                                                   |  |

| Register<br>Read  | 0    | 0   | 1       | A4      | А3 | A2 | A1 | A0 | Data byte (or more bytes in case of auto incrementing) |                                                                                     |  |

| EEPROM<br>Write   | 0    | 1   | 0       | 0       | 0  | 0  | 0  | 0  | Word 4 bytes of<br>Address byte word data              |                                                                                     |  |

| EEPROM<br>Read    | 0    | 1   | 1       | 1       | 1  | 1  | 1  | 1  | Word<br>Address byte                                   | 4 bytes of<br>word data (or<br>multiple<br>words in case<br>of auto<br>incrementing |  |

| FIFO Load         | 1    | 0   | 0       | 0       | 0  | 0  | 0  | 0  | One or more bytes of FIFO data                         |                                                                                     |  |

| FIFO Read         | 1    | 0   | 1       | 1       | 1  | 1  | 1  | 1  | One or more bytes of FIFO data                         |                                                                                     |  |

| COMMAND<br>Mode   | 1    | 1   | C5      | C4      | C3 | C2 | C1 | C0 |                                                        |                                                                                     |  |

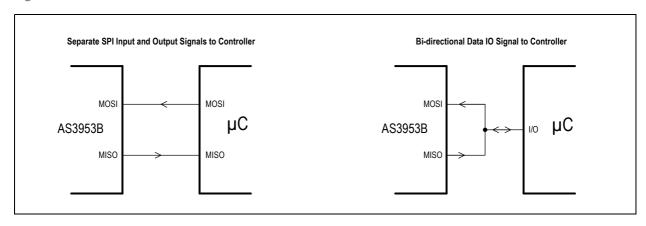

MISO output is usually in tristate, it is only driven when output data is available. Due to this the MOSI and the MISO can be externally shorted to create a bidirectional signal.

During the time the MISO output is in tristate, it is possible to switch on a 10 k $\Omega$  pull-down by activating option bits *miso\_pd1* and *miso\_pd2* in IO Configuration Register.

Figure 40: Signal to Controller

ams Datasheet Page 31

[v1-04] 2016-Jan-07 Document Feedback

# Writing of Data to Addressable Registers (Register Write Mode)

Following figures show cases of writing a single byte and writing multiple bytes with auto-incrementing address. After the SPI operation mode bits, the address of register to be written is provided. Then one or more data bytes are transferred from the SPI, always from the MSB to the LSB. The data byte is written in register on falling edge of its last clock. In case the communication is terminated by putting /SS high before a packet of 8 bits composing one byte is sent, writing of this register is not performed. In case the register on the defined address does not exist or it is a read only register no write is performed.

**Note(s):** When the AS3953B is powered via vp\_SPI and not via field; the registers and EEPROM can be readout. When CS is set to low, after 50us of the falling edge, the Registers and the EEPROM can be readout. Nevertheless, if there is no activity for 1ms, there is a timeout and the logic goes to sleep, hence losing the values in the registers. (EEPROM values are retained).

Figure 41: Writing of a Single Register

Figure 42: Writing of Register Data with Auto-Incrementing Address

Page 32

Document Feedback

[v1-04] 2016-Jan-07

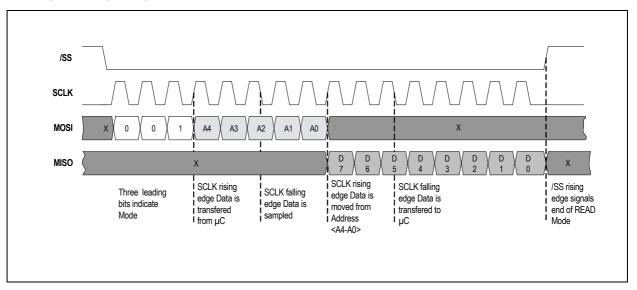

## Reading of Data from Addressable Registers (Register Read Mode)

After the SPI operation mode bits the address of register to be read has to be provided from the MSB to the LSB. Then one or more data bytes are transferred to MISO output, always from the MSB to the LSB. As in case of the write mode also the read mode supports auto-incrementing address.

MOSI is sampled at the falling edge of SCLK (like shown in the following diagrams); data to be read from the AS3953B internal register is driven to MISO pin on rising edge of SCLK and is sampled by the master at the falling edge of SCLK.

In case the register on defined address does not exist all '0' data is sent to MISO.

In the following figure example for reading of single byte is given.

Figure 43: Reading of a Single Register

ams Datasheet Page 33

[v1-04] 2016-Jan-07 Document Feedback

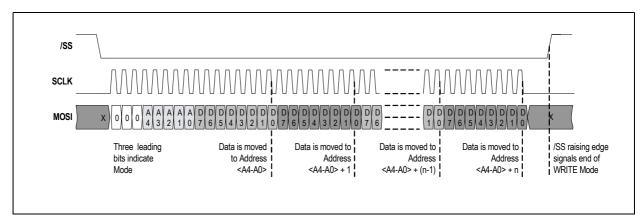

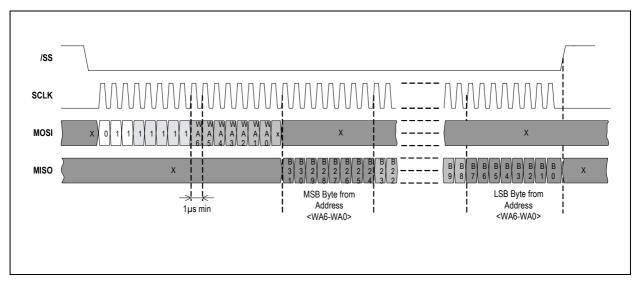

#### Writing and Reading of EEPROM Through SPI

EEPROM data can be read and written also through SPI interface. Due to possible conflict with RFID interface trying to access the EEPROM in ISO 14443A - level4 mode, access is granted to SPI only in case the PICC AFE is not active.

In all other modes defined in Mode Definition Registers, the EEPROM can be accessed via SPI when the RF field is active.

Activity of the PICC AFE can be checked by observing *hf\_pon* bit of RFID Status Display Register. In case PICC AFE is activated while the EEPROM writing or reading operation is going on, this operation is interrupted, and *l\_ee\_spi* IRQ is sent.

#### **Word Address Byte**

Both EEPROM modes (Read and Write) use Word Address byte to define the address of EEPROM word which is accessed. 7 MSB bits of the Address Byte are used to define the address; while the last bit is "don't care" (utilized to synchronize EEPROM access).

**Note(s):** The valid range for the Word Address byte is from 0000 000xb to 0011 111xb (EEPROM words from 00h to 1Fh).

Figure below defines the EEPROM Word Address byte.

Figure 44: EEPROM Word Address Byte

|                        | В7  | В6  | B5  | В4  | В3  | B2  | B1  | В0 |

|------------------------|-----|-----|-----|-----|-----|-----|-----|----|

| EEPROM Word<br>Address | WA6 | WA5 | WA4 | WA3 | WA2 | WA1 | WAO | х  |

#### **EEPROM Write**

In order to program an EEPROM word six bytes have to be sent (mode byte, word address byte and 4 bytes of word data, all of them MSB first)). Actual programming of EEPROM is started with rising edge of /SS signal which terminated the **EEPROM Write** command. During EEPROM programming the controller is not allowed to start another SPI activity. Controller is informed about the end of EEPROM programming by sending an interrupt (an interrupt flag is set in the Auxiliary Interrupt Register). *I\_eew* flag is set in case EEPROM programming is normally finished; in case of an error (writing to write protected word, writing to non-existent address) an error flag (*I\_er\_eew*) is set. Typical EEPROM programing time for one word is 8ms.

**Note(s):** Word data is sent MSB first which is opposite to RFID EEPROM programming where LSB is sent first.

Page 34

Document Feedback [v1-04] 2016-Jan-07

### **EEPROM Read**

In order to read data from EEPROM first a mode byte is sent, followed by the word address byte (MSB first). Then one or more words of data with address auto incrementing (packets of 4 bytes) are transferred to MISO output, always from the MSB to the LSB. MOSI is sampled at the falling edge of SCLK; data to be read from the AS3953B EEPROM is driven to MISO pin on rising edge of SCLK and is sampled by the master at the falling edge of SCLK. In case the word on defined address does not exist all '0' data is sent to MISO.

Please note that SCLK frequency should not exceed 1MHz during EEPROM Read (limited by EEPROM read access time).

Figure 45: Reading of EEPROM Page

ams Datasheet Page 35

[v1-04] 2016-Jan-07 Document Feedback

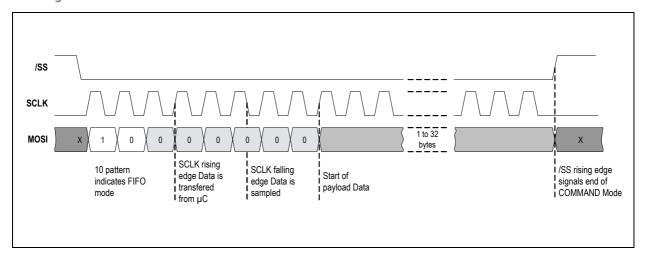

#### **Loading Transmitting Data into FIFO**

Loading the transmitting data into the FIFO is similar to writing data into an addressable registers. Difference is that in case of loading more bytes all bytes go to the FIFO. The command mode code 10 indicates FIFO operations. In case of loading transmitting data into FIFO all bits <C5 -C0> are set to '0'. Then a bit-stream, the data to be sent (1 to 32 bytes), can be transferred.

Figure 46 shows how to load the transmitting data into the FIFO.

Figure 46: Loading of FIFO

### Reading Received Data from FIFO

Reading received data from the FIFO is similar to reading data from an addressable registers. Difference is that in case of reading more bytes they all come from the FIFO. The command mode code 10 indicates FIFO operations. In case of reading the received data from the FIFO all bits  $<\!C5-C0\!>$  are set to '1'. On the following SCLK rising edges the data from FIFO appears as in case of read data from addressable registers. In case the command is terminated by putting /SS high before a packet of 8 bits composing one byte is read that particular byte is considered read.

Page 36

Document Feedback

[v1-04] 2016-Jan-07

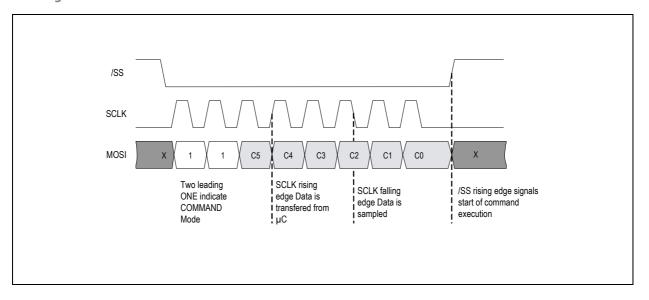

### **Direct Command Mode**

Direct Command Mode has no arguments, so a single byte is sent. SPI operation mode bits 11 indicate Direct Command Mode. The following six bits define command code, sent MSB to the LSB. The command is executed on falling edge of last clock.

Figure 47: Sending a Direct Command

ams Datasheet Page 37

[v1-04] 2016-Jan-07 Document Feedback

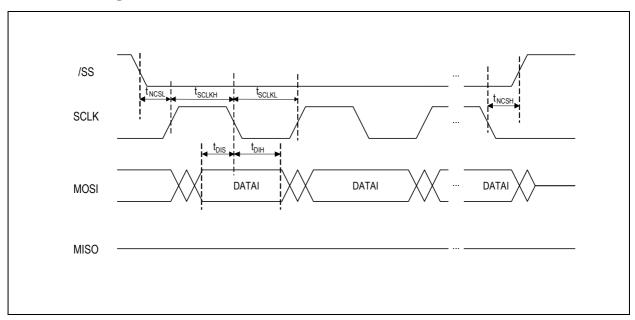

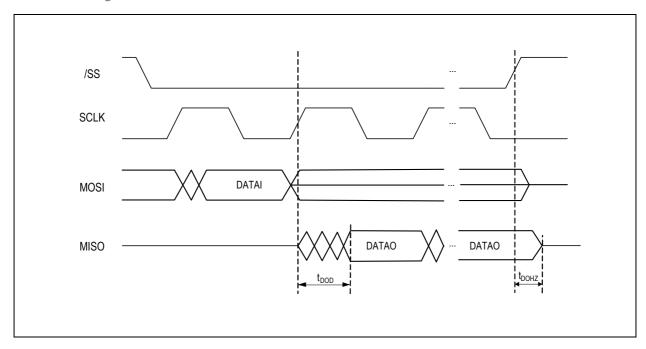

# **SPI Timing**

Figure 48: **Timing Parameters**

| Symbol                                                                                | Parameter                                                             | Min | Тур | Max | Units | Note                                                                                                                                                                                          |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                       | <b>General Timing</b> (VDD = VDD_IO = VDD_D = 3.3V, Temperature 25°C) |     |     |     |       |                                                                                                                                                                                               |  |

| T <sub>SCLK</sub>                                                                     | SCLK period                                                           | 200 |     |     | ns    | T <sub>SCLK</sub> =T <sub>SCLKL</sub> +T <sub>SCLKH</sub> , during<br>EEPROM read the SCLK period<br>has to be increased to 1µs (this<br>limitation is imposed by<br>EEPROM read access time) |  |

| T <sub>SCLKL</sub>                                                                    | SCLK low                                                              | 80  |     |     | ns    |                                                                                                                                                                                               |  |

| T <sub>SCLKH</sub>                                                                    | SCLK high                                                             | 80  |     |     | ns    |                                                                                                                                                                                               |  |

| T <sub>SSH</sub>                                                                      | SPI reset (/SS high)                                                  | 50  |     |     | ns    |                                                                                                                                                                                               |  |

| T <sub>NCSL</sub>                                                                     | /SS falling to SCLK rising                                            | 25  |     |     | ns    | first SCLK pulse                                                                                                                                                                              |  |