# **DDR3 SDRAM Reduced tFAW Addendum**

## MT41J256M16 – 32 Meg x 16 x 8 Banks

## Features

- $V_{DD} = V_{DDQ} = 1.5V \pm 0.075V$

- 1.5V center-terminated push/pull I/O

- Differential bidirectional data strobe

- 8*n*-bit prefetch architecture

- Differential clock inputs (CK, CK#)

- 8 internal banks

- Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals

- Programmable CAS READ latency (CL)

- Posted CAS additive latency (AL)

- Programmable CAS WRITE latency (CWL) based on  ${}^{\mathrm{t}}\!\mathrm{CK}$

- Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS])

- Selectable BC4 or BL8 on-the-fly (OTF)

- Self refresh mode

- $T_C of 0^{\circ}C to 95^{\circ}C$

- 64ms, 8192 cycle refresh at 0°C to 85°C

32ms, 8192 cycle refresh at 85°C to 95°C

- Self refresh temperature (SRT)

**Table 1: Key Timing Parameters**

- Write leveling

- Multipurpose register

- Output driver calibration

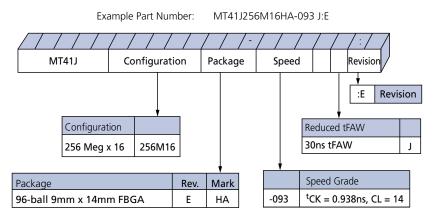

## Options Marking

| Configuration                                         | -      |

|-------------------------------------------------------|--------|

| – 256 Meg x 16                                        | 256M16 |

| • FBGA package (Pb-free) – x16                        |        |

| – 96-ball (8mm x 14mm)                                | HA     |

| • Timing – cycle time                                 |        |

| - 938ps @ CL = 14 (DDR3-2133)                         | -093   |

| Reduced tFAW                                          |        |

| - <sup>t</sup> FAW = 30ns <sup>1</sup>                | J      |

| <ul> <li>Operating temperature</li> </ul>             |        |

| - Commercial (0°C $\leq$ T <sub>C</sub> $\leq$ +95°C) | None   |

| Revision                                              | :E     |

- Notes: 1. Standard DDR3-2133, 2KB page size, <sup>t</sup>FAW specification is 35ns.

- For complete device functionality and specifications, refer to the standard 4Gb DDR3 SDRAM data sheet found at www.micron.com. The information in this data sheet supersedes the standard data sheet.

CL (ns) 13.09

| Speed Grade | Data Rate (MT/s) | <sup>t</sup> FAW | Target <sup>t</sup> RCD- <sup>t</sup> RP-CL | <sup>t</sup> RCD (ns) | <sup>t</sup> RP (ns) |

|-------------|------------------|------------------|---------------------------------------------|-----------------------|----------------------|

| -093        | 2133             | 30ns             | 14-14-14                                    | 13 09                 | 13 09                |

#### Table 2: Addressing

| Parameter         | 256 Meg x 16          |

|-------------------|-----------------------|

| Configuration     | 32 Meg x 16 x 8 banks |

| Refresh count     | 8К                    |

| Row addressing    | 32K (A[14:0])         |

| Bank addressing   | 8 (BA[2:0])           |

| Column addressing | 1K (A[9:0])           |

| Page size         | 2КВ                   |

PDF: 09005aef857c6ed1 4Gb\_DDR3\_SDRAM\_tFAW.pdf - Rev. B 3/14 EN Products and specifications discussed herein are subject to change by Micron without notice.

#### Figure 1: DDR3 Part Numbers

Note: 1. Not all options listed can be combined to define an offered product. Use the part catalog search on http://www.micron.com for available offerings.

### **FBGA Part Marking Decoder**

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the part number. For a quick conversion of an FBGA code, see the FBGA Part Marking Decoder on Micron's Web site: http://www.micron.com.

## **AC Timing Adjustments**

#### Table 3: Electrical Characteristics and AC Operating Conditions for Speed Extensions

Notes 1–8 apply to the entire table

|                            |                  |                  | DDR3-2133 |     |      |       |  |  |  |

|----------------------------|------------------|------------------|-----------|-----|------|-------|--|--|--|

| Parameter                  |                  | Symbol           | Min       | Max | Unit | Notes |  |  |  |

| Command and Address Timing |                  |                  |           |     |      |       |  |  |  |

| Four ACTIVATE windows      | 2KB page<br>size | <sup>t</sup> FAW | 30        | _   | ns   | 9     |  |  |  |

- Notes: 1. AC timing parameters are valid from specified T<sub>C</sub> MIN to T<sub>C</sub> MAX values.

- 2. All voltages are referenced to V<sub>ss</sub>.

- 3. Output timings are only valid for  $R_{ON34}$  output buffer selection.

- 4. The unit <sup>t</sup>CK (AVG) represents the actual <sup>t</sup>CK (AVG) of the input clock. The unit CK represents one clock cycle of the input clock, counting the actual clock edges.

- 5. AC timing and I<sub>DD</sub> tests may use a V<sub>IL</sub>-to-V<sub>IH</sub> swing of up to 900mV in the test environment, but input timing is still referenced to V<sub>REF</sub> (except <sup>t</sup>IS, <sup>t</sup>IH, <sup>t</sup>DS, and <sup>t</sup>DH use the AC/DC trip points and CK, CK# and DQS, DQS# use their crossing points). The minimum slew rate for the input signals used to test the device is 1 V/ns for single-ended inputs (DQs are at 2V/ns for DDR3-1866 and DDR3-2133) and 2 V/ns for differential inputs in the range between V<sub>IL(AC)</sub> and V<sub>IH(AC)</sub>.

- 6. All timings that use time-based values (ns, μs, ms) should use <sup>t</sup>CK (AVG) to determine the correct number of clocks (Table 3 (page 3) uses CK or <sup>t</sup>CK [AVG] interchangeably). In the case of noninteger results, all minimum limits are to be rounded up to the nearest whole integer, and all maximum limits are to be rounded down to the nearest whole integer.

- 7. Strobe or DQSdiff refers to the DQS and DQS# differential crossing point when DQS is the rising edge. Clock or CK refers to the CK and CK# differential crossing point when CK is the rising edge.

- This output load is used for all AC timing (except ODT reference timing) and slew rates. The actual test load may be different. The output signal voltage reference point is V<sub>DDQ</sub>/2 for single-ended signals and the crossing point for differential signals.

- 9. For these parameters, the DDR3 SDRAM device supports <sup>t</sup>*n*PARAM (*n*CK) = RU(<sup>t</sup>PARAM [*ns*]/<sup>t</sup>CK[AVG] [*ns*]), assuming all input clock jitter specifications are satisfied. For example, the device will support <sup>t</sup>*n*RP (*n*CK) = RU(<sup>t</sup>RP/<sup>t</sup>CK[AVG]) if all input clock jitter specifications are met. This means that for DDR3-800 6-6-6, of which <sup>t</sup>RP = 5*ns*, the device will support <sup>t</sup>*n*RP = RU(<sup>t</sup>RP/<sup>t</sup>CK[AVG]) = 6 as long as the input clock jitter specifications are met. That is, the PRECHARGE command at T0 and the ACTIVATE command at T0 + 6 are valid even if six clocks are less than 15*ns* due to input clock jitter.

- 8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900 www.micron.com/productsupport Customer Comment Line: 800-932-4992 Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

- This data sheet contains minimum and maximum limits specified over the power supply and temperature range set forth herein.

Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur.