## scale Semiconductor

Advance Information

Document Number: MC34726

Rev. 2.0, 1/2014

**VRoHS**

# 300 mA High Efficiency Low **Quiescent Current Synchronous Buck Regulator With Z-mode**

The 34726 is a high efficiency, low quiescent current ( $I_{\Omega}$ ), synchronous buck regulator, implementing Freescale's innovative Z-mode architecture. Freescale's Z-mode architecture greatly improves the ripple performance during light load currents, but still maintains a low guiescent current of 65µA, at no load in "Sleepy" Z-mode.

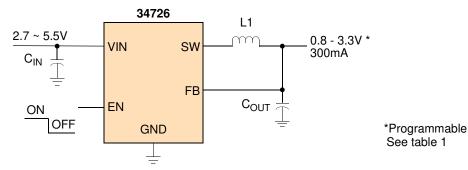

The 34726 accepts an input voltage in the range of 2.7 to 5.5 V, making it ideally suited for single cell Li-lon based applications. Factory preset output voltages, ranging from 0.8 to 3.3 V, reduce the number of required auxiliary components. The part is able to provide 300 mA of continuous load current across the input and the output voltage ranges.

The 34726 switches at 2.0 MHz to allow the use of small, surface mount inductors and capacitors to save precious board space.

The 34726 is available in the small, space saving, and low cost, 2x2 UDFN-8 packages. The part is guaranteed for operation over the -25°C to 85°C temperature range.

#### **Features**

- 94% peak efficiency

- · 2.0 MHz switching frequency

- · 2.7 to 5.5 V input voltage range

- Automatic transition to energy saving light load Z-mode (low ripple)

- Fixed output voltage options from 0.8 to 3.3 V

- 65 μA guiescent current during sleepy Z-mode

- 300 mA maximum continuous output current

- Internal 2.0 ms soft start

- Thermal and over-current protection

- 0.1 μA quiescent current in shutdown (disabled)

- Ultra thin 2x2 UDFN package

- Pb-free packaging designated by suffix code FC

## 34726

#### POWER MANAGEMENT IC

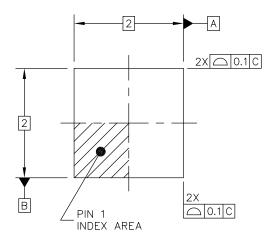

**Bottom View**

FC SUFFIX (PB-FREE) 98ASA10787D **8-PIN UDFN** 2X2

| ORDERING INFORMATION                       |                                        |         |  |  |  |

|--------------------------------------------|----------------------------------------|---------|--|--|--|

| Device                                     | Temperature<br>Range (T <sub>A</sub> ) | Package |  |  |  |

| Refer to Table 1. <u>Device Variations</u> | -25°C to 85°C                          | 8-UDFN  |  |  |  |

Figure 1. 34726 Typical Operating Circuit

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

## **DEVICE VARIATIONS**

## **Table 1. Device Variations**

| Freescale Part No. | V <sub>IN</sub> Range | Output Voltage <sup>(1)</sup> | Maximum Load Current  | Switch Frequency (MHz) <sup>(2)</sup> |

|--------------------|-----------------------|-------------------------------|-----------------------|---------------------------------------|

| MC34726AFC         | 2.7 - 5.5 V           | 1.2 V                         | 300 mA                | 2.0                                   |

| MC34726BFC         | 2.7 - 5.5 V           | 1.8 V                         | 300 mA                | 2.0                                   |

| MC34726CFC         | 3.6 - 5.5 V           | 3.3 V                         | 300 mA                | 2.0                                   |

| MC34726DFC         | 2.7 - 5.5 V           | 1.5 V                         | 300 mA                | 2.0                                   |

| MC34726EFC         | 2.7 - 5.5 V           | 2.5 V                         | 300 mA <sup>(3)</sup> | 2.0                                   |

- 1. Output voltages of: 0.8 V, 0.9 V, 1.0 V, 1.1 V, 1.3 V, 1.4 V, 1.85 V, 2.0 V options available on request. Contact Freescale sales.

- 2. Factory programmable at 2.0 MHz or 4.0 Mhz. Contact Freescale sales for availability of the 4.0 MHz functionality.

- 3. The minimum input voltage must be higher than 2.8 V for 300 mA of load current.

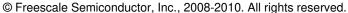

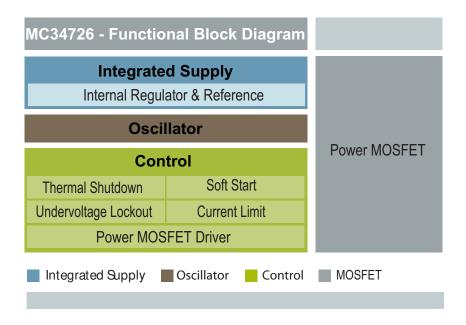

## **INTERNAL BLOCK DIAGRAM**

Figure 2. 34726 Simplified Internal Block Diagram

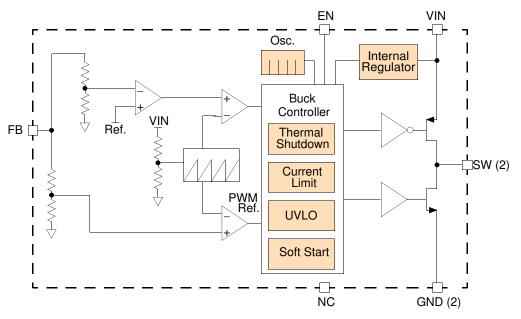

## **PIN CONNECTIONS**

Figure 3. 34726 Pin Connections

Table 2. 34726 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 10.

| Pin Number | Pin Name | Pin Function | Formal Name          | Definition                                          |

|------------|----------|--------------|----------------------|-----------------------------------------------------|

| 1          | VIN      | Input        | Supply Voltage Input | Power input                                         |

| 2          | GND      | Ground       | Ground               | Ground                                              |

| 3          | GND      | Ground       | Ground               | Low noise ground                                    |

| 4          | EN       | Input        | Enable               | Active high enable input                            |

| 5          | FB       | Input        | Feedback Input       | Feedback of the output voltage                      |

| 6          | NC       | N/A          | No Connection        | Internally not connected. Connect to GND externally |

| 7          | SW       | Output       | Switching Node       | This terminal connects to the output inductor       |

| 8          | SW       | Output       | Switching Node       | This terminal connects to the output inductor       |

## **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                      | Symbol                           | Value       | Unit |

|--------------------------------------------------------------|----------------------------------|-------------|------|

| ELECTRICAL RATINGS                                           |                                  |             | _L   |

| All pins voltages                                            | $V_{IN}, V_{EN}, V_{FB}, V_{SW}$ | -0.3 to 6.0 | V    |

| ESD Voltage <sup>(1)</sup>                                   | V <sub>ESD</sub>                 |             | V    |

| Human Body Model (HBM)                                       |                                  | ±2000       |      |

| Machine Model (MM)                                           |                                  | ±200        |      |

| THERMAL RATINGS                                              | ,                                |             | •    |

| Operating Ambient Temperature Range                          | T <sub>A</sub>                   | -25 to +85  | °C   |

| Storage Temperature Range                                    | T <sub>STG</sub>                 | -25 to +150 | °C   |

| Maximum Lead Temperature <sup>(2),(3)</sup>                  | T <sub>PPRT</sub>                | Note 3      | °C   |

| Junction Temperature                                         | TJ                               |             | °C   |

| Operating Junction Temperature                               |                                  | 125         |      |

| Maximum Junction Temperature                                 |                                  | +150        |      |

| Thermal Resistance <sup>(4)</sup>                            |                                  |             | °C/W |

| Junction-to-Case                                             | $R_{	hetaJC}$                    | 104         |      |

| Junction-to-Ambient                                          | $R_{	hetaJA}$                    | 122         |      |

| Power Dissipation                                            | P <sub>D</sub>                   |             | W    |

| Continuous (Derate 3.0 mW/°C and over T <sub>A</sub> = 70°C) |                                  | 0.5         |      |

- 1. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), and the Machine Model (MM) ( $C_{ZAP} = 200 \text{ pF}$ ,  $R_{ZAP} = 0 \Omega$ ).

- 2. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 3. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL). Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- 4. Device mounted on the Freescale EVB test board per JEDEC DESD51-2.

#### STATIC ELECTRICAL CHARACTERISTICS

#### **Table 4. Static Electrical Characteristics**

Characteristics noted under conditions; 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$  5.5 V, 0.8 V  $\leq$  V<sub>OUT</sub>  $\leq$  3.3 V, -25°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, C<sub>IN</sub> = C<sub>OUT</sub> = 4.7  $\mu$ F, L1 = 4.7  $\mu$ H (See Figure 1), unless otherwise noted. The typical specifications are measured at the following conditions; T<sub>A</sub> = +25°C, V<sub>IN</sub> = 3.6 V, f<sub>SW</sub> = 2.0 MHz with the typical operating circuit (See Figure 1), unless otherwise noted.

| Characteristic                                                                                         | Symbol                          | Min | Тур | Max | Unit             |

|--------------------------------------------------------------------------------------------------------|---------------------------------|-----|-----|-----|------------------|

| Supply Voltage                                                                                         | V <sub>IN</sub>                 | 2.7 | -   | 5.5 | ٧                |

| Output Voltage (Factory preset)                                                                        | V <sub>OUT</sub>                | 0.8 | -   | 3.3 | ٧                |

| Output Current                                                                                         | I <sub>OUT</sub>                | 300 | -   | -   | mA               |

| Total Supply Current <sup>(5)</sup>                                                                    | I <sub>DIS</sub>                |     |     |     | μА               |

| Regulator disabled                                                                                     |                                 | -   | 0.1 | 1.0 |                  |

| Quiescent Current (Switching)                                                                          | IQ                              |     |     |     | μА               |

| Sleepy Z-mode and $I_{LOAD} = 0 \text{ mA}$                                                            |                                 | -   | 65  | 85  |                  |

| Current Limit                                                                                          | I <sub>PK</sub>                 |     |     |     | mA               |

| Current rising at high side                                                                            |                                 | -   | 450 | -   |                  |

| Output Voltage Accuracy (% of output voltage)                                                          | $\Delta V_{OUT}$                |     |     |     | V <sub>OUT</sub> |

| Overload and temperature                                                                               |                                 | -3% | =   | 3%  |                  |

| UVLO Threshold <sup>(6)</sup>                                                                          | $V_{UVLO}$                      |     |     |     | V                |

| V <sub>IN</sub> : 2.7 -5.5 V                                                                           |                                 |     |     |     |                  |

| V <sub>IN</sub> rising                                                                                 |                                 | -   | =   | 2.7 |                  |

| V <sub>IN</sub> falling                                                                                |                                 | 2.5 | =   | -   |                  |

| Enable Voltage                                                                                         | $V_{EN}$                        |     |     |     | V                |

| Regulator operating                                                                                    |                                 | 1.6 | -   | -   |                  |

| Regulator shutdown                                                                                     |                                 | -   | -   | 0.4 |                  |

| High Side Power MOSFET On Resistance                                                                   | R <sub>DS(ON)H</sub>            |     |     |     | mΩ               |

| $V_{IN} = 3.6 \text{ V}, V_{OUT} = 1.8 \text{ V}, T_A = 40^{\circ}\text{C}, I_{LOAD} = 150 \text{ mA}$ |                                 | -   | 250 | -   |                  |

| Low Side Power MOSFET On Resistance                                                                    | $R_{DS(ON)L}$                   |     |     |     | mΩ               |

| $V_{IN} = 3.6 \text{ V}, V_{OUT} = 1.8 \text{ V}, T_A = 40^{\circ}\text{C}, I_{LOAD} = 150 \text{ mA}$ |                                 | -   | 350 | -   |                  |

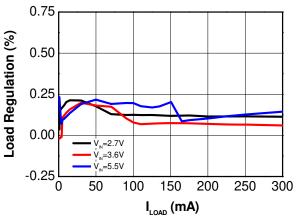

| Load Regulation                                                                                        | $\Delta V_{OUT}/\Delta I_{OUT}$ |     |     |     | %                |

| 1.0 mA < $I_{LOAD}$ < 300 mA and $V_{OUT}$ = 1.8 $V$                                                   |                                 | -   | 0.5 | -   |                  |

| Line Regulation                                                                                        | $\Delta V_{OUT}/\Delta V_{IN}$  |     |     |     | %                |

| $V_{IN} = 2.7 \text{ to } 5.5 \text{ V}$                                                               |                                 | -   | 0.5 | -   |                  |

| Start-up Overshoot (% of output voltage)                                                               | V <sub>STO</sub>                |     |     |     | V <sub>OUT</sub> |

| $I_{LOAD}$ = 0 mA, $V_{OUT}$ = 1.8 V and $C_{OUT}$ = 4.7 $\mu F$                                       |                                 | -   | 3%  | -   |                  |

| Thermal Shutdown Threshold (Junction Temperature)                                                      | T <sub>STDN</sub>               | -   | 140 | -   | °C               |

| Thermal Shutdown Hysteresis (Junction Temperature)                                                     | T <sub>HYSTR</sub>              | -   | 10  | -   | °C               |

- 5. Maximum  $I_{DIS}$  measured at  $V_{IN}$  = 3.6 V and  $T_A$  = 25°C.

- 6. For a product with a  $V_{OUT}$  of 3.3 V and a  $V_{IN}$  minimum less than 3.6 V, the  $V_{OUT}$  value will track (drop below 3.3 V)  $V_{IN}$  down to a value of 2.5 V, where the UVLO shutdown mechanism will activate.

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 5. Dynamic Electrical Characteristics**

Characteristics noted under conditions; 2.7 V  $\leq$  V<sub>IN</sub>  $\leq$ 5.5 V, 0.8 V  $\leq$  V<sub>OUT</sub>  $\leq$ 3.3 V, -20°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, C<sub>IN</sub> = C<sub>OUT</sub> = 4.7  $\mu$ F, L1 = 4.7  $\mu$ H (See <u>Figure 1</u>), unless otherwise noted. The typical specifications are measured at the following conditions; T<sub>A</sub> = +25°C, V<sub>IN</sub> = 3.6 V, f<sub>SW</sub> = 2.0 MHz with the typical operating circuit (See <u>Figure 1</u>), unless otherwise noted.

| Characteristic                     | Symbol           | Min | Тур | Max | Unit |

|------------------------------------|------------------|-----|-----|-----|------|

| Switching Frequency <sup>(7)</sup> | f <sub>SW</sub>  | 1.8 | 2.0 | 2.2 | MHz  |

| Maximum Duty Cycle <sup>(8)</sup>  | D <sub>MAX</sub> |     |     |     | %    |

| Measured from SW pin               |                  | 95  | -   | 100 |      |

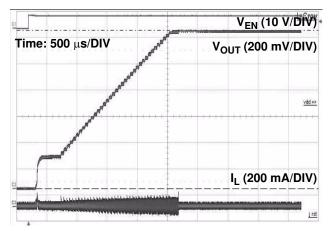

| Internal Soft-start Timer          | t <sub>S</sub>   |     |     |     | ms   |

| V <sub>OUT</sub> Rise Time         |                  | -   | 2.0 | -   |      |

- 7.  $f_{SW}$  can be factory programmed to  $\pm 20\%$  of nominal 2.0 MHz.

- 8. The maximum duty limits the range of output voltages achievable for a given input voltage.

#### **ELECTRICAL PERFORMANCE CURVES**

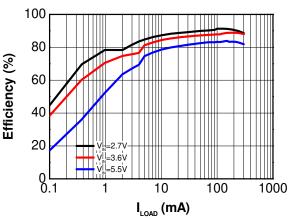

Figure 4. Efficiency vs. Load Current  $V_{IN} = 3.6 \text{ V}, V_{OUT} = 1.8 \text{ V}, T_A=25^{\circ}\text{C}$

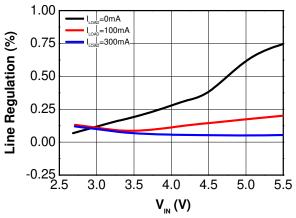

Figure 5. Line Regulation  $V_{IN}$  is 2.7 V to 5.5 V and  $V_{OUT}$  is 1.8 V,  $T_A = 25 ^{\rm o} C$

Figure 6. Load Regulation 1.0 mA < I<sub>LOAD</sub> < 300 mA, V<sub>OUT</sub> = 1.8 V

Figure 7. Start-up Response I<sub>LOAD</sub> = 0 mA, V<sub>OUT</sub>=1.2 V

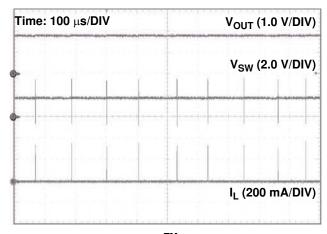

Figure 8. Sleepy Z-Mode<sup>TM</sup> Switching Waveforms  $V_{IN} = 3.6 \text{ V}$ ,  $V_{OUT} = 1.8 \text{ V}$  and  $I_{LOAD} = 1.0 \text{ mA}$

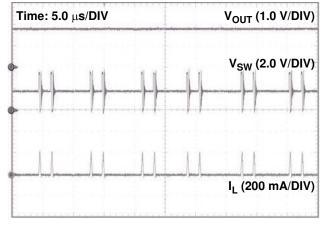

Figure 9. Z-Mode<sup>TM</sup> Switching Waveforms  $V_{IN} = 3.6 \text{ V}$ ,  $V_{OUT} = 1.8 \text{ V}$  and  $I_{LOAD} = 10 \text{ mA}$

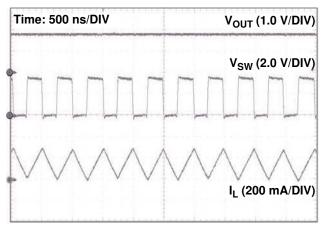

Figure 10. CCM Switching Waveforms  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V and  $I_{LOAD}$  = 150 mA

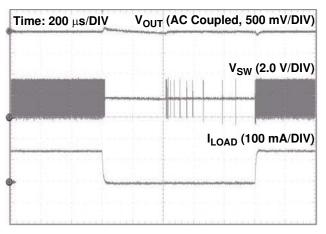

Figure 11. Load Transient in Sleepy Z-Mode<sup>TM</sup>  $V_{IN} = 3.6 \text{ V}, I_{LOAD} = 1.0 \text{ to } 150 \text{ mA}$

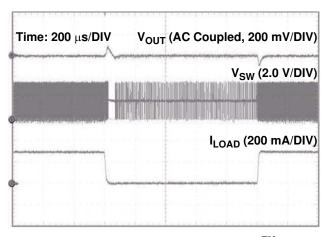

Figure 12. Load Transient in Z-Mode<sup>TM</sup>  $V_{IN} = 3.6 \text{ V}, I_{LOAD} = 10 \text{ to } 300 \text{ mA}$

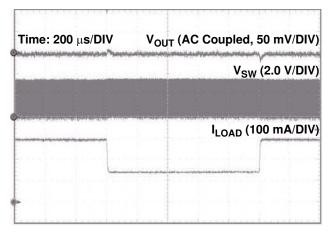

Figure 13. Load Transient in CCM  $V_{IN}$  = 3.6 V,  $I_{LOAD}$  = 150 to 300 mA

## **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

The 34726 is a high efficiency, synchronous, buck regulator, utilizing a voltage mode control architecture with feed forward. It is capable of providing a 300 mA load current for output voltages of 0.8 to 3.3 V, from a single input voltage rail between 2.7 and 5.5 V.

In a buck converter, most of the losses at high output loads are due to conduction losses in the power train, but at light output loads, the conduction losses are reduced and most of the losses become switching losses. Using Freescale's Z-mode architecture, the 34726, at light output loads, will smoothly transition into a lower switching frequency, thus improving its efficiency.

#### **FUNCTIONAL PIN DESCRIPTION**

## **SUPPLY VOLTAGE INPUT (VIN)**

2.7 to 5.5 V DC power input. Bypass with a  $4.7~\mu F$  ceramic capacitor as close as possible to the VIN and GND pins.

## **GROUND (GND)**

Ground.

#### **ENABLE (EN)**

Active high enable input. EN is over-voltage protected to 6.0 V, independent of the supply voltage. Drive with a logic high signal (or connect to VIN) for normal operation. Drive with a logic low signal, or connect to GND will disable the 34726.

## FEEDBACK INPUT (FB)

Feedback of the output voltage.

## **SWITCHING NODE (SW)**

This terminal connects to the output inductor. The node internally connects the drain of both high side MOSFET and low side MOSFET.

#### NO CONNECTION (NC)

Internally not connected. Connect to GND externally.

## FUNCTIONAL INTERNAL BLOCK DESCRIPTION

Figure 14. 34726 Functional Internal Block Diagram

#### INTEGRATED SUPPLY

## INTERNAL REGULATOR AND REFERENCE

The internal regulator and reference block steps down the high input voltage to lower voltage to power all the internal blocks, and provides the reference voltage for the other internal blocks.

## **OSCILLATOR**

The oscillator block provides 2.0 MHz clock signal to the controller.

#### CONTROLLER

#### THERMAL SHUTDOWN

The thermal shutdown block monitors the die temperature. Once the die temperature reaches its threshold, this block turns off the device to prevent the further die temperature rise.

#### **SOFT-START**

The soft-start block controls the output voltage ramp after the device is enabled, to limit the in-rush current. The start-up time is internally set to approximately 2.0 ms, and is independent of input voltage, output voltage, or load current. The soft-start sequence also occurs upon recovery from any fault condition.

#### **UVLO**

The UVLO block monitors the input voltage. Once the input voltage is lower than the falling threshold voltage, this block turns off the device, to avoid unpredictable circuit behavior.

#### **CURRENT LIMIT**

The current limit block monitors the inductor current. When the peak inductor current reaches its current limit, this block turns off the high side MOSFET, to prevent the device and external components from damage.

#### **POWER-MOSFET DRIVER**

The power-MOSFET-driver block controls the phase of the diver signals and enhances the drive capability of these.

## **POWER-MOSFET**

The power-MOSFET block contains two power MOSFETs. One is a PMOS that passes the current from the input to the output, and the other one is an NMOS that provides the inductor current loop when PMOS is turned off.

34726

## **FUNCTIONAL DEVICE OPERATION**

#### **OPERATIONAL MODES**

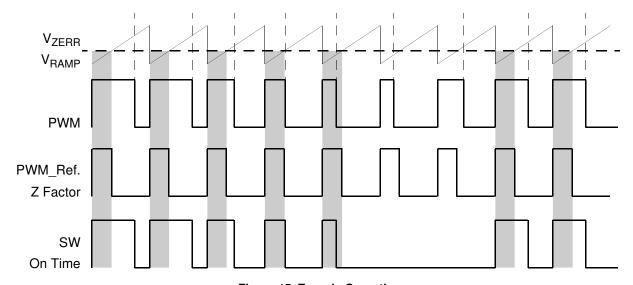

#### **Z-MODE OPERATION**

The 34726 operates as a typical fixed frequency, PWM regulator, at moderate to heavy load currents. As the load is decreased, such that operation transitions from continuous conduction mode (CCM) to discontinuous conduction mode (DCM), the duty cycle is reduced until it approaches 85% of the full load duty cycle. At this point the 34726 transitions into Z-mode operation, where the Z-mode Factor is 0.85. In Z-mode, the regulator skips pulses whenever the duty cycle is

below 85% of the CCM duty cycle. As the load decreases, this pulse skipping reduces the switching frequency and the switching losses thus improving efficiency. For example, if a light load demanded a 30% duty cycle at 2.0 MHz, with Z-mode this same load will require only  $(0.3/0.85)^2 \times 2.0$  MHz = 0.249 MHz switching frequency, hence switching losses will be reduced by almost ten fold. Figure 15 illustrates the transition to and the exit from Z-mode.

Figure 15. Z-mode Operation

## **SLEEPY Z-MODE OPERATION**

To improve low current efficiency, the 34726 transitions into the Sleepy Z-mode at load currents of approximately 1.0 mA and lower. This is accomplished by powering down

internal circuit blocks to lower the device's quiescent current. Additionally, the oscillator frequency drops to 250 kHz and the low side switch is turned off to emulate the operation of an asynchronous buck converter.

#### **DETAILED FUNCTIONAL DEVICE OPERATION**

## **OVER-CURRENT PROTECTION**

The 34726 implements two layers of protection during overload conditions. The first is a current limit feature to prevent the device and external components from damage. When the peak inductor current reaches the over-current limit, nominally 450 mA, the high side MOSFET turns off to provide cycle by cycle protection. If the over-current condition persists and the die temperature surpasses the over-temperature protection (OTP) threshold, this second layer of protection shuts down the device.

#### SHORT-CIRCUIT PROTECTION

When a short-circuit condition occurs on the output, typical regulators will tend to operate at maximum duty cycle. This condition can saturate the inductor and produce severe peak currents, resulting in damage to the device. The 34726 avoids this scenario by detecting output voltages below 0.5 V. Upon detection, the part re-starts continuously until the short circuit condition is removed, or the part surpasses its OTP threshold.

#### **OVER-TEMPERATURE PROTECTION**

To limit its operating temperature, the 34726 shuts down if the junction temperature of the switching MOSFET surpasses 140°C. If the junction temperature subsequently drops to 130°C, the 34726 restarts.

#### **SOFT-START OPERATION**

To limit the in-rush current, an internal timer controls the output voltage ramp after the part is enabled. The start-up time is internally set to approximately 2.0 ms and is independent of input voltage, output voltage, or load current. The soft-start sequence also occurs upon recovery from any fault condition.

#### **UNDER-VOLTAGE LOCK-OUT**

The UVLO threshold is set to 2.7 V for rising V<sub>IN</sub>, and to 2.5 V for falling  $V_{IN}$ . For a  $V_{OUT}$  of 3.3 V or 2.5 V, the  $V_{OUT}$ value will track  $V_{IN}$  below 3.6 V or 2.8 V until the 2.5 V falling V<sub>IN</sub> threshold is reached.

If the UVLO falling threshold is met, the part shuts down and will power-up again with soft-start, when the UVLO rising threshold is surpassed.

## TYPICAL APPLICATIONS

## **APPLICATION INFORMATION**

#### INPUT CAPACITOR

The input capacitor is used to minimize the input voltage transient that may cause instability when the load transient current is high. Typically a 4.7  $\mu F$  X5R ceramic capacitor is sufficient for most applications.

#### **OUTPUT CAPACITOR**

For stable operation and low output voltage ripple, an X5R ceramic capacitor of 4.7  $\mu$ F minimum value is needed.

Depending on the load transient current, a larger capacitance may be required.

#### **INDUCTOR SELECTION**

A 4.7  $\mu H$  low DC resistance inductor is typically used for the 34726 to guarantee the system stable operation.

## TYPICAL APPLICATIONS

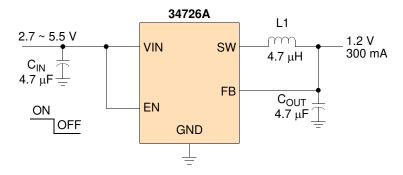

#### 1.2 V OUTPUT DC/DC CONVERTOR

Figure 16 shows a typical application using 34726A. CIN and COUT are typically 4.7  $\mu$ F/X5R ceramic capacitors. L1 is typically a 4.7  $\mu$ H low DC resistance inductor. The FB

connects to the output directly for monitoring the output voltage. Normally, the EN pin connects to the input supply directly to enable the regulator.

Figure 16. 1.2 V/300 mA DC/DC Convertor

## **PACKAGE DIMENSIONS**

For the most current package revision, visit <u>www.freescale.com</u> and perform a keyword search using the "98A" listed below.

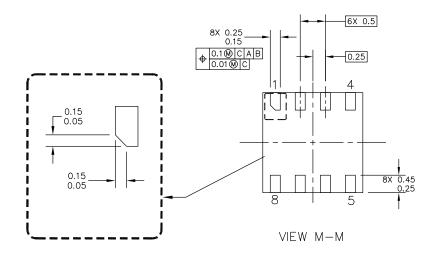

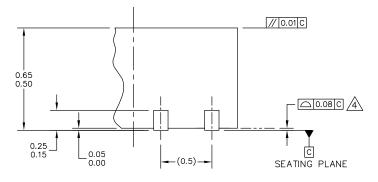

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                             | MECHANICA | L OUTLINE    | PRINT VERSION NO | T TO SCALE  |

|------------------------------------------------------------------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: PLASTIC ULTRA—THIN  FINE PITCH DUAL FLAT NON—LEADED  (UDFN) PACKAGE, 8 TERMINAL,  2 X 2 X 0.65, 0.5 PITCH |           | DOCUMENT NO  | ): 98ASA10787D   | REV: A      |

|                                                                                                                  |           | CASE NUMBER  | 2: 1944–02       | 10 DEC 2007 |

|                                                                                                                  |           | STANDARD: NO | N-JEDEC          |             |

FC SUFFIX 12-PIN 98ASA10787D REVISION A

34726

PIN 1 BACKSIDE IDENTIFIER

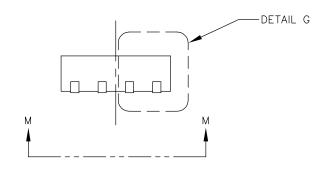

DETAIL G VIEW ROTATED 90° CW

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                                                          | MECHANICA | L OUTLINE    | PRINT VERSION NO | T TO SCALE  |

|---------------------------------------------------------------------------------------------------------------|-----------|--------------|------------------|-------------|

| TITLE: PLASTIC ULTRA-THIN FINE PITCH DUAL FLAT NON-LEADED (UDFN) PACKAGE, 8 TERMINAL, 2 X 2 X 0.65, 0.5 PITCH |           | DOCUMENT NO  | ): 98ASA10787D   | REV: A      |

|                                                                                                               |           | CASE NUMBER  | : 1944–02        | 10 DEC 2007 |

|                                                                                                               |           | STANDARD: NO | N-JEDEC          |             |

FC SUFFIX 12-PIN 98ASA10787D REVISION A

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS UF-PSON.

4. COPLANARITY APPLIES TO LEADS.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED.                                                       | MECHANICA | L OUTLINE                       | PRINT VERSION NO | OT TO SCALE |

|---------------------------------------------------------------------------------------------------------------|-----------|---------------------------------|------------------|-------------|

| TITLE: PLASTIC ULTRA—THIN FINE PITCH DUAL FLAT NON—LEADED (UDFN) PACKAGE, 8 TERMINAL, 2 X 2 X 0.65, 0.5 PITCH |           | DOCUMENT NO                     | : 98ASA10787D    | REV: A      |

|                                                                                                               |           | CASE NUMBER: 1944-02 10 DEC 200 |                  | 10 DEC 2007 |

|                                                                                                               |           | STANDARD: NO                    | N-JEDEC          |             |

FC SUFFIX 12-PIN 98ASA10787D REVISION A

34726

## **REVISION HISTORY**

| REVISION | DATE   | DESCRIPTION OF CHANGES                                                                                                                                    |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 5/2008 | Initial Release                                                                                                                                           |

| 2.0      | 9/2009 | <ul> <li>Minor adjustments to the Ordering information and Device Variations</li> <li>Updated to match the current Freescale format and style.</li> </ul> |

|          | 1/2014 | Added archive information                                                                                                                                 |

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd.

Exchange Building 23F

No. 118 Jianguo Road

Chaoyang District

Beijing 100022

China

+86 10 5879 8000

support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty. representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2010. All rights reserved.

MC34726 Rev. 2.0 1/2014