# life.augmented

### P-NUCLEO-LRWAN1

## STM32 Nucleo pack for LoRa® technology and high-performance FSK/OOK RF transceiver modem

Data brief

#### **Features**

- Ultra-low-power STM32L0 Series MCU, ARM<sup>®</sup>

Cortex<sup>®</sup> -M0+ based with 192 Kbytes of Flash

memory, 20 Kbytes of RAM, 6 Kbytes of

EEPROM, LCD, crystal-less USB, T-RNG,

PCROP

- 157 dB maximum link budget

- +20 dBm, 100 mW constant RF output versus Vsupply

- +14 dBm high efficiency PA

- Programmable bit rate up to 300 kbps

- High sensitivity: down to -137 dBm

- Bullet-proof front end: IIP3 = -12.5 dBm

- 89 dB blocking immunity

- Low RX current of 10 mA, 200 nA register retention

- Fully integrated synthesizer with a resolution of 61 Hz

- FSK, GFSK, MSK, GMSK, LoRa<sup>®</sup> and OOK modulations

- Built-in bit synchronizer for clock recovery

- Sync word recognition

- Preamble detection

- 127 dB+ dynamic range RSSI

- Built-in temperature sensor and low-battery indicator 1.65 V to 3.6 V power supply

1. Picture is not contractual.

### **Description**

The STM32 Nucleo pack for LoRa<sup>®</sup> technology and high-performance FSK/OOK RF transceiver modem (P-NUCLEO-LRWAN1) is a development tool to learn and develop solutions based on LoRa<sup>®</sup> and FSK/OOK technologies.

This tool, in association with the certified embedded software solution (I-CUBE-LRWAN), provides the means to set up a complete LoRaWAN™ node compliant with class A, based on the Semtech SX1272MB2xAS LoRa® extension board. To control the LoRa® extension board, the pack comes with a NUCLEO-L073RZ board based on the ultra-low-power, 32-bit STM32L0 based on ARM® Cortex® -M0 microcontroller. The I-CUBE-LRWAN is LoRaWAN™ class A certified.

This pack is the perfect fit for any countries with 868 MHz or 915 ISM frequency bands.

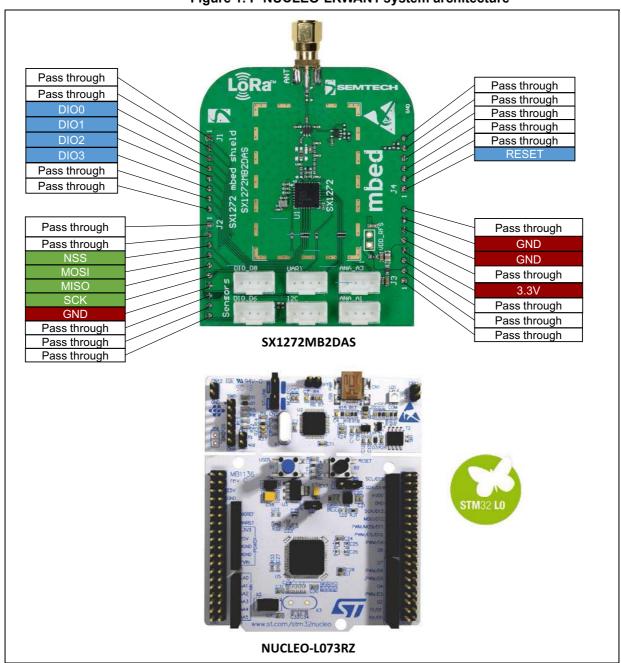

## P-NUCLEO-LRWAN1 system architecture

The STM32 Nucleo pack for LoRa<sup>®</sup> technology and high-performance FSK/OOK RF transceiver modem is composed of two main blocks (see *Figure 1: P-NUCLEO-LRWAN1 system architecture*):

- The SX1272MB2xAS LoRa® extension board

- A control block: NUCLEO-L073RZ MCU board

Figure 1. P-NUCLEO-LRWAN1 system architecture

2/6 DocID029505 Rev 2

#### The SX1272MB2xAS expansion board includes:

The SX1272 transceiver:

The SX1272 transceiver features the LoRa<sup>®</sup> long-range modem that provides an ultra-long range spread spectrum communication and a high-interference immunity whilst minimizing the current consumption.

Using the Semtech patented LoRa<sup>®</sup> modulation technique, the SX1272/73 transceivers can achieve a sensitivity of over -137 dBm using a low-cost crystal and bill of materials. The high sensitivity combined with the integrated +20 dBm power amplifier makes the link budget optimal for any application requiring range or robustness. The LoRa<sup>®</sup> modulation also provides significant advantages in both blocking and selectivity, over the conventional modulation techniques, solving the traditional design compromise between the range, the interference immunity and the energy consumption. These transceivers also support the high performance (G)FSK modes for systems including WMBus, IEEE802.15.4g. The SX1272/73 transceivers deliver an exceptional phase noise, a selectivity, a receiver linearity and IIP3 for significantly lower current consumption than the competing devices.

The LoRa<sup>®</sup> modulation:

The LoRa® Semtech proprietary modulation is a spread-spectrum technique that uses wideband linear frequency modulated pulses to encode information, whose frequency increases or decreases over a certain amount of time. Like with other spread-spectrum modulation techniques, the LoRa® modulation uses the entire channel bandwidth to broadcast a signal, making it robust to the channel noise. In addition, because the LoRa® modulation uses a broad band of the spectrum, the signal is resistant to long term relative frequency error, multi-path, fading and doppler effects.

#### The SX1272 transceiver has the following features:

- 157 dB maximum link budget

- +20 dBm,100 mW constant RF output versus Vsupply

- +14 dBm high efficiency PA

- Programmable bit rate up to 300 kbps

- High sensitivity: down to -137 dBm

- Bullet-proof front end: IIP3 = -12.5 dBm

- 89 dB blocking immunity

- Low RX current of 10 mA, 200 nA register retention

- Fully integrated synthesizer with a resolution of 61 Hz

- FSK, GFSK, MSK, GMSK, LoRa<sup>®</sup> and OOK modulations

- Built-in bit synchronizer for clock recovery

- Svnc word recognition

- Preamble detection

- 127 dB+ dynamic range RSSI

- Automatic RF Sense with ultra-fast AFC

- Packet engine up to 64 bytes with CRC

- Built-in temperature sensor and low battery indicator

#### The NUCLEO-L073RZ board includes:

- An STM32L073RZT6 ultra-low-power 32-bit microcontroller based on ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ with 192 Kbytes of Flash memory, 20 Kbytes of SRAM, 6 Kbytes of true EEPROM, USB 2.0 full speed and crystal-less data interface, a LCD driver, 2x 12-bit DAC and a T-RNG in a LQFP64 package

- Two types of extension resources:

- Arduino<sup>™</sup> Uno V3 connectivity

- ST morpho extension pin headers for full access to all STM32 I/Os

- On-board ST-LINK/V2-1 debugger/programmer with SWD connector

- Selection-mode switch to use the pack as a standalone ST-LINK/V2-1

- Flexible board power supply:

- USB V<sub>BUS</sub> on Type-B connector or external source

- Power management access point

- Three LEDs:

- USB communication (LD1), user LED (LD2), power LED (LD3)

- Two push-buttons: USER and RESET

- USB re-enumeration capability: three different interfaces supported on USB:

- Virtual COM port

- Mass storage

- Debug port

- Supported by a wide choice of Integrated Development Environments (IDEs) including IAR<sup>™</sup>, ARM<sup>®</sup> Keil<sup>®</sup>, GCC-based IDEs

57

P-NUCLEO-LRWAN1 Revision history

## **Revision history**

**Table 1. Document revision history**

| Date        | Revision | Changes                                                |

|-------------|----------|--------------------------------------------------------|

| 12-Aug-2016 | 1        | Initial version.                                       |

| 29-Nov-2016 | 2        | Updated Figure 1: P-NUCLEO-LRWAN1 system architecture. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved

577