64Mb/32Mb 3.0V PAGE MODE PARALLEL FLASH MEMORY

DATA SHEET

# IS29GL064/032 64/32 Megabit Flash Memory Page mode Flash Memory, CMOS 3.0 Volt-only

# FEATURES

- Supply operation

- $V_{CC} = 2.7 \sim 3.6 V$

- V<sub>CCQ</sub> = 1.65~3.6V (I/O buffers)

- V<sub>HH</sub> = 9.5~10.5V (WP#/ACC)

- Asynchronous random or page read

- Page size: 8 words or 16 bytes

- Page access: 25ns

- Random access (V<sub>CCQ</sub> =  $2.7 \sim 3.6$ V):70ns

- Buffer program: 256-word MAX program buffer

- Program time

- 0.56us per byte (1.8MB/s TYP when using 256-word buffer size in buffer program without  $V_{\text{HH}}$ )

- 0.31us per byte (3.2MB/s TYP when using 256-word buffer size in buffer program with  $V_{\text{HH}})$

- Memory Organization

32Mb: 64x 64KB (Uniform), or 8x 8KB (Top or Bottom Boot)+63x64KB

- 64Mb: 128x 64KB (Uniform), or 8x 8KB (Top or Bottom Boot)+127x64KB

- Program/erase suspend and resume capability

Program suspend: Read from another sector

- Erase suspend: Read or Program from another sector

- BLANK CHECK operation to verify an erased sector

- Unlock bypass, sector erase, chip erase, and buffer program capability

- Fast buffered/batch programming

- Fast sector and chip erase

- WP#/ACC pin protection

- V<sub>HH</sub> voltage on WP#/ACC to accelerate programing performance

- Protects highest/lowest sector (H/L uniform) or top/bottom two sectors (T/B boot)

- Software Protection

Advanced Sector Protection (ASP)

- Support CFI (Common Flash Interface)

- Extended Memory Sector

128-word (256-byte) sector for permanent secure identification

Program or lock implemented at the factory or by customer

- Low Power consumption: Standby mode

- Data retention: 20 years (TYP)

- 100K minimum ERASE cycles per sector

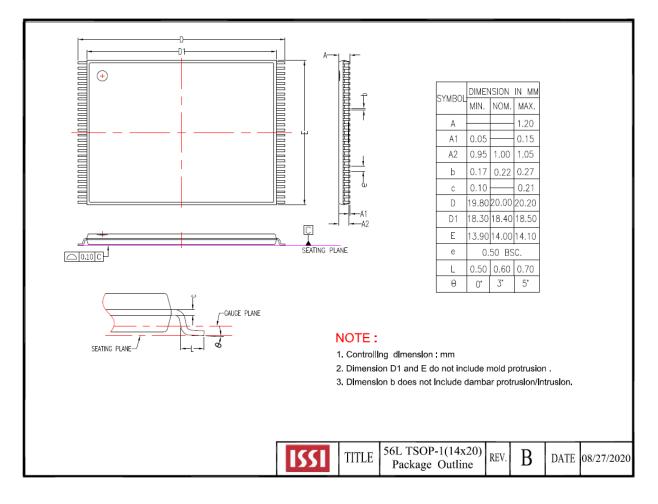

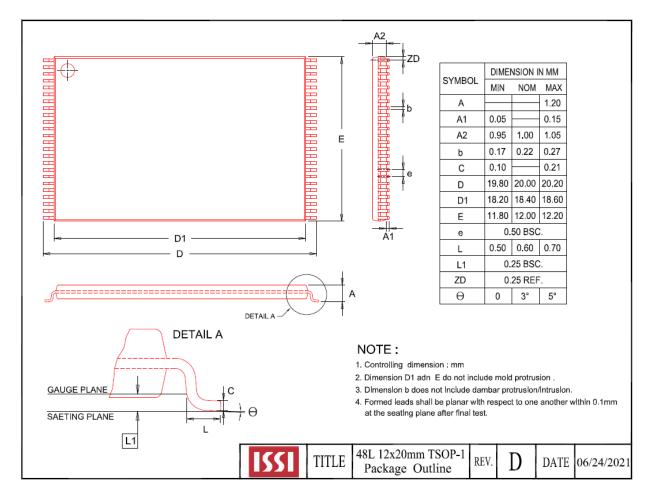

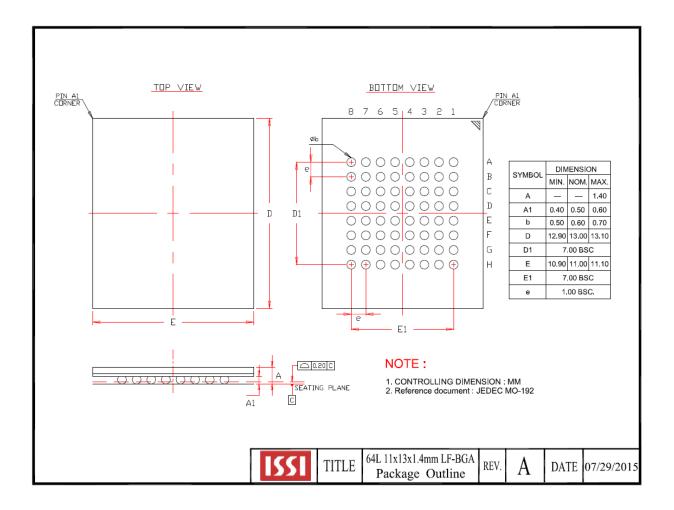

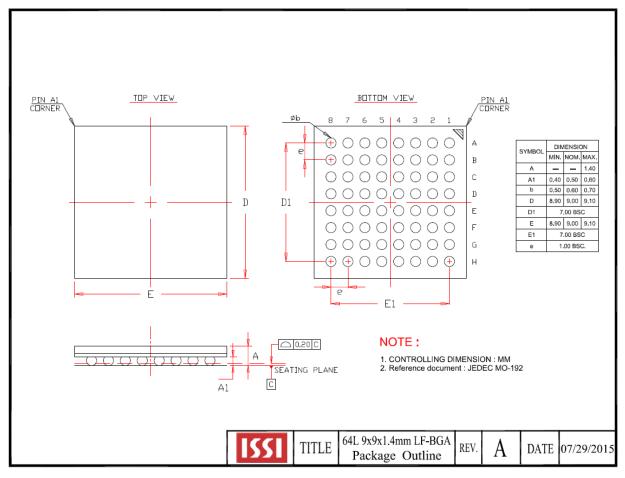

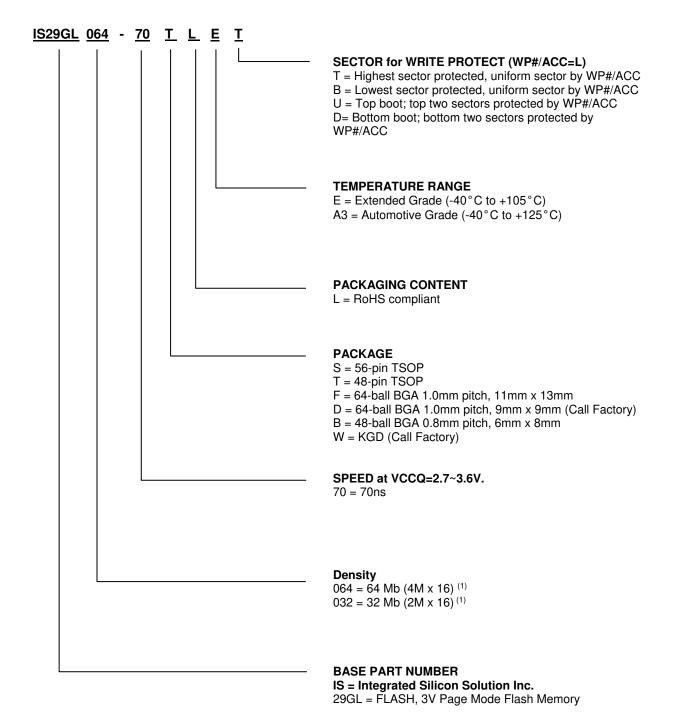

- Package Options

- 48-pin TSOP

- 56-pin TSOP

- 64-ball 9mm x 9mm BGA (Call Factory)

- 64-ball 11mm x 13mm BGA

- 48-ball 6mm x 8mm BGA

- Temperature Range

- Extended Grade: -40°C to +105°C

- Automotive A3 Grade: -40°C to +125°C

# **GENERAL DESCRIPTION**

The IS29GL064/032 offer fast page access time of 25ns with a corresponding random access time as fast as 70ns. It features a Write Buffer that allows a maximum of 256 words/512 bytes to be programmed in one operation, resulting in faster effective programming time than standard programming algorithms. This makes the device ideal for today's embedded applications that require higher density, better performance and lower power consumption.

# **PRODUCT SELECTOR GUIDE**

• Speed bin depends on V<sub>CCQ</sub> voltage.

|                                              | IS29GL064/032   |                 |  |  |  |

|----------------------------------------------|-----------------|-----------------|--|--|--|

| Supply Voltage for<br>Input/Output & Package | Temperature     |                 |  |  |  |

|                                              | -40°C to +105°C | -40°C to +125°C |  |  |  |

| $V_{CCQ} = 2.7 - 3.6V$                       | 70ns            | 70ns            |  |  |  |

| V <sub>CCQ</sub> < 2.7V                      | 75ns            | 75ns            |  |  |  |

Note:

1. No  $V_{CCQ}$  pin for 48-pin TSOP and 48-ball BGA.

### TABLE OF CONTENTS

| GENERAL DESCRIPTION                        |    |

|--------------------------------------------|----|

| PRODUCT SELECTOR GUIDE                     | 3  |

| TABLE OF CONTENTS                          |    |

| 1. PIN CONFIGURATION                       |    |

| 2. PIN DESCRIPTIONS                        | 9  |

| 3. LOGIC DIAGRAM AND BLOCK DIAGRAM         | 10 |

| 4. MEMORY CONFIGURATION                    |    |

| 5. BUS OPERATIONS                          |    |

| 6. COMMAND OPERATIONS                      |    |

| 7. STATUS REGISTER                         | 32 |

| 8. PROTECTION                              |    |

| 8.1 Device Protection Methods              |    |

| 8.2 Sector Protection Methods              |    |

| 8.3 Dynamic Protection Bits                |    |

| 8.4 Persistent Protection Bits             |    |

| 8.5 Lock Register                          |    |

| 8.6 PPB Lock Bit                           |    |

| 8.8 Password Lock mode                     |    |

| 8.9 Sector Protection Command Definitions  |    |

| 9. Secured Silicon Region Command Sequence |    |

| 10. COMMON FLASH INTERFACE (CFI)           | 50 |

| 11. POWER-UP AND RESET CHARACTERISTICS     |    |

| 12. ELECTRICAL CHARACTERISTICS             |    |

| 12.1 ABSOLUTE MAXIMUM RATINGS              |    |

| 12.2 OPERATING RANGE                       |    |

| 12.3 DC CHARACTERISTICS                    |    |

| 12.4 AC MEASUREMENT CONDITIONS             |    |

| 12.5 AC CHARACTERISTICS                    |    |

| 13. PACKAGE INFORMATION                    |    |

| 14. ORDERING INFORMATION                   | 75 |

### **1. PIN CONFIGURATION**

Figure 1.1 48-pin TSOP (Top View), (PKG Code: T)

| 1                     |    |    |                             |

|-----------------------|----|----|-----------------------------|

| A15                   | 1  | 48 | A16                         |

| A14                   | 2  | 47 | <b>BYTE#</b> <sup>(4)</sup> |

| A13                   | 3  | 46 | ] <b>vss</b> (2)            |

| A12                   | 4  | 45 | DQ15/A-1                    |

| A11                   | 5  | 44 | DQ7                         |

| A10                   | 6  | 43 | DQ14                        |

| A9                    | 7  | 42 | DQ6                         |

| A8 🗌                  | 8  | 41 | DQ13                        |

| A19                   | 9  | 40 | DQ5                         |

| A20                   | 10 | 39 | DQ12                        |

| WE#                   | 11 | 38 | DQ4                         |

| RESET#                | 12 | 37 | VCC                         |

| <sup>(1)</sup> A21/NC | 13 | 36 | DQ11                        |

| WP#/ACC               | 14 | 35 | DQ3                         |

| RY/BY#                | 15 | 34 | DQ10                        |

| A18                   | 16 | 33 | DQ2                         |

| A17                   | 17 | 32 | DQ9                         |

| A7                    | 18 | 31 | DQ1                         |

| A6                    | 19 | 30 | DQ8                         |

| A5                    | 20 | 29 | DQ0                         |

| A4                    | 21 | 28 | OE#                         |

| _                     | 22 | 27 | VSS                         |

| A2                    | 23 | 26 | CE#                         |

| A1 🗌                  | 24 | 25 | <b>A</b> 0                  |

| l                     |    |    |                             |

- 1. A21 is valid for 64Mb, and it is NC in 32Mb

- 2. A-1 is the least significant address in x8 mode

- 3. For 48-pin, there is no  $V_{CCQ}$  pin. Vcc also supply IO, it can only be 2.7~3.6V

- 4. Word mode (x16) only supported. Please contact Factory for Byte mode and Word mode.

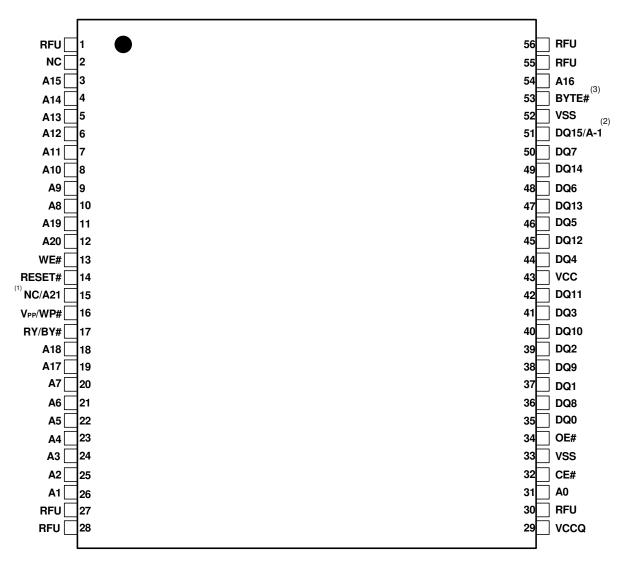

Figure 1.2. 56-pin TSOP (Top View), (PKG Code: S)

- 1. A21 is valid for 64Mb, and it is NC in 32Mb

- 2. A-1 is the least significant address in x8 mode

- 3. Word mode (x16) only supported. Please contact Factory for Byte mode and Word mode.

- 1. A21 is valid for 64Mb, and it is NC in 32Mb

- 2. A-1 is the least significant address in x8 mode

- 3. Word mode (x16) only supported. Please contact Factory for Byte mode and Word mode.

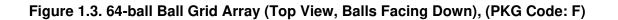

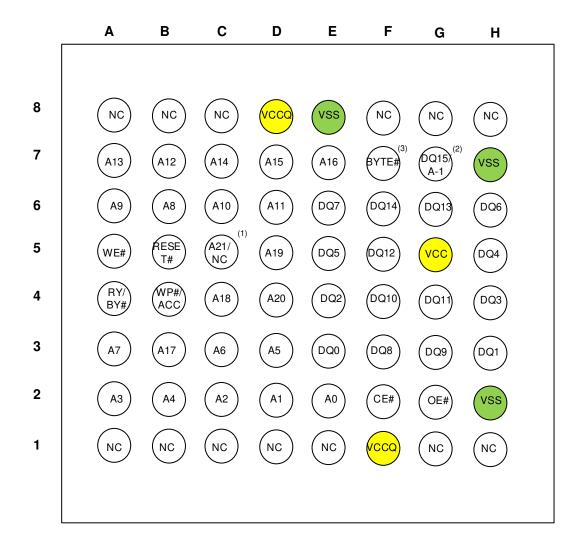

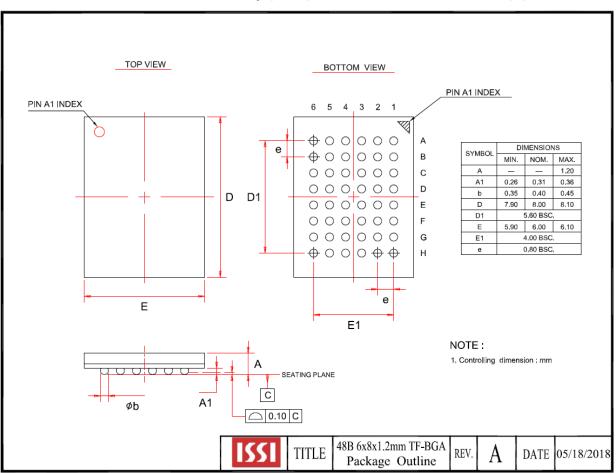

### Figure 1.4. 48-ball Ball Grid Array (Top View, Balls Facing Down)

- 1. A21 is valid for 64Mb, and it is NC in 32Mb

- 2. A-1 is the least significant address in x8 mode

- 3. For 48-ball, there is no V<sub>CCQ</sub> pin. Vcc also supply IO, it can only be 2.7~3.6V

- 4. Word mode (x16) only supported. Please contact Factory for Byte mode and Word mode.

# 2. PIN DESCRIPTIONS

| Pin Name    | Function                                                                                            |

|-------------|-----------------------------------------------------------------------------------------------------|

| A21(A20)-A0 | Address                                                                                             |

| DQ0-DQ14    | Data input/output.                                                                                  |

| DQ15 / A-1  | DQ15 (data input/output, word mode), A-1 (LSB address input, byte mode)                             |

| CE#         | Chip Enable                                                                                         |

| OE#         | Output Enable                                                                                       |

| RESET#      | Hardware Reset Pin                                                                                  |

| RY/BY#      | Ready/Busy Output                                                                                   |

| WE#         | Write Enable                                                                                        |

| Vcc         | Supply Voltage                                                                                      |

| Vccq        | Supply Voltage for Input/Output.                                                                    |

| Vss         | Ground                                                                                              |

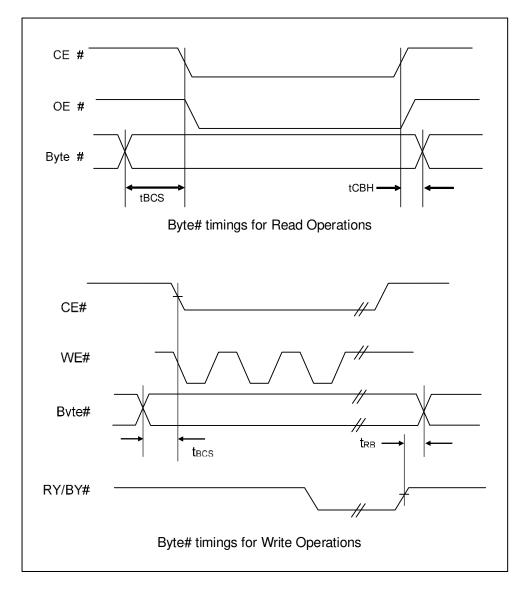

| BYTE#       | Word mode only supported. Please contact Factory for Byte mode and Word mode                        |

| WP#/ACC     | Write Protect / Acceleration Pin<br>(WP# has an internal pull-up; when unconnected, WP# is at VIH.) |

| NC          | No Connect                                                                                          |

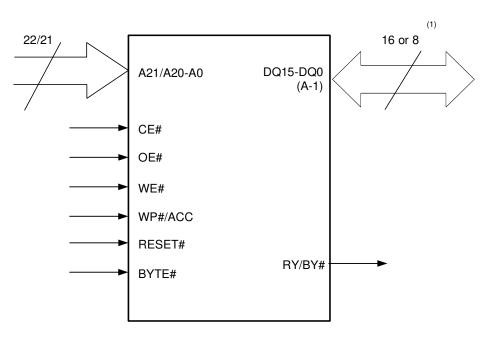

# 3. LOGIC DIAGRAM AND BLOCK DIAGRAM

# FIGURE 3.1. LOGIC DIAGRAM

64Mb/32Mb Logic Symbol

Note:

1. Word mode (x16) only supported. Please contact Factory for Byte mode and Word mode.

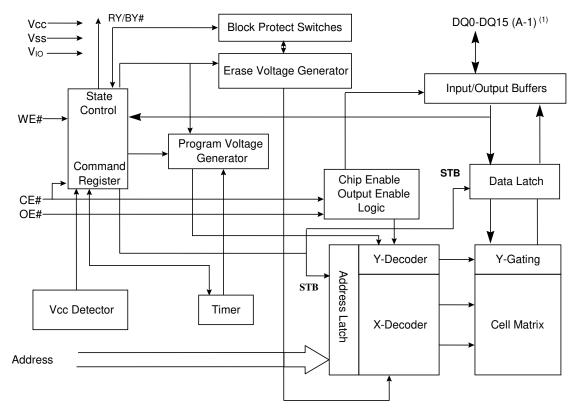

### FIGURE 3.2 BLOCK DIAGRAM

Note:

1. Word mode (x16) only supported. Please contact Factory for Byte mode and Word mode.

# 4. MEMORY CONFIGURATION

- The 64Mb device (x8/x16) can be divided into 127 main sectors (64KB each) and 8 top or bottom boot sectors (8KB each).

It is also divided into 128 main uniform sectors (64KB each)

- The 32Mb device (x8/x16) can be divided into 63 main sectors (64KB each) and 8 top or bottom boot sectors (8KB each).

It is also divided into 64 main uniform sectors (64KB each)

| Sector | Sector | r Address Range<br>(x8 Top Boot) |           | Sector | Sector | Address Range<br>(x8 Bottom Boot) |           |

|--------|--------|----------------------------------|-----------|--------|--------|-----------------------------------|-----------|

|        | Size   | Start                            | End       |        | Size   | Start                             | End       |

| 134    |        | 007F E000                        | 007F FFFF | 134    |        | 007F 0000                         | 007F FFFF |

| 133    | _      | 007F C000                        | 007F DFFF | 133    | 64KB   | 007E 0000                         | 007E FFFF |

| 132    |        | 007F A000                        | 007F BFFF | 132    |        | 007D 0000                         | 007D FFFF |

| 131    | 8KB    | 007F 8000                        | 007F 9FFF | :      | :      | :                                 | :         |

| 130    | 0112   | 007F 6000                        | 007F 7FFF | 8      | 64KB   | 0001 0000                         | 0001 FFFF |

| 129    |        | 007F 4000                        | 007F 5FFF | 7      |        | 0000 E000                         | 0000 FFFF |

| 128    |        | 007F 2000                        | 007F 3FFF | 6      |        | 0000 C000                         | 0000 DFFF |

| 127    |        | 007F 0000                        | 007F 1FFF | 5      |        | 0000 A000                         | 0000 BFFF |

| 126    | 64KB   | 007E 0000                        | 007E FFFF | 4      |        | 0000 8000                         | 0000 9FFF |

| :      | :      | :                                | :         | 3      | - 8KB  | 0000 6000                         | 0000 7FFF |

| 2      |        | 0002 0000                        | 0002 FFFF | 2      | 1      | 0000 4000                         | 0000 5FFF |

| 1      | 64KB   | 0001 0000                        | 0001 FFFF | 1      |        | 0000 2000                         | 0000 3FFF |

| 0      |        | 0000 0000                        | 0000 FFFF | 0      |        | 0000 0000                         | 0000 1FFF |

## Table 4.1. 64Mb Memory Map – x8 Top and Bottom Boot [134:0]

# Table 4.2. 64Mb Memory Map – x16 Top and Bottom Boot [134:0]

| Sector | Sector<br>Size | Address Range<br>(x16 Top Boot) |           | Sector | Sector | Address Range<br>(x16 Bottom Boot) |           |

|--------|----------------|---------------------------------|-----------|--------|--------|------------------------------------|-----------|

|        | Size           | Start                           | End       |        | Size   | Start                              | End       |

| 134    |                | 003F F000                       | 003F FFFF | 134    |        | 003F 8000                          | 003F FFFF |

| 133    |                | 003F E000                       | 003F EFFF | 133    | 32KW   | 003F 0000                          | 003F 7FFF |

| 132    |                | 003F D000                       | 003F DFFF | 132    |        | 003E 8000                          | 003E FFFF |

| 131    | 4KW            | 003F C000                       | 003F CFFF | :      | :      | :                                  | :         |

| 130    |                | 003F B000                       | 003F BFFF | 8      | 32KW   | 0000 8000                          | 0000 FFFF |

| 129    |                | 003F A000                       | 003F AFFF | 7      |        | 0000 7000                          | 0000 7FFF |

| 128    |                | 003F 9000                       | 003F 9FFF | 6      |        | 0000 6000                          | 0000 6FFF |

| 127    |                | 003F 8000                       | 003F 8FFF | 5      |        | 0000 5000                          | 0000 5FFF |

| 126    | 32KW           | 003F 7000                       | 003F 7FFF | 4      |        | 0000 4000                          | 0000 4FFF |

| :      | :              | :                               | :         | 3      | 4KW    | 0000 3000                          | 0000 3FFF |

| 2      |                | 0001 0000                       | 0001 7FFF | 2      |        | 0000 2000                          | 0000 2FFF |

| 1      | 32KW           | 0000 8000                       | 0000 FFFF | 1      |        | 0000 1000                          | 0000 1FFF |

| 0      |                | 0000 0000                       | 0000 7FFF | 0      |        | 0000 0000                          | 0000 0FFF |

| Sector | Sector Sector | Address Range (x8) |           | Sector | Sector | Address Range (x16) |            |

|--------|---------------|--------------------|-----------|--------|--------|---------------------|------------|

| Sector | Size          | Start              | End       | Sector | Size   | Start               | End        |

| 127    |               | 07F 0000h          | 07F FFFFh | 127    |        | 03F 8000h           | 03F FFFFh  |

| :      |               | :                  | :         | :      |        | :                   | :          |

| 63     | 64KB          | 03F 0000h          | 03F FFFFh | 63     | 32KW   | 01F 8000h           | 01F FFFFh  |

| :      |               | :                  |           | :      |        | :                   | :          |

| 0      |               | 000 0000h          | 000 FFFFh | 0      |        | 000 0000h           | 0000 7FFFh |

### Table 4.3. 64Mb Memory Map – x8/x16 Uniform Sectors [127:0]

# Table 4.4. 32Mb Memory Map – x8 Top and Bottom Boot [70:0]

| S      | Sector | Address       | s Range   |        | Sector | Address Range    |           |  |

|--------|--------|---------------|-----------|--------|--------|------------------|-----------|--|

| Sector | Size   | (x8 Top Boot) |           | Sector | Size   | (x8 Bottom Boot) |           |  |

|        | 5120   | Start         | End       |        | Size   | Start            | End       |  |

| 70     |        | 003F E000     | 003F FFFF | 70     |        | 003F 0000        | 003F FFFF |  |

| 69     |        | 003F C000     | 003F DFFF | 69     | 64KB   | 003E 0000        | 003E FFFF |  |

| 68     |        | 003F A000     | 003F BFFF | 68     |        | 003D 0000        | 003D FFFF |  |

| 67     | 8KB    | 003F 8000     | 003F 9FFF | :      | :      | :                | :         |  |

| 66     |        | 003F 6000     | 003F 7FFF | 8      | 64KB   | 0001 0000        | 0001 FFFF |  |

| 65     |        | 003F 4000     | 003F 5FFF | 7      |        | 0000 E000        | 0000 FFFF |  |

| 64     |        | 003F 2000     | 003F 3FFF | 6      |        | 0000 C000        | 0000 DFFF |  |

| 63     |        | 003F 0000     | 003F 1FFF | 5      |        | 0000 A000        | 0000 BFFF |  |

| 62     | 64KB   | 003E 0000     | 003E 1FFF | 4      |        | 0000 8000        | 0000 9FFF |  |

| :      | :      | :             | :         | 3      | 8KB    | 0000 6000        | 0000 7FFF |  |

| 2      |        | 0002 0000     | 0002 FFFF | 2      |        | 0000 4000        | 0000 5FFF |  |

| 1      | 64KB   | 0001 0000     | 0001 FFFF | 1      |        | 0000 2000        | 0000 3FFF |  |

| 0      |        | 0000 0000     | 0000 FFFF | 0      |        | 0000 0000        | 0000 1FFF |  |

| Sector | Sector<br>Size | Address Range<br>(x16 Top Boot) |           | Sector | Sector<br>Size | Address Range<br>(x16 Bottom Boot) |           |

|--------|----------------|---------------------------------|-----------|--------|----------------|------------------------------------|-----------|

|        | Size           | Start                           | End       |        | 5120           | Start                              | End       |

| 70     |                | 001F F000                       | 001F FFFF | 70     |                | 001F 8000                          | 001F FFFF |

| 69     |                | 001F E000                       | 001F EFFF | 69     | 32KW           | 001F 0000                          | 001F 7FFF |

| 68     |                | 001F D000                       | 001F DFFF | 68     |                | 001E 8000                          | 001E FFFF |

| 67     | 4KW            | 001F C000                       | 001F CFFF | :      | :              | :                                  | :         |

| 66     |                | 001F B000                       | 001F BFFF | 8      | 32KW           | 0000 8000                          | 0000 FFFF |

| 65     |                | 001F A000                       | 001F AFFF | 7      |                | 0000 7000                          | 0000 7FFF |

| 64     |                | 001F 9000                       | 001F 9FFF | 6      |                | 0000 6000                          | 0000 6FFF |

| 63     |                | 001F 8000                       | 001F 8FFF | 5      |                | 0000 5000                          | 0000 5FFF |

| 62     | 32KW           | 001F 7000                       | 001F 7FFF | 4      |                | 0000 4000                          | 0000 4FFF |

| :      | :              | :                               | :         | 3      | 4KW            | 0000 3000                          | 0000 3FFF |

| 2      |                | 0001 0000                       | 0001 7FFF | 2      |                | 0000 2000                          | 0000 2FFF |

| 1      | 32KW           | 0000 8000                       | 0000 FFFF | 1      |                | 0000 1000                          | 0000 1FFF |

| 0      |                | 0000 0000                       | 0000 7FFF | 0      |                | 0000 0000                          | 0000 0FFF |

| Table 4.5. 32Mb | Memory Map – : | x16 Top and Botto | om Boot [70:0] |

|-----------------|----------------|-------------------|----------------|

|                 |                |                   |                |

| Table 4.6. 32Mb Memory Map – x8/x16 | Uniform Sectors [63:0] |

|-------------------------------------|------------------------|

|-------------------------------------|------------------------|

| Sector |                | Address Range (x8) |           | Sector |                | Address Range (x16) |            |  |

|--------|----------------|--------------------|-----------|--------|----------------|---------------------|------------|--|

| Sector | •              | Start              | End       | Sector |                | Start               | End        |  |

| 63     | Sector<br>Size | 03F 0000h          | 03F FFFFh | 63     | Sector<br>Size | 01F 8000h           | 01F FFFFh  |  |

| :      | Size           | •                  | :         | •      | 5126           | •                   | :          |  |

| 0      |                | 000 0000h          | 000 FFFFh | 0      |                | 000 0000h           | 0000 7FFFh |  |

# 5. BUS OPERATIONS

# Table 5.1. Device OPERATING MODES

|                   |     |     |     |        |                  | Byte                  | Mode (x8) | (5)                          | Word Mod        | e (x16) <sup>(5)</sup>       |

|-------------------|-----|-----|-----|--------|------------------|-----------------------|-----------|------------------------------|-----------------|------------------------------|

| Operation         | CE# | OE# | WE# | RESET# | WP#/ACC          | A[MAX:0],<br>DQ15/A-1 | DQ[14:8]  | DQ[7:0]                      | A[MAX:0]        | DQ15/A-1,<br>DQ[14:0]        |

| READ              | L   | L   | Н   | Н      | х                | Byte<br>address       | High-Z    | Data<br>output               | Word<br>address | Data<br>output               |

| WRITE             | L   | Н   | L   | Н      | H <sup>(3)</sup> | Command address       | High-Z    | Data<br>input <sup>(4)</sup> | Command address | Data<br>input <sup>(4)</sup> |

| STANDBY           | Н   | Х   | х   | Н      | Н                | х                     | High-Z    | High-Z                       | Х               | High-Z                       |

| OUTPUT<br>DISABLE | L   | Н   | Н   | Н      | х                | Х                     | High-Z    | High-Z                       | х               | High-Z                       |

| RESET             | Х   | Х   | х   | L      | х                | Х                     | High-Z    | High-Z                       | Х               | High-Z                       |

Notes:

1. Typical glitch of less than 3ns on CE#, and WE# are ignored by the device and do not affect bus operation.

2. H = Logic level HIGH ( $V_{IH}$ ); L = Logic Level LOW ( $V_{IL}$ ); X = HIGH or LOW

3. If WP# is LOW, then the highest or lowest sector remains protected, or the top two sectors or the bottom two sectors, depending on the item.

4. Data input is required when issuing a command sequence or when performing data polling or sector protection.

5. BYTE# = H for Word mode, L for Byte mode.

# 6. COMMAND OPERATIONS

# Table 6.1. Standard Command Definitions

|                               |             |         |     |     |      | Addre | ess an | d Data | Cycle | S |    |   |    |           |

|-------------------------------|-------------|---------|-----|-----|------|-------|--------|--------|-------|---|----|---|----|-----------|

| Command                       | Bus<br>Size | 15      | st  | 2n  | ıd   | 31    | rd     | 4      | th    | 5 | th | 6 | th | Note<br>s |

|                               |             | Α       | D   | Α   | D    | Α     | D      | Α      | D     | Α | D  | Α | D  |           |

| READ and AUTO SEL             | ECT O       | peratio | ons |     |      |       |        |        |       |   |    |   |    |           |

|                               | X8          | Х       | F0  |     |      |       |        |        |       |   |    |   |    |           |

|                               | 70          | AAA     | AA  | 555 | 55   | х     | F0     |        |       |   |    |   |    |           |

| READ/RESET (F0h)              | VIC         | х       | F0  |     |      |       |        |        |       |   |    |   |    |           |

|                               | X16         | 555     | AA  | 2AA | 55   | х     | F0     |        |       |   |    |   |    |           |

|                               | X8          | AA      |     |     |      |       |        |        |       |   |    |   |    |           |

| READ CFI (98h)                | X16         | 55      | 98  |     |      |       |        |        |       |   |    |   |    |           |

|                               | X8          | AAA     |     | 555 |      | AAA   |        | Note   | Note  |   |    |   |    |           |

| AUTO SELECT (90h)             | X16         | 555     | AA  | 2AA | 55   | 555   | 90     | 2      | 2     |   |    |   |    | 2,3,4     |

| BYPASS Operations             |             |         | 1   |     | 1    |       |        |        |       |   |    |   |    |           |

| UNLOCK BYPASS                 | X8          | AAA     |     | 555 | - 55 | AAA   |        |        |       |   |    |   |    |           |

| (20h)                         | X16         | 555     | AA  | 2AA | 55   | 555   | 20     |        |       |   |    |   |    |           |

| UNLOCK BYPASS                 | X8          | V       |     | v   |      |       | •      |        |       |   |    |   |    |           |

| RESET (90h/00h)               | X16         | X       | 90  | х   | 00   |       |        |        |       |   |    |   |    |           |

| PROGRAM Operation             | s           |         |     | •   |      |       |        |        |       |   |    |   |    |           |

| PROGRAM (A0h)                 | X8          | AAA     | AA  | 555 | - 55 | AAA   | A0     | РА     | PD    |   |    |   |    |           |

|                               | X16         | 555     | ~~  | 2AA | 55   | 555   | AU     | FA     | FD    |   |    |   |    |           |

| UNLOCK BYPASS                 | X8          | ~       | A0  | PA  | PD   |       |        |        |       |   |    |   |    | 5         |

| PROGRAM (A0h)                 | X16         | X       | AU  | PA  | PD   |       |        |        |       |   |    |   |    | 5         |

|                               | X8          | AAA     | 50  |     |      |       |        |        |       |   |    |   |    |           |

| BYTE/WORD<br>PROGRAM (50h)    | X16         | 555     | 50  | PA2 | PD   |       |        |        |       |   |    |   |    |           |

|                               | X8          | AAA     | 50  |     |      |       |        |        |       |   |    |   |    |           |

| BYTE/WORD<br>PROGRAM (56h)    | X16         | 555     | 56  | PA4 | PD   |       |        |        |       |   |    |   |    |           |

| OCTUPLE BYTE<br>PROGRAM (8Bh) | X8          | AAA     | 8B  | PA8 | PD   |       |        |        |       |   |    |   |    | 6         |

|                               |             |     |    |     |    | Addre | ess an | d Data | Cycle | s   |          |       |    |           |

|-------------------------------|-------------|-----|----|-----|----|-------|--------|--------|-------|-----|----------|-------|----|-----------|

| Command                       | Bus<br>Size | 19  | st | 2n  | d  | 3r    | d      | 4t     | h     | 5t  | h        | 6tl   | า  | Note<br>s |

|                               |             | Α   | D  | Α   | D  | Α     | D      | Α      | D     | Α   | D        | Α     | D  |           |

| WRITE BUFFER                  | X8          | AAA |    | 555 |    | BSA   | 05     | BSA    | N     | WBP |          |       |    | 7.0       |

| LOAD (25h)                    | X16         | 555 | AA | 2AA | 55 | d     | 25     | d      | N     | Α   | PD       |       |    | 7, 8      |

| UNLOCK BYPASS                 | X8          | BSA | 25 | BSA | N  | WBP   |        |        |       |     | <u> </u> |       |    | 5, 7,     |

| WRITE BUFFER<br>LOAD (25h)    | X16         | d   | 25 | d   | IN | Α     | PD     |        |       |     |          |       |    | 8         |

| PROGRAM BUFFER<br>TO FLASH    | X8          | BSA | 29 |     |    |       |        |        |       |     |          |       |    |           |

| CONFIRM (29h)                 | X16         | d   | 29 |     |    |       |        |        |       |     |          |       |    |           |

| BUFFERED<br>PROGRAM ABORT     | X8          | AAA | AA | 555 | 55 | AAA   | F0     |        |       |     |          |       |    |           |

| and RESET (F0h)               | X16         | 555 | ~~ | 2AA | 55 | 555   | 10     |        |       |     |          |       |    |           |

| PROGRAM                       | X8          | x   | В0 |     |    |       |        |        |       |     |          |       |    |           |

| SUSPEND (B0h)                 | X16         | ^   | 50 |     |    |       |        |        |       |     |          |       |    |           |

| PROGRAM<br>RESUME (30h)       | X8          | х   | 30 |     |    |       |        |        |       |     |          |       |    |           |

| ERASE Operations              | X16         |     |    |     |    |       |        |        |       |     |          |       |    |           |

|                               |             |     |    |     |    |       |        |        |       |     |          |       |    |           |

| CHIP ERASE                    | X8          | AAA | AA | 555 | 55 | AAA   | 80     | AAA    | AA    | 555 | 55       | AAA   | 10 |           |

| (80/10h)                      | X16         | 555 | ~~ | 2AA | 55 | 555   | 00     | 555    | ~~    | 2AA | 55       | 555   | 10 |           |

| UNLOCK BYPASS<br>CHIP ERASE   | X8          | x   | 80 | x   | 10 |       |        |        |       |     | •        |       | •  | 5         |

| (80/10h)                      | X16         | ^   | 00 | ^   | 10 |       |        |        |       |     | _        |       | -  | 5         |

| SECTOR ERASE                  | X8          | AAA | AA | 555 | 55 | AAA   | 80     | AAA    | AA    | 555 | 55       | BAd   | 30 | 9         |

| (80/30h)                      | X16         | 555 |    | 2AA |    | 555   |        | 555    |       | 2AA |          | 27.10 |    | Ŭ         |

| UNLOCK BYPASS<br>SECTOR ERASE | X8          | х   | 80 | BAd | 30 |       |        |        |       |     |          |       |    | 5         |

| (80/30h)                      | X16         |     |    |     |    |       |        |        |       |     |          |       |    | -         |

| ERASE SUSPEND<br>(B0h)        | X8          | х   | В0 |     |    |       |        |        |       |     |          |       |    |           |

|                               | X16         |     |    |     |    |       |        |        |       |     |          |       |    |           |

| ERASE RESUME<br>(30h)         | X8          | х   | 30 |     |    |       |        |        |       |     |          |       |    |           |

|                               | X16         |     |    |     |    |       |        |        |       |     |          |       |    |           |

### Table 6.1. Standard Command Definitions (Continued)

|                                 |               | Address and Data Cycles |     |      |      |     |     |     |     |     |    |     |    |           |

|---------------------------------|---------------|-------------------------|-----|------|------|-----|-----|-----|-----|-----|----|-----|----|-----------|

| Command                         | Bus<br>Size 1 |                         | 1st |      | 2nd  |     | 3rd |     | 4th |     | th | 6th |    | Note<br>s |

|                                 |               | Α                       | D   | Α    | D    | Α   | D   | Α   | D   | Α   | D  | Α   | D  | -         |

| BLANK CHECK Opera               | ations        |                         |     |      |      |     |     |     |     |     |    |     |    |           |

| BLANK CHECK                     | X8            | AAA                     | AA  | 555  | 55   | BAd | EB  | BAd | 76  | BAd | 00 | BAd | 00 |           |

| SETUP (EB/76h)                  | X16           | 555                     | 77  | 2AA  | 55   | DAU | LD  | DAU | 70  | BAu | 00 | DAU | 00 |           |

| BLANK CHECK<br>CONFIRM and READ | X8            | BAd                     | 29  | BAd  | Note |     |     |     |     |     |    |     |    | 2         |

| (29h)                           | X16           | 2.10                    | _0  | 2710 | 2    |     |     |     |     |     |    |     |    | _         |

#### Table 6.1. Standard Command Definitions (Continued)

- 1. A = Address; D = Data; X = Don't Care, BAd = Any address in the sector; BSAd = Any address in the sector with constant A[Max:12]; WBPA = write buffer program address with A[Max:12] = BSAd, N = Number of bytes to be programmed; PA = program address; PA2 = Program address with constant A[Max:0] for x8 or A[Max:1] for x16, which should be used two times to select adjacent two bytes/words; PA4 = Program address with constant A[Max:2] for x8 or A[Max:2] for x16, which should be used four times to select four bytes/words; PA8 = Program address with constant A[Max:2] for x8 or A[Max:2] for x8, which should be used eight times to select adjacent eight bytes; PD = Program data; Gray shading = Not applicable. All values in the table are hexadecimal. Some commands require both a command code and subcode.

- 2. These cells represent READ cycles (versus WRITE cycles for others).

- 3. AUTO SELECT enables the device to read the manufacturer code, device code, sector protection status, and Secured Silicon Region protection indicator.

- 4. AUTO SELECT addresses and data are specified in the Electronic Signature table and the Secured Silicon Region table.

- 5. For any UNLOCK BYPASS ERASE/PROGRAM command, the first two UNLOCK cycles are unnecessary.

- 6. This command is only for x8 devices.

- 7. WRITE BUFFER LOAD operation: maximum cycles = 261 (x8) and 261 (x16).

- UNLOCK BYPASS WRITE BUFFER LOAD operation: maximum cycles = 259 (x8), 259 (x16).

- WRITE BUFFER LOAD operation: N +1 = bytes to be programmed;

- Maximum buffer size = 256 bytes (x8) and 512 bytes (x16)

- 8. For x8, A [Max: 7] address pins for WBPA should remain unchanged while A [6:0] and A-1 pins for WBPA are used to select a byte within the N+1 byte page. For x16, A [Max: 8] address pins for WBPA should remain unchanged while A [7:0] pins for WBPA are used to select a word within the N+1 word page.

- 9. BLLOCK ERASE address cycles can extend beyond six address data cycles, depending on the number of sectors to erase.

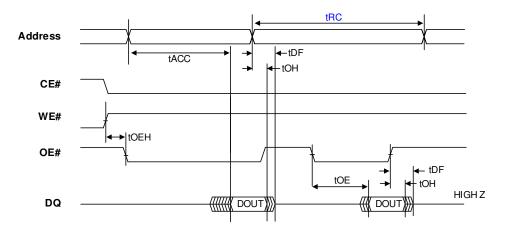

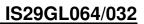

# 6.1 Read Operation

Bus READ operations read from the memory cells, or CFI space. To accelerate the READ operation, the memory array can be read in page mode where data is internally read and stored in a page buffer.

Page size is 8 words (16 bytes) and is addressed by address inputs A [2:0] in x16 bus mode and A[2:0] plus DQ15/A-1 in x8 bus mode. The Secured Silicon Region and CFI area do not support page mode.

A valid bus READ operations involves setting the desired address on the address inputs, taking CE# and OE# LOW, and holding WE# HIGH. The data I/Os will output the value.

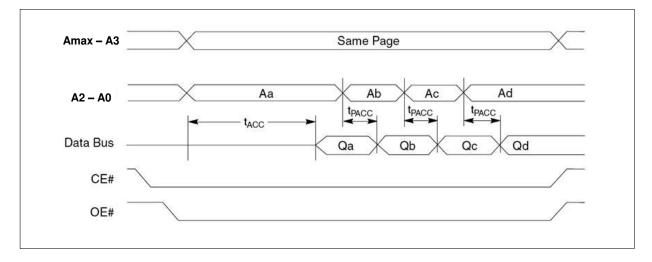

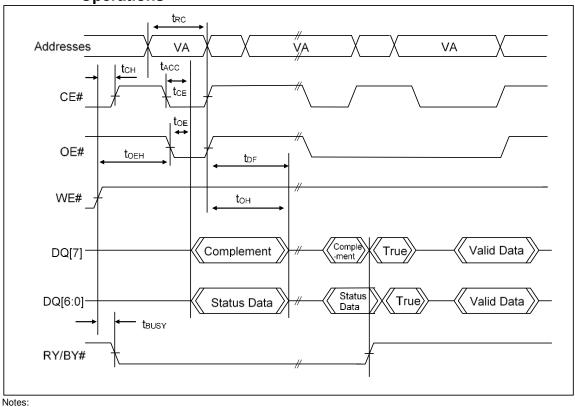

# 6.2 Page Read Operation

The device is capable of fast page mode read and is compatible with the page mode Mask ROM read operation. This mode provides faster read access speed for random locations within a page. The page size of the device is 8 words/16 bytes. The appropriate page is selected by the higher address bits Amax-A3. Address bits A2-A0 in word mode (A2 to A-1 in byte mode) determine the specific word within a page. The microprocessor supplies the specific word location.

The random or initial page access is equal to tACC or tCE and subsequent page read accesses (as long as the locations specified by the microprocessor falls within that page) is equivalent to tPACC. When CE# is deasserted and reasserted for a subsequent access, the access time is tACC or tCE. Fast page mode accesses are obtained by keeping the "read-page addresses" constant and changing the "intra-read page" addresses.

## 6.3 Autoselect Operation

The Autoselect mode provides manufacturer ID, Device identification, sector protection status and Secured Silicon Region protection indicator with executing a READ operation with control signals and addresses set. In addition, this device information can be read or set by issuing an AUTO SELECT command.

The device only support to use Autoselect command to access Autoselect codes.

#### It does not support the mode of applying $V_{HH}$ on address pin A9.

- The Autoselect command sequence may be written to an address within a sector that is either in the read or erase-suspend-read mode.

- The Autoselect command may not be written while the device is actively programming or erasing.

- The system must write the reset command to return to the read mode (or erase-suspend-read mode if the sector was previously in Erase Suspend).

|          |                               |   |     |     |           | A       | ddress | Input |    |    |     | Da       | ata Input/O | utput    |

|----------|-------------------------------|---|-----|-----|-----------|---------|--------|-------|----|----|-----|----------|-------------|----------|

| Re       | Read Cycle                    |   | OE# | WE# | X8/x16 x8 |         |        |       |    |    |     | X8 only  |             | x16 only |

|          |                               |   |     |     | A[Max:11] | A[10:4] | A3     | A2    | A1 | A0 | A-1 | DQ[14:8] | DQ[7:0]     | DQ[15:0] |

| Manufac  | cturer code                   | L | L   | Н   | Х         | L       | L      | L     | L  | L  | Х   | Х        | 9Dh         | 009Dh    |

| Device I | D 1                           | L | L   | Н   | Х         | L       | L      | L     | L  | Н  | Х   | Х        | 7Eh         | 227Eh    |

|          | 64Mb boot                     |   |     |     |           |         |        |       |    |    |     |          | 10h         | 2210h    |

| Device   | 64Mb<br>uniform               |   |     | н   | х         | L       | н      | н     | н  | L  | х   | x        | 0Ch         | 220Ch    |

| ID 2     | 32Mb boot                     |   | LL  | п   | ^         |         |        |       |    |    | ^   | ^        | 1Ah         | 221Ah    |

|          | 32Mb<br>uniform               |   |     |     |           |         |        |       |    |    |     |          | 1Dh         | 221Dh    |

|          | 64/32Mb<br>High<br>protection |   |     |     |           |         |        |       |    |    |     |          | 01h         | 2201h    |

| Device   | 64/32Mb Top<br>boot           |   |     |     |           |         |        |       |    |    |     |          | •           |          |

| ID 3     |                               |   |     | Н   | X         |         | Н      | H     | H  | н  | Х   | X        | 00h         | 2200h    |

|          | 64/32Mb<br>Bottom boot        |   |     |     |           |         |        |       |    |    |     |          |             |          |

### Table 6.2. Manufacturer ID and Device ID

Note:

1.  $H = Logic level HIGH (V_{IH}); L = Logic level LOW (V_{IL}); X = HIGH or LOW.$

# Table 6.3. Sector Protection

| Read Cycle         |                           |         |   |     |                 | Ado      | dress Inp | Data Input/Output |    |      |          |                    |                      |

|--------------------|---------------------------|---------|---|-----|-----------------|----------|-----------|-------------------|----|------|----------|--------------------|----------------------|

|                    |                           | CE# OE# |   | WE# |                 | X8/)     | c16       | x8<br>only        | X8 | only | x16 only |                    |                      |

|                    | Opti<br>on <sup>(6)</sup> |         |   |     | A[Max:15]       | A[14:11] | A[10:2]   | A1                | A0 | A-1  | DQ[14:8] | DQ[7:0]            | DQ[15:0]             |

|                    | 1                         |         |   | н   | х               | х        |           | н                 | н  | Х    | х        | 8Ah <sup>(2)</sup> | 008Ah <sup>(2)</sup> |

| Secured            | L                         | L       | L |     | ^               | ^        | L         | П                 | П  | ^    | ^        | 0Ah <sup>(3)</sup> | 000Ah <sup>(3)</sup> |

| Silicon            | н                         | н і     |   | н   | Х               | х        |           | н                 | н  | Х    | х        | 9Ah <sup>(2)</sup> | 009Ah <sup>(2)</sup> |

| Region             |                           | L       | L |     | ~               | ~        | L         |                   |    | ~    | ^        | 1Ah <sup>(3)</sup> | 001Ah <sup>(3)</sup> |

| protection         | В                         |         |   | н   | х               | х        |           | н                 | н  | х    | х        | 8Ah <sup>(2)</sup> | 008Ah <sup>(2)</sup> |

| indicator<br>(DQ7) | Б                         | L       |   |     | ^               | ^        | L         |                   |    | ^    | ^        | 0Ah <sup>(3)</sup> | 000Ah <sup>(3)</sup> |

| (DQT)              | Т                         |         |   | н   | Х               | х        |           | н                 | н  | Х    | х        | 9Ah <sup>(2)</sup> | 009Ah <sup>(2)</sup> |

|                    | I                         | L       |   |     | ^               | ^        | L         |                   |    | ^    | ^        | 1Ah <sup>(3)</sup> | 001Ah <sup>(3)</sup> |

| Sector Prote       | ection                    |         |   |     | Sector          |          |           |                   |    | v    | V        | 01h <sup>(4)</sup> | 0001h <sup>(4)</sup> |

| status             |                           | L       | L | Н   | base<br>address | L        | L         | Н                 | L  | Х    | Х        | 00h <sup>(5)</sup> | 0000h <sup>(5)</sup> |

#### Notes:

1. H = Logic level HIGH ( $V_{IH}$ ); L = Logic level LOW ( $V_{IL}$ ); X = HIGH or LOW.

2. ISSI - prelocked (permanent).

3. Customer lockable.

4. Protected: DQ [7:0] = 01h. This protection status includes PPB and DYB but does not include WP#/ACC=L effect

- 5. Unprotected: DQ[7:0] = 00h.

- 6. Sector Protection Option:

- H = Highest sector protected by WP#/ACC; uniform sector

- L = Lowest sector protected by WP#/ACC; uniform sector

- T = Top boot; top two sectors protected by WP#/ACC

- B = Bottom boot; bottom two sectors protected by WP#/ACC

# 6.4 UNLOCK BYPASS Operation

The UNLOCK BYPASS (20h) command is also used to place the device in unlock bypass mode. Three bus WRITE operations are required to issue the UNLOCK BYPASS command.

When the device enters unlock bypass mode, the two initial UNLOCK cycles required for a standard PROGRAM or ERASE operation are not needed, thus enabling faster total program or erase time.

During the unlock bypass mode, below UNLOCK BYPASS COMMANDs are available. UNLOCK BYPASS PROGRAM UNLOCK BYPASS WRITE BUFFER LOAD UNLOCK BYPASS CHIP ERASE UNLOCK BYPASS SECTOR ERASE UNLOCK BYPASS RESET

The UNLOCK BYPASS RESET (90/00h) command is used to return to read/reset mode from unlock bypass mode. Two bus WRITE operations are required to issue the UNLOCK BYPASS RESET command. The READ/RESET command does not exit from unlock bypass mode.

Also the device automatically enters UNLOCK BYPASS mode when WP# /ACC is raised to  $V_{HH}$ .

Note: It is recommended that entering and exiting unlock bypass mode using the ENTER UNLOCK BYPASS and UNLOCK BYPASS RESET commands rather than raising WP#/ACC to V<sub>HH</sub>. WP#/ACC should never be raised to V<sub>HH</sub> from any mode except read mode; otherwise, the device may be left in an indeterminate state.

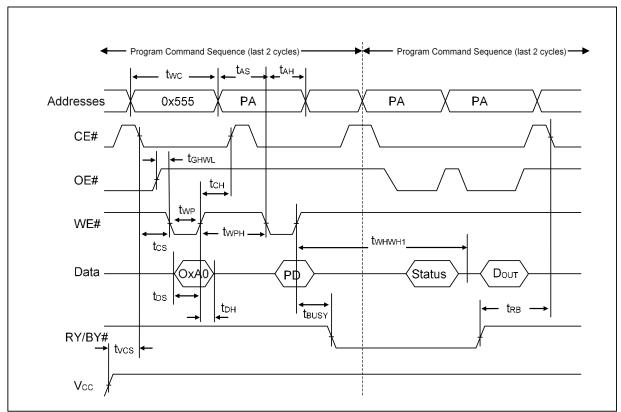

# 6.5 Program Operations

The PROGRAM (A0h) command is used to program a value to address in the memory array.

The command requires 4 bus WRITE operations, and the final WRITE operation latches the address and data in the internal state machine and starts the program/erase controller. After programming has started, bus READ operations output the status register content.

Programming can be suspended and then resumed by issuing a PROGRAM SUSPEND command and a PROGRAM RESEUM command, respectively.

If programming address is within a protected sector, the PROGRAM command is ignored, and the data remains unchanged. The status register is not read, and no error condition is given.

After the PROGRAM operation has completed, the device returns to read mode, unless an error has occurred.

When an error occurs, bus READ operations to the device continue to output the status register. A READ/RESET command must be issued to reset the error condition and return the device to read mode.

The PROGRAM command cannot change a bit set to 0 back to 1, and an attempt to do so is masked during a PROGRAM operation. Instead, an ERASE command must be used to set all bits in one memory sector or in the entire memory from 0 to 1.

The PROGRAM operation is aborted by performing a hardware reset or by powering-down the device. In this case, data integrity cannot be ensured, and it is recommended that the words or bytes that were aborted be reprogrammed.

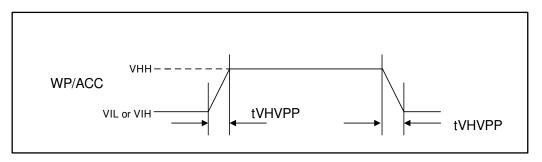

# 6.6 ACCELERATED PROGRAM

Accelerated single word programming and write buffer programming operations are enabled through the WP#/ACC pin. This method is faster than the standard program command sequences.

If the system asserts V<sub>HH</sub> on this input, the device automatically enters the Accelerated Program mode and uses the higher voltage and current provided by WP#/ACC pin to reduce the time required for program operations. Also the device automatically enters UNLOCK BYPASS mode when WP# /ACC is raised to V<sub>HH</sub>.

The system can then use the Write Buffer Load command sequence provided by the Accelerated Program mode. When WP#/ACC returns to VIH or VIL, upon completion of the embedded program operation, returns the device to normal operation.

- Sectors must be unprotected prior to raising WP#/ACC to V<sub>HH</sub>.

- The WP#/ACC pin must not be at V<sub>HH</sub> for operations other than accelerated programming, or device damage may result.

- It is recommended that WP#/ACC apply V<sub>HH</sub> after power-up sequence is completed. In addition, it is recommended that WP#/ACC apply from V<sub>HH</sub> to V<sub>IH</sub>/V<sub>IL</sub> before powering down V<sub>CC</sub>/ V<sub>CCQ</sub>.

# 6.7 DOUBLE BYTE/WORD PROGRAM

The DOUBLE BYTE/WORD PROGRAM (50h) command is used to write a page of two adjacent bytes/words in parallel. The two bytes/words must differ only for the address A-1 or A0, respectively. Three bus write cycles are necessary to issue the command:

- The first bus cycle sets up the command.

- The second bus cycle latches the address and data of the first byte/word to be programmed.

- The third bus cycle latches the address and data of the second byte/word to be programmed and starts the program/erase controller.

# 6.8 QUADRUPLE BYTE/WORD PROGRAM

The QUADRUPLE BYTE/WORD PROGRAM (56h) command is used to write a page of four adjacent bytes/words in parallel. The four bytes/words must differ only for the address A0, DQ15/A-1 in x8 mode or for addresses A1, A0 in x16 mode.

Five bus write cycles are necessary to issue the command:

- The first bus cycle sets up the command.

- The second bus cycle latches the address and data of the first byte/word to be programmed.

- The third bus cycle latches the address and data of the second byte/word to be programmed.

- The fourth bus cycle latches the address and data of the third byte/word to be programmed.

- The fifth bus cycle latches the address and data of the fourth byte/word to be programmed and starts the program/erase controller.

Note: The DOUBLE/QUADRUPLE PROGRAM commands are available in the 32Mb and 64Mb device; also only  $V_{PPL}$  is to be applied to the WP#/ACC pin.

# 6.9 OCTUPLE BYTE PROGRAM

The OCTUPLE BYTE PROGRAM (8Bh) command is used to write a page of eight adjacent bytes in parallel. The eight bytes must differ only for the address A1, A0, DQ15/A-1 in x8 mode only.

Nine bus write cycles are necessary to issue the command:

The first bus cycle sets up the command.

The second bus cycle latches the address and data of the first byte to be programmed.

The third bus cycle latches the address and data of the second byte to be programmed.

The fourth bus cycle latches the address and data of the third byte to be programmed.

The fifth bus cycle latches the address and data of the fourth byte to be programmed.

The sixth bus cycle latches the address and data of the fifth byte to be programmed.

The seventh bus cycle latches the address and data of the sixth byte to be programmed.

The eighth bus cycle latches the address and data of the seventh byte to be programmed.

The ninth bus cycle latches the address and data of the eighth byte to be programmed and starts the program/erase controller.

# Note: The OCTUPLE BYTE PROGRAM command is available only in the 32Mb and 64Mb X8 devices; also only $V_{PPL}$ is to be applied to the WP#/ACC pin.

# 6.10 WRITE BUFFER PROGRAM Operation

Write Buffer Programming allows the system to write a maximum of 256 words in one programming operation. This results in a faster effective word programming time than the standard "word/byte" programming algorithms. When issuing a WRITE BUFFER LOAD command, WP#/ACC can be held HIGH or raised to  $V_{HH}$ . Also, it can be held LOW if the sector is not the lowest or highest sector or the top/bottom two sectors, depending on the part number. When  $V_{HH}$  is applied to the WP#/ACC pin during execution of the command, programming speed increases.

The Write Buffer Programming command sequence is initiated by first writing two unlock cycles. This is followed by a third write cycle containing the WRITE BUFFER LOAD command written at the Boot Sector Address (BSAd; A[Max:12]) in which programming occurs.

At this point, the system writes the number of words/bytes to be programmed. Value n is written to the same Boot Sector address (BSAd), where n+1 is the number of words/bytes to be programmed. Value n+1 must not exceed the size of the program buffer, or the operation will abort. For example, if the system programs 6 address locations, then 05h should be written to the device.

The fifth cycle loads the starting address/data combination. This starting address is the first address/data pair to be programmed, and selects the "write-buffer-page" address. All subsequent address/data pairs must fall within the selected-write-buffer-page.

After writing the Starting Address/Data pair, the system then writes the remaining address/data pairs into the write buffer. Addresses must be within the range from the **start address+1** to the **start address + (n-1)**. For x8 device, maximum buffer size is 256 bytes; for x16 device, maximum buffer size is 512 bytes.

The "write-buffer-page" is selected by using A[Max:8] within Write Buffer Program Address (WBPA, where A[Max:12] of WBPA = BSAd) . A[Max:8] must be the same for all address/data pairs loaded into the write buffer. This means Write Buffer Programming cannot be performed across multiple "write-buffer-pages." This also means that Write Buffer Programming cannot be performed across multiple sectors.

Note that if a Write Buffer address location is loaded multiple times, the "address/data pair" counter is decremented for every data load operation. Also, the last data loaded at a location before the "Program Buffer to Flash" confirm command is the data programmed into the device. It is the software's responsibility to comprehend ramifications of loading a write-buffer location more than once. The counter decrements for each data load operation, NOT for each unique write-buffer-address location. Once the specified number of write buffer locations have been loaded, the system must then write the "Program Buffer to Flash" command at the Sector Address. Any other address/data write combinations abort the Write Buffer Programming operation. The Write Operation Status bits should be used while monitoring the last address location loaded into the write buffer. This eliminates the need to store an address in memory because the system can load the last address location, issue the program confirm command at the last loaded address location, and then check the write operation status at that same address. The status register bits DQ1, DQ5, DQ6, DQ7 can be used to monitor the device status during Write Buffer Programming.

The write-buffer "embedded" programming operation can be suspended or resumed using the standard suspend/resume commands. Upon successful completion of the Write Buffer Programming operation, the device returns to READ mode.

The Write Buffer Programming Sequence is ABORTED under any of the following conditions:

- Load a value that is greater than the page buffer size during the "Number of Locations to Program" step.

- Write to a different BSAd, A[Max:12], different than the one specified during the Write-Buffer-Load command.

- Write an Address/Data pair to a different write-buffer-page than the one selected by the "Starting Address" during the "write buffer data loading" stage of the operation.

- Writing anything other than the Program to Buffer Flash Command after the specified number of "data load" cycles.

BUFFERED PROGRAM ABORT AND RESET (F0h) command must be issued to reset the device to read mode when the BUFFER PROGRAM operation is aborted. The buffer programming sequence can be aborted in the following ways.

The abort condition is indicated by DQ1 = 1, DQ7 = DQ7# (for the last address location loaded), DQ6 = toggle, DQ5 = 0 (all of which are status register bits).

Note: The full three-cycle BUFFERED PROGRAM ABORT and RESET command sequence is required when using buffer programming features in unlock bypass mode.

# 6.11 PROGRAM BUFFER TO FLASH OPERATION

The PROGRAM BUFFER TO FLASH (29h) command is used to confirm a WRITE BUFFER LOAD command to program the n+1 words/bytes loaded in the program buffer.

# 6.12 PROGRAM SUSPEND OPERATION

The PROGRAM SUSPEND (B0h) command allows the system to interrupt a PROGRAM operation or a "Buffer Program" operation so that data can be read from any non-suspended sector. When the PROGRAM SUSPEND command is issued during a programming process, the device suspends the programming operation within the program suspend latency time (15 µs maximum, 5 µs typical) and updates the status register bits. Addresses are "don't-cares" when writing the Program Suspend command.

After the PROGRAM operation has been suspended, data can be read array data from any non-suspended sector.

The PROGRAM SUSPEND command may also be issued during a PROGRAM operation while an erase is suspended. In this case, data may be read from any addresses not within a sector in ERASE SUSPEND or PROGRAM SUSPEND.

If a read is needed from the Secured Silicon Region area (one-time programmable area), the ENTER/EXIT Secured Silicon Region command sequence must be issued.

The system may also issue the AUTO SELECT command sequence and CFI query command when the device is in program suspend mode. The system can read as many auto select codes as required.

When the device exits the auto select mode, the device reverts to Program Suspend mode, and is ready for another valid operation.

The PROGRAM SUSPEND operation is aborted by performing a device reset or power down. In this case, data integrity cannot be ensured, and it is recommended that the words or bytes that were aborted be reprogrammed.

After the Program Resume command is written, the device reverts to programming. The system can determine the status of the program operation using the write operation status bits, just as in the standard program operation.

### 6.13 PROGRAM RESUME command

The PROGRAM RESUME (30h) command must be issued to exit a program suspend mode and resume a PROGRAM operation. The host can use DQ7 or DQ6 status bits to determine the status of the PROGRAM operation. After a PROGRAM RESUME command is issued, subsequent PROGRAM RESUME commands are ignored. Another PROGRAM SUSPEND command can be issued after the device has resumed programming.

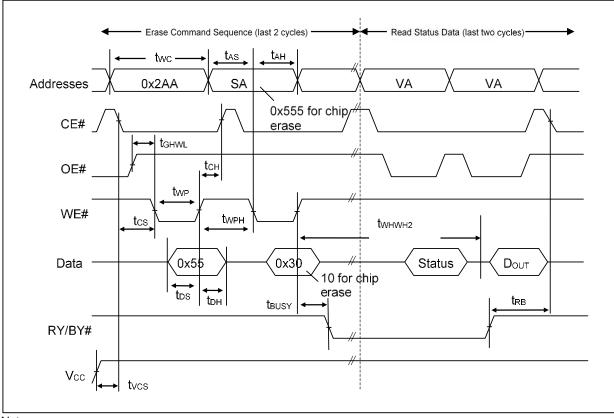

# 6.14 CHIP ERASE OPERATION

Chip Erase (80/10h).is a six-bus cycle operation. These commands invoke the Embedded Erase algorithm, which does not require the system to preprogram prior to erase. The Embedded Erase algorithm automatically preprograms and verifies the entire memory to an all zero data pattern prior to electrical erase. After a successful chip erase, all locations of the chip contain FFFFh, except for any protected sectors. The system is not required to provide any controls or timings during these operations.

Protected sectors are not erased. If all sectors are protected, the data remains unchanged. No error is reported when protected sectors are not erased.

When the Embedded Erase algorithm is complete, that sector returns to the read mode and addresses are no longer latched.

Any commands including suspend command written during the chip erase operation are ignored.

However, note that a hardware reset or powering down the device immediately terminates the erase operation. If that occurs, the chip erase command sequence should be reinitiated once that sector has returned to reading array data, to ensure the entire array is properly erased.

# **6.15 SECTOR ERASE OPERATION**

Sector Erase (80/30h) is a six bus cycle operation. The sector erase command sequence is initiated by writing two un-lock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the address of the sector to be erased, with the sector erase command. The Command Definitions table shows the address and data requirements for the sector erase command sequence.

During the period specified by the sector erase timeout parameter, additional sector addresses and SECTOR ERASE commands can be written. Any command except SECTOR ERASE or SECTOR SUSPEND during this timeout period resets the device to the read mode. The system can monitor DQ3 to determine if the sector erase timer has timed out.

After the program/erase controller has started, it is not possible to select any more sectors. Each additional sector must therefore be selected within the timeout period of the last sector. The timeout timer restarts when an additional sector is selected.

After the sixth bus WRITE operation, a bus READ operation outputs the data polling register. If an error occurs, READ/RESET command must be issued to reset the error condition and return to read mode.

When the Embedded Erase algorithm is completed, the device returns to reading array data and addresses are no longer latched.

# 6.16 SECTOR ERASE SUSPEND OPERATION

The SECTOR ERASE SUSPEND (B0h) command allows the system to interrupt a sector erase operation and then read data from, or program data to, any sector not selected for erase. One bus WRITE operation is required to issue the command. The sector address is "Don't Care." The Suspend command is ignored if written during the chip erase operation.

When the SECTOR ERASE SUSPEND command is written during the sector erase operation, the device requires erase suspend latency time of the ERASE SUSPEND command being issued to suspend the erase operation.

However, when the ERASE SUSPEND command is written during the sector erase timeout, the device immediately terminates the timeout period and suspends the ERASE operation.

If the ERASE SUSPEND operation is aborted by performing a device hardware reset or power-down, data integrity cannot be ensured, and it is recommended that the suspended sectors be erased again.

After the program/erase controller has stopped, the device enters the erase-suspend-read mode. The system can read data from or program data to any sector not selected for erasure. During erase-suspend-read mode, it is possible to execute below operations:

- READ (main memory array)

- PROGRAM

- WRITE BUFFER LOAD

- AUTO SELECT

- READ CFI

- UNLOCK BYPASS

- Secured Silicon Region commands

- READ/RESET

Reading from a suspended sector will output the data polling register. If an attempt is made to program in a protected or suspended sector, the PROGRAM command is ignored and the data remains unchanged; also, the data polling register is not read and no error condition is given.

Before the RESUME command is initiated, the READ/RESET command must be issued to exit AUTO SELECT and READ CFI operations. In addition, the EXIT UNLOCK BYPASS and EXIT Secured Silicon Region commands must be issued to exit unlock bypass mode and the Secured Silicon Region mode.

# 6.17 SECTOR ERASE RESUME OPERATION

To resume the sector erase operation from erase-suspend-read mode, the system must write SECTOR ERASE RESUME (30h).

The device must be in read mode before the RESUME command will be accepted.

An erase can be suspended and resumed more than once.

# 6.18 BLANK CHECK OPERATION

The BLANK CHECK operation will confirm if a selected sector is currently erased. Two commands are required to execute a BLANK CHECK operation: BLANK CHECK SETUP (EBh/76h) and BLANK CHECK CONFIRM AND READ (29h).

It can also be used to determine whether a previous ERASE operation was successful, including ERASE operations that might been interrupted by power loss.

If it finds any bit not erased, the device will halt the operation and report the results. A READ/RESET command must be issued to reset the error condition and return the device to read mode

If it returns a passing status, the sector is guaranteed blank (all 1s) and is ready to program. After the BLANK CHECK operation has completed, the device returns to read mode unless an error has occurred.

Before executing, the ERASE operation initiates an embedded BLANK CHECK operation, and if the target sector is blank, the ERASE operation is skipped, benefitting overall cycle performance; otherwise, the ERASE operation continues.

The BLANK CHECK operation can occur in only one sector at a time, and during its execution, reading the data polling register is the only other operation allowed. Reading from any address in the device enables reading the data polling register to monitor blank check progress or errors. Operations such as READ (array data), PROGRAM, ERASE, and any suspended operation are not allowed.

# 7. STATUS REGISTER

# Table 7.1. Status Register Bit Definitions

| Bit      | Name                             | Setting                                                      | Description                                                                                                                                                                                                                                                                              | Notes   |

|----------|----------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| DQ15:DQ8 | EIP                              | All 0 = Erase in<br>Progress, All 1 =No<br>Erase in Progress | Indicates Erase in progress for x16 device.                                                                                                                                                                                                                                              | 8       |

| DQ7      | Data<br>polling bit              | 0 or 1, depending on operations                              | Monitors whether the program/erase controller has successfully<br>completed its operation, or has responded to an ERASE<br>SUSPEND operation.                                                                                                                                            | 2, 3, 4 |

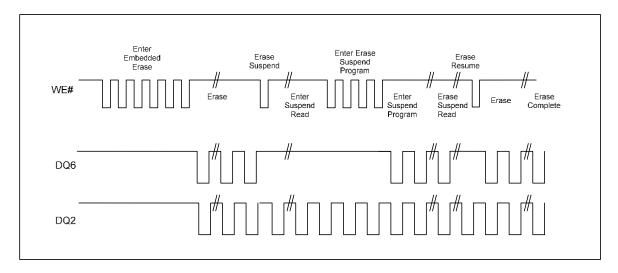

| DQ6      | Toggle bit                       | Toggles: 0 to 1; 1 to 0;<br>and so on                        | Monitors whether the program/erase controller has successfully<br>completed its operations, or has responded to an ERASE<br>SUSPEND operation. During a PROGRAM/ERASE operation,<br>DQ6 toggles from 0 to 1, 1 to 0, and so on, with each successive<br>READ operation from any address. | 3, 4, 5 |

| DQ5      | Error bit                        | 0 = Success<br>1 = Failure                                   | Identifies errors detected by the program/erase controller. DQ5 is<br>set to 1 when a PROGRAM, SECTOR ERASE, or CHIP ERASE<br>operation fails to write the correct data to the memory, or when a<br>BLANK CHECK operation fails.                                                         | 4, 6    |

| DQ3      | Erase timer<br>bit               | 0 = Erase not in<br>progress<br>1 = Erase in progress        | Identifies the start of program/erase controller operation during a SECTOR ERASE command. Before the program/erase controller starts, this bit set to 0, and additional Sectors to be erased can be written to the command interface.                                                    | 4       |

| DQ2      | Alternative toggle bit           | Toggles: 0 to 1; 1 to 0;<br>and so on                        | Monitors the program/erase controller during ERASE operations.<br>During CHIP ERASE, SECTOR ERASE, and ERASE SUSPEND<br>operations, DQ2 toggles from 0 to 1, 1 to 0, and so on, with each<br>successive READ operation from addresses within the sectors<br>being erased.                | 3, 4, 7 |

| DQ1      | Buffered<br>program<br>abort bit | 1 = Abort                                                    | Indicates a BUFFER PROGRAM operation abort. The<br>BUFFERED PROGRAM ABORT and RESET command must be<br>issued to return the device to read mode.                                                                                                                                         |         |

#### Notes:

1. The status register can be read during PROGRAM, ERASE, or ERASE SUSPEND operations; the READ operation outputs data on DQ [7:0].

2. For a PROGRAM operation in progress, DQ7 outputs the complement of the bit being programmed. For a READ operation from the address previously programmed successfully, DQ7 outputs existing DQ7 data. For a READ operation from addresses with sectors to be erased while an SECTOR ERASE SUSPEND operation, DQ7 outputs 1. For an ERASE or BLANK CHECK operation in progress, DQ7 outputs 0; upon either operation's successful completion, DQ7 outputs 1.

Operation in progress, DQ7 outputs 0; upon either operation's successful completion, DQ7 outputs 1.

After successful completion of a PROGRAM, ERASE, or BLANK CHECK operation, the device returns to read mode.

Anter successful completion of a PROGRAM, ERASE, of BLANK CRECK operation, the device returns to read mode.

During SECTOR ERASE SUSPEND mode, READ operations to address within sectors not being erased output memory array .data as if in read mode. A protected sector is treated the same as a sector not being erased.

5 During SECTOR ERASE SUSPEND, DQ6 toggles when addressing a cell within a sector being erased. The toggling stops when the program/erase controller has suspended the SECTOR ERASE operation.

6. When DQ5 is set to 1, a READ/RESET command must be issued before any subsequent command.

7. DQ2 toggles for an actively erasing sector during SECTOR ERASE operation.

8. DQ [15:8] are supported in x16 only. DQ15 through DQ8 are 0 during erase operation, and 1 after completion of erase operation.

# Table 7.2. Operations and Corresponding Bit Settings

| Operation                      | Address                    | DQ7  | DQ6          | DQ5        | DQ3        | DQ2          | DQ1 | RY/BY# | Notes |

|--------------------------------|----------------------------|------|--------------|------------|------------|--------------|-----|--------|-------|

| PROGRAM                        | Any address                | DQ7# | Toggle       | 0          | -          | -            | 0   | 0      | 2     |

| BLANK CHECK                    | Any address                | 0    | Toggle       | 0          | -          | -            | 0   | 0      |       |

| CHIP ERASE                     | Any address                | 0    | Toggle       | 0          | 1          | Toggle       | -   | 0      |       |

| SECTOR ERASE                   | Erasing sector             | 0    | Toggle       | 0          | 0          | Toggle       | -   | 0      |       |

| before time-out                | Non-erasing sector         | 0    | Toggle       | 0          | 0          | No Toggle    | -   | 0      |       |

| SECTOR ERASE                   | Erasing sector             | 0    | Toggle       | 0          | 1          | Toggle       | -   | 0      | 3     |

| SECTOR ERASE                   | Non-erasing sector         | 0    | Toggle       | 0          | 1          | No Toggle    | -   | 0      |       |

|                                | Programming sector         |      |              | Invalid c  | peration   |              |     | High-Z |       |

| PROGRAM SUSPEND                | Non-program<br>ming sector | С    | Outputs men  | High-Z     |            |              |     |        |       |

| SECTOR ERASE                   | Erasing blk                | 1    | No<br>Toggle | 0          | -          | Toggle       | -   | High-Z |       |

| SUSPEND                        | Non-erasing blk            | C    | Outputs men  | nory array | data as if | in read mode |     | High-Z |       |

| PROGRAM during<br>SECTOR ERASE | Erasing sector             | DQ7# | Toggle       | 0          | -          | Toggle       | -   | 0      | 2     |

| SUSPEND                        | Non-erasing sector         | DQ7# | Toggle       | 0          | -          | No Toggle    | -   | 0      | 2     |

| BUFFERED<br>PROGRAM ABORT      | Any address                | DQ7# | Toggle       | 0          | -          | -            | 1   | 0      |       |

| PROGRAM Error                  | Any address                | DQ7# | Toggle       | 1          | -          | -            | -   | 0      | 2     |

|                                | Erase success sector       | 0    | Toggle       | 1          | 1          | No Toggle    | -   | 0      |       |

| ERASE Error                    | Erase fail sector          | 0    | Toggle       | 1          | 1          | Toggle       | -   | 0      |       |

| BLANK CHECK Error              | Any address                | 0    | Toggle       | 1          | 1          | Toggle       | -   | 0      |       |

#### Notes:

Unspecified data bits should be ignored.

DQ7# for buffer program is related to the last address location loaded.

DQ2 toggles only for actively erasing sector during SECTOR ERASE operation.

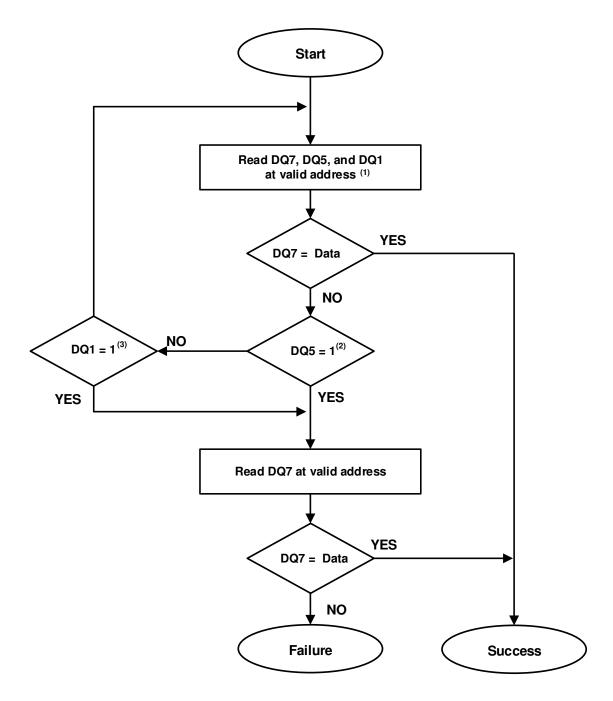

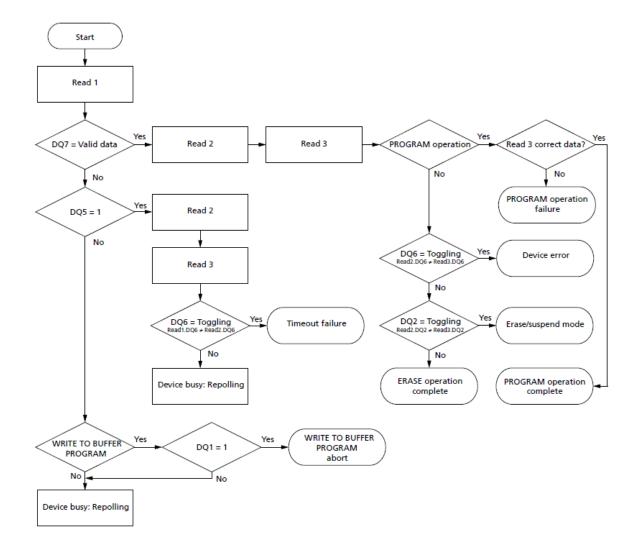

# Figure 7.1. Data Polling Flowchart

- 1. Valid address is the address being programmed or an address within the sector being erased.

- 2. Failure results: DQ5 = 1 indicates an operation error.

- 3. DQ1 = 1 indicates a WRITE BUFFER PROGRAM ABORT operation.

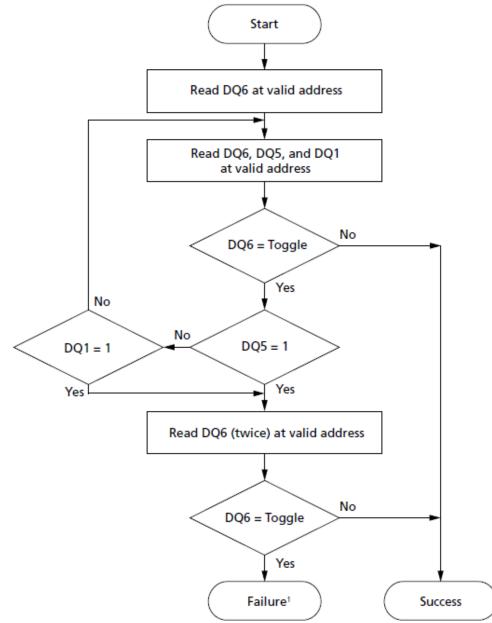

# Figure 7.2. Toggle Bit Flowchart

#### Note:

1. Failure results: DQ5 = 1 indicates an operation error; DQ1 = 1 indicates a BUFFER PROGRAM ABORT operation.

# Figure 7.3. Status Register Polling Flowchart

# 8. PROTECTION

#### 8.1 Device Protection Methods

#### 8.1.1 Low Vcc Write Inhibit

When VCC is less than VLKO (Lock-Out Voltage), the device does not accept any write cycles. This protects data during VCC power-up and power-down.

The command register and all internal program/erase circuits are disabled, and the device resets to reading array data. Subsequent writes are ignored until VCC is greater than VLKO. The system must provide the proper signals to the control inputs to prevent unintentional writes when VCC is greater than VLKO.

#### 8.1.2 Power-Up Write Inhibit

If WE# = CE# = RESET# = VIL and OE# = VIH during power up, the device does not accept commands on the rising edge of WE#. The internal state machine is automatically reset to the read mode on power-up.

#### 8.2 Sector Protection Methods

#### 8.2.1 WP#/ACC Method

The WP#/ACC function provides a hardware method of protecting either the highest/lowest sector or the top/bottom two sectors. When WP#/ACC is LOW, PROGRAM/ERASE operations on either of these sector options is ignored to provide protection.

When WP#/ACC is HIGH, either the highest/lowest sector or the top/bottom two sectors are not protected from PROGRAM/ERASE operations. WP#/ACC has an internal pull-up; when unconnected, WP#/ACC is at V<sub>IH</sub>. WP#/ACC should not change between V<sub>IL</sub> and V<sub>IH</sub> during any embedded operation.

# 8.2.2 Advanced Sector Protection

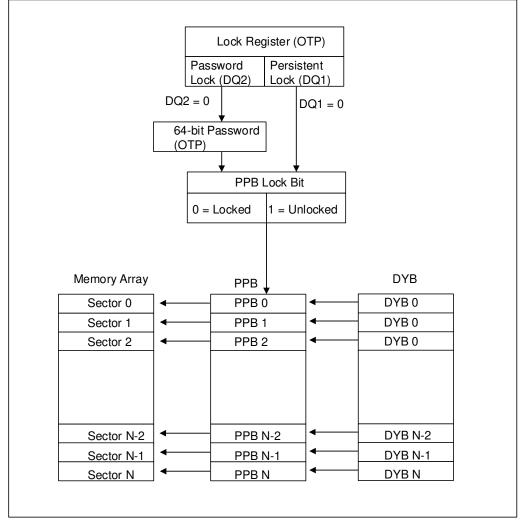

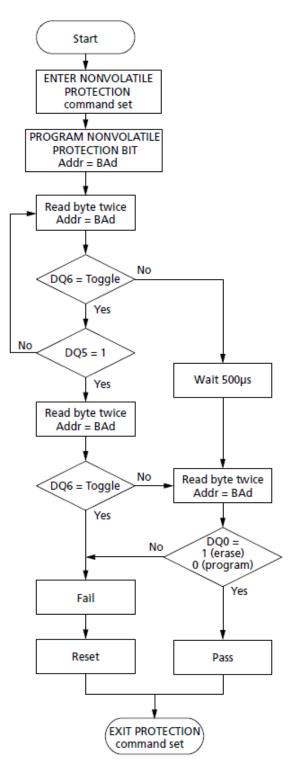

Advanced Sector Protection (ASP) is a set of protection methods used to disable or enable programming or erase operations, individually, in any or all sectors.

Every sector has a non-volatile (PPB) and a volatile (DYB) protection bit associated with it.

As for PPB bits, they are protected when PPB Lock bit is "0". There are two methods for managing the state of the PPB Lock bit; Persistent Lock and Password Lock.

The selection of method for managing the state of PPB Lock bit is made by programming OTP bits in the Lock Register.

The Persistent Lock method sets the PPB Lock bit to 1 during POR or Hardware Reset, so PPB bits are unlocked by a device reset. In Persistent Lock mode, there is a command to set the PPB Lock bit to "0", but no command to clear to "1", so PPB Lock bit remains 0 until the next power-off or hardware reset.

The Password Lock method sets the PPB Lock bit to "0" during POR or Hardware Reset to protect all PPB bits. A command together with correct 64-bit password must be used to clear PPB Lock bit to "1".

Sectors with DYB and PPB protection can coexist within the memory array. If the user attempts to program or erase a protected sector, the device ignores the command and returns to read mode.

The sector protection status can be read by performing a read electronic signature or by issuing an AUTO SELECT command.

# Figure 8.1. Advanced Sector Protection

# 8.3 Dynamic Protection Bits

Dynamic Protection Bits are volatile and unique for each sector and can be individually modified. DYBs only control the protection scheme for unprotected sectors that have their PPBs erased to "1". By issuing the DYB Set or Clear command sequences, the DYBs are set to "0" or cleared to "1", thus placing each sector in the protected or unprotected state respectively. This feature allows software to easily protect sectors against inadvertent changes yet does not prevent the easy removal of protection when changes are needed.

#### Notes

- 1. The DYBs are programmed or cleared individually. When the parts are first shipped from the factory, the all DYBs are set to "1" (Unprotected).

- 2. If all DYBs are cleared to "1" after power up, then the sectors may be modified if PPB of that sector is also cleared to "1".

- 3. It is possible to have sectors that are persistently locked with sectors that are left in the dynamic state.

- 4. The DYB Set or Clear commands for the dynamic sectors signify protected or unprotected state of the sectors respectively. However, if there is a need to change the status of the persistently locked sectors, a few more steps are required. First, the PPB Lock Bit must be cleared by either putting the device through a power-cycle, or hardware reset. The PPBs can then be changed to reflect the desired settings. Setting the PPB Lock Bit once again locks the PPBs, and the device operates normally again.

- 5. To achieve the best protection, it is recommended to execute the PPB Lock Bit Set command early in the boot code and protect the boot code by holding WP#/ACC = VIL. Note that the PPB and DYB bits have the same function when WP#/ACC = V<sub>HH</sub> as they do when

Note that the PPB and DYB bits have the same function when WP#/ACC =  $V_{HH}$  as they do when WP#/ACC =VIH.

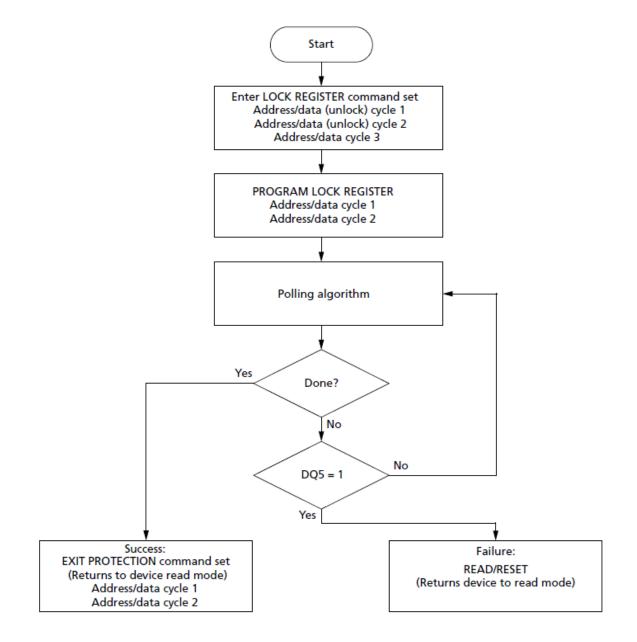

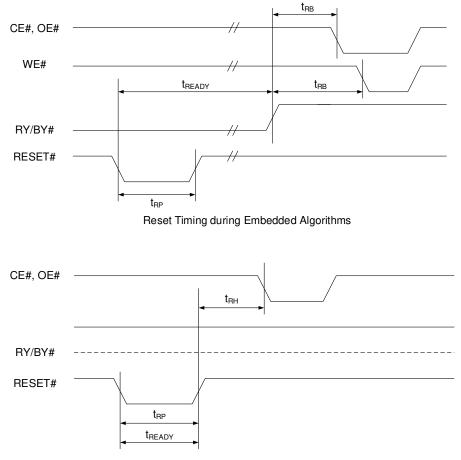

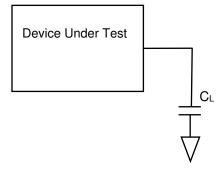

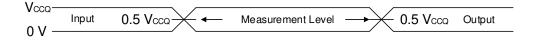

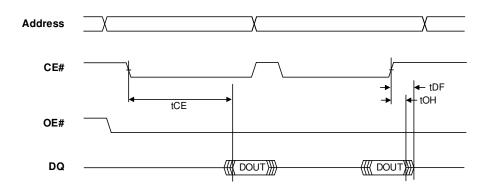

#### **8.4 Persistent Protection Bits**