# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

# LMX2522/LMX2532

# PLLatinum™ Frequency Synthesizer System with Integrated VCOs

### **General Description**

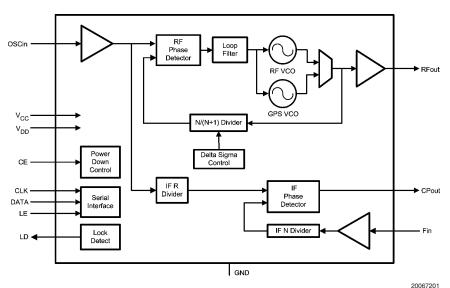

LMX2522 and LMX2532 are highly integrated, high performance, low power frequency synthesizer systems optimized for Korean PCS (K-PCS) with GPS and Korean Cellular (K-Cellular) with GPS, CDMA (1xRTT, IS-95) mobile handsets. Using a proprietary digital phase locked loop technique, LMX2522 and LMX2532 generate very stable, low noise local oscillator signals for up and down conversion in wireless communications devices.

LMX2522 and LMX2532 include a RF voltage controlled oscillator (VCO), a GPS VCO, a loop filter, and a fractional-N RF PLL based on a delta sigma modulator. In concert these blocks form a closed loop RF and GPS synthesizer system. LMX2522 supports the Korean PCS band with GPS and LMX2532 supports the Korean Cellular band with GPS.

LMX2522 and LMX2532 include an Integer-N IF PLL also. For more flexible loop filter designs, the IF PLL includes a 4-level programmable charge pump. Together with an external VCO and loop filter, LMX2522 and LMX2532 make a complete closed loop IF synthesizer system.

Serial data is transferred to the device via a three-wire MICROWIRE interface (DATA, LE, CLK).

Operating supply voltage ranges from 2.7 V to 3.3 V. LMX2502 and LMX2512 feature low current consumption: 17 mA at 2.8 V.

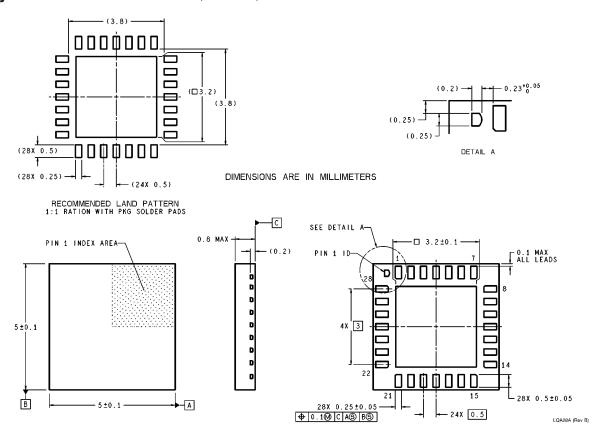

LMX2522 and LMX2532 are available in a 28-pin leadless leadframe package (LLP).

#### **Features**

- Small Size

- Small 5.0 mm x 5.0 mm x 0.75 mm 28-Pin LLP Package

- RF/GPS Synthesizer System

Integrated RF VCO

Integrated GPS VCO

Integrated Loop Filter

Low Spurious, Low Phase Noise Fractional-N RF PLL Based on 11-bit Delta Sigma Modulator

10 kHz Frequency Resolution

- IF Synthesizer System

Integer-N IF PLL

Programmable Charge Pump Current Levels

Programmable Frequencies

- Supports Various Reference Oscillator Frequencies 19.20/19.68 MHz

- Fast Lock Time: 500 µs

- Low Current Consumption 17 mA at 2.8 V

- 2.7 V to 3.3 V Operation

- Digital Filtered Lock Detect Output

- Hardware and Software Power Down Control

### **Applications**

- Korean PCS CDMA Systems with GPS

- Korean Cellular CDMA Systems with GPS

## **Functional Block Diagram**

PLLatinum is a trademark of National Semiconductor Corporation.

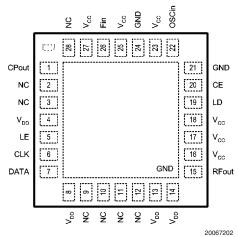

# **Connection Diagram**

### 28-Pin LLP (LQ) Package

NOTE: Analog ground connected through exposed die attached pad.

# **Pin Descriptions**

|    | Name            | I/O | Description                                          |

|----|-----------------|-----|------------------------------------------------------|

| 1  | CPout           | 0   | IF PLL charge pump output                            |

| 2  | NC              | _   | Do not connect to any node on printed circuit board. |

| 3  | NC              | _   | Do not connect to any node on printed circuit board. |

| 4  | $V_{DD}$        | _   | Supply voltage for IF analog circuitry               |

| 5  | LE              | I   | MICROWIRE Latch Enable                               |

| 6  | CLK             | I   | MICROWIRE Clock                                      |

| 7  | DATA            | I   | MICROWIRE Data                                       |

| 8  | $V_{DD}$        | _   | Supply voltage for VCOs                              |

| 9  | NC              | _   | Do not connect to any node on printed circuit board. |

| 10 | NC              | _   | Do not connect to any node on printed circuit board. |

| 11 | NC              | _   | Do not connect to any node on printed circuit board. |

| 12 | NC              | _   | Do not connect to any node on printed circuit board. |

| 13 | $V_{DD}$        | _   | Supply voltage for VCOs                              |

| 14 | $V_{DD}$        | _   | Supply voltage for VCOs output buffer                |

| 15 | RFout           | 0   | Buffered VCO output                                  |

| 16 | V <sub>CC</sub> | _   | Supply voltage for RF prescaler                      |

| 17 | V <sub>CC</sub> | _   | Supply voltage for charge pump                       |

| 18 | V <sub>CC</sub> | _   | Supply voltage for RF digital circuitry              |

| 19 | LD              | 0   | Lock Detect                                          |

| 20 | CE              | I   | Chip Enable control pin                              |

| 21 | GND             | _   | Ground for digital circuitry                         |

| 22 | OSCin           | I   | Reference frequency input                            |

| 23 | V <sub>CC</sub> | _   | Supply voltage for reference input buffer            |

| 24 | GND             | _   | Ground for digital circuitry                         |

| 25 | V <sub>CC</sub> | _   | Supply voltage for IF digital circuitry              |

| 26 | Fin             | I   | IF buffer/prescaler input                            |

| 27 | V <sub>CC</sub> | _   | Supply voltage for IF buffer/prescaler               |

| 28 | NC              | _   | Do not connect to any node on printed circuit board. |

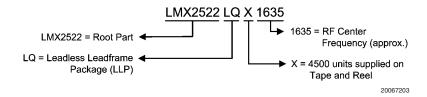

# **Ordering Information**

| Part Number    | RF Min.<br>(MHz) | RF Max.<br>(MHz) | RF Center<br>(MHz) | IF<br>(MHz) | GPS<br>(MHz) | Package<br>Marking | Supplied As   |

|----------------|------------------|------------------|--------------------|-------------|--------------|--------------------|---------------|

| LMX2522LQX1635 | 1619.62          | 1649.62          | ~1635              | 440.76      | 1355.04      | 25221635           | 4500 units on |

|                |                  |                  |                    |             |              |                    | tape and reel |

| LMX2522LQ1635  | 1619.62          | 1649.62          | ~1635              | 440.76      | 1355.04      | 25221635           | 1000 units on |

|                |                  |                  |                    |             |              |                    | tape and reel |

| LMX2532LQX0967 | 954.42           | 979.35           | ~967               | 170.76      | 1490.04      | 25320967           | 4500 units on |

|                |                  |                  |                    |             |              |                    | tape and reel |

| LMX2532LQ0967  | 954.42           | 979.35           | ~967               | 170.76      | 1490.04      | 25320967           | 1000 units on |

|                |                  |                  |                    |             |              |                    | tape and reel |

| LMX2532LQX1065 | 1052.64          | 1077.57          | ~1065              | 367.20      | 1391.82      | 25321065           | 4500 units on |

|                |                  |                  |                    |             |              |                    | tape and reel |

| LMX2532LQ1065  | 1052.64          | 1077.57          | ~1065              | 367.20      | 1391.82      | 25321065           | 1000 units on |

|                |                  |                  |                    |             |              |                    | tape and reel |

# **Part Number Description**

# **Absolute Maximum Ratings** (Notes 1,

2, 3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Parameter           | Symbol           | Ratings                       | Units |

|---------------------|------------------|-------------------------------|-------|

| Supply Voltage      | $V_{CC}, V_{DD}$ | -0.3 to 3.6                   | V     |

| Voltage on any pin  | V <sub>I</sub>   | -0. 3 to V <sub>DD</sub> +0.3 | V     |

| to GND              |                  | -0. 3 to V <sub>CC</sub> +0.3 | V     |

| Storage Temperature | T <sub>STG</sub> | -65 to 150                    | °C    |

| Range               |                  |                               |       |

# Recommended Operating Conditions

| Parameter               | Symbol           | Min | Тур | Max | Units |

|-------------------------|------------------|-----|-----|-----|-------|

| Ambient Temperature     | T <sub>A</sub>   | -30 | 25  | 85  | Ĵ     |

| Supply Voltage (to GND) | $V_{CC}, V_{DD}$ | 2.7 |     | 3.3 | V     |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, refer to the Electrical Characteristics section. The guaranteed specifications apply only for the conditions listed.

Note 2: This device is a high performance RF integrated circuit with an ESD rating  $\leq$  2 kV and is ESD sensitive. Handling and assembly of this device should be done at ESD protected work stations.

Note 3: GND = 0 V.

# **Electrical Characteristics** $(V_{CC} = V_{DD} = 2.8 \text{ V}, T_A = 25 ^{\circ}\text{C}; \text{ unless otherwise noted.})$

| Symbol                            | Parameter                              |                    | Conditions          | Min     | Тур  | Max             | Units     |

|-----------------------------------|----------------------------------------|--------------------|---------------------|---------|------|-----------------|-----------|

| I <sub>CC</sub> PARA              | METERS                                 |                    |                     |         | -    |                 |           |

| I <sub>CC</sub> + I <sub>DD</sub> | Total Supply Current                   |                    | OB_CRL [1:0] = 00   |         | 17   | 19              | mA        |

| (I <sub>CC</sub> +                |                                        |                    | OB_CRL [1:0] = 00   |         | 16   | 18              | mA        |

| $I_{DD})_{RF}$                    |                                        |                    |                     |         |      |                 |           |

| I <sub>PD</sub>                   | Power Down Current (Note 4)            |                    | CE = Low or         |         |      | 20              | μΑ        |

|                                   |                                        |                    | RF_EN = 0           |         |      |                 |           |

|                                   |                                        |                    | IF_EN = 0           |         |      |                 |           |

| REFEREN                           | CE OSCILLATOR                          |                    |                     |         |      |                 |           |

| f <sub>OSCin</sub>                | Reference Oscillator                   | Input Frequency    | 19.20 MHz and 19.68 | 19.20   |      | 19.68           | MHz       |

|                                   | (Note 5)                               |                    | MHz are supported   |         |      |                 |           |

| V <sub>OSCin</sub>                | Reference Oscillator Input sensitivity |                    |                     |         | 0.2  | V <sub>CC</sub> | $V_{P-P}$ |

| RF VCO                            |                                        |                    |                     |         |      |                 |           |

| $f_{RFout}$                       | Frequency Range                        | LMX2522LQ1635      | RF VCO              | 1619.62 |      | 1649.62         | MHz       |

|                                   | (Note 6)                               | LMX2532LQ0967      |                     | 954.42  |      | 979.35          | MHz       |

|                                   |                                        | LMX2532LQ1065      |                     | 1052.64 |      | 1077.57         | MHz       |

| P <sub>RFout</sub>                | RF Output Power                        | OB_CRL [1:0] = 11  |                     | -2      | 1    | 4               | dBm       |

|                                   |                                        | OB_CRL [1:0] = 10  |                     | -5      | -2   | 1               | dBm       |

|                                   |                                        | OB_CRL [1:0] = 01  |                     | -7      | -4   | -1              | dBm       |

|                                   |                                        | OB_CRL [1:0] = 00  |                     | -9      | -6   | -3              | dBm       |

|                                   | Lock Time (Note 7)                     | LMX2522LQ1635      | 30 MHz Band for RF  |         | 500  | 800             | μs        |

|                                   |                                        |                    | PLL                 |         |      |                 |           |

|                                   |                                        | LMX2532LQ0967      | 25 MHz Band for RF  |         | 500  | 800             | μs        |

|                                   |                                        |                    | PLL                 |         |      |                 |           |

|                                   |                                        | LMX2532LQ1065      | 25 MHz Band for RF  |         | 500  | 800             | μs        |

|                                   |                                        |                    | PLL                 |         |      |                 |           |

|                                   | Reference Spurs                        |                    |                     |         |      | -75             | dBc       |

|                                   | RMS Phase Error                        | RF PLL in all band |                     |         | 1.3  |                 | degrees   |

| L(f)                              | Phase Noise                            | LMX2522LQ1635      | @100 kHz offset     |         | -113 | -112            | dBc/Hz    |

|                                   |                                        |                    | @1.25 MHz offset    |         | -138 | -136            | dBc/Hz    |

|                                   |                                        | LMX2532LQ0967      | @100 kHz offset     |         | -117 | -115            | dBc/Hz    |

|                                   |                                        |                    | @900 kHz offset     |         | -139 | -138            | dBc/Hz    |

|                                   |                                        | LMX2532LQ1065      | @100 kHz offset     |         | -117 | -115            | dBc/Hz    |

|                                   |                                        |                    | @900kHz offset      |         | -139 | -138            | dBc/Hz    |

|                                   | 2nd Harmonic Suppre                    | ession             |                     |         |      | -25             | dBc       |

|                                   | 3rd Harmonic Suppre                    | ession             |                     |         |      | -20             | dBc       |

# **Electrical Characteristics** ( $V_{CC} = V_{DD} = 2.8 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ ; unless otherwise noted.) (Continued)

| Symbol             | Parameter              |                | Conditions          | Min                 | Тур     | Max                 | Units   |

|--------------------|------------------------|----------------|---------------------|---------------------|---------|---------------------|---------|

| GPS VCO            | )                      |                |                     |                     |         |                     |         |

| f <sub>RFout</sub> | Operating Frequency    | LMX2522LQ1635  | GPS VCO             |                     | 1355.04 |                     | MHz     |

|                    |                        | LMX2532LQ0967  |                     |                     | 1490.04 |                     | MHz     |

|                    |                        | LMX2532LQ1065  |                     |                     | 1391.82 |                     | MHz     |

| p <sub>RFout</sub> | Output Power           |                | OB_CRL [1:0] = 11   | -2                  | 1       | 4                   | dBm     |

|                    |                        |                | OB_CRL [1:0] = 10   | -5                  | -2      | 1                   | dBm     |

|                    |                        |                | OB_CRL [1:0] = 01   | -7                  | -4      | -1                  | dBm     |

|                    |                        |                | OB_CRL [1:0] = 00   | -9                  | -6      | -3                  | dBm     |

|                    | Lock Time (Note 7)     |                | From RF to GPS PLL  |                     | 600     | 800                 | μs      |

|                    | Reference Spurs        |                |                     |                     |         | -75                 | dBc     |

|                    | RMS Phase Error        |                | RF PLL in all band  |                     | 1.3     |                     | degrees |

| L(f)               | Phase Noise            |                | @100 kHz offset     |                     | -113    | -112                | dBc/Hz  |

|                    |                        |                | @1.25 MHz offset    |                     | -138    | -136                | dBc/Hz  |

|                    | 2nd Harmonic Suppre    | ssion          |                     |                     |         | -25                 | dBc     |

|                    | 3rd Harmonic Suppres   | ssion          |                     |                     |         | -20                 | dBc     |

| IF PLL             |                        |                |                     |                     |         |                     |         |

| f <sub>Ein</sub>   | Operating Frequency    | LMX2522LQ1635  | IF_FREQ [1:0] = 10, |                     | 440.76  |                     | MHz     |

|                    | (Note 8)               |                | Default Value       |                     |         |                     |         |

|                    |                        | LMX2532LQ0967  | IF_FREQ [1:0] = 00, |                     | 170.76  |                     | MHz     |

|                    |                        |                | Default Value       |                     |         |                     |         |

|                    |                        | LMX2532LQ1065  | IF_FREQ [1:0] = 01, |                     | 367.20  |                     | MHz     |

|                    |                        |                | Default Value       |                     |         |                     |         |

| p <sub>Fin</sub>   | IF Input Sensitivity   |                |                     | -10                 |         | 0                   | dBm     |

| $f_{\PhiIF}$       | Phase Detector Frequ   | ency           |                     |                     | 120     |                     | kHz     |

| I <sub>CPout</sub> | Charge Pump Current    |                | IF_CUR [1:0] = 00   |                     | 100     |                     | μΑ      |

|                    |                        |                | IF_CUR [1:0] = 01   |                     | 200     |                     | μΑ      |

|                    |                        |                | IF_CUR [1:0] = 10   |                     | 300     |                     | μΑ      |

|                    |                        |                | IF_CUR [1:0] = 11   |                     | 800     |                     | μΑ      |

| DIGITAL I          | INTERFACE (DATA, CLI   | K, LE, LD, CE) |                     |                     |         |                     |         |

| V <sub>IH</sub>    | High-Level Input Volta | ge             |                     | 0.8 V <sub>DD</sub> |         | $V_{DD}$            | V       |

|                    |                        |                |                     | 0.8 V <sub>CC</sub> |         | V <sub>cc</sub>     | V       |

| V <sub>IL</sub>    | Low-Level Input Volta  | ge             |                     | 0                   |         | 0.2 V <sub>DD</sub> | V       |

|                    |                        |                |                     | 0                   |         | 0.2 V <sub>CC</sub> | V       |

| I <sub>IH</sub>    | High-Level Input Curre | ent            |                     | -10                 |         | 10                  | μA      |

| I <sub>IL</sub>    | Low-Level Input Curre  | nt             |                     | -10                 |         | 10                  | μA      |

|                    | Input Capacitance      |                |                     |                     | 3       |                     | pF      |

| V <sub>OH</sub>    | High-Level Output Vol  | tage           |                     | 0.9 V <sub>DD</sub> |         |                     | V       |

|                    |                        |                |                     | 0.9 V <sub>CC</sub> |         |                     | V       |

| V <sub>OL</sub>    | Low-Level Output Vol   | age            |                     |                     |         | 0.1 V <sub>DD</sub> | V       |

| UL                 | '                      | -              |                     |                     |         | 0.1 V <sub>CC</sub> | V       |

|                    | Output Capacitance     |                | +                   |                     |         | 5                   | pF      |

# $\textbf{Electrical Characteristics} \; (\textit{V}_{\textit{CC}} = \textit{V}_{\textit{DD}} = 2.8 \; \textit{V}, \; \textit{T}_{\textit{A}} = 25 \; \text{^{\circ}C}; \; \textit{unless otherwise noted.}) \; \; (\textit{Continued})$

| Symbol           | Parameter                         | Conditions | Min | Тур | Max | Units |  |  |  |  |

|------------------|-----------------------------------|------------|-----|-----|-----|-------|--|--|--|--|

| MICROWIR         | MICROWIRE INTERFACE TIMING        |            |     |     |     |       |  |  |  |  |

| t <sub>CS</sub>  | Data to Clock Set Up Time         |            | 50  |     |     | ns    |  |  |  |  |

| t <sub>CH</sub>  | Data to Clock Hold Time           |            | 10  |     |     | ns    |  |  |  |  |

| t <sub>cwh</sub> | Clock Pulse Width High            |            | 50  |     |     | ns    |  |  |  |  |

| t <sub>CWL</sub> | Clock Pulse Width Low             |            | 50  |     |     | ns    |  |  |  |  |

| t <sub>ES</sub>  | Clock to Latch Enable Set Up Time |            | 50  |     |     | ns    |  |  |  |  |

| t <sub>EW</sub>  | Latch Enable Pulse Width          |            | 50  |     |     | ns    |  |  |  |  |

Note 4: In power down mode, set DATA, CLK and LE pins to 0 V (GND).

Note 5: The reference frequency must also be programmed using the OSC\_FREQ control bit. For other reference frequencies, please contact National Semiconductor.

Note 6: For other frequency ranges, please contact National Semiconductor.

Note 7: Lock time is defined as the time difference between the beginning of the frequency transition and the point at which the frequency remains within +/- 1 kHz of the final frequency.

Note 8: Frequencies other that the default value can be programmed using Words R4 and R5. See Programming Description for details.

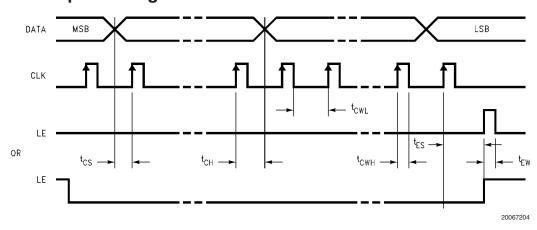

# **Serial Data Input Timing**

### **Functional Description**

#### **GENERAL DESCRIPTION**

LMX2522/32 is a highly integrated frequency synthesizer system that generates LO signals for PCS, Cellular CDMA and GPS systems. These devices include all of the functional blocks of a PLL, RF VCO, prescaler, RF phase detector, and loop filter. The need for external components is limited to a few passive elements for matching the output impedance and bypass elements for power line stabilization.

In addition to the RF circuitry, the IC also includes IF frequency dividers, and an IF phase detector to complete the IF synthesis with an external VCO and loop filter. *Table 4* summarizes the counter values to generate the default IF frequencies.

Using a low spurious fractional-N synthesizer based on a delta sigma modulator, the circuit can support 10 kHz channel spacing for PCS, Cellular CDMA and GPS systems.

The fractional-N synthesizer enables faster lock time, which reduces power consumption and system set-up time. Additionally, the loop filter occupies a smaller area as opposed to the integer-N architecture. This allows the loop filter to be embedded into the circuit, minimizing the external noise coupling and total form factor. The delta sigma architecture delivers very low spurious, which can be a significant problem for other PLL solutions.

The circuit also supports commonly used reference frequencies of 19.20 MHz and 19.68 MHz.

#### **FREQUENCY GENERATION**

#### **RF-PLL Section**

The divide ratio can be calculated using the following equation:

LMX2522 – PCS CDMA:

$f_{VCO}$  = {8 x RF\_B + RF\_A + (RF\_FN /  $f_{OSC}$ ) x 10<sup>4</sup>} x  $f_{OSC}$  where (RF\_A < RF\_B)

LMX2532 - Cellular CDMA:

$f_{VCO}$  = {6 x RF\_B + RF\_A + (RF\_FN /  $f_{OSC})$  x 10^4} x  $f_{OSC}$  where (RF\_A < RF\_B)

where

f<sub>VCO</sub>: Output frequency of voltage controlled oscillator (VCO)

RF\_B: Preset divide ratio of binary 4-bit programmable counter (2  $\leq$  RF\_B  $\leq$  15)

RF\_A: Preset divide ratio of binary 3-bit swallow counter (0  $\leq$  RF\_A  $\leq$  7 for LMX2522 or 0  $\leq$  RF\_A  $\leq$  5 for LMX2532)

RF\_FN: Preset numerator of binary 11-bit modulus counter (0  $\leq$  RF\_FN < 1920 for  $f_{\rm OSC}$  = 19.20 MHz or 0  $\leq$  RF\_FN < 1968 for  $f_{\rm OSC}$  = 19.68 MHz)

f<sub>OSC</sub>: Reference oscillator frequency

#### **GPS-PLL SECTION**

The divide ratio can be calculated using the following equation:

LMX2522 - PCS CDMA:

$f_{\rm VCO}$  = {6 x RF\_B + RF\_A + (RF\_FN /  $f_{\rm OSC})$  x 10^4} x  $f_{\rm OSC}$  where (RF\_A < RF\_B)

LMX2532 - Cellular CDMA:

$\rm f_{VCO}$  = {8 x RF\_B + RF\_A + (RF\_FN /  $\rm f_{OSC})~x~10^4}\}~x~\rm f_{OSC}$  where (RF\_A < RF\_B)

#### where

f<sub>VCO</sub>: Output frequency of voltage controlled oscillator (VCO)

RF\_B: Preset divide ratio of binary 4-bit programmable counter ( $2 \le RF_B \le 15$ )

RF\_A: Preset divide ratio of binary 3-bit swallow counter ( $0 \le RF_A \le 5$  for LMX2522 or  $0 \le RF_A \le 7$  for LMX2532)

RF\_FN: Preset numerator of binary 11-bit modulus counter (0  $\leq$  RF\_FN < 1920 for f $_{OSC}$  = 19.20 MHz or 0  $\leq$  RF\_FN < 1968 for f $_{OSC}$  = 19.68 MHz)

f<sub>OSC</sub>: Reference oscillator frequency

PCS CDMA applications using the LMX2522, if the GPS frequency is 1355.04 MHz, *Table 1* provides the proper register settings:

TABLE 1. Settings for GPS (1355.04 MHz) in LMX2522 PCS CDMA application

| Reference Frequency | RF_B | RF_A | RF_FN |

|---------------------|------|------|-------|

| 19.20 MHz           | 11   | 4    | 1104  |

| 19.68 MHz           | 11   | 2    | 1680  |

Cellular CDMA applications using the LMX2532, in which the GPS frequency is 1490.04 MHz, then *Table 2* provides the proper register settings:

TABLE 2. Settings for GPS (1490.04 MHz) in LMX2532 Cellular CDMA application

| Reference Frequency | RF_B | RF_A | RF_FN |

|---------------------|------|------|-------|

| 19.20 MHz           | 9    | 5    | 1164  |

| 19.68 MHz           | 9    | 3    | 1404  |

Cellular CDMA applications using the LMX2532, in which the GPS frequency is 1391.82 MHz, then *Table 3* provides the proper register settings:

TABLE 3. Settings for GPS (1391.82 MHz) in LMX2532 Cellular CDMA application

| Reference Frequency | RF_B | RF_A | RF_FN |

|---------------------|------|------|-------|

| 19.20 MHz           | 9    | 0    | 942   |

| 19.68 MHz           | 8    | 6    | 1422  |

#### **IF-PLL SECTION**

$f_{VCO}$  = {16 x IF\_B + IF\_A} x  $f_{OSC}$  / IF\_R where (IF\_A < IF\_B) where

$f_{\text{VCO}}\text{:}$  Output frequency of the voltage controlled oscillator (VCO)

IF\_B: Preset divide ratio of the binary 9-bit programmable counter (1  $\leq$  IF\_B  $\leq$  511)

IF\_A: Preset divide ratio of the binary 4-bit swallow counter (0  $\leq$  IF\_A  $\leq$  15)

f<sub>OSC</sub>: Reference oscillator frequency

IF\_R: Preset divide ratio of the binary 9-bit programmable reference counter ( $2 \le IF_R \le 511$ )

From the above equation, the LMX2522/32 generates the fixed IF frequencies as summarized in *Table 4*.

### Functional Description (Continued)

**TABLE 4. IF Frequencies**

| Device Type   | f <sub>vco</sub><br>(MHz) | IF_B | IF_A | f <sub>OSC</sub> /IF_R<br>(kHz) |

|---------------|---------------------------|------|------|---------------------------------|

| LMX2522LQ1635 | 440.76                    | 229  | 9    | 120                             |

| LMX2532LQ0967 | 170.67                    | 88   | 15   | 120                             |

| LMX2532LQ1065 | 367.20                    | 191  | 4    | 120                             |

#### **VCO FREQUENCY TUNING**

The center frequency of the RF VCO is mainly determined by the resonant frequency of the tank circuit. This tank circuit is implemented on-chip and requires no external inductor. The LMX2522/32 actively tunes the tank circuit to the required frequency with the built-in tracking algorithm.

#### **BANDWIDTH CONTROL AND FREQUENCY LOCK**

During the frequency acquisition period, the loop bandwidth is significantly extended to achieve frequency lock. Once frequency lock occurs, the PLL will return to a steady state condition with the loop bandwidth set to its nominal value. The transition between acquisition and lock modes occurs seamlessly and extremely fast, thereby, meeting the stringent requirements associated with lock time and phase noise. Several controls (BW\_DUR, BW\_CRL and BW\_EN) are used to optimize the lock time performance.

#### SPURIOUS REDUCTION

To improve the spurious performance of the device one of two types of spurious reduction schemes can be selected:

- A continuous optimization scheme, which tracks the environmental and voltage variations, giving the best spurious performance over changing conditions

- A one time optimization scheme, which sets the internal compensation values only when the PLL goes into a locked state.

The spurious reduction can also be disabled, but it is recommended that the continuous optimization mode be used for normal operation.

#### **POWER DOWN MODE**

The LMX2522 and LMX2532 include a power down mode to reduce the power consumption. The LMX2522/32 enters into the power down mode either by taking the CE pin LOW or by setting the power down bits in Register R1. *Table 5* summarizes the power down function. If CE is set LOW, the circuit is powered down regardless of the register values. When CE is HIGH, the IF and RF circuitry are individually powered down by setting the register bits.

**TABLE 5. Power Down Configuration**

| CE Pin | RF_EN | IF_EN | RF Circuitry | IF Circuitry |

|--------|-------|-------|--------------|--------------|

| 0      | Х     | Х     | OFF          | OFF          |

| 1      | 0     | 0     | OFF          | OFF          |

| 1      | 0     | 1     | OFF          | ON           |

| 1      | 1     | 0     | ON           | OFF          |

| 1      | 1     | 1     | ON           | ON           |

X = Don't care.

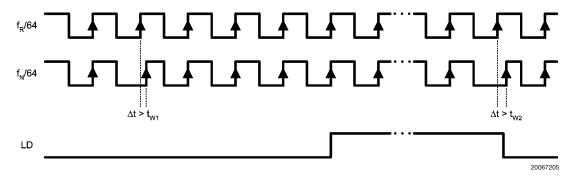

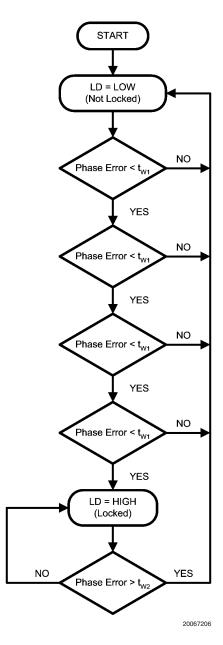

#### LOCK DETECT

The LD output can be used to indicate the lock status of the RF PLL. Bit 21 in Register R0 determines the signal that appears on the LD pin. When the RF PLL is not locked, the LD pin remains LOW. After obtaining phase lock, the LD pin will have a logical HIGH level. The output can also be programmed to be ground at all times.

**TABLE 6. Lock Detect Modes**

| LD Bit | Mode          |

|--------|---------------|

| 0      | Disable (GND) |

| 1      | Enable        |

**TABLE 7. Lock Detect Logic Table**

| RF PLL Section | LD Output |

|----------------|-----------|

| Locked         | HIGH      |

| Not Locked     | LOW       |

FIGURE 1. Lock Detect Timing Diagram Waveform

**Note 9:** LD output becomes low when the phase error is larger than  $t_{W2}$ . **Note 10:** LD output becomes high when the phase error is less than  $t_{W1}$  for four or more consecutive cycles.

Note 11: Phase Error is measured on leading edge. Only errors greater than  $t_{W1}$  and  $t_{W2}$  are labeled.

Note 12:  $t_{W1}$  and  $t_{W2}$  are equal to 10 ns.

Note 13: The lock detect comparison occurs with every 64  $^{th}$  cycle of  $\rm f_R$  and  $\rm f_{N\cdot}$

# Functional Description (Continued)

FIGURE 2. Lock Detect Flow Diagram

#### **MICROWIRE INTERFACE**

The programmable register set is accessed via the MICROWIRE serial interface. The interface comprises three signal pins: CLK, DATA, and LE. Serial data (DATA) is clocked into the 24-bit shift register on the rising edge of the

clock (CLK). The last bits decode the internal control register address. When the Latch Enable (LE) transitions from LOW to HIGH, data stored in the shift registers is loaded into the corresponding control register.

# **Programming Description**

#### **CONTROL REGISTER CONTENT MAP**

The serial interface has a 24-bit shift register to store the incoming data bits temporarily. The incoming Data is loaded into the shift register from MSB to LSB. The Data is shifted at the rising edge of the Clock signal. When the Latch Enable signal transitions from LOW to HIGH, the data stored in the shift register is transferred to the proper register depending on the address bit settings. The selection of the particular register is determined by the control bits indicated in boldface text.

At initial start-up, the MICROWIRE loading requires 4 default words (registers R3, loaded first, to R0, loaded last). After the device has been initially programmed, the RF VCO frequency can be changed using a single register (R0). If an IF frequency other than the default value for the device is desired the SPI\_DEF bit should be set to 0, the desired values for IF\_A, IF\_B, and IF\_R entered and words R6 to R0 should be sent.

The control register content map describes how the bits within each control register are allocated to the specific control functions.

#### **Complete Register Map**

| ster      | MSB   | SHIFT REGISTER BIT LOCATION |       |     |       |                 |    |             |     |    |    | BIT L | OCA | TION | 1   |   |   | LSB |    |     |     |     |   |   |

|-----------|-------|-----------------------------|-------|-----|-------|-----------------|----|-------------|-----|----|----|-------|-----|------|-----|---|---|-----|----|-----|-----|-----|---|---|

| Register  | 23    | 22                          | 21    | 20  | 19    | 18              | 17 | 16          | 15  | 14 | 13 | 12    | 11  | 10   | 9   | 8 | 7 | 6   | 5  | 4   | 3   | 2   | 1 | 0 |

| R0        | SPI_  | RF_                         | RF_   | SP  | RF_B  | RF_A RF_FN      |    |             |     |    |    |       |     |      |     | 0 | 0 |     |    |     |     |     |   |   |

| (Default) | DEF   | SEL                         | LD    | UR_ | [3:0] | 0] [2:0] [10:0] |    |             |     |    |    |       |     |      |     |   |   |     |    |     |     |     |   |   |

|           |       |                             |       | CRL |       |                 |    |             |     |    |    |       |     |      |     |   |   |     |    |     |     |     |   |   |

| R1        | IF_   |                             | OSC_  | 1   | 0     | 0               | 0  | 0           | 0   | 0  | 0  | SPL   | JR_ | 0    | 0   | 1 | 0 | 1   | OF | 3_  | RF_ | IF_ | 0 | 1 |

| (Default) | FREC  | )                           | FREQ  |     |       |                 |    |             |     |    |    | RD    | Γ   |      |     |   |   |     | CF | ٦L  | EN  | EN  |   |   |

|           | [1:0] |                             |       |     |       | [1:0]           |    |             |     |    |    |       |     |      |     |   |   |     |    |     |     |     |   |   |

| R2        | IF_   |                             | 0     | 0   | 1     | 0               | 0  | 1           | 1   | 1  | 0  | 1     | 1   | 0    | 1   | 0 | 1 | 0   | 0  | 0   | 1   | 0   | 1 | 0 |

| (Default) | CUR[  | 1:0]                        |       |     |       |                 |    |             |     |    |    |       |     |      |     |   |   |     |    |     |     |     |   |   |

| R3        | BW_   |                             | BW_   |     | BW_   | 1               | 0  | 1           | 1   | 1  | 1  | 0     | 1   | 0    | 0   | 0 | 1 | 1   | 0  | VC  | 00_ | 0   | 1 | 1 |

| (Default) | DUR   |                             | CRL   |     | EN    |                 |    |             |     |    |    |       |     |      |     |   |   |     |    | Cl  | JR  |     |   |   |

|           | [1:0] |                             | [1:0] |     |       |                 |    |             |     |    |    |       |     |      |     |   |   |     |    | [1: | [0] |     |   |   |

| R4        | 0     | 0                           | 0     | 1   | 0     | 0               | 0  |             | IF, | _A |    |       |     |      | IF_ | В |   |     |    |     | 0   | 1   | 1 | 1 |

|           |       |                             |       |     |       |                 |    | [3:0] [8:0] |     |    |    |       |     |      |     |   |   |     |    |     |     |     |   |   |

| R5        | 0     | 0                           | 1     | 1   | 0     | 0               | 0  | 0           | 1   | 0  |    |       |     | IF_I | 3   |   |   |     |    | 0   | 1   | 1   | 1 | 1 |

|           |       |                             |       |     |       |                 |    |             |     |    |    |       |     | [8:0 | )]  |   |   |     |    |     |     |     |   |   |

| R6        | 1     | 0                           | 0     | 0   | 0     | 0               | 0  | 0           | 0   | 0  | 0  | 0     | 0   | 0    | 0   | 0 | 0 | 0   | 0  | 1   | 1   | 1   | 1 | 1 |

NOTE: Bold numbers represent the address bits.

#### **RO REGISTER**

The R0 register address bits (R0 [1:0]) are "00".

The SPI\_DEF bit selects between using the default IF counter values and user programmable values. The use of the default counter values requires that only words R0 to R3 (registers R3, loaded first, to R0, loaded last) be sent after initial power up.

The RF\_LD bit activates the lock detect output of the LD pin (pin 19). The lock detect mode shows the lock status of the RF PLL. The waveform of the lock detect mode is shown in *Figure 1*, in the **Functional Description** section on **LOCK DETECT**.

The SPUR\_CRL bit is set to 1 only in the GPS mode with the LMX2532LQ1065 when a 19.68 MHz reference oscillator is used. The RF N counter consists of the 4-bit programmable counter (RF\_B counter), the 3-bit swallow counter (RF\_A counter) and the 11-bit delta sigma modulator (RF\_FN counter). The equations for calculating the counter values are presented below.

#### **R0 REGISTER**

|           | MSB  | SHIFT REGISTER BIT LOCATION |     |     |      |                 |                                              |  |      |      | LSB |  |  |  |  |     |    |   |   |  |   |               |

|-----------|------|-----------------------------|-----|-----|------|-----------------|----------------------------------------------|--|------|------|-----|--|--|--|--|-----|----|---|---|--|---|---------------|

| ter       | 23   | 22                          | 21  | 20  | 19   | 18              | 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |  |      |      |     |  |  |  |  |     |    | 1 | 0 |  |   |               |

| Register  |      |                             |     |     |      |                 |                                              |  | Data | Fiel | d   |  |  |  |  |     |    | · |   |  |   | dress<br>ield |

| R0        | SPI_ | RF_                         | RF_ | SP  | RF_  | _B              |                                              |  | RF_  | _A   |     |  |  |  |  | RF_ | FN |   |   |  | 0 | 0             |

| (Default) | DEF  | SEL                         | LD  | UR_ | [3:0 | 0] [2:0] [10:0] |                                              |  |      |      |     |  |  |  |  |     |    |   |   |  |   |               |

|           |      |                             |     | CRL |      |                 |                                              |  |      |      |     |  |  |  |  |     |    |   |   |  |   |               |

| Name         | Functions                                                              |

|--------------|------------------------------------------------------------------------|

| SPI_DEF      | Default Register Selection                                             |

|              | 0 = OFF (Use values set in R0 to R6)                                   |

|              | 1 = ON (Use default values set in R0 to R3)                            |

| RF_SEL       | RF Select Configuration                                                |

|              | See Table 8. RF_SEL Configuration below                                |

| RF_LD        | RF Lock Detect                                                         |

|              | 0 = Hard zero (GND)                                                    |

|              | 1 = Lock detect                                                        |

| SPUR_CRL     | Spur Control                                                           |

|              | 1 = LMX2532LQ1065 in GPS mode with 19.68 MHz reference oscillator only |

|              | 0 = All other options                                                  |

| RF_B [3:0]   | RF_B Counter                                                           |

|              | 4-bit programmable counter                                             |

|              | 2 ≤ RF_B ≤ 15                                                          |

| RF_A [2:0]   | RF_A Counter                                                           |

|              | 3-bit swallow counter                                                  |

|              | $0 \le RF\_A \le 7$ for LMX2522                                        |

|              | $0 \le RF\_A \le 5$ for LMX2532                                        |

| RF_FN [10:0] | RF Fractional Numerator Counter                                        |

|              | 11-bit programmable counter                                            |

|              | 0 ≤ RF_FN < 1920 for f <sub>OSC</sub> = 19.20 MHz                      |

|              | 0 ≤ RF_FN < 1968 for f <sub>OSC</sub> = 19.68 MHz                      |

#### TABLE 8. RF\_SEL Configuration

| Device Type | RF_SEL = 0 | RF_SEL = 1 |

|-------------|------------|------------|

| LMX2522     | GPS        | K-PCS      |

| LMX2532     | K-Cellular | GPS        |

RF N Counter Setting:

| Counter Name    | Symbol | Function                                                                  |

|-----------------|--------|---------------------------------------------------------------------------|

| Modulus Counter | RF_FN  | RF N Divider                                                              |

| Programmable    | RF_B   | N = Prescaler x RF_B + RF_A + (RF_FN / f <sub>OSC</sub> ) 10 <sup>4</sup> |

| Counter         |        |                                                                           |

| Swallow Counter | RF_A   |                                                                           |

Pulse Swallow Function:

$f = \{ Prescaler \ x \ RF\_B + RF\_A + (RF\_FN \ / \ f_{OSC}) \ x \ 10^4 \} \ x \ f_{OSC} \ where \ (RF\_A < RF\_B)$

where

$f_{\text{VCO}}$ : Output frequency of voltage controlled oscillator (VCO)

Prescaler Values:

| Device Type | RF Prescaler | GPS Prescaler |

|-------------|--------------|---------------|

| LMX2522     | 8            | 6             |

| LMX2532     | 6            | 8             |

RF\_B: Preset divide ratio of binary 4-bit programmable counter ( $2 \le RF_B \le 15$ )

RF\_A: Preset divide ratio of binary 3-bit swallow counter ( $0 \le RF_A \le 7$  for prescaler of 8 or  $0 \le RF_A \le 5$  for prescaler of 6) RF\_FN: Preset numerator of binary 11-bit modulus counter ( $0 \le RF_FN < 1920$  for  $f_{OSC} = 19.20$  MHz;  $0 \le RF_FN < 1968$  for  $f_{OSC} = 19.68$  MHz).

f<sub>OSC</sub>: Reference oscillator frequency

NOTE: For the use of reference frequencies other than those specified, please contact National Semiconductor.

#### **R1 REGISTER**

operation.

The R1 register address bits (R1 [1:0]) are "01".

The IF\_FREQ bits selects the default IF frequency applicable to the specific CDMA system. For the LMX2522 the default IF frequency is 440.76 MHz, and for the LMX2532 the default IF frequencies are 367.20 MHz and 170.76 MHz, depending on variant.

Reference Frequency Selection bit (OSC\_FREQ) selects either 19.20 MHz or 19.68 MHz for the reference oscillator frequency. The internal spurious reduction scheme is controlled by the SPUR\_RDT [1:0] bits. There are two different spur reduction schemes: a continuous tracking mode and a single optimization mode. The continuous tracking mode will adjust for variations in voltage and temperature. The single optimization mode fixes the internal compensation parameters only when the PLL goes into

the locked state. The spur reduction can also be disabled, but it is recommended that the continuous mode be used for normal

The OB\_CRL [1:0] bits determine the power level of the RF output buffer. The power level is set according to the system requirement.

The two bits, RF\_EN and IF\_EN, logically select the active state of the RF/GPS synthesizer system and the IF PLL, respectively. The entire IC can be placed in a power down state by using the CE control pin (pin 20).

#### **R1 REGISTER**

|           | MSB   |                                                        |      |   |   |   |   | SH | IFT | REG  | ISTE  | R BI  | T LO | CAT | 101 | 1 |   |   |      |    |     |     |   | LSB   |

|-----------|-------|--------------------------------------------------------|------|---|---|---|---|----|-----|------|-------|-------|------|-----|-----|---|---|---|------|----|-----|-----|---|-------|

| ter       | 23    | 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 |      |   |   |   |   |    |     |      |       |       | 1    | 0   |     |   |   |   |      |    |     |     |   |       |

| Register  |       |                                                        |      |   |   |   |   |    | [   | Data | Field | d     |      |     |     |   |   |   | •    |    |     |     |   | dress |

| R1        | IF_   |                                                        | OSC_ | 1 | 0 | 0 | 0 | 0  | 0   | 0    | 0     | SPU   | JR_  | 0   | 0   | 1 | 0 | 1 | ОВ   | 3_ | RF_ | IF_ | 0 | 1     |

| (Default) | FREQ  | !                                                      | FREQ |   |   |   |   |    |     |      |       | RDT   | -    |     |     |   |   |   | CR   | lL | EN  | ΕN  |   |       |

|           | [1:0] |                                                        |      |   |   |   |   |    |     |      |       | [1:0] |      |     |     |   |   |   | [1:0 | 0] |     |     |   |       |

| Name           | Functions                                           |

|----------------|-----------------------------------------------------|

| IF_FREQ [1:0]  | IF Frequency Selection                              |

|                | 00 = 170.76 MHz (LMX2532LQ0967)                     |

|                | 01 = 367.20 MHz (LMX2532LQ1065)                     |

|                | 10 = 440.76 MHz (LMX2522LQ1635)                     |

| OSC_FREQ       | Reference Frequency Selection                       |

|                | 0 = 19.20 MHz                                       |

|                | 1 = 19.68 MHz                                       |

| SPUR_RDT [1:0] | Spur Reduction Scheme                               |

|                | 00 = No spur reduction                              |

|                | 01 = Not Used                                       |

|                | 10 = Continuous tracking of variation (Recommended) |

|                | 11 = One time optimization                          |

| OB_CRL [1:0]   | RF Output Power Control                             |

|                | 00 = Minimum Output Power                           |

|                | 01 =                                                |

|                | 10 =                                                |

|                | 11 = Maximum Output Power                           |

| RF_EN          | RF Enable                                           |

|                | 0 = RF Off                                          |

|                | 1 = RF On                                           |

| IF_EN          | IF Enable                                           |

|                | 0 = IF Off                                          |

|                | 1 = IF On                                           |

#### **R2 REGISTER**

The R2 Register address bits (R2 [1:0]) are "10".

The IF\_CUR [1:0] bits program the IF charge pump current. Considering the external IF VCO and loop filter, the user can select the amount of IF charge pump current to be  $100\mu A$ ,  $200\mu A$ ,  $300\mu A$  or  $800\mu A$ .

#### **R2 REGISTER**

|         |         | MSB   | MSB SHIFT REGISTER BIT LOCATION |    |    |    |    |    |    |    |    |         |    |    | LSB |      |   |   |   |   |   |   |   |   |   |  |

|---------|---------|-------|---------------------------------|----|----|----|----|----|----|----|----|---------|----|----|-----|------|---|---|---|---|---|---|---|---|---|--|

| te      |         | 23    | 22                              | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13      | 12 | 11 | 10  | 9    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| Registe |         |       | Data Field                      |    |    |    |    |    |    |    |    | Address |    |    |     |      |   |   |   |   |   |   |   |   |   |  |

| &       |         |       |                                 |    |    |    |    |    |    |    |    |         |    |    | F   | ield |   |   |   |   |   |   |   |   |   |  |

| R2      |         | IF_   |                                 | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0       | 1  | 1  | 0   | 1    | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |  |

| (De     | efault) | CUR[1 | :0]                             |    |    |    |    |    |    |    |    |         |    |    |     |      |   |   |   |   |   |   |   |   |   |  |

| Name         | Functions              |

|--------------|------------------------|

| IF_CUR [1:0] | IF Charge Pump Current |

|              | 00 = 100 μA            |

|              | 01 = 200 μA            |

|              | 10 = 300 μA            |

|              | 11 = 800 μA            |

#### **R3 REGISTER**

The R3 register address bits (R3 [2:0]) are "011".

Register R3 contains the controls for the phase lock bandwidth controls (BW\_DUR, BW\_CRL and BW\_EN). The duration of the digital controller portion of the bandwidth control is set by BW\_DUR [1:0]. The minimum time set with 00 and increasing durations to the maximum value set with 11. BW\_CRL [1:0] sets the phase offset criterion for the bandwidth controller. Once the phase offset between the reference clock and the divided VCO signal are within the set criterion, the bandwidth control stops. The maximum phase offset is set with 00 and decreases to the minimum value set with 11. BW\_EN enables the bandwidth control in the locking state.

The VCO dynamic current is also controlled in register R3 with VCO\_CUR [1:0]. The minimum value corresponds to 00 and increases to a maximum value set at 11.

#### **R3 REGISTER**

|           | MSB   |    |      |    |     |    |    | SHI | FT R | EGIS  | STER | BIT | LOC | CATIC | N |   |   |   |   |      |           |   |     | LSB  |

|-----------|-------|----|------|----|-----|----|----|-----|------|-------|------|-----|-----|-------|---|---|---|---|---|------|-----------|---|-----|------|

| ter       | 23    | 22 | 21   | 20 | 19  | 18 | 17 | 16  | 15   | 14    | 13   | 12  | 11  | 10    | 9 | 8 | 7 | 6 | 5 | 4    | 3         | 2 | 1   | 0    |

| Register  |       |    |      |    |     |    |    |     | Dat  | a Fie | ld   |     |     | -     |   |   |   |   |   |      |           | A | ۱dd | ress |

| Re        |       |    |      |    |     |    |    |     |      |       |      |     |     |       |   |   |   |   |   |      |           |   | Fie | eld  |

| R3        | BW_   |    | BW   | _  | BW_ | 1  | 0  | 1   | 1    | 1     | 1    | 0   | 1   | 0     | 0 | 0 | 1 | 1 | 0 | VC   | <b>D_</b> | 0 | 1   | 1    |

| (Default) | DUR   |    | CRI  | L  | EN  |    |    |     |      |       |      |     |     |       |   |   |   |   |   | CUI  | R         |   |     |      |

|           | [1:0] |    | [1:0 | ]  |     |    |    |     |      |       |      |     |     |       |   |   |   |   |   | [1:0 | ]         |   |     |      |

| Name          | Functions                               |

|---------------|-----------------------------------------|

| BW_DUR [1:0]  | Bandwidth Duration                      |

|               | 00 = Minimum value (Recommended)        |

|               | 01 =                                    |

|               | 10 =                                    |

|               | 11 = Maximum value                      |

| BW_CRL [1:0]  | Bandwidth Control                       |

|               | 00 = Maximum phase offset (Recommended) |

|               | 01 =                                    |

|               | 10 =                                    |

|               | 11 = Minimum phase offset               |

| BW_EN         | Bandwidth Enable                        |

|               | 0 = Disable                             |

|               | 1 = Enable (Recommended)                |

| VCO_CUR [1:0] | VCO Dynamic Current                     |

|               | 00 = Minimum value                      |

|               | 01 =                                    |

|               | 10 =                                    |

|               | 11 = Maximum value (Recommended)        |

#### **R4 REGISTER**

The R4 register address bits (R3 [3:0]) are "0111".

Register R4 is used to set the IF N counters if the default value is not desired. This register is only active if the SPI\_DEF bit in register R0 is 0.

The IF N counter consists of the 9-bit programmable counter (IF\_B counter) and the 4-bit swallow counter (IF\_A counter). The equations for calculating the counter values are presented below.

#### **R4 REGISTER**

|          | MSB |            |    |    |    |    |    | SI | HIFT      | REGI | STEF | RBIT  | LOC | ATIO | N |      |   |   |   |   |   |   |   | LSB |

|----------|-----|------------|----|----|----|----|----|----|-----------|------|------|-------|-----|------|---|------|---|---|---|---|---|---|---|-----|

| ter      | 23  | 22         | 21 | 20 | 19 | 18 | 17 | 16 | 15        | 14   | 13   | 12    | 11  | 10   | 9 | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| Register |     | Data Field |    |    |    |    |    |    |           |      |      |       |     |      |   | dre: |   |   |   |   |   |   |   |     |

| R4       | 0   | 0          | 0  | 1  | 0  | 0  | 0  |    | IF_A IF_B |      |      |       |     |      |   |      |   | 0 | 1 | 1 | 1 |   |   |     |

|          |     |            |    |    |    |    |    |    | [3:       | :0]  |      | [8:0] |     |      |   |      |   |   |   |   |   |   |   |     |

| Name       | Functions                  |

|------------|----------------------------|

| IF_A [3:0] | IF A Counter               |

|            | 4-bit swallow counter      |

|            | $0 \le IF\_A \le 15$       |

| IF_B [8:0] | IF B Counter               |

|            | 9-bit programmable counter |

|            | 1 ≤ IF_B ≤ 511             |

IF Frequency Setting:

$\rm f_{VCO}$  = {16 x IF\_B + IF\_A} x f\_{OSC} / R where (IF\_A < IF\_B)

where

$f_{VCO}$ : Output frequency of IF voltage controlled oscillator (IF VCO)

IF\_B: Preset divide ratio of binary 9-bit programmable counter (1  $\leq$  IF\_B  $\leq$  511)

IF\_A: Preset divide ratio of binary 4-bit swallow counter (0  $\leq$  IF\_A  $\leq$  15)

IF\_R: Preset divide ratio of binary 9-bit programmable reference counter (2 ≤ IF\_R ≤ 511)

f<sub>OSC</sub>: Reference oscillator frequency

#### **R5 REGISTER**

The R5 register address bits (R5 [4:0]) are "01111".

Register R5 is used to set the IF\_R divider if the default value is not desired. This register is only active if the SPI\_DEF bit in register R0 is 0.

#### **R5 REGISTER**

|          | MSB |            |    |    |    |    |    | SI | HIFT | REGI | STEF  | RBIT | LOC | ATIO | N |   |   |   |   |   |   |   |   | LSB |

|----------|-----|------------|----|----|----|----|----|----|------|------|-------|------|-----|------|---|---|---|---|---|---|---|---|---|-----|

| ter      | 23  | 22         | 21 | 20 | 19 | 18 | 17 | 16 | 15   | 14   | 13    | 12   | 11  | 10   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| Register |     | Data Field |    |    |    |    |    |    |      |      |       |      |     |      |   |   |   |   |   |   |   |   |   |     |

| R5       | 0   | 0          | 1  | 1  | 0  | 0  | 0  | 0  | 1    | 0    |       | IF_R |     |      |   |   |   |   |   |   | 1 | 1 | 1 | 1   |

|          |     |            |    |    |    |    |    |    |      |      | [8:0] |      |     |      |   |   |   |   |   |   |   |   |   |     |

| Name       | Functions                  |

|------------|----------------------------|

| IF_R [8:0] | IF R Counter               |

|            | 9-bit programmable counter |

|            | 2 ≤ IF_R ≤ 511             |

#### **R6 REGISTER**

The R6 register address bits (R6 [5:0]) are "011111".

Register R6 is used for internal testing of the device and is not intended for customer use. This register is only active if the  $SPI_DEF$  bit in register R0 is 0.

#### **R6 REGISTER**

| ister | MSB SHIFT REGISTER BIT LOCATION                             |  |  |  |  |  |  |  |  |  |  |  |  |  |               | LSB   |   |  |  |  |  |  |  |  |

|-------|-------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|---------------|-------|---|--|--|--|--|--|--|--|

| 0     | 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |  |  |  |  |  |  |  |  |  |  |  |  |  | 0             |       |   |  |  |  |  |  |  |  |

| Re    | Data Field Address Fiel                                     |  |  |  |  |  |  |  |  |  |  |  |  |  |               | Field | d |  |  |  |  |  |  |  |

| R6    | <u> </u>                                                    |  |  |  |  |  |  |  |  |  |  |  |  |  | $\overline{}$ |       |   |  |  |  |  |  |  |  |

### Physical Dimensions inches (millimeters) unless otherwise noted

28-Pin Leadless Leadframe Package (LLP)

NS Package Number LQA28A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

Americas Customer

Support Center

Email: new feedback@psc.c

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560