#### 1 FEATURES

#### MERUS™ multilevel switching technology

- 5-level voltage modulation for ultra-low idle power consumption: 52 mW @ 18 PVDD (LPC mode) without the need of complex dynamic rail-tracking systems

- Inductor-less application for reduced system cost without output power limitations

- Reduced EMI emissions compared to traditional 2 and 3 level class D audio amplifiers for fast time to market without compromises in audio performance or efficiency

- High efficiency at low output power: 79 %, 2×1 W, 8  $\Omega$  for extended battery life and easy thermal management in multichannel products even in idle state

#### Flexible configuration and application

- BTL rated output: 2×37 W, 18 V, 4 Ω, 10% THD

PBTL rated output: 1×74 W, 18 V, 2 Ω, 10% THD

- PVDD voltage range: 10 V to 20 V

- High efficiency at low output power: 79 %, 2×1 W, 8  $\Omega$

- Selectable power mode profiles: Low Power Consumption (LPC) or High Audio Performance (HAP)

- Short circuit protection: 6 A peak (BTL) / 12 A peak (PBTL)

- External closed-loop feedback for improved THD

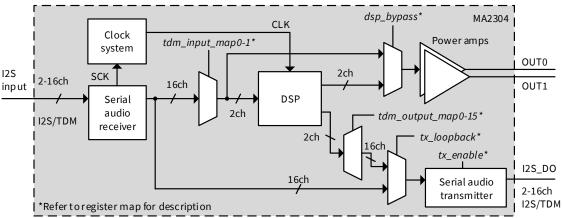

- Integrated DSP with configurable biquads, limiters, volume control and more

- Easy configuration over I2C-bus with up to 64 device addresses

- 8-bit auxiliary ADC for internal temp. / PVDD monitoring or sampling from external sources

- Configurable switching edge steepness and inter-chip PWM sync for multi-device systems.

- · No external heatsink required

#### **Audio performance**

- Output noise: 52 μVrms (A-weighted, HAP mode)

- Dynamic range: 106 dB (A-weighted, HAP mode)

- THD+N: 0.05%, 5 W, 1 kHz

#### Audio I/O

- 3-wire digital audio interface (no MCLK required)

- 32, 44.1, 48, 88.2, 96, 176.4, 192 kHz sample rates

- I2S and TDM formats supported

- · Low input-to-output latency for echo cancellation

- Post-DSP I2S output for chaining / echo cancellation

#### 2 TARGET APPLICATIONS

- Battery powered speakers

- Bluetooth/wireless/smart speakers and soundbars

- Conference speakers

- Multichannel/multi-room audio systems

#### 3 DESCRIPTION

The MA2304DNS is a 2×37 W audio amplifier with integrated audio DSP and I2S/TDM audio interface. It features the MERUS™ multilevel switching amplifier technology enabling unmatched power efficiency at both low and high output power. Multilevel switching also relaxes EMI and enables inductor-less applications with lower cost and no compromise in audio performance or efficiency. A high order internal feedback loop ensures low THD for excellent audio performance. The integrated DSP offers a configurable processing flow and can be used to correct and tune real speaker applications with e.g. equalization, limiting and more. The ultra-low idle power consumption is at least five times lower than the traditional class D audio amplifiers in the market, making MA2304DNS ideal for battery powered speaker applications with extended battery life and/or reduced battery cell cost. In mains-powered multichannel applications, the reduced and scalable EMI performance, enables otherwise impossible industrial designs, without the necessity for a heatsink or a traditional LC filter.

#### **4 PRODUCT VALIDATION**

Qualification standard: Standard

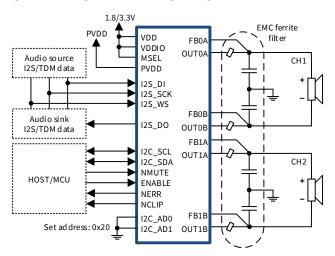

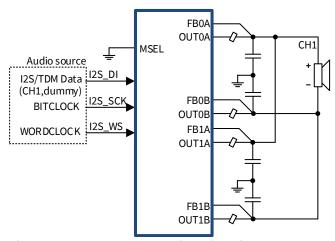

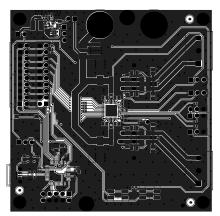

#### 5 TYPICAL APPLICATION

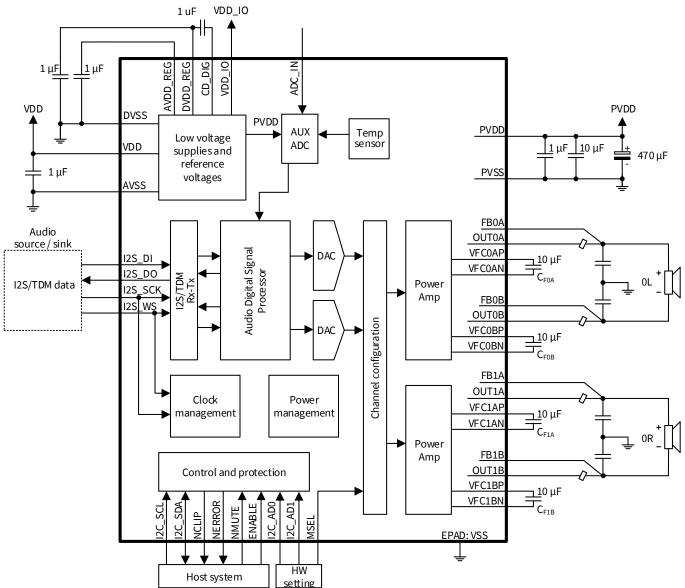

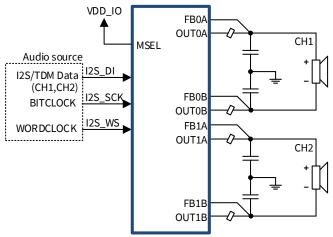

### 6 Functional Application Block Diagram

Figure 6.1: Functional Application Block Diagram

### MERUS™ Multilevel Switching Class-D Audio Amplifier

### **Contents**

| 1  | FEATURES TO THE PROPERTY OF TH | 1                                                  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2  | TARGET APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                  |

| 3  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                  |

| 4  | PRODUCT VALIDATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                  |

| 5  | TYPICAL APPLICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                  |

| 6  | Functional Application Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                  |

| 7  | Device Comparison Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                  |

| 8  | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                  |

| 9  | Pin List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                  |

| 10 | Specifications       10.1 Absolute Maximum Ratings        10.2 ESD and Thermal Characteristics        10.3 Recommended Operating Conditions        10.4 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7<br>7                                             |

| 11 | Functional description  11.1 MERUS™ Multilevel Switching  11.1.1 Multilevel Topology  11.1.2 Reduced Inductor Ripple Current  11.1.3 Ultra Low Power Consumption with Music  11.1.4 EMI Reduction  11.1.5 Power Mode Profiles (PMP)  11.2 Modes of Operation  11.2.1 Normal Operation / Shutdown (ENABLE pin)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11<br>12<br>12<br>12<br>13                         |

|    | 11.2.2 Mute / Unmute (NMUTE pin) 11.2.3 Standby  11.3 BTL/PBTL Output Configurations  11.4 Gain Configuration  11.5 Protection  11.5.1 Errors and Error Handling (NERR pin)  11.5.2 Output DC Protection (DCP)  11.5.3 Over-Current Protection (OCP)  11.5.4 PVDD Over/Under-Voltage Protection  11.5.5 Over Temperature Protection (OTP)  11.5.6 PLL Error and I2S Input Error  11.5.7 Flying Capacitor Over/Under-Voltage Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 13<br>13<br>13<br>14<br>14<br>14<br>15<br>15<br>15 |

|    | 11.5.8 NCLIP Pin  11.6 Power Supplies  11.6.1 Supplies for Internal Analog/Digital Circuitry (VDD/VDD_IO)  11.6.2 Flying Capacitors  11.6.3 Power Stage Supply (PVDD)  11.7 Clock System  11.8 Audio Interface  11.8.1 Digital Serial Audio Input  11.8.2 Digital Serial Audio Output  11.8.3 Input-to-Output Audio Propagation Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16<br>16<br>16<br>17<br>17<br>17                   |

|    | 11.9 Digital Signal Processor (DSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                 |

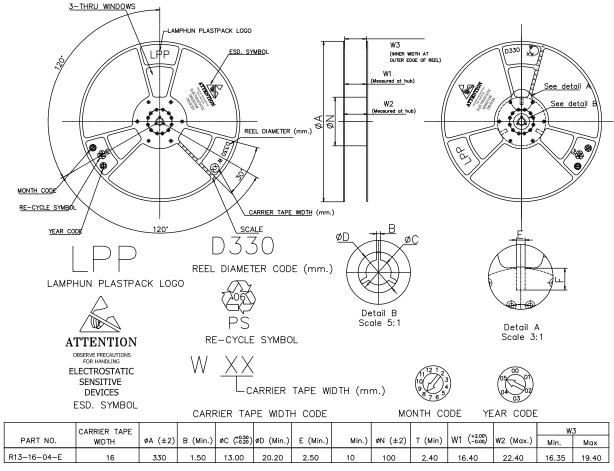

|    | Tane and Reel Information                                     | 42              |

|----|---------------------------------------------------------------|-----------------|

| 15 | Package Information                                           | 40              |

| 14 | Register map                                                  | 34              |

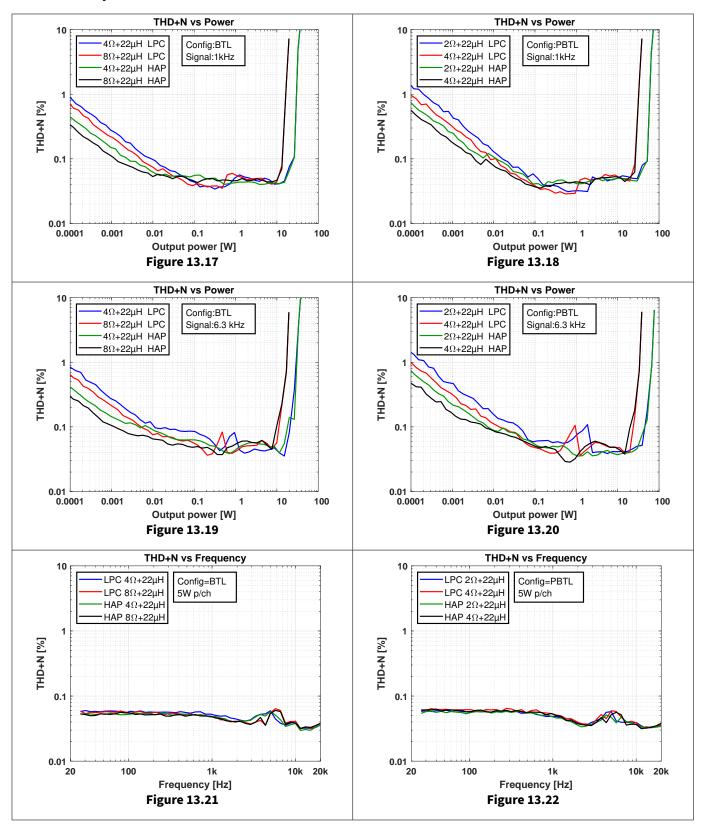

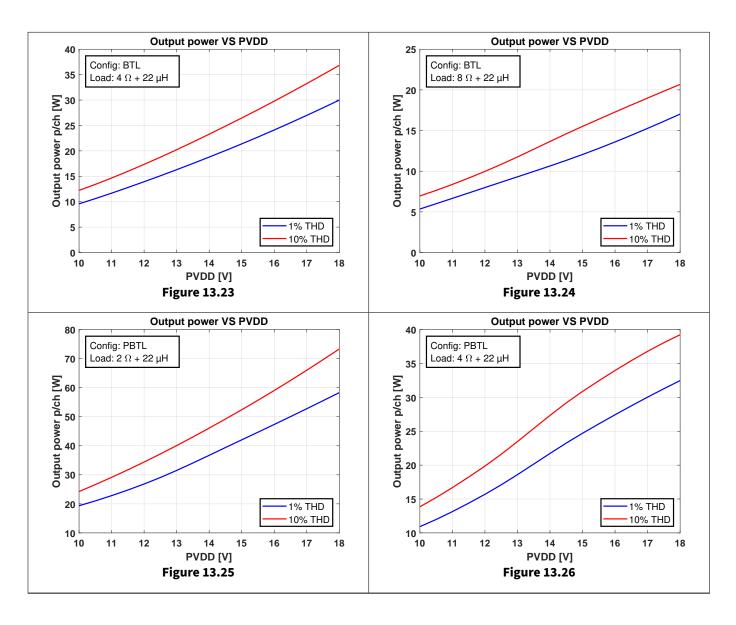

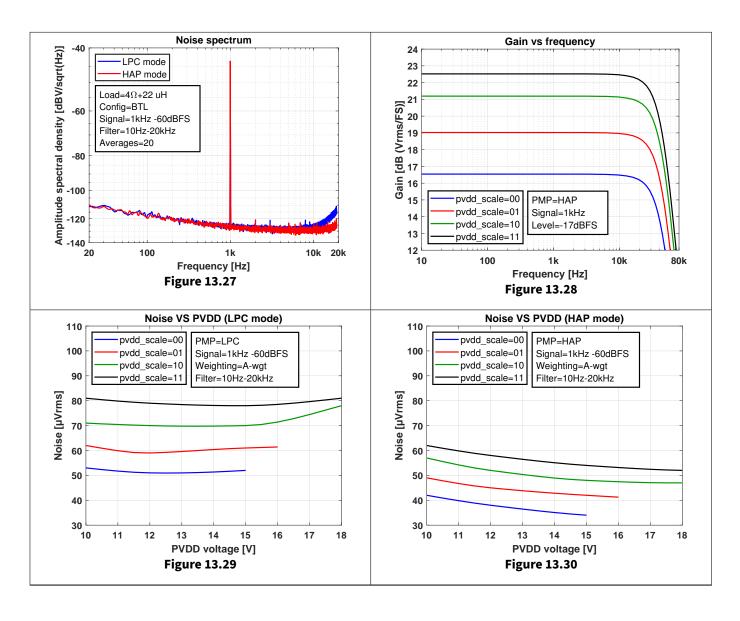

|    | 13.3 Audio performance                                        | 31              |

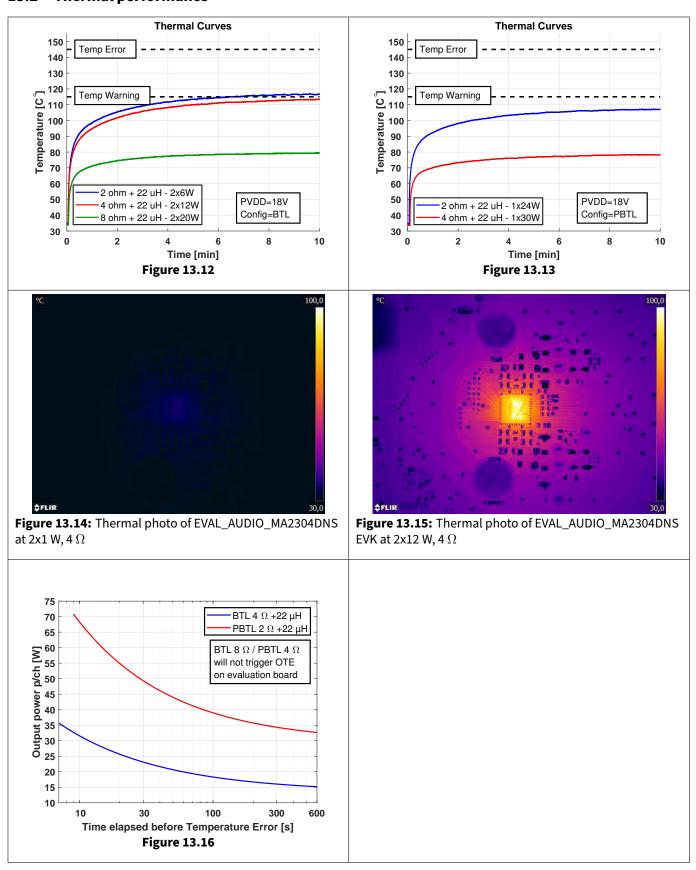

|    | 13.2 Thermal performance                                      | 30              |

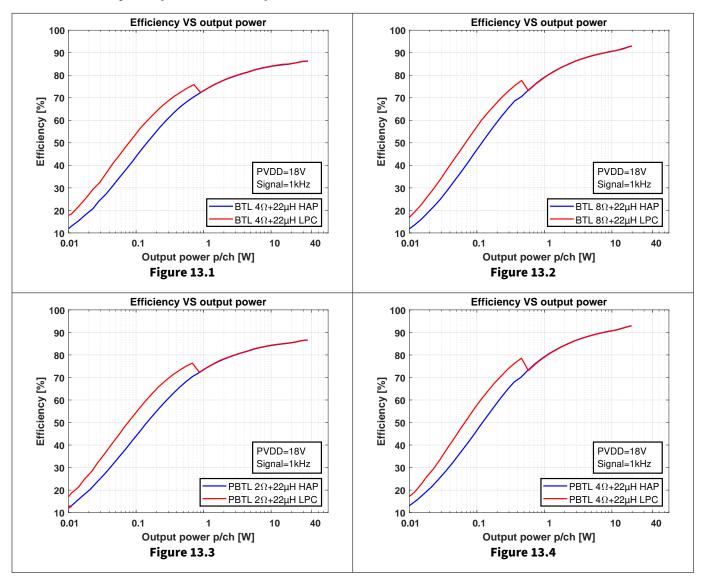

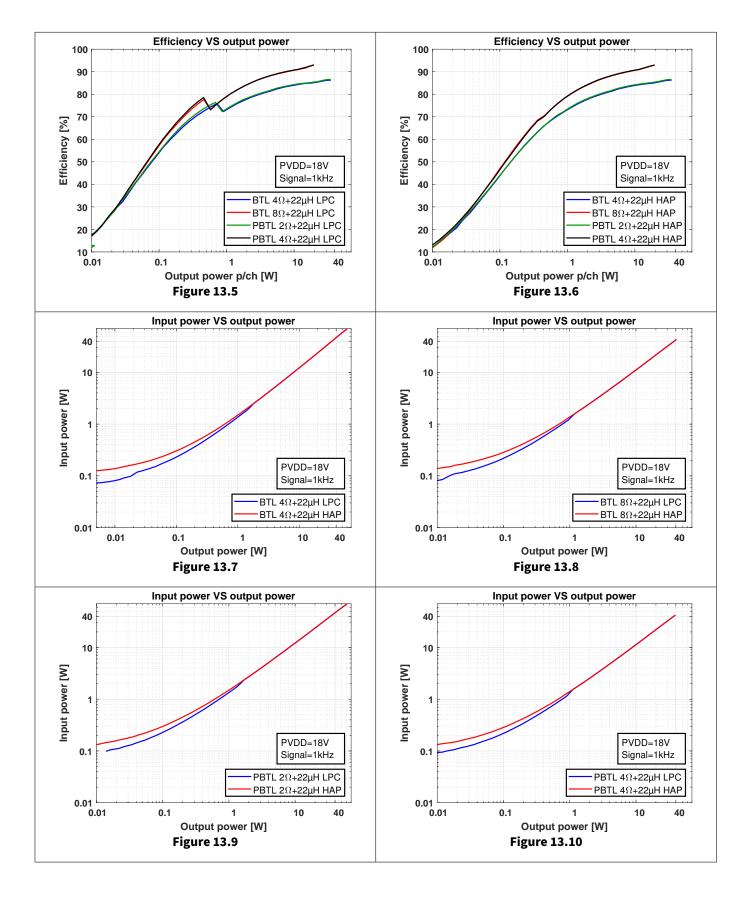

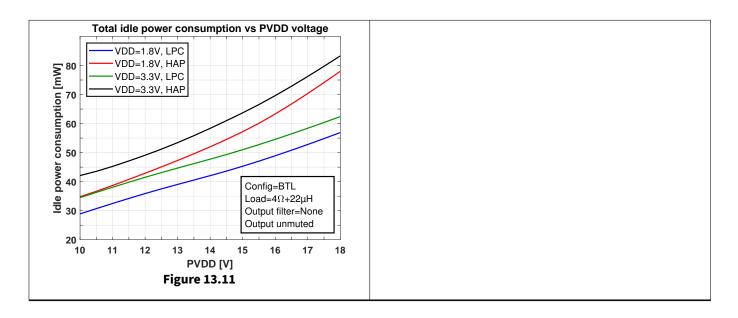

| 13 | Typical Characteristics 13.1 Efficiency and power consumption | <b>27</b><br>27 |

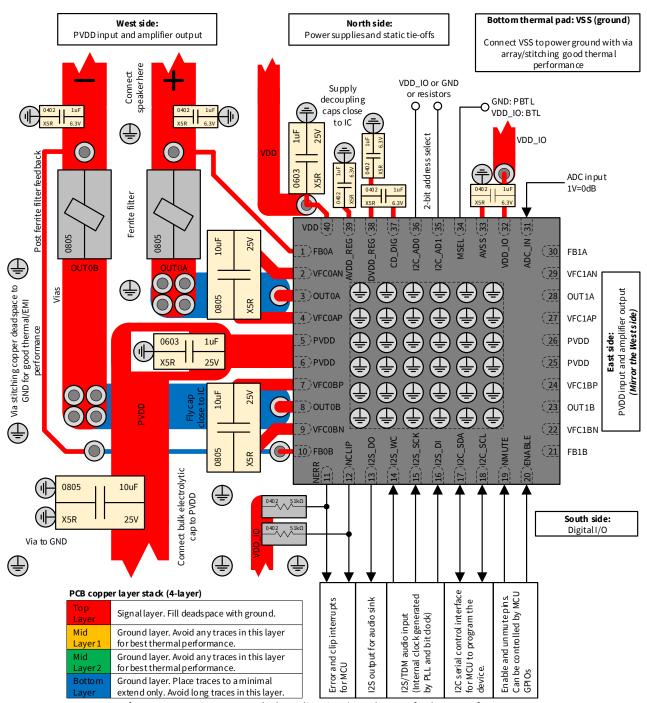

|    | 12.7 Evaluation Board as Reference                            | 25              |

|    | 12.6 Recommended Layout                                       |                 |

|    | 12.5 Power-down Procedure                                     | 24              |

|    | 12.4 Procedure for handling discontinuous audio clock         |                 |

|    | 12.3 Start-up Procedure                                       |                 |

|    | 12.2 Thermal Design                                           |                 |

|    | 12.1.3 Ferrite Filter Stability Under Light Loads             |                 |

|    | 12.1.2 Ferrite Filter Selection                               |                 |

|    | 12.1.1 Capacitor Value Impact on Power Consumption            |                 |

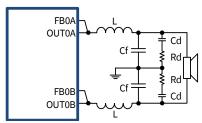

|    | 12.1 EMC Ferrite Output Filter                                |                 |

| 12 | Application Information                                       | 22              |

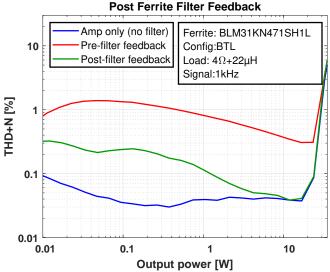

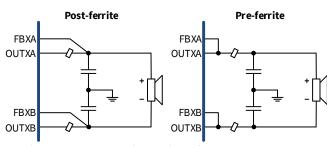

|    | 11.13 Post-Ferrite Filter Feedback                            | 21              |

|    | 11.12.2 PWM Synchronization for EMI Reduction                 |                 |

|    | 11.12.1 Configurable Switching Edge                           | 20              |

|    | 11.12 EMI Mitigation                                          |                 |

|    | 11.11.3 I2C Read Operation                                    |                 |

|    | 11.11.1 Device Address                                        |                 |

|    | 11.1112C Serial Control Interface                             |                 |

|    | 11.10 Auxiliary ADC                                           |                 |

|    | 11.9.3 Peak Limiter (ROM Code)                                |                 |

|    | 11.9.2 Volume Control                                         | 18              |

#### MERUS™ Multilevel Switching Class-D Audio Amplifier

### 7 Device Comparison Table

Table 1: Device comparison

| Device name | Functional variance                            |

|-------------|------------------------------------------------|

| MA2304DNS   | Fully configurable DSP, 10-20 V                |

| MA2304PNS   | Audio limiter and volume control only, 10-20 V |

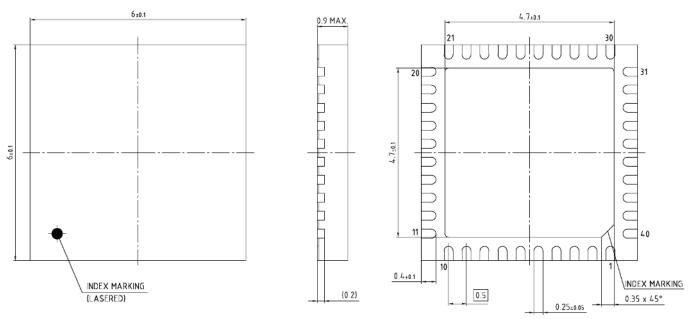

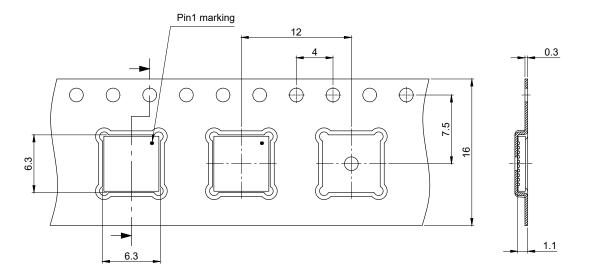

### 8 Pin Configuration

Figure 8.1: Package Overview - 6x6 mm QFN-40 pins

#### 9 Pin List

Table 2: Pin List MA2304DNS

| Pin Nr. | Name   | Type | Description                                   |

|---------|--------|------|-----------------------------------------------|

| 1       | FB0A   | I    | Output channel 0A post-ferrite feedback       |

| 2       | VFC0AN | Р    | Negative side flying capacitor for channel 0A |

| 3       | OUT0A  | 0    | Audio output channel 0A                       |

| 4       | VFC0AP | Р    | Positive side flying capacitor for channel 0A |

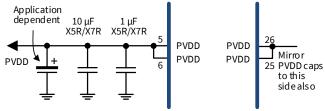

| 5       | PVDD   | Р    | Power supply for power stage                  |

| 6       | PVDD   | Р    | Power supply for power stage                  |

| 7       | VFC0BP | Р    | Positive side flying capacitor for channel 0B |

| 8       | OUT0B  | 0    | Audio output channel 0B                       |

| 9    | VFC0BN   | Р   | Negative side flying capacitor for channel 0B                                                          |

|------|----------|-----|--------------------------------------------------------------------------------------------------------|

| 10   | FB0B     | ı   | Output channel 0B post-ferrite feedback                                                                |

|      |          |     | Error indicator – open drain output. Use this pin as interrupt for host                                |

| 11   | NERR     | 0   | microcontroller to read error register.                                                                |

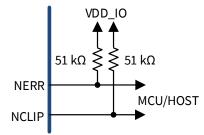

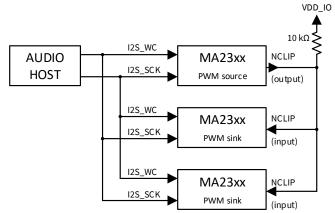

| 12   | NCLIP    | I/O | Clipping indicator output (default) or PWM synchronization I/O                                         |

| 13   | I2S_DO   | 0   | I2S/TDM digital audio data output                                                                      |

| 14   | I2S_WC   | I   | I2S/TDM digital audio word clock                                                                       |

| 15   | I2S_SCK  | I   | I2S/TDM digital audio bit clock                                                                        |

| 16   | I2S_DI   | I   | I2S/TDM digital audio data input                                                                       |

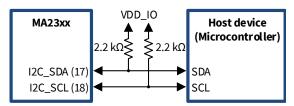

| 17   | I2C_SDA  | I/O | I2C bus serial clock                                                                                   |

| 18   | I2C_SCL  | I/O | I2C bus serial data                                                                                    |

| 19   | NMUTE    | I   | Mutes audio output when pulled low                                                                     |

| 20   | ENABLE   | I   | Enables device when pulled high. Pulling this pin low shuts down the device.                           |

| 21   | FB1B     | I   | Output channel 1B post-ferrite feedback                                                                |

| 22   | VFC1BN   | Р   | Negative side flying capacitor for channel 1B                                                          |

| 23   | OUT1B    | 0   | Audio output channel 1B                                                                                |

| 24   | VFC1BP   | Р   | Positive side flying capacitor for channel 1B                                                          |

| 25   | PVDD     | Р   | Power supply for power stage                                                                           |

| 26   | PVDD     | Р   | Power supply for power stage                                                                           |

| 27   | VFC1AP   | Р   | Positive side flying capacitor for channel 1A                                                          |

| 28   | OUT1A    | 0   | Audio output channel 1A                                                                                |

| 29   | VFC1AN   | Р   | Negative side flying capacitor for channel 1A                                                          |

| 30   | FB1A     | I   | Output channel 1a post-ferrite feedback                                                                |

| 31   | ADC_IN   | I   | Auxiliary ADC input                                                                                    |

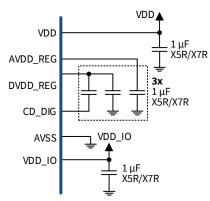

| 32   | VDD_IO   | Р   | Digital I/O supply. Used for external resistor pull-ups, e.g. for I2C bus.                             |

| 33   | AVSS     | Р   | Ground for internal analog circuitry                                                                   |

| 34   | MSEL     | I   | Hardware select for BTL (pull high) or PBTL (pull low)                                                 |

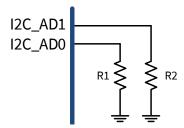

| 35   | I2C_AD1  | I   | I2C bus address pin 1. Use I2C_AD1 and I2C_AD0 to set I2C address: 00:0x20, 01:0x21, 10:0x22, 11:0x23. |

| 36   | I2C_AD0  | ı   | 12C bus address pin 0                                                                                  |

| 36   | IZC_ADU  | ı   | Internal digital core supply charge-pump. Connect 1 µF between this pin and                            |

| 37   | CD_DIG   | Р   | DVDD_REG.                                                                                              |

| 38   | DVDD_REG | Р   | Internal regulated supply decoupling. Connect 1 µF between this pin and ground.                        |

| 39   | AVDD_REG | Р   | Internal regulated supply decoupling. Connect 1 µF between this pin and ground.                        |

| 40   | VDD      | Р   | External low voltage supply.                                                                           |

| EPAD | VSS      | Р   | Ground for internal digital circuitry and PVDD                                                         |

#### MERUS™ Multilevel Switching Class-D Audio Amplifier

### 10 Specifications

#### 10.1 Absolute Maximum Ratings

NOTE: Usage outside the specifications stated in this table may cause permanent damage to the device and/or compromise reliability.

Table 3: Absolute Maximum Ratings

| Parameter          | Description                                                         | Min   | Max    | Unit |

|--------------------|---------------------------------------------------------------------|-------|--------|------|

| VDD                | Low voltage supply                                                  | -0.3  | 5.5    | V    |

| PVDD               | Power amp supply                                                    | -0.3  | 22     | V    |

| VDD_IO             | Digital I/O supply                                                  | -0.3  | 5.5    | V    |

| $V_{speak}$        | Speaker node output pins                                            | -0.3  | PVDD+2 | V    |

| V <sub>PIO</sub>   | IO and hardware setting pins (NERR, NCLIP, I2S_DO, I2S_WC, I2S_SCK, | -0.3  | VDD IO | V    |

| V PIO              | I2S_DI, I2C_SDA, I2C_SCL, NMUTE, ENABLE, MSEL, I2C_AD0, I2C_AD1)    | -0.5  | VDD_10 | V    |

| V <sub>ADC</sub>   | ADC_IN pin                                                          | -0.3  | 1.5    | V    |

| T <sub>AMB</sub>   | Ambient operating temperature                                       | -25.0 | 85     | °C   |

| TJ                 | Junction temperature                                                | -25.0 | 150    | °C   |

| T <sub>STORE</sub> | Storage temperature                                                 | -55.0 | 150    | °C   |

#### 10.2 ESD and Thermal Characteristics

**Table 4:** ESD and Thermal Characteristics

| Parameter Description |                                                                    | Min   | Тур  | Max   | Unit |

|-----------------------|--------------------------------------------------------------------|-------|------|-------|------|

| V <sub>ESD,HB</sub>   | ESD Human Body Model                                               | -3000 |      | +3000 | V    |

| V <sub>ESD,CD</sub>   | ESD Charged Device Model                                           | -1000 |      | +1000 | V    |

| T <sub>θJA</sub>      | Thermal resistance, Junction-to-Ambient, 4-layer PCB (EVAL_MA23xx) |       | 28.9 |       | °C/W |

| $T_{	hetaJC}$         | Thermal resistance, Junction-to-Case (EPAD)                        |       | 1.9  |       | °C/W |

#### 10.3 Recommended Operating Conditions

NOTE: Usage outside the recommended operating conditions stated in this table may cause the device to not behave properly. This can lead to interrupted audio playback, protection features being triggered etc. This applies to DC+AC values outside the min/max values.

Table 5: Recommended Operating Conditions

| Parameter Description |                                                                                         | Min  | Тур | Max  | Unit |

|-----------------------|-----------------------------------------------------------------------------------------|------|-----|------|------|

| VDD                   | Low voltage supply (DC+AC ripple)                                                       | 1.62 | 1.8 | 3.65 | V    |

| PVDD                  | Power amp supply (DC+AC ripple)                                                         | 10.0 | 18  | 20   | V    |

| VDD_IO                | Digital I/O supply (DC+AC ripple)                                                       | 1.62 | 1.8 | 3.65 | V    |

| ILEQ                  | Minimum required equivalent load inductance per output pin for short circuit protection | 0.5  |     |      | μН   |

Refer to sections 11.5 and 11.5.4 for more details on supply voltages and their protection mechanisms.

### MERUS™ Multilevel Switching Class-D Audio Amplifier

#### 10.4 Electrical Characteristics

Conditions (unless specified otherwise): PVDD=18 V, VDD/VDD\_IO=3.3 V, Power Mode Profile: LPC,  $T_{AMB}$ =25 °C, Load: 4 ohm + 22  $\mu$ H, PCB: EVAL\_AUDIO\_MA23xx (no output filter)

**Table 6:** Electrical characteristics.

| Parameter                | Description                                                              | Test Conditions                                                                         | Min | Тур | Max | Unit |

|--------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|------|

| BTL Output               | Power                                                                    |                                                                                         |     |     |     |      |

| P <sub>COUT,BTL</sub>    | Continuous Output Power p/ch <sup>1</sup>                                | Load=4Ω+22μH, sig=pink noise,<br>CF=9dB; Thermal Warning<br>triggered                   |     | 12  |     | W    |

|                          |                                                                          | Load=4Ω+22μH, sig=pink noise,<br>CF=9dB, Thermal Error triggered<br>(device shuts down) |     | 14  |     | W    |

|                          |                                                                          | Load=8Ω+22μH, sig=1 kHz sine,<br>THD+N=1%                                               |     | 17  |     | w    |

|                          |                                                                          | Load=8Ω+22μH, sig=1 kHz sine,<br>THD+N=10%                                              |     | 20  |     | W    |

| P <sub>RMSOUT,BTL</sub>  | RMS Output Power p/ch <sup>1</sup>                                       | Load=4Ω+22μH, sig=1 kHz sine,<br>THD+N=1%                                               |     | 30  |     | W    |

|                          |                                                                          | Load=4Ω+22μH, sig=1 kHz sine,<br>THD+N=10%                                              |     | 37  |     | W    |

| P <sub>IPOUT,BTL</sub>   | Instantaneous Peak Output<br>Power p/ch <sup>1</sup>                     | Load=4Ω+22μH, sig=1 kHz sine,<br>THD+N=1%                                               |     | 60  |     | W    |

| I <sub>OUT,BTL</sub>     | Maximum Output Current p/ch1                                             |                                                                                         | 6   |     |     | Α    |

| $T_{CASE,BTL}$           | Case temperature on board at 'Continuous Output Power p/ch' <sup>2</sup> | PCB=EVAL_AUDIO_MA23xx, Load= $4\Omega$ +22 $\mu$ H                                      |     | 113 |     | °C   |

| PBTL Output              | t Power                                                                  |                                                                                         |     |     |     | •    |

| P <sub>COUT,PBTL</sub>   | Continuous Output Power p/ch <sup>1</sup>                                | Load=4Ω+22μH, sig=pink noise,<br>CF=9dB, Thermal Warning<br>triggered                   |     | 24  |     | w    |

|                          |                                                                          | Load=4Ω+22μH, sig=pink noise,<br>CF=9dB, Thermal Error triggered<br>(device shuts down) |     | 28  |     | W    |

| P <sub>RMSOUT,PBTL</sub> | RMS Output Power p/ch <sup>1</sup>                                       | Load=2Ω+22μH, sig=1kHz sine,<br>THD+N=1%                                                |     | 60  |     | W    |

|                          |                                                                          | Load=2Ω+22μH, sig=1kHz sine,<br>THD+N=10%                                               |     | 74  |     | W    |

| P <sub>IPOUT,PBTL</sub>  | Instantaneous Peak Output<br>Power p/ch <sup>1</sup>                     | Load=2Ω+22μH, sig=1kHz sine,<br>THD+N=1%                                                |     | 120 |     | W    |

| I <sub>OUT,PBTL</sub>    | Maximum Output Current p/ch1                                             |                                                                                         | 12  |     |     | Α    |

| $T_{CASE,PBTL}$          | Case temperature on board at 'Continuous Output Power p/ch' <sup>2</sup> | PCB=EVAL_AUDIO_MA23xx,<br>Load=2Ω+22μH                                                  |     | 78  |     | °C   |

| Power stage              |                                                                          |                                                                                         |     |     |     |      |

| $\eta_{\text{BTL}}$      | Efficiency (BTL) <sup>2</sup>                                            | POUT=2x100mW,<br>Load=8Ω+22μH                                                           |     | 57  |     | %    |

|                          |                                                                          | POUT=2x1W, Load=8Ω+22μH                                                                 |     | 79  |     | %    |

|                          |                                                                          | POUT=full scale, Load=8Ω+22μH                                                           |     | 90  |     | %    |

|                          |                                                                          | POUT=2x100mW,<br>Load=4Ω+22μH                                                           |     | 54  |     | %    |

|                          |                                                                          | POUT=2x1W, Load=4Ω+22μH                                                                 |     | 73  |     | %    |

|                          |                                                                          | POUT=full scale, Load=4Ω+22μH                                                           |     | 84  |     | %    |

| R <sub>ON,BTL</sub>      | Total on-resistance of the internal power stage (BTL) <sup>1</sup>       | BTL on-resistance: 4x MOSFETS in series + bond wires                                    |     | 400 |     | mΩ   |

| R <sub>ON,PBTL</sub>     | Total on-resistance of the internal power stage (PBTL) <sup>1</sup>      | PBTL on-resistance: 2x BTL power stages in parallel                                     |     | 200 |     | mΩ   |

| f <sub>SW,FET</sub>      | Internal MOSFET switching <sup>1</sup>                                   | LPC mode, low signal level                                                              |     | 128 |     | kHz  |

|                          | frequency                                                                | LPC mode, high signal level                                                             |     | 256 |     | kHz  |

|                           |                                                                                      | HAP mode                                              |     | 256   |    | kHz   |

|---------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------|-----|-------|----|-------|

| $f_{SW,LOAD}$             | Switching frequency seen <sup>1</sup>                                                | LPC mode, low signal level                            |     | 512   |    | kHz   |

|                           | differentially by the load                                                           | LPC mode, high signal level                           |     | 1024  |    | kHz   |

|                           |                                                                                      | HAP mode                                              |     | 1024  |    | kHz   |

| Power Consu               |                                                                                      |                                                       |     |       |    |       |

| P <sub>IDLE</sub>         | Total idle power consumption for VDD+PVDD+VDD_IO <sup>1</sup>                        | PVDD=18V, LPC mode                                    |     | 52    |    | mW    |

|                           | (device enabled and unmuted)                                                         | PVDD=18V, HAP mode                                    |     | 70    |    | mW    |

| I <sub>PVDD,IDLE</sub>    | Quiescent/idle current, PVDD <sup>1</sup>                                            | PVDD=18V, LPC mode                                    |     | 2.2   |    | mA    |

|                           | (device enabled and unmuted)                                                         | PVDD=18V, HAP mode                                    |     | 3.2   |    | mA    |

| I <sub>VDD,IDLE</sub>     | Quiescent/idle current, VDD <sup>1</sup>                                             | VDD=3.3 V, LPC mode                                   |     | 3.5   |    | mA    |

|                           | (device enabled and unmuted)                                                         | VDD=1.8 V, LPCmode                                    |     | 3.5   |    | mA    |

|                           |                                                                                      | VDD=3.3 V, HAP mode                                   |     | 3.6   |    | mA    |

|                           |                                                                                      | VDD=1.8 V, HAP mode                                   |     | 3.6   |    | mA    |

| I <sub>VDD_IO,IDLE</sub>  | Quiescent/idle current, VDD_IO <sup>1</sup>                                          | VDD_IO = 3.3 V, No load on I2S_DO                     |     | 2.3   |    | μΑ    |

|                           |                                                                                      | VDD_IO = 1.8 V, No load on I2S_DO                     |     | 2.3   |    | μА    |

| P <sub>IDLE,STANDBY</sub> | Total power consumption in standby mode for VDD+PVDD+VDD_IO <sup>1</sup>             | PVDD=18V, VDD=1.8V                                    |     | 2.8   |    | mW    |

|                           |                                                                                      | PVDD=18V, VDD=3.3V                                    |     | 4.7   |    | mW    |

| $\Delta P_{DSP}$          | Power consumption difference<br>between ROM code and max DSP<br>program <sup>1</sup> | VDD=3.3 V                                             |     | 5.4   |    | mW    |

|                           | P. 28. m                                                                             | VDD=1.8 V                                             |     | 3     |    | mW    |

| Audio Perfor              | rmance/IO                                                                            | 1.5                                                   |     |       |    |       |

|                           |                                                                                      | 20-20kHz integrated noise,                            |     | 00    |    | T .,  |

| $V_{NOISE}$               | Output integrated noise level                                                        | A-weighted, LPC mode                                  |     | 82    |    | μV    |

|                           |                                                                                      | 20-20kHz integrated noise,<br>A-weighted, HAP mode    |     | 52    |    | μV    |

| DNR                       | Dynamic Range                                                                        | -60dBFS method, LPC mode                              |     | 102   |    | dB    |

|                           |                                                                                      | -60dBFS method, HAP mode                              |     | 106   |    | dB    |

| THD+N                     | Total Harmonic Distortion +<br>Noise <sup>1</sup>                                    | POUT=5W, sig=1kHz, Load=4 $\Omega$                    |     | 0.05  |    | %     |

| V <sub>OS</sub>           | Output offset voltage for low pop/click-noise                                        |                                                       | -25 | -/+ 3 | 25 | mV    |

|                           | F-F/                                                                                 |                                                       |     | 32    |    |       |

|                           |                                                                                      |                                                       |     | 44.1  |    |       |

| t                         | Supported I2S/TDM input                                                              |                                                       |     | 48    |    | latte |

| f <sub>S</sub>            | sampling rates <sup>1</sup>                                                          |                                                       |     | 88.2  |    | kHz   |

|                           |                                                                                      |                                                       |     | 96    |    |       |

|                           |                                                                                      |                                                       |     | 176.4 |    |       |

|                           | Dropagation delay from andia                                                         | Sample rate = 40 kH = DCD                             |     | 196   |    |       |

| t <sub>PD</sub>           | Propagation delay from audio input to amplifier <sup>1</sup>                         | Sample rate = 48 kHz, DSP<br>enabled running ROM code |     | 146   |    | μs    |

| I2S_SCK <sub>MAX</sub>    | Maximum supported bit clock on I2S_SCK pin <sup>1</sup>                              |                                                       |     | 25    |    | МН    |

| N <sub>CH,MAX,IN</sub>    | Maximum supported input I2S/TDM channels¹                                            |                                                       |     | 16    |    |       |

| N <sub>CH,MAX,OUT</sub>   | Maximum supported output I2S/TDM channels <sup>1</sup>                               |                                                       |     | 2     |    |       |

| G                         | Amplifier gain in dB (Vrms/FS) <sup>1</sup>                                          | pvdd_scale=11, PVDD=18 V                              |     | 22.5  |    | dB    |

|                           |                                                                                      | pvdd_scale=10, PVDD=15 V                              |     | 21.2  |    | dB    |

|                           |                                                                                      |                                                       | 1   |       |    |       |

|                           |                                                                                      | pvdd_scale=01, PVDD=12 V                              |     | 19    |    | dB    |

| т                       | Time from ENABLE=high until               |                              |     | 15   |      | ms   |

|-------------------------|-------------------------------------------|------------------------------|-----|------|------|------|

| T <sub>ENABLE</sub>     | ready for I2C communication <sup>1</sup>  |                              |     | 15   |      | 1115 |

| T <sub>UNMUTE</sub>     | Unmute time delay until audio             |                              |     | 30   |      | ms   |

|                         | output <sup>1</sup>                       |                              |     | 50   |      | 1113 |

|                         | ntrol interface                           |                              |     |      |      |      |

| $f_{SCL}$               | I2C clock frequency <sup>1</sup>          | Standard Mode                |     | 100  |      | kHz  |

|                         |                                           | Fast Mode                    |     | 400  |      | kHz  |

| $V_{IL}$                | Logic low voltage <sup>1</sup>            | Percentage of VDD_IO voltage |     | 30   |      | %    |

| V <sub>IH</sub>         | Logic high voltage <sup>1</sup>           | Percentage of VDD_IO voltage |     | 70   |      | %    |

| t <sub>r</sub>          | SDA and SCL rise time <sup>1</sup>        | Standard Mode                |     |      | 1000 | ns   |

| t <sub>f</sub>          | SDA and SCL fall time <sup>1</sup>        | Standard Mode                |     |      | 300  | ns   |

| t <sub>HIGH</sub>       | SCL clock high <sup>1</sup>               | Standard Mode                | 4   |      |      | μs   |

| t <sub>LOW</sub>        | SCL clock low <sup>1</sup>                | Standard Mode                | 4.7 |      |      | μs   |

| t <sub>SU;DAT</sub>     | Data, setup <sup>1</sup>                  | Standard Mode                | 250 |      |      | ns   |

| t <sub>HD;DAT</sub>     | Data, hold <sup>1</sup>                   | Standard Mode                | 5   |      |      | ns   |

| t <sub>BUF</sub>        | Min. stop to start condition <sup>1</sup> | Standard Mode                | 4.7 |      |      | μs   |

| R <sub>PU,FM</sub>      | Pull-up resistor for SDA/SCL <sup>1</sup> | Fast Mode                    | 1   |      | 4.7  | kΩ   |

| R <sub>PU,SM</sub>      | Pull-up resistor for SDA/SCL <sup>1</sup> | Standard Mode                | 1   |      | 5.6  | kΩ   |

| Protection              |                                           |                              |     | •    |      |      |

|                         | PVDD undervoltage lock-out                |                              |     |      |      |      |

| $UVLO_{PVDD}$           | threshold (I2C interface                  |                              |     | 6.5  |      | V    |

|                         | functional)                               |                              |     |      |      |      |

| OVP <sub>PVDD</sub>     | PVDD over-voltage error                   | PVDD rising                  |     | 21.5 |      | V    |

| OVPPVDD                 | threshold                                 | PVDD HSIIIg                  |     | 21.5 |      | V    |

| OVP <sub>PVDD,CLR</sub> | PVDD over-voltage error clear             | PVDD falling while OVP error | 20  |      |      | V    |

| OVP <sub>PVDD,CLR</sub> | PVDD over-voltage error clear             | triggered                    | 20  |      |      | V    |

| OTE <sub>TRIG</sub>     | Over-temperature error trigger            | Temperature rising           |     | 145  |      | °C   |

| OTE <sub>CLR</sub>      | Over-temperature error clear              | Temperature falling          |     | 140  |      | °C   |

| OTW <sub>TRIG</sub>     | Over-temperature warning                  | Temperature rising           |     | 115  |      | °C   |

|                         | trigger                                   | remperature rising           |     | 113  |      | _    |

| OTW <sub>CLR</sub>      | Over-temperature warning clear            | Temperature falling          |     | 110  |      | °C   |

$<sup>^1</sup>$ Guaranteed by design simulation.  $^2$ Measured on EVAL\_MA2304 evaluation kit PCB. Parameter may depend on application/layout/board stackup etc.

### 11 Functional description

#### 11.1 MERUS™ Multilevel Switching

MERUS™ multilevel switching features several benefits in class D audio amplification compared to conventional 2-level switching:

- Ultra low power consumption

- Unmatched power efficiency

- · Low electromagnetic emission

- Reduced system cost

This chapter aims to explain these benefits in more detail.

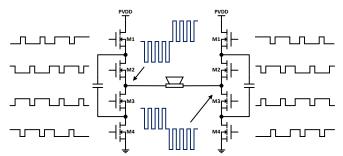

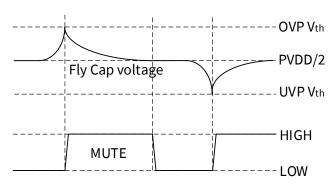

#### 11.1.1 Multilevel Topology

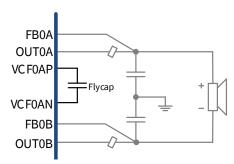

The integrated power stage of the MA2304DNS is a MERUS™ multilevel switching topology. It consists of two half-bridges with each four power MOSFETs and a flying capacitor. An intermediate voltage supply is generated over the flying capacitor's terminals, which together with the switching scheme of the MOSFETs result in a 2-phase PWM output with three voltage levels (0V, ½PVDD and PVDD) rather than the conventional two. This doubles the effective switching frequency seen at the PWM output.

**Figure 11.1:** BTL/PBTL configuration of two 3-level half bridges

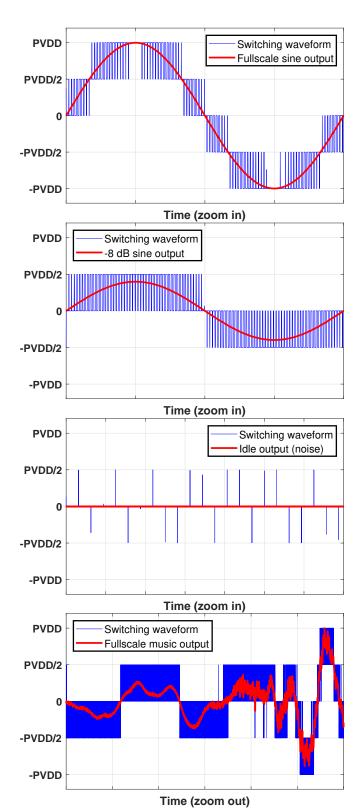

In MA2304DNS, two half-bridges are combined in a BTL/PBTL configuration (Figure 11.1) with a relative phase shift of 270° achieving a 5-level switching scheme across the load, effectively quadrupling the switching frequency seen at the load. This allows the internal MOSFETs to be driven with lower switching frequency, thus reducing power losses related to switching. Switching waveforms are shown in Figure 11.2.

#### 11.1.2 Reduced Inductor Ripple Current

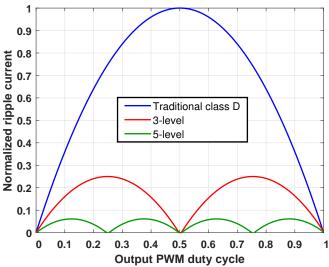

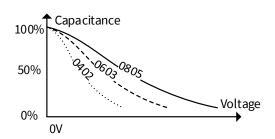

The multilevel topology reduces the voltage magnitude over the output filter inductor during switching, which in turn reduces the ripple current and relaxes filter inductor requirements. At idle operation where the output signal level is low, the MOSFETs are switched at 50 % duty cycle, resulting in near-zero ripple current. Hysteresis losses in the

**Figure 11.2:** Multilevel switching with various signals.

inductor core material are therefore also greatly reduced which improves overall power efficiency. From Figure 11.3 it is clear that 5-level switching provides greatly reduced ripple current over the entire duty cycle range compared to conventional 2-level switching. In fact, it is not even necessary to use a standard LC filter for electromagnetic inter-

#### MERUS™ Multilevel Switching Class-D Audio Amplifier

ference (EMI) suppression. The MA2304DNS can even operate with a simple ferrite filter reducing both application cost and size. See Section 11.1.4 and 12 for more information.

Figure 11.3: Ripple current comparison

#### 11.1.3 Ultra Low Power Consumption with Music

MA2304DNS exhibits ultra low power consumption at low and mid output power, which is ensured by low MOSFET switching frequency, smaller voltage transitions when switching and near zero-ripple current. The low idle power consumption can make battery-powered applications last significantly longer or reduce the amount of battery cells required for a particular application.

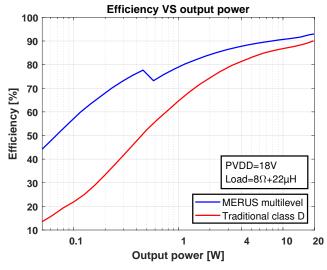

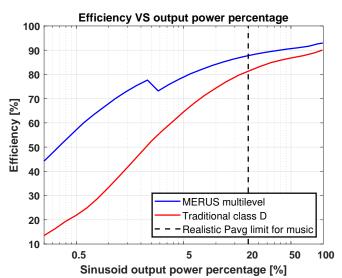

Because of the low power consumption at lower output power levels, the MA2304DNS is ideal for real applications with dynamic signals like music/noise that exhibit a high signal peak-to-RMS ratio (crest factor). Power efficiency can be as high as 80 % at 1 W output power per channel, and because of the low power losses MA2304DNS may run without external heatsink in most applications. Figure 11.4 shows the difference in power efficiency between multilevel and traditional class D. From the figure it is clear that multilevel operation yields superior results for lower playback levels, which is the normal usage in common speaker products.

#### 11.1.4 EMI Reduction

Complying with EMC regulations is a typical challenge with class D amplifiers due to the high power square wave output waveform. Traditional class D amplifiers have maximum current ripple in the output filter inductor at 50 % duty cycle (idle operation) which gives rise to high amount of common mode frequency content. However, MERUS™ multilevel operation exhibits minimal switching at idle which ensures minimal common mode emission at idle operation. The differential mode content at higher playback levels, when switching activity is stronger, is also significantly reduced as the transition between voltage levels is relatively small

**Figure 11.4:** MERUS™ multilevel modulation efficiency compared to traditional 2-level modulation

for multilevel compared to traditional class D. In addition, MA2304DNS makes it possible to address EMC issues from a software perspective with its PWM synchronization feature as well as configurable switching edge steepness (slew rate), all to reduce EMI in applications with many devices, e.g. multi-channel amplifiers.

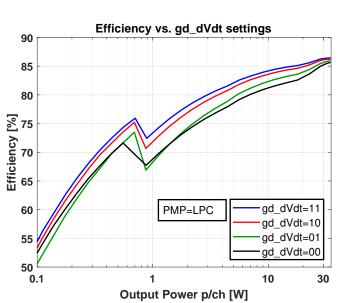

#### 11.1.5 Power Mode Profiles (PMP)

The MA2304DNS features two selectable power mode profiles (PMP):

- · Low Power Consumption (LPC) Mode

- High Audio Performance (HAP) Mode

LPC mode keeps efficiency as high as possible and minimizes idle losses by using a lower switching frequency for low output levels. HAP mode improves noise by using a higher switching frequency and therefore achieves a feedback loop with higher bandwidth. Switching frequency is dynamic for LPC mode and varies with output power with no audible artifacts. Table 7 shows the general properties of the two modes.

**Table 7:** Power Mode Profiles \*PVDD=18 V, VDD/VDD\_IO=1.8 V, BTL, Load=8  $\Omega$ +22  $\mu$ H, PCB=EVAL AUDIO MA23xx

| Parameter              | LPC          | HAP      |

|------------------------|--------------|----------|

| Idle consumption*      | 52 mW        | 70 mW    |

| Efficiency 0.1 W*      | 57 %         | 47 %     |

| Efficiency 1 W*        | 79 %         | 79 %     |

| Efficiency 10 W*       | 93 %         | 93 %     |

| FET switch. freq.      | 128-256 kHz  | 256 kHz  |

| Switch. freq. at load. | 512-1024 kHz | 1024 kHz |

| THD+N, 1 kHz, 5 W      | 0.05 %       | 0.05 %   |

| Noise, A-weighted      | 82 μV        | 52 μV    |

| Dynamic Range          | 102 dB       | 106 dB   |

#### MERUS™ Multilevel Switching Class-D Audio Amplifier

#### 11.2 Modes of Operation

#### 11.2.1 Normal Operation / Shutdown (ENABLE pin)

The ENABLE pin (20) controls the shutdown state of MA2304DNS. When ENABLE is low, the device is in shutdown mode. When ENABLE becomes high, the device exits shutdown state, boots up and enters normal operation. Refer to specifications for ENABLE timing.

#### 11.2.2 Mute / Unmute (NMUTE pin)

NMUTE (19) controls muting of the amplifier output and is an active-low pin, i.e. if NMUTE=high the output will be unmuted. Muting is instantaneous, but unmuting is a timed function with a delay (refer to NMUTE timing)

Muting can also be performed with the mute\_ch0/1 register for individual channels. Use mute\_source to choose the source of muting: NMUTE pin or register setting.

In muted state, no audio content is present at the amplifier output, but there will be some switching activity to balance and pre-charge the flying capacitors. If no switching activity is desired the individual amplifier channels can be disabled with the disable\_ch0/1 registers.

#### 11.2.3 Standby

The device can be put in standby mode for lowest possible power consumption while still maintaining a functional I2C interface (to wake the device at a later point). Standby mode is controlled with the standby register.

#### 11.3 BTL/PBTL Output Configurations

The amplifier output can be configured to operate in

- Bridge Tied Load (BTL)

- Parallel Bridge Tied Load (PBTL)

Table 8: BTL/PTBL properties

|                    | <i>'</i> ' ' |        |

|--------------------|--------------|--------|

| Parameter          | PBTL         | BTL    |

| Min. current limit | 12 A         | 6 A    |

| Recommended load   | 2-4 Ω        | 4-8 Ω  |

| MSEL pin tie-off   | Ground       | VDD_IO |

The MSEL pin (34) controls the output configuration and must be set before the device powers up (when ENABLE=1). Alternatively, the mode\_pbtl register can be used to configure the output after the device has powered up. The TBD\_reg\_ctrl register must also be set for the mode\_pbtl register to take effect and override the hardware setting of the MSEL pin.

BTL is best suited for standard current, two-channel applications, e.g. stereo speaker pairs and 2-way systems. PTBL is a 1-channel configuration but with twice the output power/current capability, which can be useful for subwoofers and/or low impedance speakers. Refer to Figure

#### 11.5 and 11.6 for configuration diagrams.

PBTL mode dynamically enables the second output based on the signal level so that idle power consumption can be as low as possible when high output power is not needed.

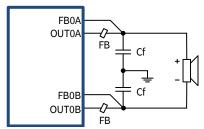

Figure 11.5: Bridge Tied Load (BTL) configuration

**Figure 11.6:** Bridge Tied Load (PBTL) configuration. Note: It is also possible to connect output pins A and B before the ferrite filter in order to use two ferrites in total instead of four.

#### 11.4 Gain Configuration

MA2304DNS offers different gain configurations for matching full scale output with the desired PVDD voltage in an application. The gain is controlled with the pvdd\_scale register. Reducing the amplifier gain to a lower value also reduces output noise. Gain frequency response is shown in Figure 13.28. Changing gain settings while the power stage is unmuted can result in significant pop/click and should be avoided. The table below shows the recommended pvdd scale setting for each different typical PVDD supply level. For a complete usable PVDD range in each pvdd scale setting refer to Figure 13.30 . Setting 11 and 10 can be used

#### MERUS™ Multilevel Switching Class-D Audio Amplifier

from 10V to 18V, setting 01 can be used from 10V to 16V and setting 00 can be used from 10V to 15V.

**Table 9:** Gain options for recommended (guideline) PVDD voltages.

| pvdd_scale   | Recommended PVDD |

|--------------|------------------|

| 00           | 10 V             |

| 01           | 12 V             |

| 10           | 15 V             |

| 11 (default) | 18 V             |

For additional noise characteristics as a function of gain and PVDD, please see Figure 13.29 and 13.30.

Note that the power stage cannot operate at full scale above 20 kHz. HAP mode is preferred if out-of-band operation is desired as its bandwidth is greater than LPC mode.

#### 11.5 Protection

MA2304DNS offers a range of protection features to avoid damage to the device itself or attached speakers.

#### 11.5.1 Errors and Error Handling (NERR pin)

The protection system in MA2304DNS monitors a range of parameters to check if min/max thresholds are exceeded. Exceeding the thresholds will trigger an error event in the protection system and the NERR pin (pin 11) will change from high to low. The NERR pin will only report errors correctly after the first PLL lock which requires clocks present on I2S\_SCK and I2S\_WC pins.

The NERR pin can be used as an interrupt flag for an external host control device, e.g. a system microcontroller. Alternatively, the err\_pin register can be used to monitor the NERR pin as well. Once an error has been detected by the host, the error type can be identified by reading the error registers. Connect a 51  $k\Omega$  resistor from NERR to VDD\_IO.

#### **General device errors:**

- Low temperature warning

- · I2S input error

- PLL error

- PVDD over-voltage

- PVDD under-voltage

- Over-temperature error

- · Over-temperature warning

The errors above can be read as individual bits in the following registers:

errVect\_now.errVector\_all\_\_0 (instantaneous)

errVect\_acc.errVector\_all\_\_0 (accumulated/sticky)

#### Individual channel errors:

- · DC error

- · Flying capacitor error

- · Over-current error

The errors above can be read as individual bits in the following registers:

- errVect\_acc.errVector\_ch0 (Channel 0 accumulated / sticky errors)

- errVect\_acc.errVector\_ch1 (Channel 1 accumulated / sticky errors)

#### **Clearing errors**

Errors can be cleared by toggling the reg.errTrig\_reset register from 0 to 1 and then back to 0.

#### **Error handling:**

It is generally recommended to use to accumulated error registers for error detection and handling. Normal error handling procedure:

- Disregard errors during start-up of the device defined by T<sub>ENABLE</sub>.

- Clear errors immediately after start-up.

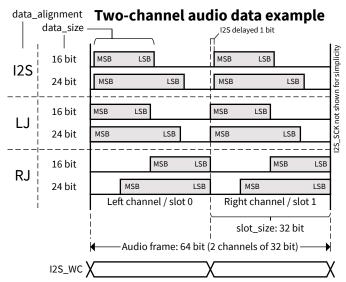

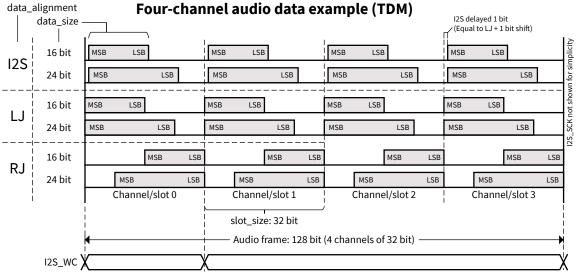

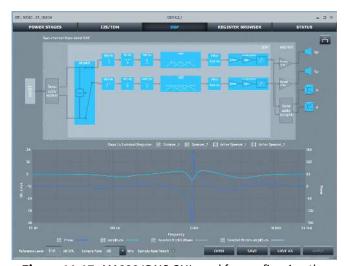

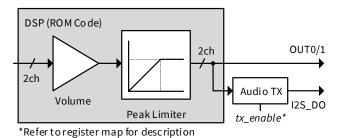

- Monitor accumulated error registers (general + channel) and take appropriate action if an error occurs.

- Clear error register(s) after action has been taken to again monitor for new errors.