LMH1208

SNLS569C - MARCH 2017-REVISED MAY 2020

# LMH1208 12G UHD-SDI Dual Output Cable Driver

#### **Features**

- Supports ST-2082-1 (12G), ST-2081-1 (6G), ST-424 (3G), ST-292 (HD), and ST-259 (SD)

- Compatible with DVB-ASI and AES10 (MADI)

- Dual differential output cable drivers

- On-chip 75-Ω termination and return loss compensation network

- Host-side equalized 100-Ω loop-back output

- Programmable slew rate control on 75-Ω outputs

- Programmable pre-emphasis and output amplitude on 75-Ω outputs

- Programmable de-emphasis and output amplitude on 100-Ω output

- Polarity inversion on 75- $\Omega$  and 100- $\Omega$  outputs

- Automatic power save in absence of input signal

- Power consumption: 25 mW (Typical)

- Power-down control through ENABLE pin

- Single 2.5-V supply

- Power consumption: 200 mW (typical)

- Programmable through pins, SPI, or SMBus interface

- -40°C to +85°C operating temperature range

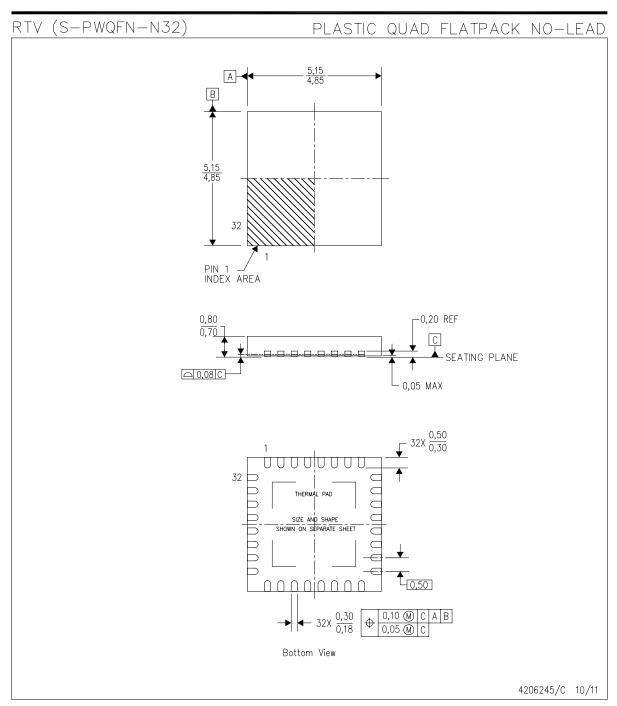

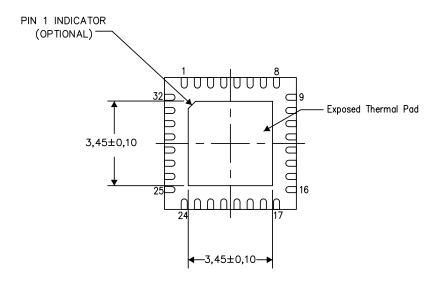

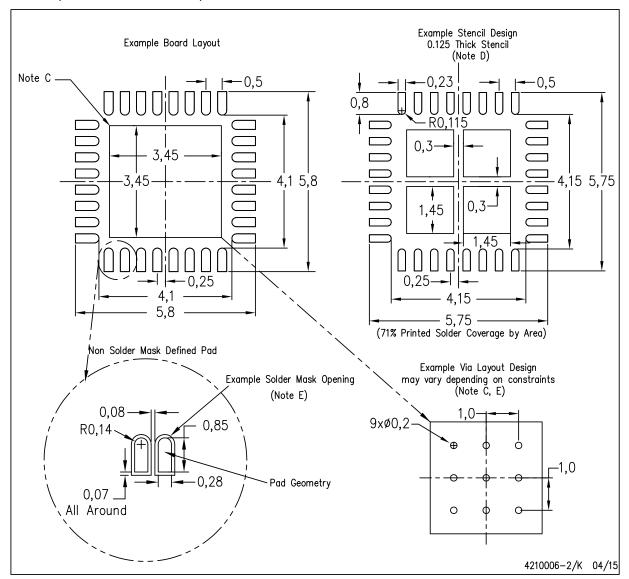

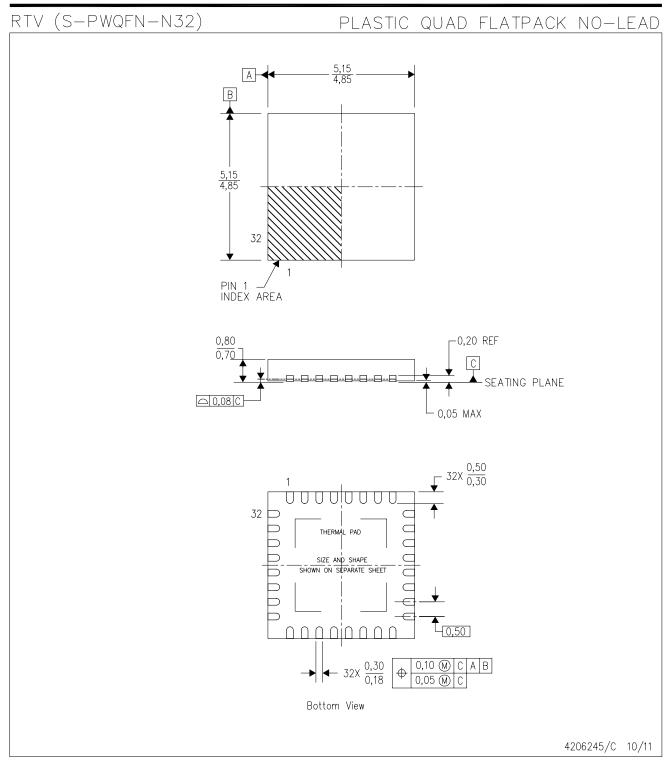

- 5-mm × 5-mm, 32-pin WQFN package

# **Applications**

- SMPTE compatible serial digital interface

- UHDTV/4K/8K/HDTV/SDTV video

- IP media gateway

- Digital video processing and editing

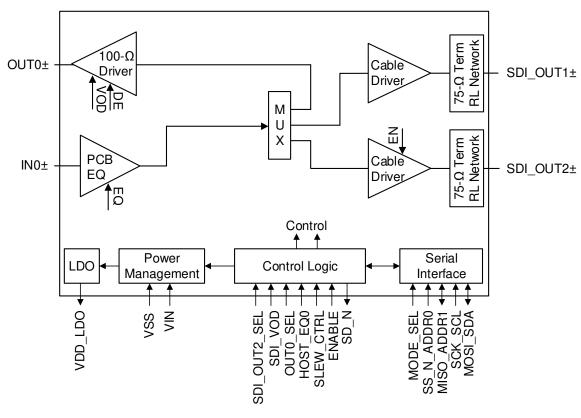

## Description

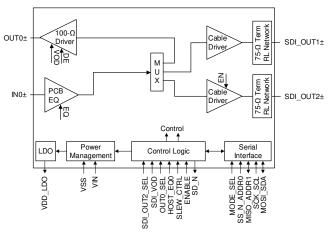

LMH1208 device is a 12G UHD-SDI low power dual output cable driver. It supports SMPTE video rates up to 11.88 Gbps, enabling UHD video for 4K/8K applications. The additional equalized  $100-\Omega$  driver output on the host-side can be used for monitoring or signal distribution purposes.

The programmable PCB input equalizer provides high frequency boost to reduce inter symbol interference (ISI) induced by PCB board trace. The integrated 75- $\Omega$  termination and return loss network at both cable driver outputs facilitate overall system design in meeting stringent SMPTE return loss requirements.

Input Signal Detect determines the presence of a valid signal at the input of the cable driver. This sensing feature may be used to alert the user of a system fault and activate a Power Save Mode, reducing the power consumption of the cable driver. The LMH1208 provides selectable slew rates for data rates up to 11.88 Gbps. The output slew rate and amplitude can be controlled by pin, SPI, or SMBus control.

The LMH1208 is powered from a single 2.5-V supply. It is offered in a small footprint 5 mm × 5 mm 32-pin WQFN package. The LMH1208 is pin compatible with the LMH1228 (12G Dual Cable Driver with Integrated Reclocker).

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LMH1208     | WQFN (32) | 5.00 mm × 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Simplified Block Diagram

Copyright @ 2016, Texas Instruments Incorporate

# **Table of Contents**

| 1 | Features 1                                 |    | 7.4 Device Functional Modes                         | 19                 |

|---|--------------------------------------------|----|-----------------------------------------------------|--------------------|

| 2 | Applications 1                             |    | 7.5 Register Maps                                   | 23                 |

| 3 | Description 1                              | 8  | Application and Implementation                      |                    |

| 4 | Revision History2                          |    | 8.1 Application Information                         | 24                 |

| 5 | Pin Configuration and Functions            |    | 8.2 Typical Applications                            | 25                 |

| 6 | Specifications6                            | 9  | Power Supply Recommendations                        | 32                 |

| • | 6.1 Absolute Maximum Ratings               | 10 | Layout                                              | 33                 |

|   | 6.2 ESD Ratings                            |    | 10.1 Layout Guidelines                              | 33                 |

|   | 6.3 Recommended Operating Conditions       |    | 10.2 Layout Example                                 | 35                 |

|   | 6.4 Thermal Information                    | 11 | Device and Documentation Support                    | 36                 |

|   | 6.5 Electrical Characteristics             |    | 11.1 Documentation Support                          | 36                 |

|   | 6.6 Recommended SMBus Interface Timing     |    | 11.2 Receiving Notification of Documentation Update | es <mark>36</mark> |

|   | Specifications 10                          |    | 11.3 Community Resources                            | 36                 |

|   | 6.7 Serial Parallel Interface (SPI) Timing |    | 11.4 Trademarks                                     | 36                 |

|   | Specifications11                           |    | 11.5 Electrostatic Discharge Caution                | 36                 |

|   | 6.8 Typical Characteristics                |    | 11.6 Export Control Notice                          | 36                 |

| 7 | Detailed Description 14                    |    | 11.7 Glossary                                       | 36                 |

|   | 7.1 Overview 14                            | 12 | Mechanical, Packaging, and Orderable                |                    |

|   | 7.2 Functional Block Diagram               |    | Information                                         | 36                 |

|   | 7.3 Feature Description                    |    | 12.1 Package Option Addendum                        | 37                 |

|   |                                            |    | 12.1 Tackage Option Addendam                        | •••                |

# 4 Revision History

| Changes from Revision B (October 2019) to Revision C   | Page |

|--------------------------------------------------------|------|

| Changed HBM Ratings and added pin 27 description       |      |

| Changes from Revision A (September 2017) to Revision B | Pago |

| Initial Public Release                                 |      |

Product Folder Links: LMH1208

Submit Documentation Feedback

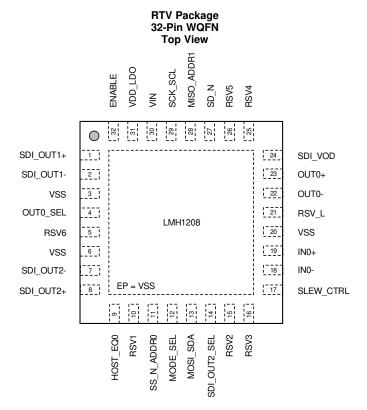

# 5 Pin Configuration and Functions

Copyright © 2016, Texas Instruments Incorporated

## **Pin Functions**

| PIN            |              | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |  |  |

|----------------|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.       |              | 1/0(-/             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |  |  |

| HIGH-SPEED DIF | FERENTI      | AL I/OS            |                                                                                                                                                                                                                                                                                                                                                            |  |  |

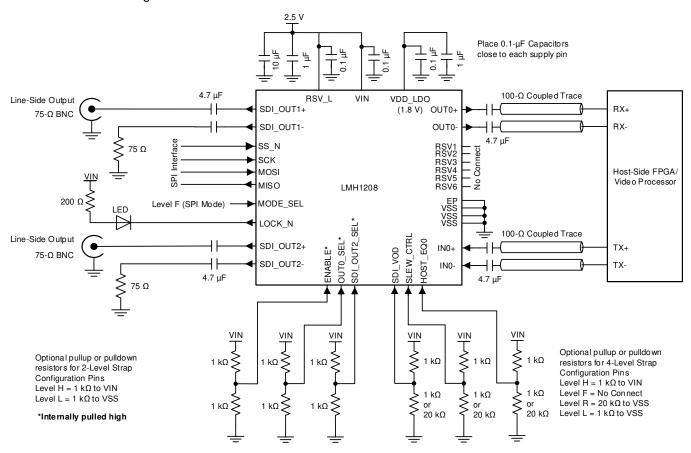

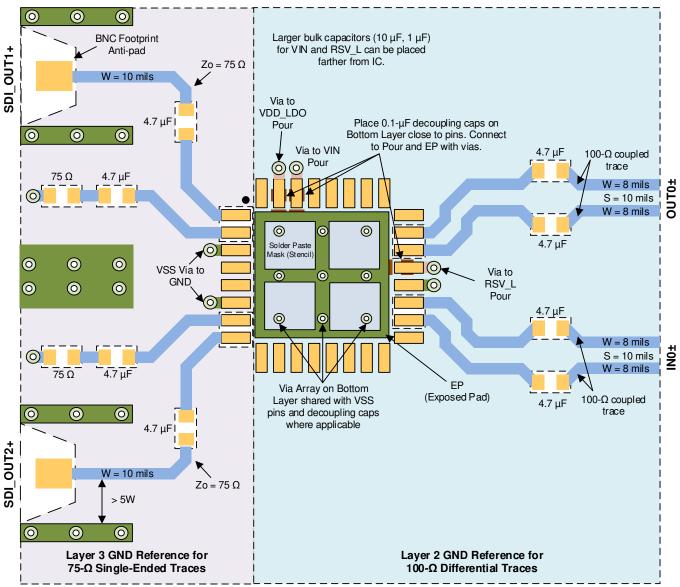

| SDI_OUT1+ 1    |              | I/O, Analog        | Single-ended complementary outputs with on-chip 75-Ω termination at SDI_OUT1+ and                                                                                                                                                                                                                                                                          |  |  |

| SDI_OUT1-      | 2            | I/O, Analog        | SDI_OUT1 SDI_OUT1± include integrated return loss networks designed to meet the SMPTE output return loss requirements. Connect SDI_OUT1+ to a BNC through a 4.7-μF, AC-coupling capacitor. SDI_OUT1- should be similarly AC-coupled and terminated with an external 4.7-μF capacitor and 75-Ω resistor to GND.                                             |  |  |

| SDI_OUT2+      | 8            | O, Analog          | Single-ended complementary outputs with on-chip 75-Ω termination at SDI_OUT2+ and                                                                                                                                                                                                                                                                          |  |  |

| SDI_OUT2-      | 7            | O, Analog          | SDI_OUT2 SDI_OUT2± include integrated return loss networks designed to meet the SMPTE output return loss requirements. SDI_OUT2± is used as a second cable driver. Connect SDI_OUT2+ to a BNC through a 4.7-μF, AC-coupling capacitor. SDI_OUT2- should be similarly AC-coupled and terminated with an external 4.7-μF capacitor and 75-Ω resistor to GND. |  |  |

| IN0+           | 19           | I, Analog          | Differential inputs from host video processor. On-chip 100-Ω differential termination.                                                                                                                                                                                                                                                                     |  |  |

| INO-           | 18           | I, Analog          | Requires external 4.7-μF, AC-coupling capacitors for SMPTE applications.                                                                                                                                                                                                                                                                                   |  |  |

| OUT0+          | 23           | O, Analog          | Differential outputs to host video processor. On-chip $100-\Omega$ differential termination. Requires                                                                                                                                                                                                                                                      |  |  |

| OUT0-          | 22           | O, Analog          | external 4.7-μF, AC-coupling capacitors for SMPTE applications.                                                                                                                                                                                                                                                                                            |  |  |

| CONTROL PINS   | CONTROL PINS |                    |                                                                                                                                                                                                                                                                                                                                                            |  |  |

| OUT0_SEL       | 4            | I, LVCMOS          | OUT0_SEL enables the use of the 100-Ω host-side output driver at OUT0±.  See Table 2 for details.  OUT0_SEL is internally pulled high by default (OUT0 disabled).                                                                                                                                                                                          |  |  |

| HOST_EQ0       | 9            | I, 4-LEVEL         | HOST_EQ0 selects the equalizer setting for IN0±.<br>See Table 4 for details.                                                                                                                                                                                                                                                                               |  |  |

(1) I = Input, O = Output, I/O = Input or Output, OD = Open Drain, LVCMOS = 2-State Logic, 4-LEVEL = 4-State Logic

# Pin Functions (continued)

| PIN            |                                                                                                                                                                                         | (1)                |                                                                                                                                                                                                                                                                                                                      |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME           | NO.                                                                                                                                                                                     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                          |  |

| MODE_SEL       | 12                                                                                                                                                                                      | I, 4-LEVEL         | MODE_SEL enables the SPI or SMBus serial control interface.<br>See Table 8 for details.                                                                                                                                                                                                                              |  |

| SDI_OUT2_SEL   | 14                                                                                                                                                                                      | I, LVCMOS          | SDI_OUT2_SEL enables the use of the 75- $\Omega$ output driver at SDI_OUT2±. See Table 2 for details. SDI_OUT2_SEL is internally pulled high by default (SDI_OUT2 disabled).                                                                                                                                         |  |

| SLEW_CTRL      | 17                                                                                                                                                                                      | I, 4-LEVEL         | SLEW_CTRL selects the edge rate for both cable driver outputs. SLEW_CTRL settings are dependent on the operating SMPTE data rate.  SLEW_CTRL also determines the pre-emphasis level applied to both cable driver outputs. See Table 6 and Table 7 for details.                                                       |  |

| SDI_VOD        | 24                                                                                                                                                                                      | I, 4-LEVEL         | SDI_VOD selects one of four output amplitudes for the cable drivers at SDI_OUT1± and SDI_OUT2±. See Table 5 for details.                                                                                                                                                                                             |  |

| SD_N           | 27                                                                                                                                                                                      | O, LVCMOS,<br>OD   | SD_N is the Signal Detect indicator. SD_N is pulled low when signal is detected at IN0±. SD_N is a 3.3-V tolerant, open-drain output. It requires an external resistor to a logic supply. SD_N can be reconfigured to indicate Interrupt (INT_N) through register programming. See Status Indicators and Interrupts. |  |

| ENABLE         | A logic-high at ENABLE enables normal operation for the LMH1208. A logic-low at ENABLE 32 I, LVCMOS places the LMH1208 in Power-Down Mode. ENABLE is internally pulled high by default. |                    |                                                                                                                                                                                                                                                                                                                      |  |

| SPI SERIAL CON | ITROL IN                                                                                                                                                                                | TERFACE, MODE      | SEL = F (FLOAT)                                                                                                                                                                                                                                                                                                      |  |

| SS_N           | 11                                                                                                                                                                                      | I, LVCMOS          | SS_N is the Slave Select. When SS_N is at logic low, it enables SPI access to the LMH1208 slave device. SS_N is a 2.5-V LVCMOS input and is internally pulled high by default.                                                                                                                                       |  |

| MOSI           | 13                                                                                                                                                                                      | I, LVCMOS          | MOSI is the SPI serial control data input to the LMH1208 slave device when the SPI bus is enabled. MOSI is a 2.5-V LVCMOS input.  An external pullup resistor is recommended.                                                                                                                                        |  |

| MISO           | 28                                                                                                                                                                                      | O, LVCMOS          | MISO is the SPI serial control data output from the LMH1208 slave device. MISO is a 2.5-V LVCMOS output.                                                                                                                                                                                                             |  |

| SCK            | 29                                                                                                                                                                                      | I, LVCMOS          | SCK is the SPI serial input clock to the LMH1208 slave device when the SPI interface is enabled. SCK is a 2.5-V LVCMOS input.  An external pullup resistor is recommended.                                                                                                                                           |  |

| SMBUS SERIAL   | CONTRO                                                                                                                                                                                  | L INTERFACE, M     | ODE_SEL = L (1 K $\Omega$ TO VSS)                                                                                                                                                                                                                                                                                    |  |

| ADDR0          | 11                                                                                                                                                                                      | Strap, 4-LEVEL     | ADDR[1:0] are 4-level straps, read into the device at power up. They are used to select one of the 16 supported SMBus addresses when SMBus is enabled. See Table 9 for details.                                                                                                                                      |  |

| SDA            | 13                                                                                                                                                                                      | I/O, LVCMOS,<br>OD | SDA is the SMBus bidirectional data line to or from the LMH1208 slave device when SMBu is enabled. SDA is an open-drain I/O and requires an external pullup resistor to the SMBus termination voltage. SDA is 3.3-V tolerant.                                                                                        |  |

| ADDR1          | 28                                                                                                                                                                                      | Strap, 4-LEVEL     | ADDR[1:0] are 4-level straps, read into the device at power up. They are used to select one of the 16 supported SMBus addresses when SMBus is enabled. See Table 9 for details.                                                                                                                                      |  |

| SCL            | 29                                                                                                                                                                                      | I/O, LVCMOS,<br>OD | SCL is the SMBus input clock to the LMH1208 slave device when SMBus is enabled. It is driven by a LVCMOS open-drain driver from the SMBus master. SCL requires an external pullup resistor to the SMBus termination voltage. SCL is 3.3-V tolerant.                                                                  |  |

# Pin Functions (continued)

| PIN                                          |                                 | I/O <sup>(1)</sup> | DECORIDEION                                                                                                                                                                                            |  |  |

|----------------------------------------------|---------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.                                     |                                 | 1/0(*)             | DESCRIPTION                                                                                                                                                                                            |  |  |

| RESERVED                                     |                                 |                    |                                                                                                                                                                                                        |  |  |

| RSV1<br>RSV2<br>RSV3<br>RSV4<br>RSV5<br>RSV6 | 10<br>15<br>16<br>25<br>26<br>5 | -                  | Reserved pins. Do not connect.                                                                                                                                                                         |  |  |

| POWER                                        |                                 |                    |                                                                                                                                                                                                        |  |  |

| VSS                                          | 3, 6, 20                        | I, Ground          | Ground reference.                                                                                                                                                                                      |  |  |

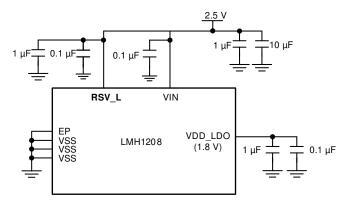

| RSV_L                                        | 21                              | I, Power           | Connect RSV_L to the same 2.5-V ± 5% supply as VIN.                                                                                                                                                    |  |  |

| VIN                                          | 30                              | I, Power           | VIN is connected to an external 2.5-V ± 5% power supply.                                                                                                                                               |  |  |

| VDD_LDO                                      | 31                              | O, Power           | VDD_LDO is the output of the internal 1.8-V LDO regulator. VDD_LDO output requires an external 1-μF and 0.1-μF bypass capacitor to VSS. The internal LDO is designed to power internal circuitry only. |  |  |

| EP                                           | _                               | I, Ground          | EP is the exposed pad at the bottom of the RTV package. The exposed pad should be connected to the VSS plane through a 3 × 3 via array.                                                                |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                     | MIN  | MAX  | UNIT |

|---------------------------------------------------------------------|------|------|------|

| Supply voltage (VIN, RSV_L)                                         | -0.5 | 2.75 | V    |

| Input voltage for 4-level pins                                      | -0.5 | 2.75 | V    |

| Input/output voltage for 2-level control pins                       | -0.5 | 2.75 | V    |

| SMBus input/output voltage (SDA, SCL)                               | -0.5 | 4    | V    |

| SPI input/output voltage (SS_N, MISO, MOSI, and SCK)                | -0.5 | 2.75 | V    |

| High-speed input/output voltage (IN0±, SDI_OUT1±, OUT0±, SDI_OUT2±) | -0.5 | 2.75 | V    |

| Input current (IN0±)                                                | -30  | 30   | mA   |

| Operating junction temperature                                      |      | 125  | °C   |

| Storage temperature, T <sub>stg</sub>                               | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|             |               |                                                                   |                               | VALUE | UNIT |

|-------------|---------------|-------------------------------------------------------------------|-------------------------------|-------|------|

|             | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | All pins except 13,27, and 29 | ±6000 |      |

| $V_{(ESD)}$ | discharge     | , , , ,                                                           | Pins 13, 27, and 29           | ±5000 | V    |

|             |               | Charged-device model (CDM), per JEDEC specification JESD2         | 2-C101 <sup>(2)</sup>         | ±1500 |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                      |                                    | MIN   | NOM  | MAX   | UNIT  |

|-------------------------|--------------------------------------|------------------------------------|-------|------|-------|-------|

|                         | Supply voltage                       | VIN, RSV_L to VSS                  | 2.375 | 2.5  | 2.625 | V     |

| VDD <sub>SMBUS</sub>    | SMBus: SDA, SCL open-drain ter       | mination voltage                   | 2.375 |      | 3.6   | V     |

|                         | Source differential launch amplitude | Before 5-inch board trace to IN0±  | 300   |      | 850   | mVp-p |

| V <sub>IN0_LAUNCH</sub> |                                      | Before 20-inch board trace to IN0± | 650   |      | 1000  |       |

| T <sub>JUNCTION</sub>   | Operating junction temperature       |                                    |       |      | 110   | °C    |

| T <sub>AMBIENT</sub>    | Ambient temperature                  |                                    | -40   | 25   | 85    | °C    |

| NTps <sub>max</sub>     | (1)                                  | 50 Hz to 1 MHz, sinusoidal         |       | < 20 |       | mVp-p |

|                         | Maximum supply noise <sup>(1)</sup>  | 1.1 MHz to 50 MHz, sinusoidal      |       | < 10 |       |       |

(1) The sum of the DC supply voltage and AC supply noise should not exceed the recommended supply voltage range.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

### 6.4 Thermal Information

|                      |                                              | LMH1208    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTV (WQFN) | UNIT |

|                      |                                              | 32 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 32.5       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 15.0       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.5        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.5        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                                         | TEST CONDITIONS                                                                 | MIN           | TYP | MAX          | UNIT |

|---------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------|-----|--------------|------|

| POWER               |                                                                                   |                                                                                 |               |     |              |      |

|                     |                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± disabled                       |               | 200 |              | mW   |

| PD                  | Power dissipation<br>Measured with PRBS10,                                        | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± enabled                        |               | 250 |              | mW   |

|                     | Operating at 11.88 Gbps,<br>VOD = default                                         | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± disabled                        |               | 340 |              | mW   |

|                     |                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± enabled                         |               | 385 |              | mW   |

| $PD_Z$              | Power dissipation,<br>Power Save Mode                                             | Power Save Mode,<br>ENABLE = H, no signal applied at IN0±                       |               | 25  |              | mW   |

|                     | Current consumption, Measured with PRBS10, Operating at 11.88 Gbps, VOD = default | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± disabled                       |               | 80  | 104          | mA   |

| IDD                 |                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± disabled<br>OUT0± enabled                        |               | 100 | 125          | mA   |

| IDD                 |                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± disabled                        |               | 136 | 170          | mA   |

|                     |                                                                                   | SDI_OUT1± enabled<br>SDI_OUT2± enabled<br>OUT0± enabled                         |               | 154 | 190          | mA   |

| IDD <sub>Z</sub>    | Current consumption, Power Save Mode                                              | Power Save Mode,<br>ENABLE = H, no signal applied at IN0±                       |               | 10  |              | mA   |

| IDD <sub>Z_PD</sub> | Current consumption, Power-Down Mode                                              | Power-Down Mode,<br>ENABLE = L, no signal applied at IN0±                       |               | 10  | 30           | mA   |

| LVCMOS DO           | SPECIFICATIONS                                                                    |                                                                                 |               |     |              |      |

| $V_IH$              | Logic high input voltage                                                          | 2-level input (SS_N, SCK, MOSI, SDI_OUT2_SEL, OUT0_SEL, ENABLE)                 | 0.72 ×<br>VIN |     | VIN +<br>0.3 | V    |

| VIH                 | Logic High Input voltage                                                          | 2-level input (SCL, SDA)                                                        | 0.7 ×<br>VIN  |     | 3.6          | ٧    |

| V <sub>IL</sub>     | Logic low input voltage                                                           | 2-level input (SS_N, SCK, MOSI,<br>SDI_OUT2_SEL, OUT0_SEL, ENABLE,<br>SCL, SDA) | 0             |     | 0.3 ×<br>VIN | V    |

| V <sub>OH</sub>     | Logic high output voltage                                                         | IOH = -2 mA, (MISO)                                                             | 0.8 ×<br>VIN  |     | VIN          | ٧    |

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                                     | TEST CONDITIONS                                                   | MIN  | TYP          | MAX          | UNIT  |

|-------------------------|---------------------------------------------------------------|-------------------------------------------------------------------|------|--------------|--------------|-------|

| $V_{OL}$                | Logic low output voltage                                      | IOL = 2 mA, (MISO)                                                | 0    |              | 0.2 ×<br>VIN | V     |

|                         |                                                               | IOL = 3 mA, (SD_N, SDA)                                           |      |              | 0.4          | V     |

|                         |                                                               | LVCMOS (SDI_OUT2_SEL, ENABLE)                                     |      |              | 15           | μΑ    |

|                         |                                                               | LVCMOS (OUT0_SEL)                                                 |      |              | 65           | μΑ    |

| Іін                     | Input high leakage current<br>(Vinput = VIN)                  | LVCMOS (SD_N)                                                     |      |              | 10           | μΑ    |

|                         | (Viliput – VIIV)                                              | SPI mode: LVCMOS (SS_N, SCK, MOSI)                                |      |              | 15           | μΑ    |

|                         |                                                               | SMBus mode: LVCMOS (SCL, SDA)                                     |      |              | 10           | μΑ    |

|                         |                                                               | LVCMOS (SDI_OUT2_SEL, ENABLE)                                     | -50  |              |              | μΑ    |

|                         |                                                               | LVCMOS (OUT0_SEL)                                                 | -15  |              |              | μΑ    |

|                         | Input low leakage current                                     | LVCMOS (SD_N)                                                     | -10  |              |              | μΑ    |

| IL                      | (Vinput = GND)                                                | SPI mode: LVCMOS (SCK, MOSI)                                      | -15  |              |              | μΑ    |

|                         |                                                               | SPI mode: LVCMOS (SS_N)                                           | -50  |              |              | μΑ    |

|                         |                                                               | SMBus mode: LVCMOS (SCL, SDA)                                     | -10  |              |              | μA    |

| 4-LEVEL LOG             | IC DC SPECIFICATIONS (APPLY T                                 | O ALL 4-LEVEL INPUT CONTROL PINS)                                 | +    |              |              |       |

| V <sub>LVL_H</sub>      | LEVEL-H input voltage                                         | Measured voltage at 4-level pin with external 1 kΩ to VIN         |      | VIN          |              | V     |

| V <sub>LVL_F</sub>      | LEVEL-F default voltage                                       | Measured voltage 4-level pin at default                           |      | 2/3 ×<br>VIN |              | V     |

| V <sub>LVL_R</sub>      | LEVEL-R input voltage                                         | Measured voltage at 4-level pin with external 20 $k\Omega$ to VSS |      | 1/3 ×<br>VIN |              | V     |

| V <sub>LVL_L</sub>      | LEVEL-L input voltage                                         | Measured voltage at 4-level pin with external 1 $k\Omega$ to VSS  |      | 0            |              | V     |

| I <sub>IH</sub>         | Input high leakage current                                    | 4-levels (HOST_EQ0, MODE_SEL, SLEW_CTRL, SDI_VOD)                 | 20   | 45           | 80           | μΑ    |

|                         | (Vinput = VIN)                                                | SMBus mode: 4-levels (ADDR0, ADDR1)                               | 20   | 45           | 80           | μΑ    |

| I <sub>IL</sub>         | Input low leakage current                                     | 4-levels (HOST_EQ0, MODE_SEL, SLEW_CTRL, SDI_VOD)                 | -160 | -93          | -40          | μΑ    |

|                         | (Vinput = GND)                                                | SMBus mode: 4-levels (ADDR0, ADDR1)                               | -160 | -93          | -40          | μΑ    |

| RECEIVER SP             | PECIFICATIONS (IN0±)                                          |                                                                   | •    |              |              |       |

| R <sub>IN0 TERM</sub>   | DC input differential termination                             | Measured across IN0+ to IN0-                                      | 80   | 100          | 120          | Ω     |

|                         |                                                               | SDD11, 10 MHz – 2.8 GHz                                           |      | -22          |              | dB    |

| RL <sub>INO SDD11</sub> | Input differential return loss (1)                            | SDD11, 2.8 GHz – 6 GHz                                            |      | -16          |              | dB    |

|                         |                                                               | SDD11, 6 GHz – 11.1 GHz                                           |      | -10          |              | dB    |

| RL <sub>IN0_SCD11</sub> | Differential to common-mode input conversion (1)              | SCD11, 10 MHz to 11.1 GHz                                         |      | -21          |              | dB    |

| V <sub>IN0_CM</sub>     | DC common-mode voltage                                        | Input common-mode voltage at IN0+ or IN0- to GND                  |      | 2.06         |              | V     |

| CD <sub>ON_IN0</sub>    | Signal detect (default) Assert ON threshold level for IN0±    | 11.88 Gbps, EQ and PLL pathological pattern                       |      | 20           |              | mVp-p |

| CD <sub>OFF_IN0</sub>   | Signal detect (default) Deassert OFF threshold level for IN0± | 11.88 Gbps, EQ and PLL pathological pattern                       |      | 18           |              | mVp-p |

| DRIVER OUTP             | PUT (SDI_OUT1+ AND SDI_OUT2+)                                 |                                                                   | •    |              |              |       |

| R <sub>OUT_TERM</sub>   | DC output single-ended termination                            | SDI_OUT1+ and SDI_OUT1-,<br>SDI_OUT2+ and SDI_OUT2- to VIN        | 63   | 75           | 87           | Ω     |

<sup>(1)</sup> This parameter is measured with the LMH1297EVM (Evaluation board for LMH1208).

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                              | TEST CONDITIONS                                                                                                                         | MIN     | TYP  | MAX | UNIT  |

|------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------|------|-----|-------|

| VOD                    | Output single-ended output                             | Measure AC signal at SDI_OUT1+ and SDI_OUT2+, with SDI_OUT1- and SDI_OUT2- AC terminated with 75 $\Omega$ SDI_VOD = H                   |         | 840  |     | mVp-p |

| VOD <sub>CD_OUTP</sub> | voltage                                                | SDI_VOD = F                                                                                                                             | 720     | 800  | 880 | mVp-p |

|                        |                                                        | SDI_VOD = R                                                                                                                             |         | 880  |     | mVp-p |

|                        |                                                        | SDI_VOD = L                                                                                                                             |         | 760  |     | mVp-p |

| VOD                    | Output single-ended output                             | Measure AC signal at SDI_OUT1- and SDI_OUT2-, with SDI_OUT1+ and SDI_OUT2+ AC terminated with 75 $\Omega$ SDI_VOD = H                   |         | 840  |     | mVp-p |

| VOD <sub>CD_OUTN</sub> | voltage                                                | SDI_VOD = F                                                                                                                             | 720     | 800  | 880 | mVp-p |

|                        |                                                        | SDI_VOD = R                                                                                                                             |         | 880  |     | mVp-p |

|                        |                                                        | SDI_VOD = L                                                                                                                             |         | 760  |     | mVp-p |

| PRE <sub>CD_OUTP</sub> | Output pre-emphasis                                    | Output pre-emphasis boost amplitude at SDI_OUT1+ and SDI_OUT2+, programmed to maximum setting through register, measured at SDI_VOD = F |         | 2    |     | dB    |

| PRE <sub>CD_OUTN</sub> | Output pre-emphasis                                    | Output pre-emphasis boost amplitude at SDI_OUT1- and SDI_OUT2-, programmed to maximum setting through register, measured at SDI_VOD = F |         | 2    |     | dB    |

|                        | Output rise and fall time <sup>(1)</sup>               | Measured with PRBS10 pattern, default VOD at 20% – 80% amplitude, default preemphasis enabled 11.88 Gbps                                |         | 34   | 42  | ps    |

| t <sub>R_F_SDI</sub>   |                                                        | 5.94 Gbps                                                                                                                               |         | 36   | 43  | ps    |

|                        |                                                        | 2.97 Gbps                                                                                                                               |         | 59   | 67  | ps    |

|                        |                                                        | 1.485 Gbps                                                                                                                              |         | 60   | 73  | ps    |

|                        |                                                        | 270 Mbps                                                                                                                                | 400 550 | 700  | ps  |       |

|                        |                                                        | Measured with PRBS10 pattern, default VOD at 20% – 80% amplitude, default preemphasis enabled 11.88 Gbps                                |         | 3    | 18  | ps    |

| t <sub>R_F_DELTA</sub> | Output rise and fall time mismatch <sup>(1)</sup>      | 5.94 Gbps                                                                                                                               |         | 2.7  | 12  | ps    |

|                        |                                                        | 2.97 Gbps                                                                                                                               |         | 0.8  | 11  | ps    |

|                        |                                                        | 1.485 Gbps                                                                                                                              |         | 8.0  | 12  | ps    |

|                        |                                                        | 270 Mbps                                                                                                                                |         | 72   | 150 | ps    |

| V <sub>OVERSHOOT</sub> | Output overshoot or undershoot                         | Measured with PRBS10 pattern, default VOD, default pre-emphasis enabled (2) 12G/6G/3G/HD/SD                                             |         | 5%   |     |       |

| V <sub>DC_OFFSET</sub> | DC offset                                              | 12G/6G/3G/HD/SD                                                                                                                         |         | ±0.2 |     | V     |

| V <sub>DC_WANDER</sub> | DC wander                                              | 12G/6G/3G/HD/SD with EQ pathological pattern                                                                                            |         | 20   |     | mV    |

|                        |                                                        | S22, 5 MHz to 1.485 GHz                                                                                                                 |         | -25  |     | dB    |

| RI                     | Output return loss at                                  | S22, 1.485 GHz to 3 GHz                                                                                                                 |         | -22  |     | dB    |

| RL <sub>CD_S22</sub>   | SDI_OUT1+ and SDI_OUT2+ reference to 75 $\Omega^{(1)}$ | S22, 3 GHz to 6 GHz                                                                                                                     |         | -12  |     | dB    |

|                        |                                                        | S22, 6 GHz to 12 GHz                                                                                                                    |         | -8   |     | dB    |

<sup>(2)</sup> V<sub>OVERSHOOT</sub> overshoot and undershoot maximum measurements are largely affected by the PCB layout and input test pattern. The maximum value specified in *Electrical Characteristics* for V<sub>OVERSHOOT</sub> is based on bench evaluation across temperature and supply voltages with the LMH1297EVM.

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                | PARAMETER                                      | TEST CONDITIONS                                                                                 | MIN | TYP     | MAX   | UNIT     |  |

|--------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|---------|-------|----------|--|

| DRIVER OUTP                    | UT (OUT0±)                                     |                                                                                                 |     |         |       |          |  |

| R <sub>OUT0_TERM</sub>         | DC output differential termination             | Measured across OUT0+ and OUT0-                                                                 | 80  | 100     | 120   | Ω        |  |

|                                |                                                | Measured with 8T pattern<br>HOST_EQ0 = H                                                        |     | 410     |       | mVp-p    |  |

| VOD <sub>OUT0</sub>            | Output differential voltage at OUT0±           | HOST_EQ0 = F                                                                                    | 485 | 560     | 620   | mVp-p    |  |

|                                | 0010±                                          | HOST_EQ0 = R                                                                                    |     | 635     |       | mVp-p    |  |

|                                |                                                | HOST_EQ0 = L                                                                                    |     | 810 mVp | mVp-p |          |  |

|                                |                                                | Measured with 8T pattern<br>HOST_EQ0 = H                                                        |     | 410     |       | mVp-p    |  |

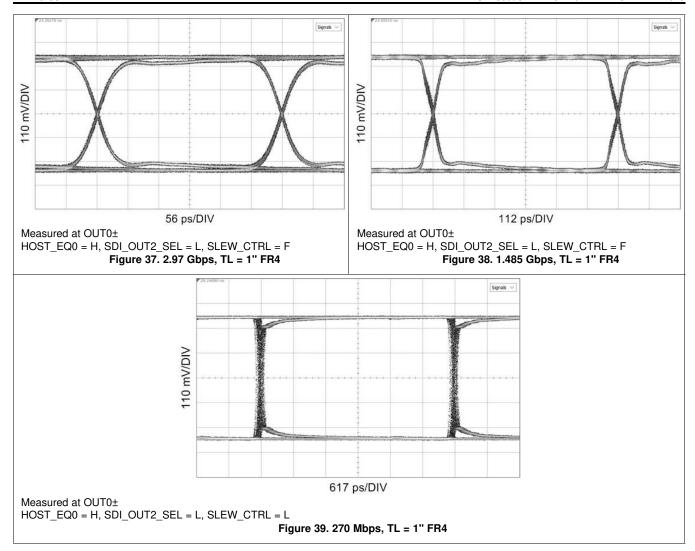

| VOD <sub>OUT0_DE</sub>         | De-emphasized output                           | HOST_EQ0 = F                                                                                    |     | 550     |       | mVp-p    |  |

| 0010_52                        | differential voltage at OUT0±                  | HOST_EQ0 = R                                                                                    |     | 545     |       | mVp-p    |  |

|                                |                                                | HOST_EQ0 = L                                                                                    |     | 532     | mVp-p |          |  |

| t <sub>R</sub> /t <sub>F</sub> | Output rise and fall time                      | Measured with 8T Pattern, 20% – 80% amplitude                                                   |     | 45      |       | ps       |  |

| DI                             | Output differential return loss <sup>(1)</sup> | Measured with the device powered up and outputs a 10-MHz clock signal SDD22, 10 MHz – 2.8 GHz   |     | -24     |       | dB       |  |

| RL <sub>OUT0-SDD22</sub>       |                                                | SDD22, 2.8 GHz – 6 GHz                                                                          |     | -16     |       | dB       |  |

|                                |                                                | SDD22, 6 GHz – 11.1 GHz                                                                         |     | -15     |       | dB       |  |

| RL <sub>OUT0-SCC22</sub>       | Output common-mode return loss <sup>(1)</sup>  | Measured with the device powered up and outputs a 10-MHz clock signal. SCC22, 10 MHz – 4.75 GHz |     | -12     |       | dB       |  |

|                                |                                                | SCC22, 4.75 GHz – 11.1 GHz                                                                      |     | -9      |       | dB       |  |

| V <sub>OUT0_CM</sub>           | AC common-mode voltage on OUT0± <sup>(1)</sup> | Default setting, PRBS31, 11.88 Gbps                                                             |     | 8       |       | mV (rms) |  |

| OUTPUT JITTE                   | ir                                             |                                                                                                 |     |         |       |          |  |

| ADDJ <sub>CD</sub>             | Additive jitter <sup>(1)</sup>                 | Measured at SDI_OUT1+ and SDI_OUT2+,<br>OUT0± disabled<br>PRBS10, 12G/6G/3G/HD/SD               |     | 0.03    |       | UI       |  |

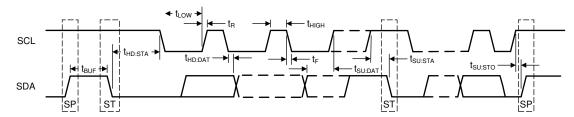

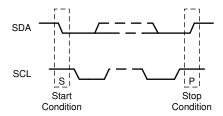

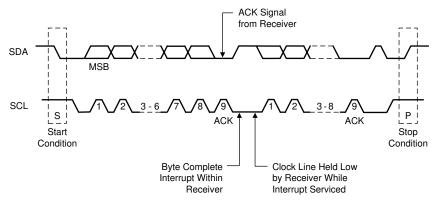

# 6.6 Recommended SMBus Interface Timing Specifications

over recommended operating supply and temperature ranges unless otherwise specified<sup>(1)</sup>

|                     | PARAMETER                                      | TEST CONDITIONS                                             | MIN | NOM M | ΔX | UNIT |

|---------------------|------------------------------------------------|-------------------------------------------------------------|-----|-------|----|------|

| F <sub>SCL</sub>    | SMBUS SCL frequency                            |                                                             | 10  | 4     | 00 | kHz  |

| T <sub>BUF</sub>    | Bus free time between stop and start condition | See Figure 1.                                               | 1.3 |       |    | μs   |

| T <sub>HD:STA</sub> | Hold time after (repeated) start condition     | After this period, the first clock is generated.            | 0.6 |       |    | μs   |

| T <sub>SU:STA</sub> | Repeated start condition setup time            | See Figure 1.                                               | 0.6 |       |    | μs   |

| T <sub>SU:STO</sub> | Stop condition setup time                      | See Figure 1.                                               | 0.6 |       |    | μs   |

| T <sub>HD:DAT</sub> | Data hold time                                 | See Figure 1.                                               | 0   |       |    | ns   |

| T <sub>SU:DAT</sub> | Data setup time                                | See Figure 1.                                               | 100 |       |    | ns   |

| T <sub>LOW</sub>    | Clock low period                               | See Figure 1.                                               | 1.3 |       |    | μs   |

| T <sub>HIGH</sub>   | Clock high period                              | See Figure 1.                                               | 0.6 |       |    | μs   |

| T <sub>R</sub>      | Clock and data rise time                       | See Figure 1.                                               |     | 3     | 00 | ns   |

| T <sub>F</sub>      | Clock and data fall time                       | See Figure 1.                                               |     | 3     | 00 | ns   |

| T <sub>POR</sub>    | SMBus ready time after POR                     | Time from minimum VDDIO to SMBus valid write or read access |     |       | 50 | ms   |

<sup>(1)</sup> These parameters support SMBus 2.0 specifications.

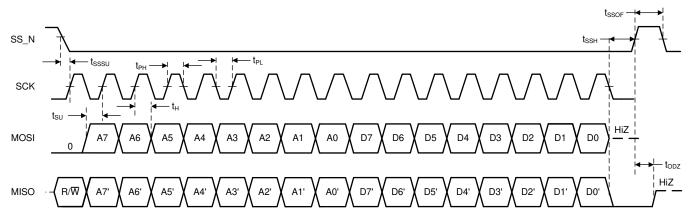

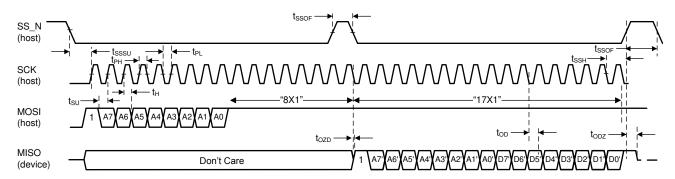

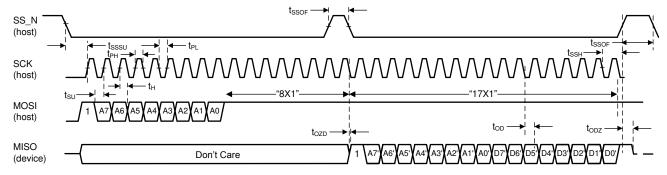

# 6.7 Serial Parallel Interface (SPI) Timing Specifications

over recommended operating supply and temperature ranges unless otherwise specified<sup>(1)</sup>

|                   | PARAMETER                    | TEST CONDITIONS           | MIN NO | XAM MC | UNIT         |

|-------------------|------------------------------|---------------------------|--------|--------|--------------|

| F <sub>SCK</sub>  | SPI SCK frequency            |                           |        | 20     | MHz          |

| T <sub>PH</sub>   | SCK pulse width high         | See Figure 2 and Figure 3 | 40     |        | % SCK period |

| T <sub>PL</sub>   | SCK pulse width low          | See Figure 2 and Figure 3 | 40     |        | % SCK period |

| $T_{SU}$          | MOSI setup time              | See Figure 2 and Figure 2 | 4      |        | ns           |

| T <sub>H</sub>    | MOSI hold time               | See Figure 2 and Figure 3 | 4      |        | ns           |

| T <sub>SSSU</sub> | SS setup time                |                           | 14     |        | ns           |

| T <sub>SSH</sub>  | SS hold time                 | See Figure 2 and Figure 3 | 4      |        | ns           |

| T <sub>SSOF</sub> | SS off time                  |                           | 1      |        | μs           |

| T <sub>ODZ</sub>  | MISO driven-to-tristate time |                           |        | 20     | ns           |

| T <sub>OZD</sub>  | MISO tristate-to-driven time | See Figure 2 and Figure 3 |        | 10     | ns           |

| T <sub>OD</sub>   | MISO output delay time       |                           | _      | 15     | ns           |

### (1) Typical SPI load capacitance is 2 pF.

Figure 1. SMBus Timing Parameters

Figure 2. SPI Timing Parameters (Write Operation)

Copyright © 2017–2020, Texas Instruments Incorporated

Submit Documentation Feedback

Figure 3. SPI Timing Parameters (Read Operation)

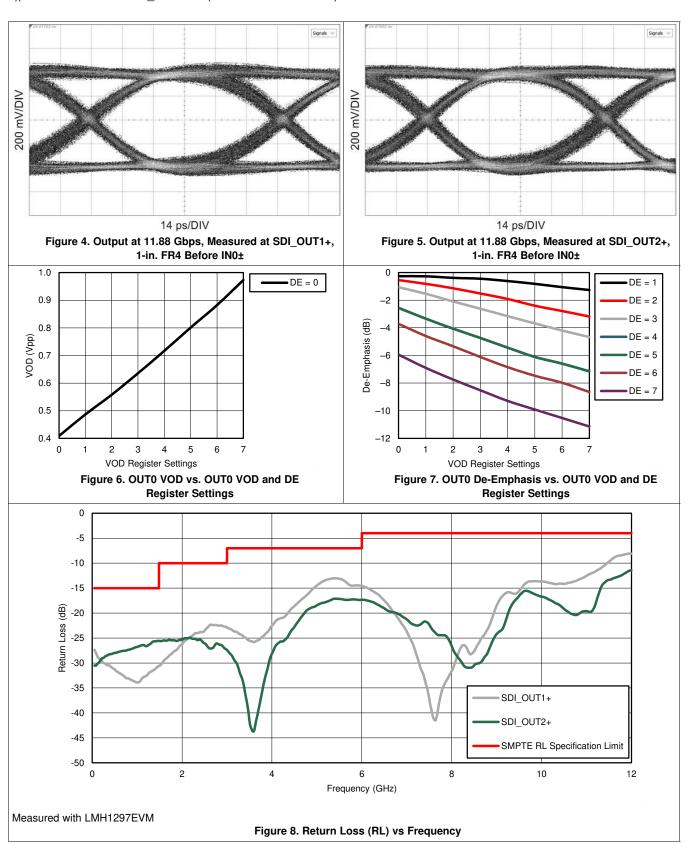

## 6.8 Typical Characteristics

$T_A = 25$ °C and VIN = RSV\_L = 2.5 V (unless otherwise noted)

## 7 Detailed Description

#### 7.1 Overview

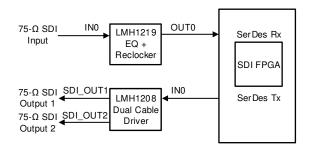

The LMH1208 is a 12G UHD-SDI dual output cable driver. From the host-side input at IN0 $\pm$ , the signal is equalized and routed to 75- $\Omega$  cable driver outputs at SDI\_OUT1+ and SDI\_OUT2+. The 100- $\Omega$  driver at OUT0 $\pm$  can be used as a host-side loop-back output for monitoring purposes.

## 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 9. LMH1208 Block Diagram Overview

Submit Documentation Feedback

### 7.3 Feature Description

The LMH1208 data path consists of several key blocks as shown in the functional block diagram. These key blocks are:

- 4-Level Input Pins and Thresholds

- OUT0 SEL and SDI OUT2 SEL Control

- Input Signal Detect

- Continuous Time Linear Equalizer (CTLE)

- Output Driver Control

- Status Indicators and Interrupts

## 7.3.1 4-Level Input Pins and Thresholds

The 4-level input configuration pins use a resistor divider to provide four logic states for each control pin. There is an internal  $30\text{-k}\Omega$  pullup and a  $60\text{-k}\Omega$  pulldown connected to the control pin that sets the default voltage at  $2/3 \times VIN$ . These resistors, together with the external resistor, combine to achieve the desired voltage level. By using the  $1\text{-k}\Omega$  pulldown,  $20\text{-k}\Omega$  pulldown, no connect, and  $1\text{-k}\Omega$  pullup, the optimal voltage levels for each of the four input states are achieved as shown in Table 1.

LEVELSETTINGNOMINAL PIN VOLTAGEHTie 1 k $\Omega$  to VINVINFFloat (leave pin open) $2/3 \times \text{VIN}$ RTie 20 k $\Omega$  to VSS $1/3 \times \text{VIN}$ LTie 1 k $\Omega$  to VSS0

**Table 1. 4-Level Control Pin Settings**

Typical 4-Level Input Thresholds:

- Internal Threshold between L and R = 0.2 x VIN

- Internal Threshold between R and F = 0.5 x VIN

- Internal Threshold between F and H = 0.8 x VIN

### 7.3.2 OUT0 SEL and SDI OUT2 SEL Control

The OUT0\_SEL and SDI\_OUT2\_SEL pins select the LMH1208 data-path routes. Table 2 shows all possible signal path combinations and typical use cases for each configuration.

Table 2. LMH1208 Signal Path Combinations

| OUT0_SEL | SDI_OUT2_SEL | INPUT | MAIN<br>OUTPUT | LINE SIDE<br>SECONDARY<br>OUTPUT | HOST SIDE<br>LOOP-BACK<br>OUTPUT | TYPICAL APPLICATION                                  |

|----------|--------------|-------|----------------|----------------------------------|----------------------------------|------------------------------------------------------|

| Н        | Н            | IN0±  | SDI_OUT1±      |                                  |                                  | Single cable driver                                  |

| Н        | L            | IN0±  | SDI_OUT1±      | SDI_OUT2±                        |                                  | Dual cable drivers                                   |

| L        | Н            | IN0±  | SDI_OUT1±      |                                  | OUT0±                            | Single cable driver with host-side loop-back enabled |

| L        | L            | IN0±  | SDI_OUT1±      | SDI_OUT2±                        | OUT0±                            | Dual cable drivers with host-side loop-back enabled  |

## 7.3.3 Input Signal Detect

INO has a signal detect circuit to monitor the presence or absence of an input signal. When the input signal amplitude for the selected input exceeds the signal detect assert threshold, the LMH1208 operates in normal operation mode.

In the absence of an input signal, the LMH1208 automatically goes into Power Save Mode to conserve power dissipation. When a valid signal is detected, the LMH1208 automatically exits Power Save Mode and returns to the normal operation mode. If the ENABLE pin is pulled low, the LMH1208 is forced into Power-Down Mode. In Power Save Mode, both the signal detect circuit and the serial interface remain active. In Power-Down Mode, only the serial interface remains active.

Users can monitor the status of the signal detect with the SD N pin or through register programming.

Table 3. Input Signal Detect Modes of Operation

| ENABLE | SIGNAL INPUT               | OPERATING MODE                                                         |

|--------|----------------------------|------------------------------------------------------------------------|

| Н      | 100-Ω signal input at IN0± | Normal operation<br>Signal Detector at IN0±<br>Serial interface active |

| Н      | No signal at IN0±          | Power Save Mode<br>Signal Detector at IN0±<br>Serial interface active  |

| L      | Input signal ignored       | Power-Down Mode<br>Forced device power down<br>Serial interface active |

#### 7.3.4 Continuous Time Linear Equalizer (CTLE)

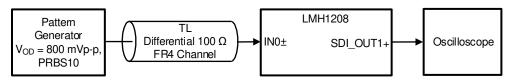

The LMH1208 has a continuous time linear equalizer (CTLE) block for IN0. The CTLE compensates for frequency-dependent loss due to the transmission media prior to the device input. The CTLE accomplishes this by applying variable gain to the input signal, thereby boosting higher frequencies more than lower frequencies. The CTLE block extends the signal bandwidth, restores the signal amplitude, and reduces ISI caused by the transmission medium.

IN0 has an on-chip  $100-\Omega$  termination and is designed for AC coupling, requiring a  $4.7-\mu F$ , AC-coupling capacitor for minimizing base-line wander. The PCB equalizer can compensate up to 20 inches of board trace at data rates up to 11.88 Gbps. There is one adapt mode for IN0: AM0 manual mode. In AM0 manual mode, fixed EQ boost settings are applied through user-programmable control.

The HOST\_EQ0 pin determines the IN0 adapt mode and EQ boost level. For normal operation, HOST\_EQ0 = F is recommended. HOST\_EQ0 pin logic settings are shown in Table 4. These HOST\_EQ0 pin settings can be overridden by register control. For more information, refer to the *LMH1228 and LMH1208 Programming Guide* (SNAU206).

Table 4. HOST EQ0 Pin EQ Settings

| HOST_EQ0 <sup>(1)</sup> | IN0± EQ BOOST                       | RECOMMENDED BOARD<br>TRACE IN0± <sup>(2)</sup> |

|-------------------------|-------------------------------------|------------------------------------------------|

| H, F                    | All Rates: AM0 Manual Mode, EQ=0x00 | < 1 inch                                       |

| R                       | All Rates: AM0 Manual Mode, EQ=0x80 | 10-15 inches                                   |

| L                       | All Rates: AM0 Manual Mode, EQ=0x90 | 20 inches                                      |

The HOST\_EQ0 pin is also used to set OUT0 VOD and de-emphasis values. See Host-Side 100-Ω

Output Driver (OUT0±) for more information.

#### 7.3.5 Output Driver Control

### 7.3.5.1 Line-Side Output Cable Driver (SDI\_OUT1+, SDI\_OUT2+)

The LMH1208 has two output cable driver (CD) blocks, one for SDI\_OUT1 and another for SDI\_OUT2. These SDI outputs are designed to drive  $75-\Omega$  single-ended coaxial cables at data rates up to 11.88 Gbps. Both SDI\_OUT1 and SDI\_OUT2 feature an integrated  $75-\Omega$  termination and return loss compensation network for meeting stringent SMPTE return loss requirements (see Figure 8). The cable drivers are designed for AC coupling, requiring a  $4.7-\mu F$ , AC-coupling capacitor for minimizing base-line wander due to the rare-occurring pathological bit pattern.

## 7.3.5.1.1 Output Amplitude (VOD)

SDI\_OUT1 and SDI\_OUT2 are designed for transmission across 75-Ω single-ended impedance. The nominal SDI cable driver output amplitude (VOD) is 800 mVp-p single-ended. In the presence of long output cable lengths or crosstalk, the SDI\_VOD pin can be used to optimize the cable driver output with respect to the nominal amplitude. Table 5 details VOD settings that can be applied to both SDI\_OUT1 and SDI\_OUT2. The SDI\_VOD pin can be overridden through register control. In addition, the nominal VOD amplitude can be changed by register control. For more information, refer to the *LMH1228 and LMH1208 Programming Guide* (SNAU206).

<sup>(2)</sup> Recommended board trace at 11.88 Gbps.

Table 5. SDI\_VOD Settings for Line-Side Output Amplitude

| SDI_VOD | DESCRIPTION           |

|---------|-----------------------|

| Н       | about +5% of nominal  |

| F       | 800 mVp-p (nominal)   |

| R       | about +10% of nominal |

| L       | about -5% of nominal  |

#### 7.3.5.1.2 Output Pre-Emphasis

In addition to SDI cable driver VOD control, the LMH1208 can add pre-emphasis on the cable driver output to improve output signal integrity at a UHD (12G, 6G) or HD (3G, 1.5G) input data rate. By default, pre-emphasis is enabled based on the SLEW CTRL pin setting shown in Table 6.

Table 6. SLEW\_CTRL Settings for SDI\_OUT1 and SDI\_OUT2 Pre-Emphasis

| SLEW_CTRL | OUTPUT PRE-EMPHASIS   | DATA RATE                         |

|-----------|-----------------------|-----------------------------------|

| Н         | Enabled               | UHD: 11.88 Gbps<br>UHD: 5.94 Gbps |

| F         | Disabled              | HD: 2.97 Gbps<br>HD: 1.485 Gbps   |

| R, L      | Disabled SD: 270 Mbps |                                   |

When enabled, the amount of pre-emphasis applied to cable driver outputs is determined by register control. When disabled, no pre-emphasis is applied. Pre-emphasis control can be overridden for select or all data rates through register control. For more information, refer to the *LMH1228 and LMH1208 Programming Guide* (SNAU206).

#### 7.3.5.1.3 Output Slew Rate

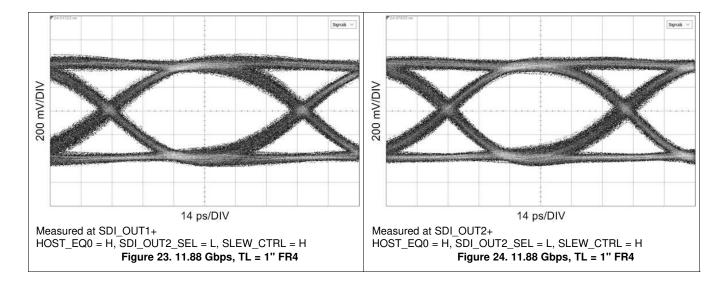

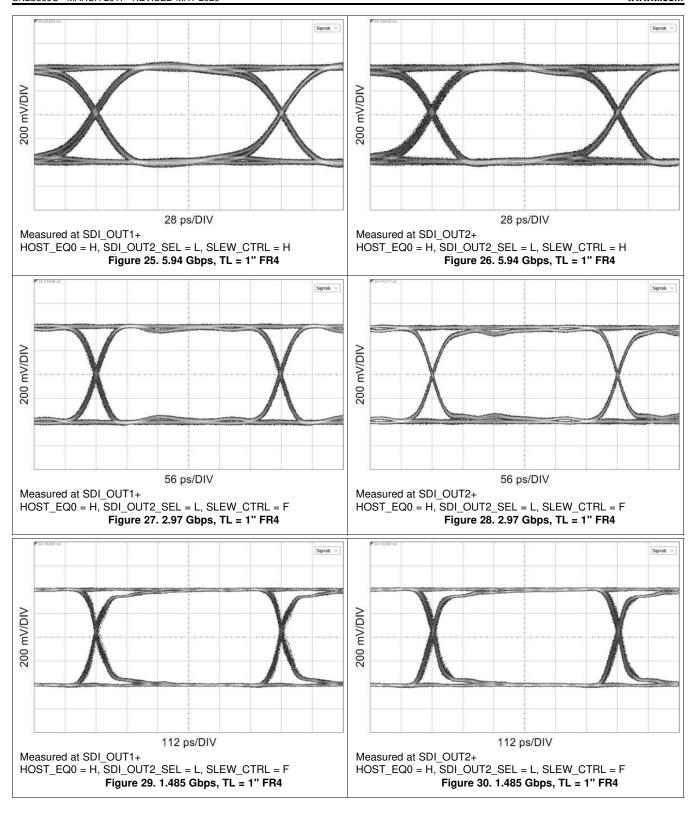

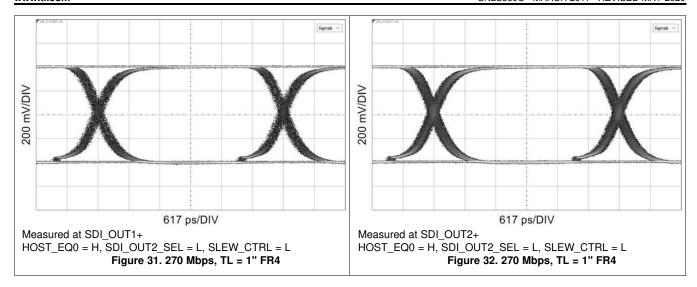

SMPTE specifications require different output driver rise and fall times depending on the operating data rate. To meet these requirements, the output edge rate of SDI\_OUT1 and SDI\_OUT2 can be configured by the SLEW\_CTRL pin. Table 7 shows the recommended SLEW\_CTRL pin logic setting and typical edge rate at the cable driver output for each data rate.

Table 7. SLEW CTRL Settings for SDI OUT1 and SDI OUT2 Output Edge Rate

| SLEW_CTRL     | DATA RATE  | CABLE DRIVER OUTPUT<br>EDGE RATE (TYP) |

|---------------|------------|----------------------------------------|

| 11            | 11.88 Gbps | 34 ps                                  |

| Н             | 5.94 Gbps  | 36 ps                                  |

| г             | 2.97 Gbps  | 59 ps                                  |

| F             | 1.485 Gbps | 60 ps                                  |

| R, L 270 Mbps |            | 550 ps                                 |

Users can also program the desired edge rate manually through register control. For more information, refer to the *LMH1228 and LMH1208 Programming Guide* (SNAU206).

## 7.3.5.1.4 Output Polarity Inversion

Polarity inversion is supported on both SDI\_OUT1 and SDI\_OUT2 outputs through register control.

### 7.3.5.2 Host-Side 100-Ω Output Driver (OUT0±)

OUT0 is a  $100-\Omega$  driver output. OUT0 serves as a host-side loop-back output. OUT0 also supports polarity inversion.

The driver offers users the capability to select higher output amplitude and de-emphasis levels for longer board trace that connects the drivers to their downstream receivers. Driver de-emphasis provides transmitter equalization to reduce the ISI caused by the board trace.

The VOD and de-emphasis levels for OUT0 are set by default to 570 mVp-p and -0.4 dB, and these values are recommended for driving 1-2 inches of board trace from OUT0± at 11.88 Gbps. These settings can be changed through register control if desired. When these parameters are controlled by registers, the VOD and de-emphasis levels can be programmed independently. For more information, refer to the *LMH1228 and LMH1208 Programming Guide* (SNAU206).

#### 7.3.6 Status Indicators and Interrupts

The SD\_N pin is a 3.3-V tolerant, active-low, open-drain output. An external resistor to the logic supply is required. The SD\_N pin can be configured to indicate input signal detect or an interrupt event.

#### 7.3.6.1 SD\_N (Signal Detect)

By default, SD\_N indicates a SD\_N (signal detect) event, and this pin asserts low after a valid signal is detected by the IN0 signal detect circuit. For more information about how to reconfigure the SD\_N pin functionality, refer to the *LMH1228 and LMH1208 Programming Guide* (SNAU206).

### 7.3.6.2 INT\_N (Interrupt)

The SD\_N pin can be configured to indicate an INT\_N (interrupt) event. When configured as an INT\_N output, the pin asserts low when an interrupt occurs, according to the programmed interrupt masks. Two separate masks can be programmed through register control as interrupt sources:

• If there is a loss of signal (LOS) event on IN0 (2 separate masks).

INT\_N is a sticky bit, meaning that it will flag after an interrupt occurs and will not clear until read-back. Once the Interrupt Status Register is read, the INT\_N pin will assert high again. For more information about how to configure the SD\_N pin for INT\_N functionality, refer to the *LMH1228 and LMH1208 Programming Guide* (SNAU206).

#### 7.4 Device Functional Modes

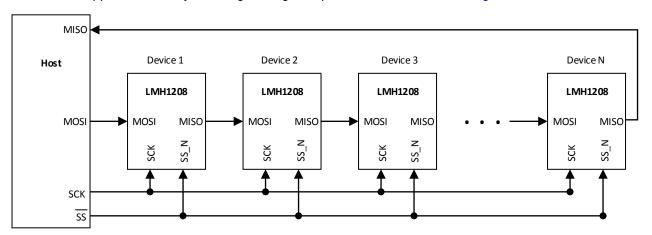

The LMH1208 operates in one of two modes: System Management Bus (SMBus) or Serial Peripheral Interface (SPI) mode. To determine the mode of operation, the proper setting must be applied to the MODE SEL pin at power up, as detailed in Table 8.

Table 8. MODE SEL Pin Settings

| LEVEL | DESCRIPTION                                 |  |

|-------|---------------------------------------------|--|

| Н     | Reserved for factory testing – do not use   |  |

| F     | Selects SPI Interface for register access   |  |

| R     | Reserved for factory testing – do not use   |  |

| L     | Selects SMBus Interface for register access |  |

### 7.4.1 System Management Bus (SMBus) Mode

The SMBus interface can also be used to control the device. If MODE SEL = Low (1 k $\Omega$  to VSS), Pins 13 and 29 are configured as SDA and SCL. Pins 11 and 28 are address straps ADDR0 and ADDR1 during power up. The maximum operating speed supported on the SMBUS pins is 400 kHz.

Table 9. SMBus Device Slave Addresses<sup>(1)</sup>

| ADDR0<br>(LEVEL) | ADDR1<br>(LEVEL) | 7-BIT SLAVE<br>ADDRESS [HEX] | 8-BIT WRITE<br>COMMAND [HEX] |

|------------------|------------------|------------------------------|------------------------------|

| L                | L                | 2D                           | 5A                           |

| L                | R                | 2E                           | 5C                           |

| L                | F                | 2F                           | 5E                           |

| L                | Н                | 30                           | 60                           |

| R                | L                | 31                           | 62                           |

| R                | R                | 32                           | 64                           |

| R                | F                | 33                           | 66                           |

| R                | Н                | 34                           | 68                           |

| F                | L                | 35                           | 6A                           |

| F                | R                | 36                           | 6C                           |

| F                | F                | 37                           | 6E                           |

| F                | Н                | 38                           | 70                           |

| Н                | L                | 39                           | 72                           |

| Н                | R                | 3A                           | 74                           |

| Н                | F                | 3B                           | 76                           |

| Н                | Н                | 3C                           | 78                           |

<sup>(1)</sup> The 8-bit write command consists of the 7-bit slave address (Bits 7:1) with 0 appended to the LSB to indicate an SMBus write. For example, if the 7-bit slave address is 0x2D (010 1101'b), the 8-bit write command is 0x5A (0101 1010'b).

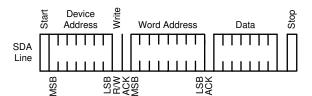

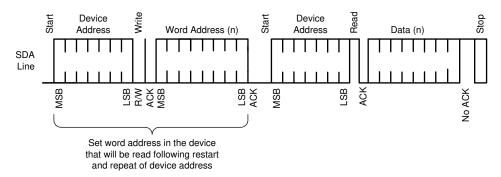

#### 7.4.1.1 SMBus Read and Write Transaction

Copyright © 2017-2020, Texas Instruments Incorporated

SMBus is a two-wire serial interface through which various system component chips can communicate with the master. Slave devices are identified by having a unique device address. The two-wire serial interface consists of SCL and SDA signals. SCL is a clock output from the master to all of the slave devices on the bus. SDA is a bidirectional data signal between the master and slave devices. The LMH1208 SMBus SCL and SDA signals are open-drain and require external pullup resistors.

### Start and Stop:

The master generates Start and Stop patterns at the beginning and end of each transaction.

- Start: High-to-low transition (falling edge) of SDA while SCL is high.

- Start: High-to-low transition (falling edge) of SDA while SCL is high.

Figure 10. Start and Stop Conditions