# V850E/IG4-H, V850E/IH4-H

User's Manual: Hardware

**RENESAS MCU** V850E/Ix4-H Microcontrollers

V850E/IG4-H:

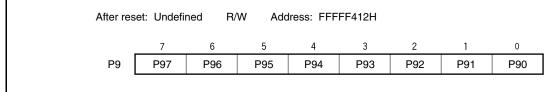

μPD70F3919

μPD70F3920

μPD70F3921

V850E/IH4-H:

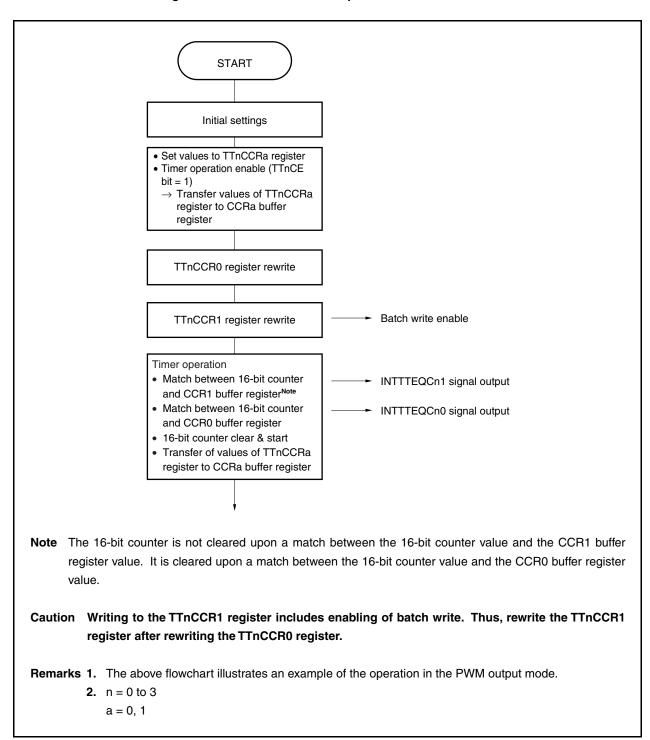

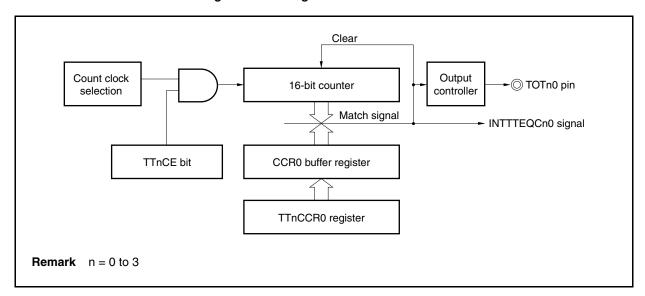

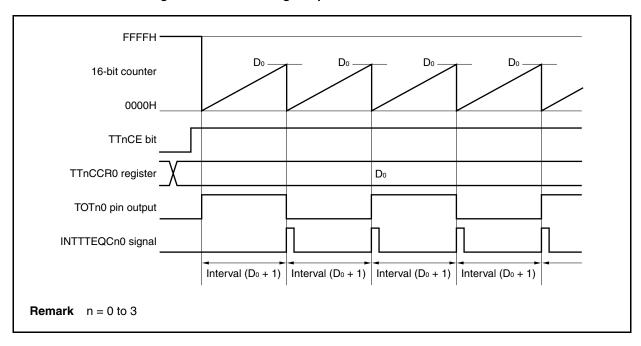

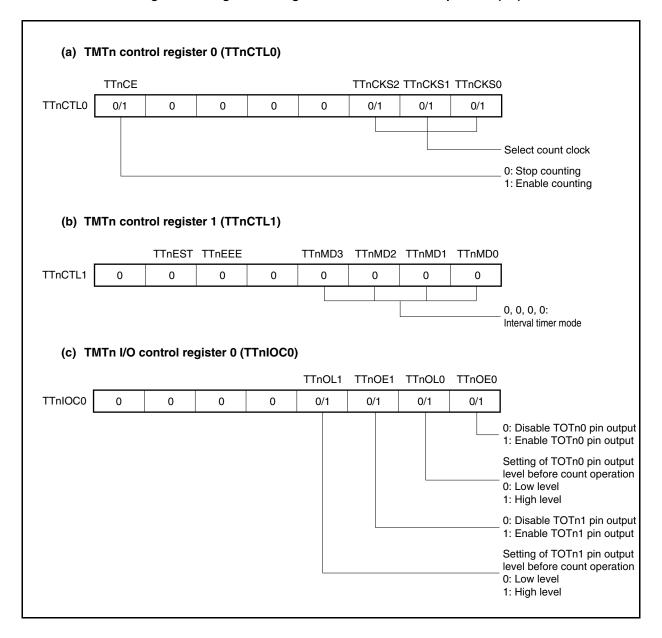

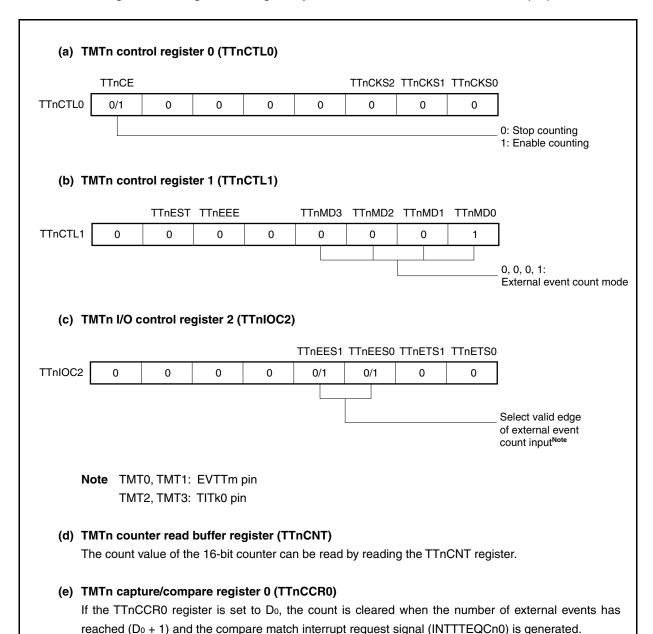

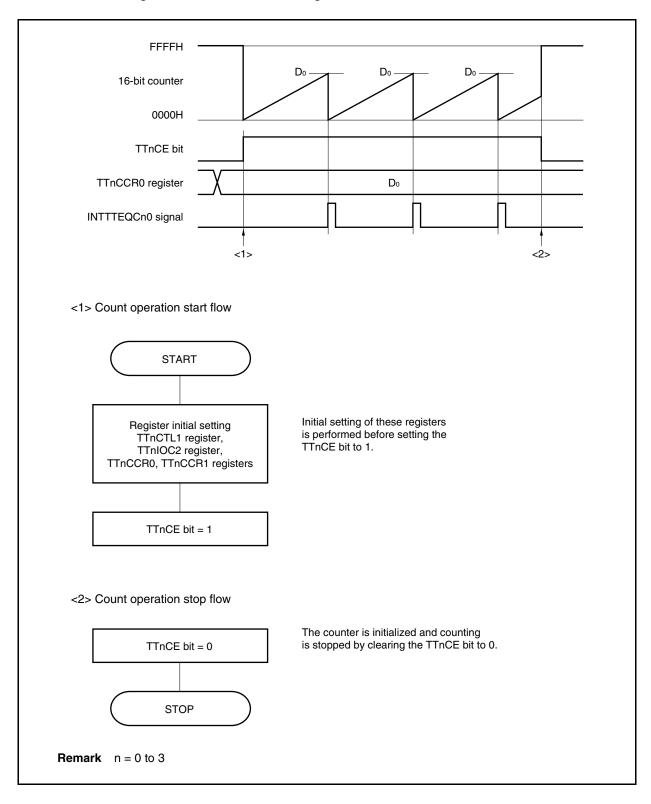

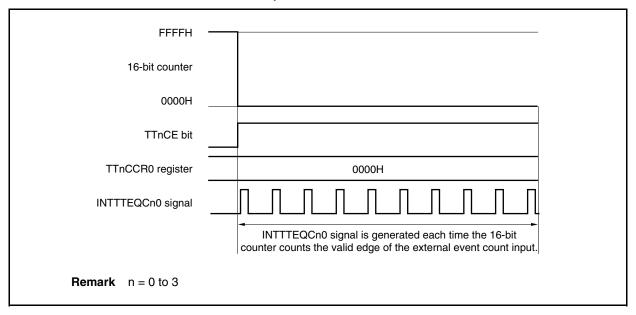

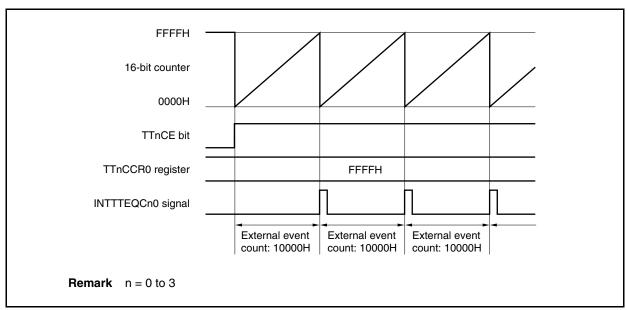

μPD70F3922

μPD70F3923

μPD70F3924

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

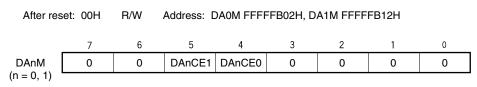

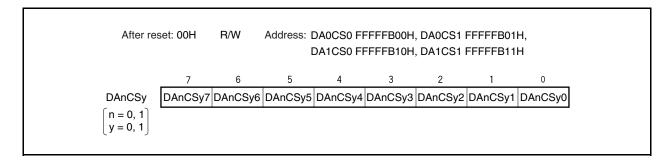

## Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### NOTES FOR CMOS DEVICES -

## (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

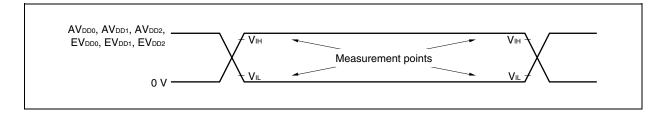

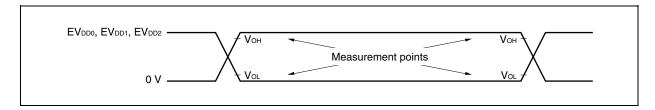

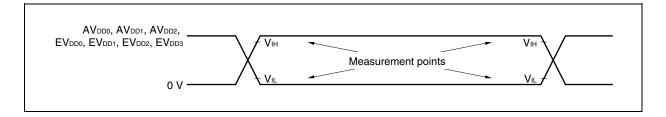

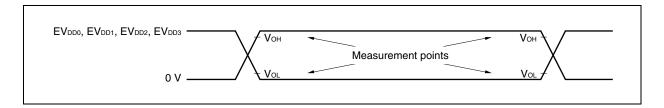

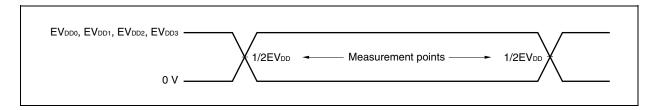

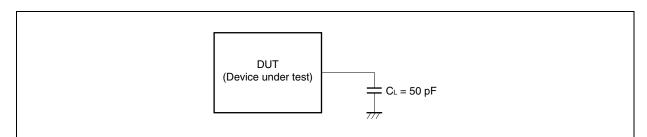

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

## (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### ③ PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

## **4** STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

## **5** POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### (6) INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

## How to Use This Manual

Readers

This manual is intended for users who wish to understand the functions of the V850E/IG4-H ( $\mu$ PD70F3919, 70F3920, 70F3921) and V850E/IH4-H ( $\mu$ PD70F3922, 70F3923, 70F3924) and design application systems using the V850E/IG4-H and V850E/IH4-H.

**Purpose**

This manual is intended to give users an understanding of the hardware functions of the V850E/IG4-H and V850E/IH4-H shown in the Organization below.

Organization

This manual is divided into two parts: Hardware (this manual) and Architecture (V850E1 Architecture User's Manual).

#### Hardware

- Pin functions

- CPU function

- On-chip peripheral functions

- Flash memory programming

- Electrical specifications

#### Architecture

- · Data types

- Register set

- Instruction format and instruction set

- Interrupts and exceptions

- Pipeline operation

How to Read This Manual It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

To understand the overall functions of the V850E/IG4-H and V850E/IH4-H

→ Read this manual according to the CONTENTS.

To find the details of a register where the name is known

→ See APPENDIX B REGISTER INDEX.

## Register format

→ The name of the bit whose number is in angle brackets (<>) in the figure of the register format of each register is defined as a reserved word in the device file.

To understand the details of an instruction function

→ Refer to the V850E1 Architecture User's Manual.

To know the electrical specifications of the V850E/IG4-H and V850E/IH4-H

→ See CHAPTER 28 ELECTRICAL SPECIFICATIONS.

The "yyy bit of the xxx register" is described as the "xxx.yyy bit" in this manual. Note with caution that even if "xxx.yyy" is described as is in a program, however, the compiler/assembler cannot recognize it correctly.

The mark <R> shows major revised points.

The revised points can be easily searched by copying an "<R>" in the PDF file and specifying it in the "Find what:" field.

#### Conventions

Data significance: Higher digits on the left and lower digits on the right

Active low representation: xxx (overscore over pin or signal name)

Memory map address: Higher addresses on the top and lower addresses on the

bottom

Note: Footnote for item marked with Note in the text Caution: Information requiring particular attention

**Remark**: Supplementary information

Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory capacity):

K (kilo):  $2^{10} = 1,024$ M (mega):  $2^{20} = 1,024^2$ G (giga):  $2^{30} = 1,024^3$ Word ... 32 bits

Data type: Word ... 32 bits

Halfword ... 16 bits

Byte ... 8 bits

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

## Documents related to V850E/IG4-H and V850E/IH4-H

| Document Name                                   | Document No. |

|-------------------------------------------------|--------------|

| V850E1 Architecture User's Manual               | U14559E      |

| V850E/IG4-H, V850E/IH4-H Hardware User's Manual | This manual  |

## Documents related to development tools (user's manuals)

| Document Nam                               | Document No.        |         |

|--------------------------------------------|---------------------|---------|

| QB-V850MINI On-Chip Debug Emulator         | U17638E             |         |

| QB-MINI2 On-Chip Debug Emulator with Pro   | gramming Function   | U18371E |

| QB-Programmer Programming GUI              | Operation           | U18527E |

| CA850 Ver. 3.20 C Compiler Package         | Operation           | U18512E |

|                                            | C Language          | U18513E |

|                                            | Assembly Language   | U18514E |

|                                            | Link Directives     | U18515E |

| PM+ Ver. 6.30 Project Manager              |                     | U18416E |

| ID850QB Ver. 3.40 Integrated Debugger      | U18604E             |         |

| TW850 Ver. 2.00 Performance Analysis Tunir | ng Tool             | U17241E |

| SM+ System Simulator                       | Operation           | U18601E |

|                                            | User Open Interface | U18212E |

| RX850 Ver. 3.20 Real-Time OS               | Basics              | U13430E |

|                                            | Installation        | U17419E |

|                                            | Technical           | U13431E |

|                                            | Task Debugger       | U17420E |

| RX850 Pro Ver. 3.21 Real-Time OS           | Basics              | U18165E |

|                                            | In-Structure        | U18164E |

|                                            | Task Debugger       | U17422E |

| AZ850 Ver. 3.30 System Performance Analyz  | er                  | U17423E |

| PG-FP4 Flash Memory Programmer             |                     | U15260E |

| PG-FP5 Flash Memory Programmer             | U18865E             |         |

**Remark** The in-circuit emulator is a product of Midas lab Inc. For details, contact Midas lab.

#### Other Documents

| Document Name                                                                      | Document No. |

|------------------------------------------------------------------------------------|--------------|

| RENESAS MICROCOMPUTER GENERAL CATALOG                                              | R01CS0001E   |

| Semiconductor Device Mount Manual                                                  | Note         |

| Quality Grades on NEC Semiconductor Devices                                        | C11531E      |

| NEC Semiconductor Device Reliability/Quality Control System                        | C10983E      |

| Guide to Prevent Damage for Semiconductor Devices by Electrostatic Discharge (ESD) | C11892E      |

**Note** See the "Semiconductor Device Mount Manual" website (http://www.renesas.com/prod/package/manual/index.html).

Caution The related documents listed above are subject to change without notice. Be sure to use the latest version of each document when designing.

Caution: This product uses SuperFlash® technology licensed from Silicon Storage Technology, Inc.

**EEPROM** is a trademark of Renesas Electronics Corporation.

MINICUBE is a registered trademark of Renesas Electronics Corporation in Japan and Germany or a trademark in the United States of America.

SuperFlash is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

## **CONTENTS**

| CHAPTE | ER 1 INTRODUCTION                                          | 20 |

|--------|------------------------------------------------------------|----|

| 1.1    | Overview                                                   | 20 |

| 1.2    | Features                                                   | 22 |

| 1.3    | Application Fields                                         | 24 |

| 1.4    | Ordering Information                                       | 24 |

|        | 1.4.1 V850E/IG4-H                                          | 24 |

|        | 1.4.2 V850E/IH4-H                                          | 24 |

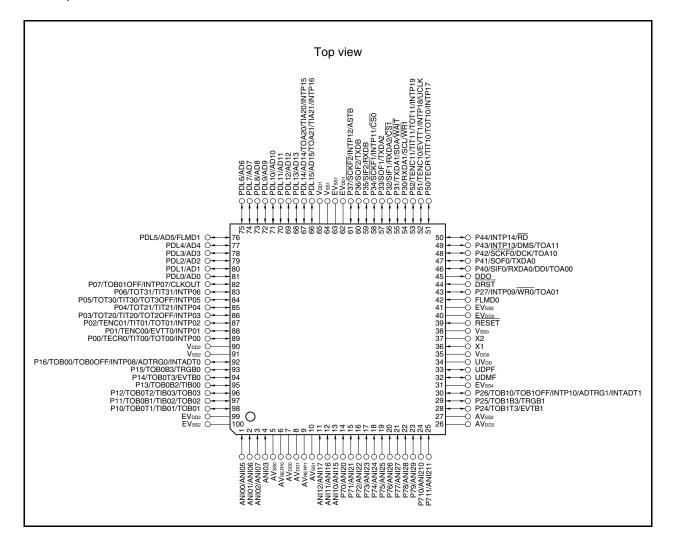

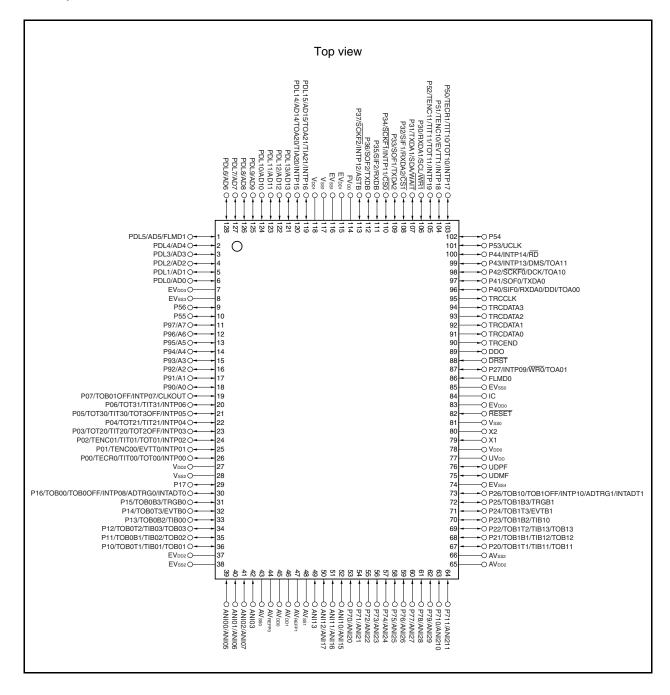

| 1.5    | Pin Configuration                                          | 25 |

|        | 1.5.1 V850E/IG4-H                                          | 25 |

|        | 1.5.2 V850E/IH4-H                                          | 27 |

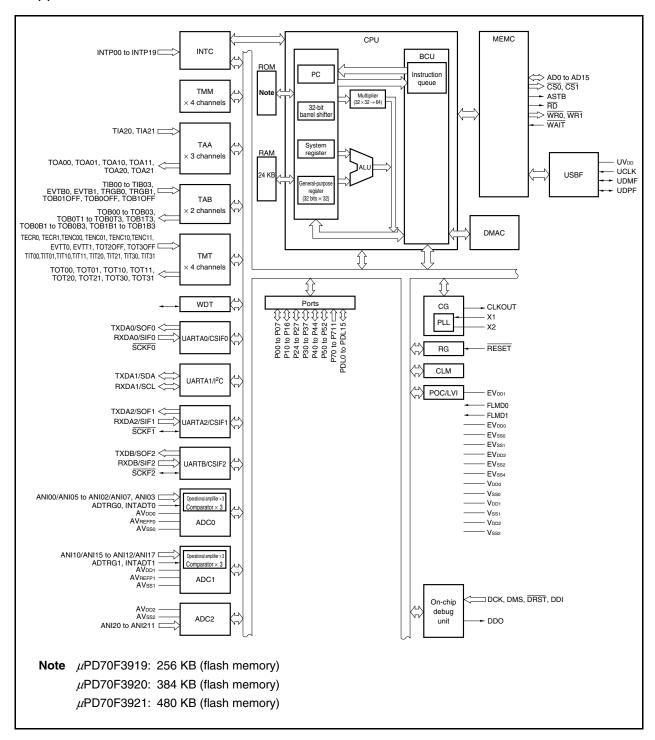

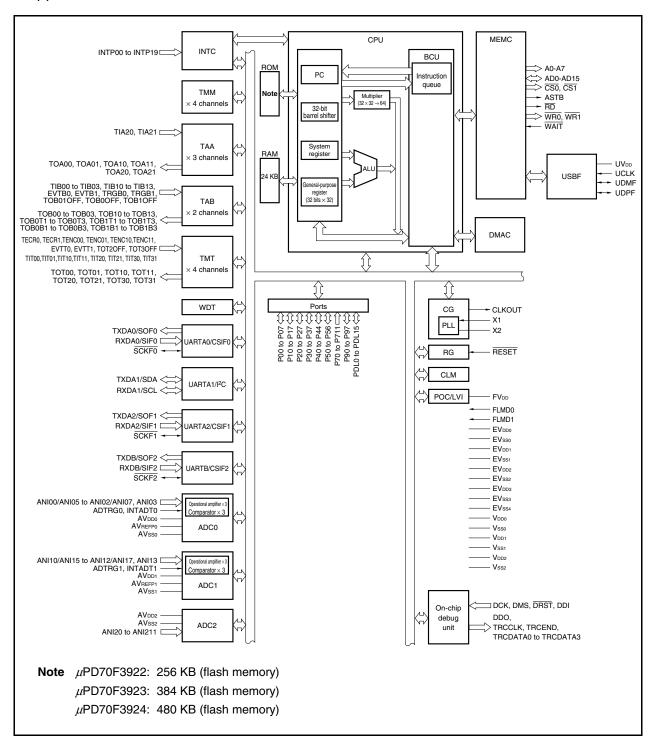

| 1.6    | Function Blocks                                            | 29 |

|        | 1.6.1 Internal block diagrams                              | 29 |

|        | 1.6.2 Internal units                                       | 31 |

|        |                                                            |    |

| СНАРТЕ | ER 2 PIN FUNCTIONS                                         | 33 |

| 2.1    | List of Pin Functions                                      | 33 |

| 2.2    | Pin I/O Circuits and Recommended Connection of Unused Pins | 45 |

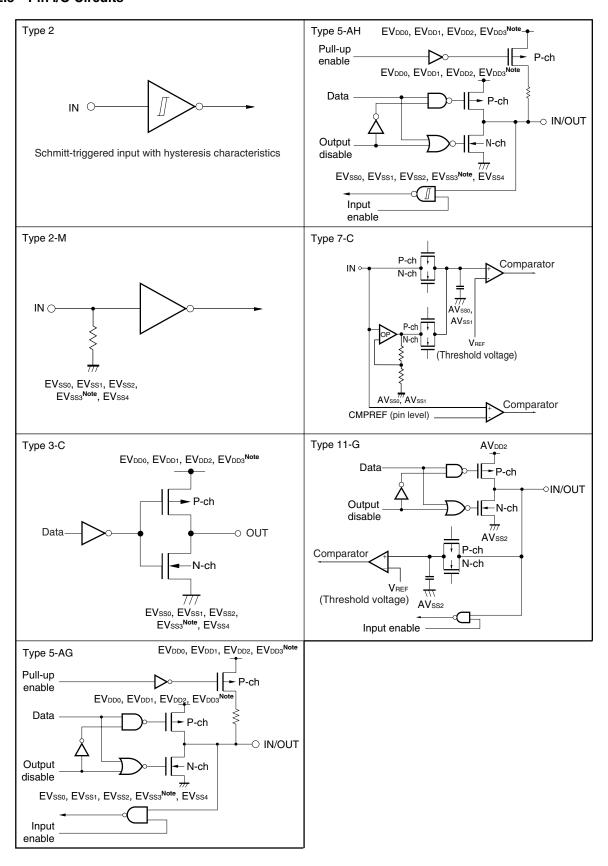

| 2.3    | Pin I/O Circuits                                           | 49 |

|        |                                                            |    |

| CHAPTE | ER 3 CPU FUNCTION                                          | 50 |

| 3.1    | Features                                                   | 50 |

| 3.2    | CPU Register Set                                           | 51 |

|        | 3.2.1 Program register set                                 | 52 |

|        | 3.2.2 System register set                                  | 53 |

| 3.3    | Operating Modes                                            | 59 |

|        | 3.3.1 Operating modes                                      | 59 |

|        | 3.3.2 Operating mode specification                         | 59 |

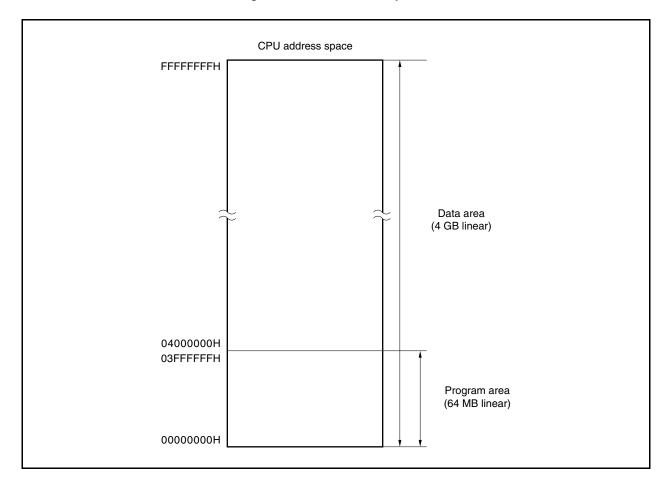

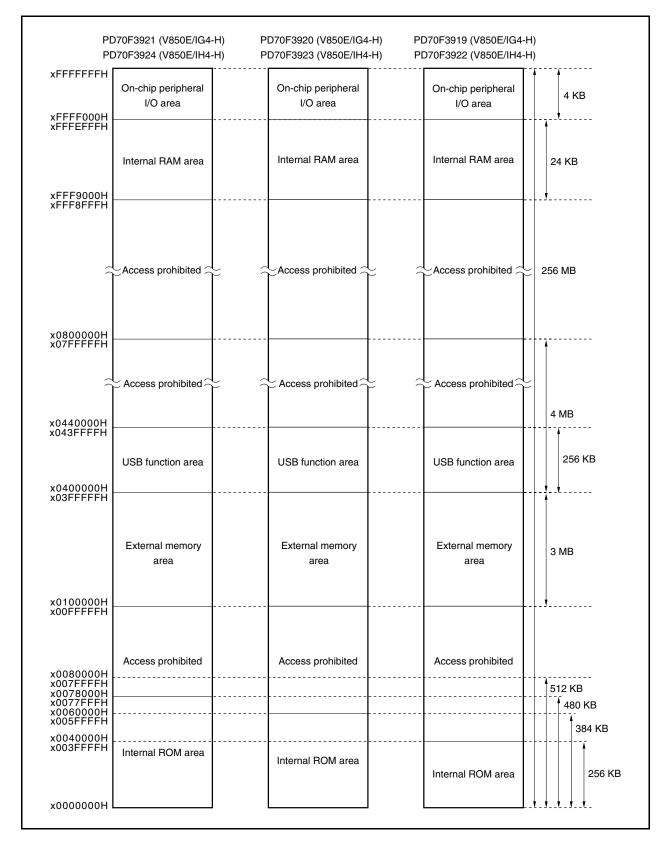

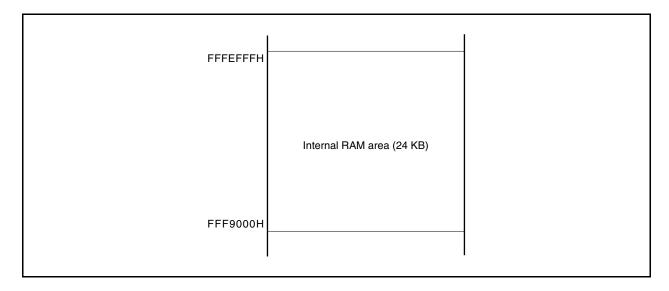

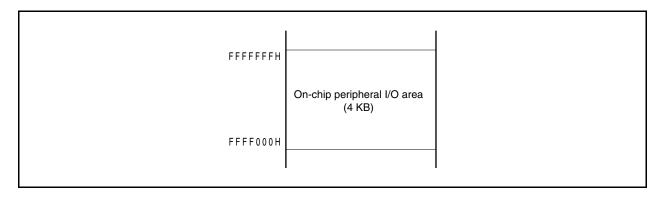

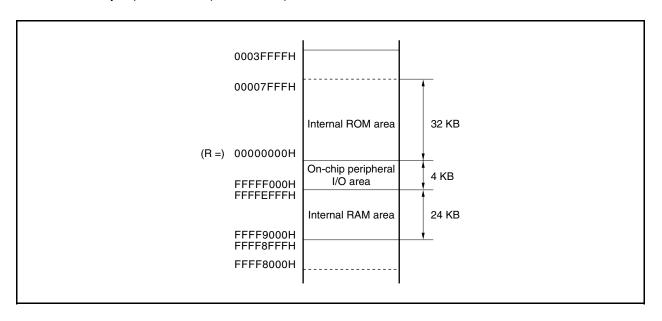

| 3.4    | Address Space                                              | 60 |

|        | 3.4.1 CPU address space                                    | 60 |

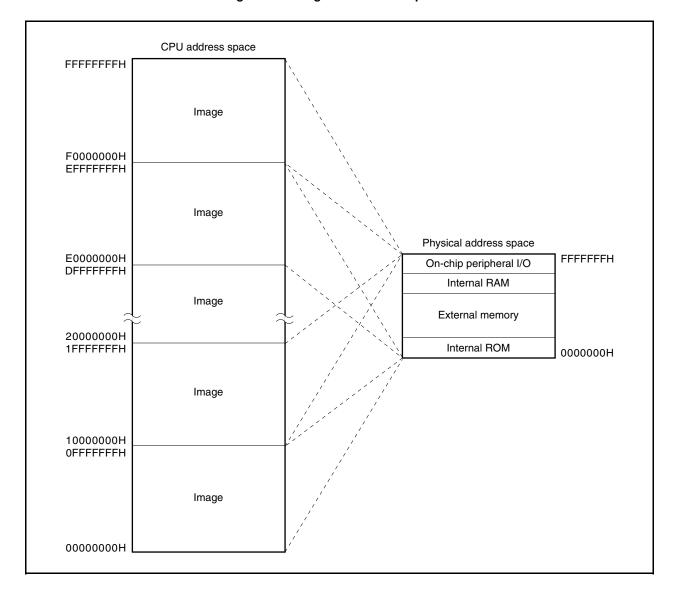

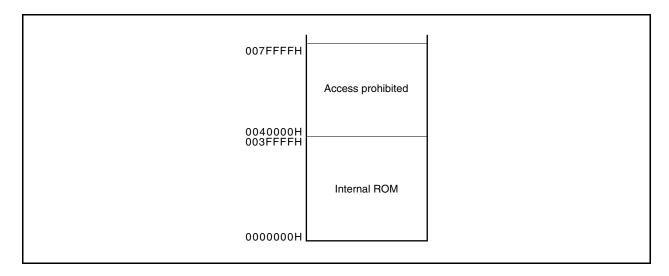

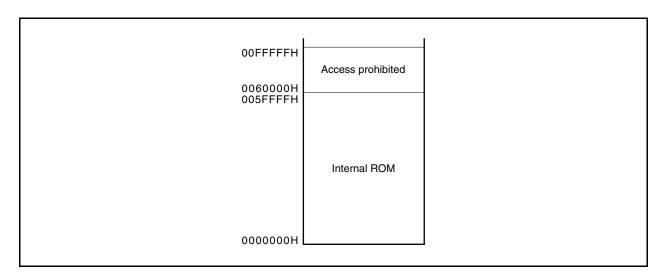

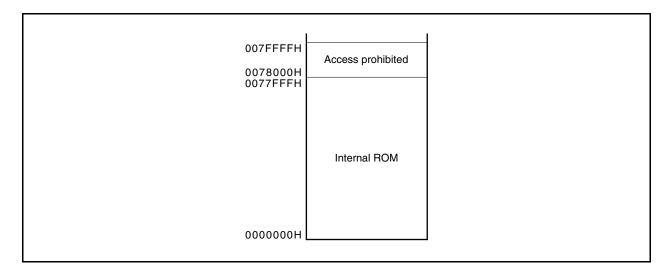

|        | 3.4.2 Image                                                | 61 |

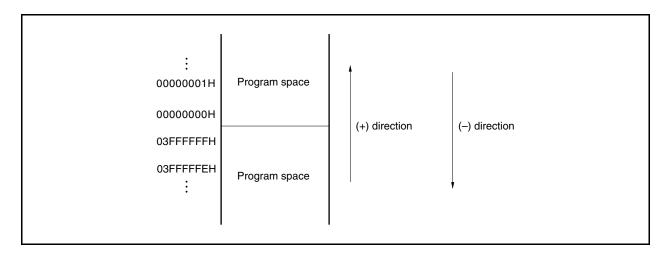

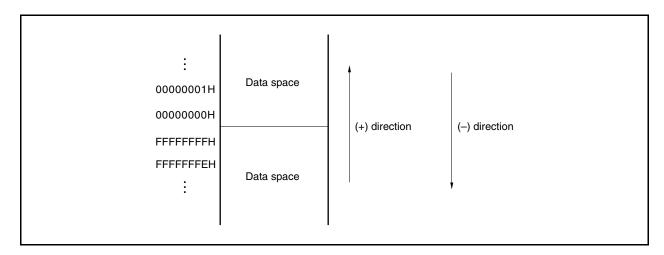

|        | 3.4.3 Wraparound of CPU address space                      | 62 |

|        | 3.4.4 Memory map                                           | 63 |

|        | 3.4.5 Areas                                                | 64 |

|        | 3.4.6 Recommended use of address space                     |    |

|        | 3.4.7 On-chip peripheral I/O registers                     | 69 |

|        | 3.4.8 Special registers                                    |    |

|        | 3.4.9 System wait control register (VSWC)                  | 91 |

|        | 3.4.10 DMA wait control registers 0, 1 (DMAWC0, DMAWC1)    | 91 |

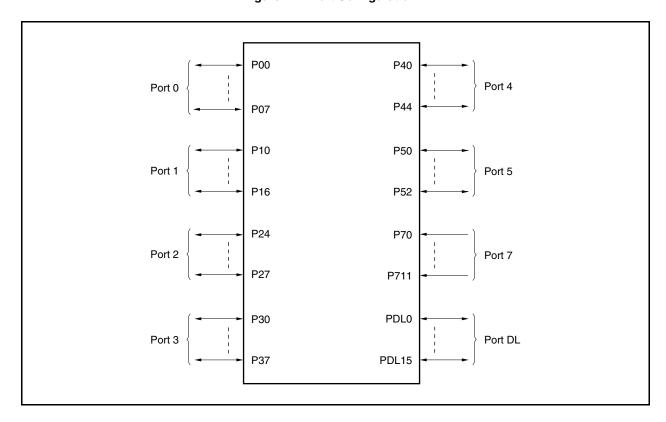

| CHAPTE | ER 4 PORT FUNCTIONS                                        | 92 |

| 4.1    | Features                                                   | 92 |

|        | 4.1.1 V850E/IG4-H                                          | 92 |

|            | 4.1.2 V85   | 50E/IH4-H                                                       | 92  |

|------------|-------------|-----------------------------------------------------------------|-----|

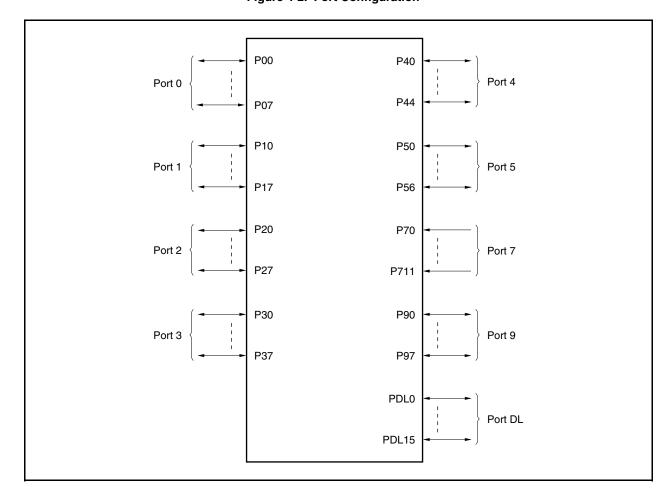

| 4.2        | Port Config | guration                                                        | 93  |

|            | 4.2.1 V85   | 50E/IG4-H                                                       | 93  |

|            | 4.2.2 V85   | 50E/IH4-H                                                       | 94  |

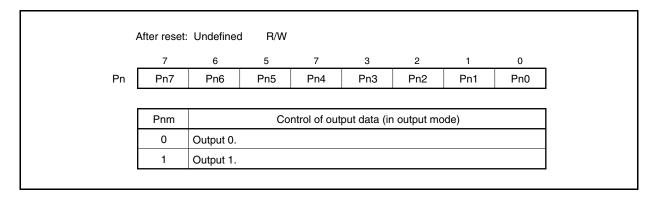

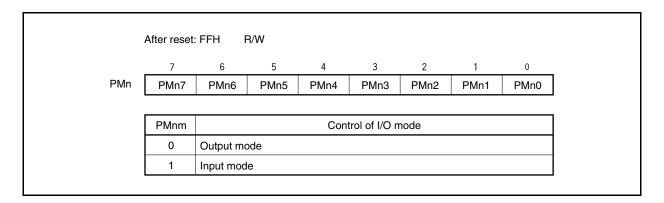

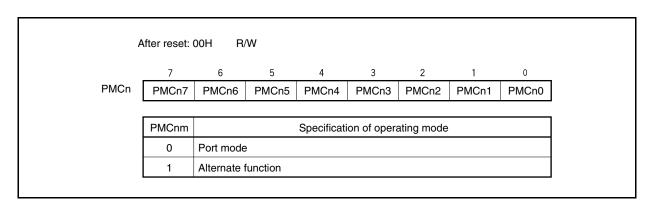

| 4.3        | Port Config | guration                                                        | 95  |

|            | 4.3.1 Por   | rt 0                                                            | 100 |

|            | 4.3.2 Por   | rt 1                                                            | 106 |

|            | 4.3.3 Por   | rt 2                                                            | 112 |

|            | 4.3.4 Por   | rt 3                                                            | 118 |

|            | 4.3.5 Por   | rt 4                                                            | 124 |

|            | 4.3.6 Por   | rt 5                                                            | 129 |

|            | 4.3.7 Por   | rt 7                                                            | 134 |

|            | 4.3.8 Por   | rt 9 (V850E/IH4-H only)                                         | 136 |

|            | 4.3.9 Por   | rt DL                                                           | 140 |

| 4.4        | Output Dat  | ta and Port Read Value for Each Setting                         | 146 |

| 4.5        | Port Regis  | ter Settings When Alternate Function Is Used                    | 159 |

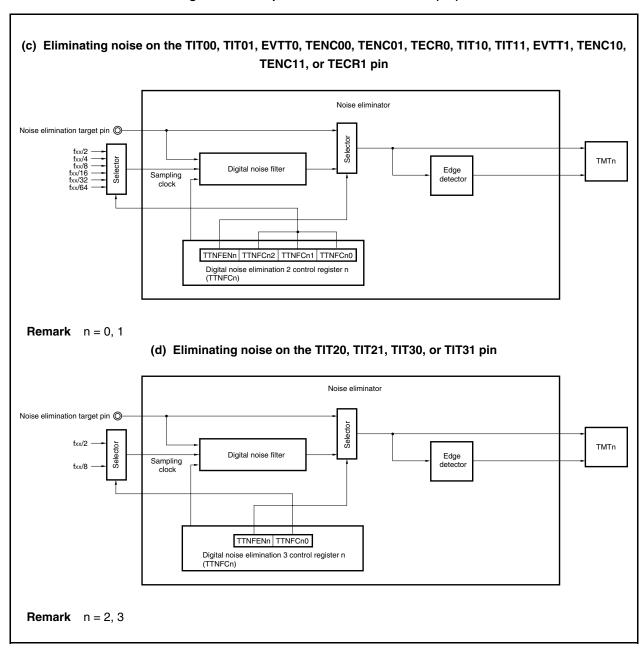

| 4.6        | Noise Elim  | ninator                                                         | 168 |

| 4.7        | Cautions    |                                                                 | 179 |

|            | 4.7.1 Ca    | utions on setting port pins                                     | 179 |

|            | 4.7.2 Ca    | utions on bit manipulation instruction for port n register (Pn) | 180 |

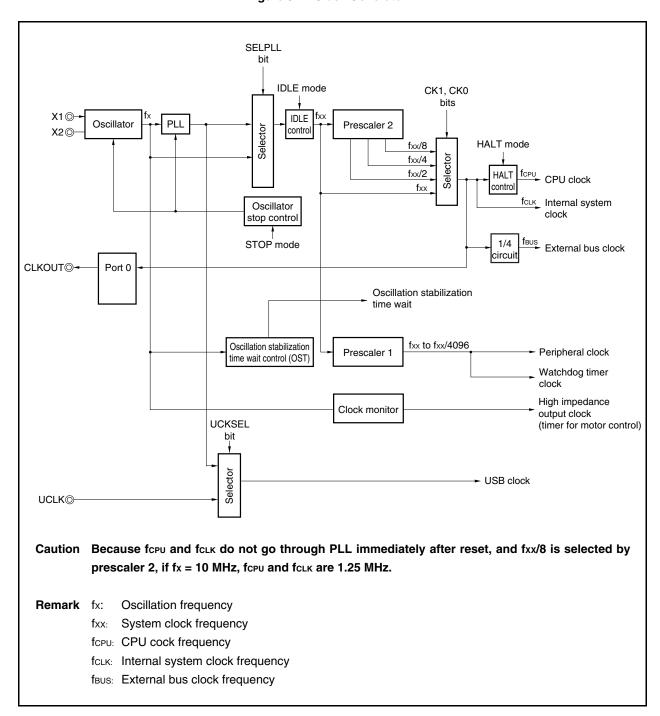

| CHAPTI     | R 5 CLOCI   | K GENERATOR                                                     | 181 |

| 5.1        | Overview    |                                                                 | 101 |

| 5.1<br>5.2 |             | tion                                                            |     |

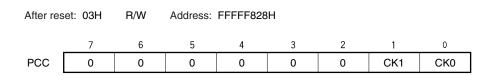

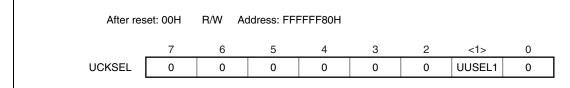

| 5.2<br>5.3 | •           | egisters                                                        |     |

| 5.4        |             | ion                                                             |     |

| 5.4        |             | erview                                                          |     |

|            |             | L mode                                                          | _   |

|            |             |                                                                 |     |

| 5.5        |             | ck-through mode                                                 |     |

| 3.3        | •           | eration of each clock                                           |     |

|            | •           | ock output function                                             |     |

|            |             | eration timing                                                  |     |

| 5.6        | •           | itor                                                            |     |

| 3.0        | CIOCK MOII  |                                                                 | 190 |

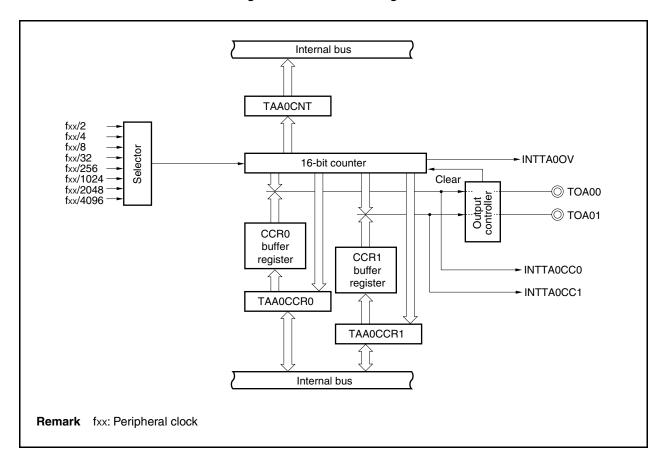

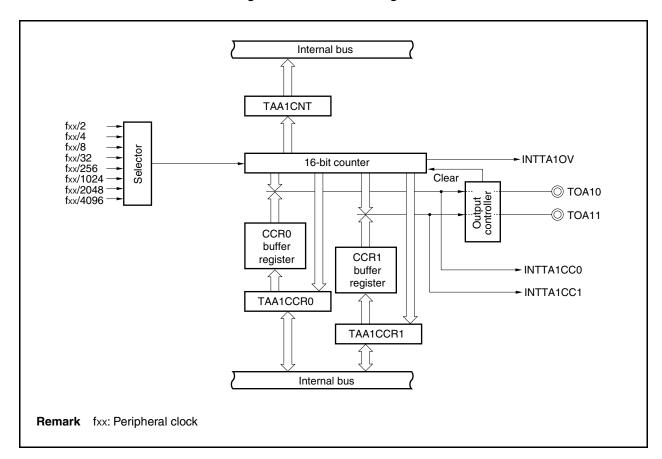

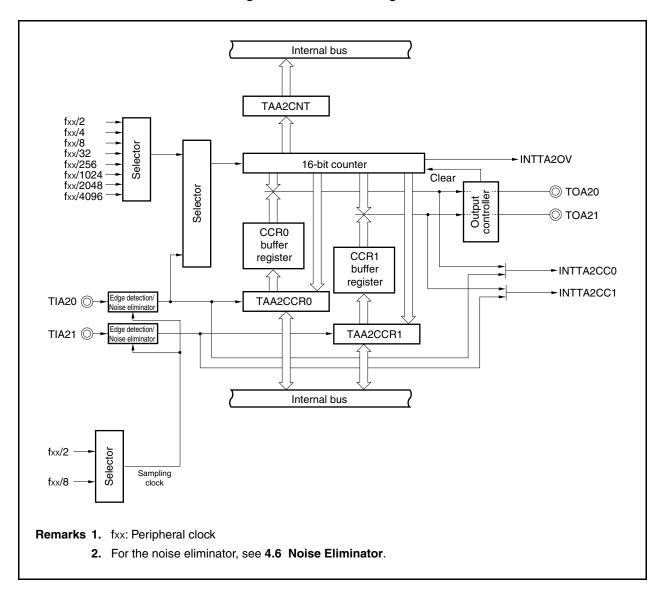

| CHAPTI     | R 6 16-BIT  | TIMER/EVENT COUNTER AA (TAA)                                    | 197 |

| 6.1        | Overview    |                                                                 | 197 |

| 6.2        |             |                                                                 |     |

| 6.3        | _           | tion                                                            |     |

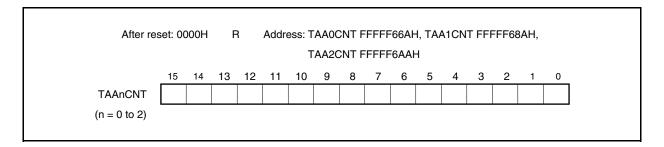

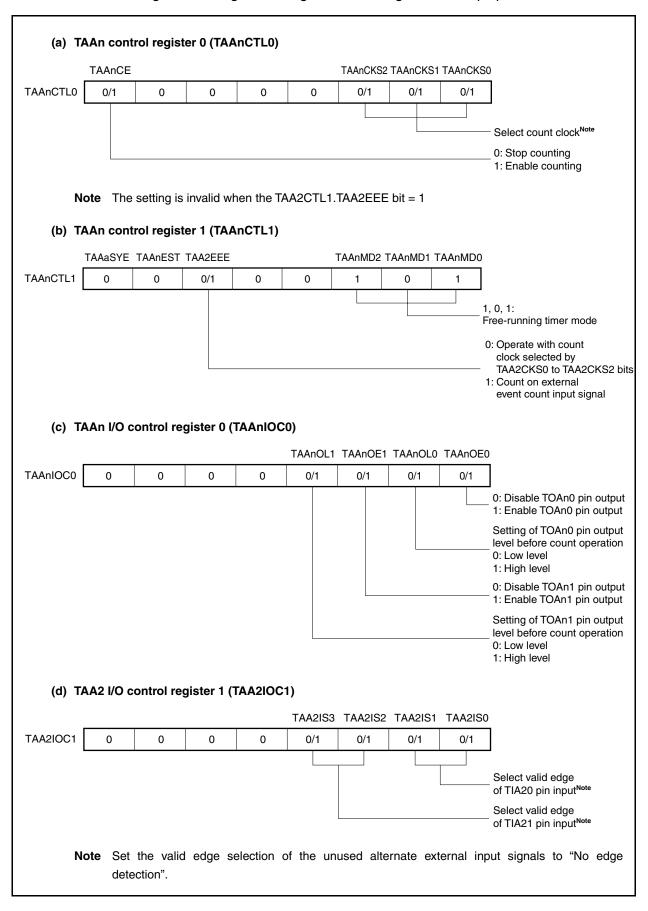

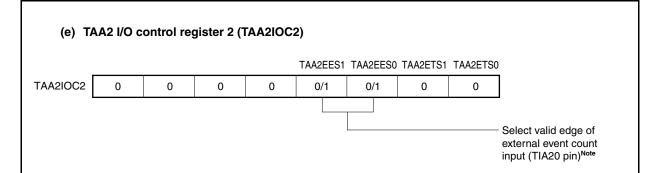

| 6.4        | Registers . |                                                                 | 203 |

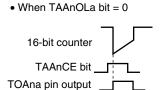

| 6.5        | Timer Outp  | out Operations                                                  | 215 |

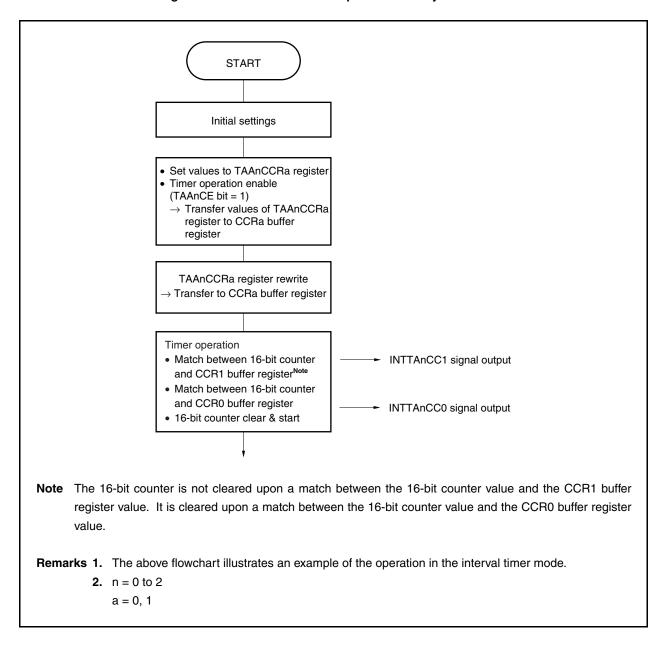

| 6.6        | Operation.  |                                                                 | 216 |

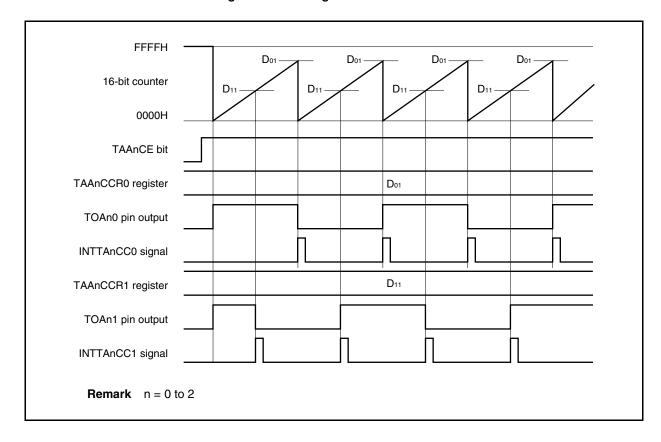

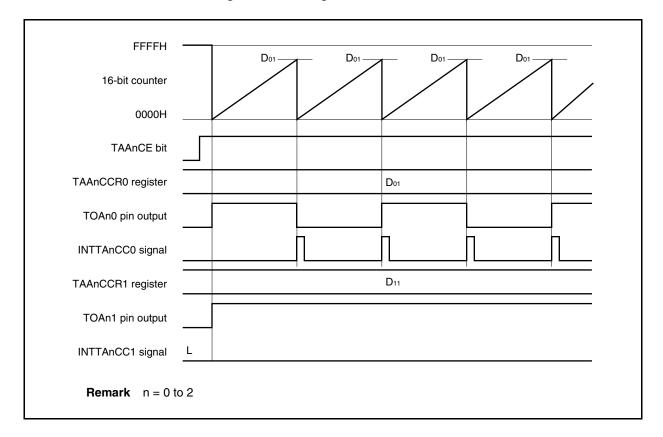

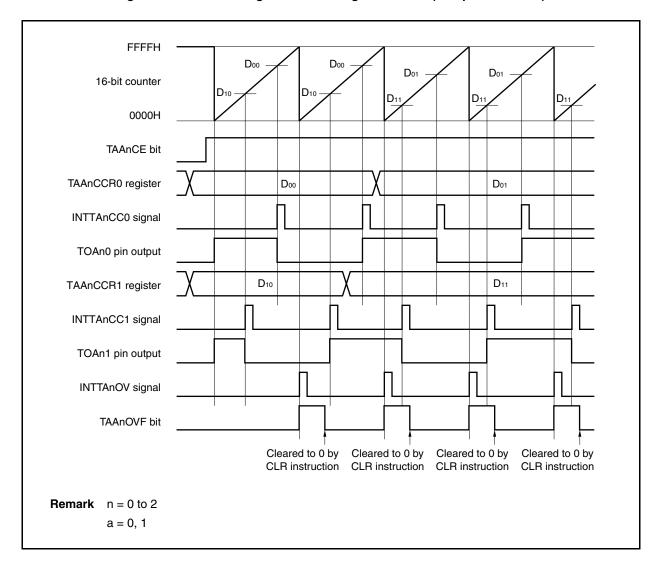

|            | 6.6.1 Inte  | erval timer mode (TAAnMD2 to TAAnMD0 bits = 000)                | 225 |

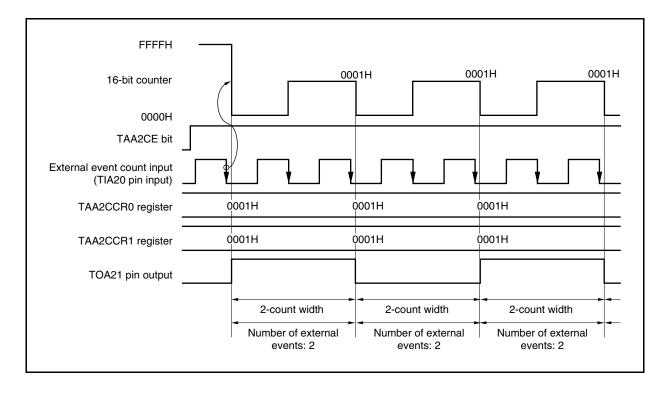

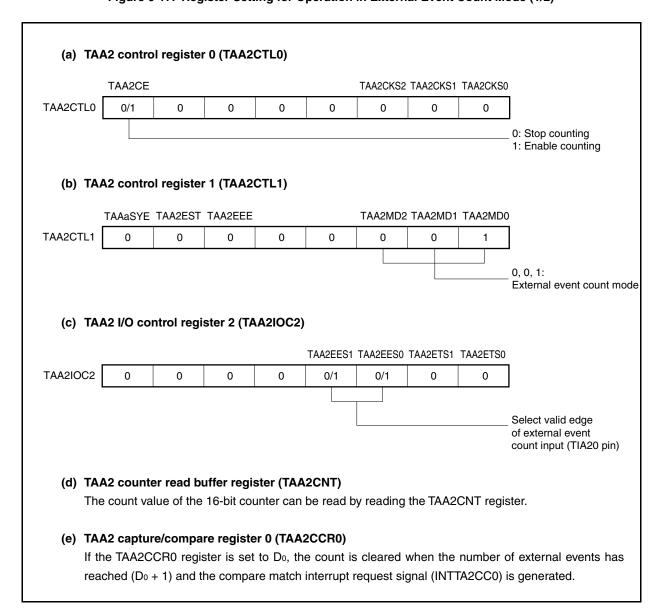

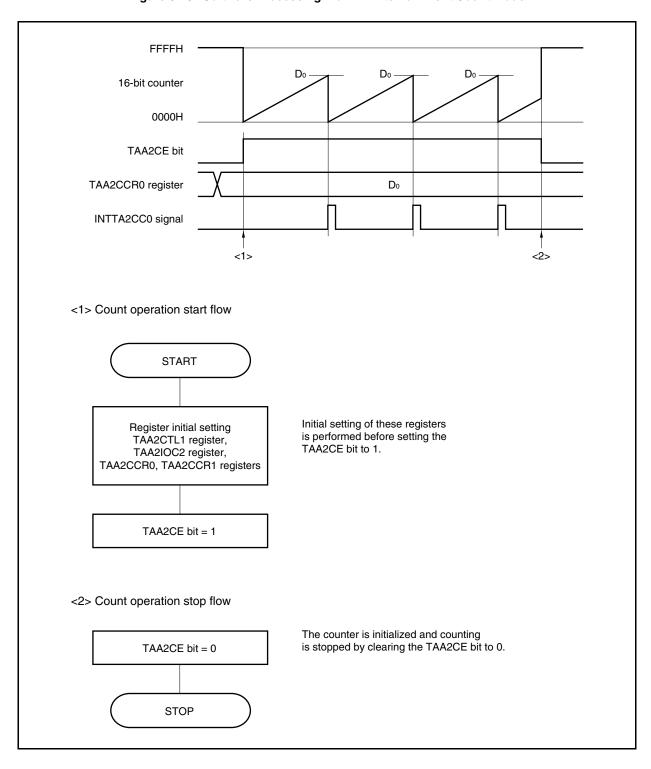

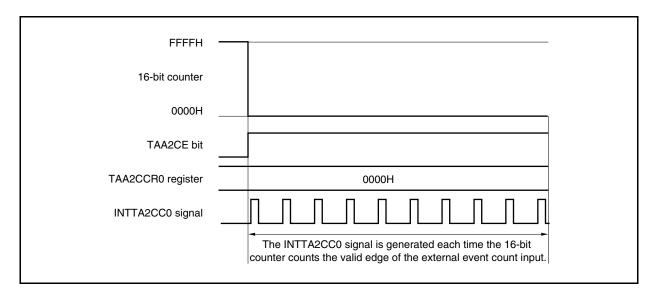

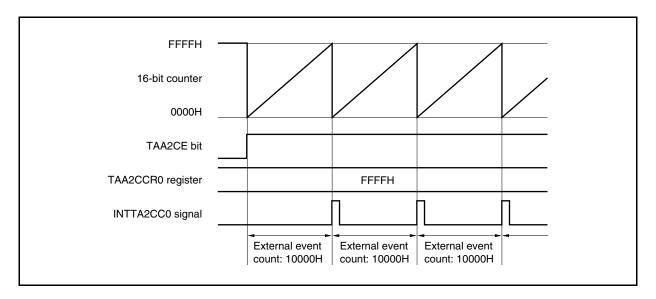

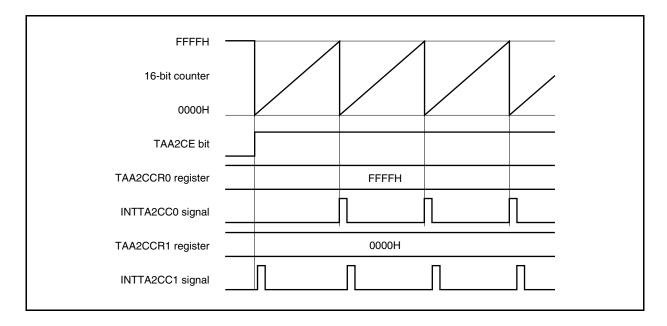

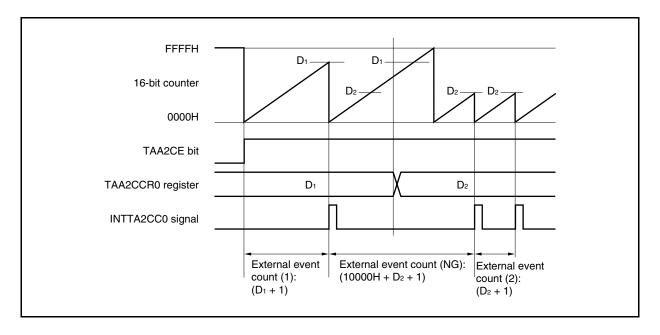

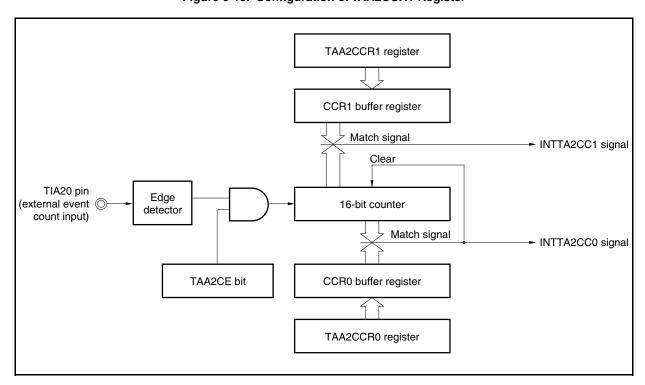

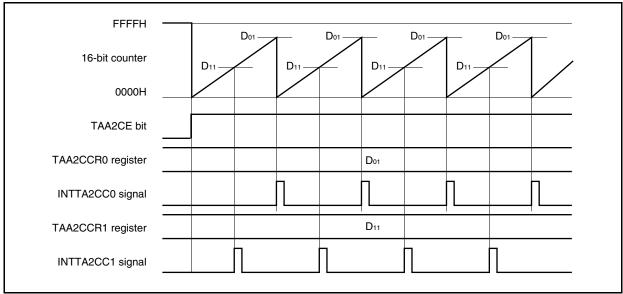

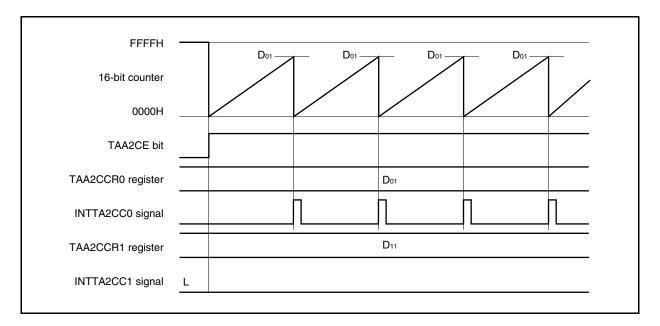

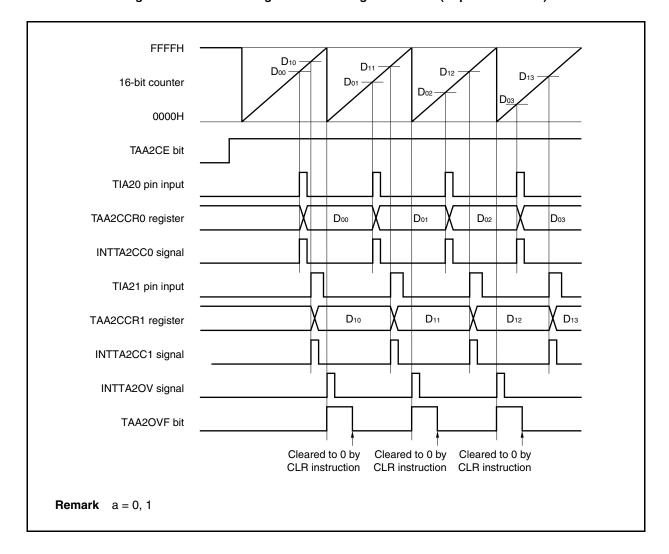

|            | 6.6.2 Ext   | ernal event count mode (TAA2MD2 to TAA2MD0 bits = 001)          | 237 |

|            | 6.6.3 Ext   | ernal trigger pulse output mode (TAAnMD2 to TAAnMD0 bits = 010) | 248 |

|        | 6.6.4   | One-shot pulse output mode (TAAnMD2 to TAAnMD0 bits = 011)         | 262 |

|--------|---------|--------------------------------------------------------------------|-----|

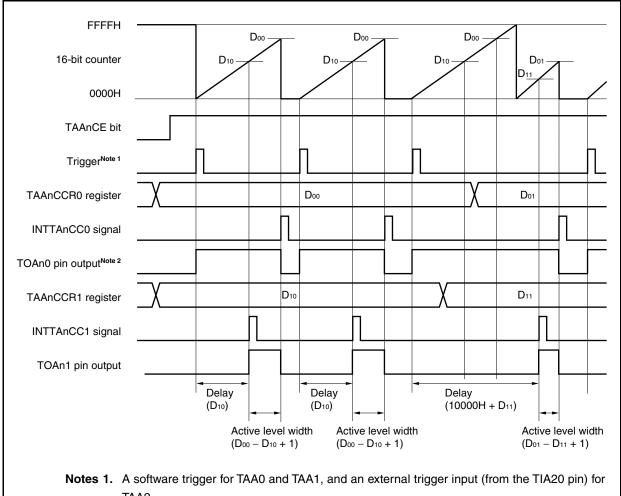

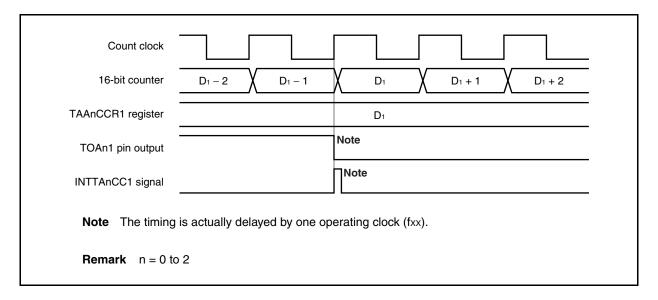

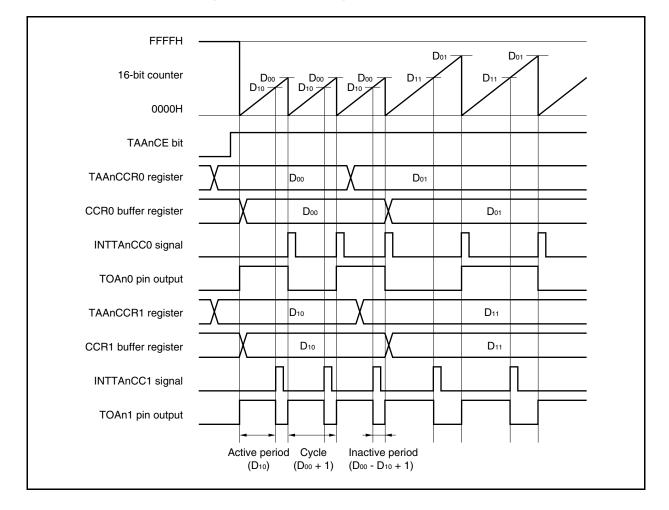

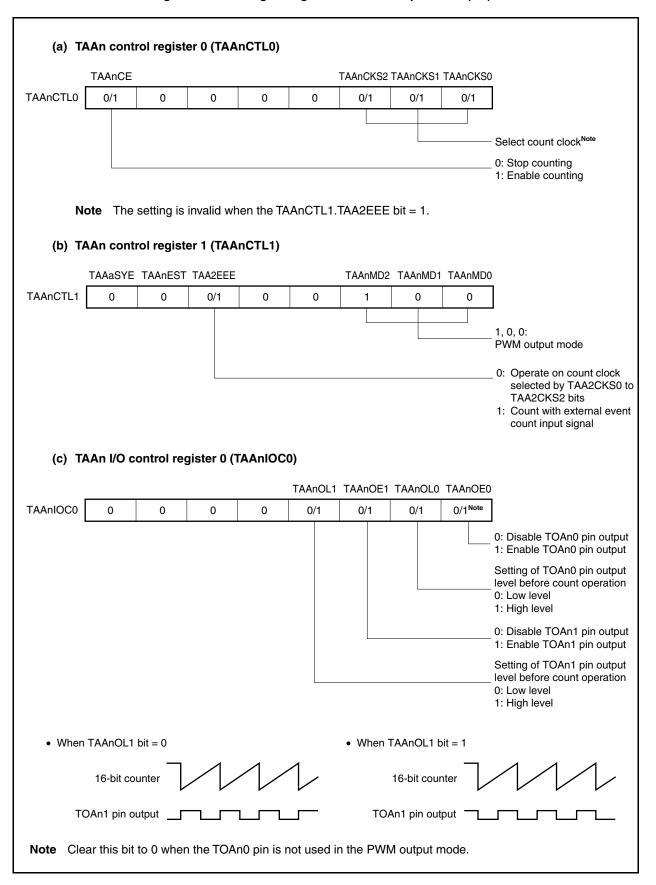

|        | 6.6.5   | PWM output mode (TAAnMD2 to TAAnMD0 bits = 100)                    | 271 |

|        | 6.6.6   | Free-running timer mode (TAAnMD2 to TAAnMD0 bits = 101)            | 281 |

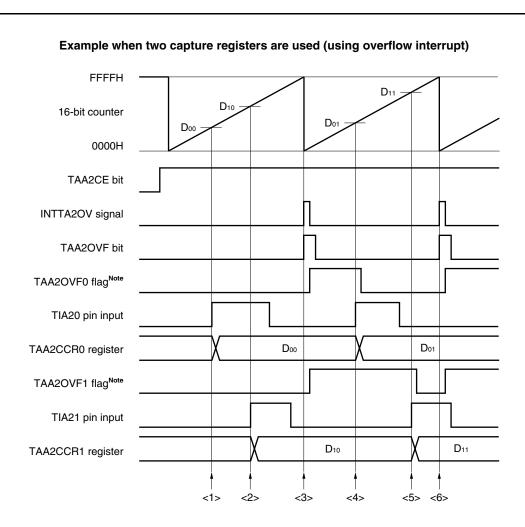

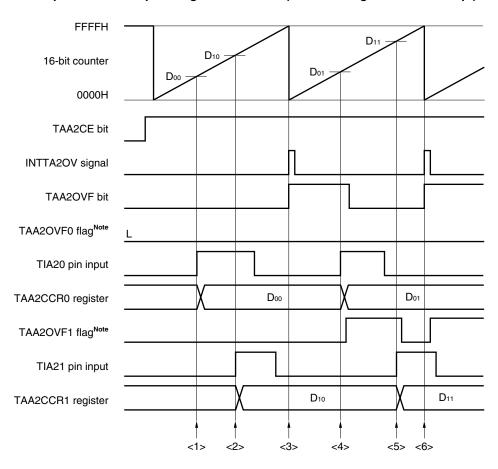

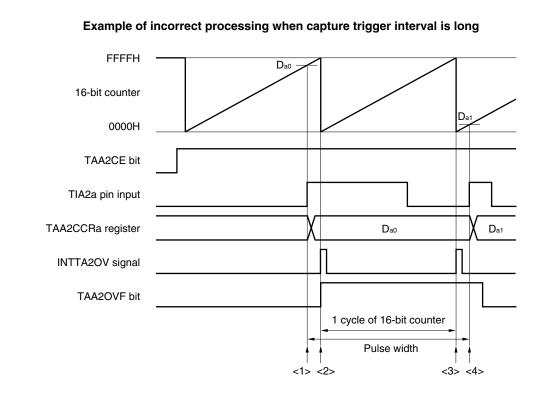

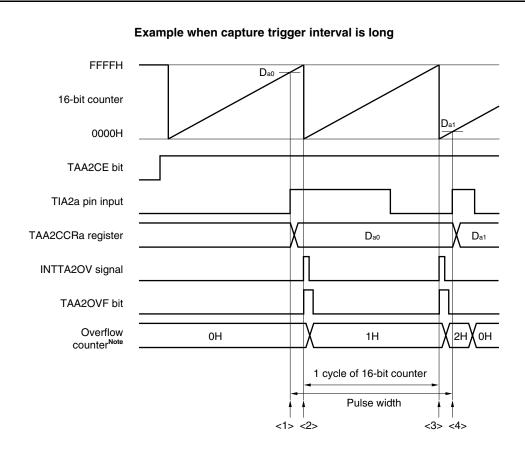

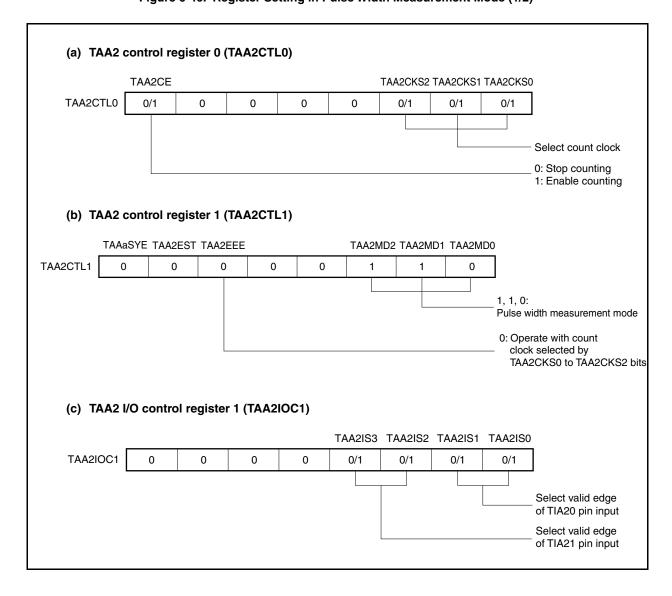

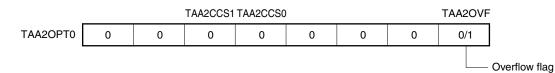

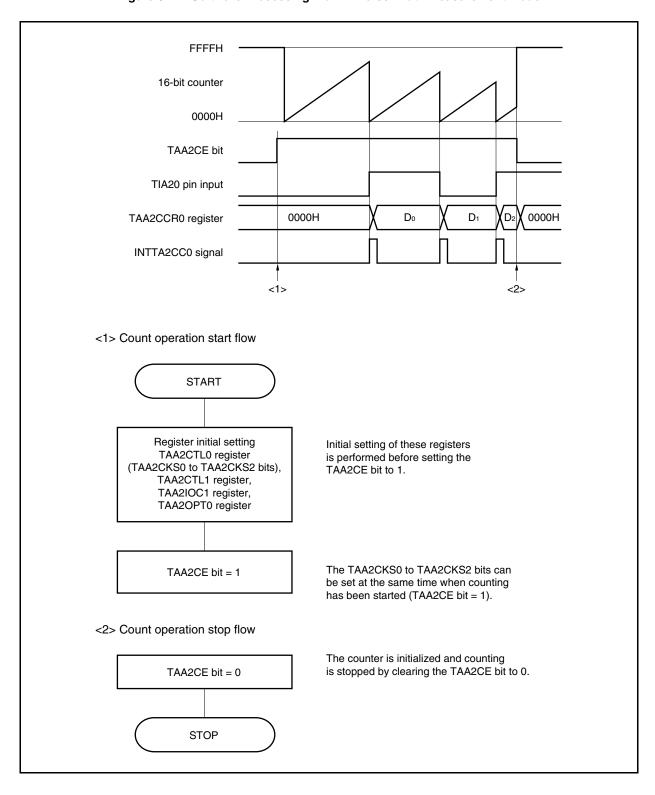

|        | 6.6.7   | Pulse width measurement mode (TAA2MD2 to TAA2MD0 bits = 110)       | 298 |

| CHAPTE | ER 7 10 | 6-BIT TIMER/EVENT COUNTER AB (TAB)                                 | 304 |

| 7.1    | Overv   | riew                                                               | 304 |

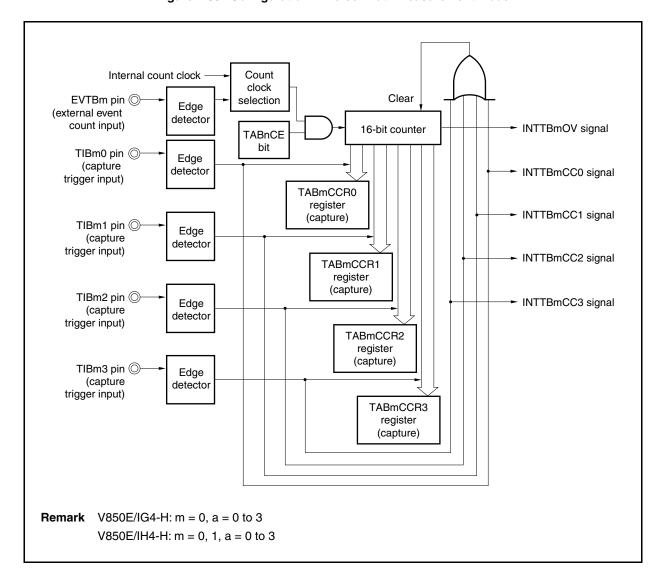

|        | 7.1.1   | TAB0 of V850E/IG4-H, and TAB0 and TAB1 of V850E/IH4-H              | 304 |

|        | 7.1.2   | TAB1 of V850E/IG4-H                                                | 304 |

| 7.2    | Funct   | ions                                                               | 305 |

|        | 7.2.1   | TAB0 of V850E/IG4-H, and TAB0 and TAB1 of V850E/IH4-H              | 305 |

|        | 7.2.2   | TAB1 of V850E/IG4-H                                                | 305 |

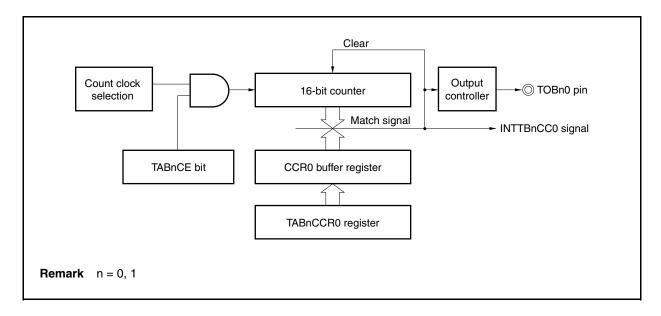

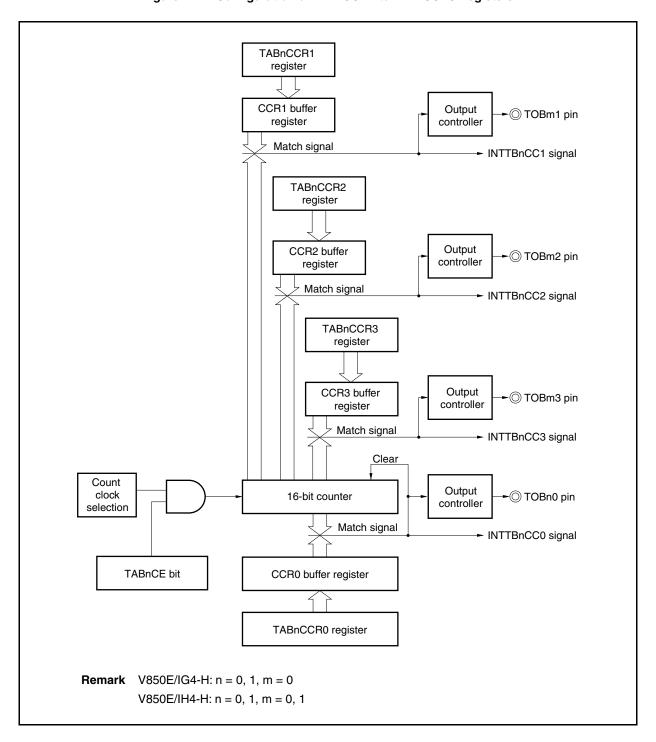

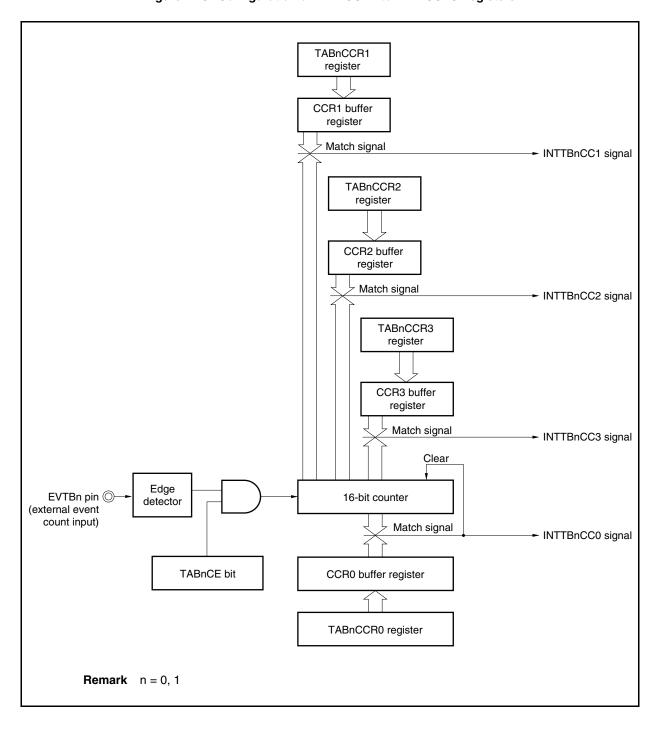

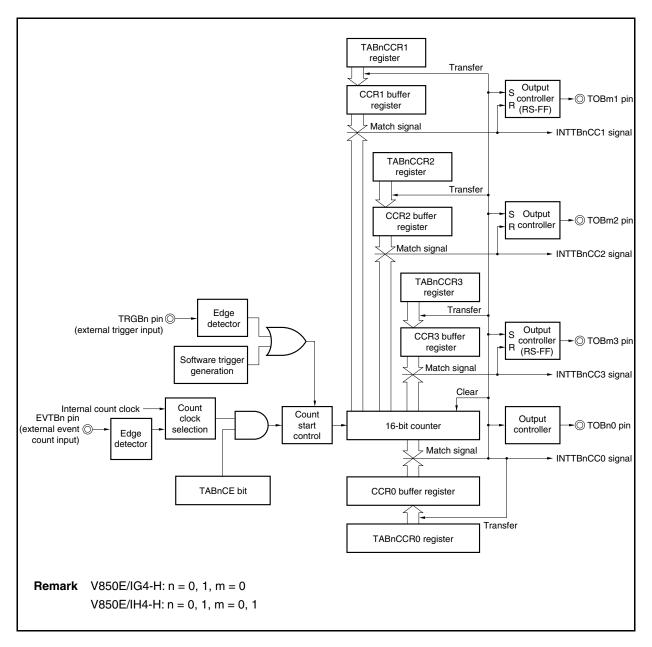

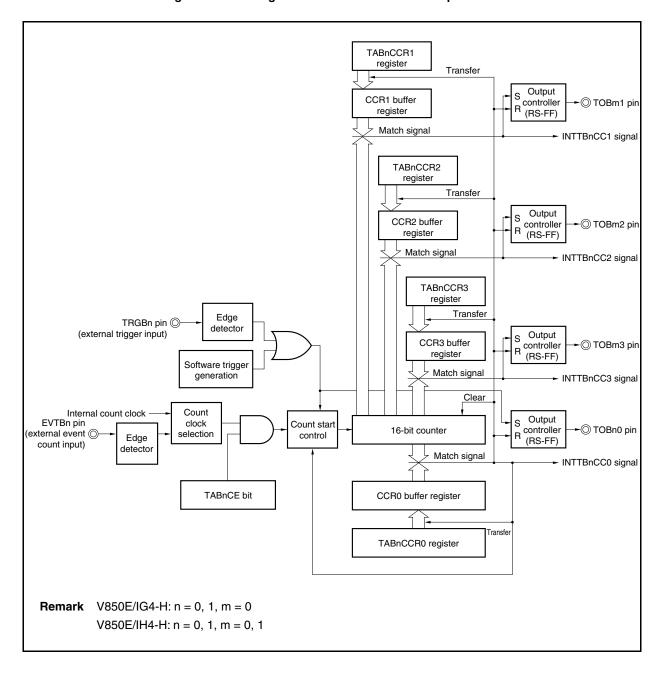

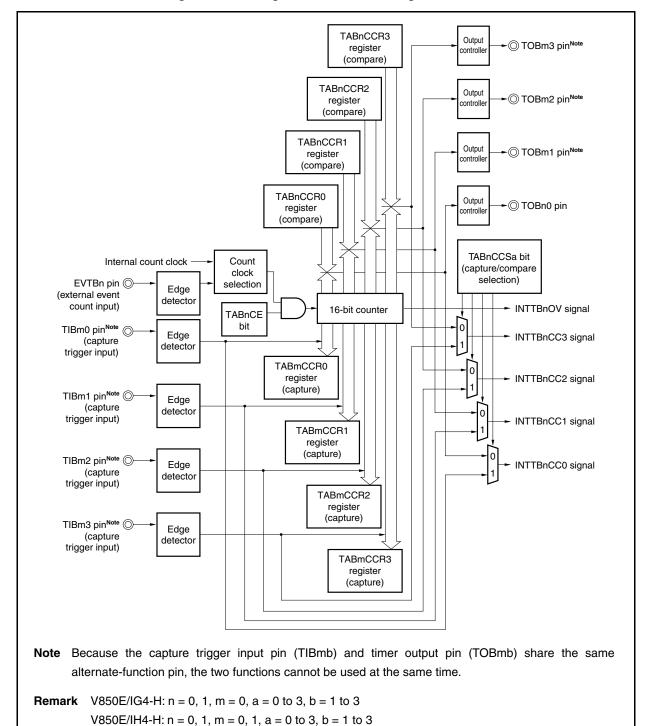

| 7.3    | Config  | guration                                                           | 306 |

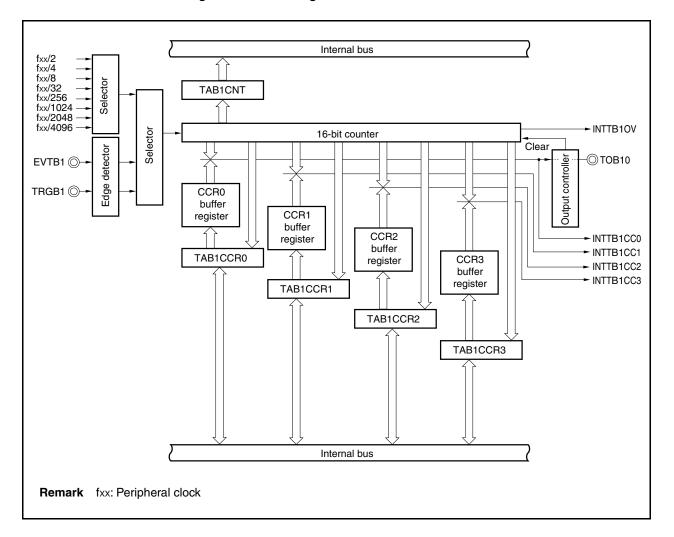

|        | 7.3.1   | TAB0 of V850E/IG4-H, and TAB0 and TAB1 of V850E/IH4-H              | 306 |

|        | 7.3.2   | TAB1 of V850E/IG4-H                                                | 309 |

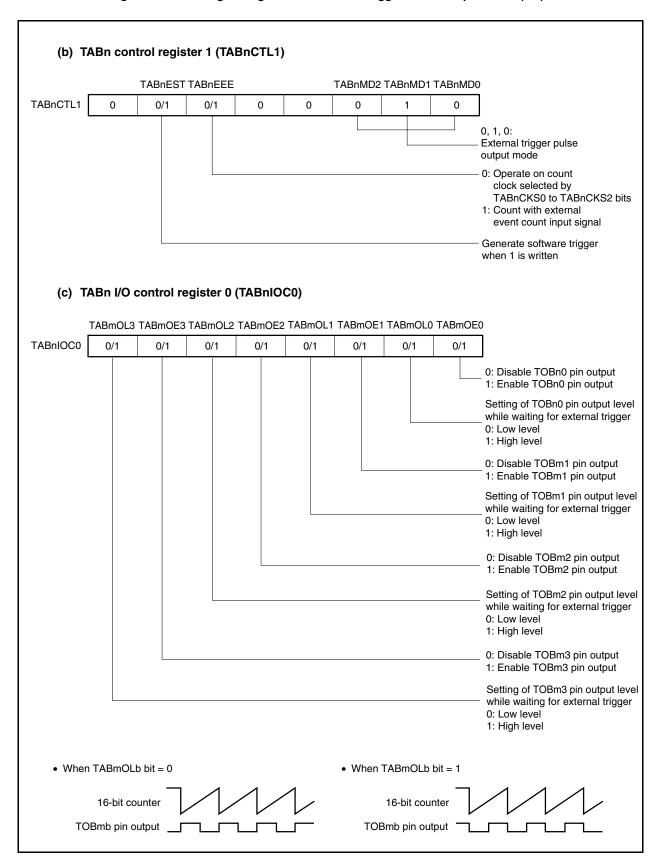

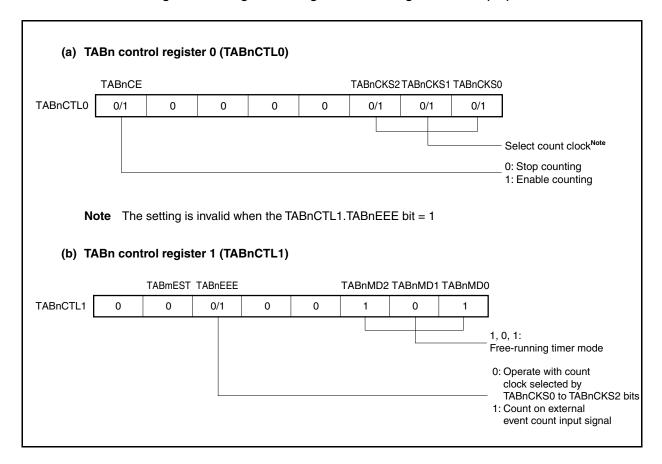

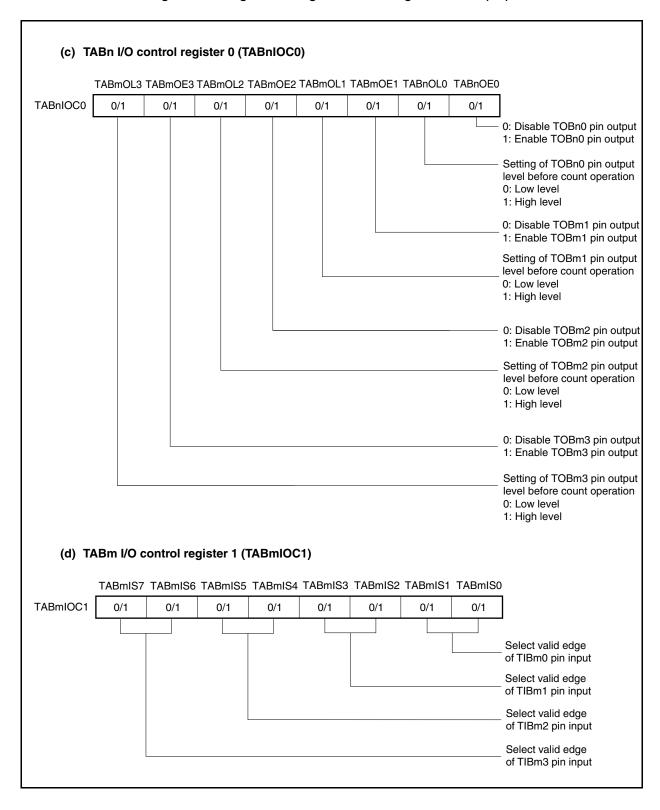

| 7.4    | Regis   | ters                                                               | 311 |

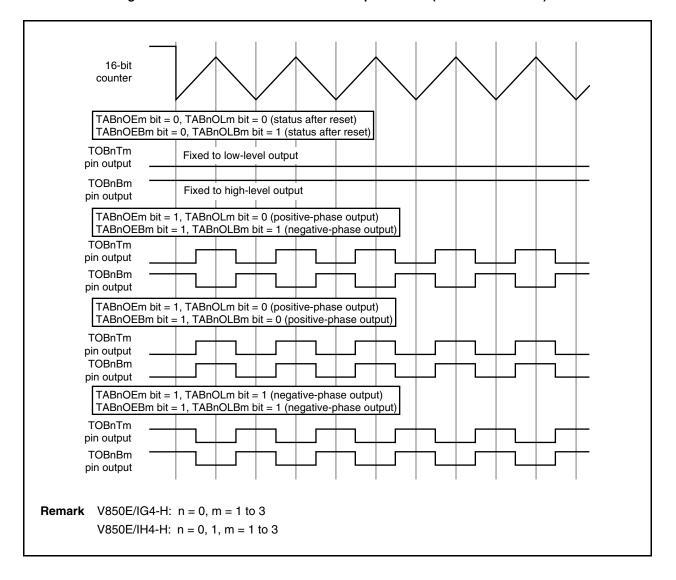

| 7.5    | Timer   | Output Operations                                                  | 325 |

| 7.6    | Opera   | ation                                                              | 326 |

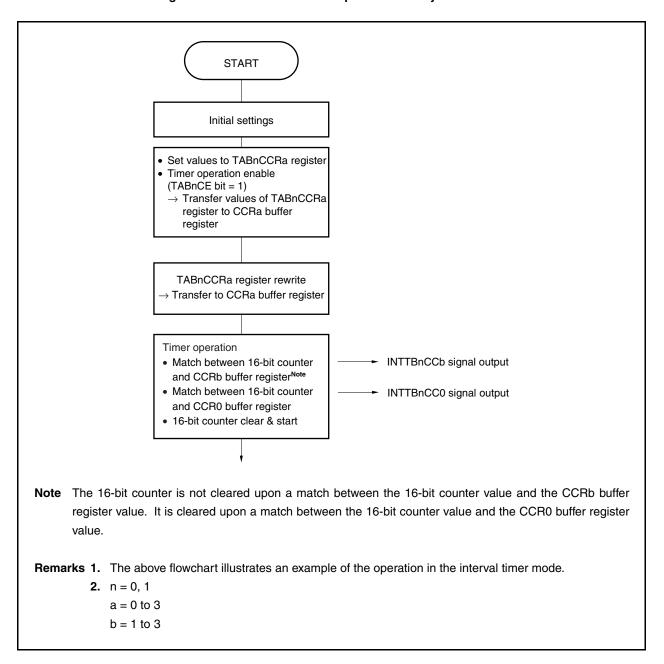

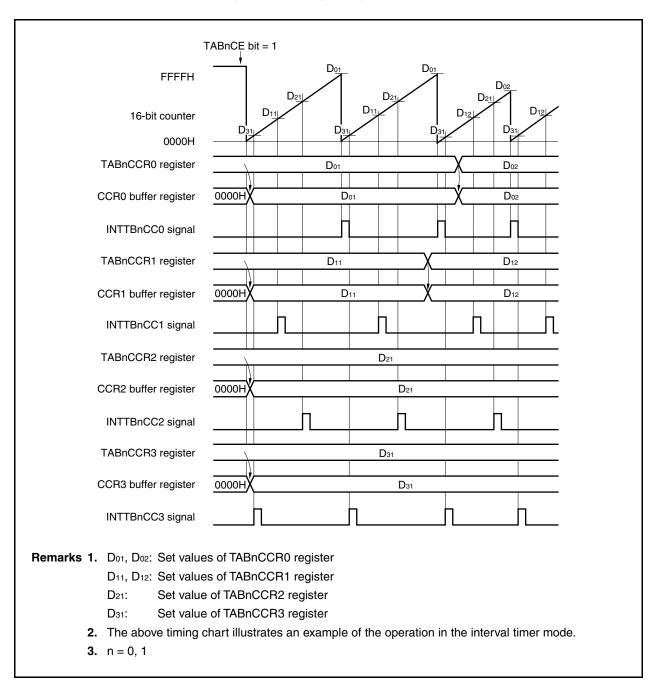

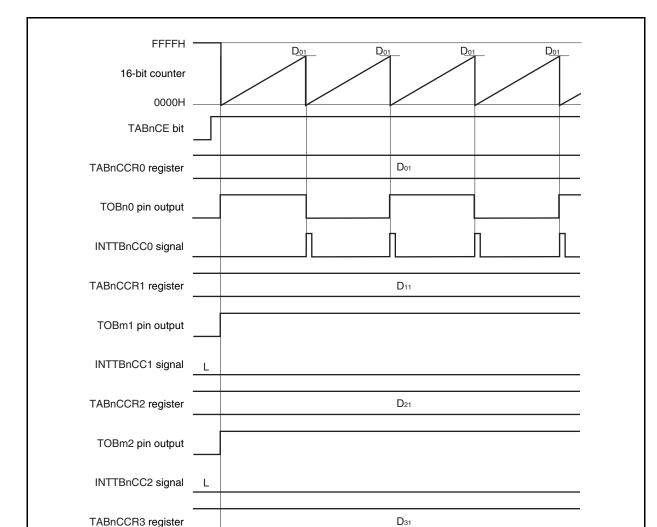

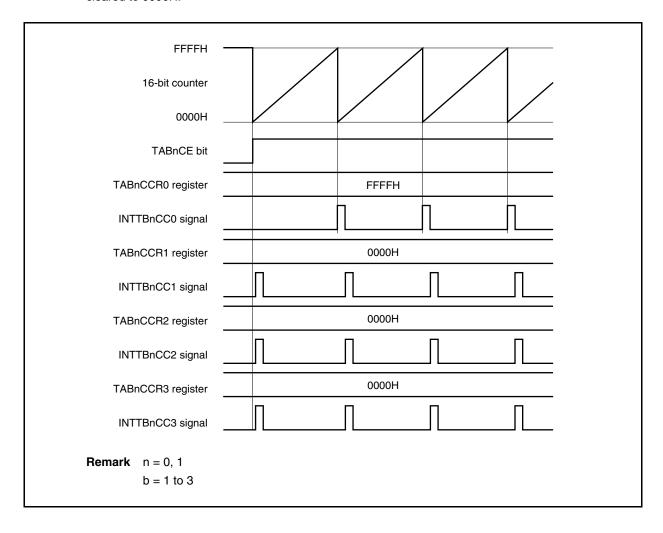

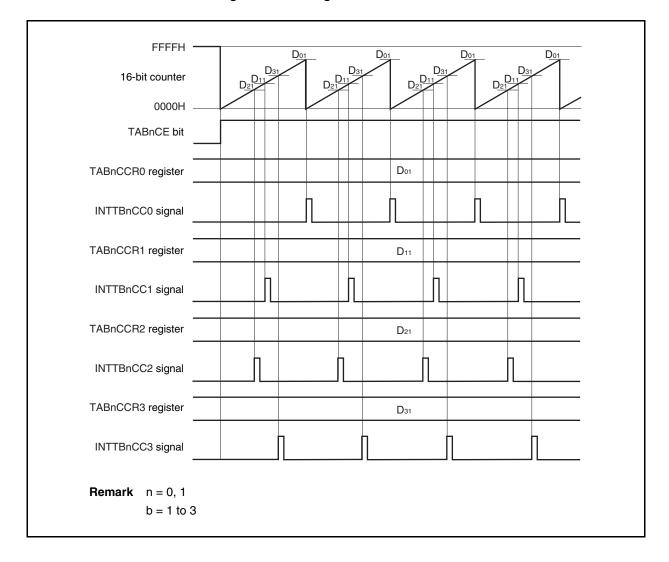

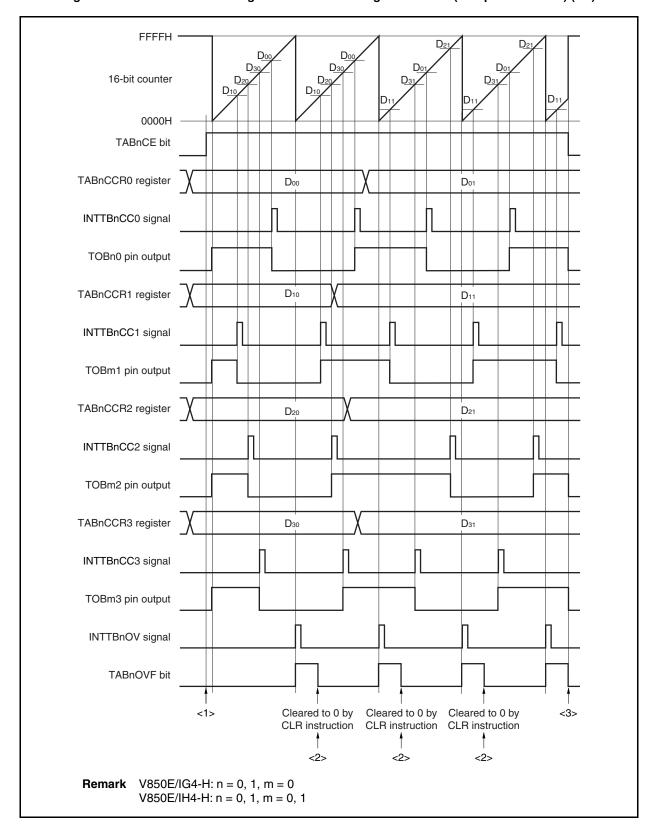

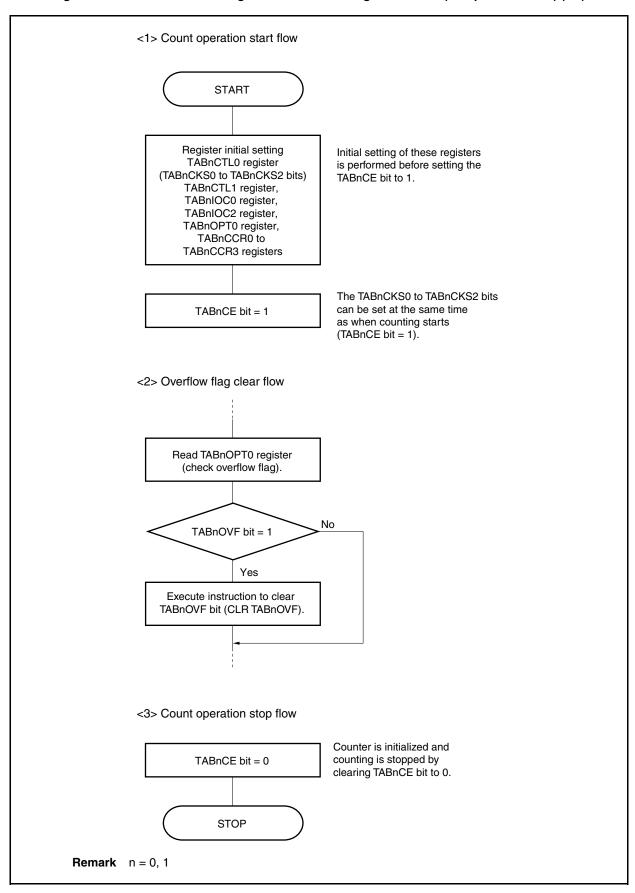

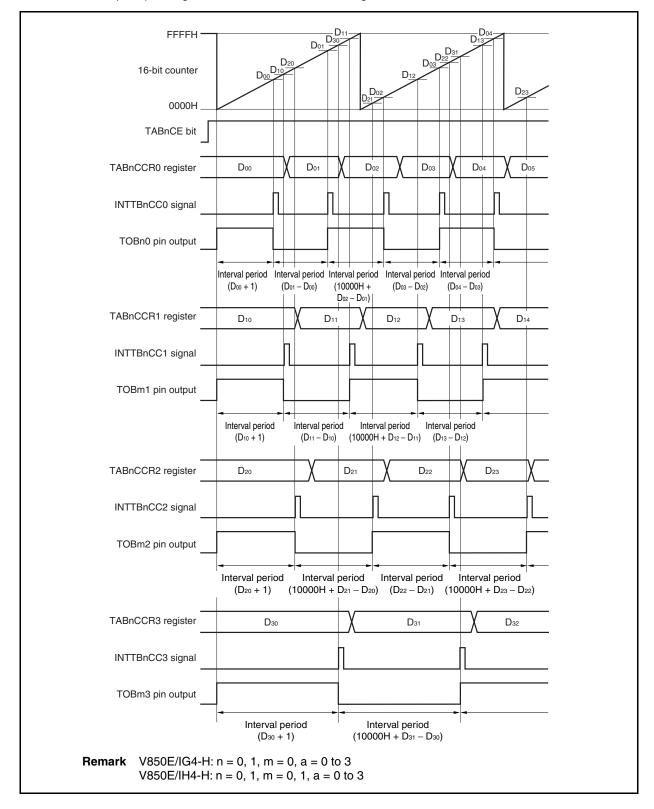

|        | 7.6.1   | Interval timer mode (TABnMD2 to TABnMD0 bits = 000)                | 334 |

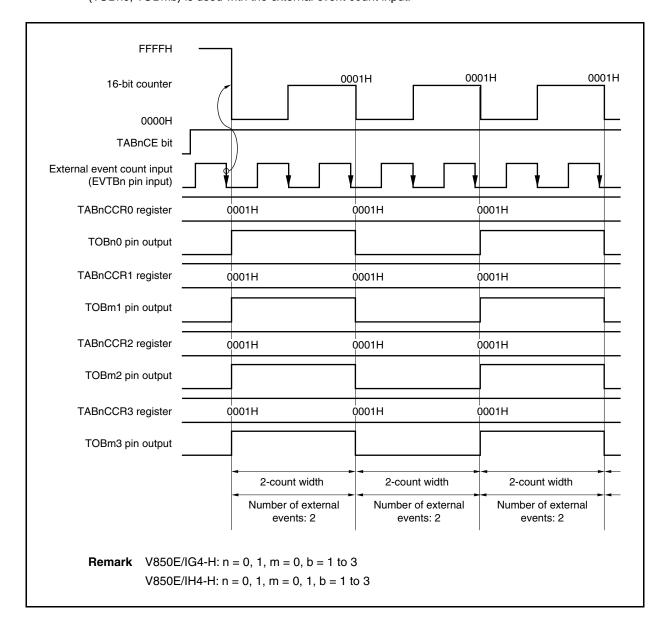

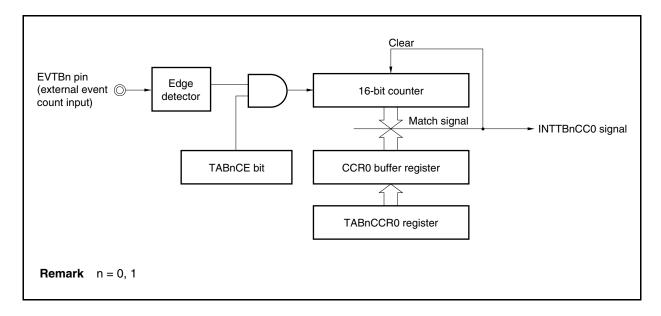

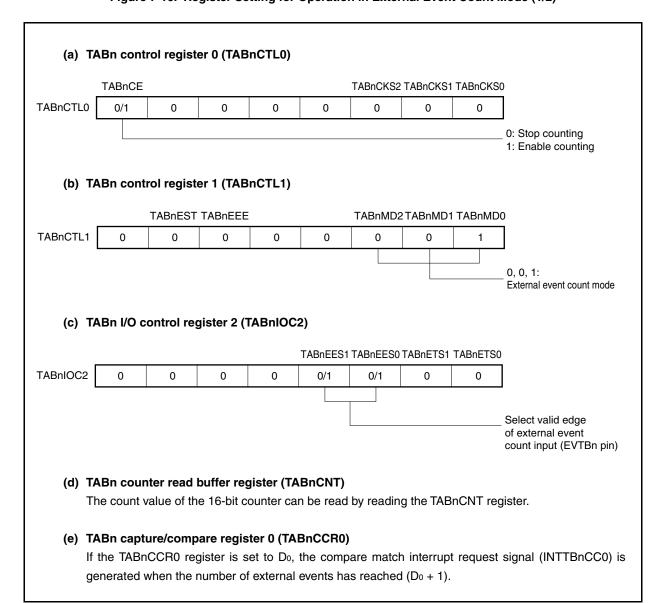

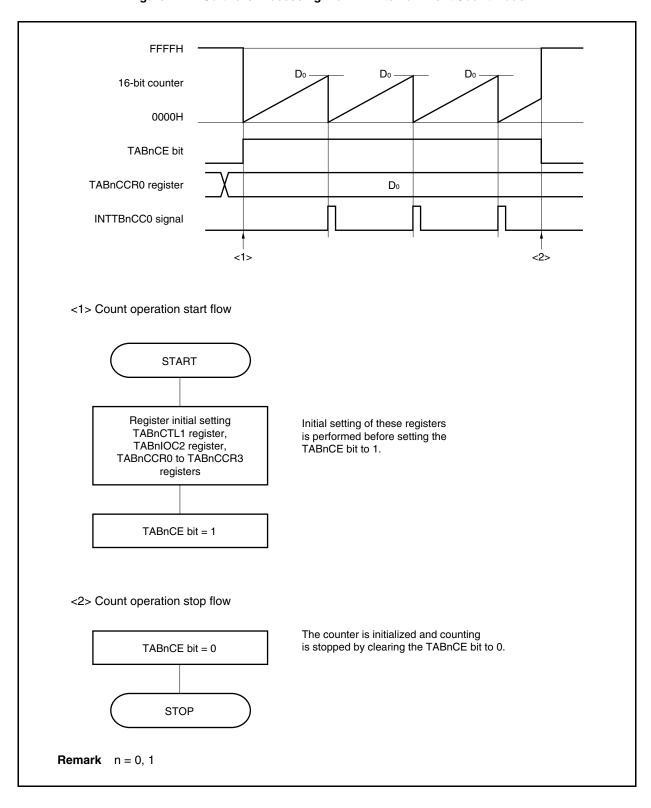

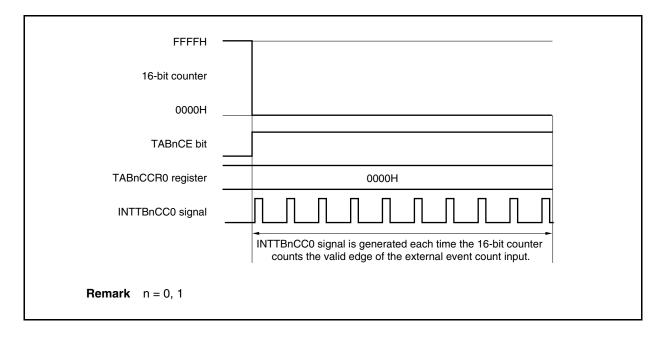

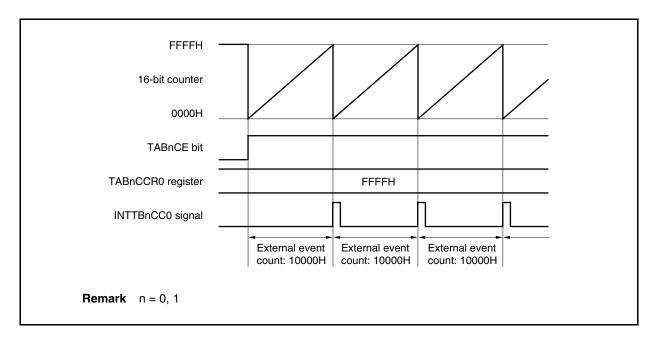

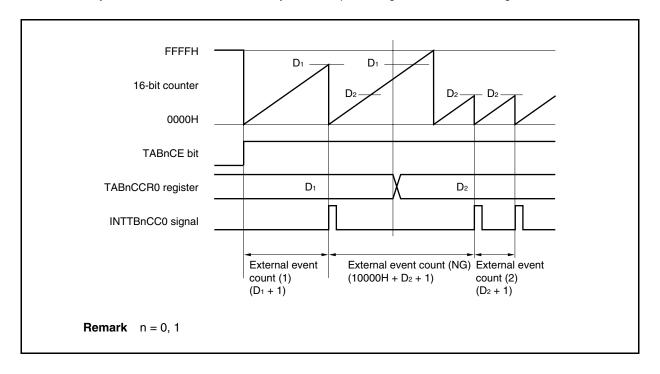

|        | 7.6.2   | External event count mode (TABnMD2 to TABnMD0 bits = 001)          | 347 |

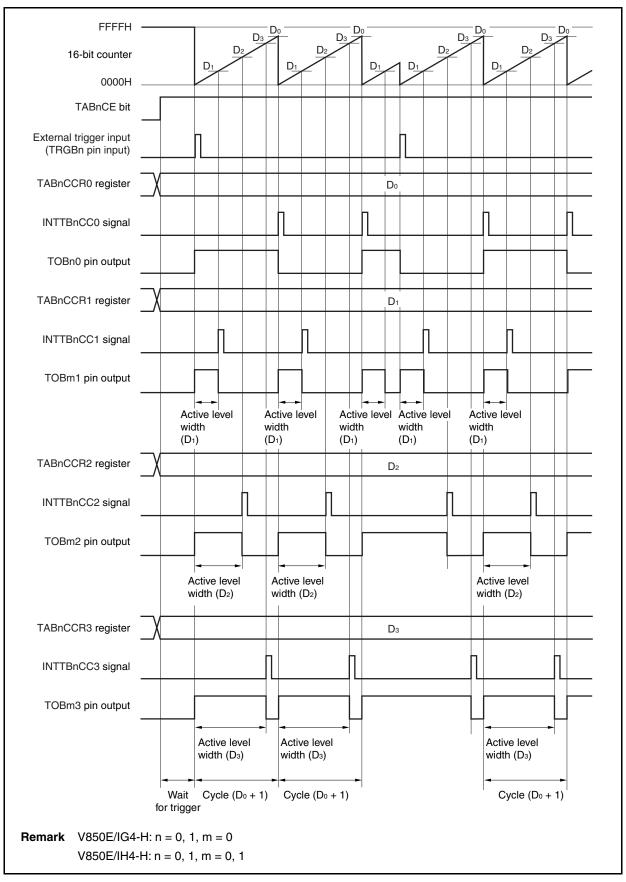

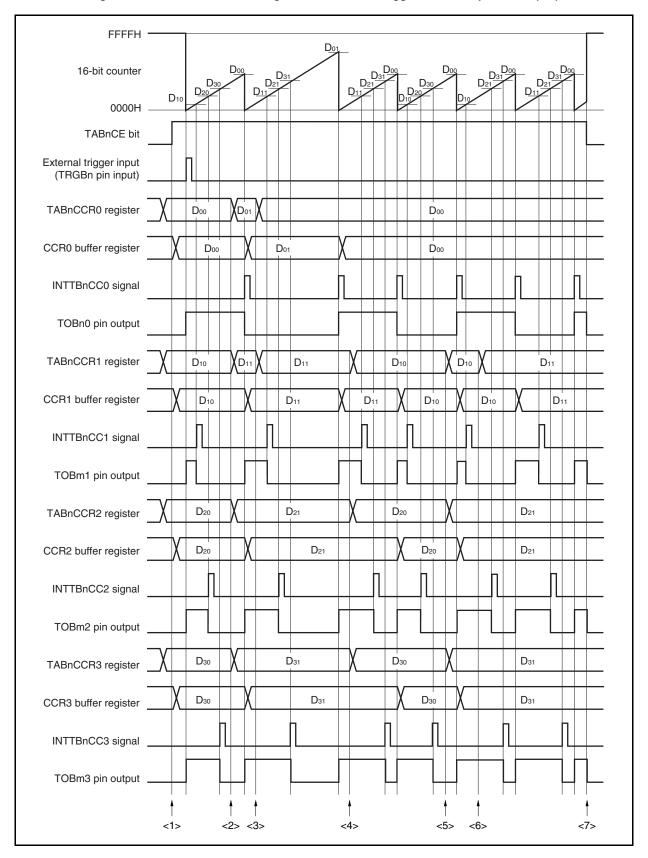

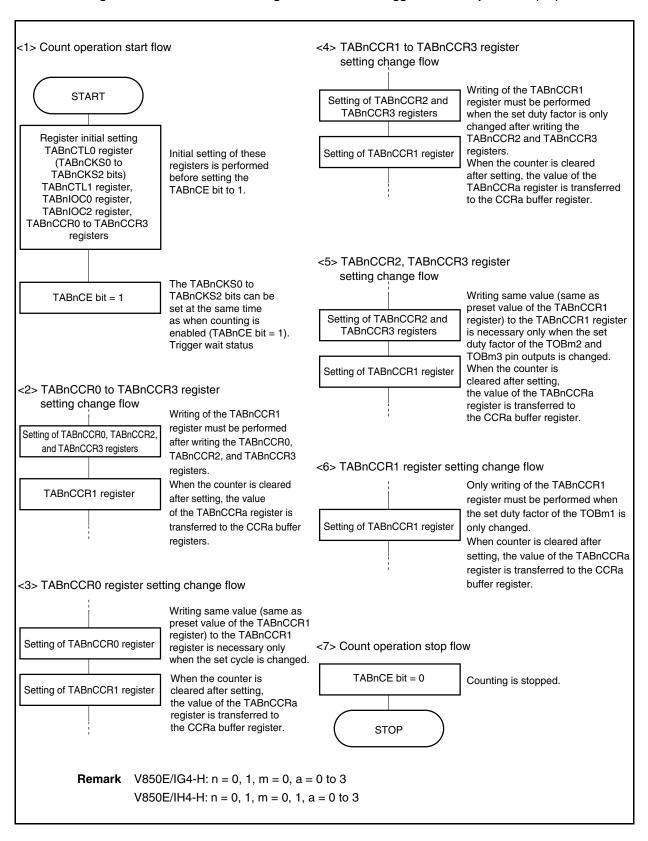

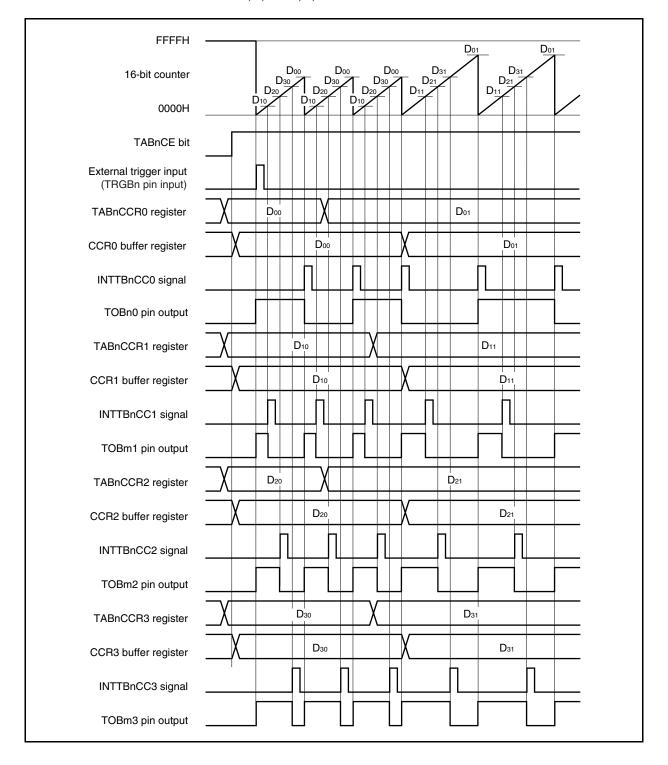

|        | 7.6.3   | External trigger pulse output mode (TABnMD2 to TABnMD0 bits = 010) | 359 |

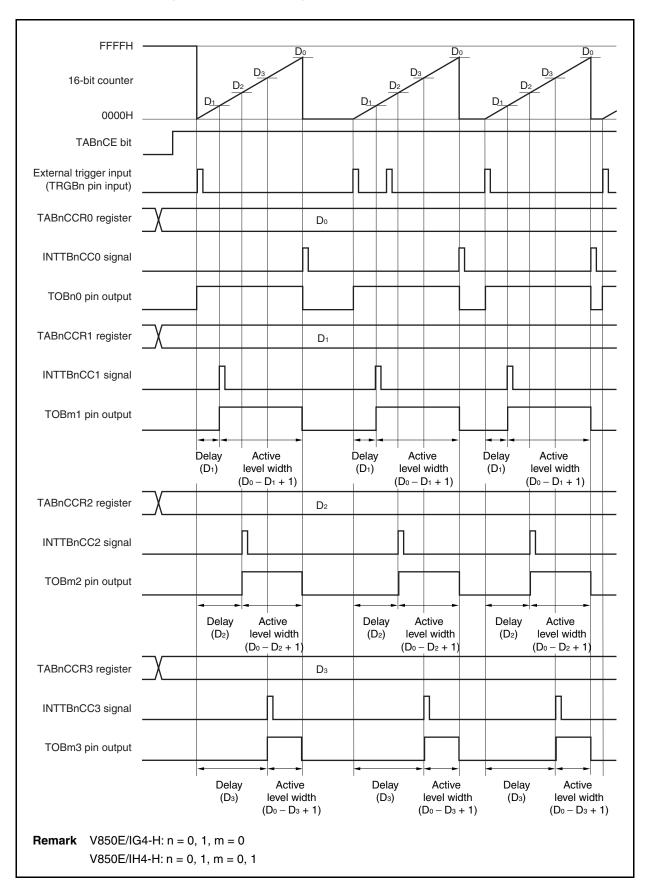

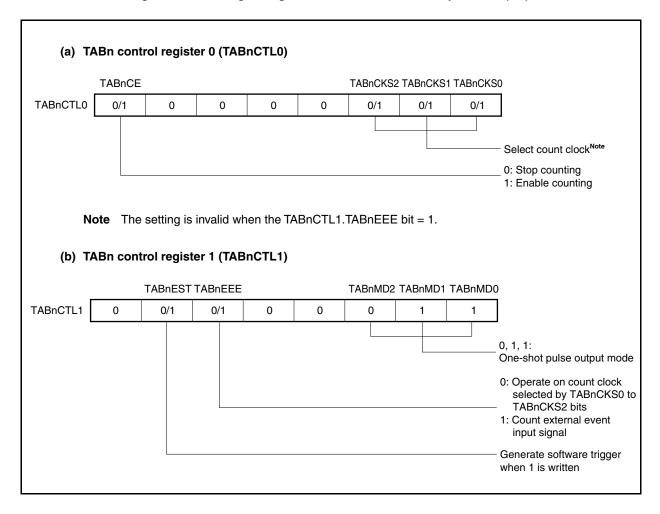

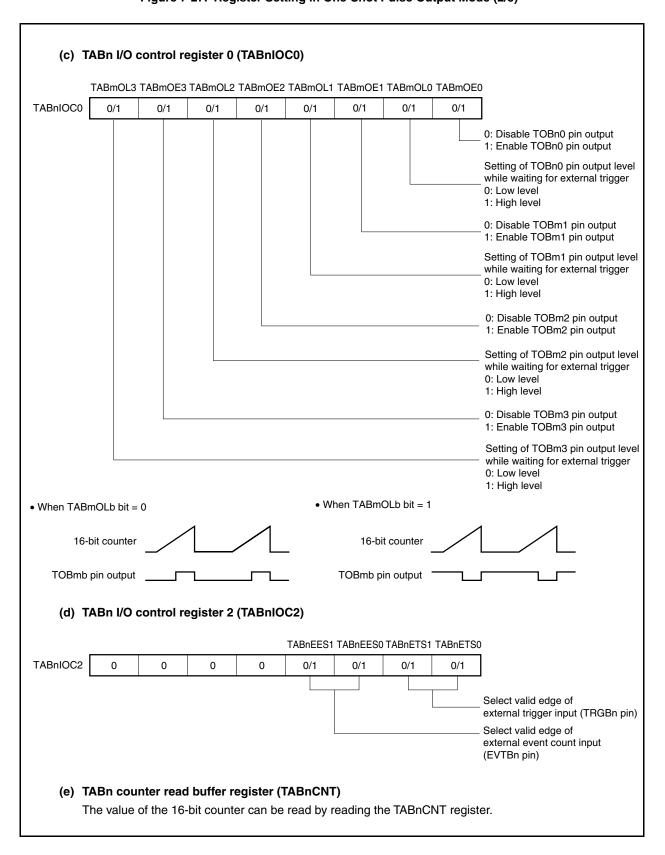

|        | 7.6.4   | One-shot pulse output mode (TABnMD2 to TABnMD0 bits = 011)         | 373 |

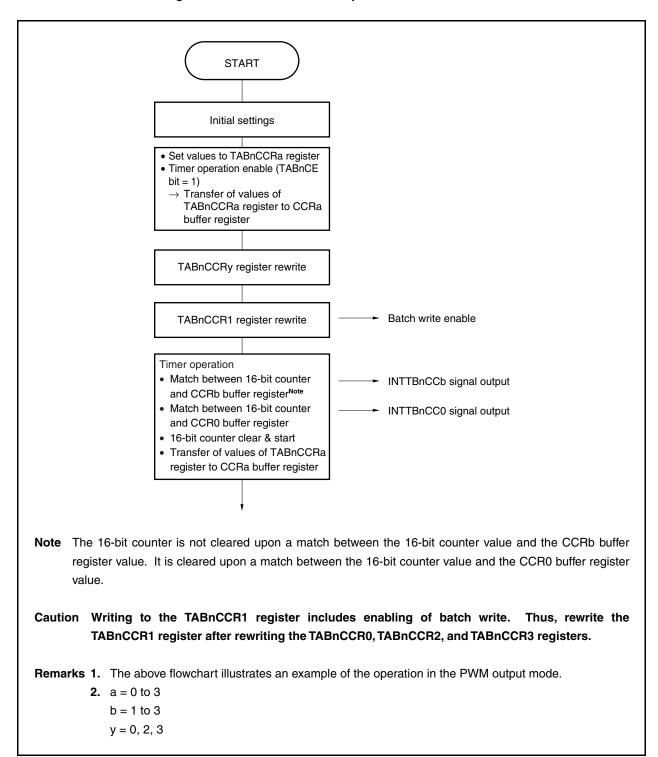

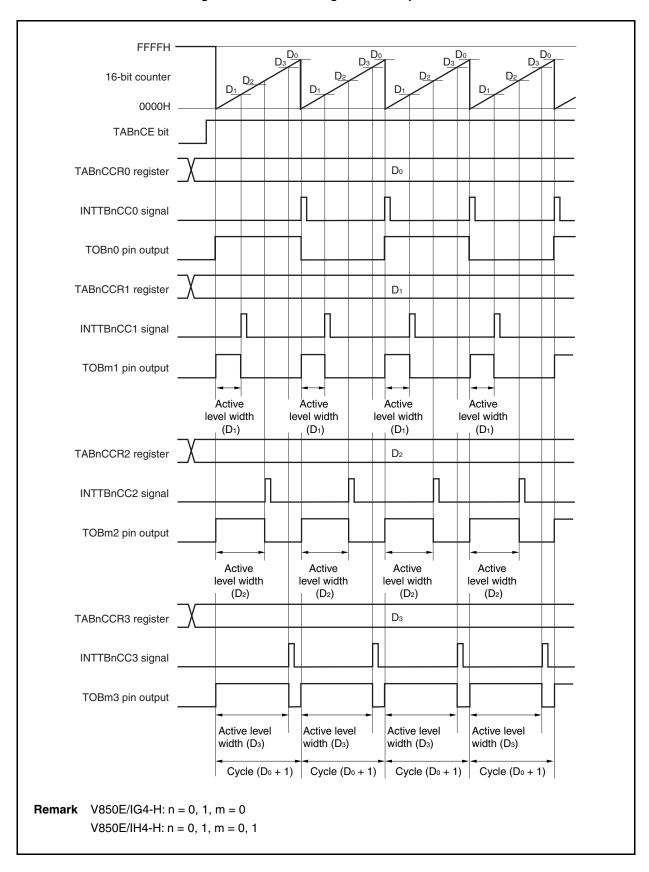

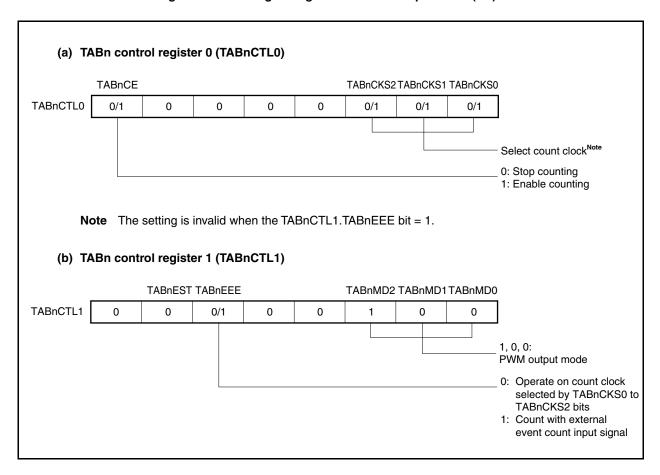

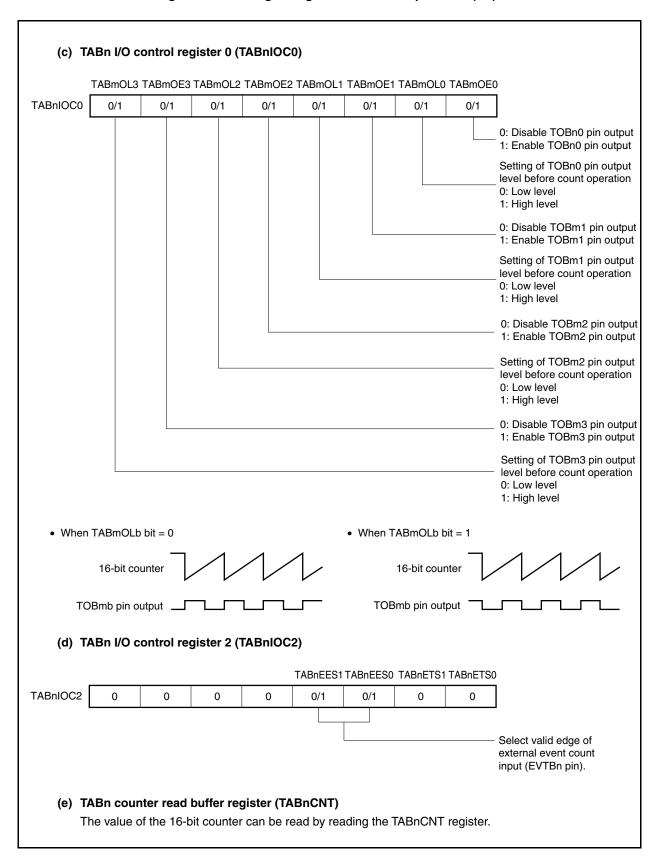

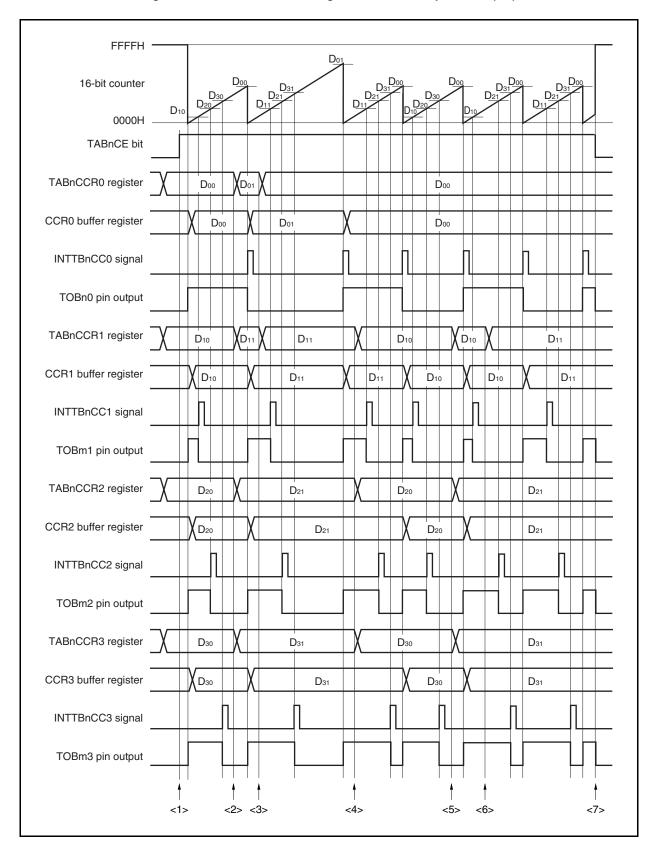

|        | 7.6.5   | PWM output mode (TABnMD2 to TABnMD0 bits = 100)                    | 382 |

|        | 7.6.6   | Free-running timer mode (TABnMD2 to TABnMD0 bits = 101)            | 394 |

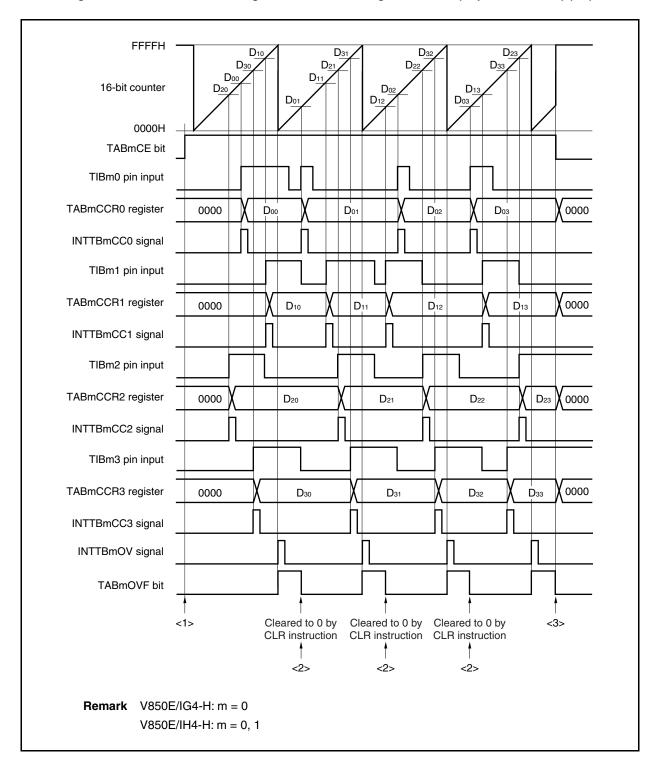

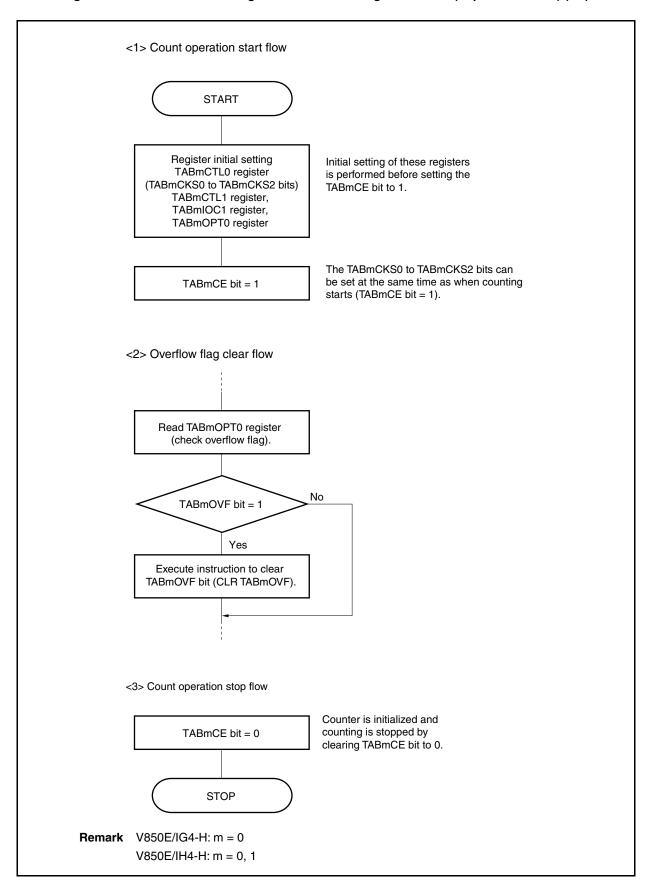

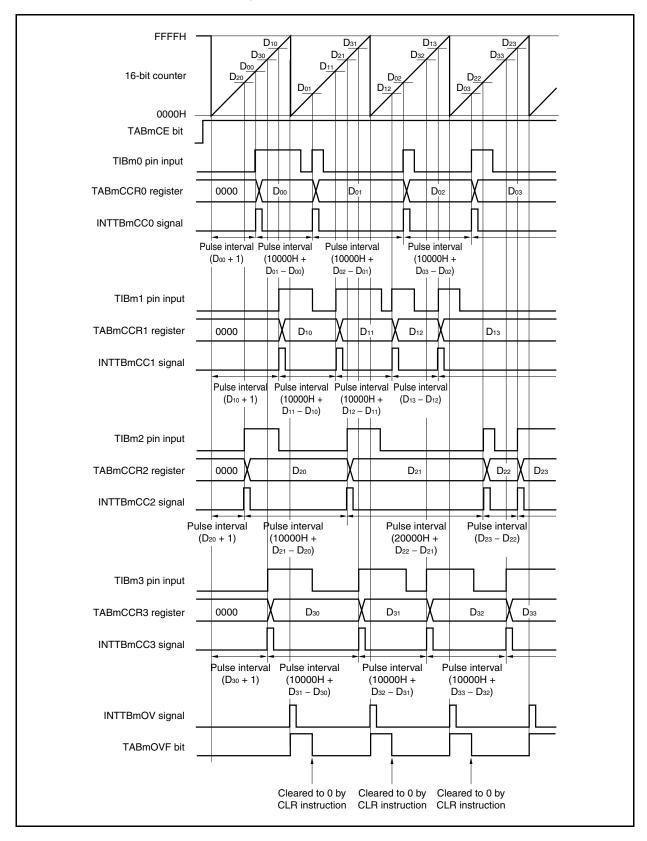

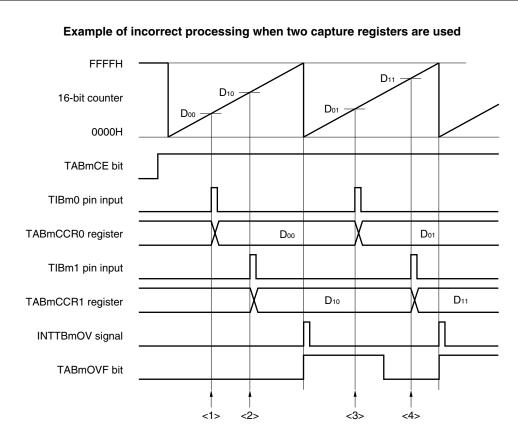

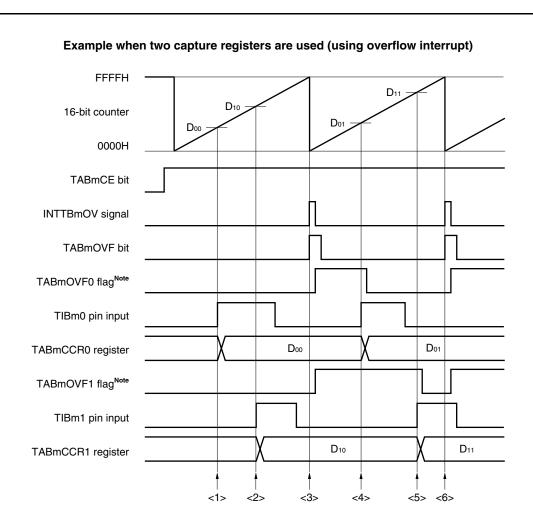

|        | 7.6.7   | Pulse width measurement mode (TABmMD2 to TABmMD0 bits = 110)       | 414 |

| CHAPTE | ER 8 10 | 6-BIT TIMER/EVENT COUNTER T (TMT)                                  | 420 |

| 8.1    | Overv   | riew                                                               | 420 |

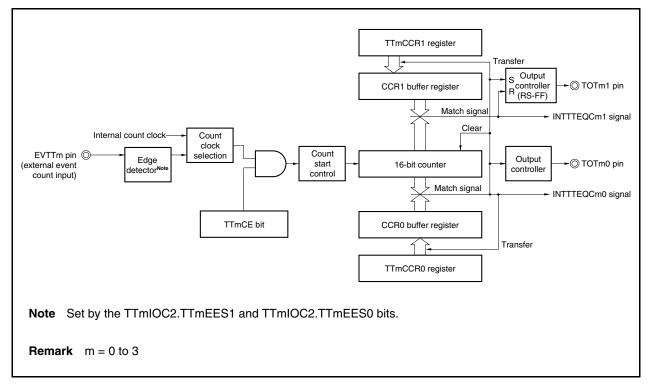

|        | 8.1.1   | TMT0 and TMT1                                                      | 420 |

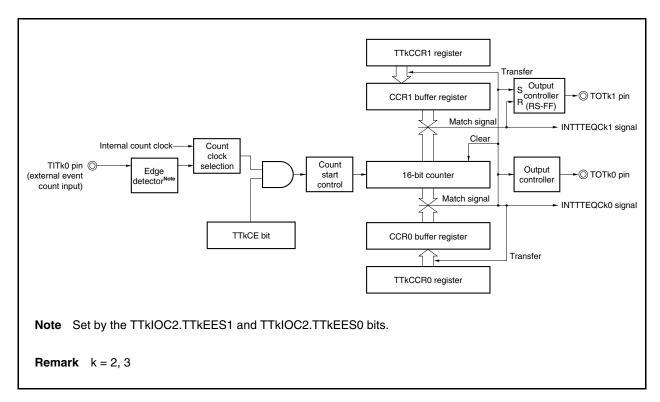

|        | 8.1.2   | TMT2 and TMT3                                                      | 420 |

| 8.2    | Funct   | ions                                                               | 421 |

|        | 8.2.1   | TMT0 and TMT1                                                      | 421 |

|        | 8.2.2   | TMT2 and TMT3                                                      | 421 |

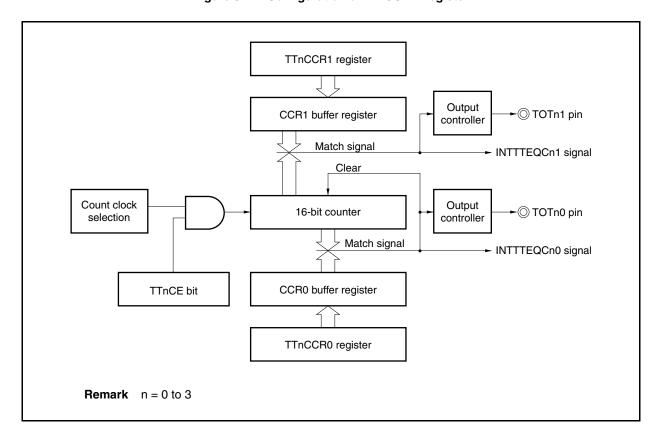

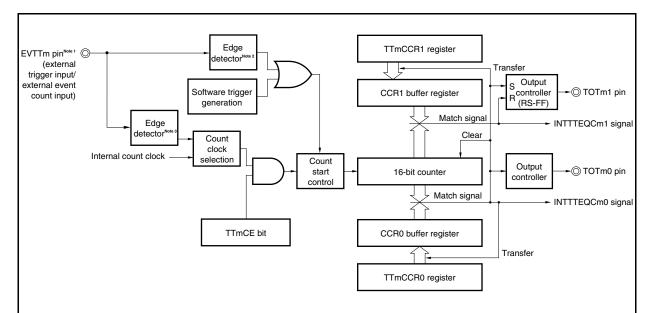

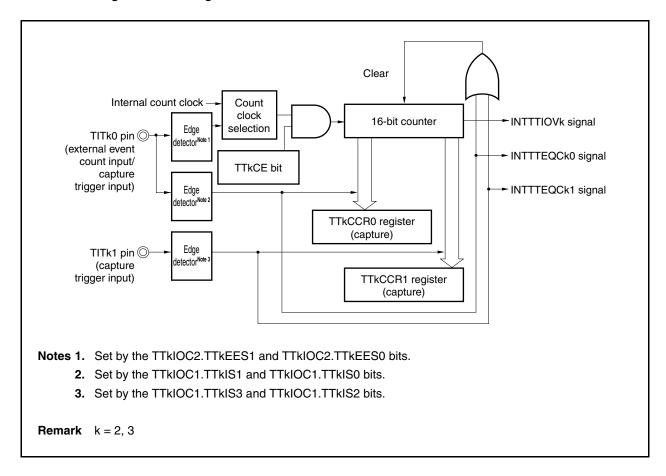

| 8.3    | Confi   | guration                                                           | 422 |

|        | 8.3.1   | TMT0 and TMT1                                                      | 422 |

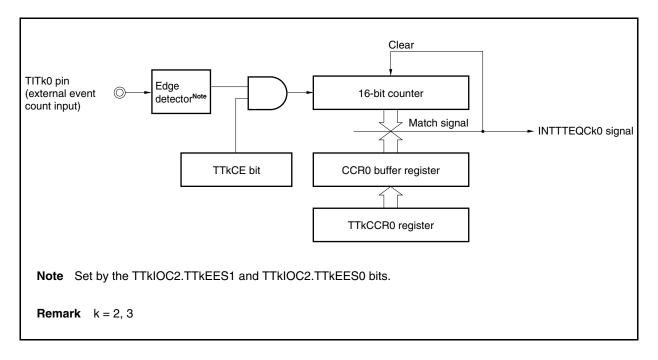

|        | 8.3.2   | TMT2 and TMT3                                                      | 425 |

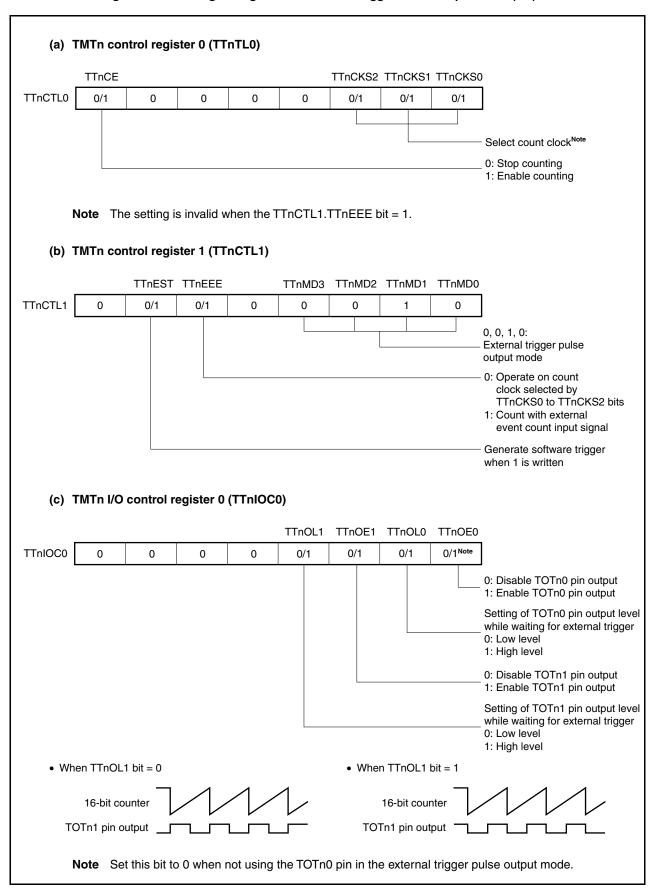

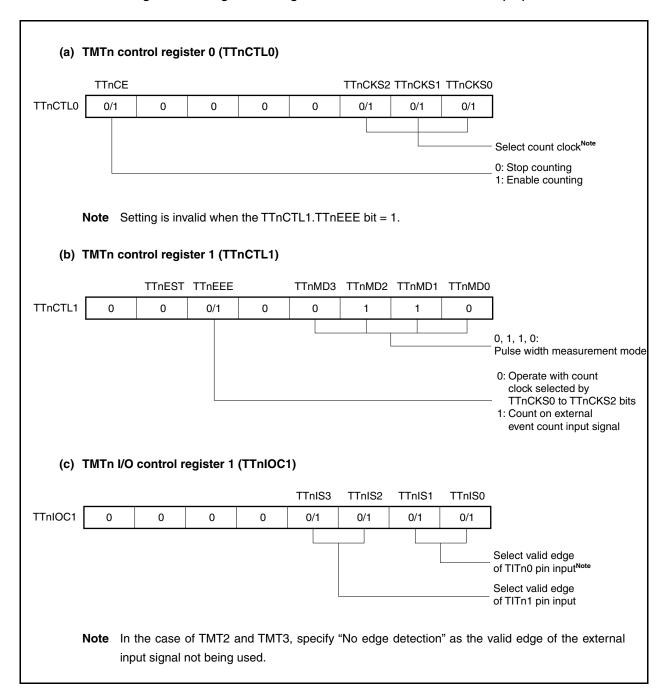

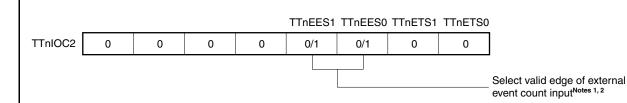

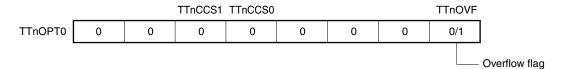

| 8.4    | Regis   | ters                                                               | 428 |

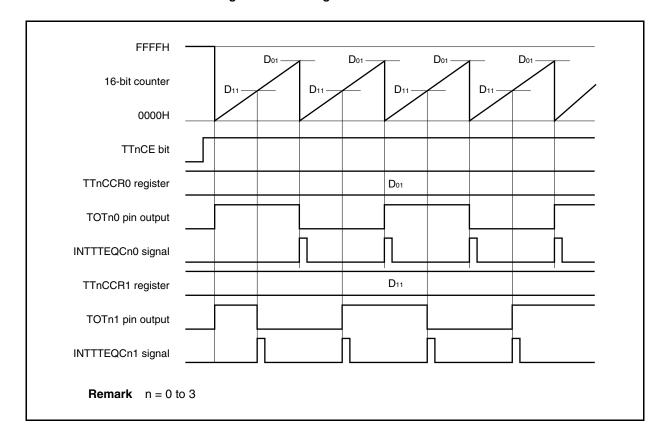

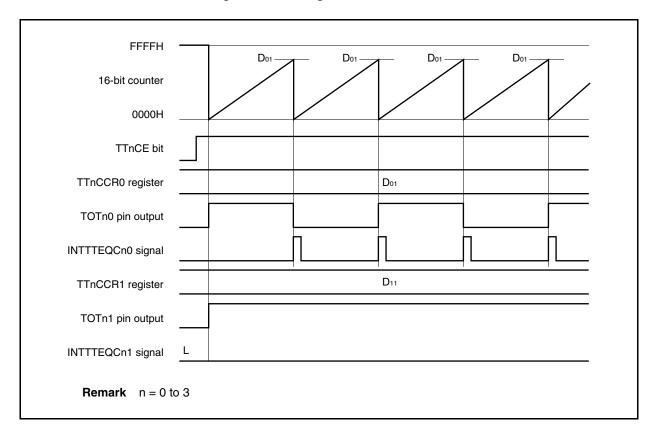

| 8.5    | Timer   | Output Operations                                                  | 448 |

| 8.6    | Opera   | ation                                                              | 449 |

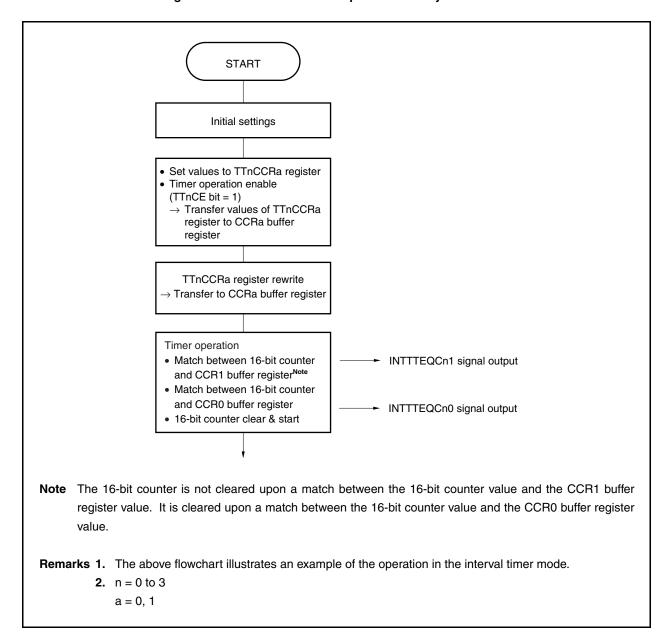

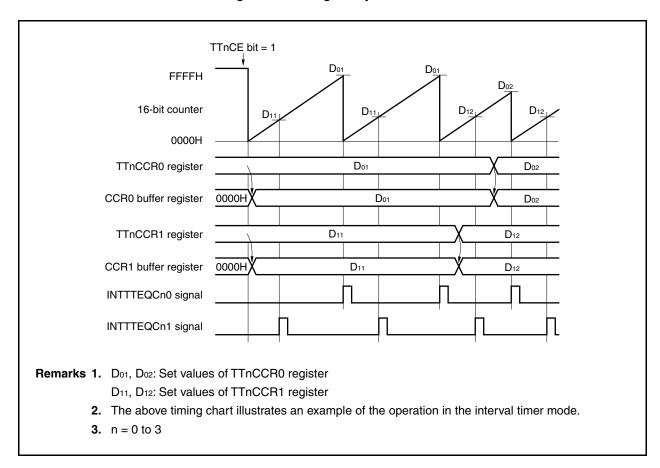

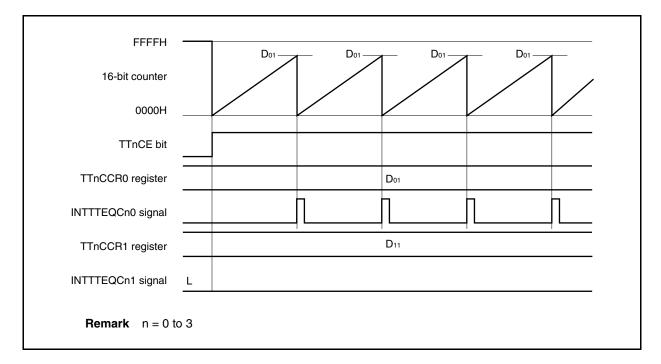

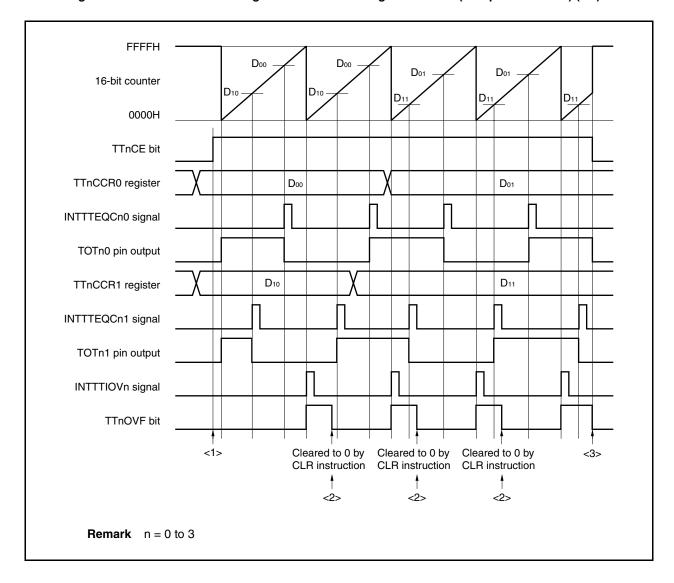

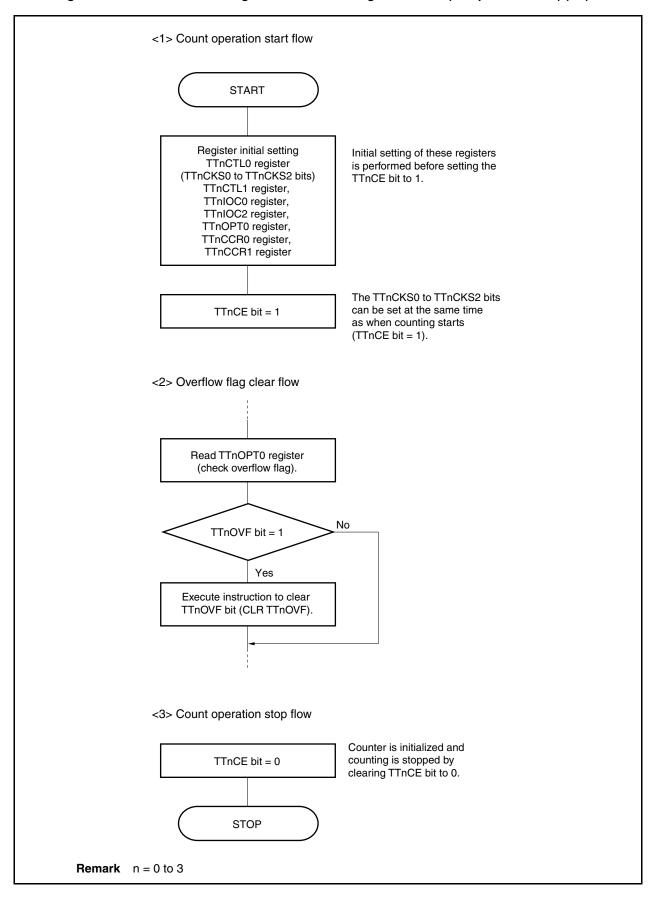

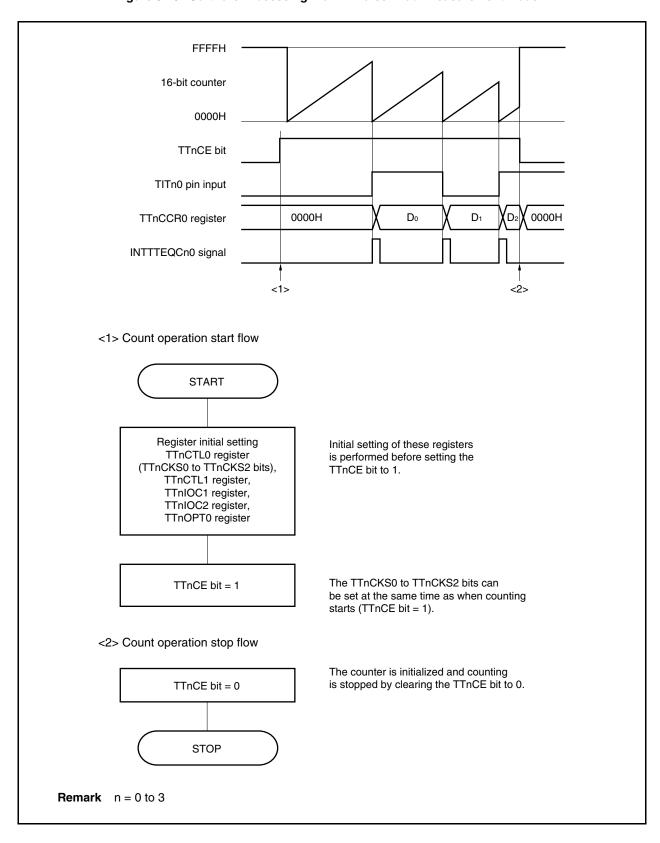

|        | 8.6.1   | Interval timer mode (TTnMD3 to TTnMD0 bits = 0000)                 | 459 |

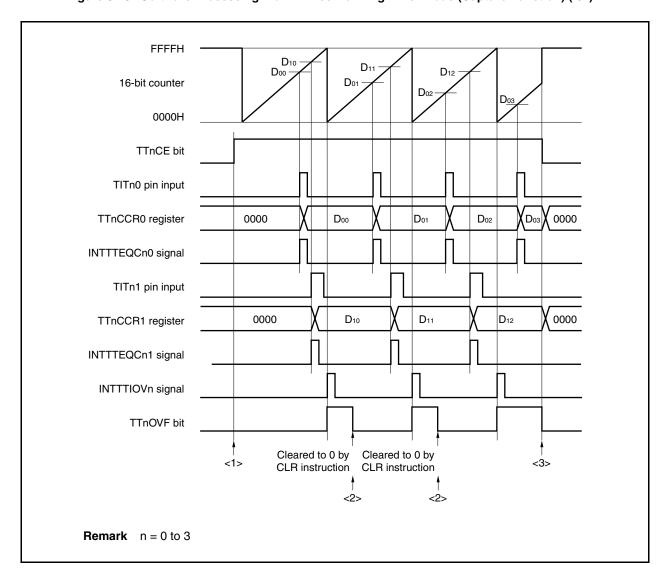

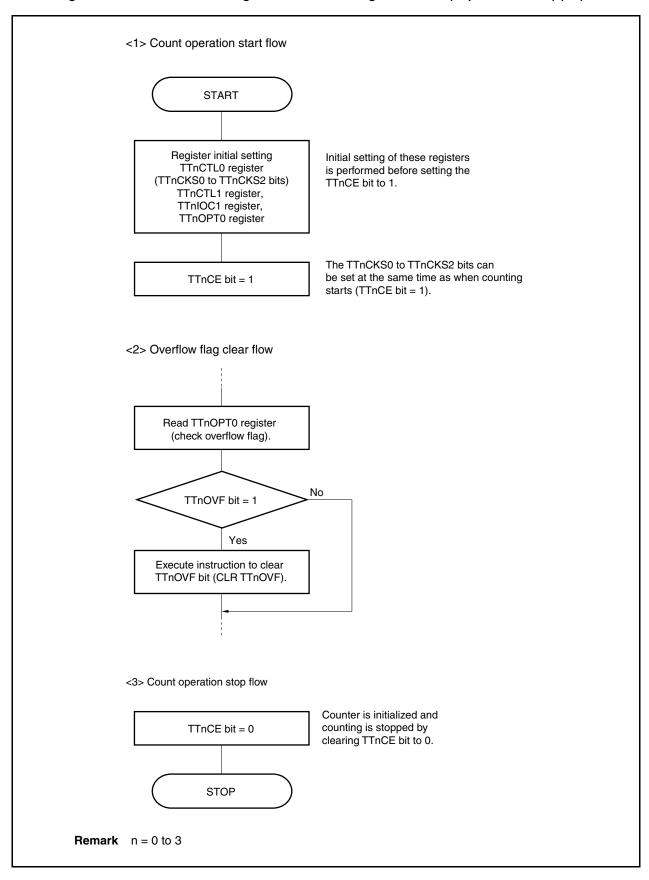

|        | 8.6.2   | External event count mode (TTnMD3 to TTnMD0 bits = 0001)           | 468 |

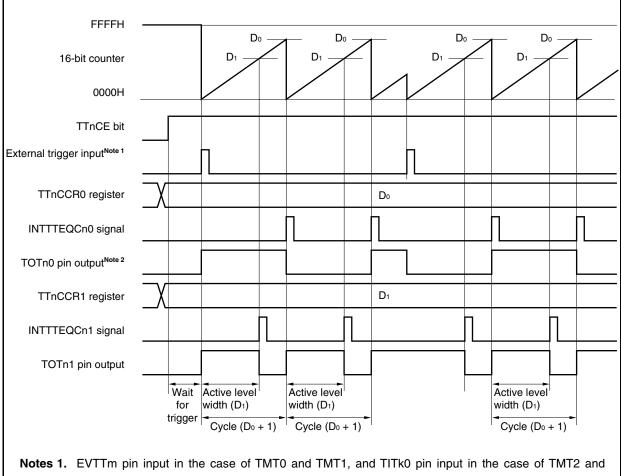

|        | 8.6.3   | External trigger pulse output mode (TTnMD3 to TTnMD0 bits = 0010)  | 479 |

|        | 8.6.4   | One-shot pulse output mode (TTnMD3 to TTnMD0 bits = 0011)          | 494 |

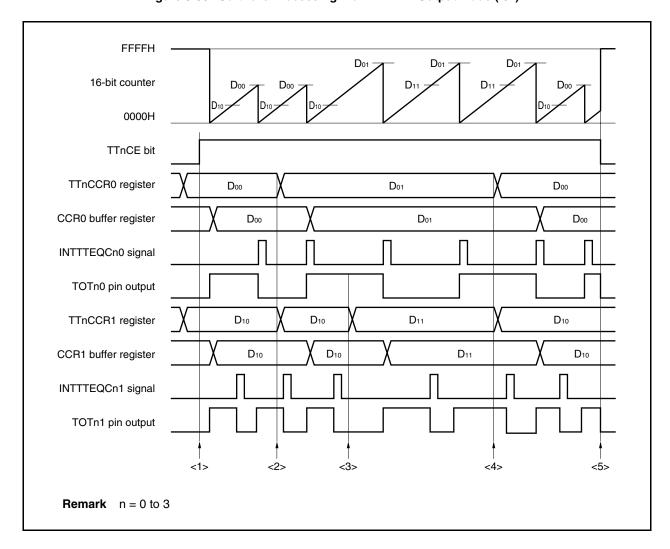

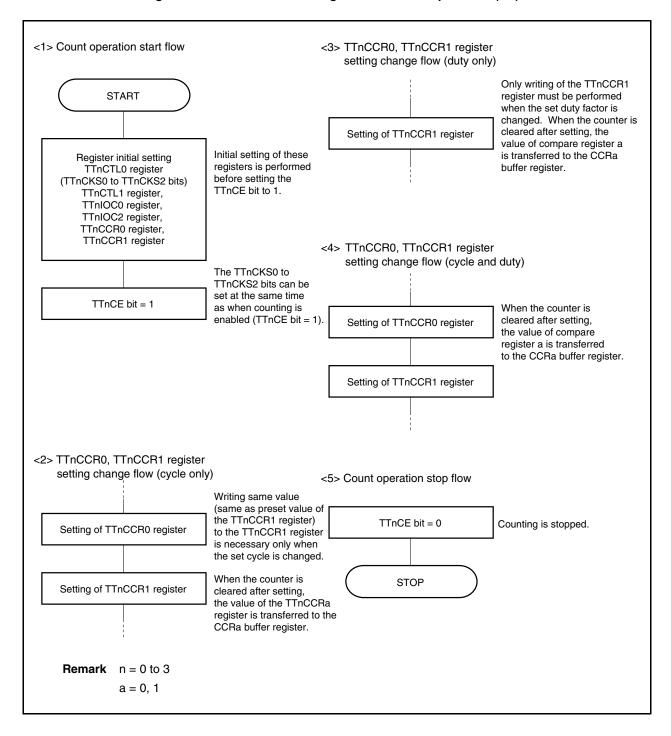

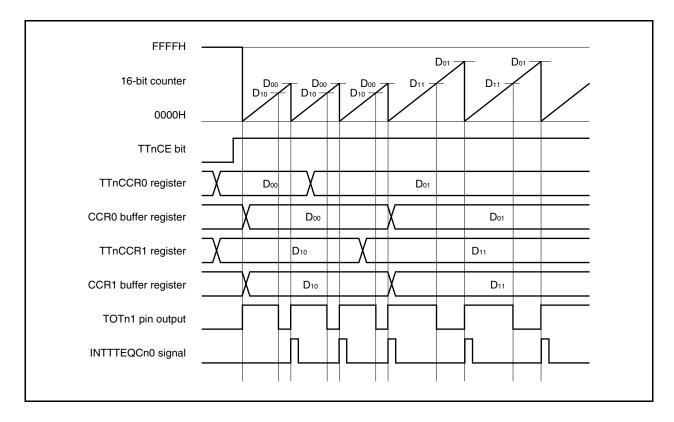

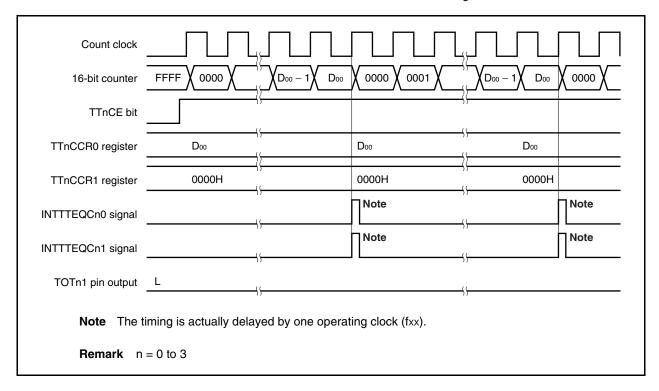

|        | 8.6.5   | PWM output mode (TTnMD3 to TTnMD0 bits = 0100)                     | 502 |

|        | 8.6.6   | Free-running timer mode (TTnMD3 to TTnMD0 bits = 0101)             | 512 |

|        |         |                                                                    |     |

|        | 8.6.7 Pulse width measurement mode (TTnMD3 to TTnMD0 bits = 0110)           | 529 |

|--------|-----------------------------------------------------------------------------|-----|

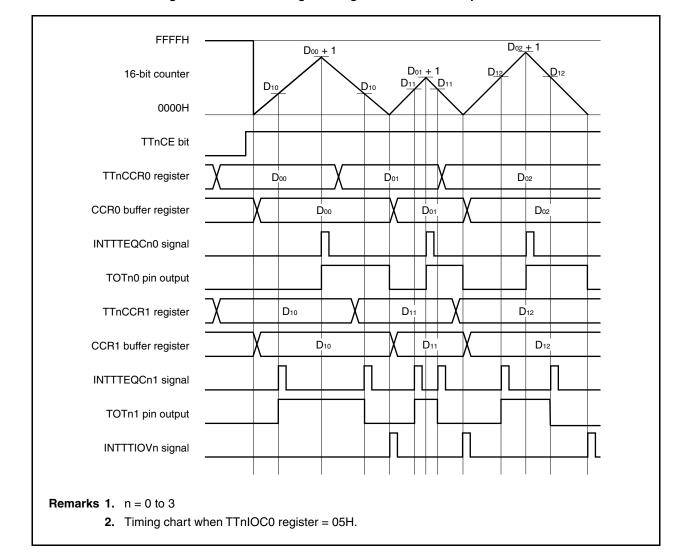

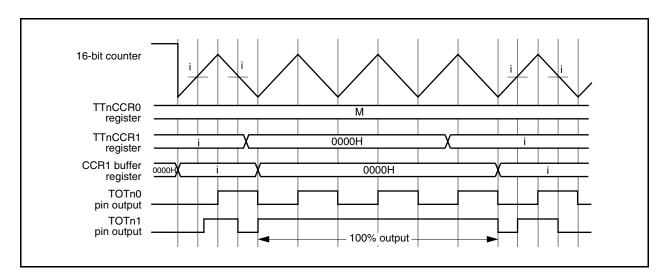

|        | 8.6.8 Triangular-wave PWM output mode (TTnMD3 to TTnMD0 bits = 0111)        | 536 |

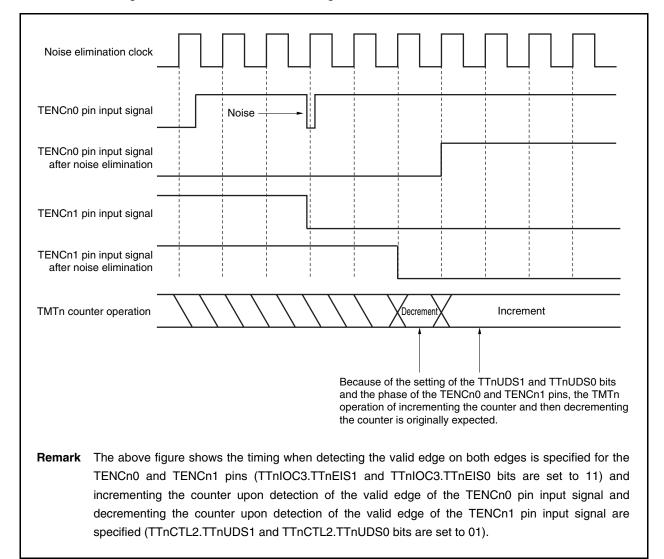

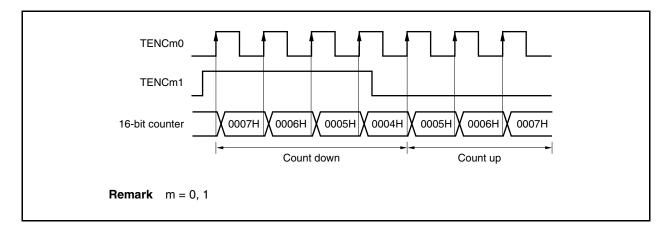

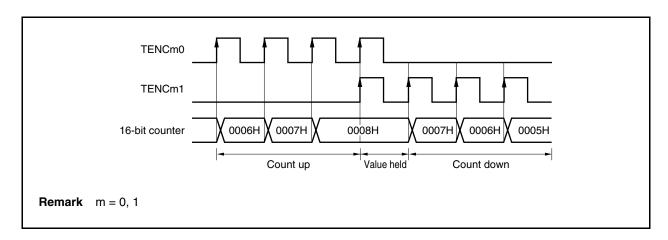

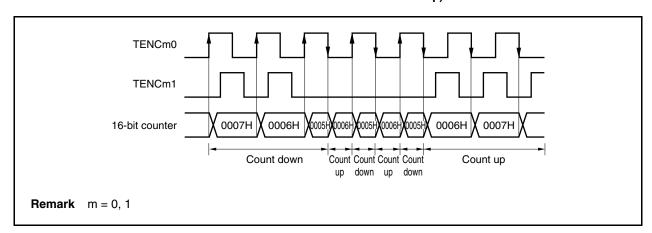

|        | 8.6.9 Encoder count function                                                | 540 |

|        | 8.6.10 Encoder compare mode (TTmMD3 to TTmMD0 bits = 1000)                  | 556 |

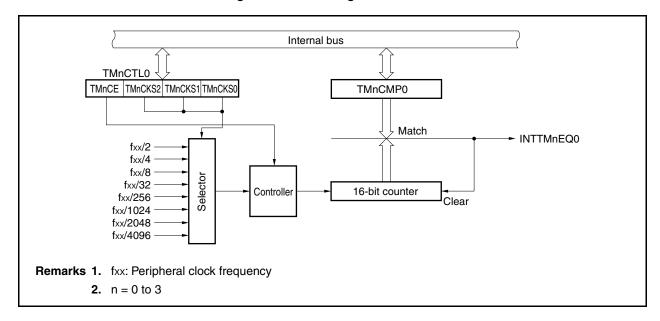

| CHAPTE | R 9 16-BIT INTERVAL TIMER M (TMM)                                           | 564 |

| 9.1    | Overview                                                                    | 564 |

| 9.2    | Configuration                                                               | 565 |

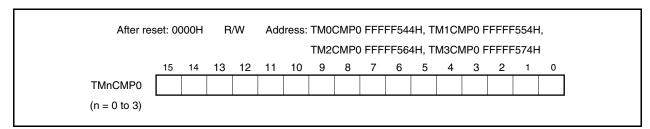

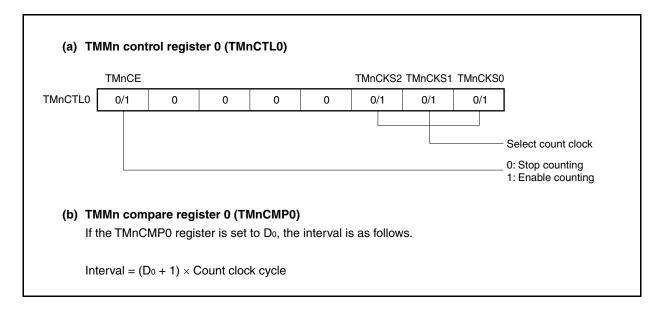

| 9.3    | Control Register                                                            | 566 |

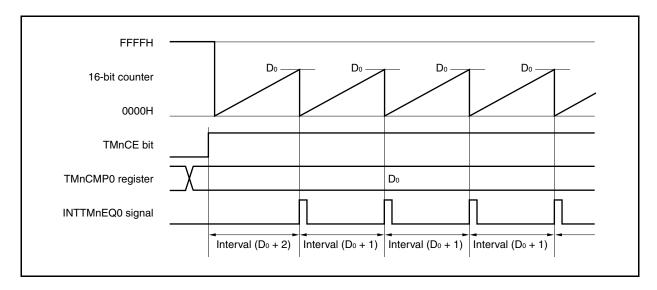

| 9.4    | Operation                                                                   | 567 |

|        | 9.4.1 Interval timer mode                                                   | 567 |

| 9.5    | Cautions                                                                    | 571 |

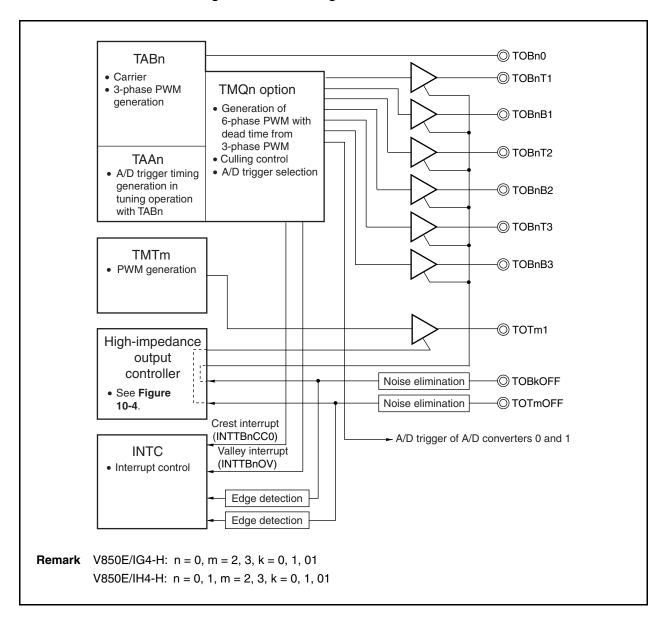

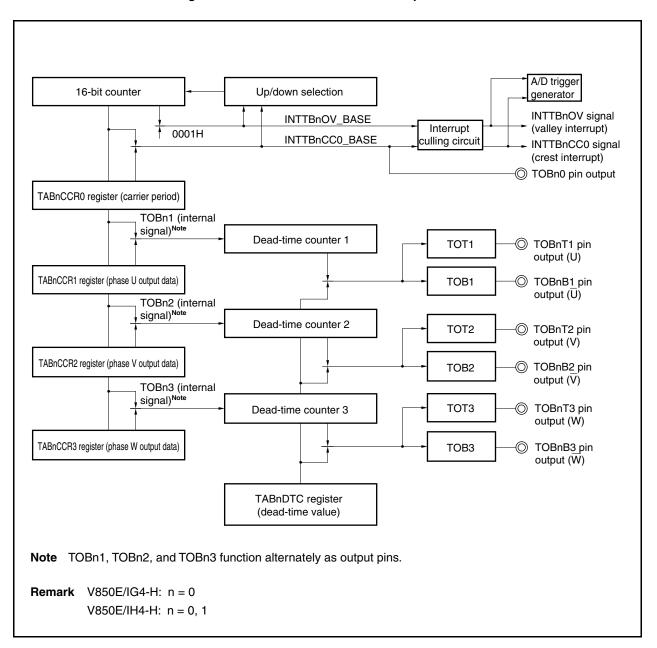

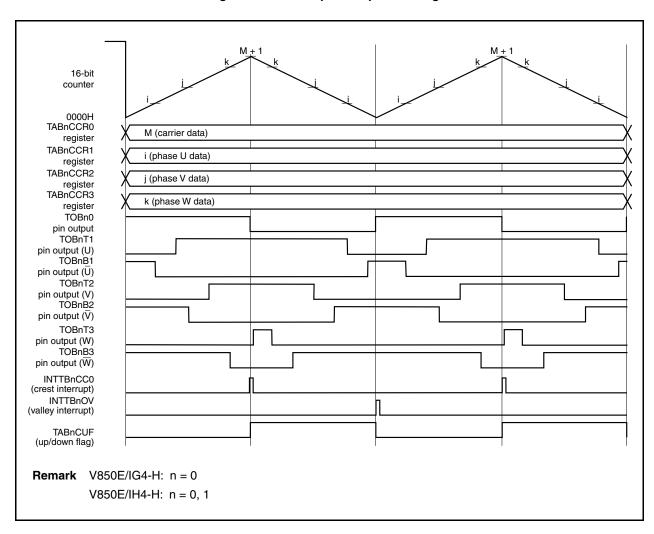

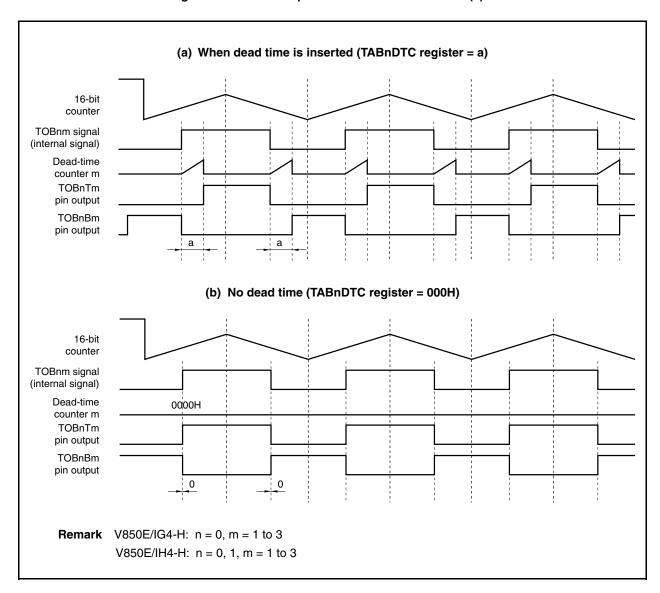

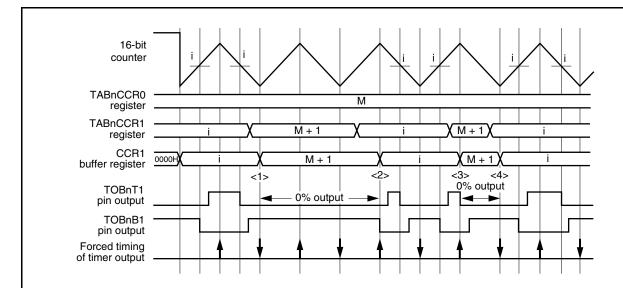

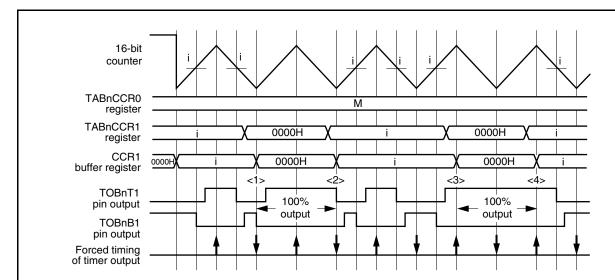

| CHAPTE | R 10 MOTOR CONTROL FUNCTION                                                 | 572 |

| 10.1   | Functional Overview                                                         | 572 |

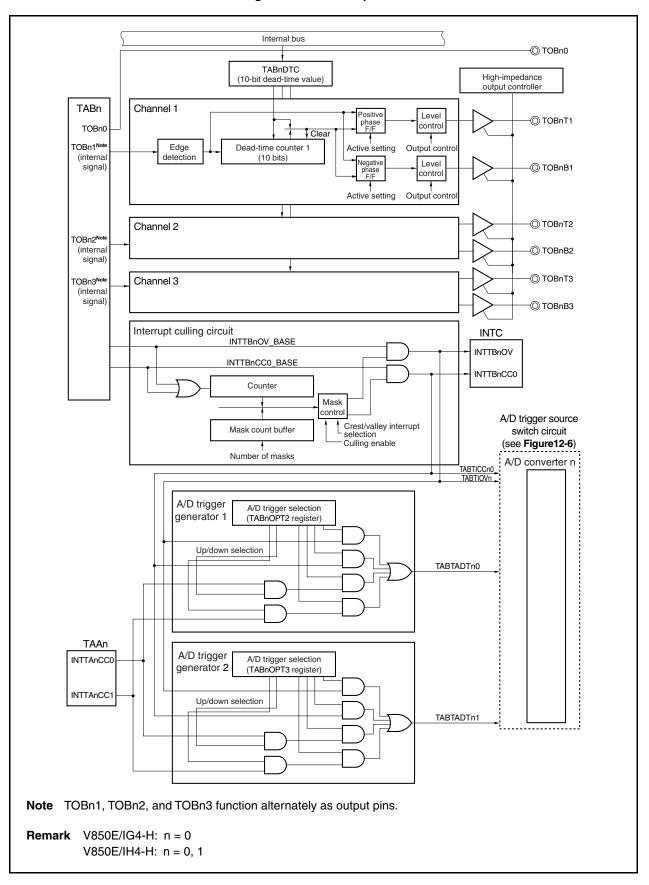

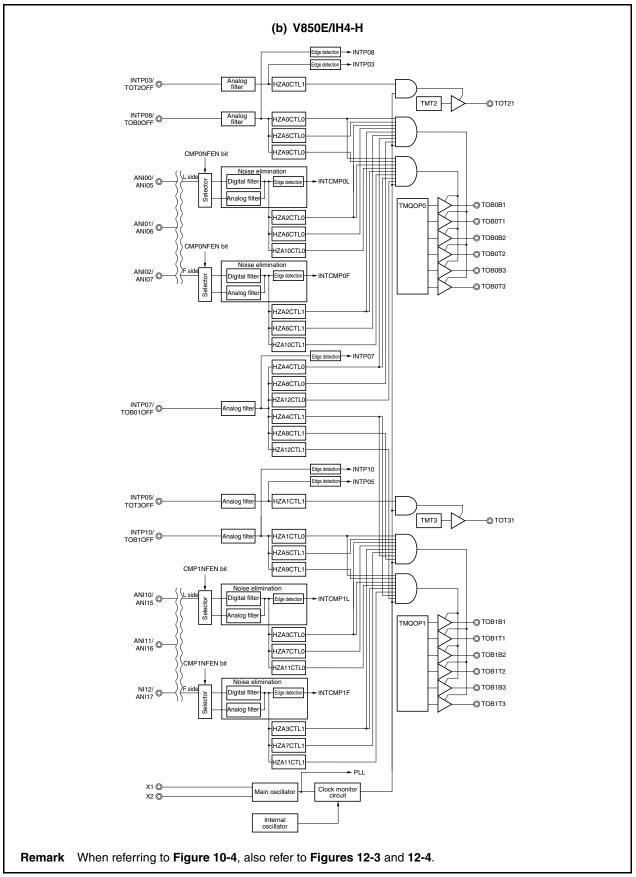

| 10.2   | Configuration                                                               | 573 |

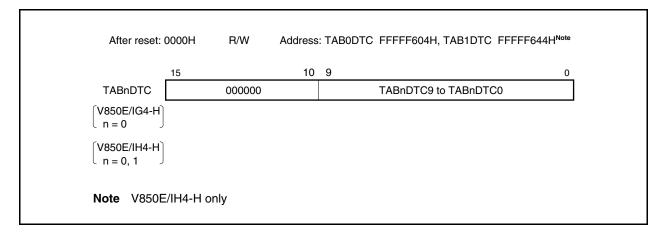

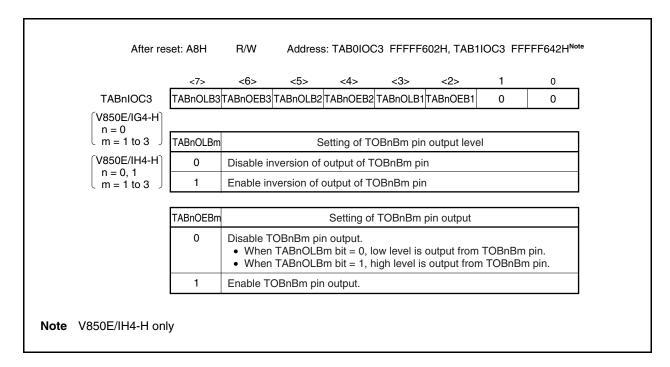

| 10.3   | Control Registers                                                           | 577 |

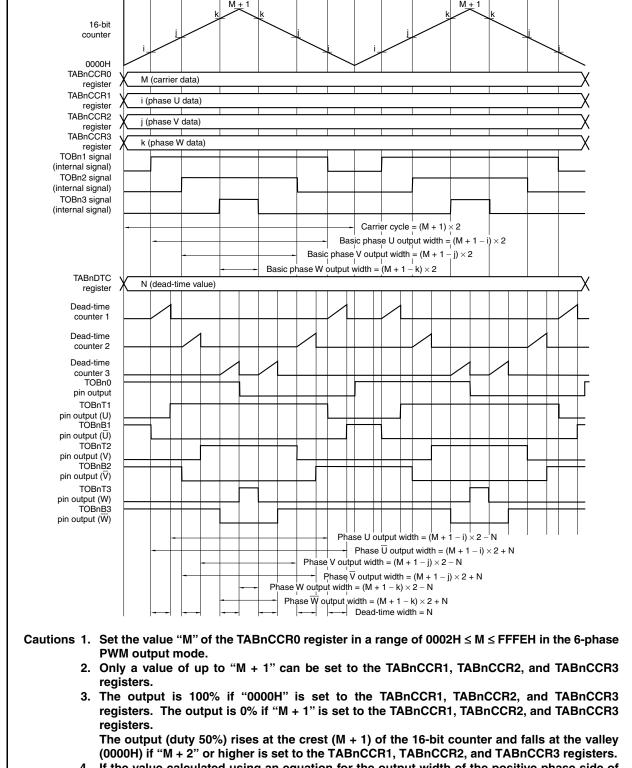

| 10.4   | Operation                                                                   | 596 |

|        | 10.4.1 System outline                                                       | 596 |

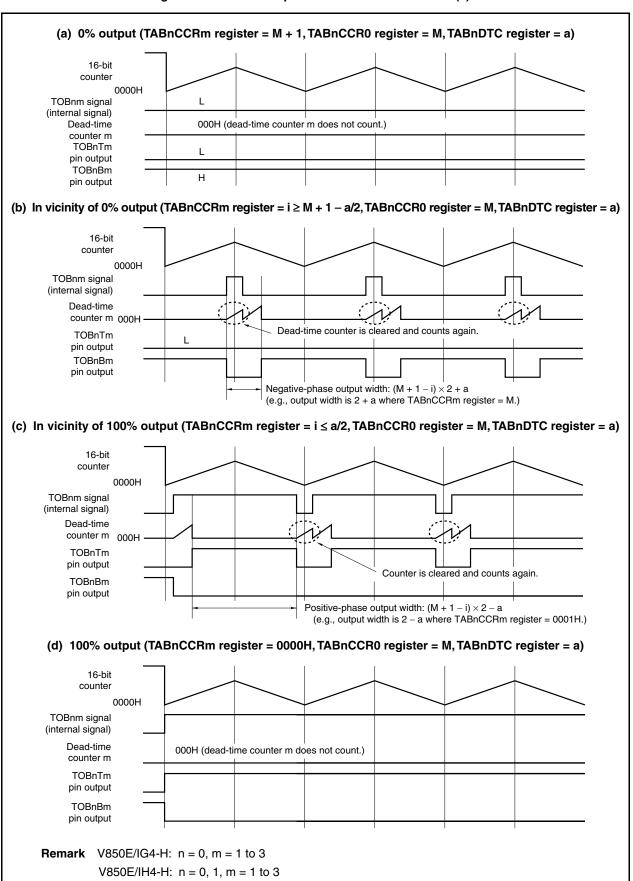

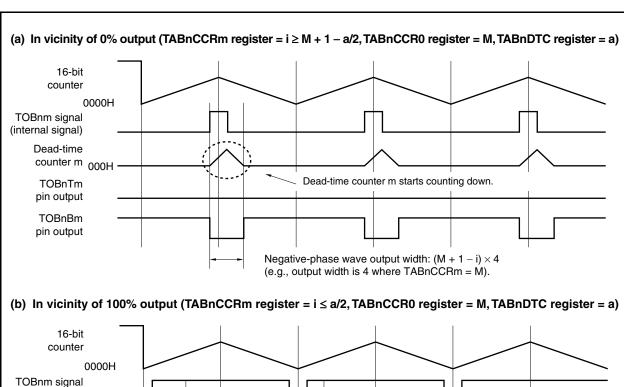

|        | 10.4.2 Dead-time control (generation of negative-phase wave signal)         |     |

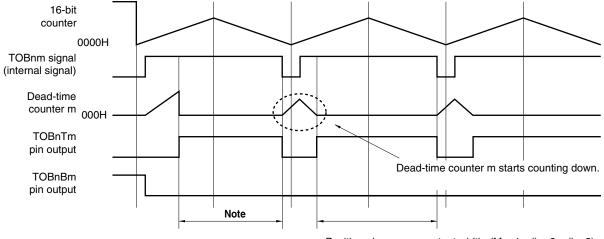

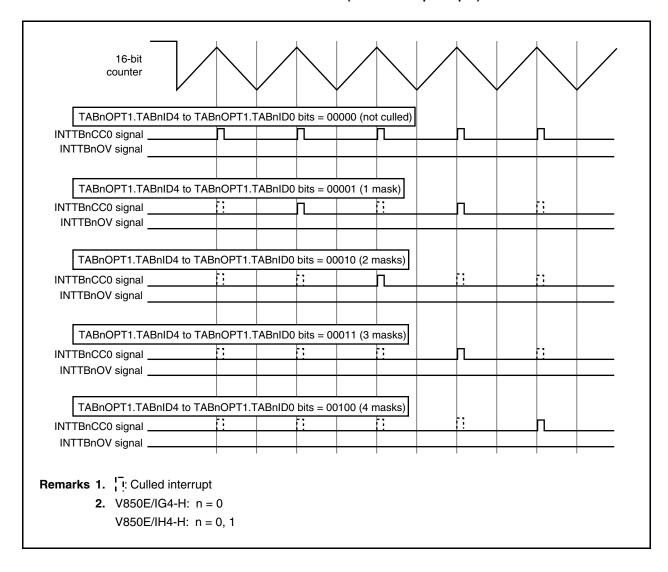

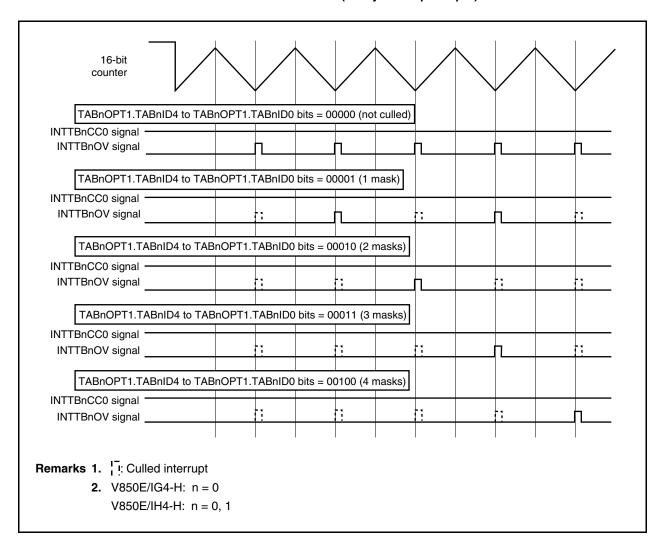

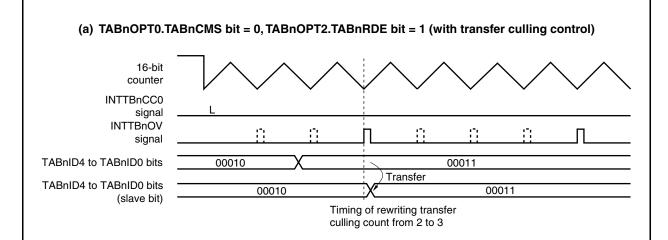

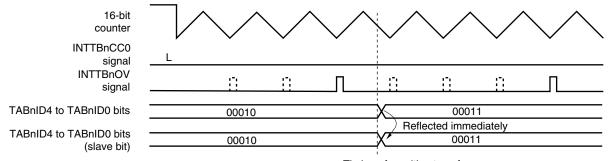

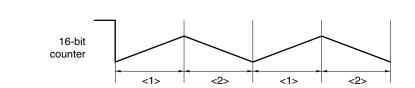

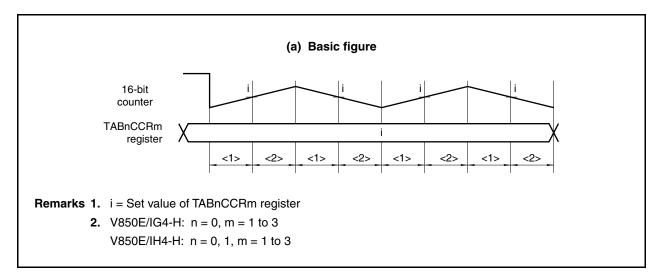

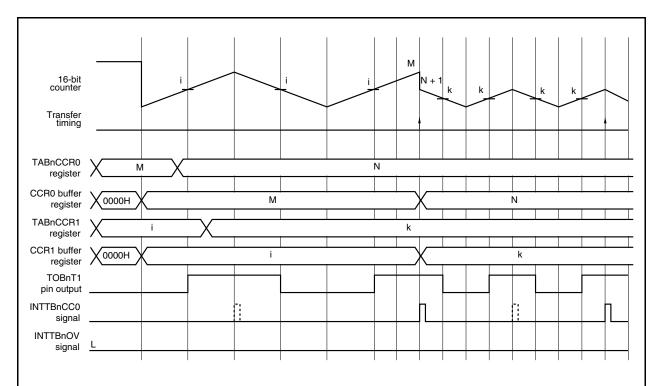

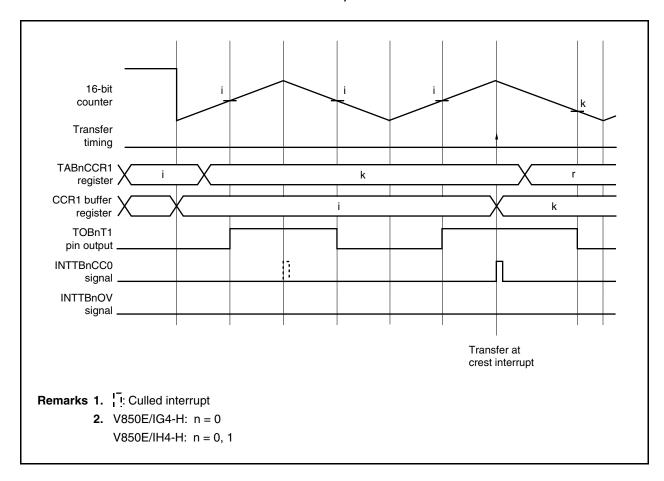

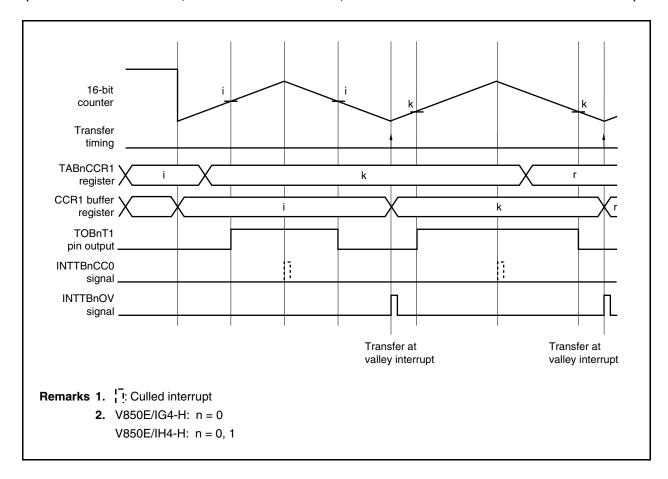

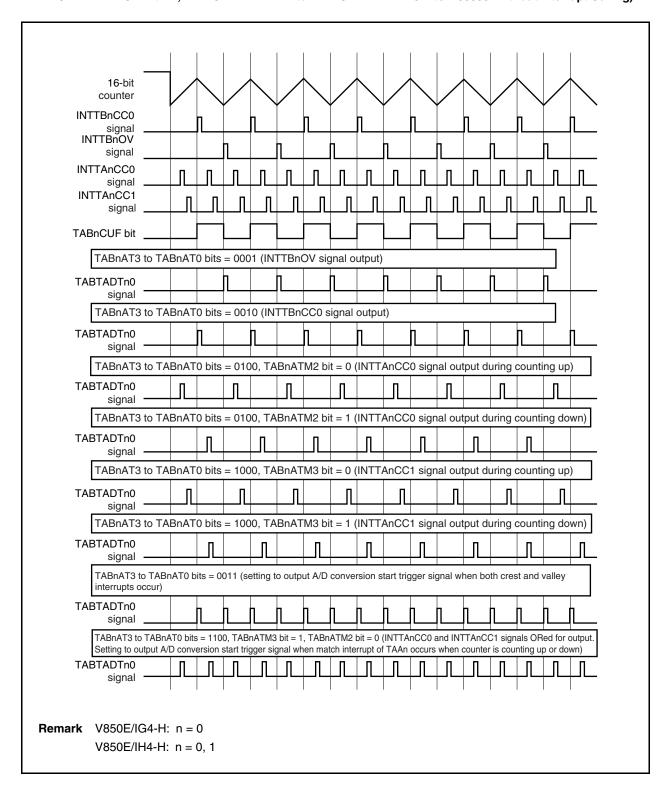

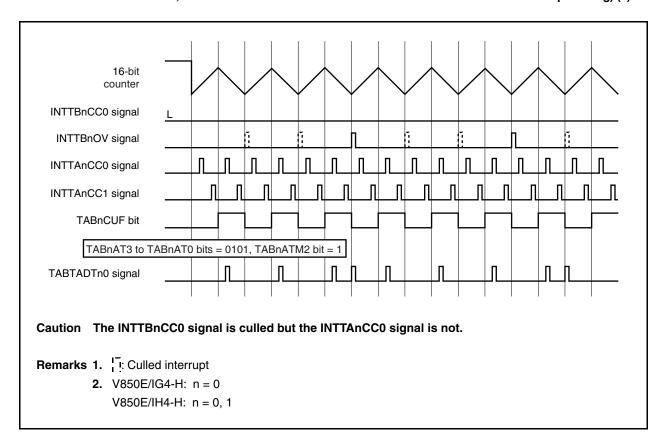

|        | 10.4.3 Interrupt culling function                                           | 608 |

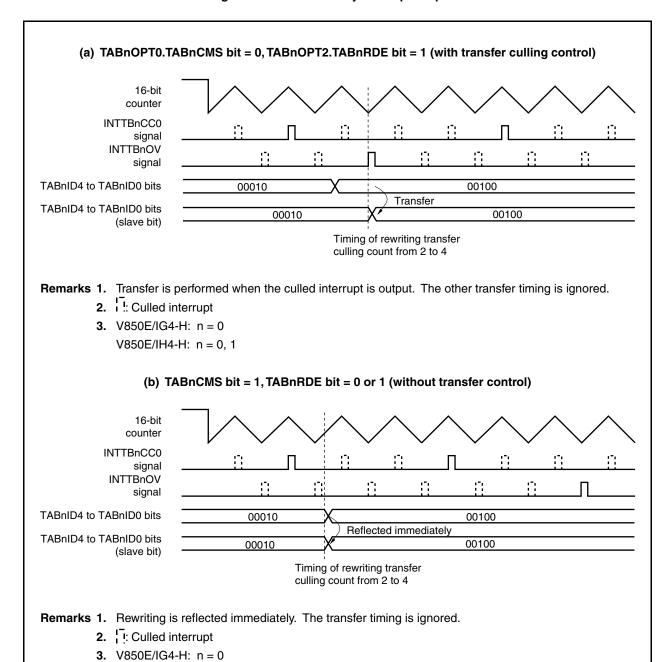

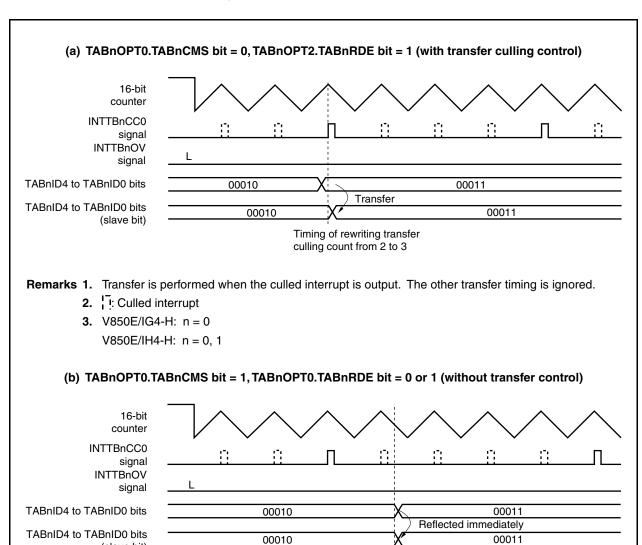

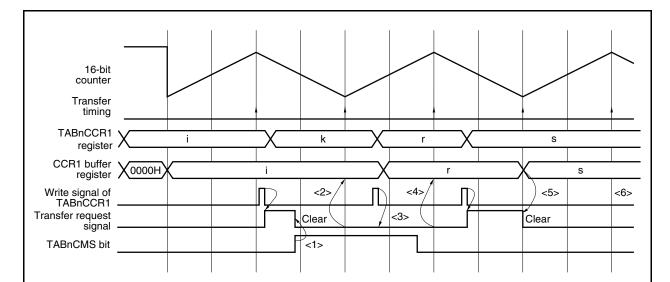

|        | 10.4.4 Operation to rewrite register with transfer function                 | 615 |

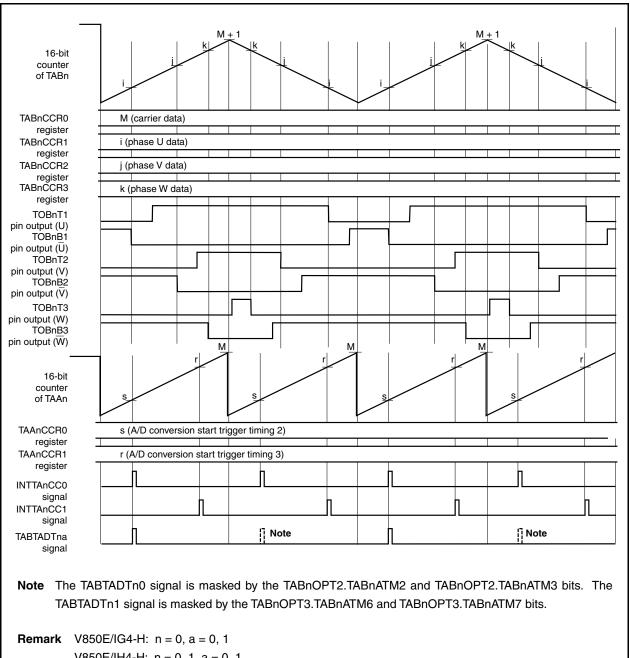

|        | 10.4.5 TAAn tuning operation for A/D conversion start trigger signal output | 633 |

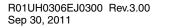

|        | 10.4.6 A/D conversion start trigger output function                         | 636 |

| CHAPTE | R 11 WATCHDOG TIMER FUNCTIONS                                               | 641 |

| 11.1   | Functions                                                                   | 641 |

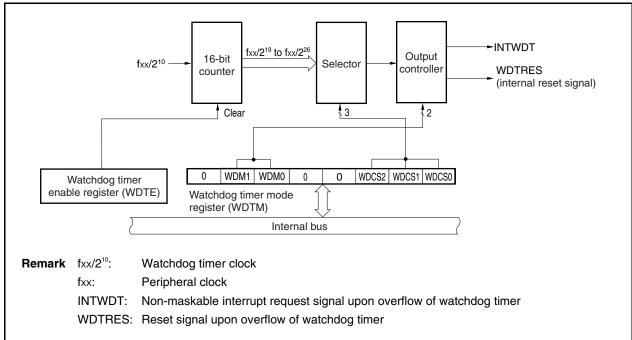

| 11.2   | Configuration                                                               | 641 |

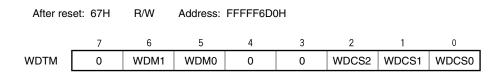

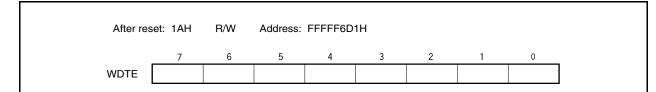

| 11.3   | Control Registers                                                           | 642 |

| 11.4   | Operation                                                                   | 643 |

| 11.5   | Caution                                                                     | 643 |

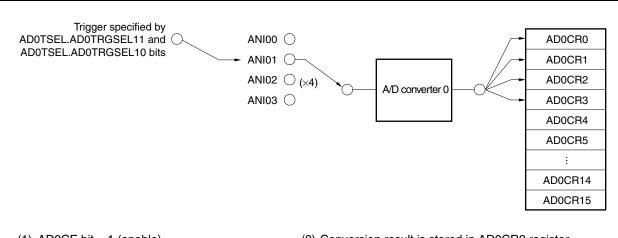

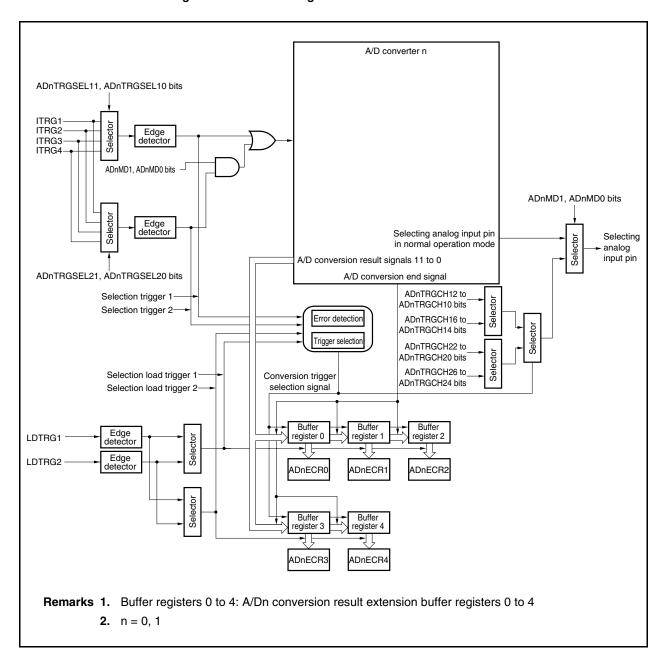

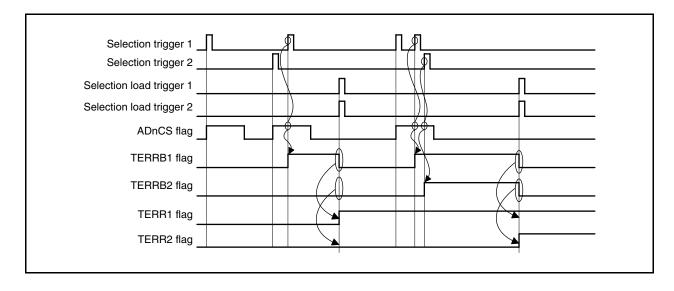

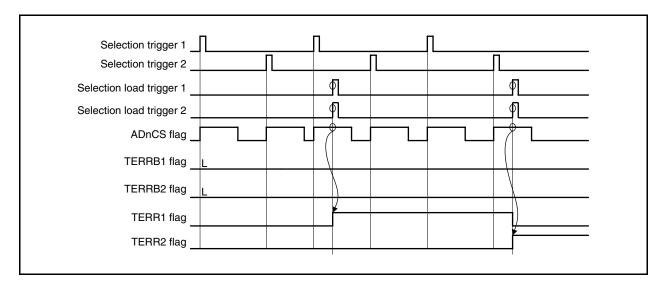

| CHAPTE | R 12 A/D CONVERTERS 0 AND 1                                                 | 644 |

| 12.1   | Features                                                                    | 644 |

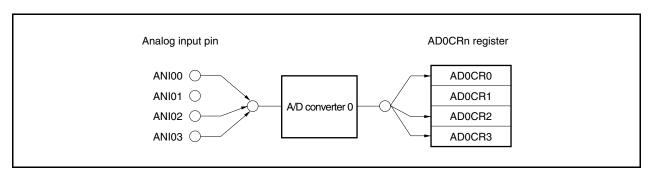

| 12.2   | Configuration                                                               | 646 |

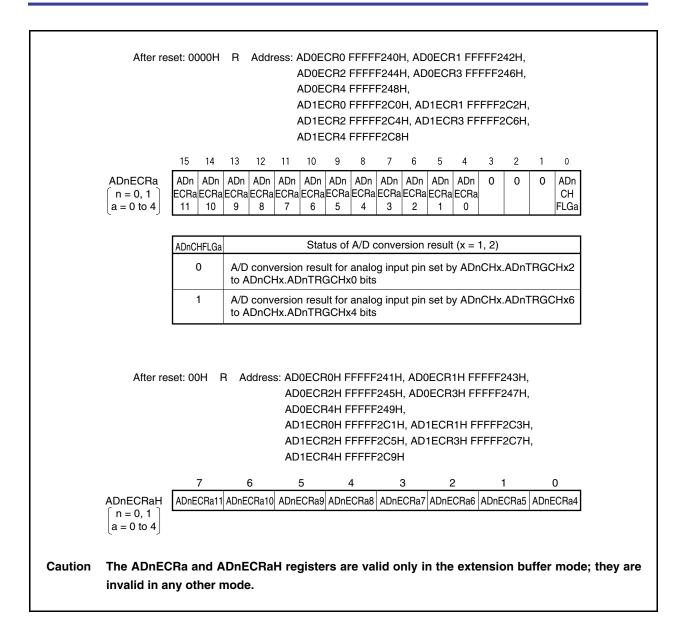

| 12.3   | Control Registers                                                           | 657 |

| 12.4   | Operation                                                                   | 690 |

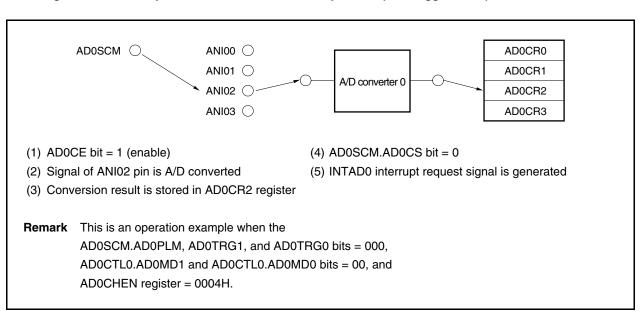

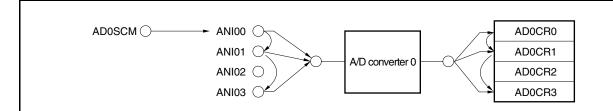

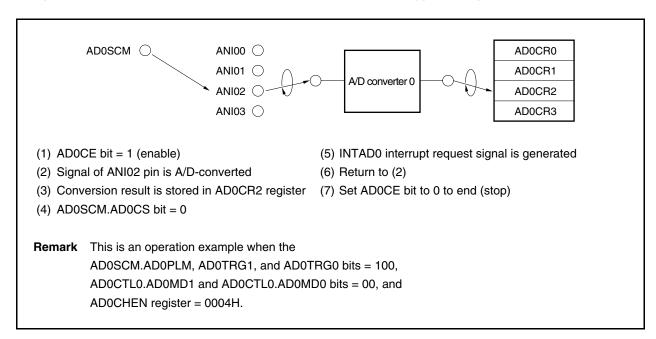

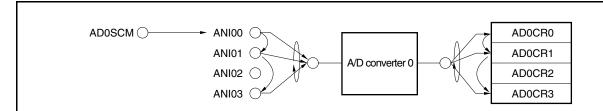

|        | 12.4.1 Basic operation                                                      | 690 |

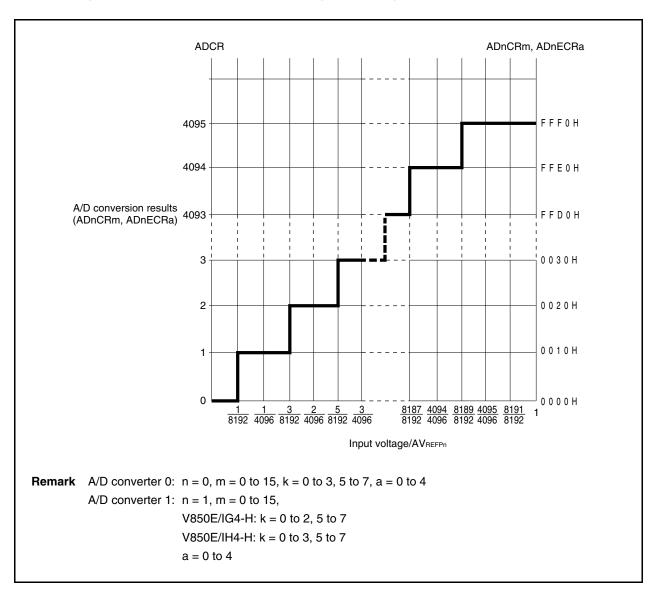

|        | 12.4.2 Input voltage and conversion result                                  | 692 |

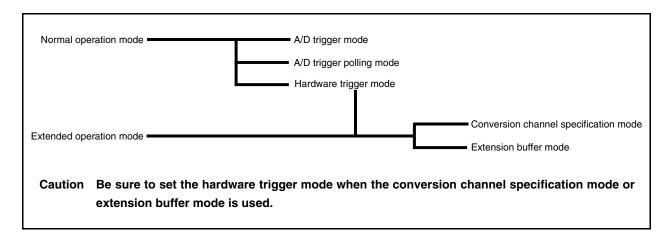

|        | 12.4.3 Operation mode                                                       | 694 |

|        | 12.4.4 Operation setting                                                    | 694 |

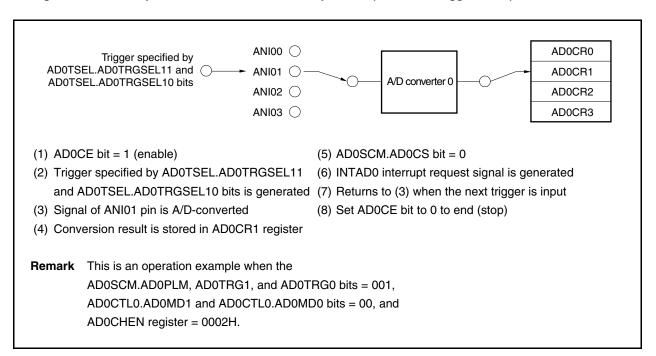

|        | 12.4.5 Operation of 1-channel conversion                                    | 695 |

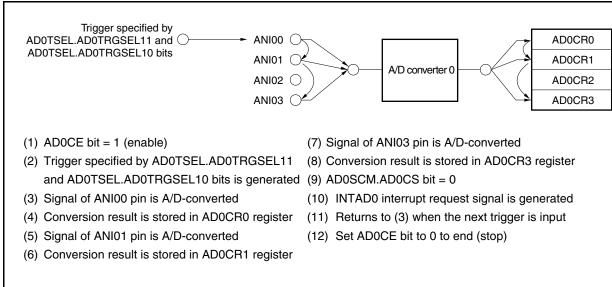

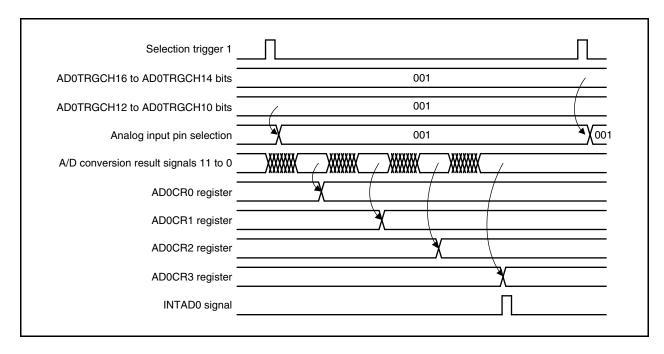

|        | 12.4.6 Operation of multiple channel conversion                             | 696 |

|        | 12.4.7 A/D trigger mode (normal operation mode)                             | 698 |

|        | 12.4.8 A/D trigger polling mode (normal operation mode)                     | 700 |

|        | 12.4.9  | Hardware trigger mode (normal operation mode)                                        | 702 |

|--------|---------|--------------------------------------------------------------------------------------|-----|

|        | 12.4.10 | Conversion channel specification mode (extension operation mode)                     | 704 |

|        | 12.4.11 | Extension buffer mode (extension operation mode)                                     | 706 |

| 12.5   | Interna | l Equivalent Circuit                                                                 | 712 |

| 12.6   | Cautio  | ns                                                                                   | 713 |

|        | 12.6.1  | Stopping conversion operation                                                        | 713 |

|        | 12.6.2  | Interval of trigger during conversion operation in hardware trigger mode, conversion |     |

|        |         | channel specification mode, and extension buffer mode                                | 713 |

|        | 12.6.3  | Writing to ADnSCM register                                                           | 713 |

|        | 12.6.4  | A/D conversion start timing                                                          | 714 |

|        | 12.6.5  | Operation in standby mode                                                            | 714 |

|        | 12.6.6  | Timing of accepting trigger in conversion channel specification mode and extension   |     |

|        |         | buffer mode                                                                          | 714 |

|        | 12.6.7  | Variation of A/D conversion results                                                  | 714 |

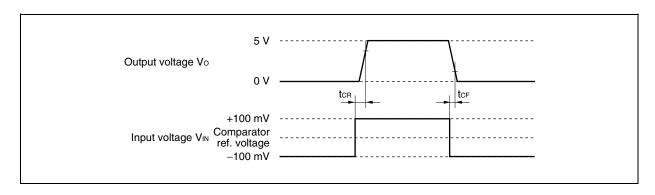

|        | 12.6.8  | A/D conversion result hysteresis characteristics                                     | 715 |

|        | 12.6.9  | A/D conversion trigger interval for continuous conversion                            | 715 |

| 12.7   | How to  | Read A/D Converter Characteristics Table                                             | 716 |

| CHAPTE | R 13 A  | /D CONVERTER 2                                                                       | 720 |

| 13.1   | Feature | es                                                                                   | 720 |

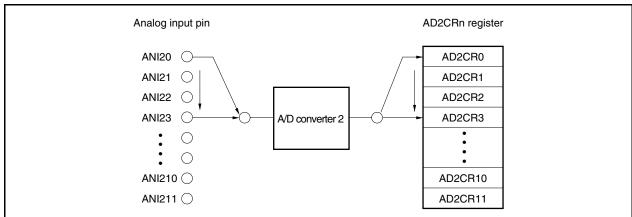

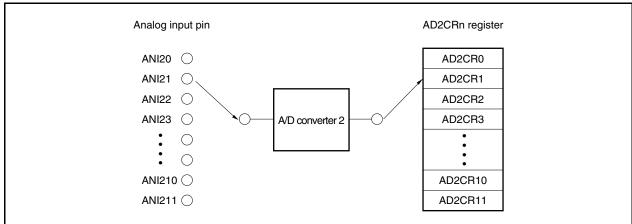

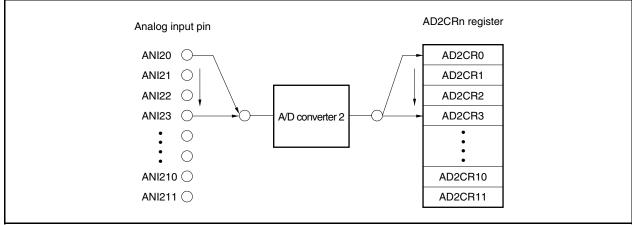

| 13.2   | Config  | uration                                                                              | 721 |

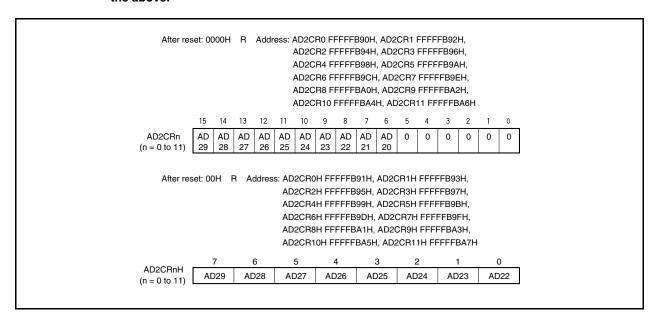

| 13.3   | Contro  | I Registers                                                                          | 724 |

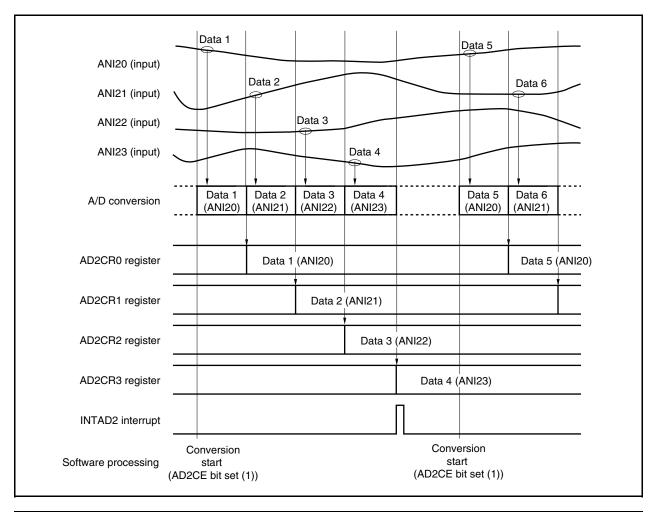

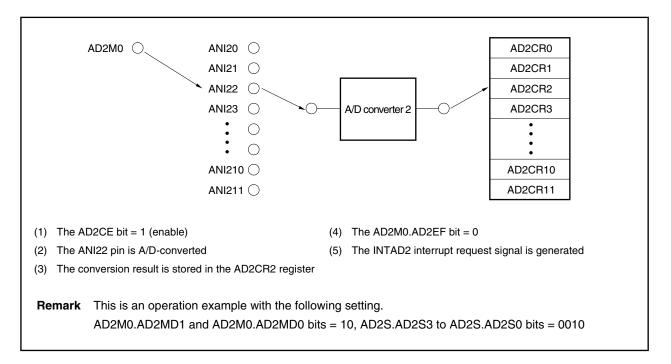

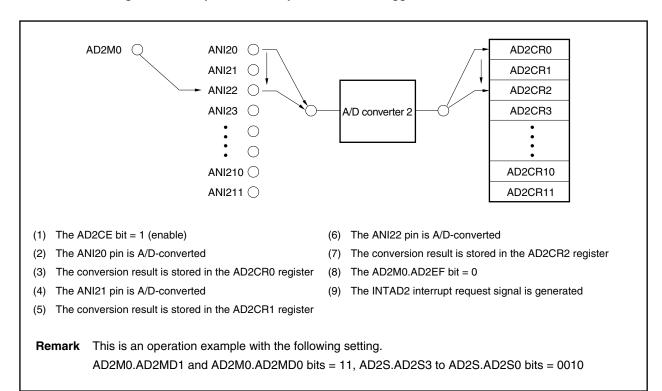

| 13.4   | Operat  | ion                                                                                  | 730 |

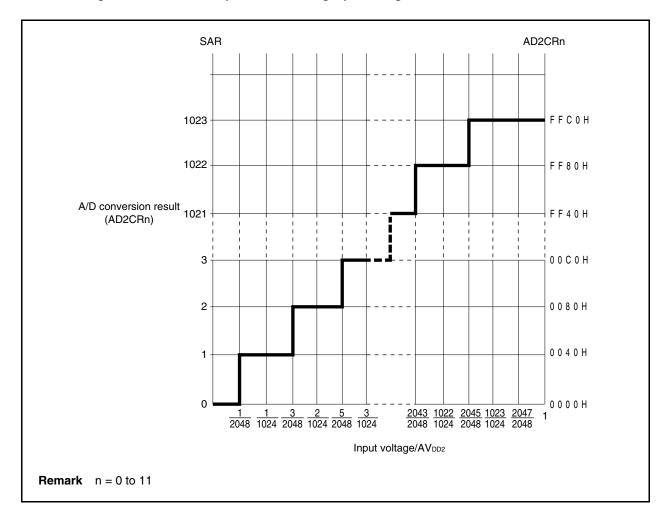

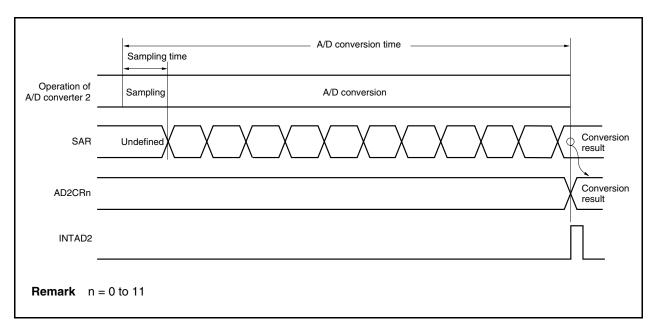

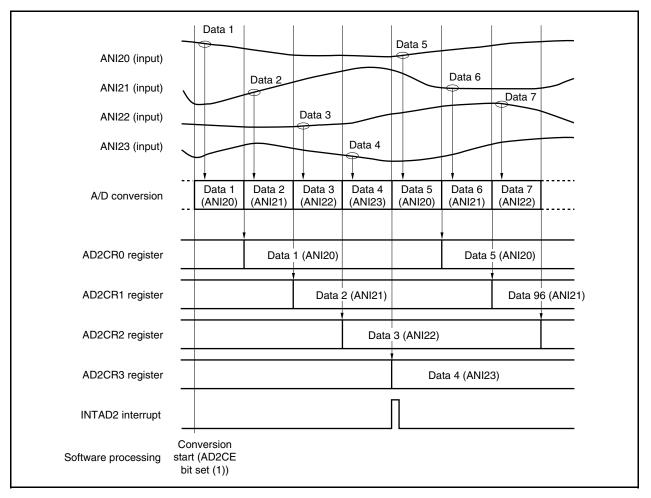

|        | 13.4.1  | Basic operation                                                                      | 730 |

|        | 13.4.2  | Trigger mode                                                                         | 732 |

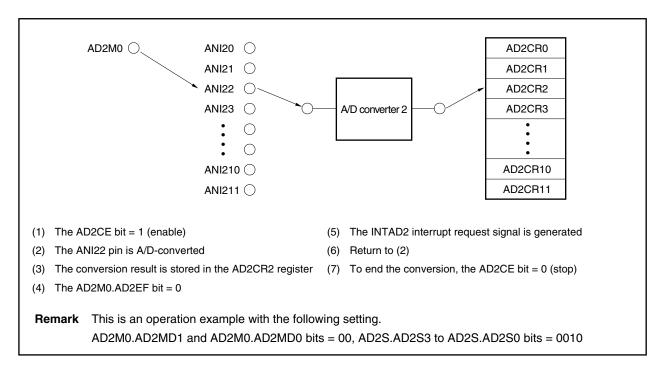

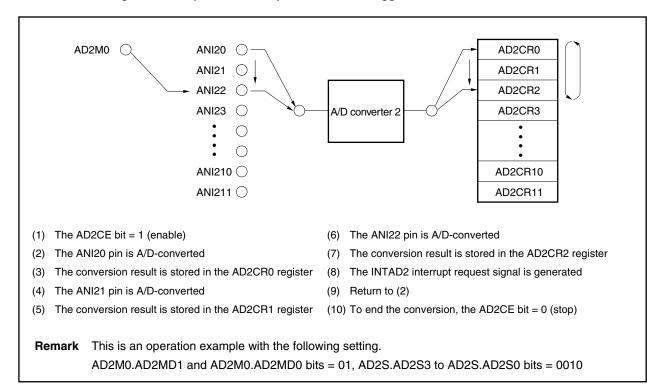

|        | 13.4.3  | Operation mode                                                                       | 733 |

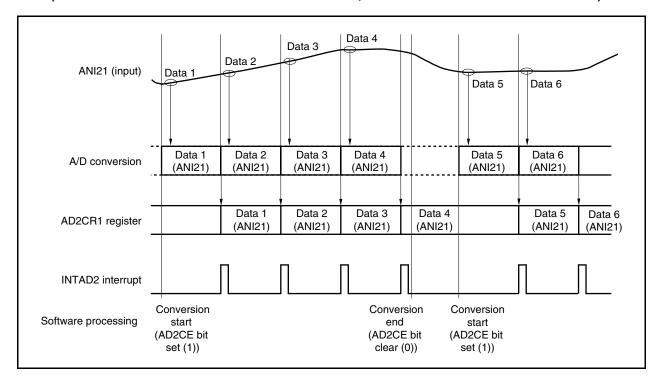

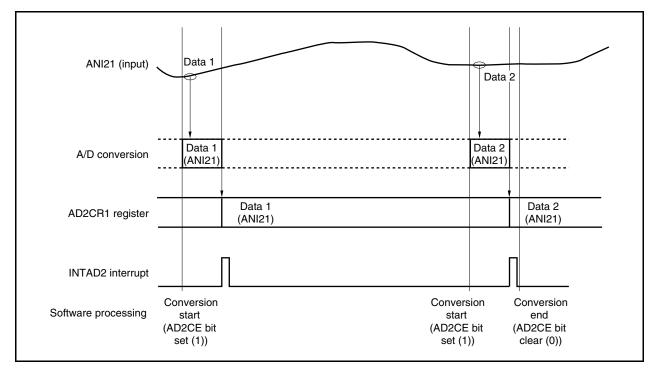

| 13.5   | Operat  | ion in Software Trigger Mode                                                         | 740 |

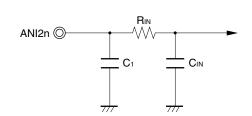

| 13.6   | Interna | l Equivalent Circuit                                                                 | 744 |

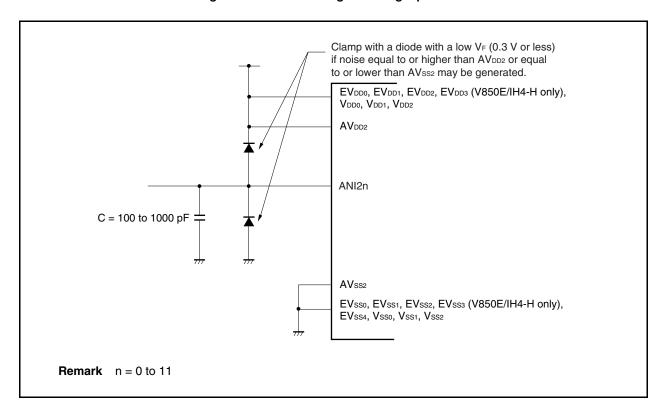

| 13.7   | Cautio  | ns                                                                                   | 745 |

| 13.8   | How to  | Read A/D Converter Characteristics Table                                             | 748 |

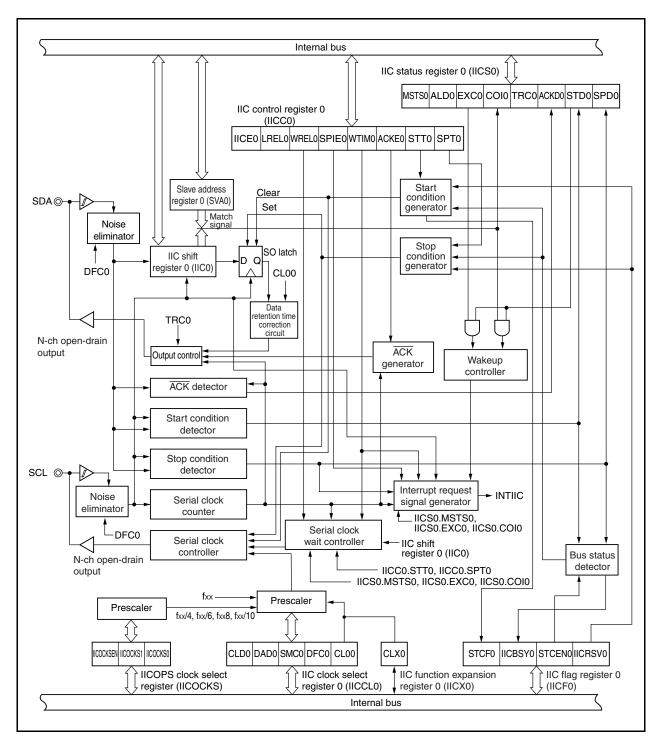

| CHAPTE | R 14 A  | SYNCHRONOUS SERIAL INTERFACE A (UARTA)                                               | 749 |

| 14.1   |         | es                                                                                   |     |

| 14.2   |         | uration                                                                              |     |

|        | 1421    | Pin functions of each channel                                                        |     |

| 14.3   |         | Switching Between UARTA and Other Serial Interface                                   |     |

|        | 14.3.1  | Mode switching between UARTA0 and CSIF0                                              |     |

|        | 14.3.2  | Mode switching between UARTA1 and I <sup>2</sup> C                                   |     |

|        | 14.3.3  | Mode switching between UARTA2 and CSIF1                                              |     |

| 14.4   |         | I Registers                                                                          |     |

| 14.5   |         | pt Request Signals                                                                   |     |

| 14.6   | '       | ion                                                                                  |     |

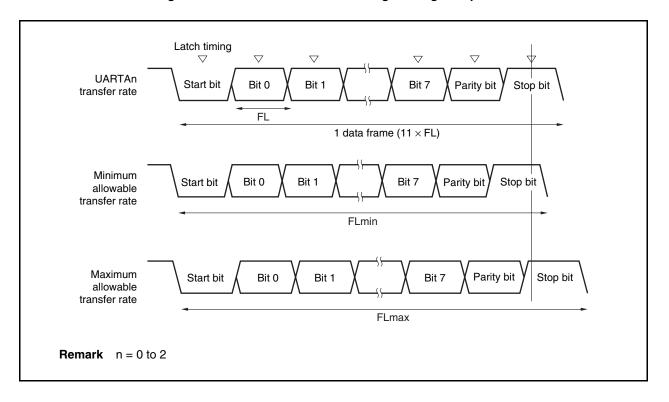

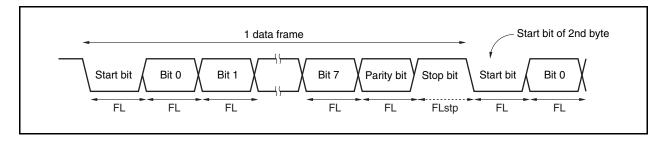

|        | 14.6.1  | Data format                                                                          |     |

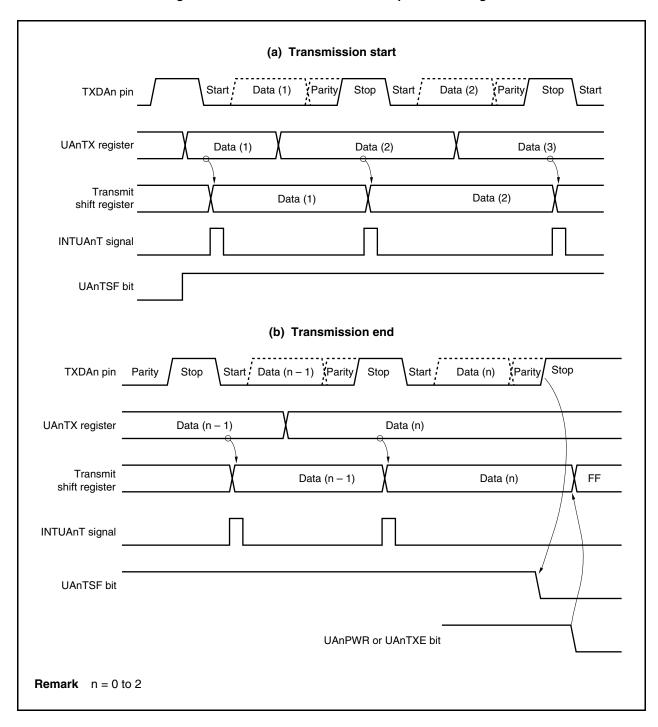

|        | 14.6.2  | UART transmission                                                                    |     |

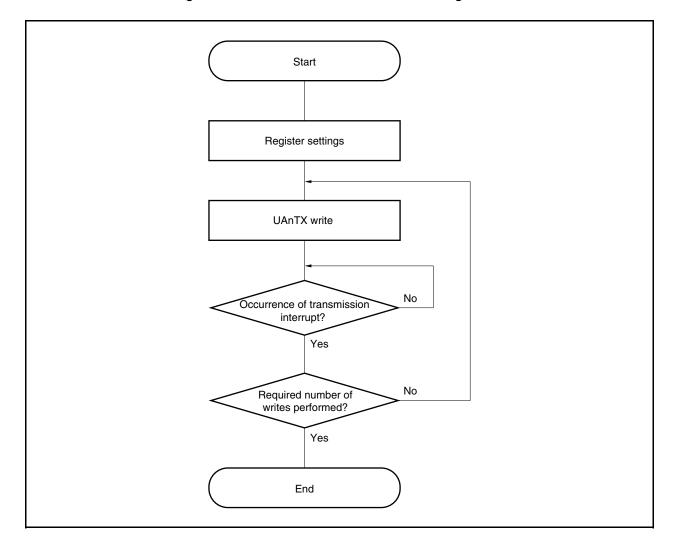

|        | 14.6.3  | Continuous transmission procedure                                                    |     |

|        |         | •                                                                                    | _   |

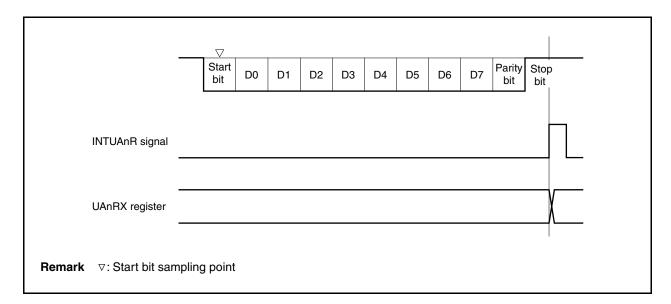

|        | 14.6.4  | UART reception                                                  | 768 |

|--------|---------|-----------------------------------------------------------------|-----|

|        | 14.6.5  | Reception errors                                                | 769 |

|        | 14.6.6  | Parity types and operations                                     | 770 |

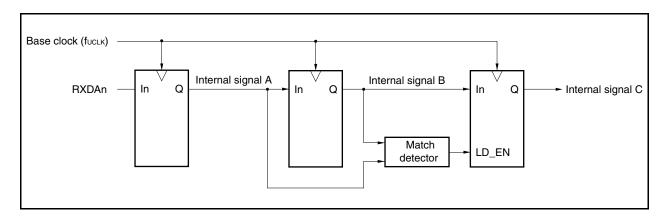

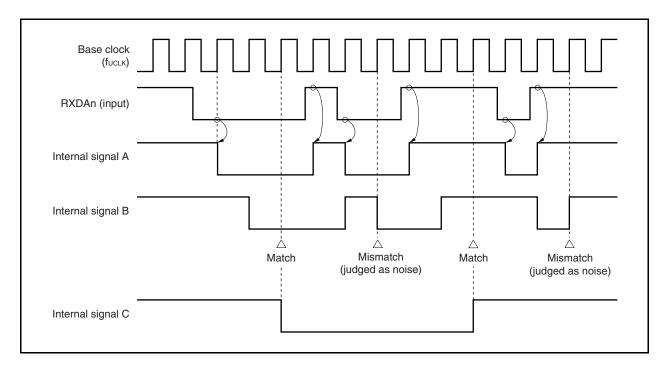

|        | 14.6.7  | Receive data noise filter                                       | 771 |

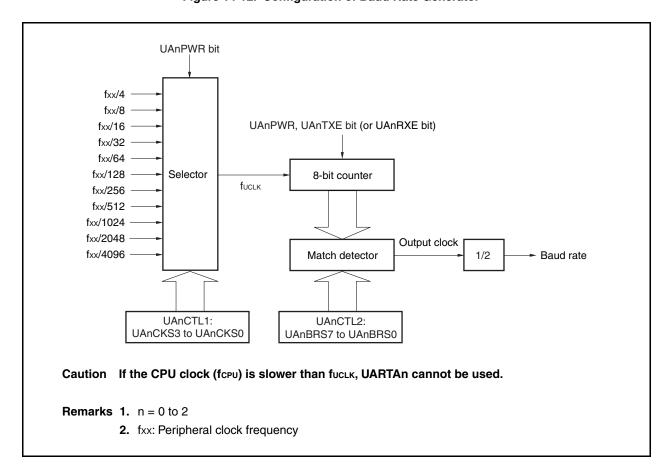

| 14.7   | Dedica  | ated Baud Rate Generator                                        | 772 |

| 14.8   | Cautio  | ns                                                              | 779 |

|        |         |                                                                 |     |

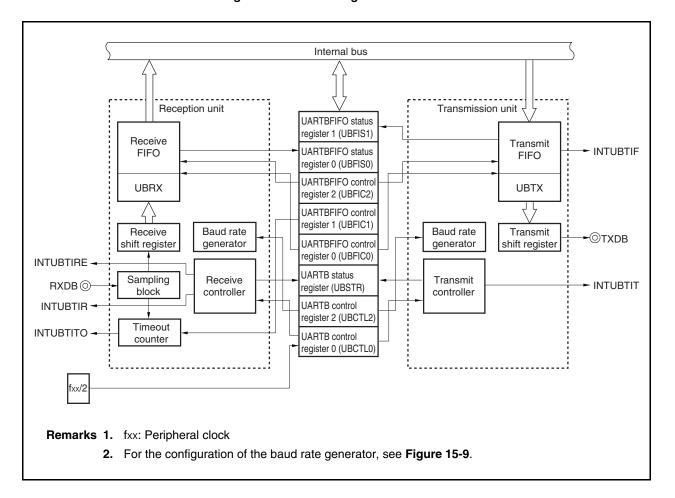

| CHAPTE | R 15 A  | SYNCHRONOUS SERIAL INTERFACE B (UARTB)                          | 780 |

| 15.1   | Featur  | es                                                              | 780 |

| 15.2   | Config  | uration                                                         | 781 |

|        | 15.2.1  | Pin functions of each channel                                   | 785 |

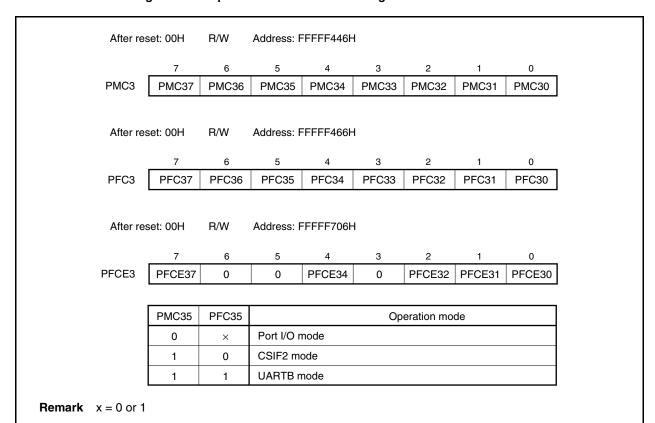

| 15.3   | Mode 9  | Switching Between UARTB and CSIF2                               | 786 |

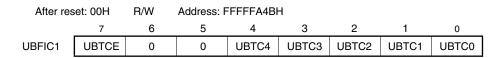

| 15.4   | Contro  | ol Registers                                                    | 787 |

| 15.5   | Interru | pt Request Signals                                              | 803 |

| 15.6   | Contro  | ol Modes                                                        | 806 |

| 15.7   | Operat  | tion                                                            | 810 |

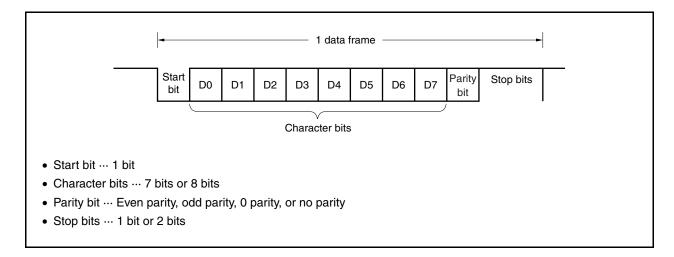

|        | 15.7.1  | Data format                                                     | 810 |

|        | 15.7.2  | Transmit operation                                              | 811 |

|        | 15.7.3  | Continuous transmission operation                               | 814 |

|        | 15.7.4  | Receive operation                                               | 815 |

|        | 15.7.5  | Reception error                                                 | 818 |

|        | 15.7.6  | Parity types and corresponding operation                        | 819 |

|        | 15.7.7  | Receive data noise filter                                       | 820 |

| 15.8   | Dedica  | ated Baud Rate Generator (BRG)                                  | 821 |

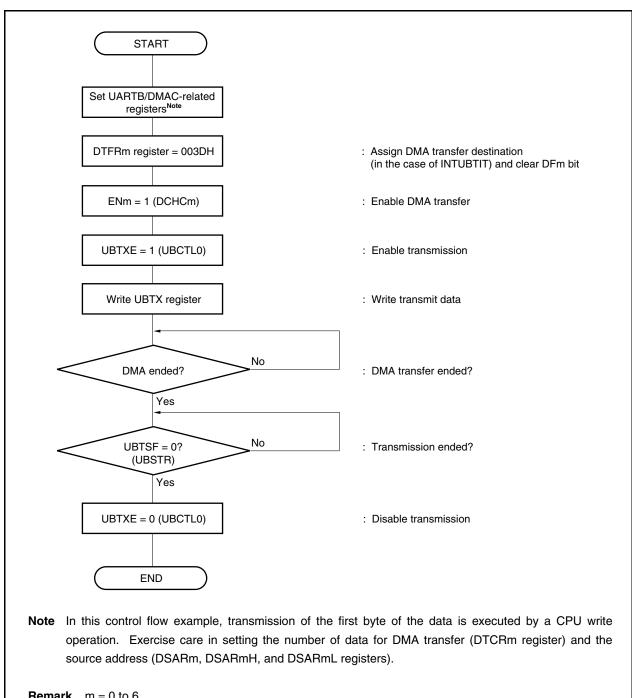

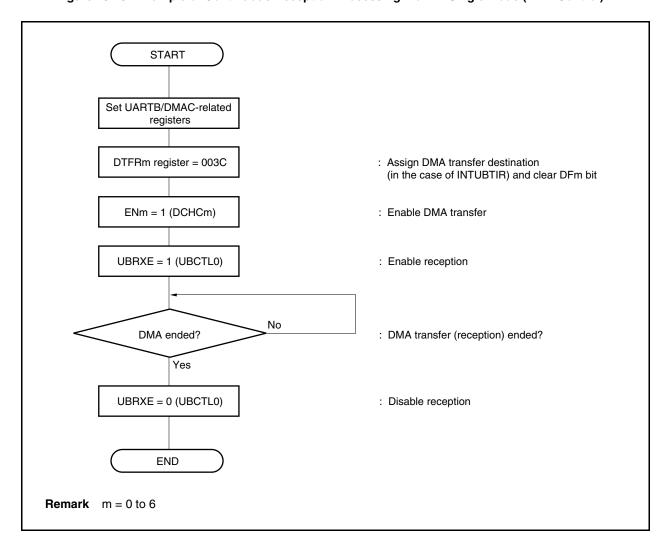

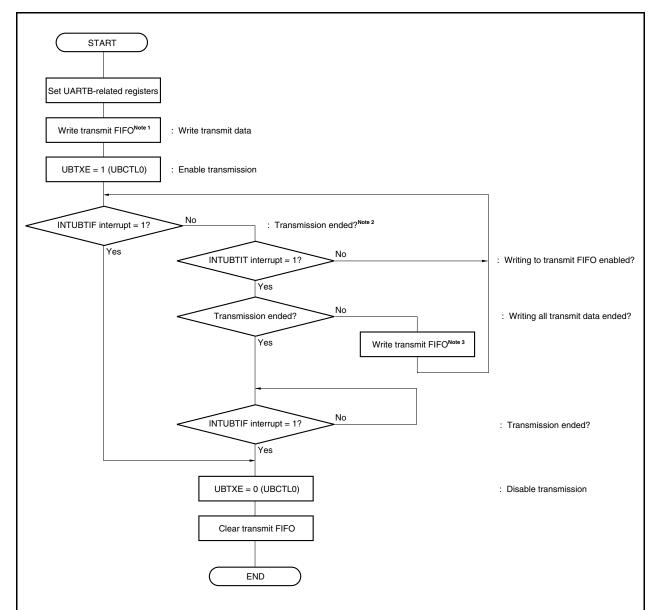

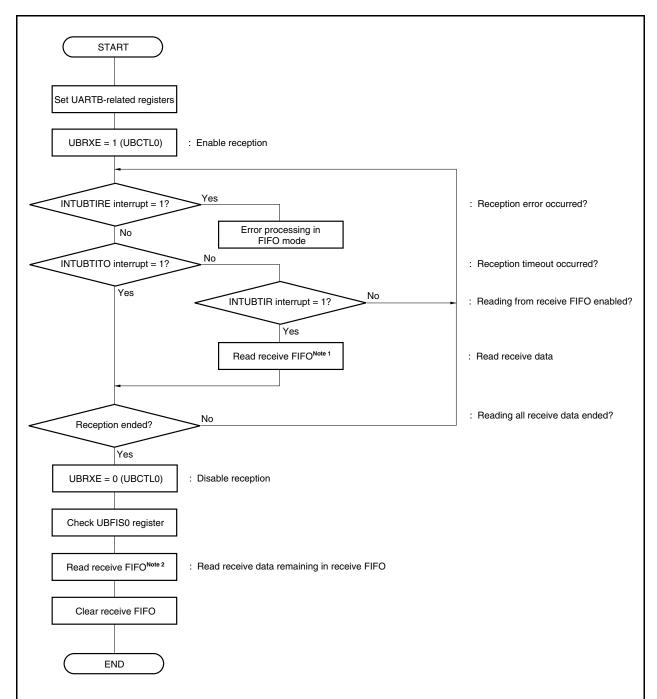

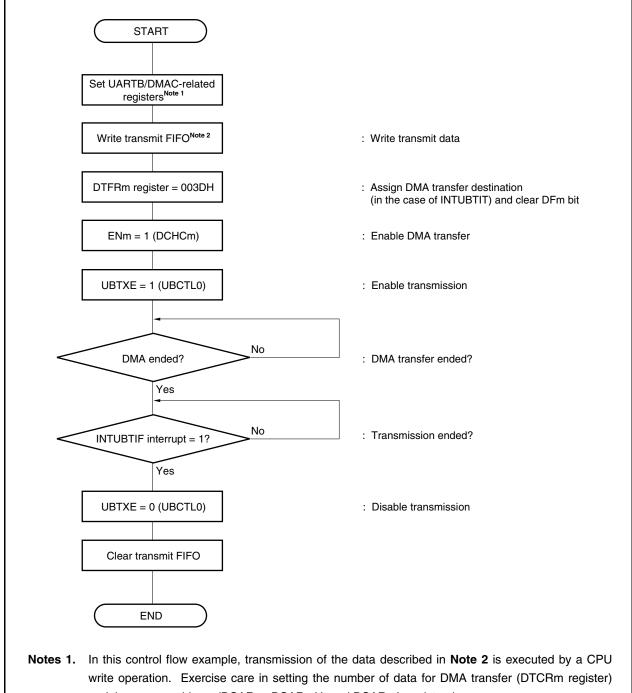

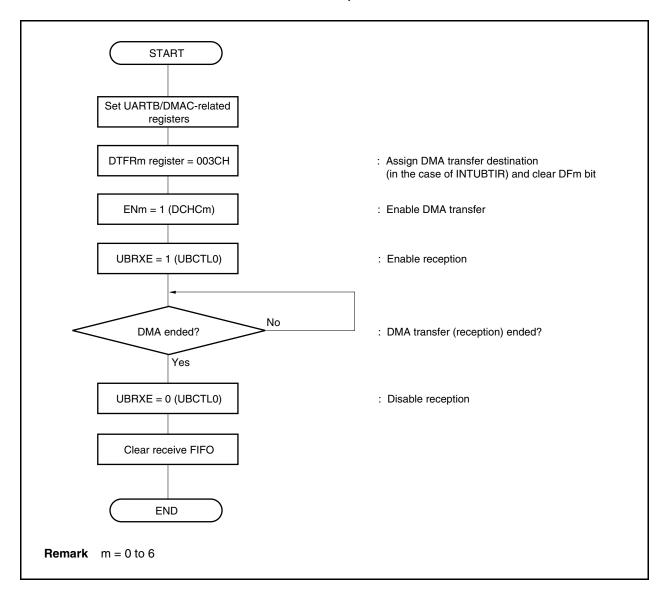

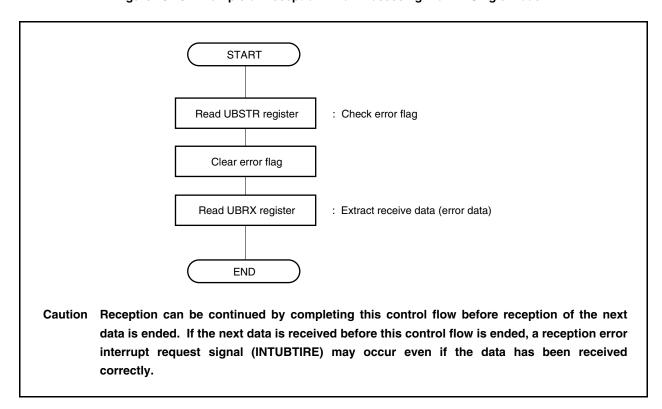

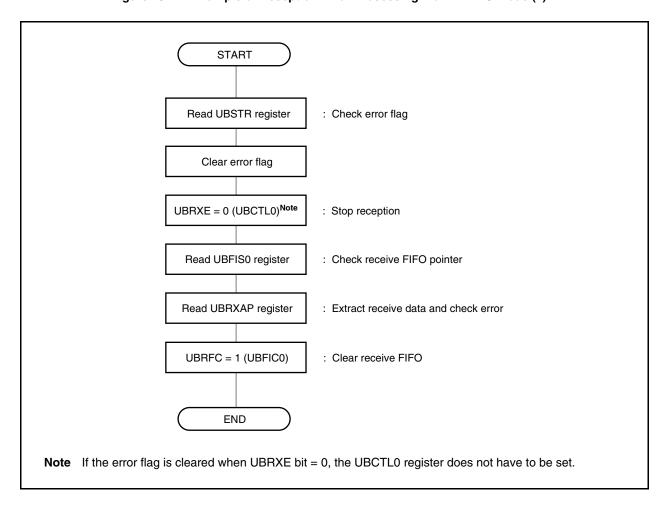

| 15.9   | Contro  | ol Flow                                                         | 827 |

| 15.10  | Cautio  | ns                                                              | 838 |

|        |         |                                                                 |     |

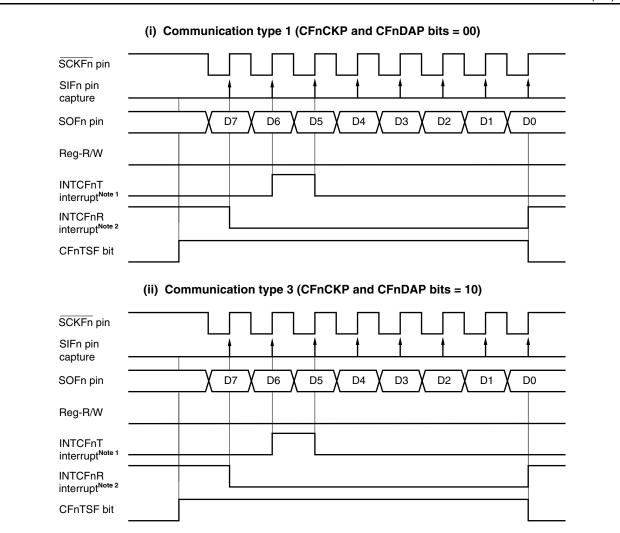

| CHAPTE | R 16 C  | CLOCKED SERIAL INTERFACE F (CSIF)                               | 840 |

| 16.1   | Featur  | es                                                              | 840 |

| 16.2   | Config  | uration                                                         | 841 |

|        | 16.2.1  | Pin functions of each channel                                   | 842 |

| 16.3   | Mode 9  | Switching Between CSIF and Other Serial Interface               | 843 |

|        | 16.3.1  | Mode switching between CSIF0 and UARTA0                         | 843 |

|        | 16.3.2  | Mode switching between CSIF1 and UARTA2                         | 844 |

|        | 16.3.3  | Mode switching between CSIF2 and UARTB                          | 845 |

| 16.4   | Contro  | ol Registers                                                    | 846 |

| 16.5   | Operat  | tion                                                            | 855 |

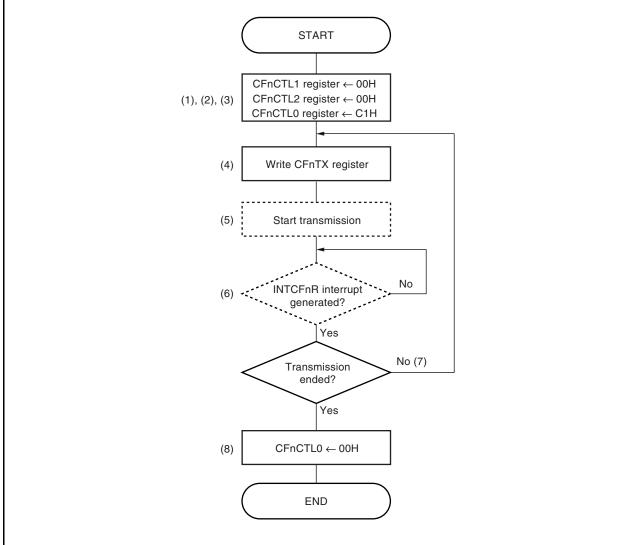

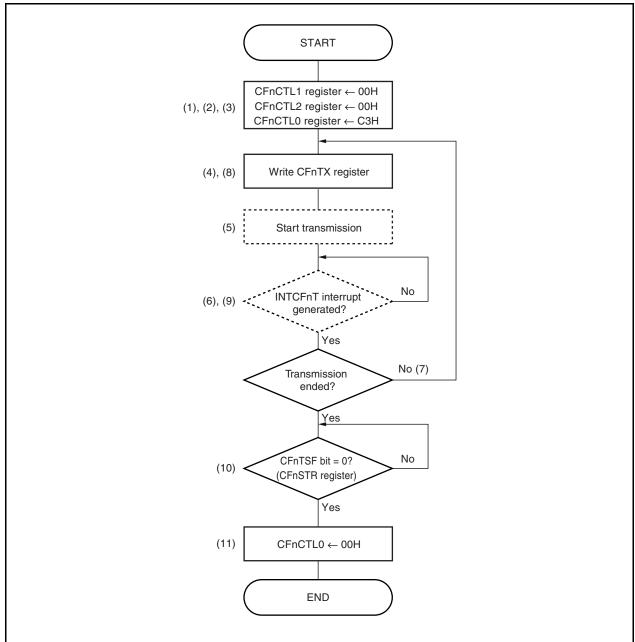

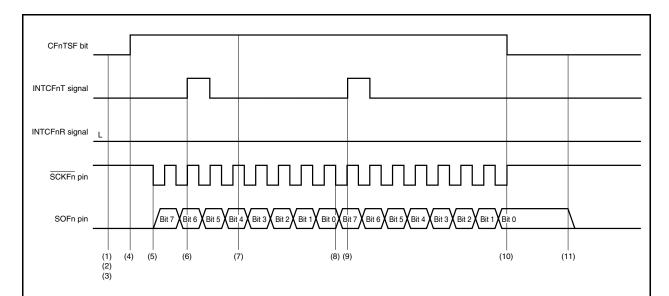

|        | 16.5.1  | Single transfer mode (master mode, transmission mode)           | 855 |

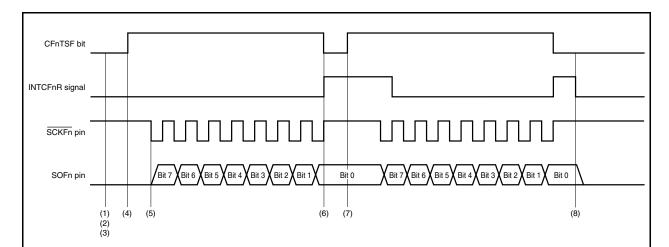

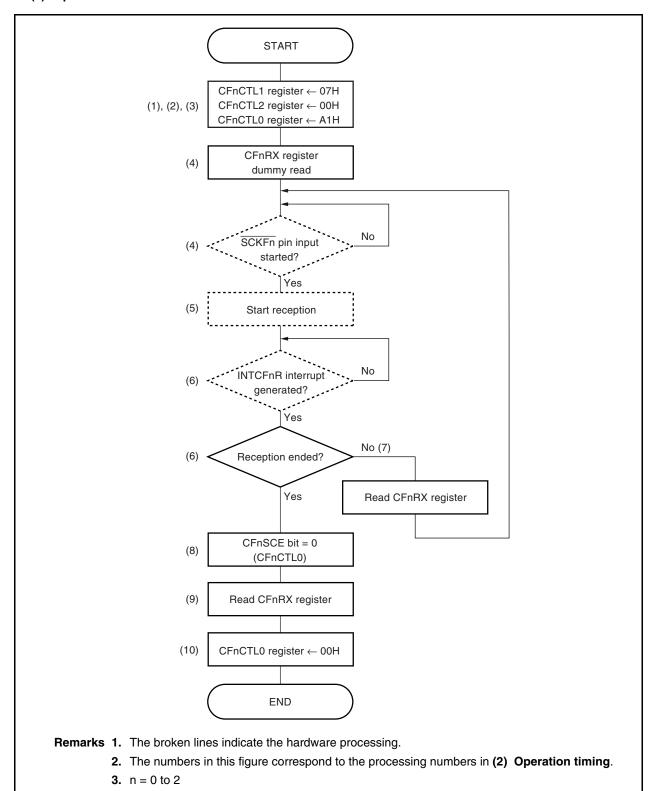

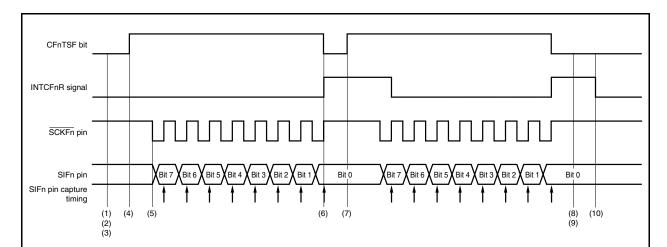

|        | 16.5.2  | Single transfer mode (master mode, reception mode)              | 857 |

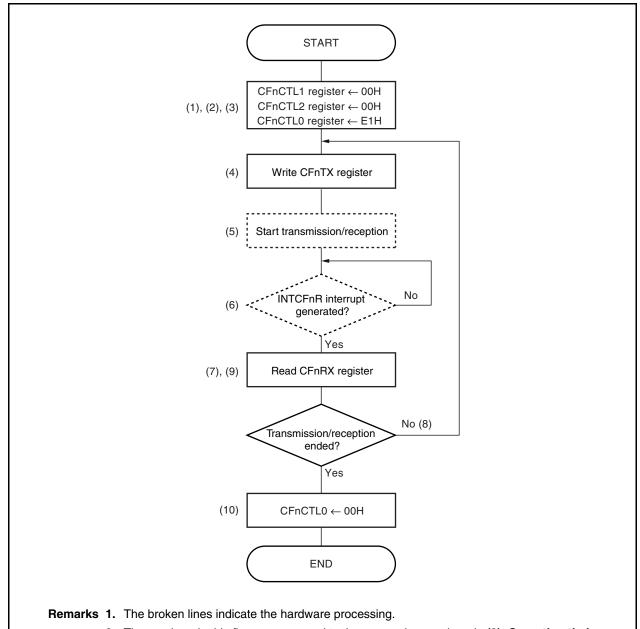

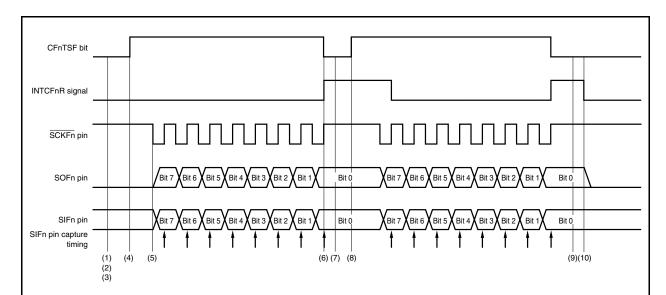

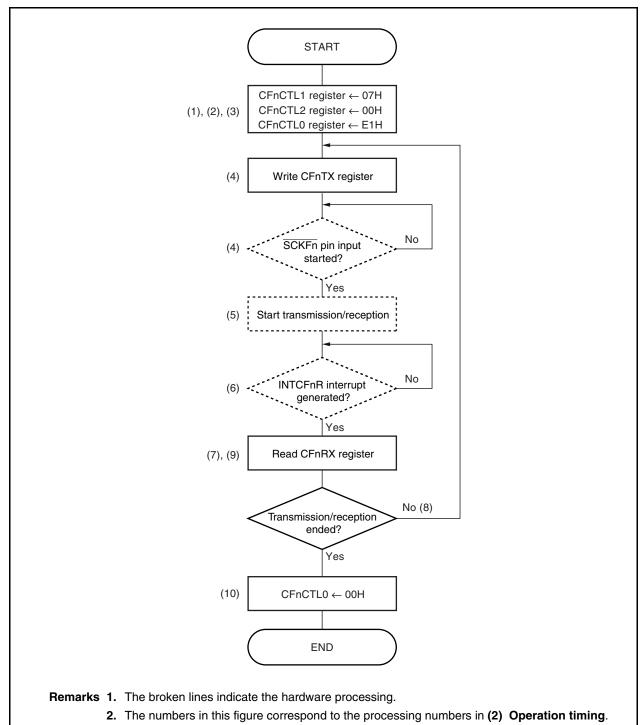

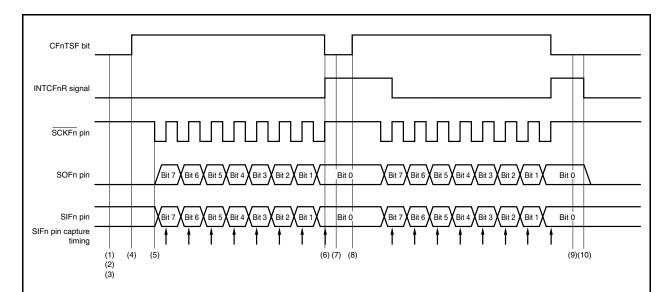

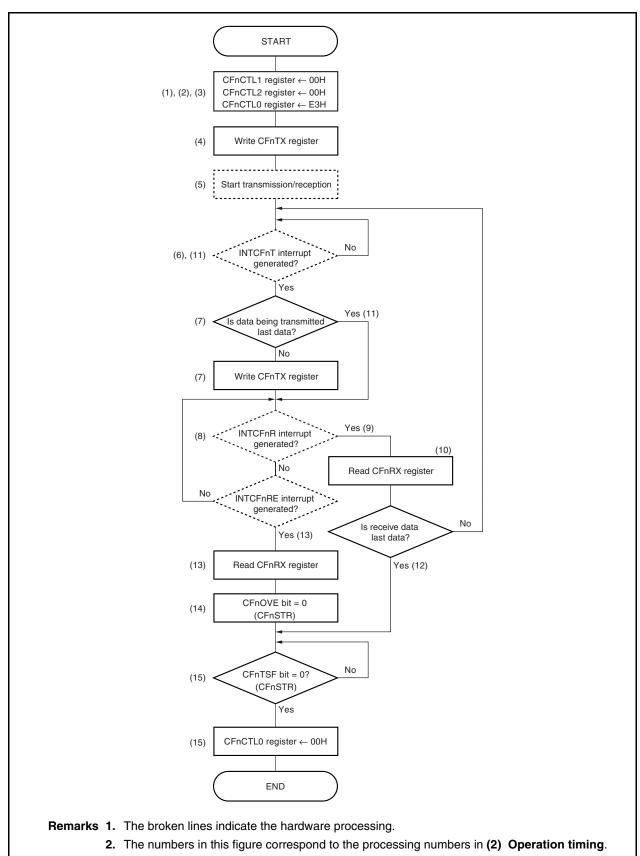

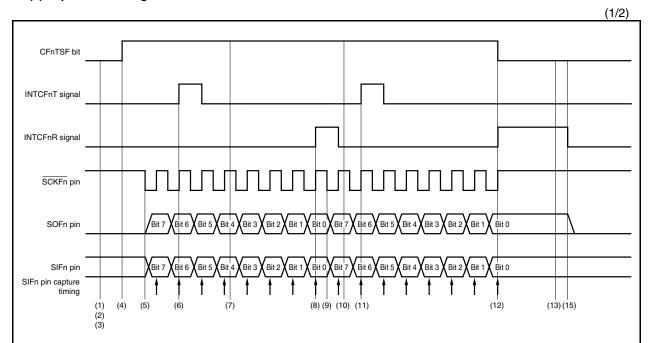

|        | 16.5.3  | Single transfer mode (master mode, transmission/reception mode) | 859 |

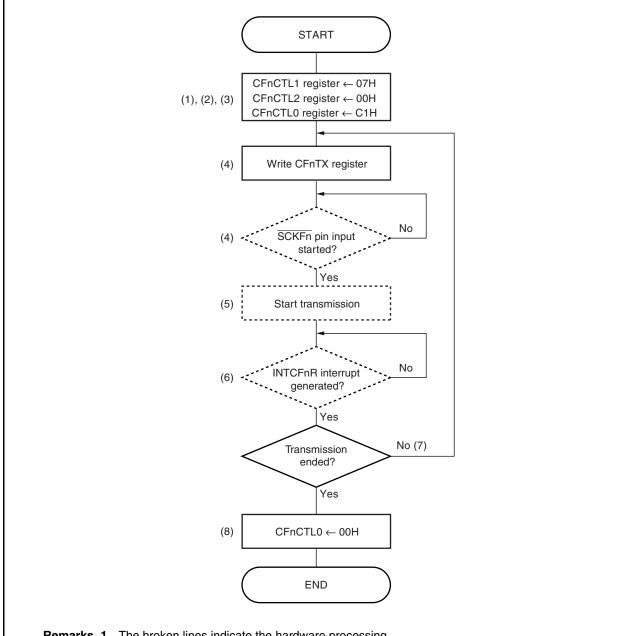

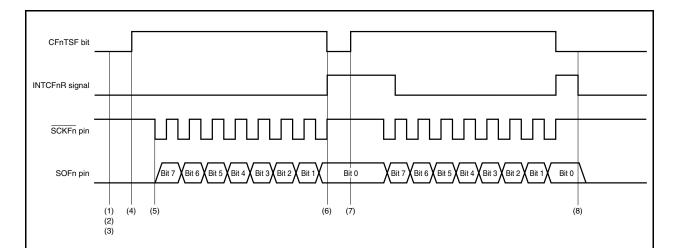

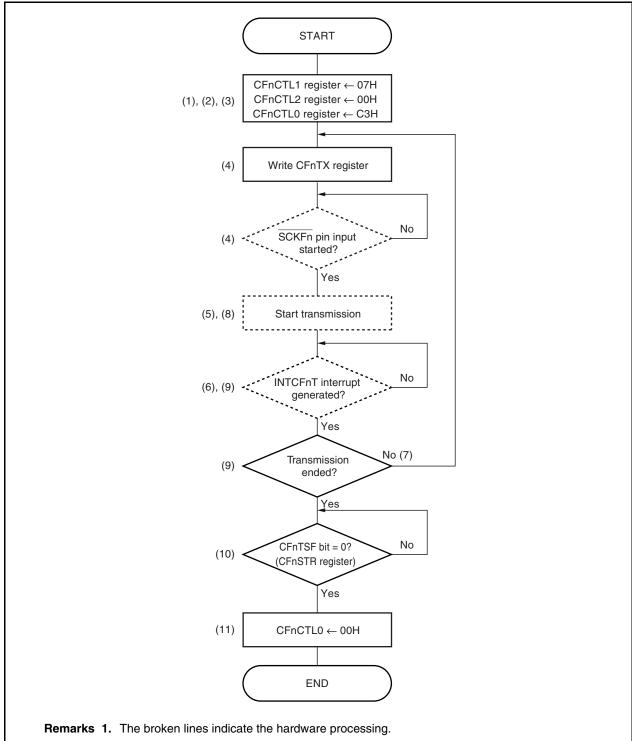

|        | 16.5.4  | Single transfer mode (slave mode, transmission mode)            | 861 |

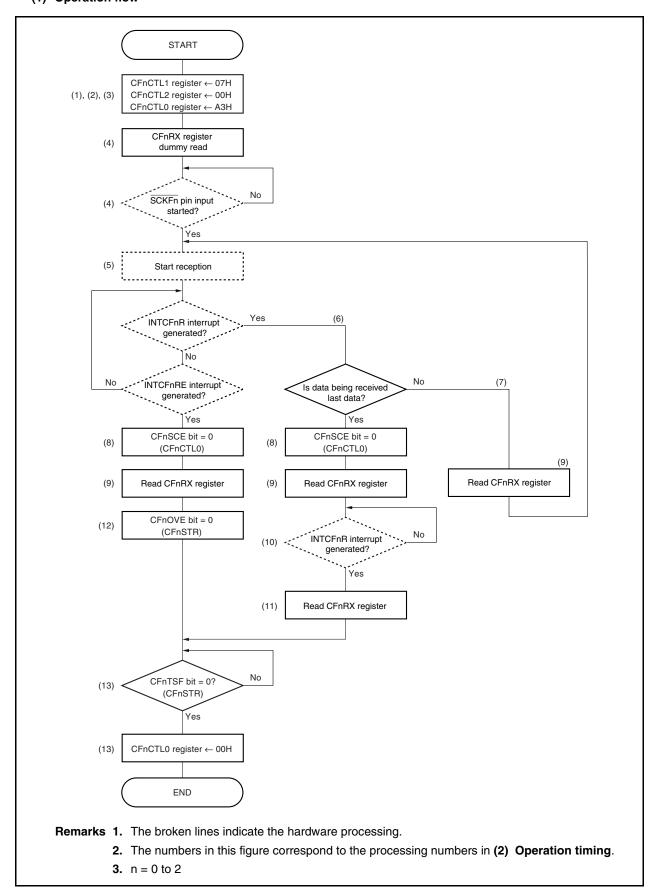

|        | 16.5.5  | Single transfer mode (slave mode, reception mode)               | 863 |

|        | 16.5.6  | Single transfer mode (slave mode, transmission/reception mode)  |     |

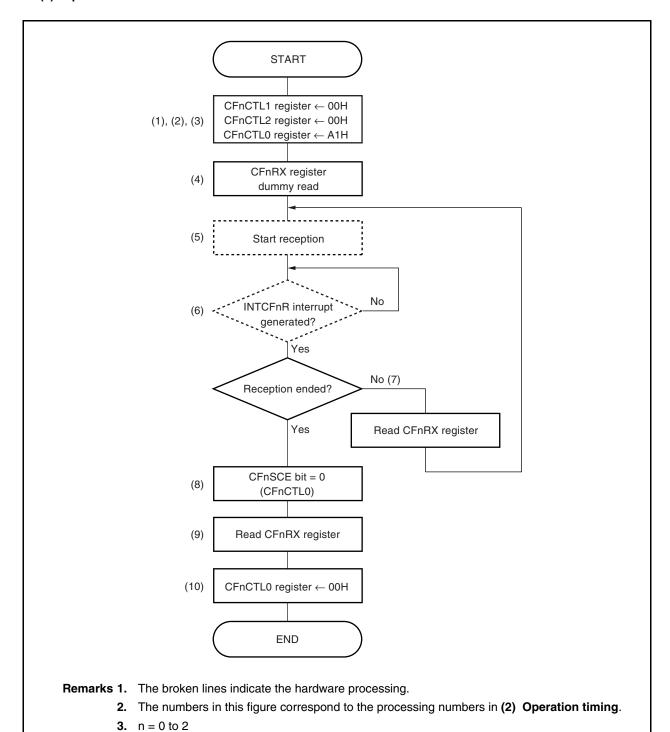

|        | 16.5.7  | Continuous transfer mode (master mode, transmission mode)       |     |

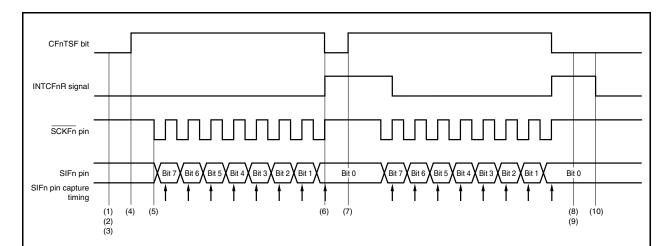

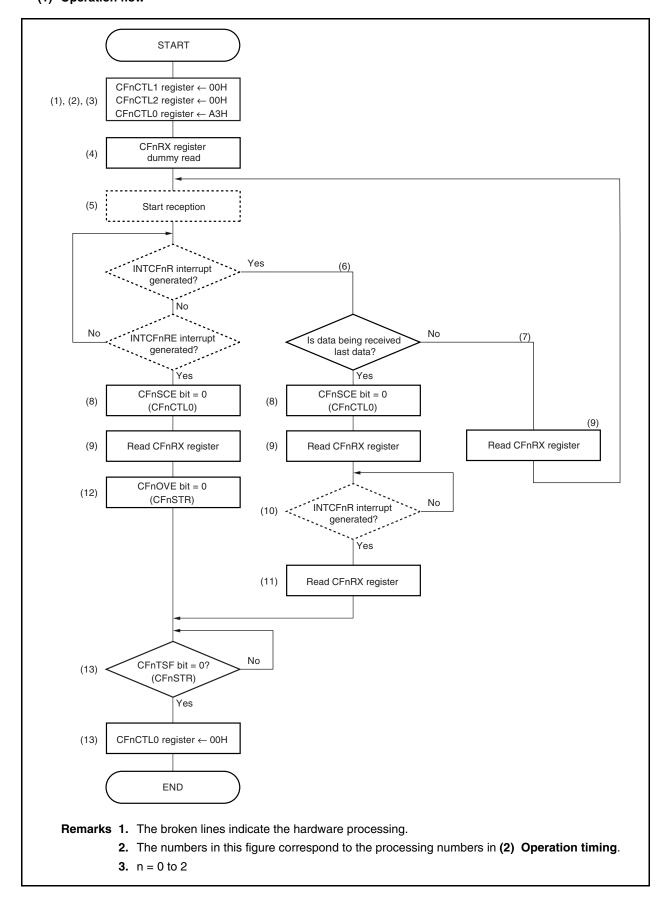

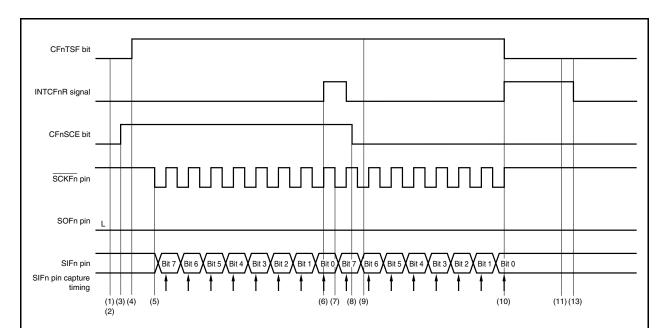

|        | 16.5.8  | Continuous transfer mode (master mode, reception mode)          | 869 |

|         | 16.5.9 Continuous transfer mode (master mode, transmission/reception mode)              | 872 |

|---------|-----------------------------------------------------------------------------------------|-----|

|         | 16.5.10 Continuous transfer mode (slave mode, transmission mode)                        | 876 |

|         | 16.5.11 Continuous transfer mode (slave mode, reception mode)                           | 878 |

|         | 16.5.12 Continuous transfer mode (slave mode, transmission/reception mode)              | 881 |

|         | 16.5.13 Reception error                                                                 | 885 |

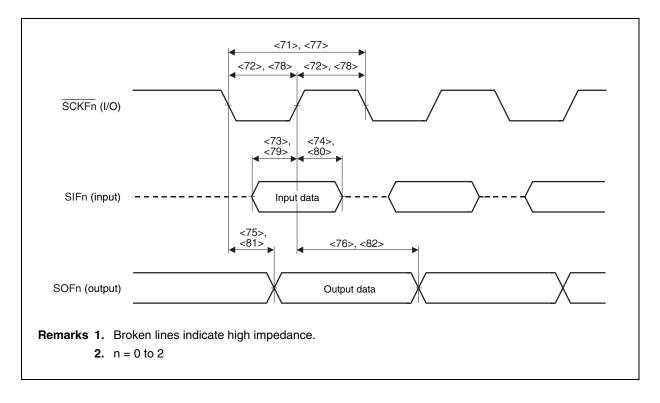

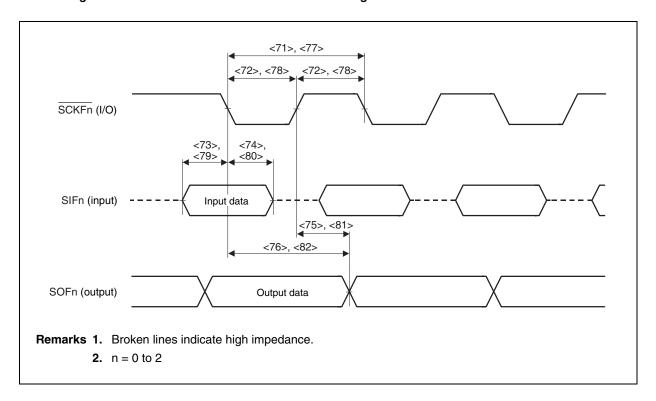

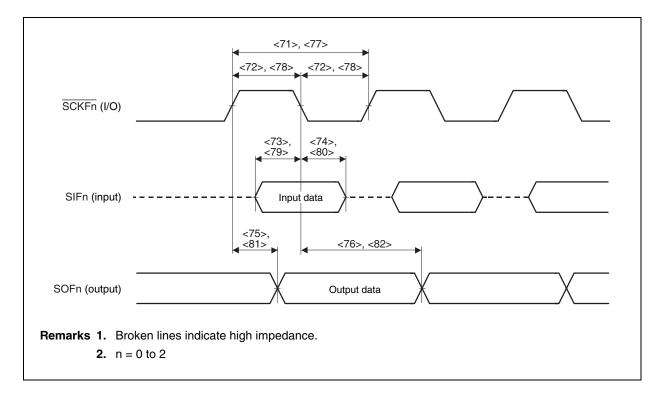

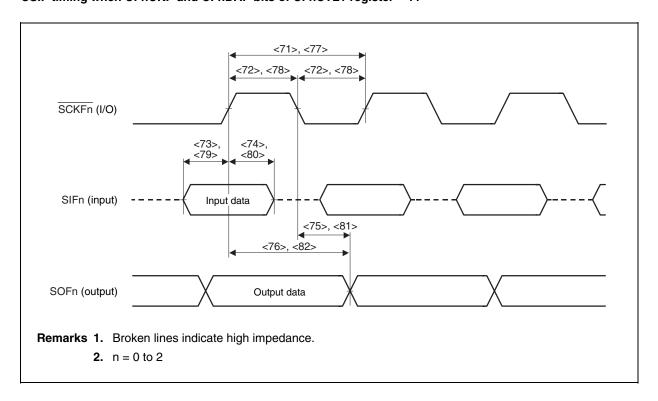

|         | 16.5.14 Clock timing                                                                    | 886 |

| 16.6    | Output Pins                                                                             | 888 |

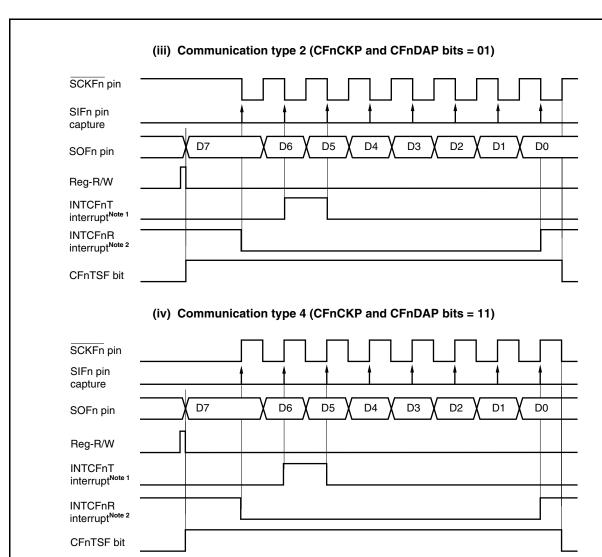

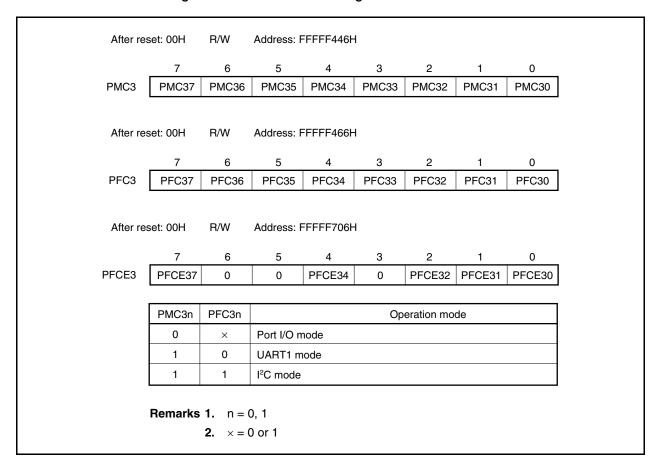

| CHAPTER | R 17 I'C BUS                                                                            | 889 |

| 17.1    | Features                                                                                | 889 |

| 17.2    | Configuration                                                                           | 890 |

|         | 17.2.1 Pin functions of each channel                                                    | 894 |

| 17.3    | Mode Switching Between I <sup>2</sup> C and UARTA1                                      | 895 |

| 17.4    | Registers                                                                               | 896 |

| 17.5    | Functions                                                                               | 910 |

|         | 17.5.1 Pin configuration                                                                | 910 |

| 17.6    | I <sup>2</sup> C Bus Definitions and Control Methods                                    | 911 |

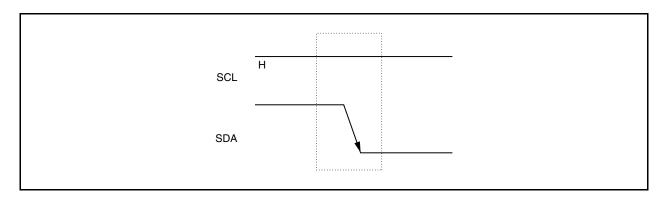

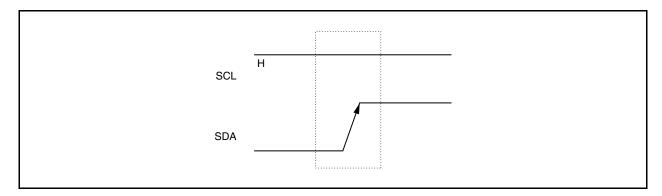

|         | 17.6.1 Start condition                                                                  | 911 |

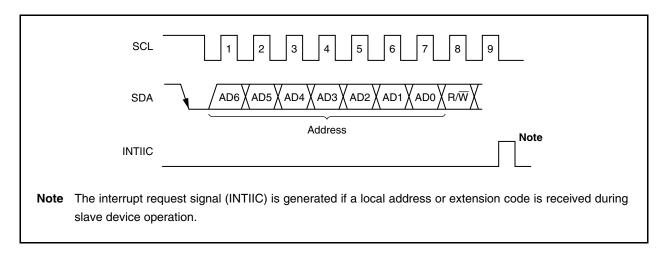

|         | 17.6.2 Addresses                                                                        | 912 |

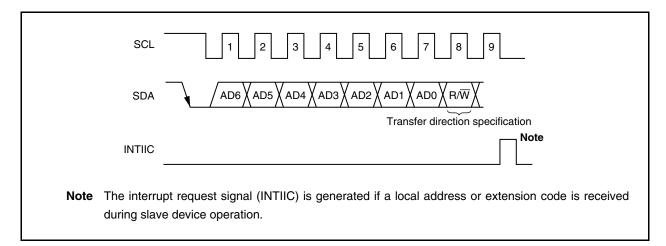

|         | 17.6.3 Transfer direction specification                                                 | 913 |

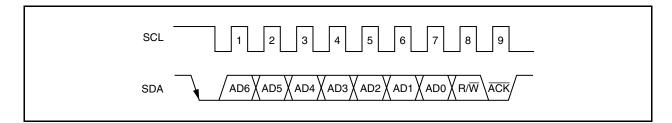

|         | 17.6.4 ACK                                                                              | 914 |

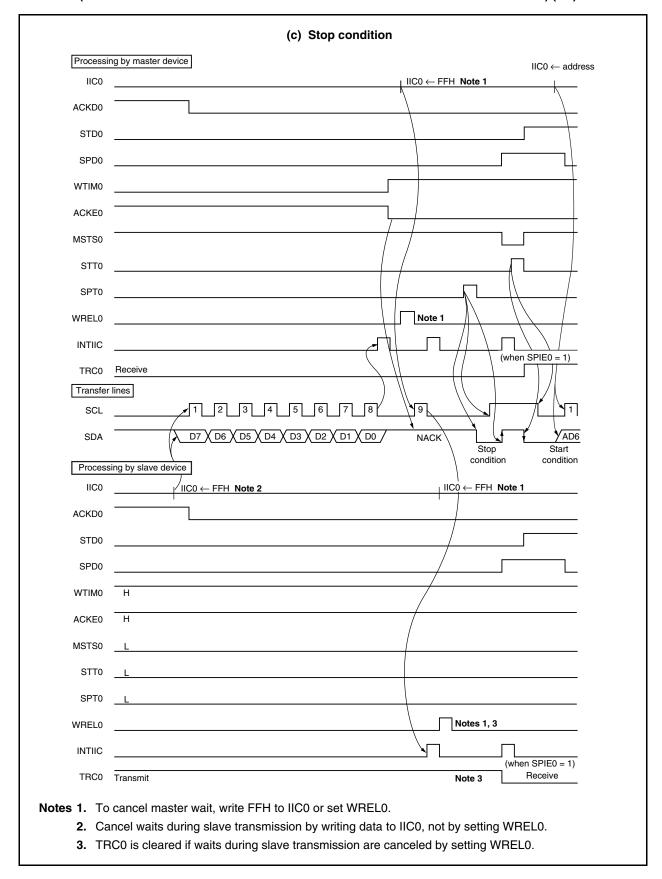

|         | 17.6.5 Stop condition                                                                   | 915 |

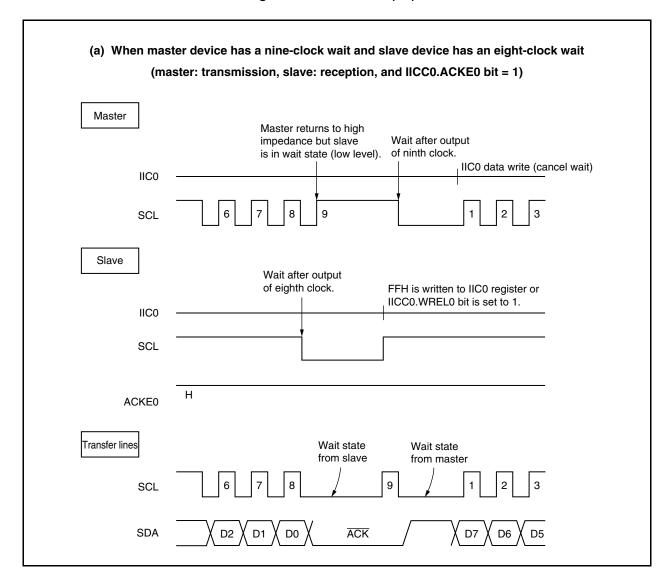

|         | 17.6.6 Wait state                                                                       | 916 |

|         | 17.6.7 Wait state cancellation method                                                   | 918 |

| 17.7    | I <sup>2</sup> C Interrupt Request Signals (INTIIC)                                     | 919 |

|         | 17.7.1 Master device operation                                                          | 920 |

|         | 17.7.2 Slave device operation (when receiving slave address data (address match))       | 923 |

|         | 17.7.3 Slave device operation (when receiving extension code)                           | 927 |

|         | 17.7.4 Operation without communication                                                  | 931 |

|         | 17.7.5 Arbitration loss operation (operation as slave after arbitration loss)           | 932 |

|         | 17.7.6 Operation when arbitration loss occurs (no communication after arbitration loss) | 934 |

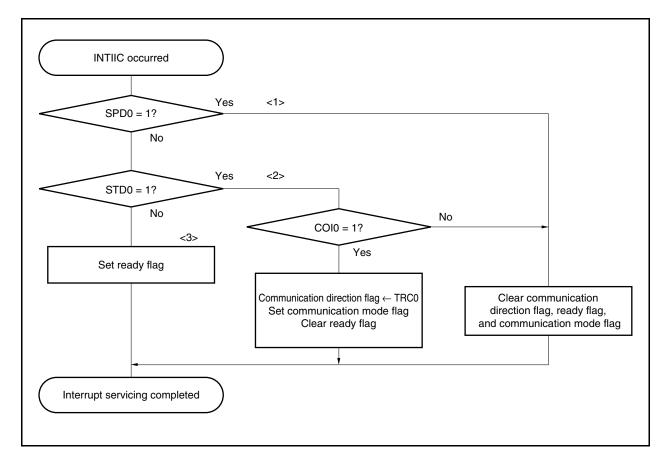

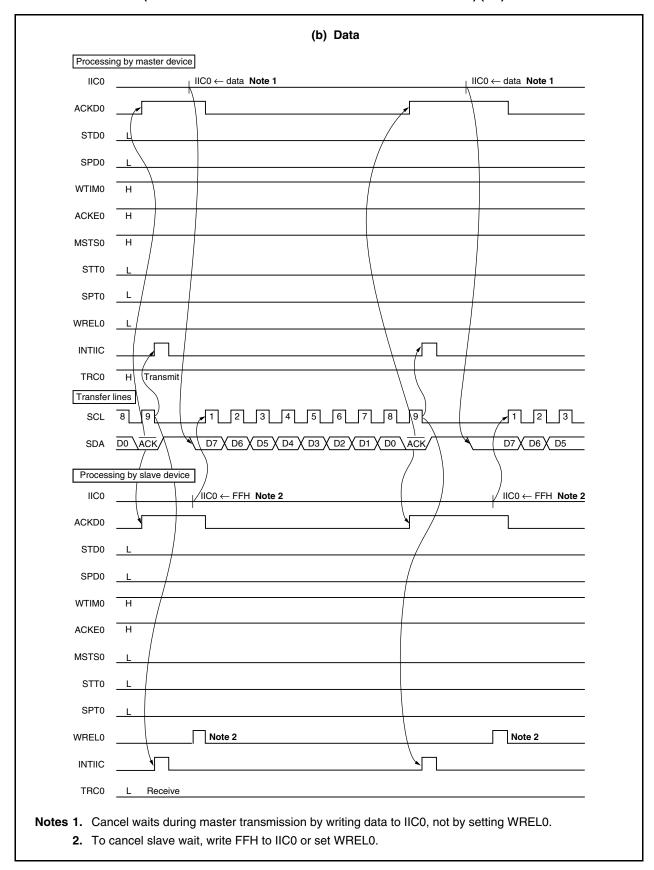

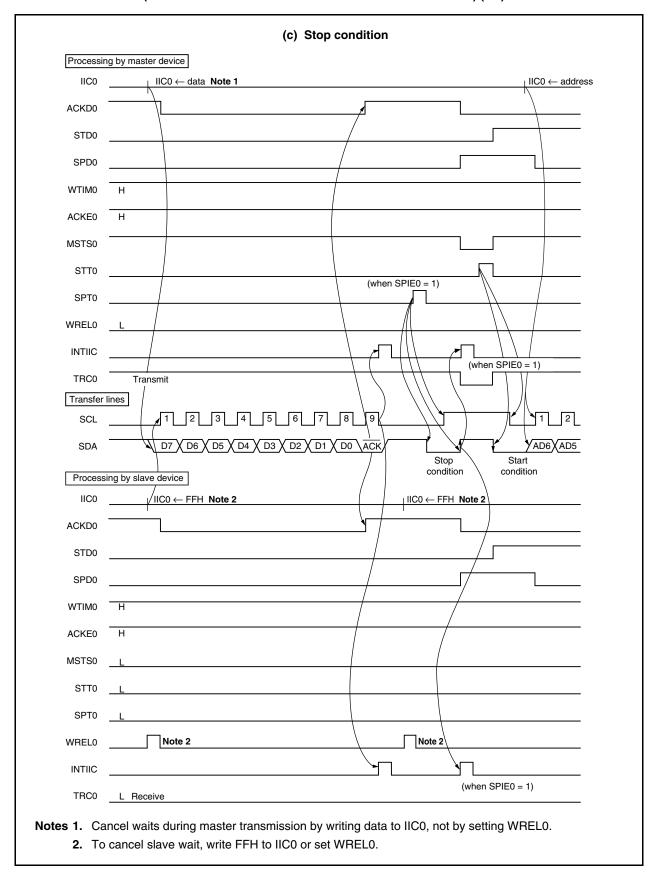

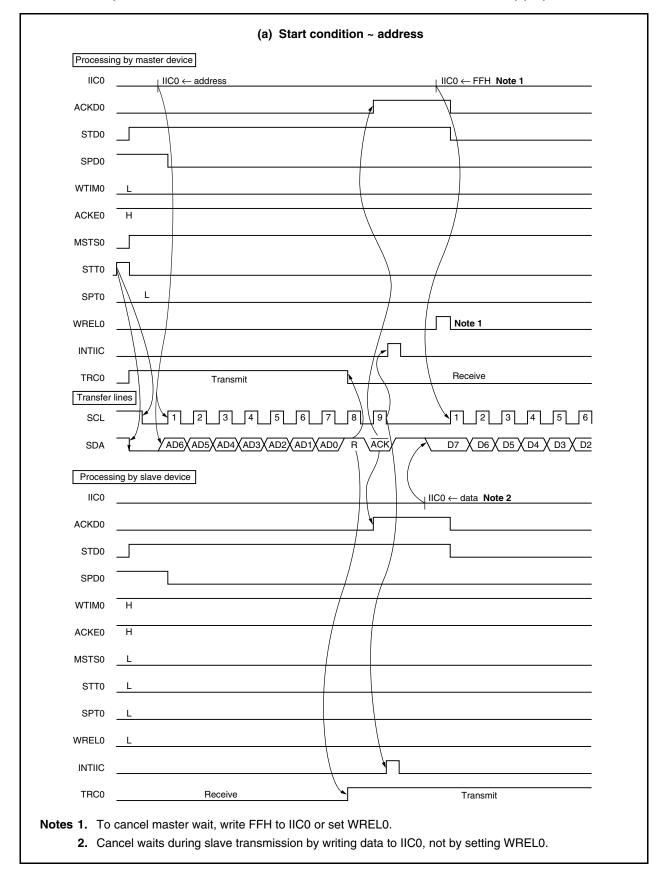

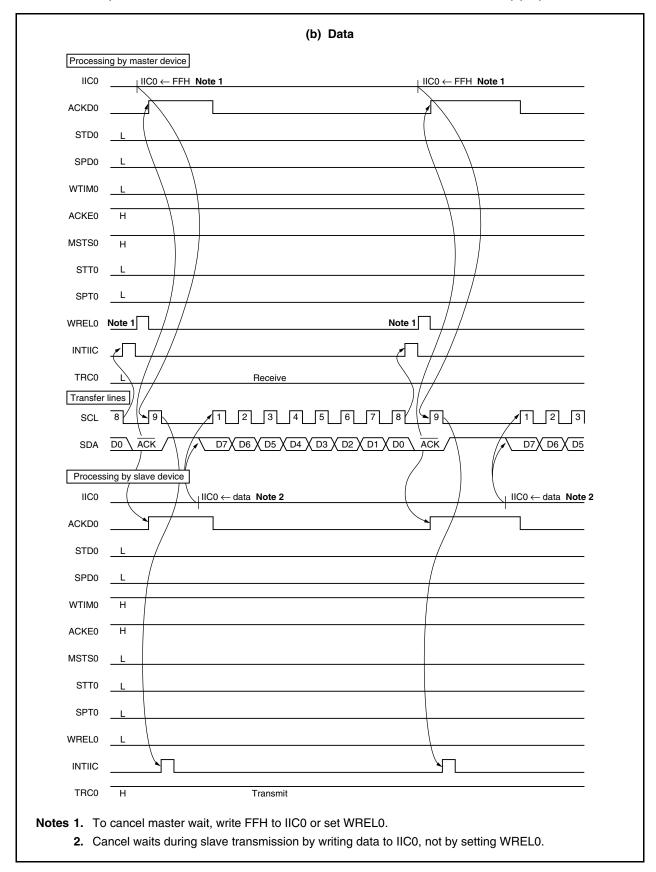

| 17.8    | Interrupt Request Signal (INTIIC) Generation Timing and Wait Control                    | 941 |

| 17.9    | Address Match Detection Method                                                          | 942 |

| 17.10   | Error Detection                                                                         | 942 |

| 17.11   | Extension Code                                                                          | 943 |

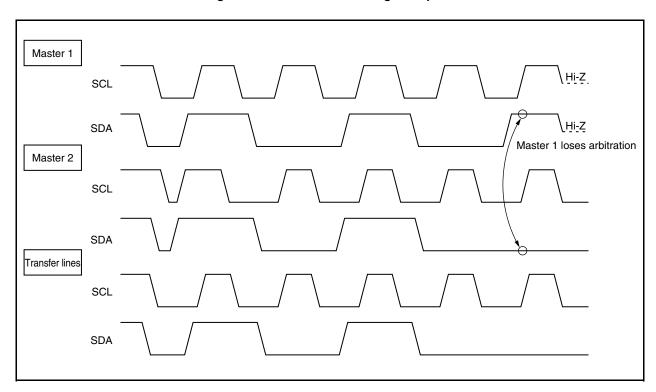

| 17.12   | Arbitration                                                                             | 944 |

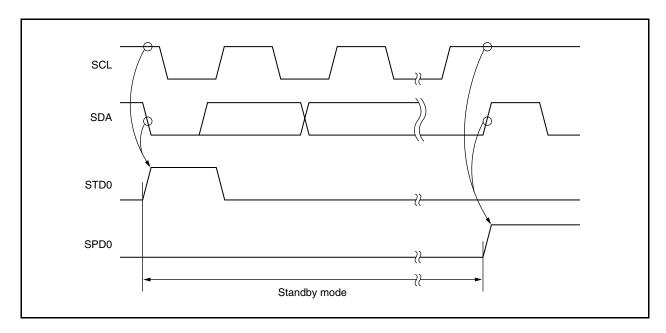

| 17.13   | Wakeup Function                                                                         | 945 |

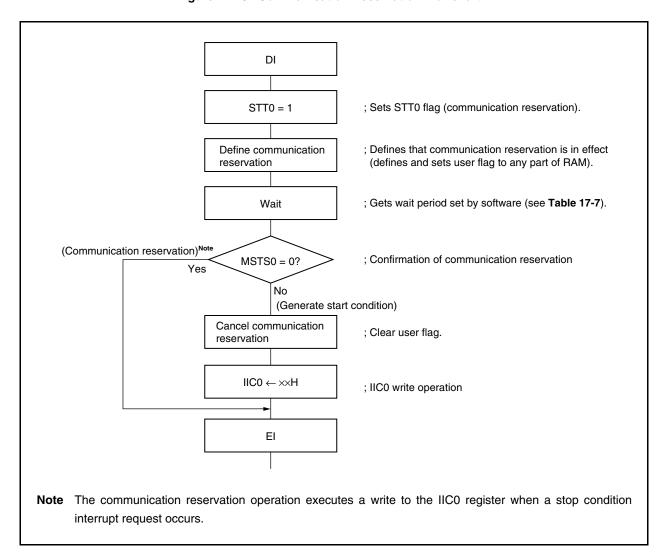

| 17.14   | Communication Reservation                                                               | 946 |

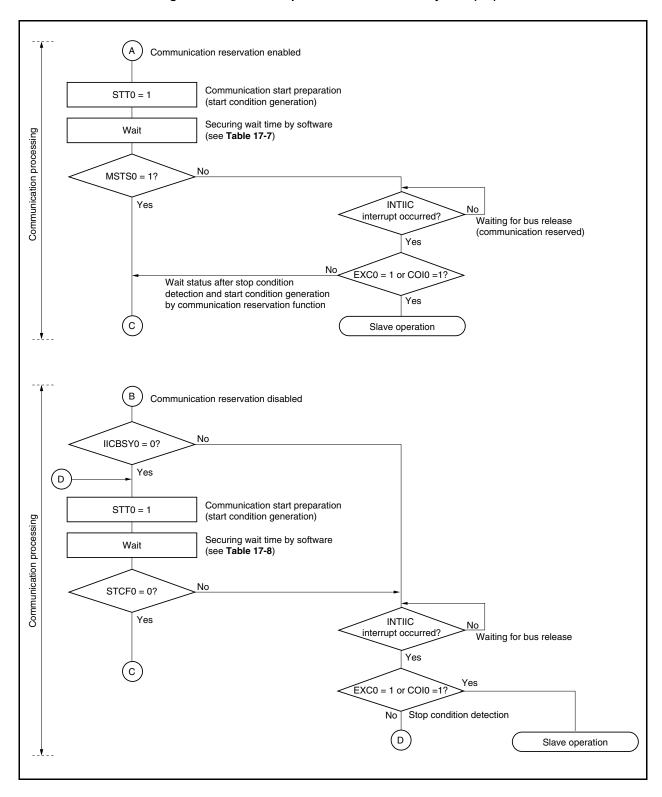

|         | 17.14.1 When communication reservation function is enabled (IICF0.IICRSV0 bit = 0)      | 946 |

|         | 17.14.2 When communication reservation function is disabled (IICF0.IICRSV0 bit = 1)     | 949 |

| 17.15   | Cautions                                                                                | 950 |

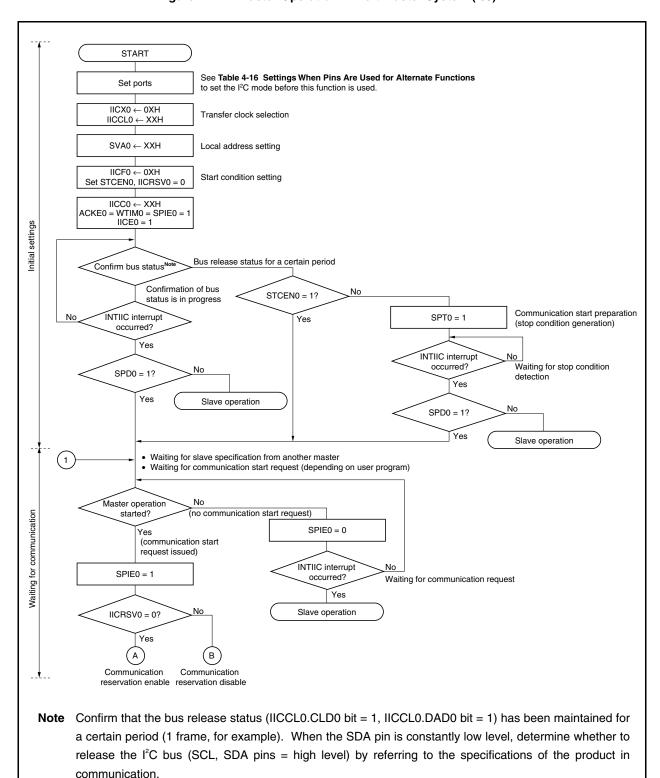

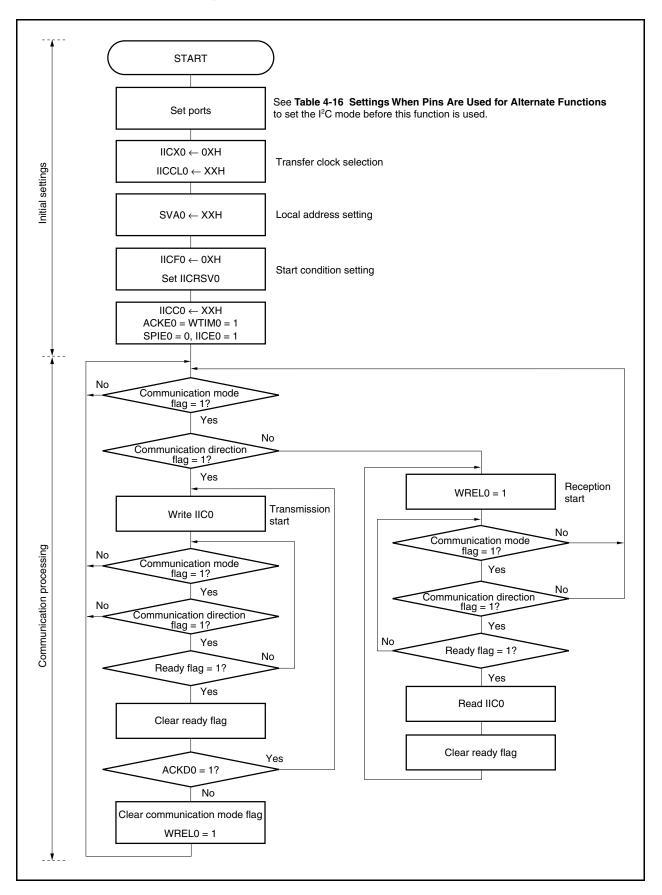

| 17.16   | Communication Operations                                                                | 951 |

|         | 17.16.1 Master operation in single master system                                        | 952 |

|         | 17.16.2 Master operation in multimaster system                                          | 953 |

|         | 17.16.3 Slave operation                                                                 | 956 |

|         |                                                                                         |     |

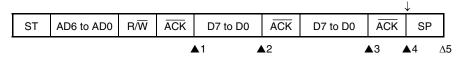

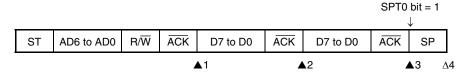

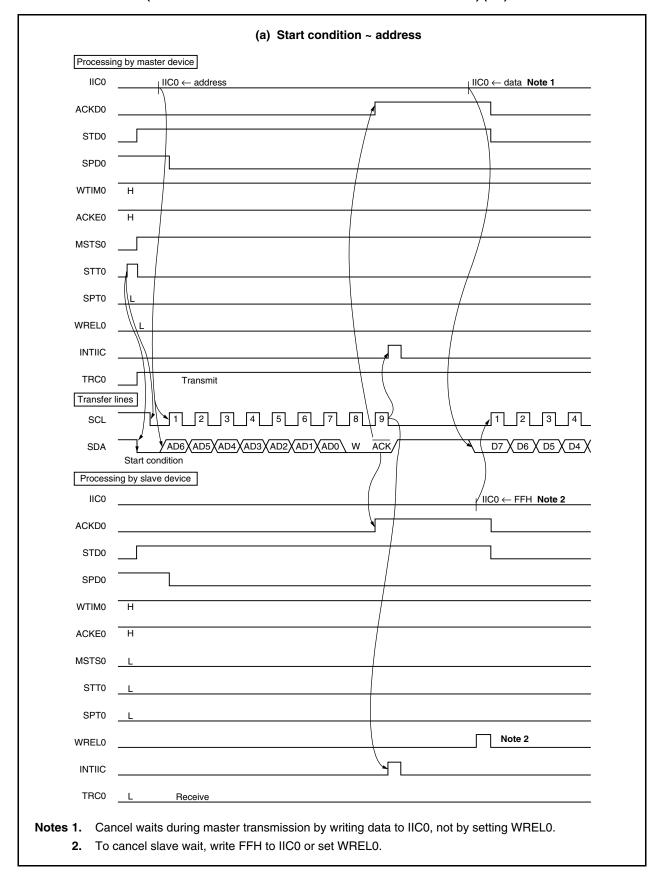

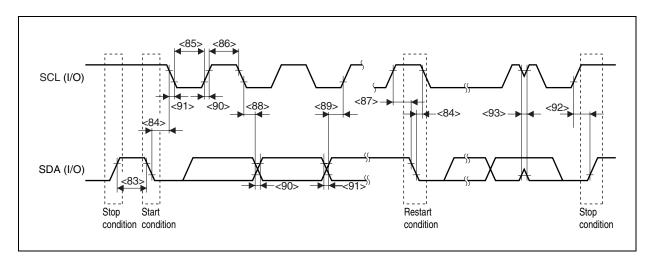

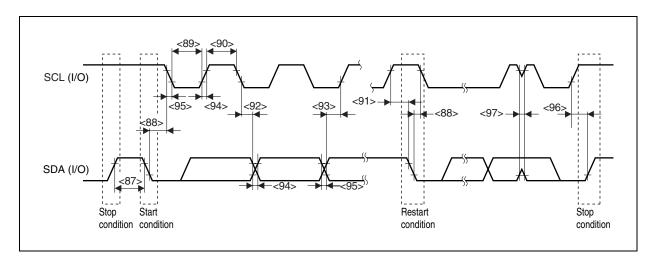

| 17.17  | ' Timing | of Data Communication                                                           | 960  |

|--------|----------|---------------------------------------------------------------------------------|------|

| CHAPTE | R 18 U   | SB FUNCTION CONTROLLER (USBF)                                                   | 967  |

| 18.1   | Overvi   | ew                                                                              | 967  |

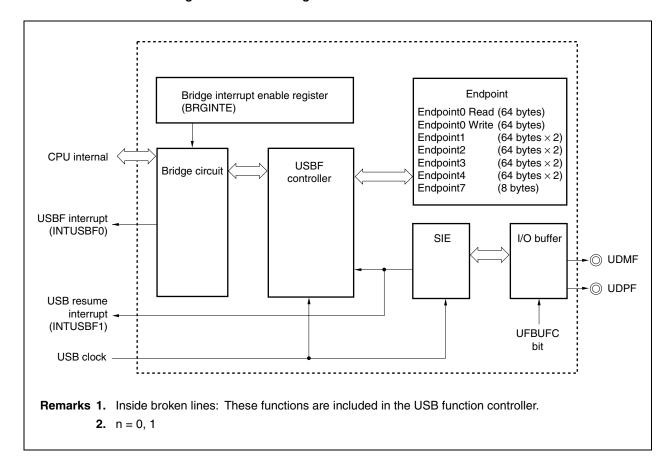

| 18.2   | Config   | uration                                                                         | 968  |

|        | 18.2.1   | Block diagram                                                                   | 968  |

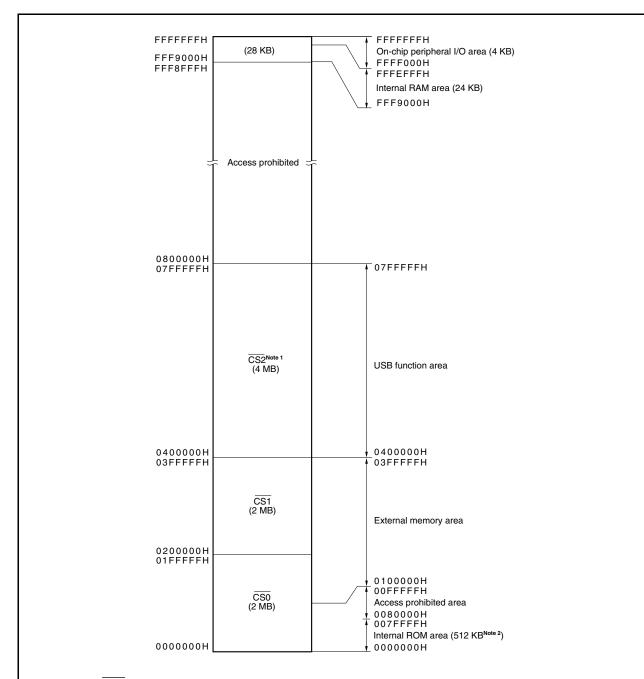

|        | 18.2.2   | USB memory map                                                                  | 969  |

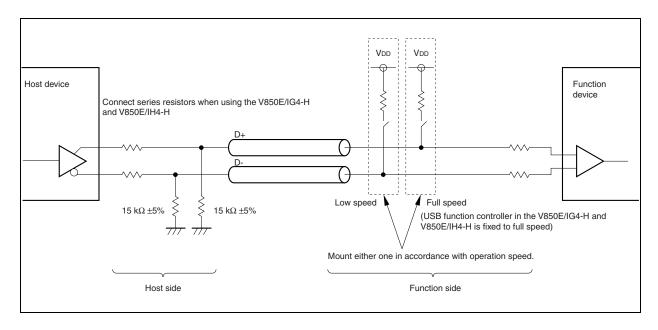

| 18.3   | Externa  | al Circuit Configuration                                                        | 970  |

|        | 18.3.1   | Outline                                                                         | 970  |

|        | 18.3.2   | Connection configuration                                                        | 971  |

| 18.4   | Cautio   | ns                                                                              | 973  |

| 18.5   | Reques   | sts                                                                             | 973  |

|        | 18.5.1   | Automatic requests                                                              | 973  |

|        | 18.5.2   | Other requests                                                                  |      |

| 18.6   | Registe  | er Configuration                                                                | 982  |

|        | 18.6.1   | USB control registers                                                           | 982  |

|        | 18.6.2   | USB function controller register list                                           | 983  |

|        | 18.6.3   | EPC control registers                                                           | 998  |

|        | 18.6.4   | Data hold registers                                                             | 1045 |

|        | 18.6.5   | EPC request data registers                                                      | 1068 |

|        | 18.6.6   | Bridge register                                                                 | 1083 |

| 18.7   | STALL    | Handshake or No Handshake                                                       | 1089 |

| 18.8   | •        | er Values in Specific Status                                                    |      |

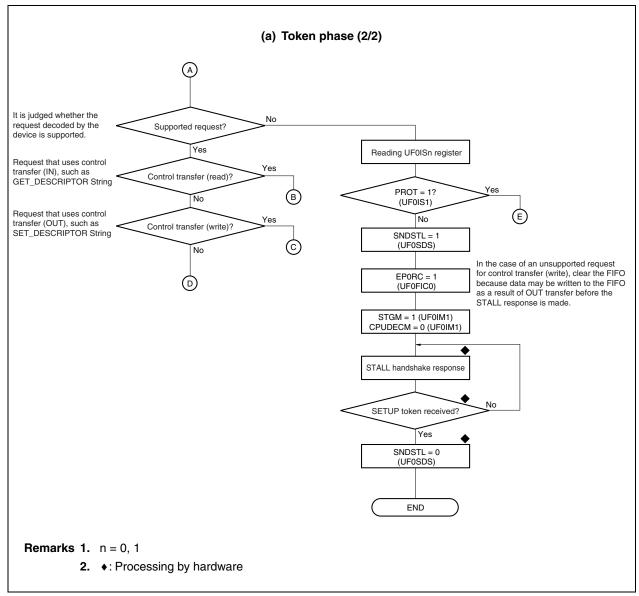

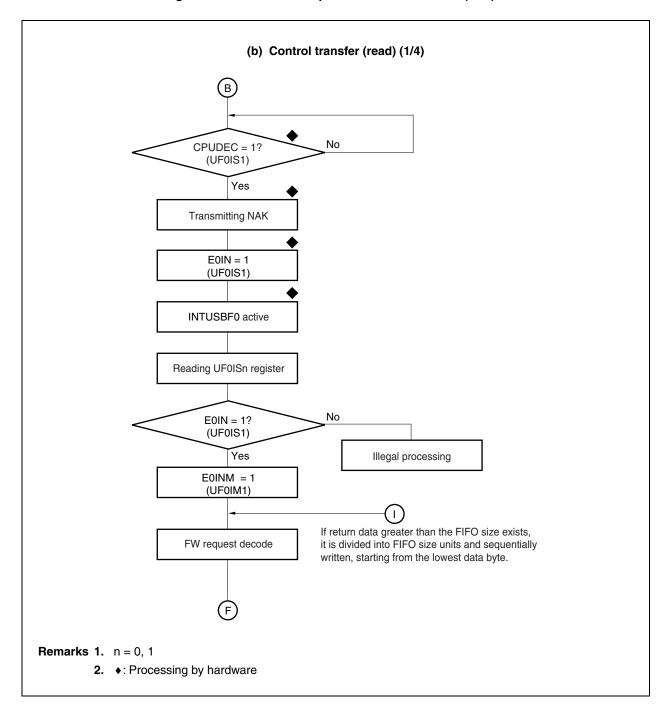

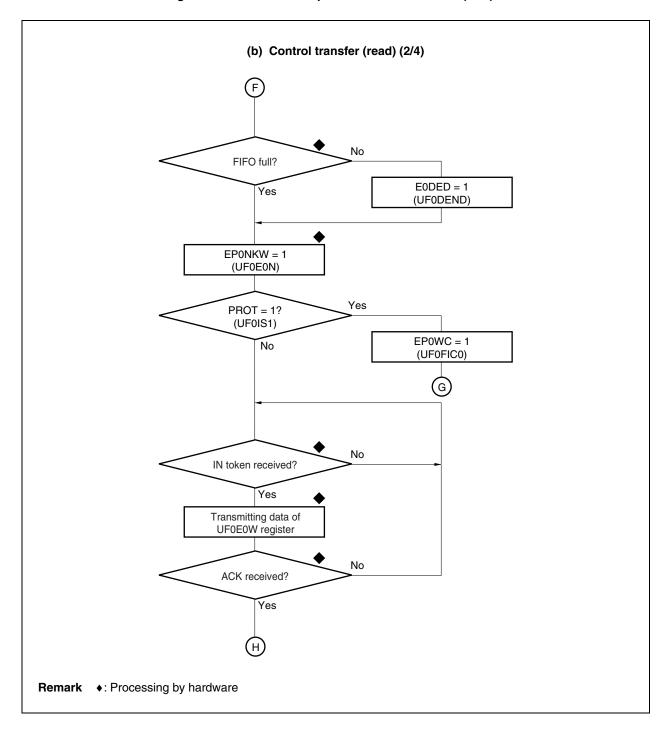

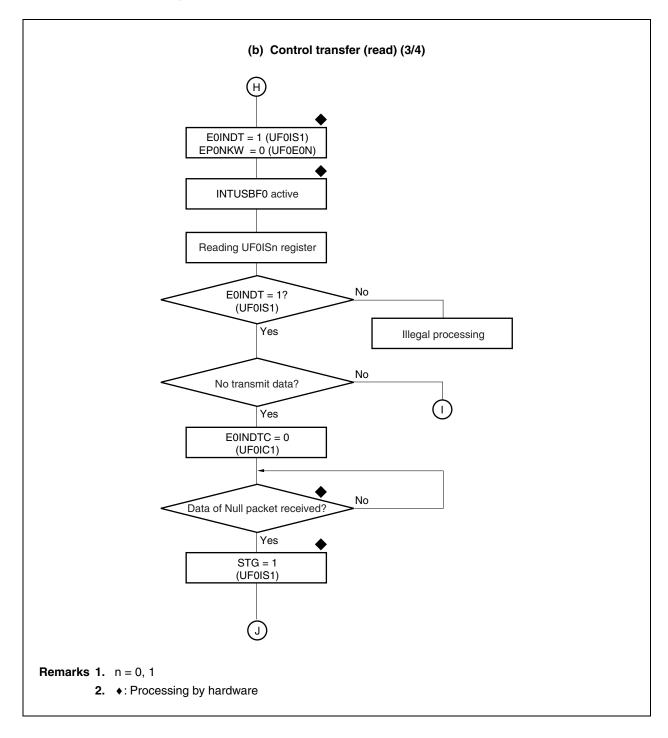

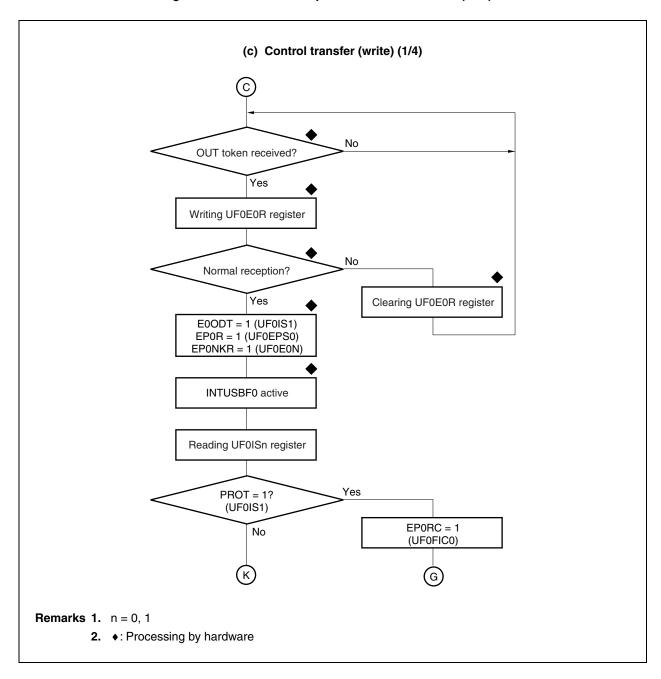

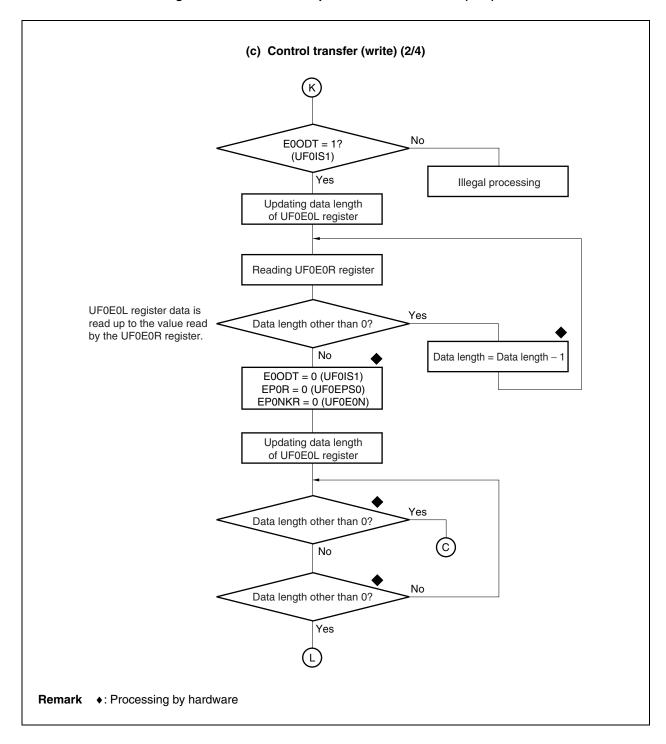

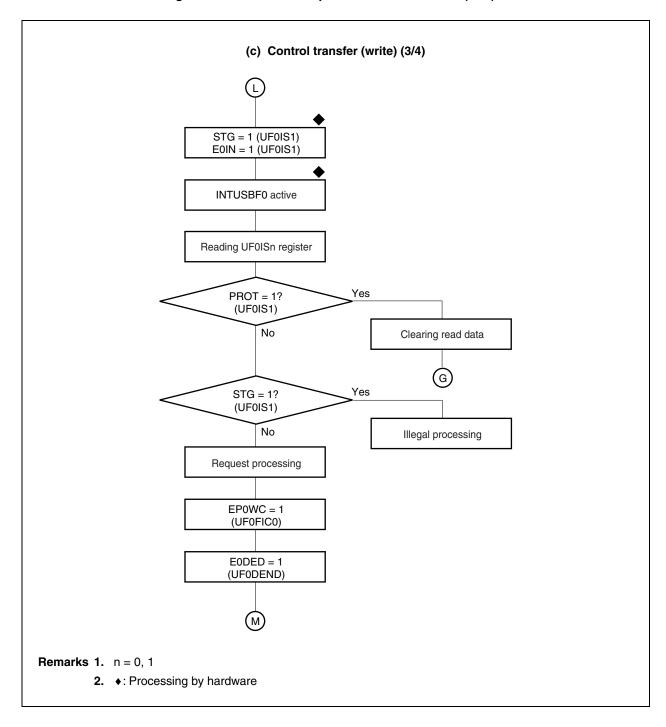

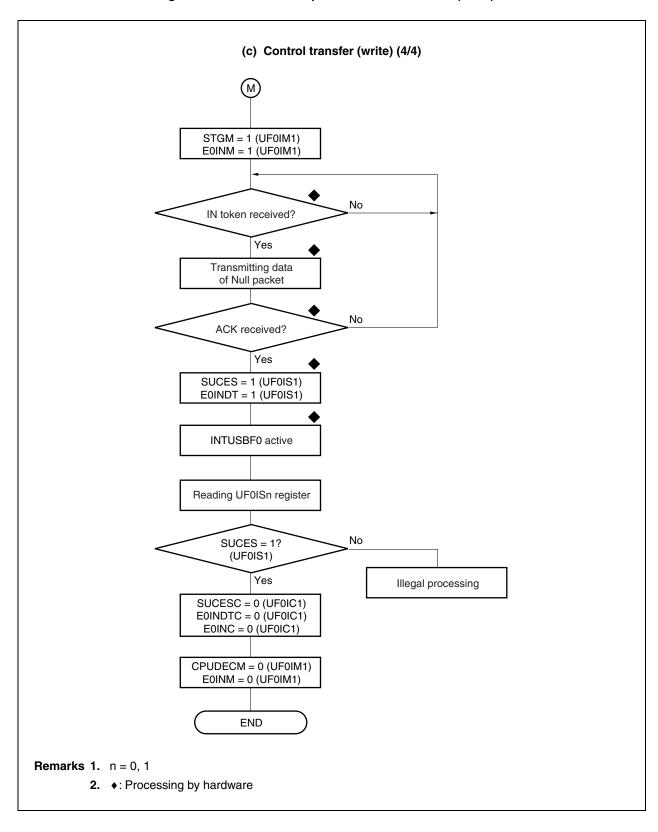

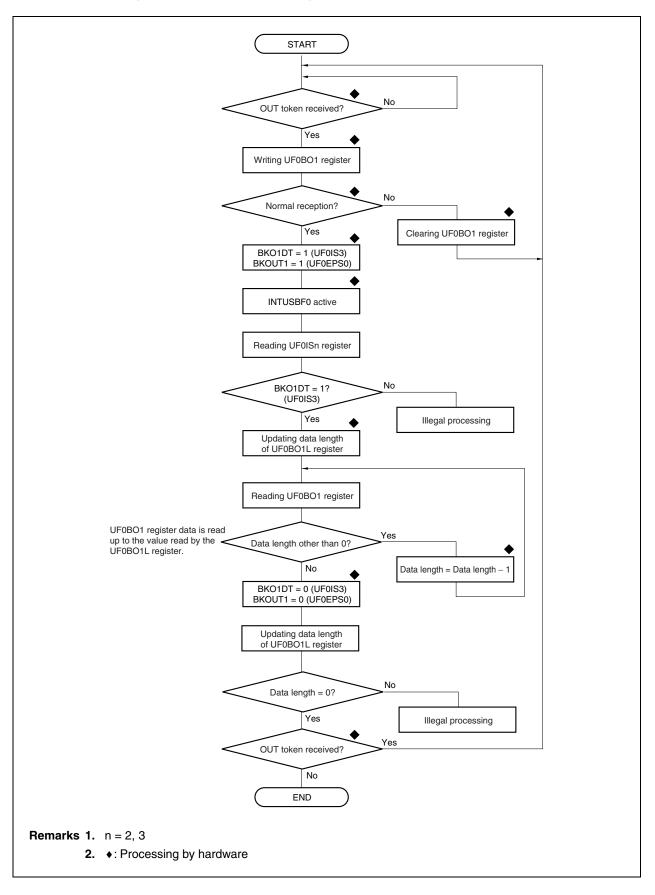

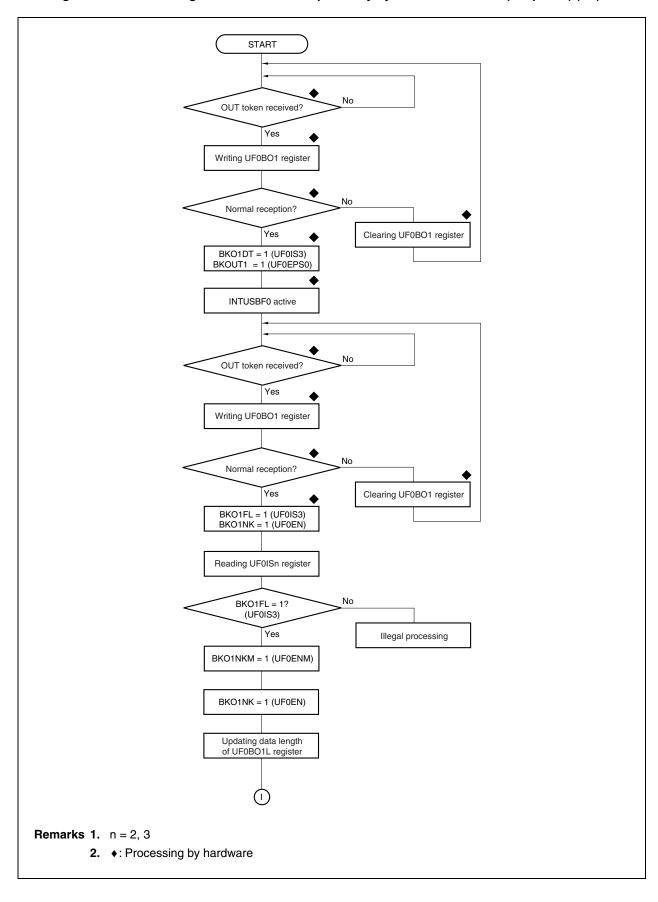

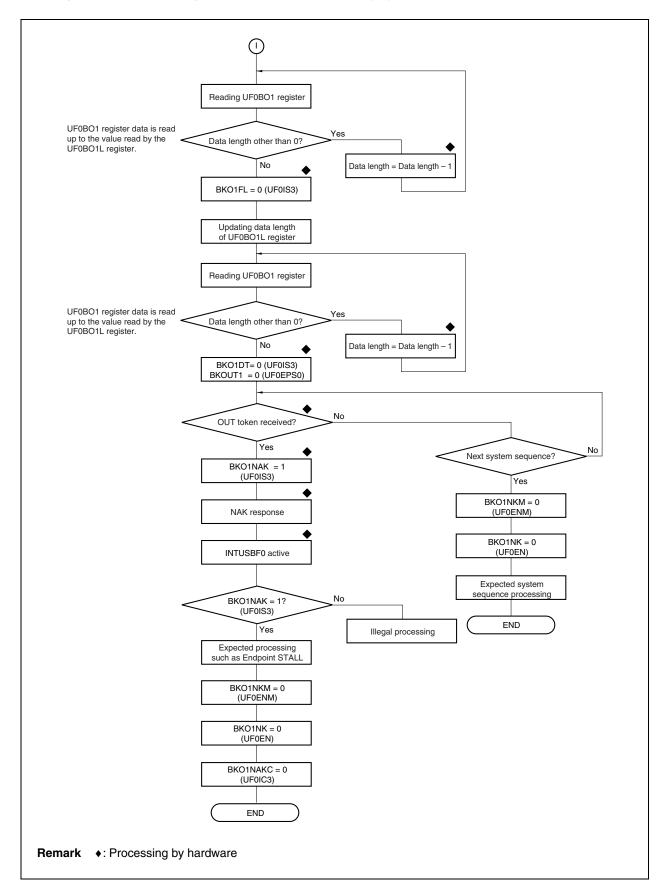

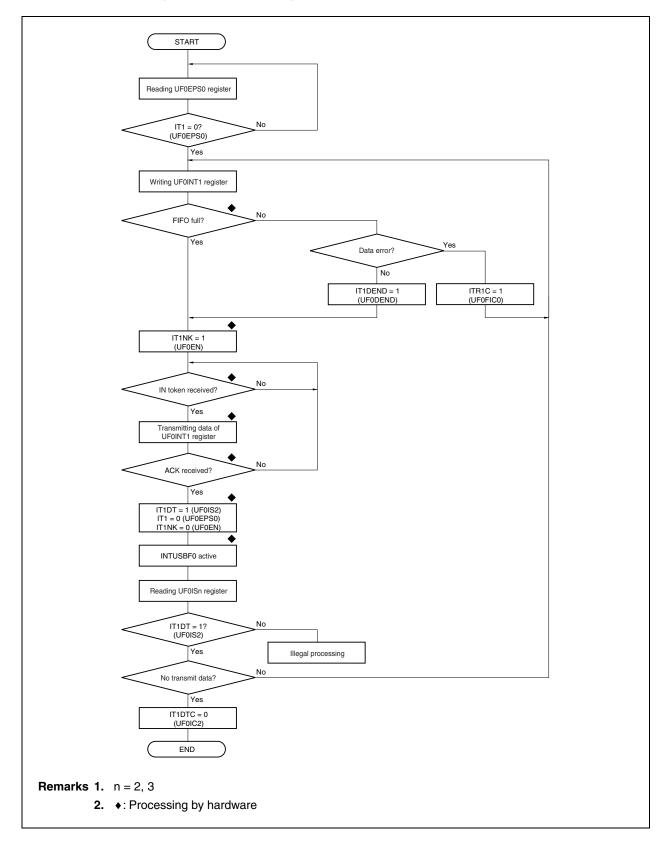

| 18.9   | FW Pro   | ocessing                                                                        | 1092 |

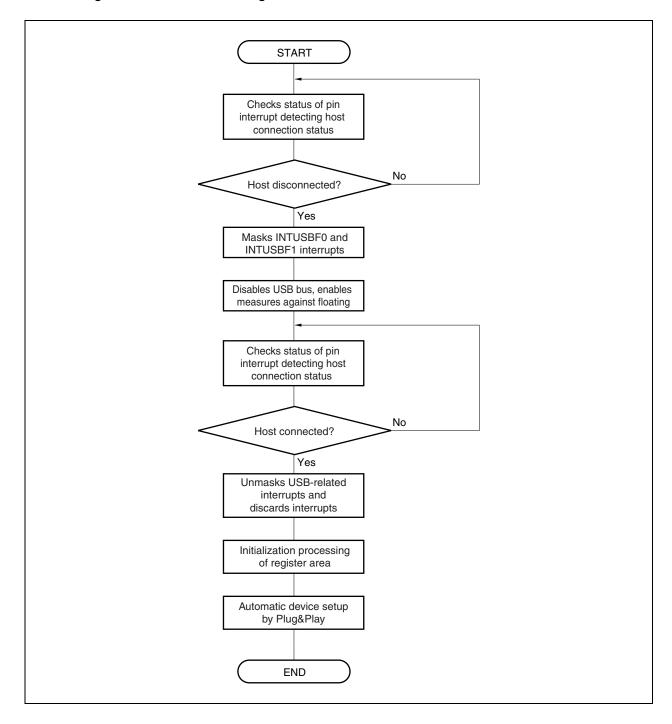

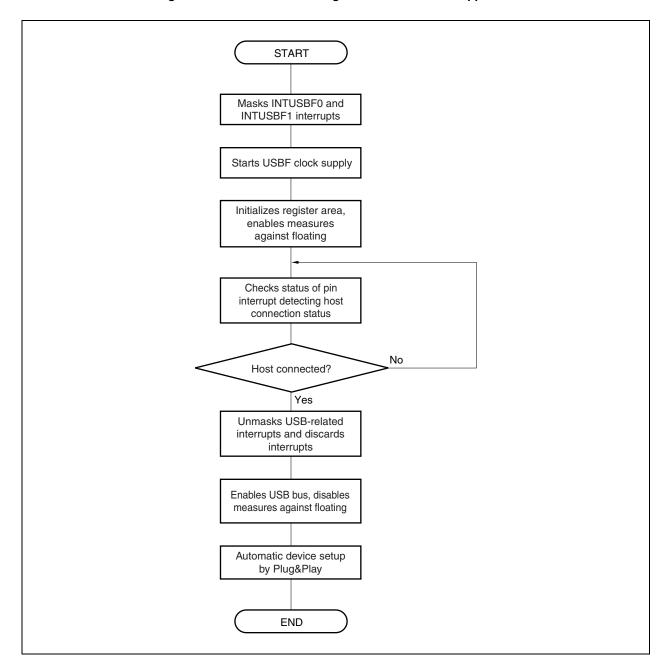

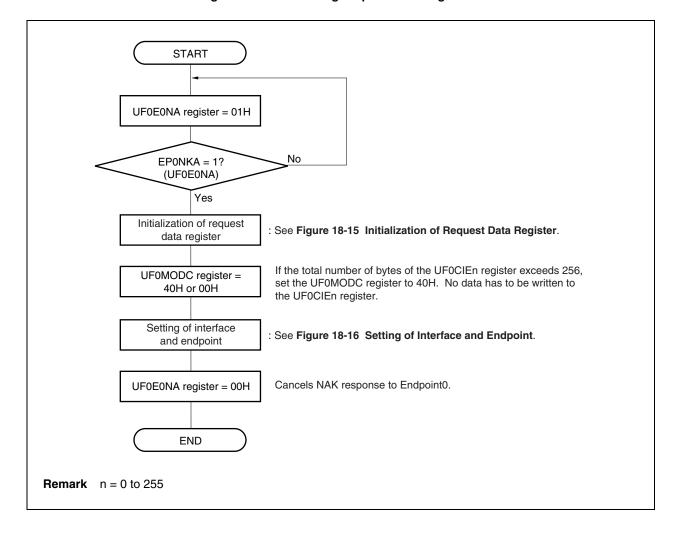

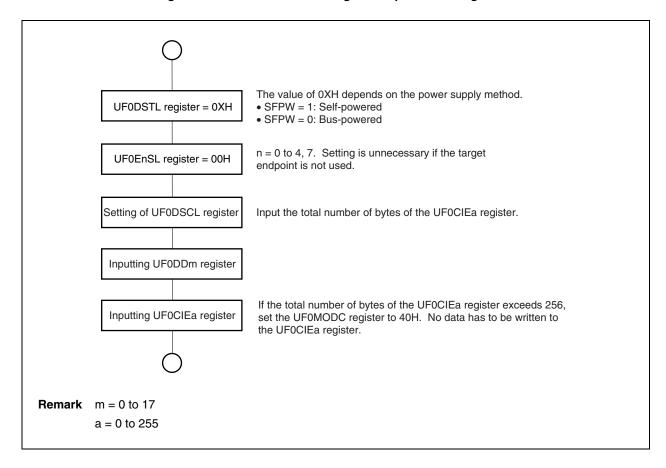

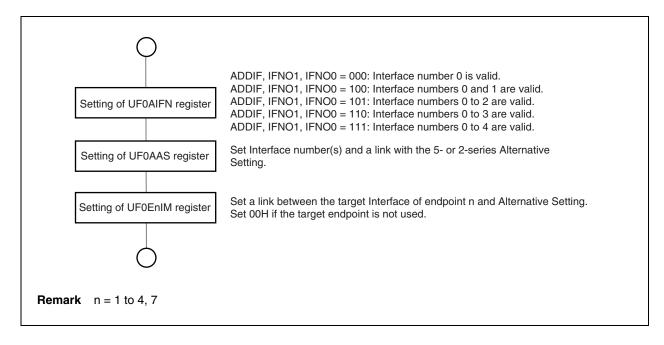

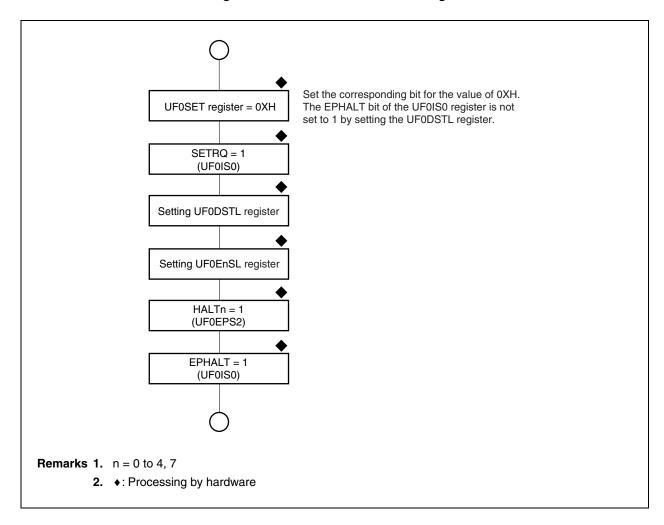

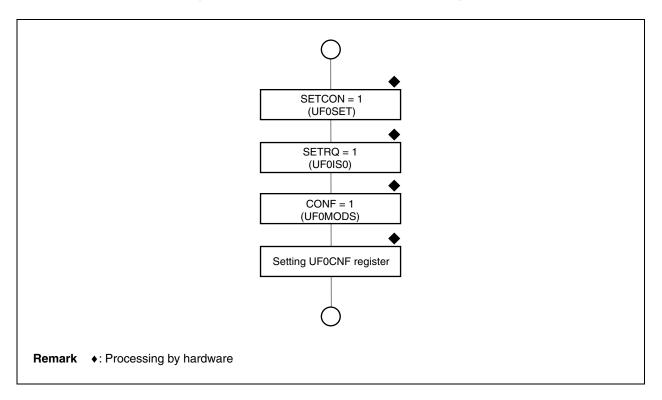

|        | 18.9.1   | Initialization processing                                                       | 1094 |

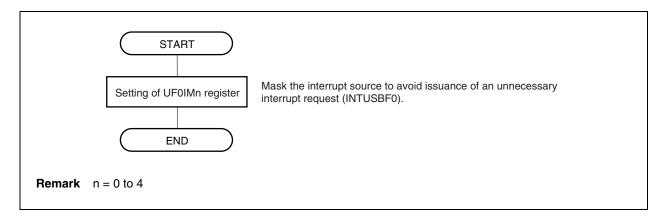

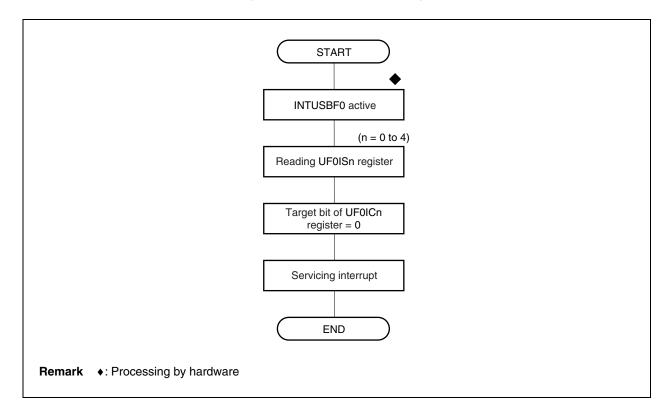

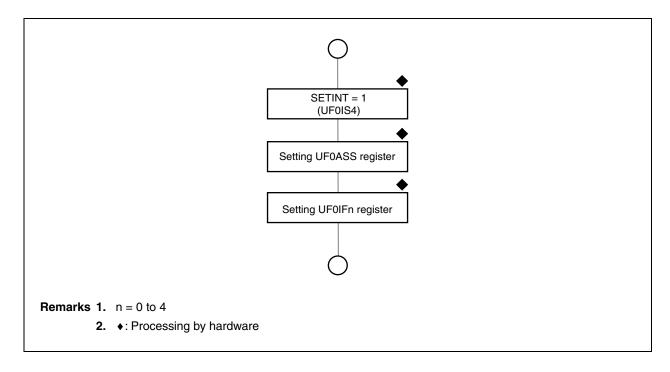

|        | 18.9.2   | Interrupt servicing                                                             | 1097 |

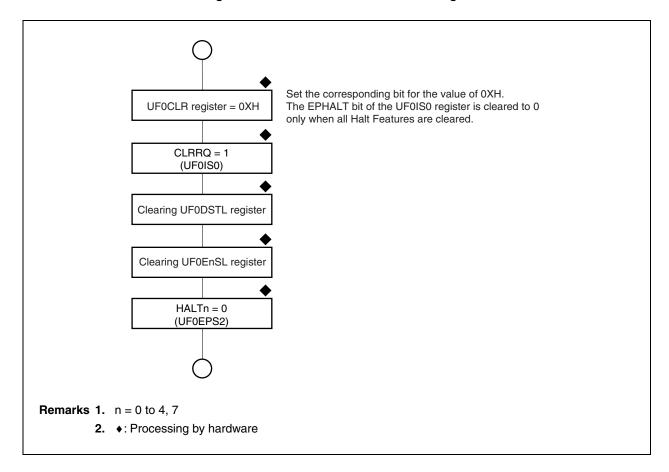

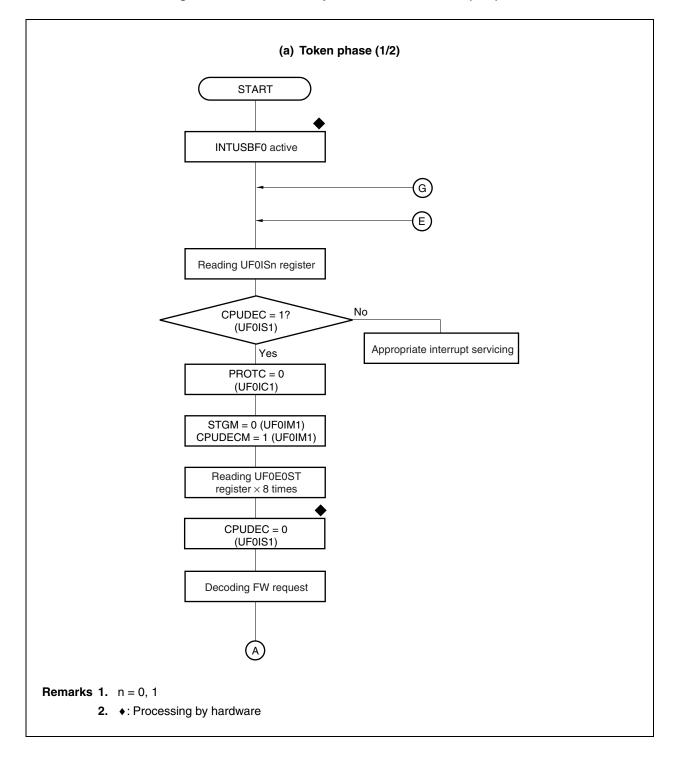

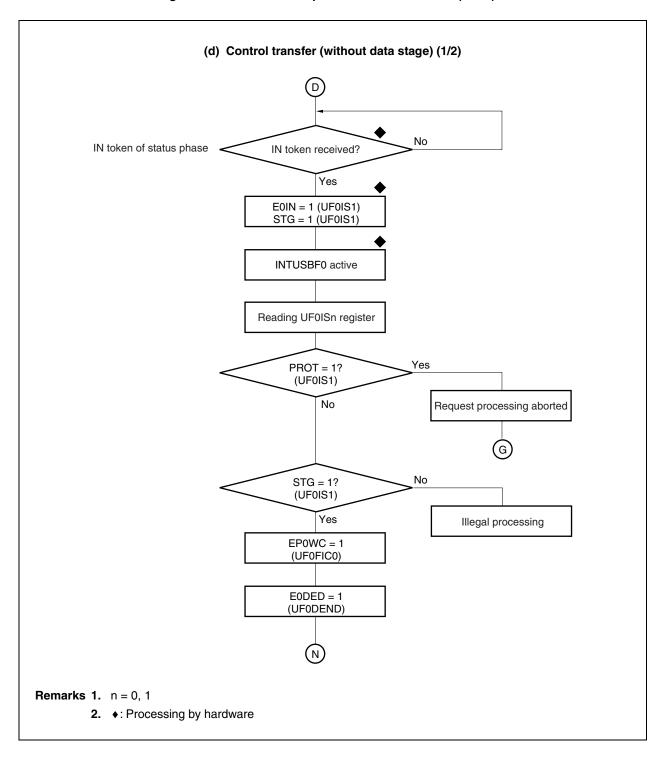

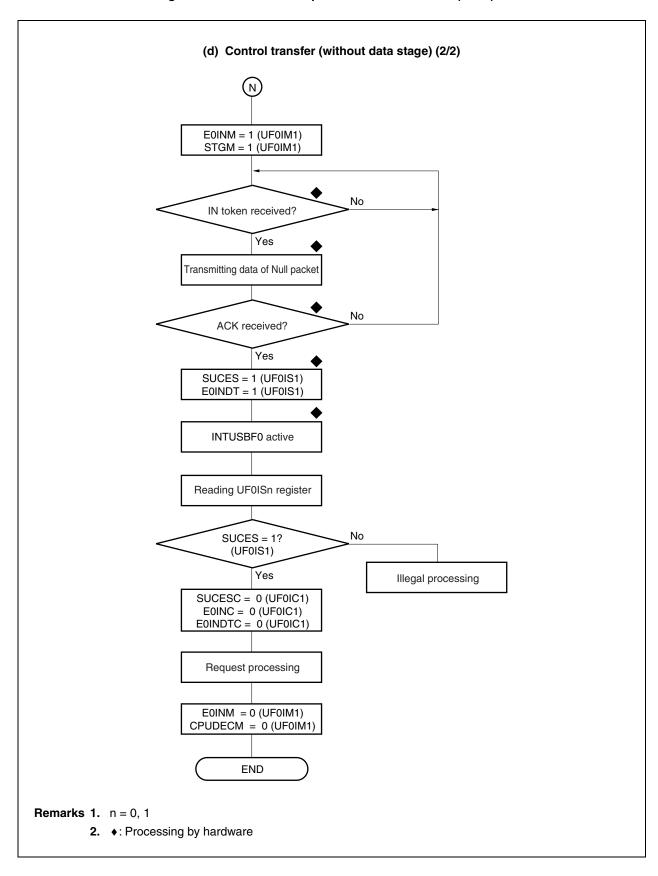

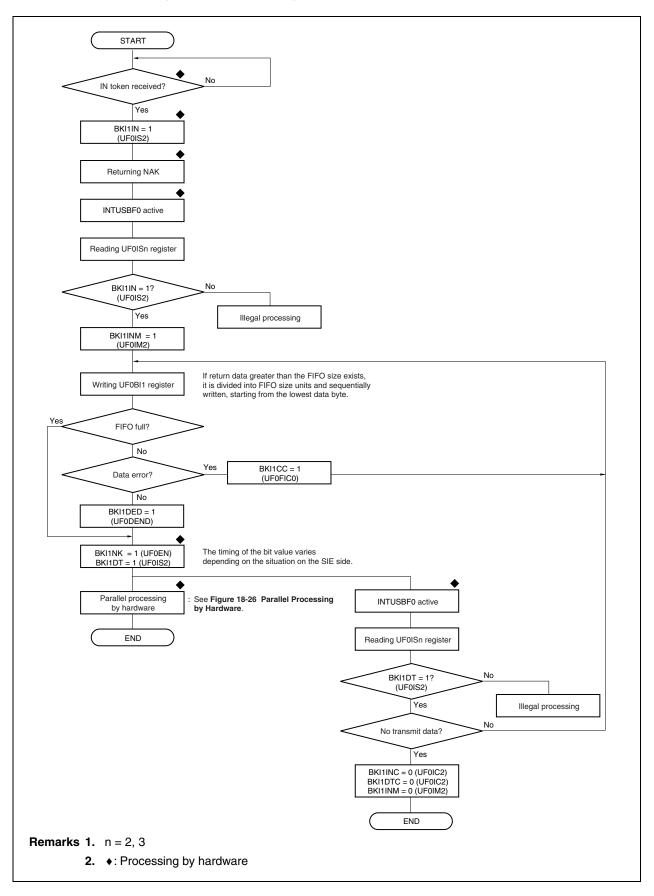

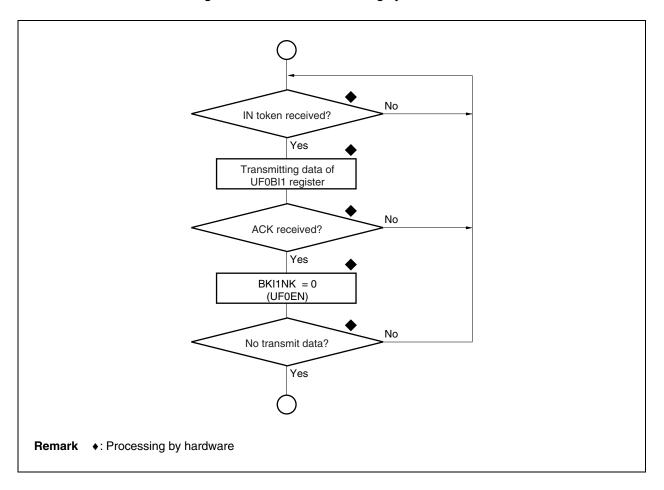

|        | 18.9.3   | USB main processing                                                             | 1098 |

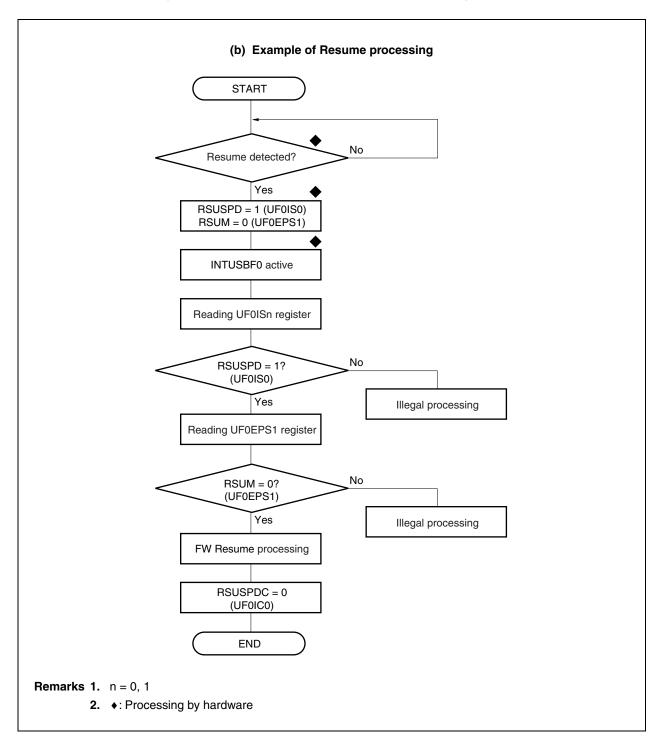

|        | 18.9.4   | Suspend/Resume processing                                                       | 1124 |

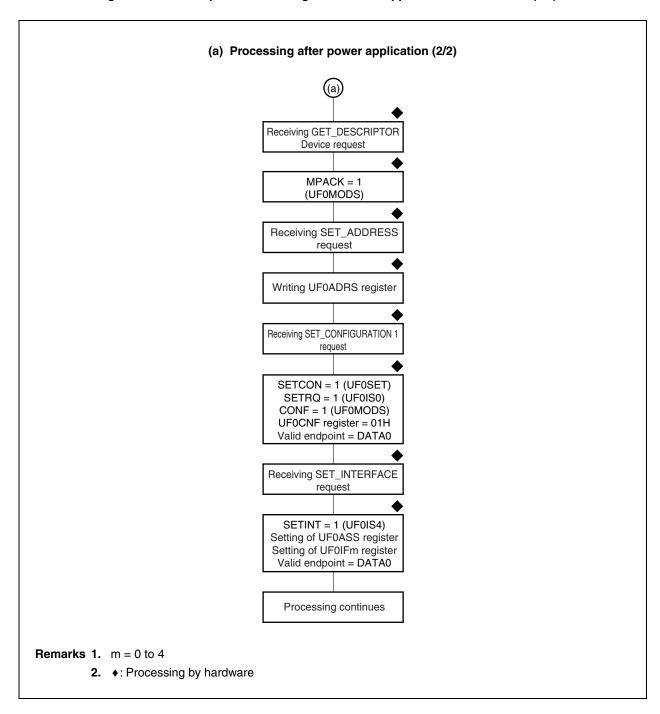

|        | 18.9.5   | Processing after power application                                              | 1127 |

| CHAPTE | R 19 B   | US CONTROL FUNCTION                                                             | 1130 |

| 19.1   | Feature  | 9S                                                                              | 1130 |

| 19.2   | Bus Co   | ontrol Pins                                                                     | 1131 |

|        | 19.2.1   | Pin status during internal ROM, internal RAM, and on-chip peripheral I/O access | 1131 |

| 19.3   | Memor    | y Block Function                                                                | 1132 |

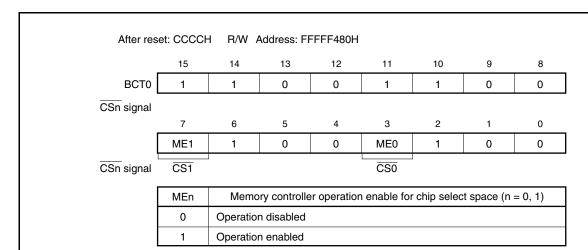

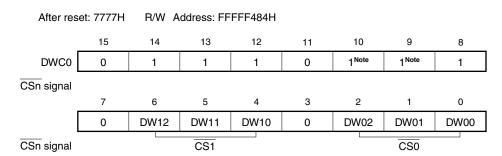

|        | 19.3.1   | Chip select control function                                                    | 1133 |

| 19.4   | Bus Cy   | cle Type Control Function                                                       | 1133 |

| 19.5   | Bus Ac   | cess                                                                            | 1134 |

|        | 19.5.1   | Number of access clocks                                                         | 1134 |

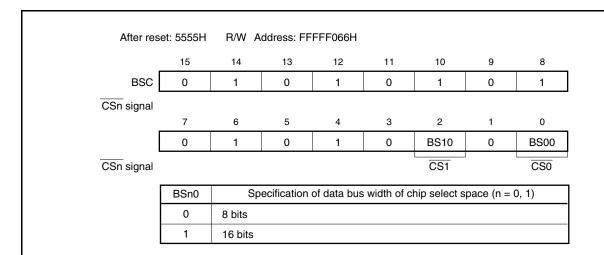

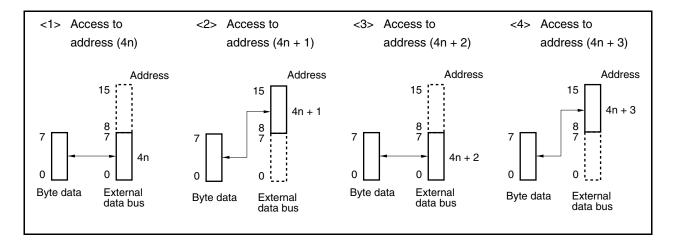

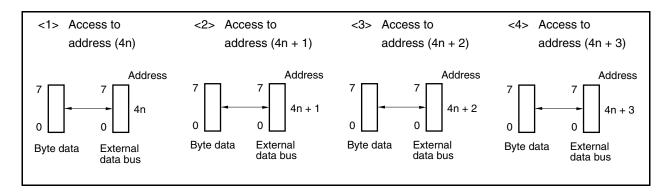

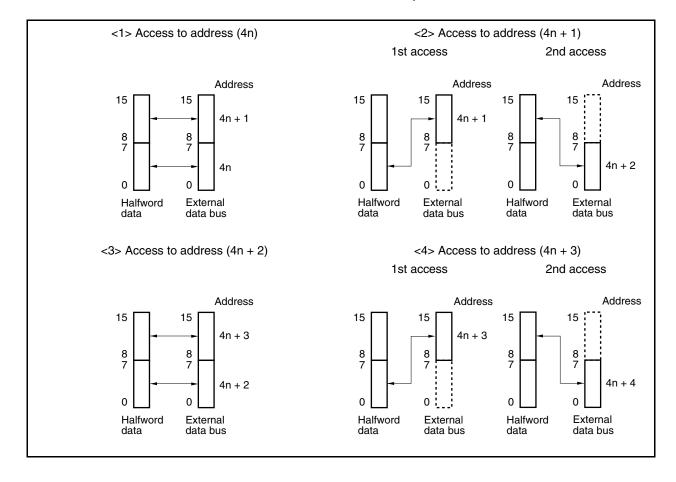

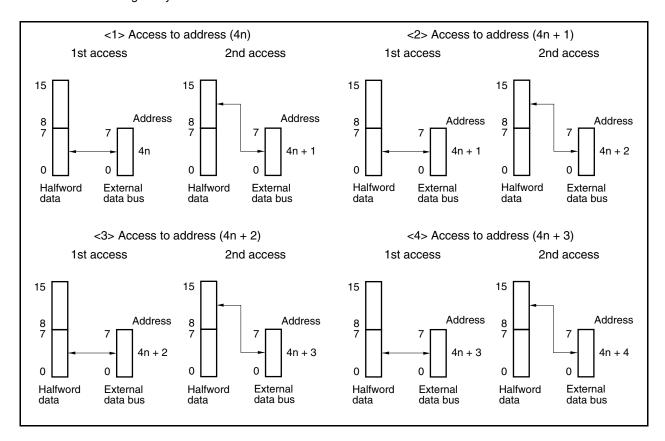

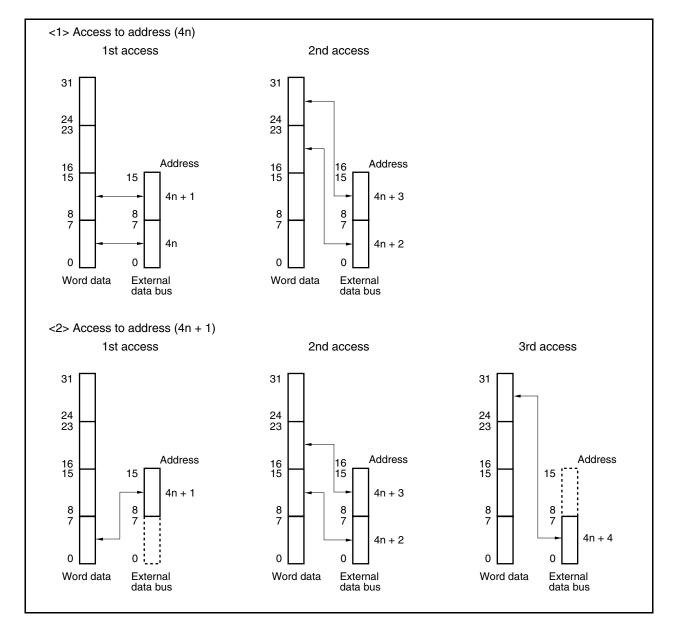

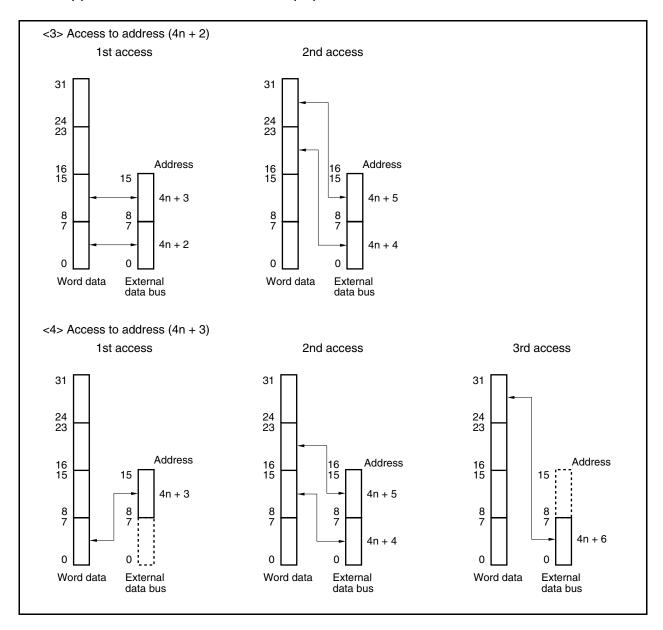

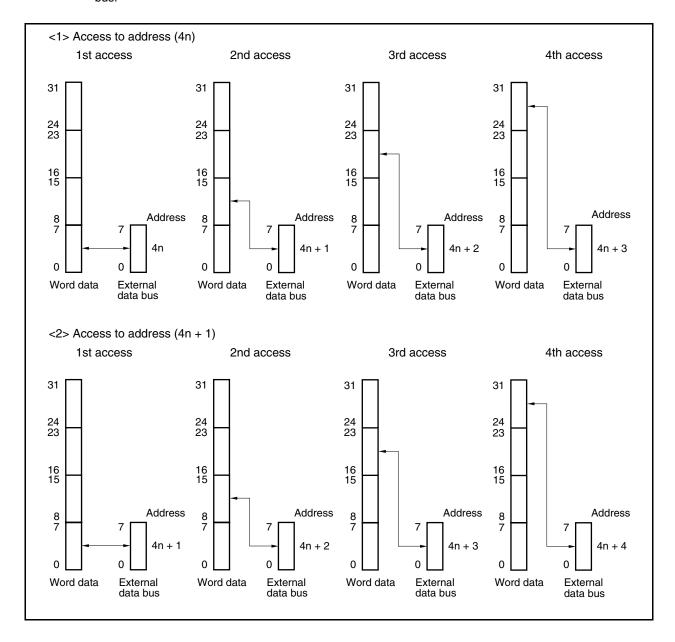

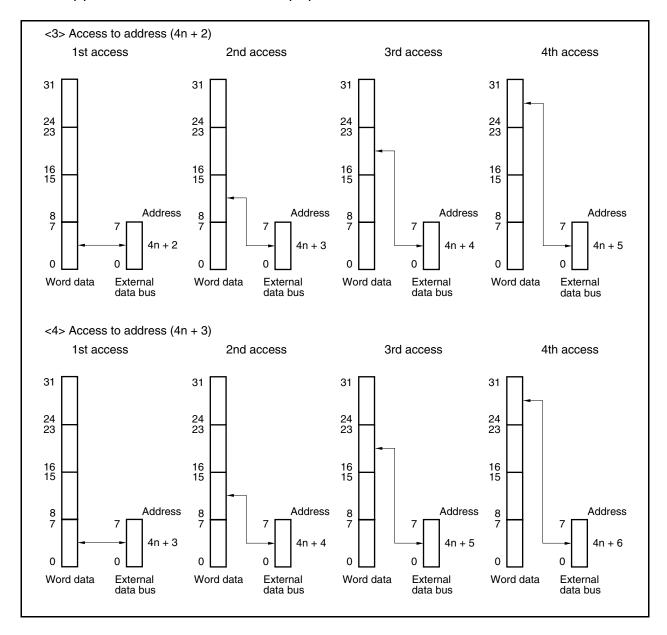

|        | 19.5.2   | Bus sizing function                                                             | 1135 |

|        | 19.5.3   | Endian function                                                                 | 1136 |

|        | 19.5.4   | Bus width                                                                       | 1136 |

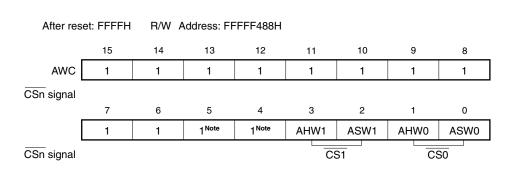

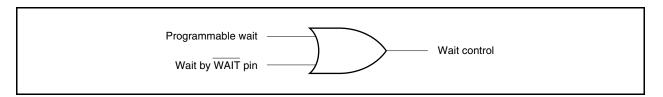

| 19.6   | Wait Fเ  | unction                                                                         | 1143 |

|        | 19.6.1   | Programmable wait function                                                      | 1143 |

|        | 19.6.2   | External wait function                                                          | 1146 |

|    |        | 19.6.3   | Relationship between programmable wait and external wait                         | 1146 |

|----|--------|----------|----------------------------------------------------------------------------------|------|

|    |        | 19.6.4   | Bus cycles in which wait function is valid                                       | 1148 |

|    | 19.7   | Idle Sta | ate Insertion Function                                                           | 1148 |

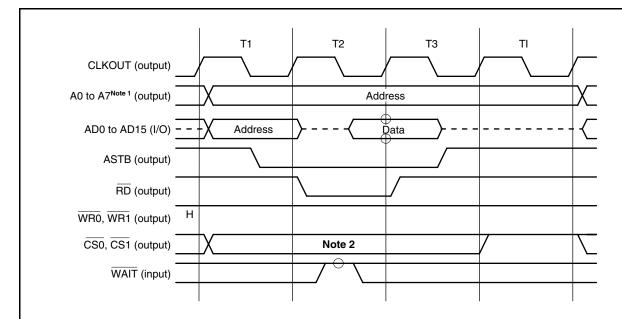

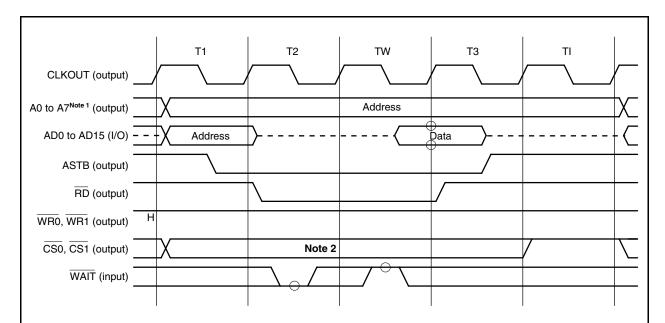

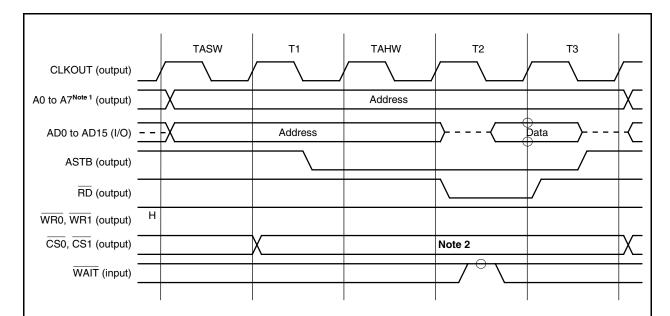

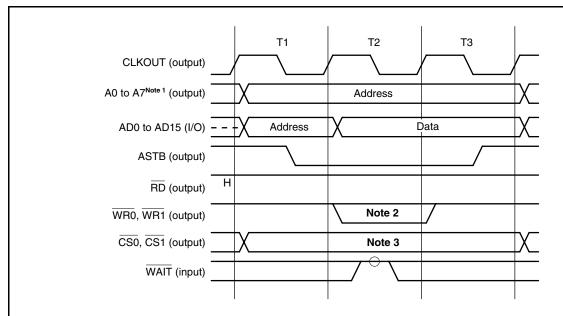

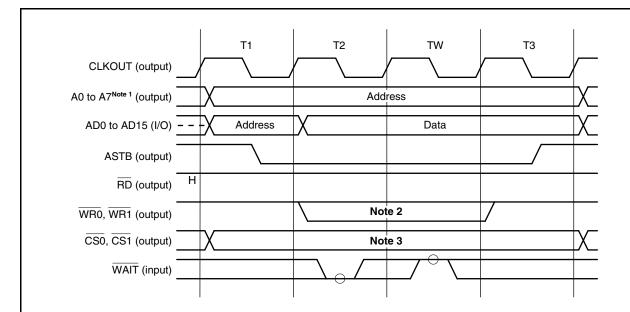

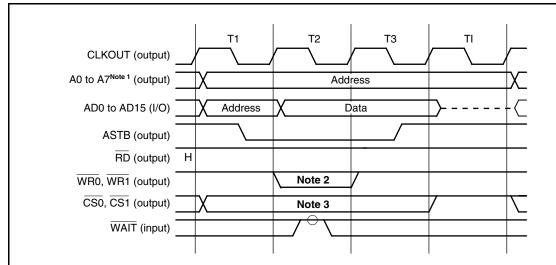

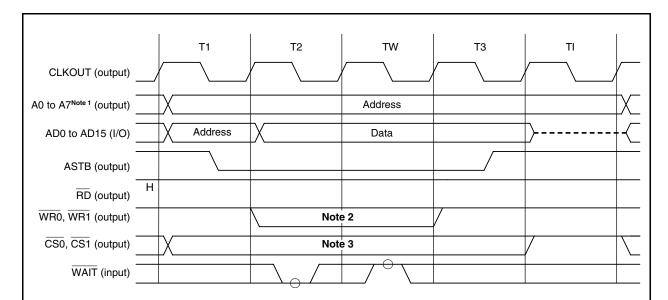

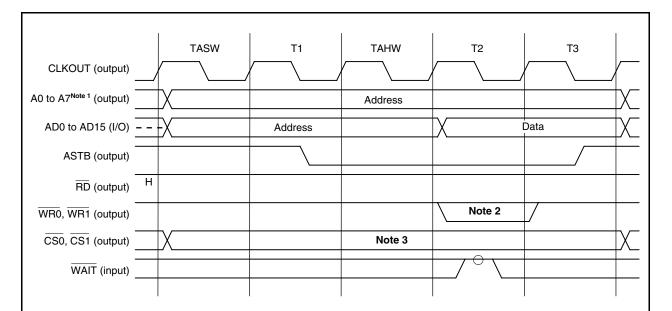

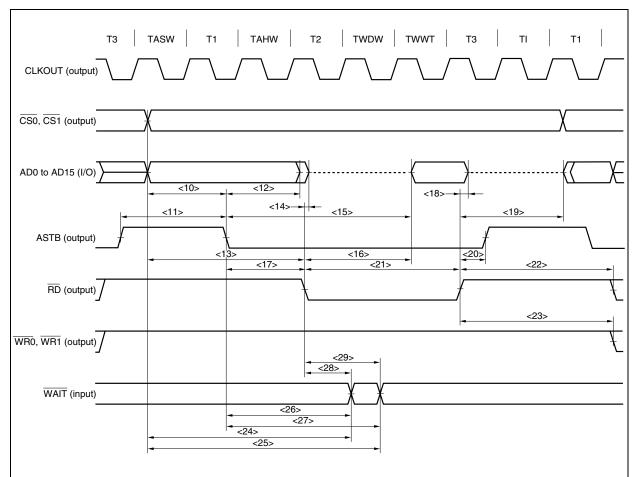

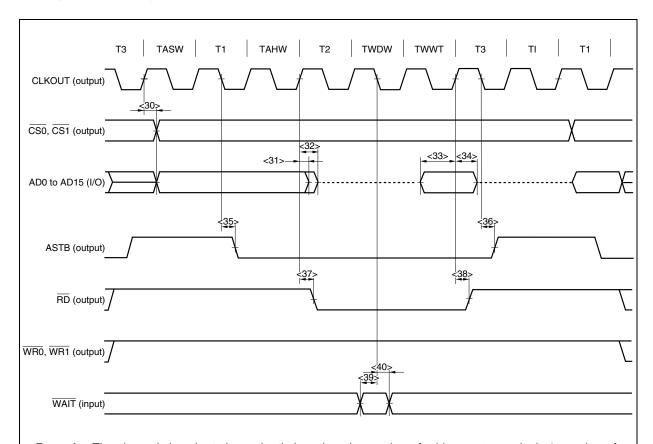

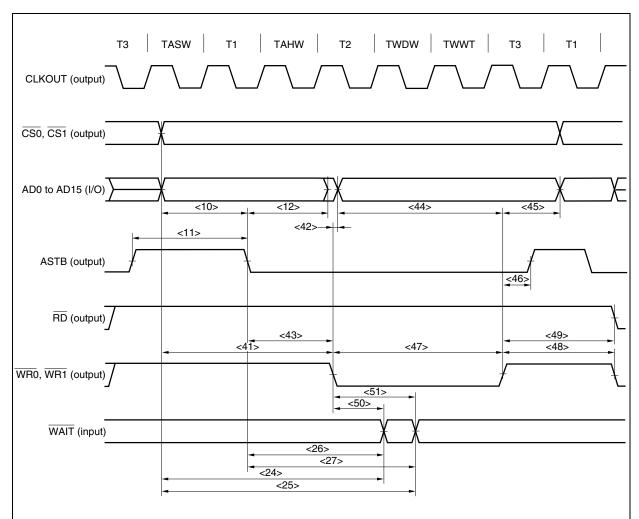

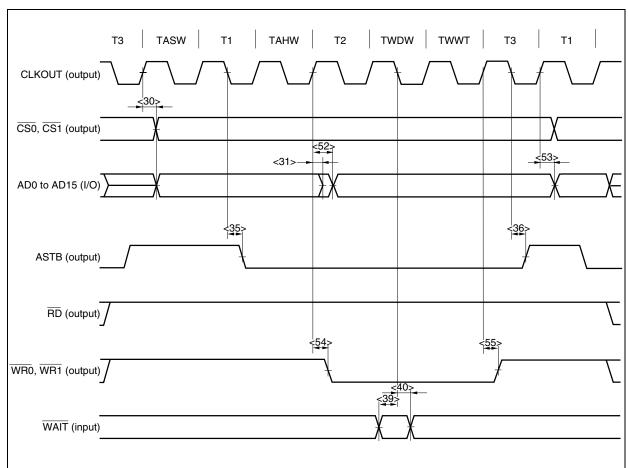

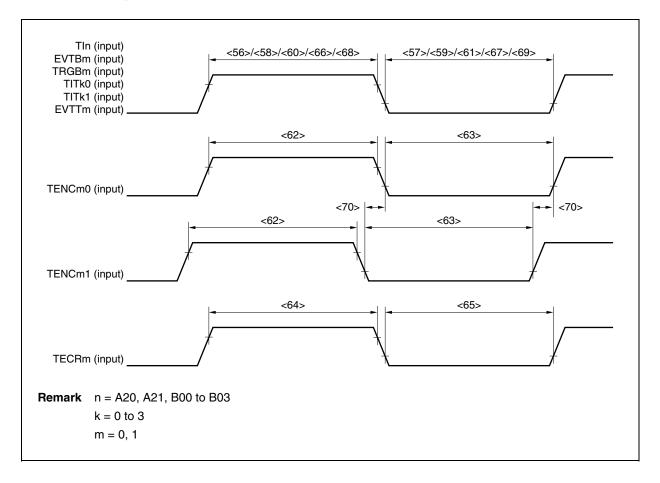

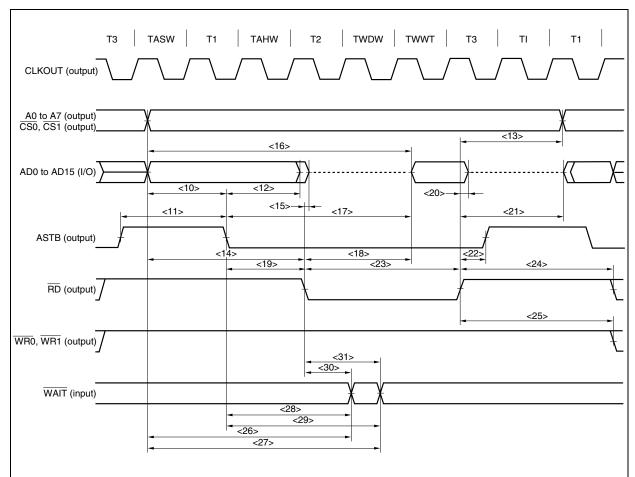

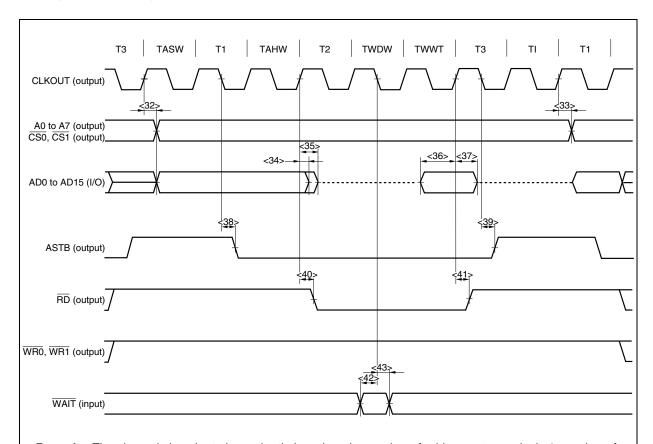

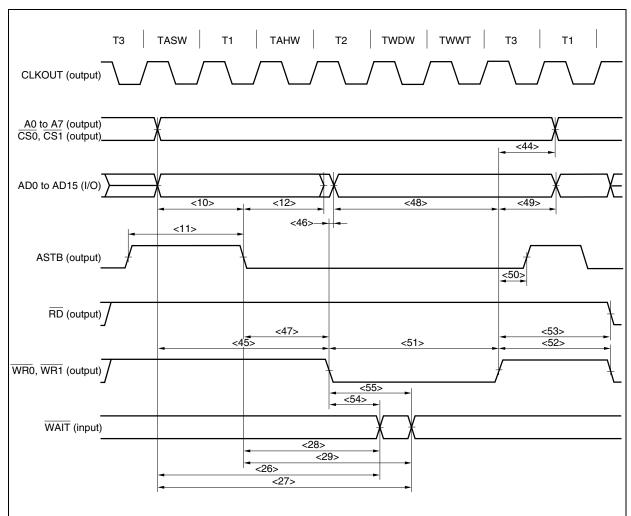

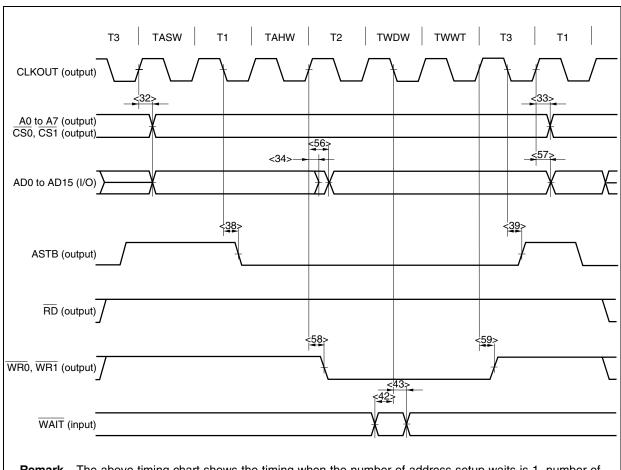

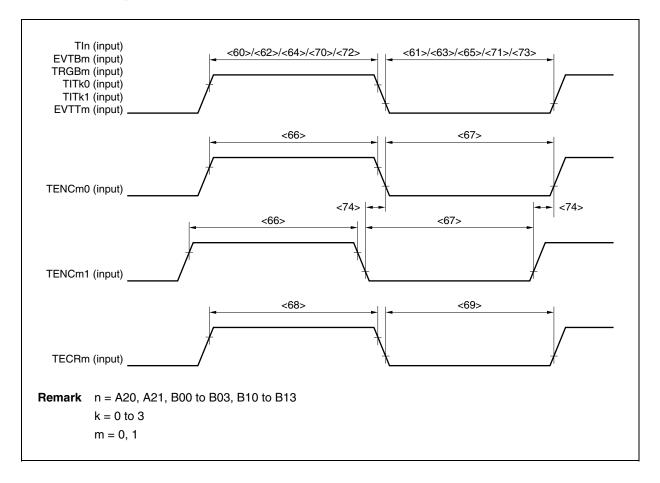

|    | 19.8   | Bus Tir  | ming                                                                             | 1151 |

|    | 19.9   | Bus Pr   | iority Order                                                                     | 1161 |

|    | 19.10  | Bounda   | ary Operation Conditions                                                         | 1161 |

|    |        | 19.10.1  | Program space                                                                    | 1161 |

|    |        | 19.10.2  | Data space                                                                       | 1161 |

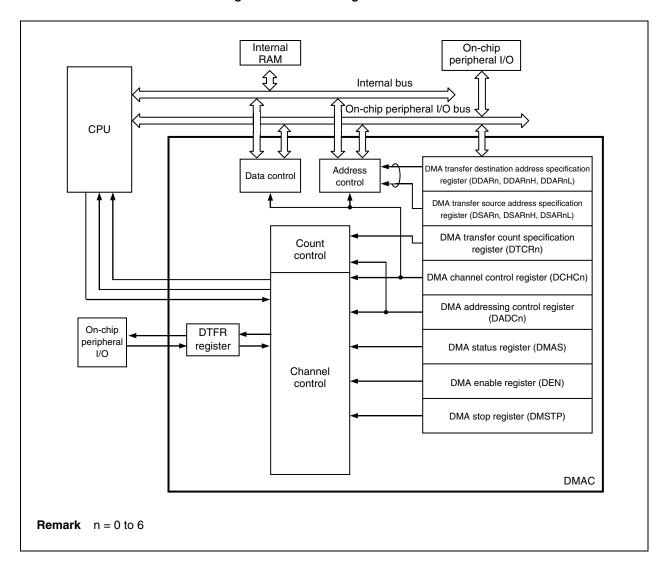

| CH | IAPTEF | R 20 D   | MA (DMA CONTROLLER)                                                              | 1162 |

|    | 20.1   | Feature  | es                                                                               | 1162 |

|    | 20.2   | Config   | uration                                                                          | 1163 |

|    |        | 20.2.1   | DMAC configuration                                                               | 1163 |

|    |        | 20.2.2   | Operation outline                                                                | 1164 |

|    |        | 20.2.3   | Number of DMA transfer clock cycles                                              | 1164 |

|    | 20.3   | Contro   | I Registers                                                                      | 1165 |

|    |        | 20.3.1   | DMA transfer destination address specification registers 0 to 6 (DDAR0 to DDAR6) | 1165 |

|    |        | 20.3.2   | DMA transfer source address specification registers 0 to 6 (DSAR0 to DSAR6)      | 1168 |

|    |        | 20.3.3   | DMA transfer count specification registers 0 to 6 (DTCR0 to DTCR6)               | 1171 |

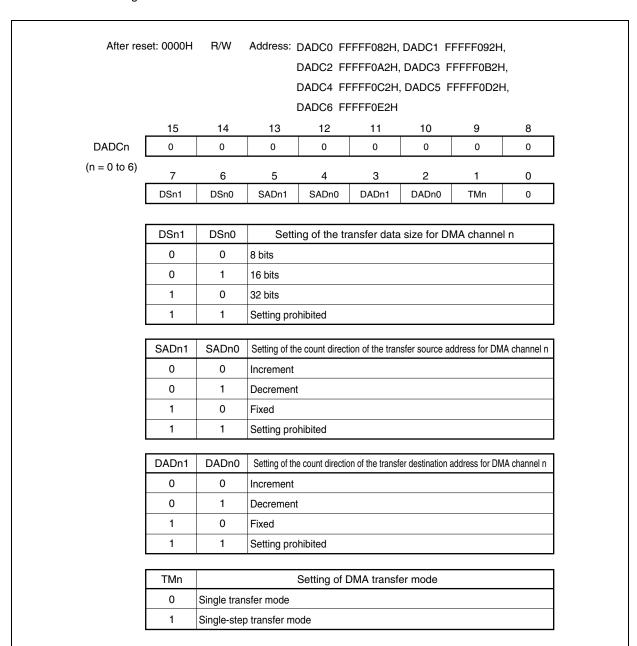

|    |        | 20.3.4   | DMA addressing control registers 0 to 6 (DADC0 to DADC6)                         | 1172 |

|    |        | 20.3.5   | DMA channel control registers 0 to 6 (DCHC0 to DCHC6)                            | 1173 |

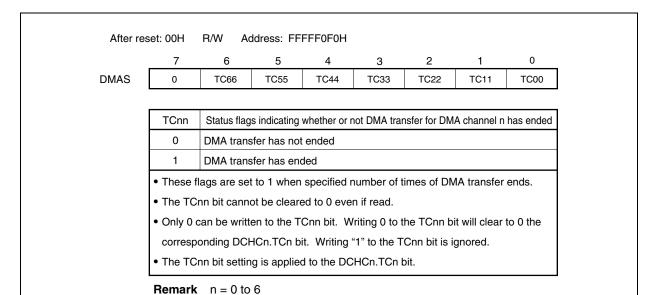

|    |        | 20.3.6   | DMA status register (DMAS)                                                       | 1176 |

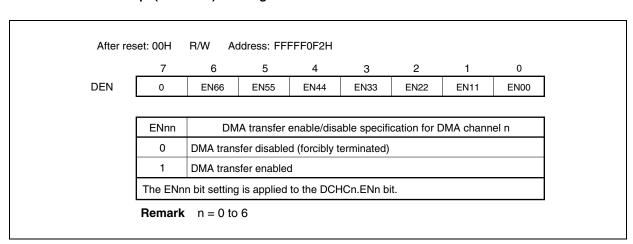

|    |        | 20.3.7   | DMA enable register (DEN)                                                        | 1177 |

|    |        | 20.3.8   | DMA stop register (DMSTP)                                                        | 1178 |

|    |        | 20.3.9   | DMA trigger factor register n (DTFRn)                                            | 1179 |

|    | 20.4   | Transfe  | er Modes                                                                         | 1184 |

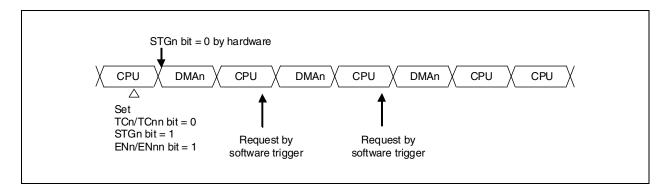

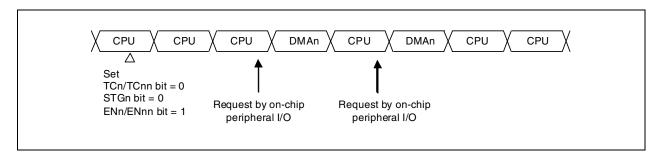

|    |        | 20.4.1   | Single transfer mode                                                             | 1184 |

|    |        | 20.4.2   | Single-step transfer mode                                                        | 1187 |

|    | 20.5   | Transfe  | er Types                                                                         | 1189 |

|    | 20.6   | Transfe  | er Sources and Destinations                                                      | 1189 |

|    | 20.7   | DMA C    | hannel Priorities                                                                | 1189 |

|    | 20.8   | Next A   | ddress Setting Function                                                          | 1190 |

|    | 20.9   | Buffer   | Register Configuration                                                           | 1190 |

|    | 20.10  | DMA T    | ransfer Start Triggers                                                           | 1191 |

|    | 20.11  | Susper   | nsion                                                                            | 1192 |

|    |        |          | DMA Transfer                                                                     |      |

|    |        |          | e Termination                                                                    |      |

|    | 20.14  | Caution  | ns                                                                               | 1193 |

| CH | IAPTEF | R 21 IN  | ITERRUPT SERVICING/EXCEPTION PROCESSING FUNCTION                                 | 1195 |

|    | 21.1   | Feature  | es                                                                               | 1195 |

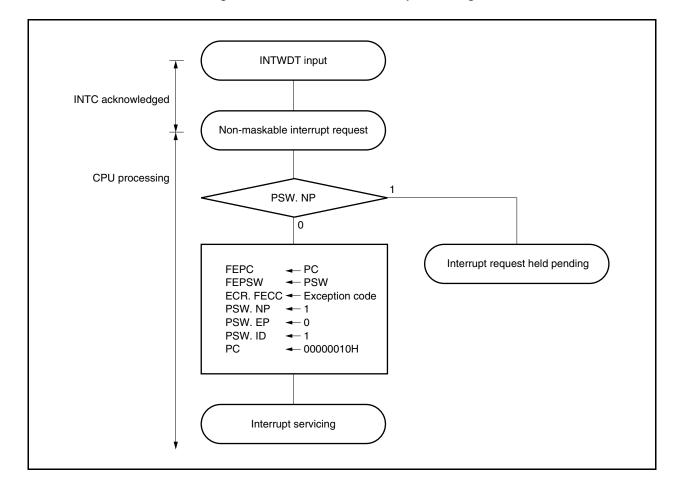

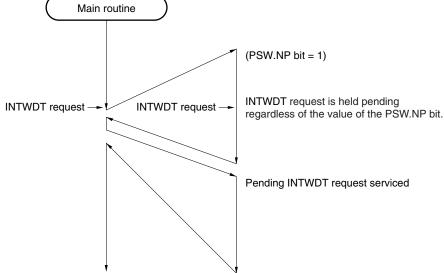

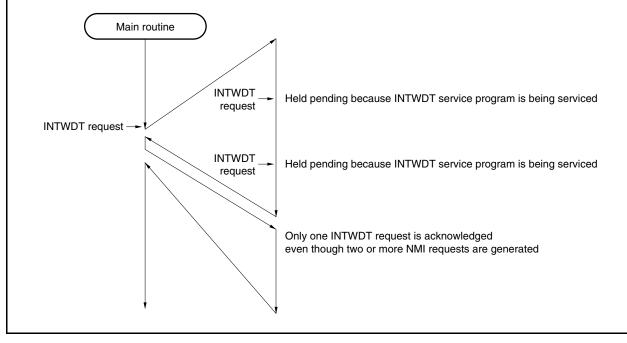

|    | 21.2   | Non-Ma   | askable Interrupts                                                               | 1201 |

|    |        | 21.2.1   | Operation                                                                        | 1202 |

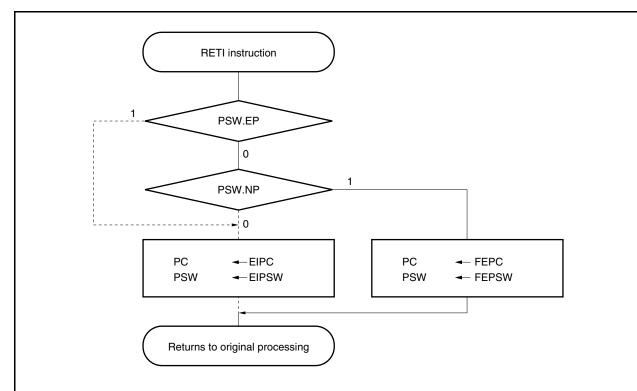

|    |        | 21.2.2   | Return processing                                                                | 1204 |

|    |        | 21.2.3   | Non-maskable interrupt status flag (NP)                                          |      |

|    |        |          |                                                                                  |      |

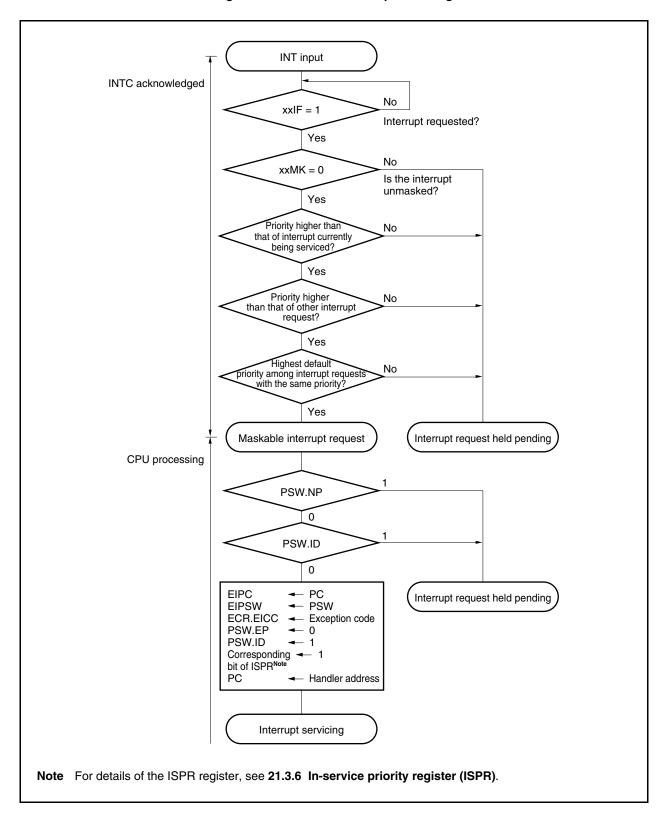

| 21.3         | Maskable Interrupts                                                        | 1206 |

|--------------|----------------------------------------------------------------------------|------|

|              | 21.3.1 Operation                                                           | 1206 |

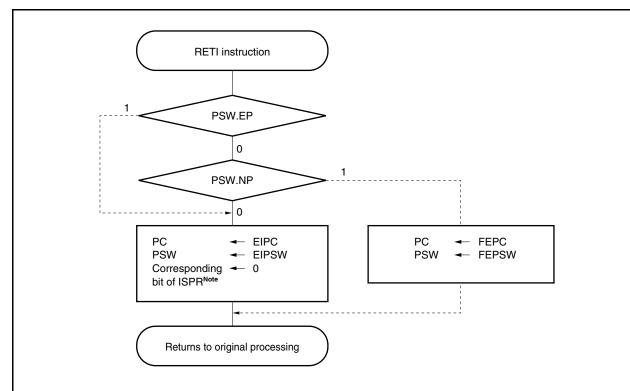

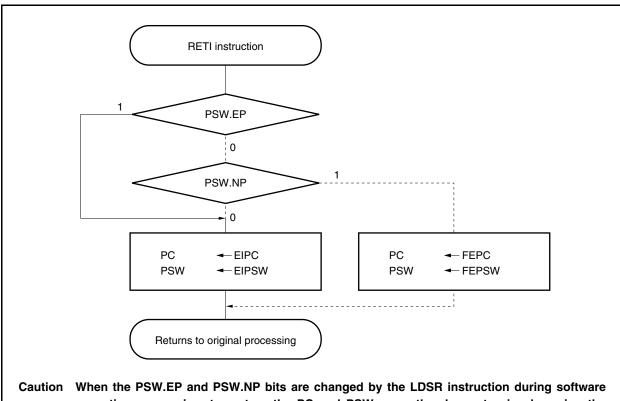

|              | 21.3.2 Return processing                                                   | 1208 |

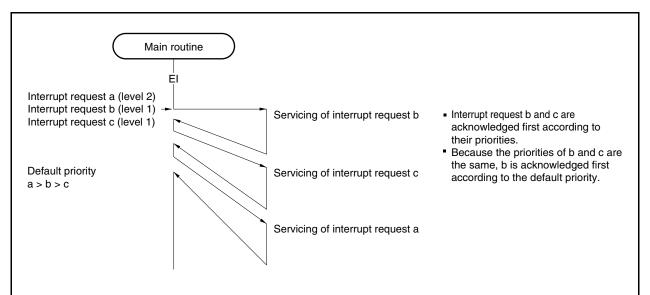

|              | 21.3.3 Priorities of maskable interrupts                                   | 1209 |

|              | 21.3.4 Interrupt control registers (xxICn)                                 | 1213 |

|              | 21.3.5 Interrupt mask registers 0 to 6 (IMR0 to IMR6)                      | 1218 |

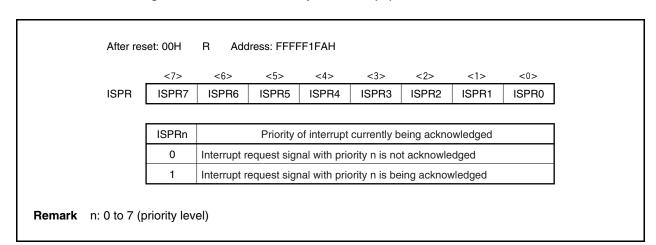

|              | 21.3.6 In-service priority register (ISPR)                                 | 1221 |

|              | 21.3.7 Maskable interrupt status flag (ID)                                 | 1222 |

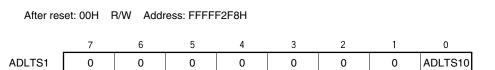

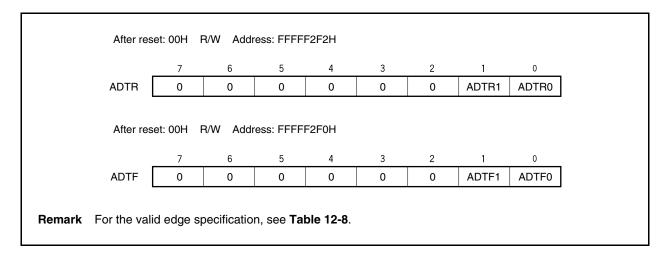

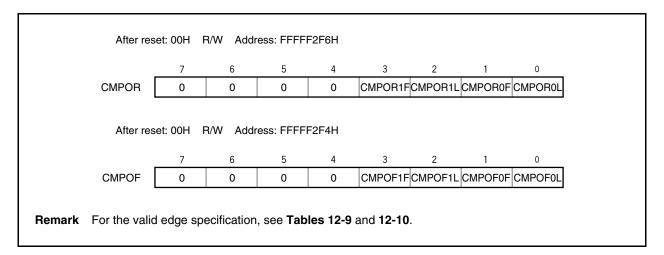

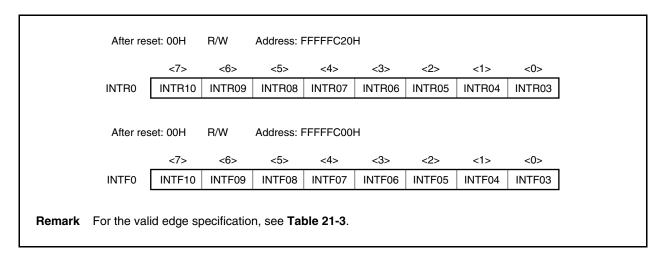

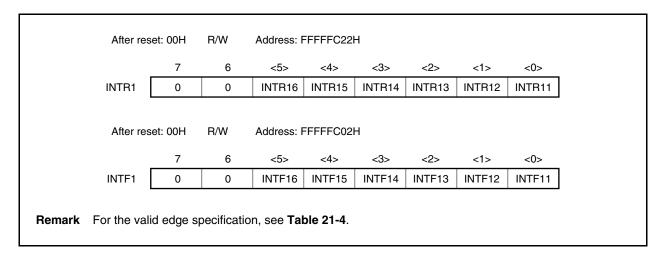

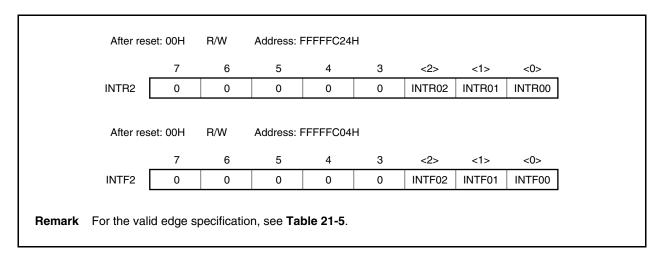

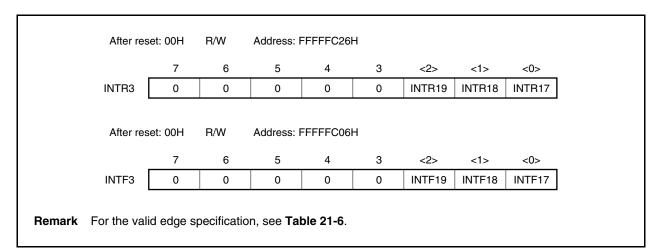

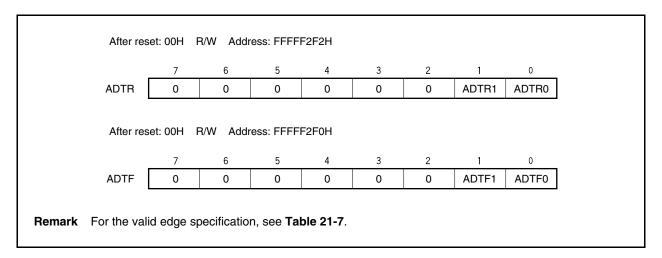

| 21.4         | External Interrupt Request Input Pins (INTP00 to INTP19, INTADT0, INTADT1) | 1223 |

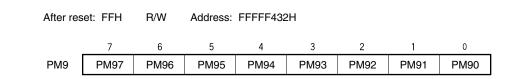

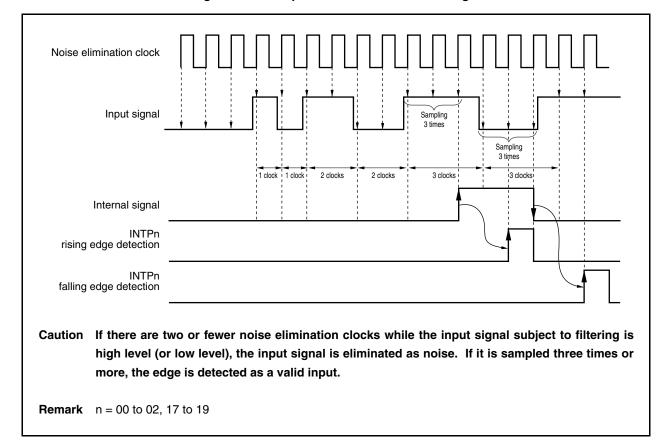

|              | 21.4.1 Noise elimination                                                   | 1223 |

|              | 21.4.2 Edge detection                                                      | 1223 |

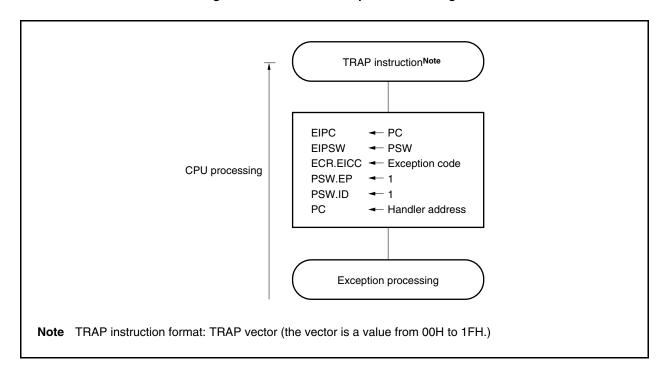

| 21.5         | Software Exception                                                         | 1229 |

|              | 21.5.1 Operation                                                           | 1229 |

|              | 21.5.2 Return processing                                                   | 1230 |

|              | 21.5.3 Exception status flag (EP)                                          | 1231 |

| 21.6         | Exception Trap                                                             | 1232 |

|              | 21.6.1 Illegal opcode definition                                           | 1232 |

|              | 21.6.2 Debug trap                                                          | 1234 |

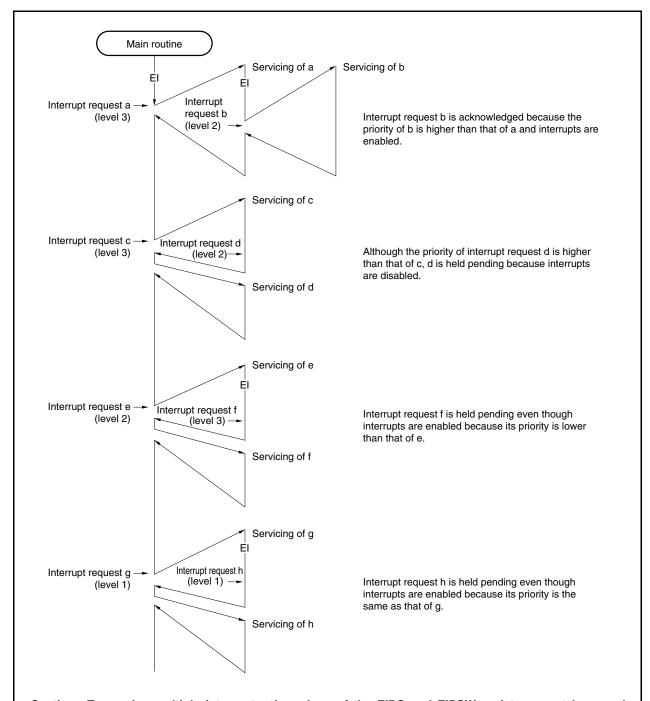

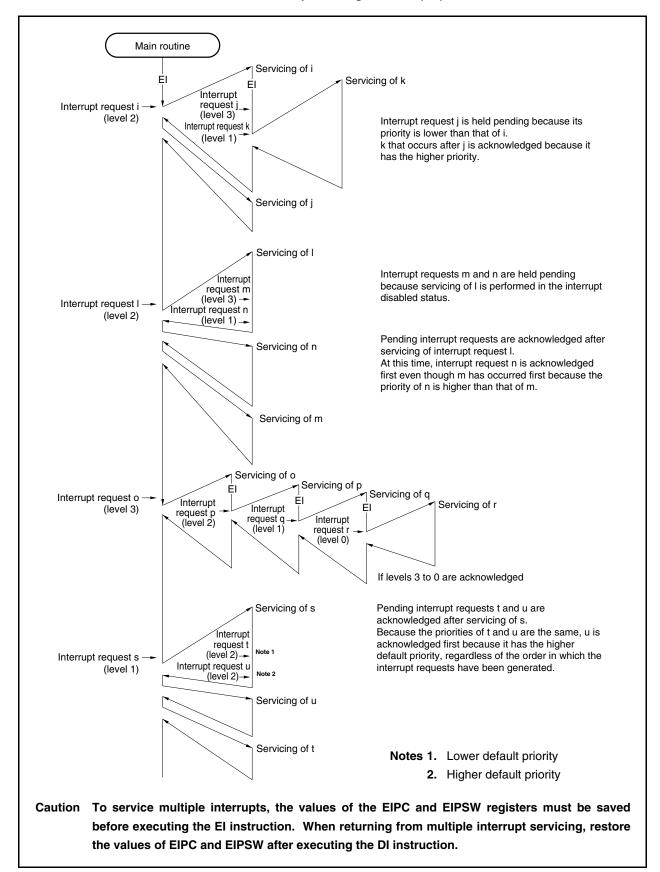

| 21.7         | Multiple Interrupt Servicing Control                                       | 1236 |

| 21.8         | Interrupt Response Time of CPU                                             | 1238 |

| 21.9         | Periods in Which CPU Does Not Acknowledge Interrupts                       | 1239 |

| 21.10        | Caution                                                                    | 1239 |

| 22.1         | Overview                                                                   |      |

| 22.2         | Control Registers HALT Mode                                                |      |

| 22.3         |                                                                            |      |

|              | 22.3.1 Setting and operation status                                        |      |

| 22.4         | 22.3.2 Releasing HALT mode                                                 |      |

| 22.4         | 22.4.1 Setting and operation status                                        |      |

|              | 22.4.1 Setting and operation status                                        |      |

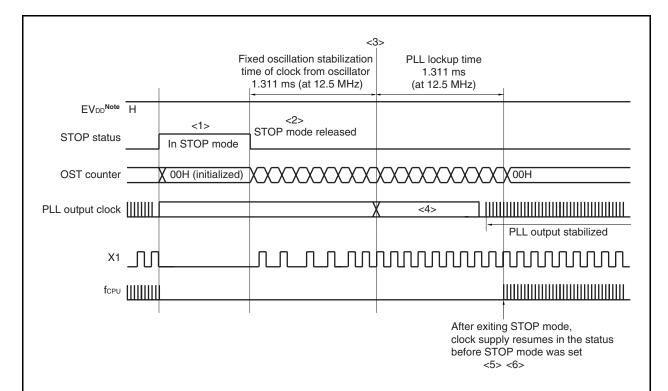

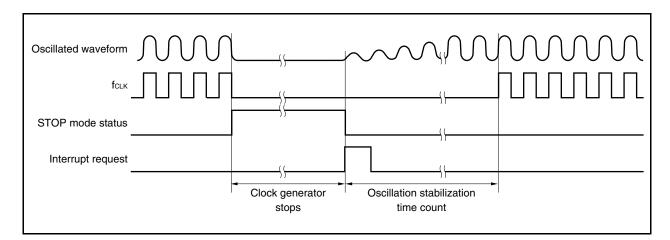

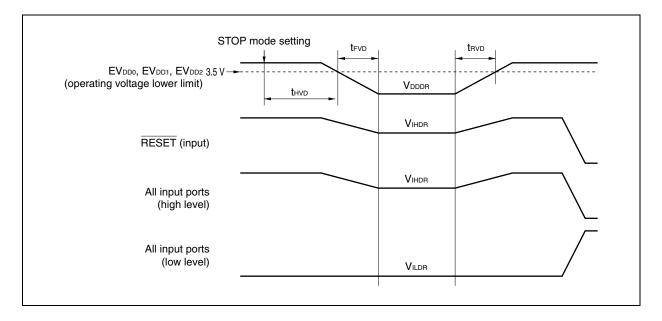

| 22.5         | STOP Mode                                                                  |      |

| 22.5         | 22.5.1 Setting and operation status                                        |      |

|              | 22.5.1 Setting and operation status                                        |      |

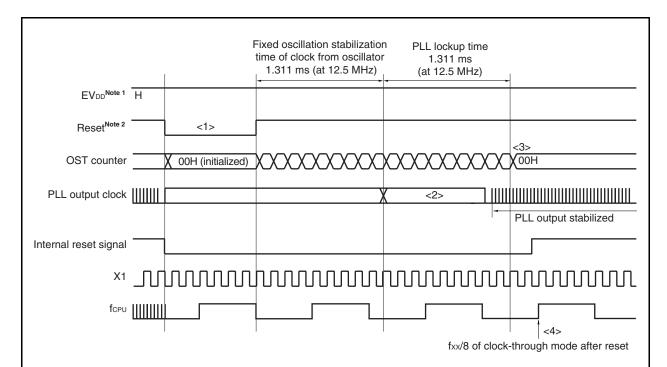

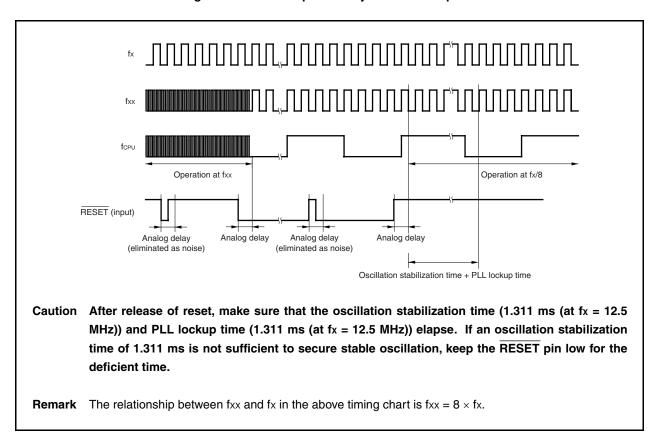

| 22.6         | Securing Oscillation Stabilization Time                                    |      |

| 22.0         | Occurring Occumentation Otabilization Time                                 | 1230 |

| CHAPTE       | R 23 RESET FUNCTIONS                                                       |      |

| 23.1         | Overview                                                                   |      |

| 23.2         | Control Register                                                           |      |

| 23.3         | Operation                                                                  | 1254 |

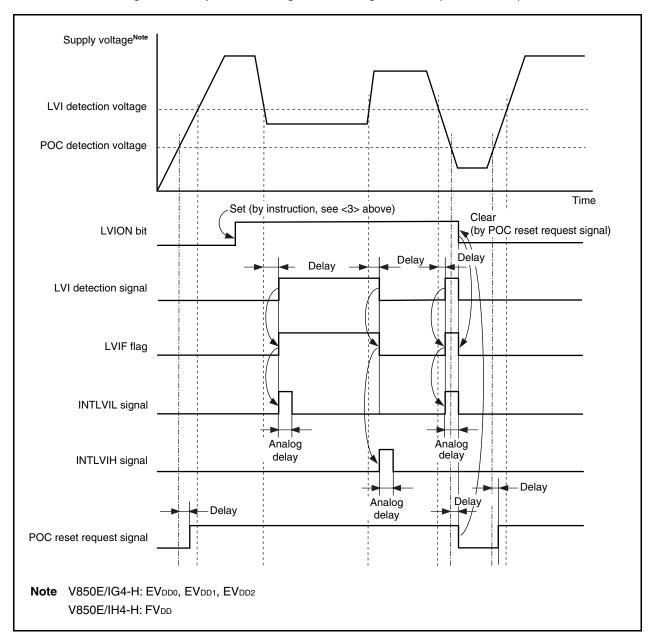

| CHAPTE       | R 24 LOW-VOLTAGE DETECTOR                                                  | 1257 |

| 24.1         |                                                                            |      |

| <b>24.</b> I | Functions                                                                  | 1257 |

| 24.3   | Control Registers                                        | 1259 |

|--------|----------------------------------------------------------|------|

| 24.4   | Operation                                                | 1261 |

|        | 24.4.1 To use for internal reset signal                  | 1261 |

|        | 24.4.2 To use for interrupt                              | 1263 |

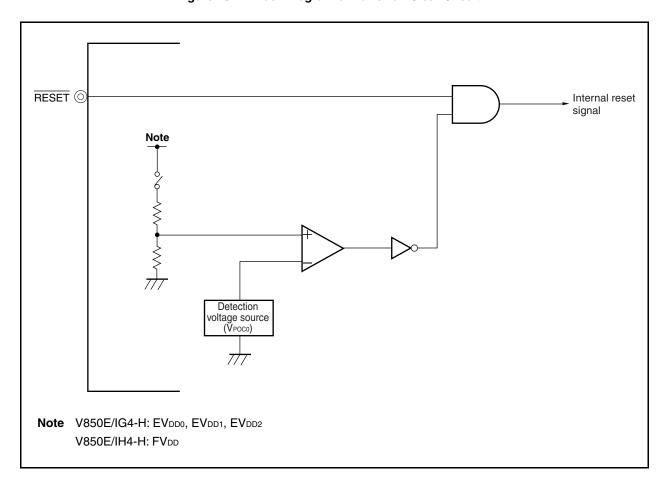

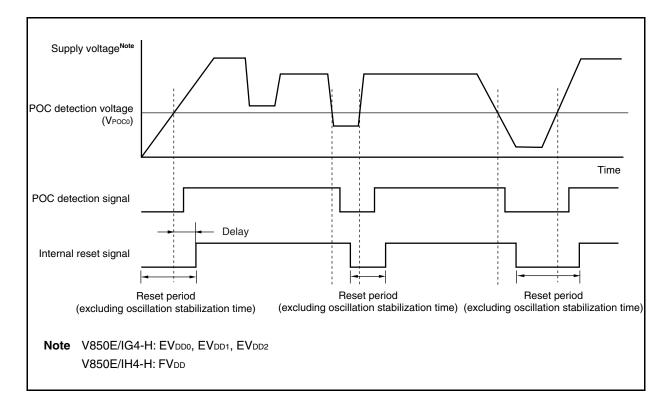

| CHAPTE | R 25 POWER-ON CLEAR CIRCUIT                              | 1264 |

| 25.1   | Function                                                 | 1264 |

| 25.2   | Configuration                                            | 1265 |

| 25.3   | Operation                                                |      |

| CHAPTE | R 26 ON-CHIP DEBUG FUNCTION                              | 1267 |

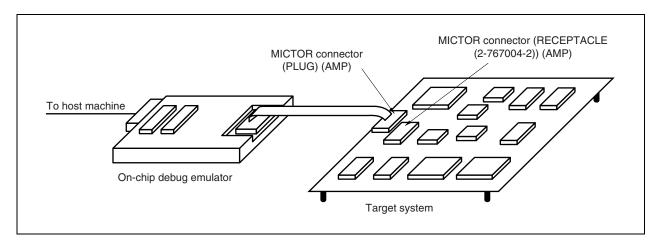

| 26.1   | Debugging Using DCU (Trace Function)                     |      |

|        | 26.1.1 Functional Outline                                |      |

|        | 26.1.2 Connection with on-chip debug emulator of partner |      |

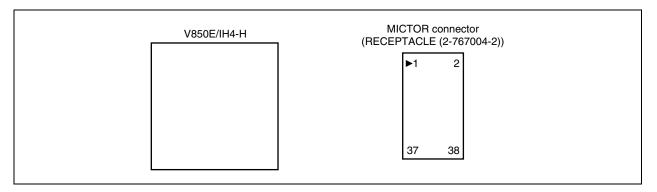

| 26.2   | Debugging Using DCU (No Trace Function)                  |      |

|        | 26.2.1 Circuit connection examples                       |      |

|        | 26.2.2 Interface signals                                 |      |

|        | 26.2.3 Maskable functions                                |      |

|        | 26.2.4 Cautions                                          |      |

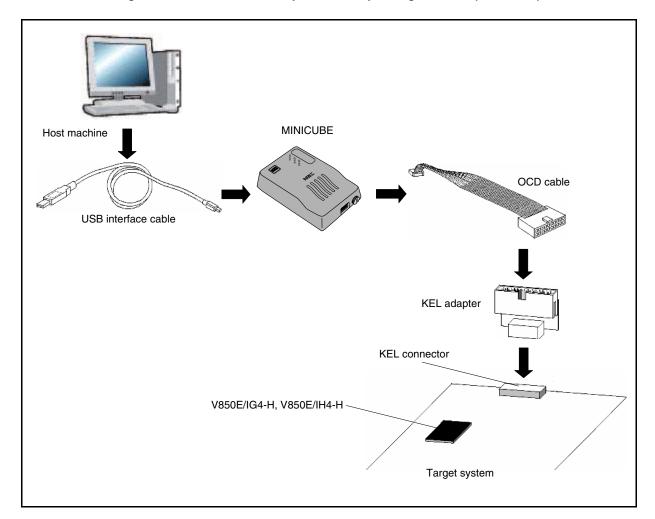

| 26.3   | Debugging Without Using DCU                              |      |

|        | 26.3.1 Circuit connection examples                       |      |

|        | 26.3.2 Maskable functions                                |      |

|        | 26.3.3 Securing of user resources                        |      |

|        | 26.3.4 Cautions                                          |      |

| 26.4   | ROM Security Function                                    |      |

|        | 26.4.1 Security ID                                       | 1291 |

|        | 26.4.2 Setting                                           | 1292 |

|        |                                                          |      |

| CHAPTE | R 27 FLASH MEMORY                                        | 1293 |

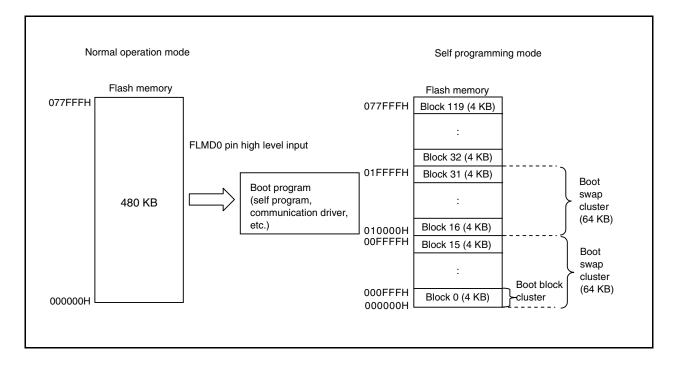

| 27.1   | Features                                                 | 1293 |

| 27.2   | Memory Configuration                                     | 1294 |

| 27.3   | Functional Overview                                      | 1295 |

|        | 27.3.1 Erase units                                       | 1297 |

|        | 27.3.2 Security function                                 | 1297 |

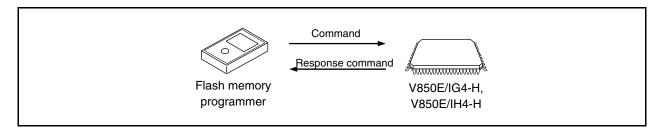

| 27.4   | Writing with Flash Memory Programmer                     | 1298 |

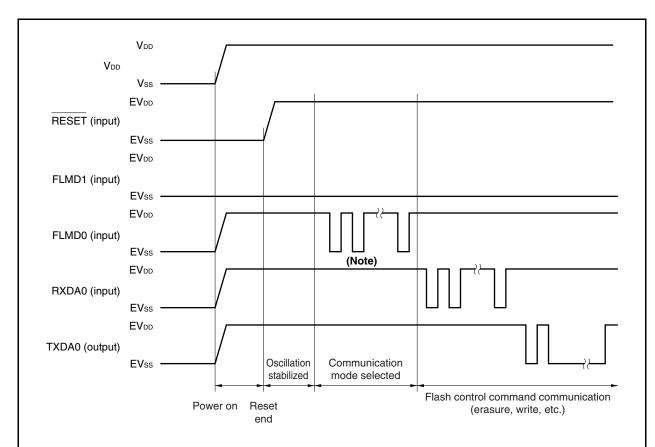

| 27.5   | Flash Memory Programming Environment                     | 1299 |

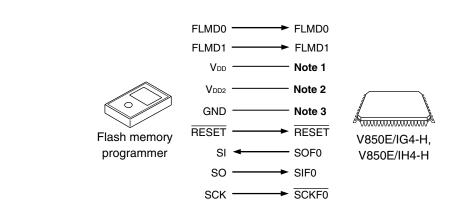

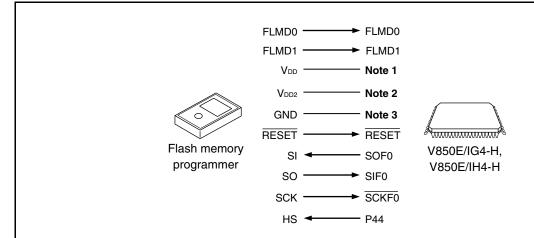

| 27.6   | Communication Method of Flash Memory Programming         | 1300 |

| 27.7   | Pin Processing During Flash Memory Programming           |      |

|        | 27.7.1 Power supply                                      | 1309 |

|        | 27.7.2 <u>Pins used</u>                                  | 1309 |

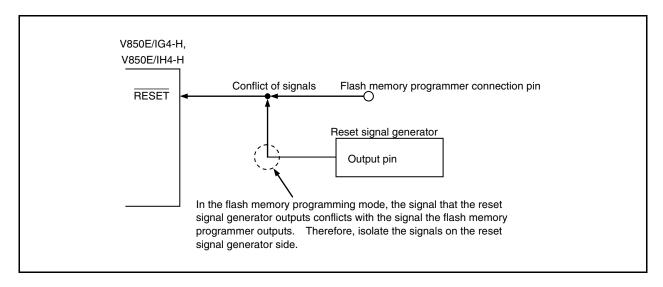

|        | 27.7.3 RESET pin                                         | 1312 |

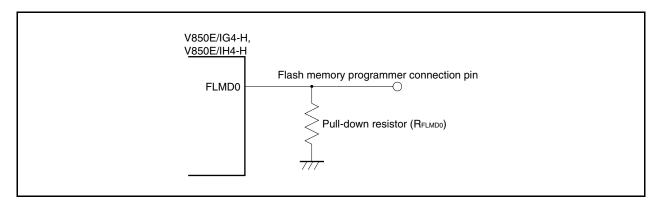

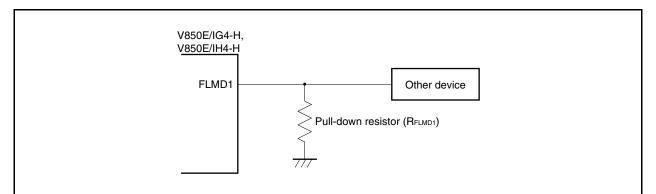

|        | 27.7.4 FLMD0 and FLMD1 pins                              | 1312 |

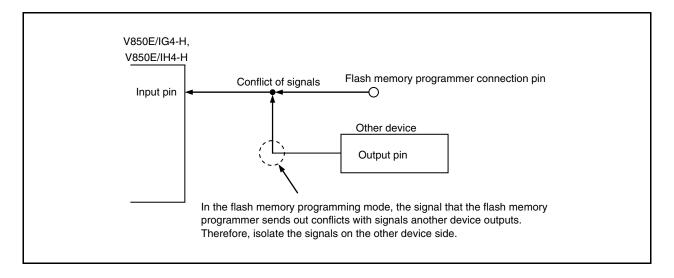

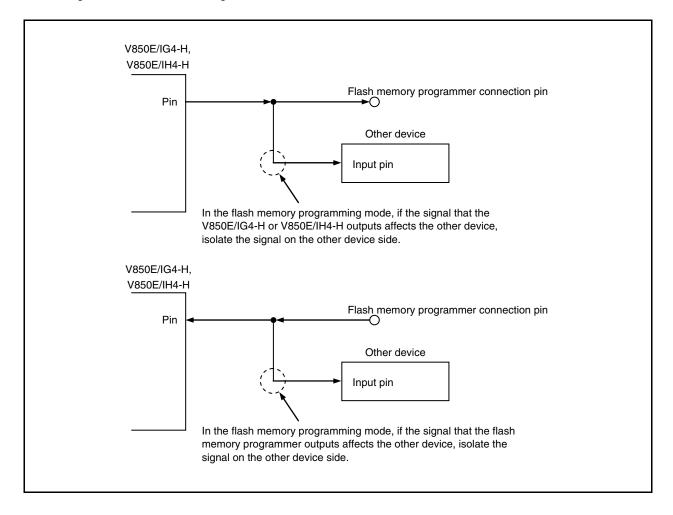

|        | 27.7.5 Port pins                                         | 1313 |

|        | 27.7.6 Other signal pins                                 |      |

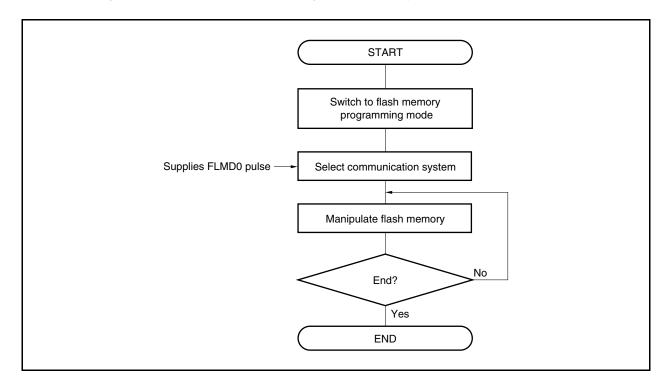

| 27.8   | Flash Memory Programming Mode                            | 1314 |

|        | 27.8.1  | Flash memory control                      | 1314 |

|--------|---------|-------------------------------------------|------|

|        | 27.8.2  | Selection of communication mode           | 1315 |

|        | 27.8.3  | Communication commands                    | 1316 |

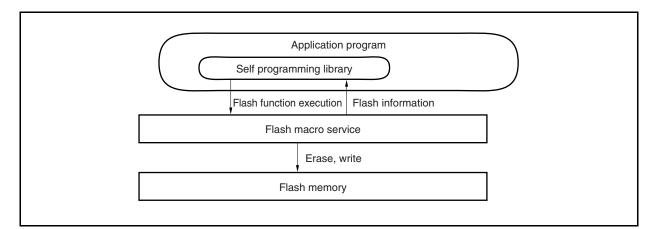

| 27.9   | Rewriti | ing by Self Programming                   | 1318 |

|        | 27.9.1  | Overview                                  | 1318 |

|        | 27.9.2  | Features                                  | 1319 |

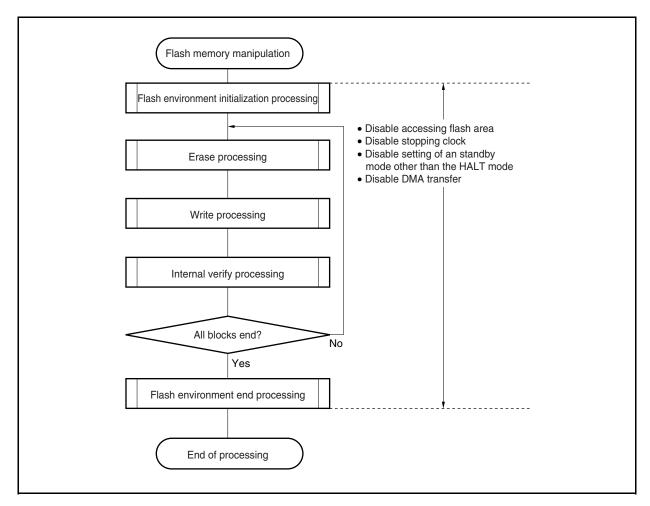

|        | 27.9.3  | Standard self programming flow            | 1320 |

|        | 27.9.4  | Flash functions                           | 1321 |

|        | 27.9.5  | Pin processing                            | 1321 |

|        | 27.9.6  | Internal resources used                   | 1322 |

|        | _       |                                           |      |

| CHAPTE | R 28 E  | LECTRICAL SPECIFICATIONS                  | 1323 |

| 28.1   | V850E/  | /IG4-H                                    | 1323 |

|        | 28.1.1  | Absolute maximum ratings                  | 1323 |

|        | 28.1.2  | Capacitance                               | 1324 |

|        | 28.1.3  | Operating conditions                      | 1324 |

|        | 28.1.4  | Clock oscillator characteristics          | 1324 |

|        | 28.1.5  | DC characteristics                        | 1325 |

|        | 28.1.6  | Data retention characteristics            | 1327 |

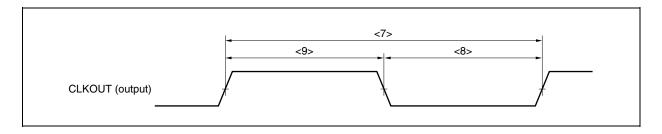

|        | 28.1.7  | AC characteristics                        | 1328 |

|        | 28.1.8  | Characteristics of A/D converters 0 and 1 | 1346 |

|        | 28.1.9  | Characteristics of A/D converter 2        | 1347 |

|        | 28.1.10 | Operational amplifier characteristics     | 1348 |

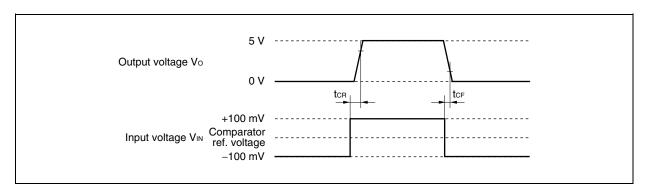

|        | 28.1.11 | Comparator characteristics                | 1349 |

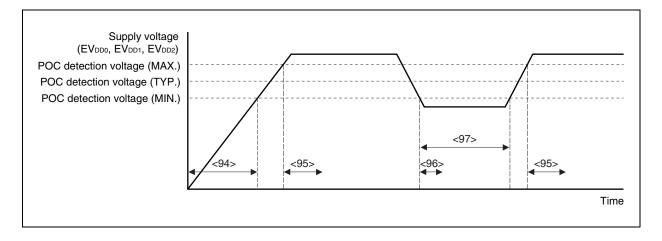

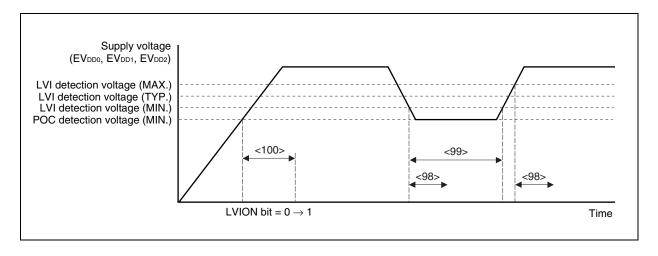

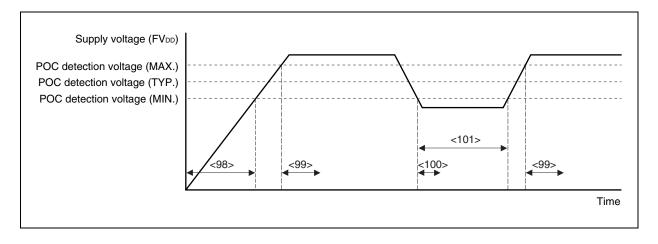

|        | 28.1.12 | Power-on-clear circuit (POC)              | 1350 |

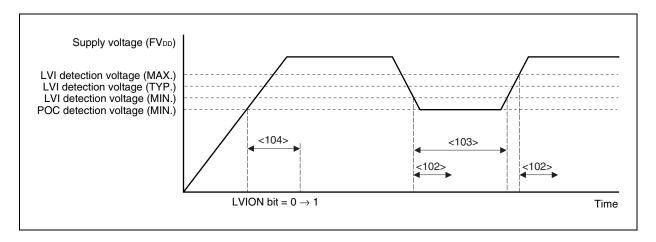

|        | 28.1.13 | Low-voltage detector (LVI)                | 1351 |

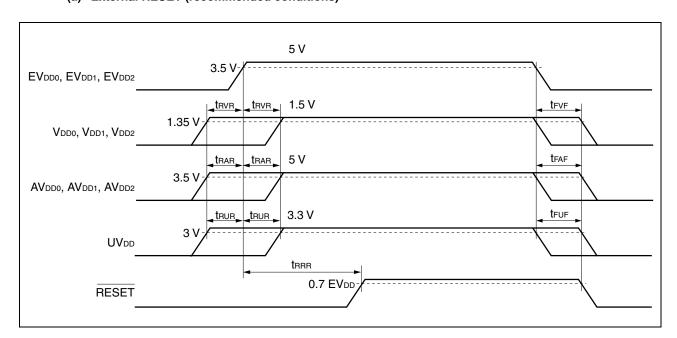

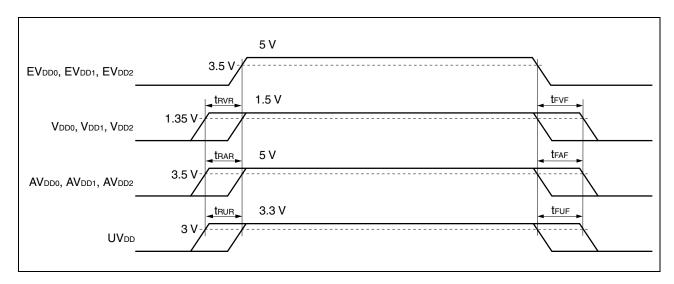

|        | 28.1.14 | Supply voltage application/cutoff timing  | 1352 |

|        | 28.1.15 | Flash memory programming characteristics  | 1354 |

| 28.2   | V850E/  | /IH4-H                                    | 1355 |

|        | 28.2.1  | Absolute maximum ratings                  | 1355 |

|        | 28.2.2  | Capacitance                               | 1356 |

|        | 28.2.3  | Operating conditions                      | 1356 |

|        | 28.2.4  | Clock oscillator characteristics          | 1356 |

|        | 28.2.5  | DC characteristics                        | 1357 |

|        | 28.2.6  | Data retention characteristics            | 1359 |

|        | 28.2.7  | AC characteristics                        | 1360 |

|        | 28.2.8  | Characteristics of A/D converters 0, 1    | 1382 |

|        | 28.2.9  | Characteristics of A/D converter 2        | 1383 |

|        | 28.2.10 | Operational amplifier characteristics     | 1384 |

|        | 28.2.11 | Comparator characteristics                | 1385 |

|        | 28.2.12 | Power-on-clear circuit (POC)              | 1386 |

|        | 28.2.13 | Low-voltage detector (LVI)                | 1387 |

|        | 28.2.14 | Supply voltage application/cutoff timing  | 1388 |

|        | 28.2.15 | Flash memory programming characteristics  | 1390 |

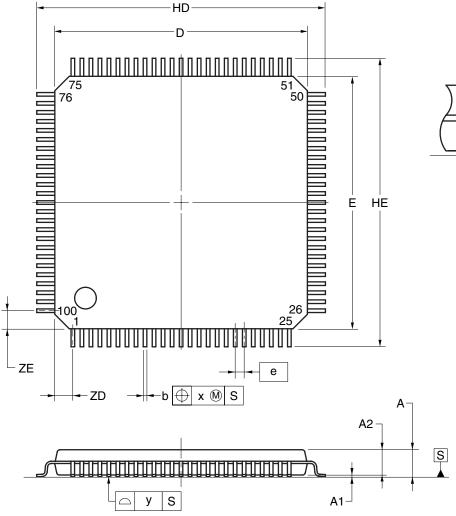

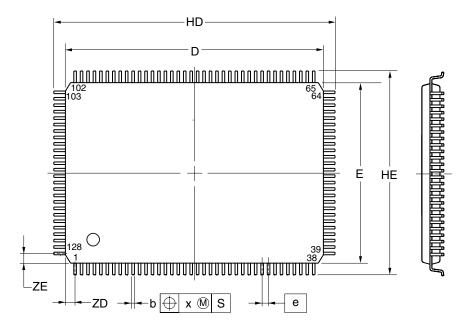

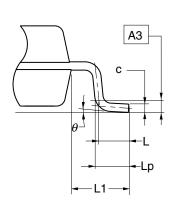

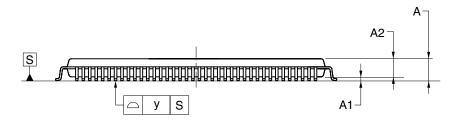

|         | СНАРТЕ | ER 29 PACKAGE DRAWINGS                                                | 1391 |

|---------|--------|-----------------------------------------------------------------------|------|

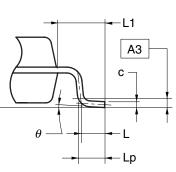

|         | СНАРТЕ | ER 30 RECOMMENDED SOLDERING CONDITIONS                                | 1393 |

|         | APPEND | DIX A CAUTIONS                                                        | 1394 |

|         | A.1    | Restriction on Conflict Between sld Instruction and Interrupt Request | 1394 |

|         |        | A.1.1 Description                                                     |      |

|         |        | A.1.2 Countermeasure                                                  | 1394 |

|         | APPEND | DIX B REGISTER INDEX                                                  | 1395 |

|         | APPEND | DIX C INSTRUCTION SET LIST                                            | 1419 |

|         | C.1    | Conventions                                                           | 1419 |

|         | C.2    | Instruction Set (in Alphabetical Order)                               | 1422 |

|         | APPEND | DIX D REVISION HISTORY                                                | 1429 |

|         | D.1    | Major Revisions in This Edition                                       |      |

| <r></r> | D.2    | Revision History of Previous Editions                                 | 1430 |

R01UH0306EJ0300 Rev.3.00 Sep 30, 2011

## **CHAPTER 1 Introduction**

The V850E/IG4-H and V850E/IH4-H are products of the Renesas Electronics V850 single-chip microcontrollers. This chapter gives an outline of the V850E/IG4-H and V850E/IH4-H.

## 1.1 Overview

The V850E/IG4-H and V850E/IH4-H are 32-bit single-chip microcontrollers that use the V850E1 CPU core and incorporate ROM/RAM and various peripheral functions such as DMA controller, timer/counter, watchdog timer, serial interfaces, USB function controller, A/D converter, and on-chip debug function.

In addition to high real-time response characteristics and 1-clock-pitch basic instructions, the V850E/IG4-H and V850E/IH4-H feature instructions such as multiply instructions realized by a hardware multiplier, saturated operation instructions, and bit manipulation instructions, as optimum instructions for digital servo control applications. Moreover, as a real-time control system, the V850E/IG4-H and V850E/IH4-H enable an extremely high costperformance for applications such as motor inverter control.

Table 1-1 lists the V850E/IG4-H and V850E/IH4-H products.

Table 1-1. V850E/IG4-H, V850E/IH4-H Product List

|             | Function   | Package | RC     | OM     | RAM Size | Operating           | Maskable | Interrupt | Non-                  |  |

|-------------|------------|---------|--------|--------|----------|---------------------|----------|-----------|-----------------------|--|

| Part Number |            | Туре    |        | Size   |          | Frequency<br>(MAX.) | External | Internal  | Maskable<br>Interrupt |  |

| V850E/IG4-H | μPD70F3919 | 100GC   | Flash  | 256 KB | 24 KB    | 100 MHz             | 22       | 83        | 1                     |  |

|             | μPD70F3920 |         | memory | 384 KB |          |                     |          |           |                       |  |

|             | μPD70F3921 |         |        | 480 KB |          |                     |          |           |                       |  |

| V850E/IH4-H | μPD70F3922 | 128GF   |        | 256 KB |          |                     |          |           |                       |  |

|             | μPD70F3923 |         |        | 384 KB |          |                     |          |           |                       |  |

|             | μPD70F3924 |         |        | 480 KB |          |                     |          |           |                       |  |

Remark 100GC (V850E/IG4-H): 100-pin plastic LQFP (fine pitch) (14 × 14)

128GF (V850E/IH4-H): 128-pin plastic LQFP (fine pitch) (14  $\times$  20) Table 1-2 shows the differences in functions between the V850E/IG4-H and V850E/IH4-H.

Table 1-2. Differences in Functions Between V850E/IG4-H and V850E/IH4-H

| Item                    | Separate bus mode                         | V850E/IG4-H                                                                                  | V850E/IH4-H                                                                                |

|-------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Port function           | I/O                                       | 51                                                                                           | 68                                                                                         |

|                         | Input                                     | 12                                                                                           | 12                                                                                         |

|                         | On-chip pull-up resistor                  | 51                                                                                           | 68                                                                                         |

| External bus function   | Separate bus mode                         | None                                                                                         | Provided                                                                                   |

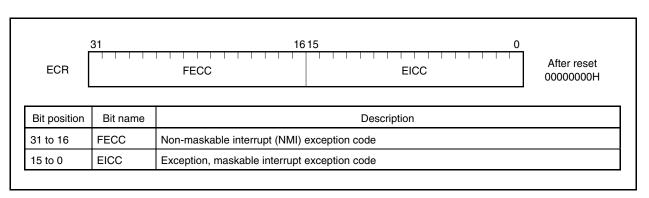

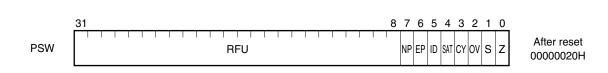

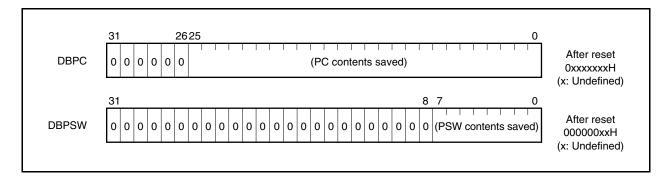

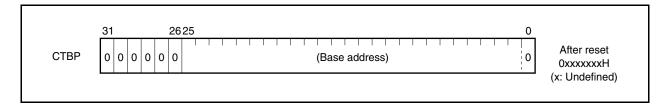

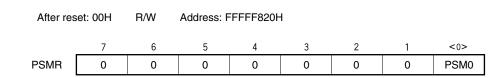

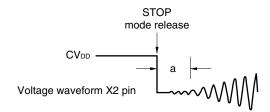

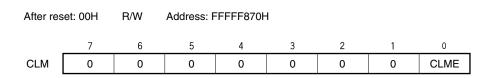

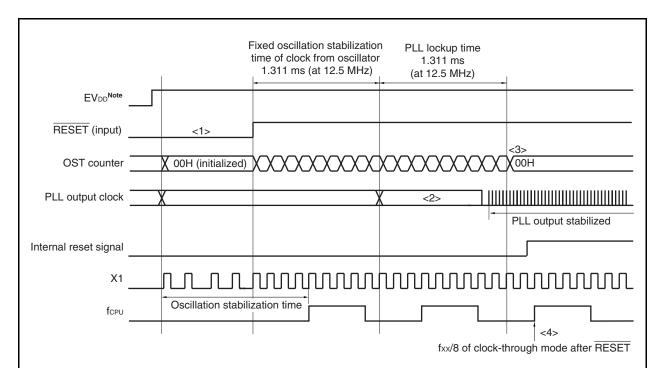

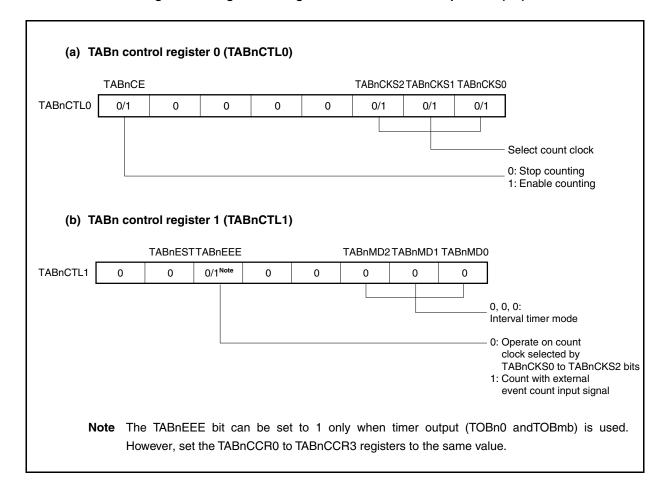

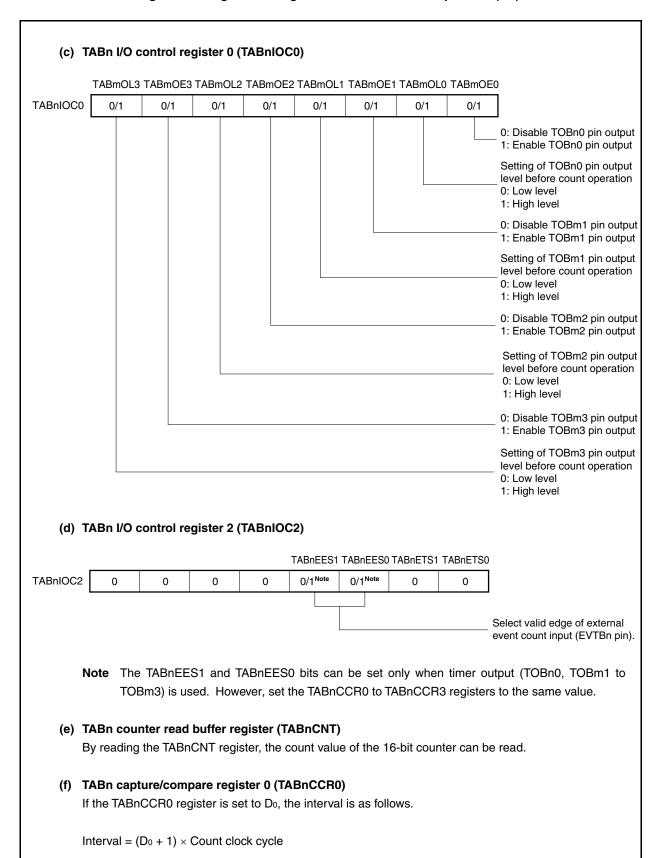

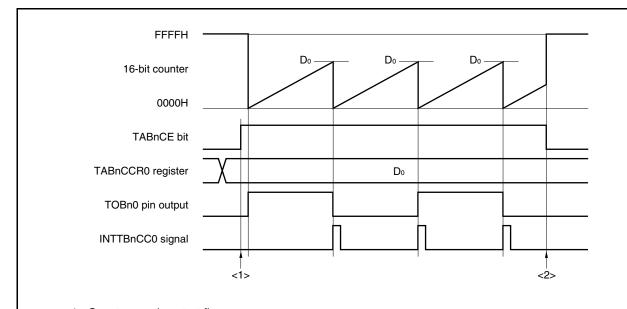

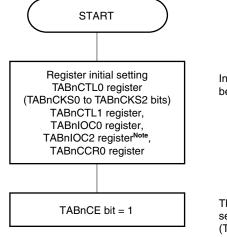

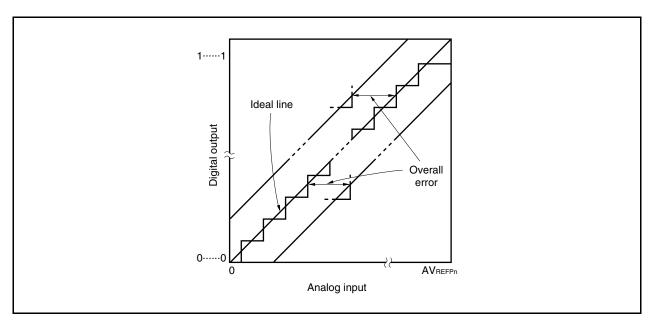

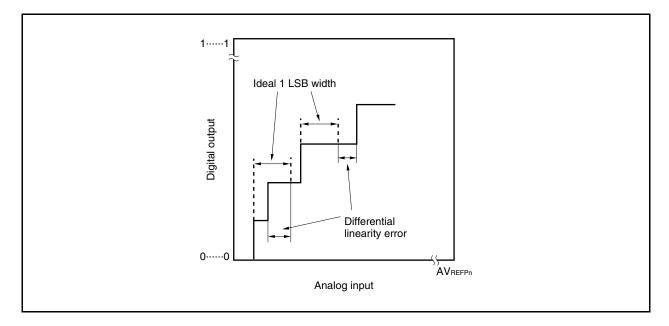

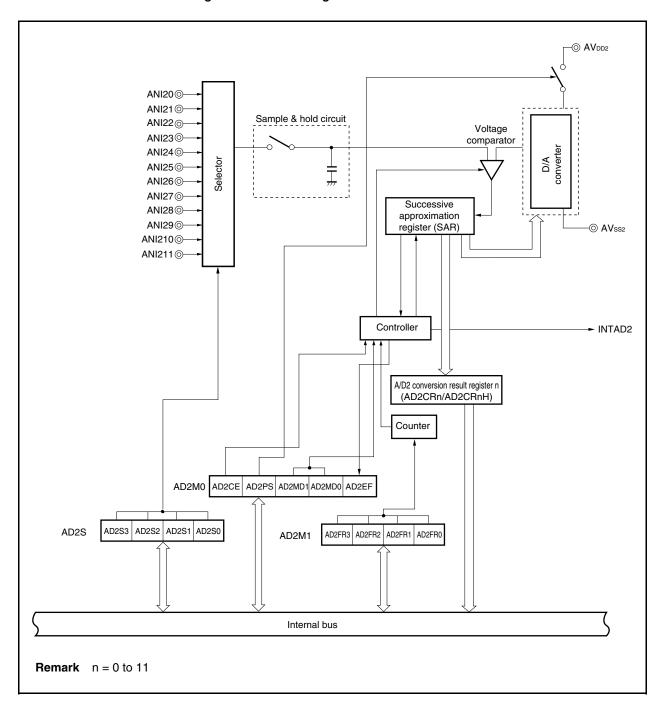

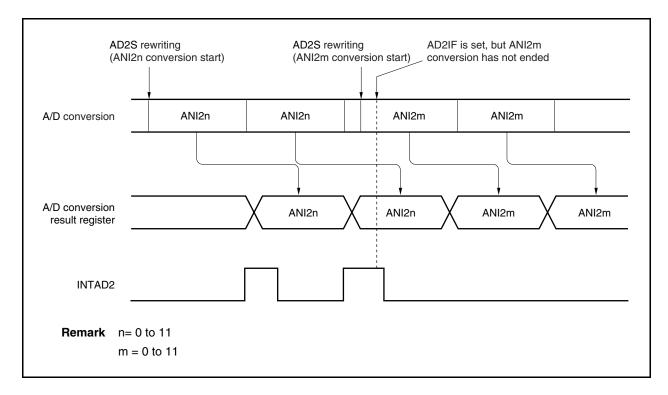

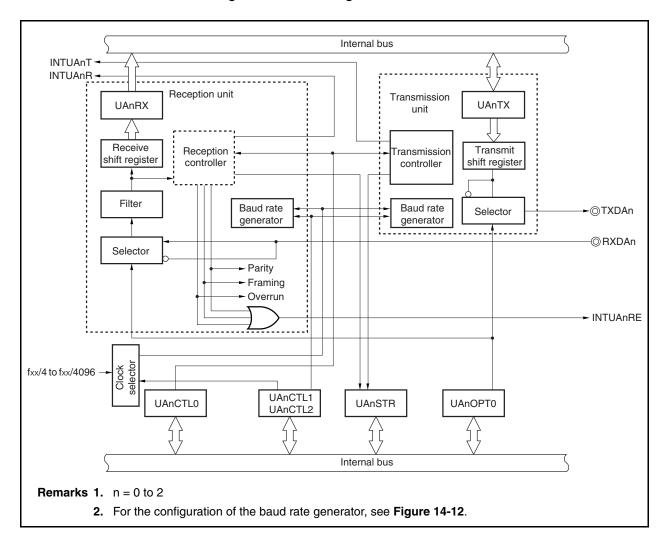

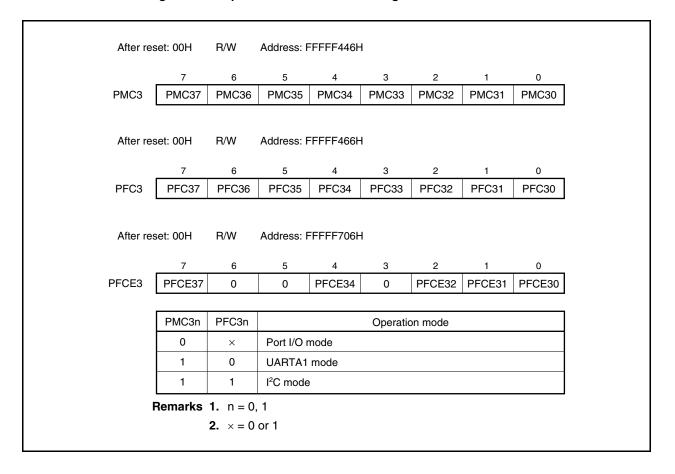

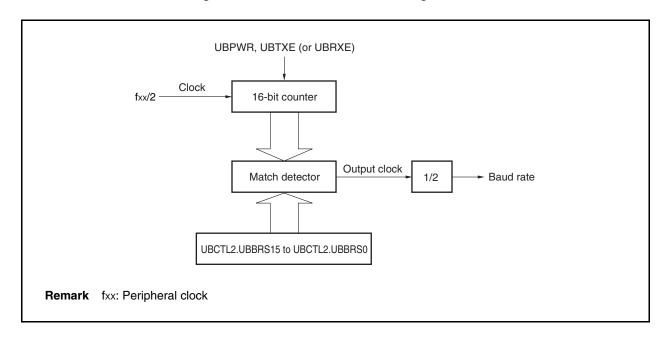

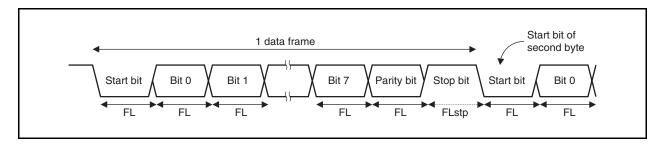

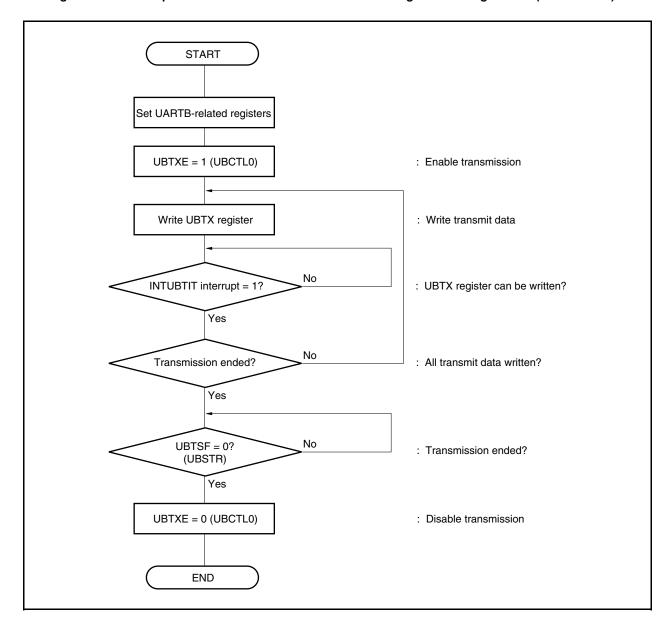

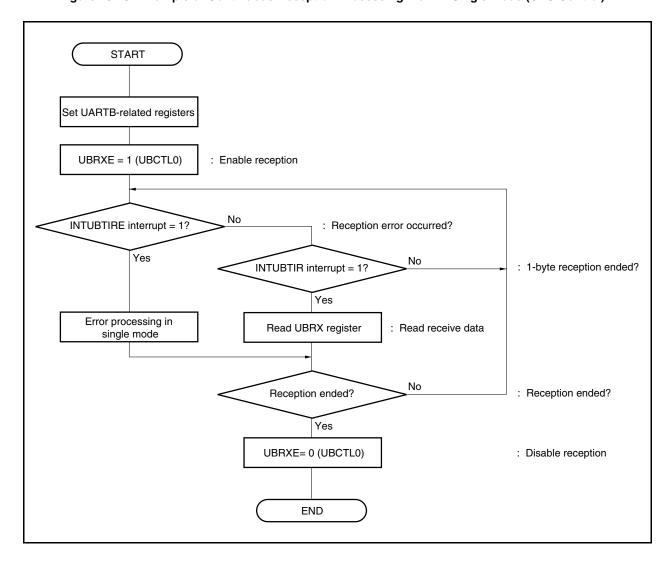

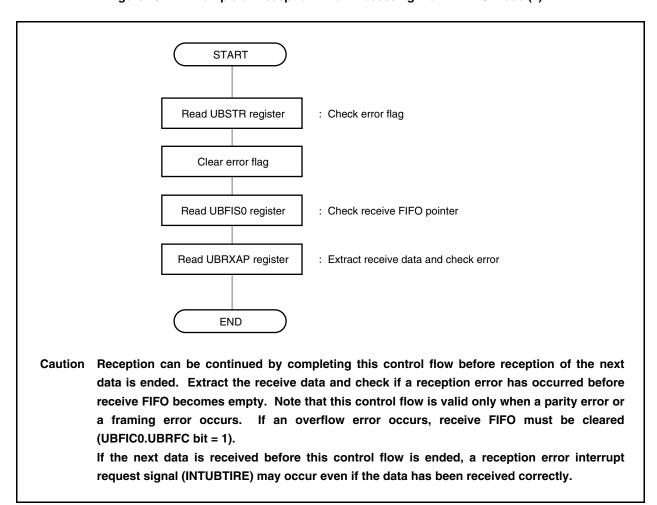

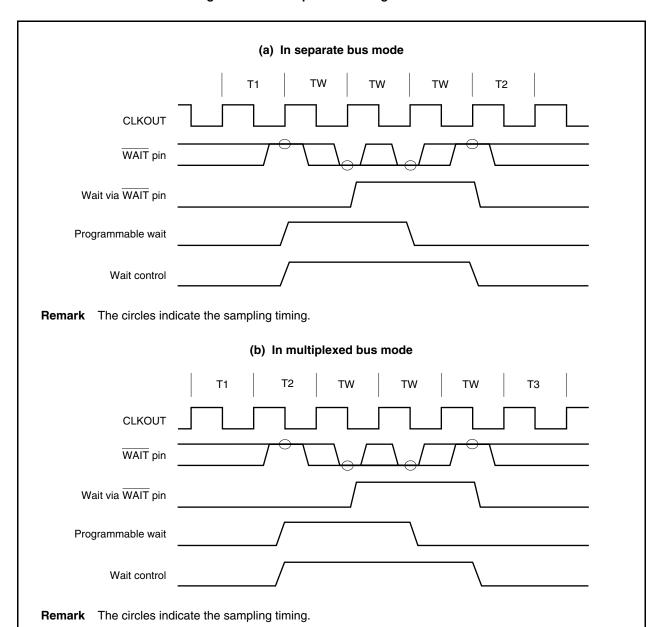

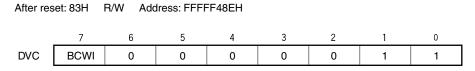

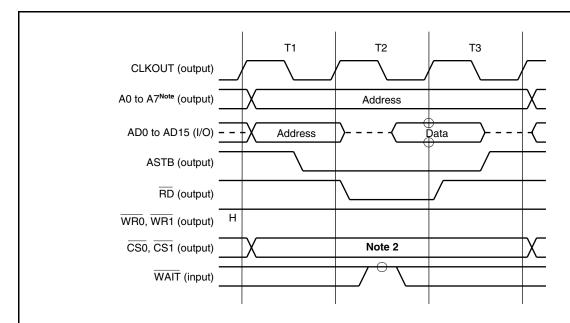

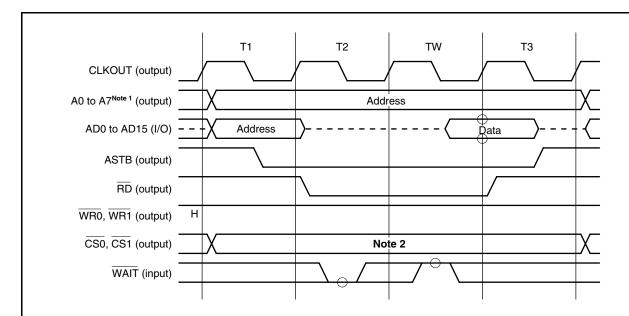

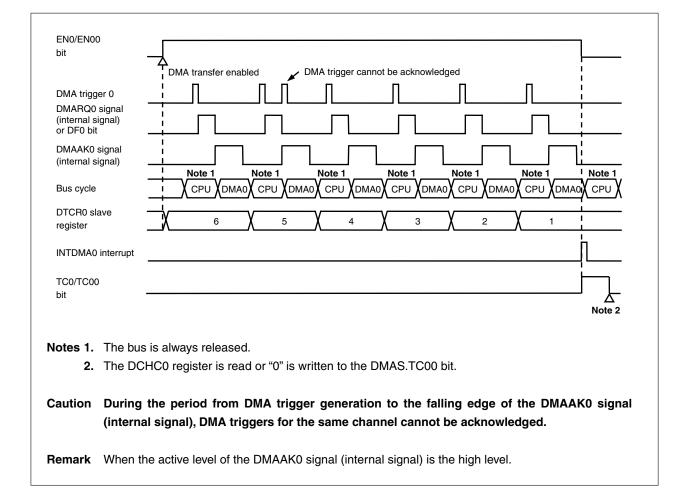

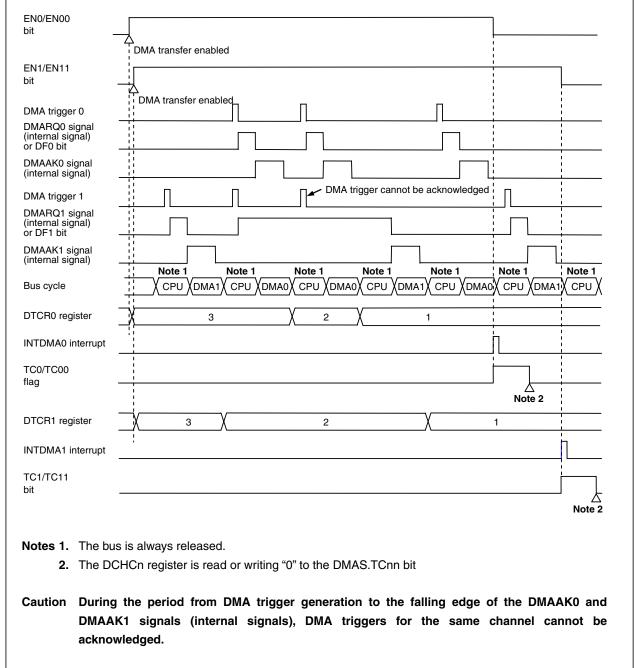

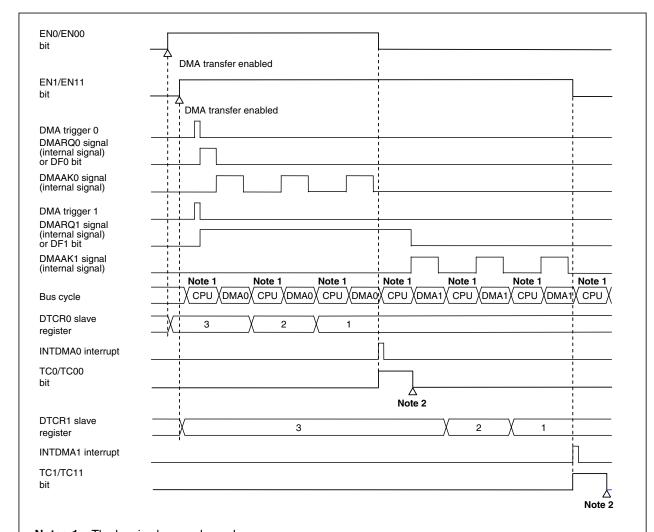

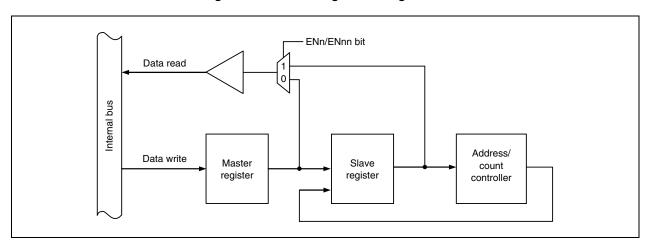

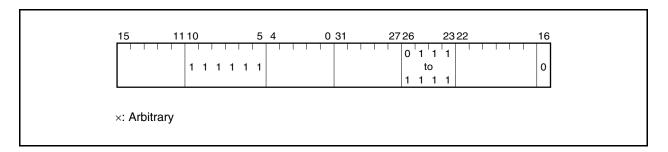

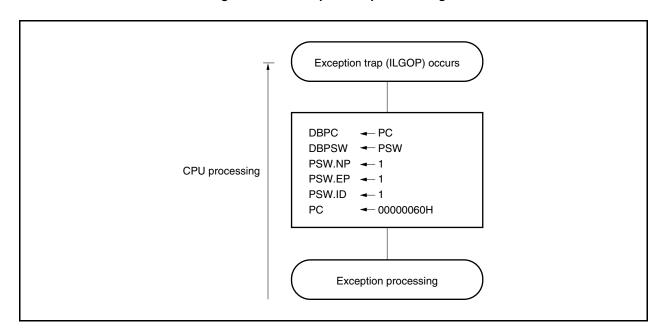

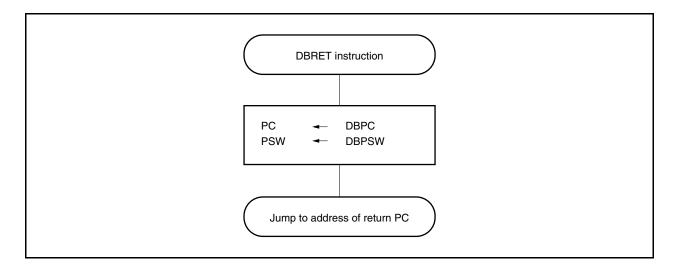

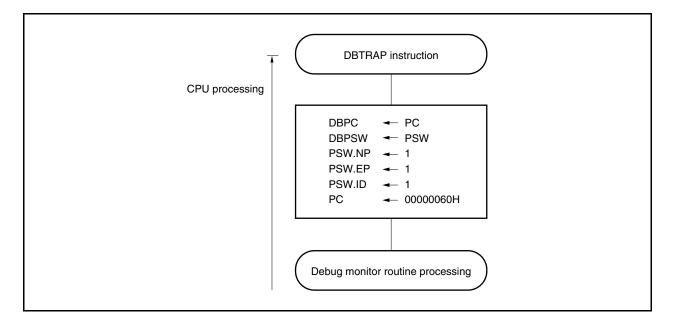

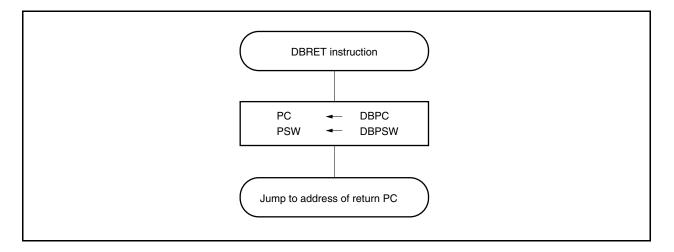

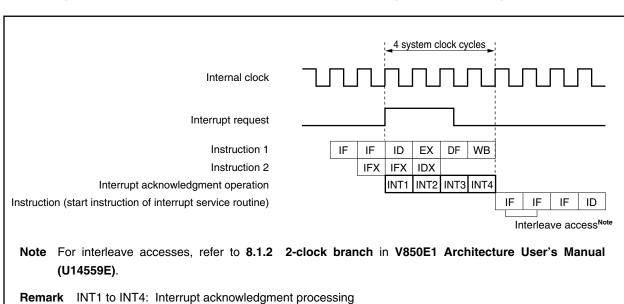

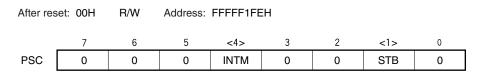

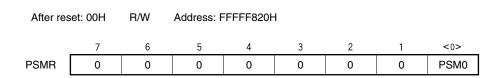

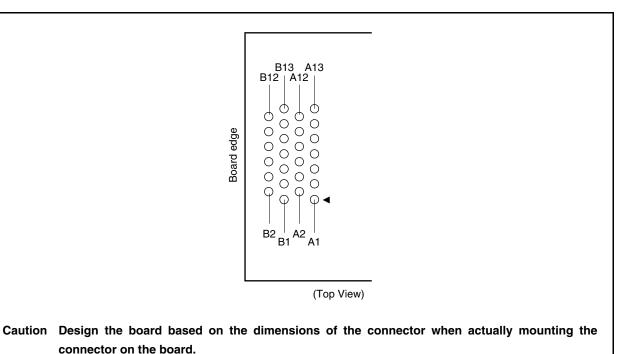

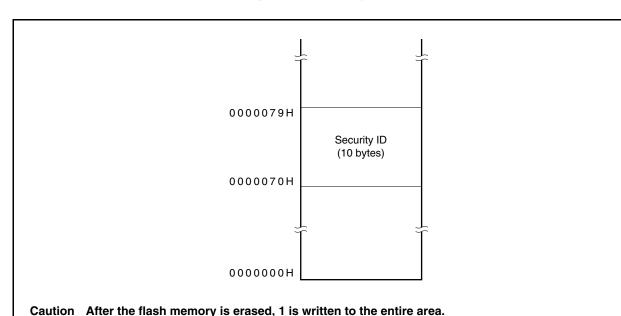

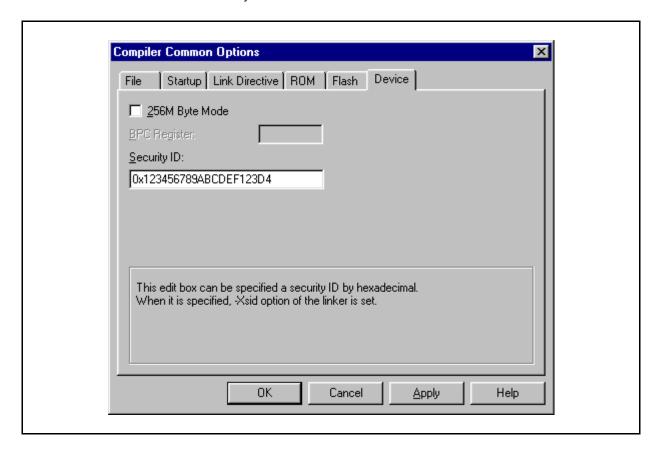

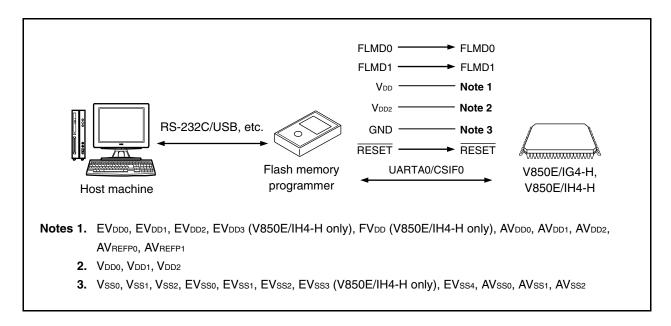

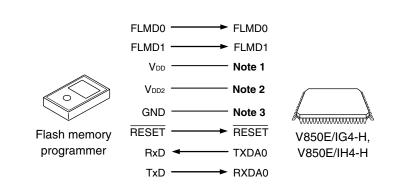

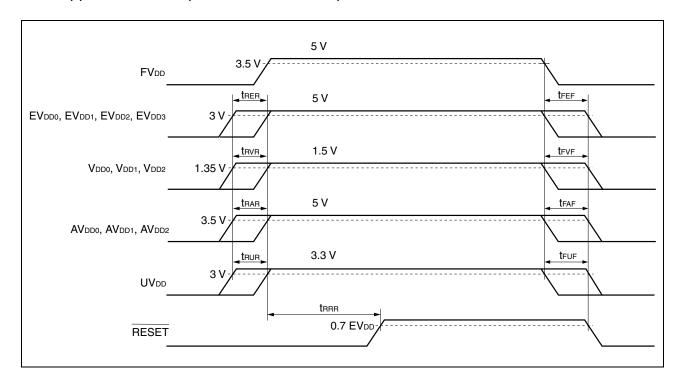

| Timer AB0, timer<br>AB1 | Input pin                                 | TIB00 to TIB03                                                                               | TIB00 to TIB03<br>TIB10 to TIB13                                                           |