# Ultra Low-Power Cryptographic Controller with ChipDNA<sup>TM</sup> for Embedded Devices

#### **General Description**

The MAXQ1065 is a security coprocessor that provides turnkey cryptographic functions for root-of-trust, mutual authentication, data confidentiality and integrity, secure boot, secure firmware update, and secure communications with generic key exchange and bulk encryption or complete TLS support. The device integrates 8KB of secure storage for user data, keys, certificates, and counters with user-defined access control and life cycle management. It also has a configurable output pin and a tamper input pin. Commands are accessible through a standard SPI interface.

The MAXQ1065's low power consumption makes it suitable for battery-powered applications, and the extremely reduced footprint and pin count allow easy integration into medical and wearable devices. Its lifetime and operating range make it compatible with long-term deployments in harsh environments. The MAXQ1065 life cycle management allows flexible access control rules during the major life cycle stages of the device. Secure key loading protocol and secure factory preprogramming are available.

DeepCover® embedded security solutions cloak sensitive data under multiple layers of advanced security to provide the most secure key storage possible. To protect against device-level security attacks, invasive and noninvasive countermeasures are implemented including active die shield, encrypted storage of keys using the ChipDNA PUF technology, and externally callable algorithmic subroutines.

### **Applications**

The MAXQ1065 enhances the security of connected embedded systems in applications such as industrial IoT, SCADA, medical equipment, building and home automation, smart city, smart metering. It is a key element for the cybersecurity of infrastructures and connected device network nodes, routers, and gateways. It is ideally suited for:

- Secure Communication: Key Exchange, TLS

- Secure Data Storage

- Mutual Authentication

- Certificate Management

- Anti-cloning, Anti-counterfeiting, Feature and Usage Control

- System-Level Tamper Protection and Integrity

- Secure Boot, Secure Firmware Update

#### **Benefits and Features**

- ECC Compute Engine Using Curve NIST P-256

- FIPS-186 ECDSA

- NIST SP800-56Ar3 Key Exchange with Static Unified Model, C(0e, 2s, ECC CDH) with One-Step Key Derivation Using SHA-256

- On-Board EC Key Generation with SP800-90B/A

- SHA-2 Compute Engine

- NIST FIPS-180-4 SHA2-256, HMAC-SHA-256

- AES Compute Engine with 128 and 256 Key Sizes

- ECB, CBC, CCM, GCM Cipher Modes

- CBC-MAC, CMAC Message Authentication Codes

- Onboard AES Key Generation with SP800-90A/B

- True Random Number Generator (TRNG)

- NIST SP800-90A/C Compliant

- NIST SP800-90B Entropy Source

- Secure Communication

- TLS/DTLS 1.2 Handshake and Record Layer

- ECDSA Authentication

- ECDHE Key Exchange

- AES-GCM or CCM Record Layer

- SP800-56Ar3-Based Key Exchange

- X.509 v3 Certificate Support

- · Storage of Root and Device Certificates

- · Onboard Verification of Chains of Certificates

- ECDSA Verification on Supported Curves

- High-Speed Interface for Host Microcontroller Communication

- 10MHz SPI with Mode 0 or Mode 3 Operation

- 8KB User Flash Array with ChipDNA PUF Encryption

- Unique, Unalterable Factory-Programmed ID Number

- Tamper Input Detects System-Level Intrusion

- Secure Factory Provisioning Service

- 12-Pin, 3mm x 3mm TDFN Package

- -40°C to +105°C, 1.62V to 3.63V

- Low-Power Operation: 100nA (typ) in Standby

Request MAXQ1065 Security User Guide

Ordering Information appears at end of data sheet.

ChipDNA is a trademark of Maxim Integrated Products, Inc.

DeepCover is a registered trademark of Maxim Integrated Products, Inc.

# **Functional Diagrams**

### **Absolute Maximum Ratings**

| (All voltages with respect to GNI | ), unless otherwise noted.)      |

|-----------------------------------|----------------------------------|

| V <sub>DD</sub> to GND            | 0.3V to 3.63V                    |

| Any Pin to GND except VDD         | 0.3V to (V <sub>DD</sub> + 0.3)V |

| Operating Temperature Range       | 40°C to +105°C                   |

| Storage Temperature Range         | 40°C to +150°C                   |

| Junction Temperature              | +150°C                           |

| Soldering Temperature (reflow)    | +260°C                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **12 TDFN**

| TD1233+1C                             |  |  |  |

|---------------------------------------|--|--|--|

| <u>21-0664</u>                        |  |  |  |

| 90-0397                               |  |  |  |

|                                       |  |  |  |

| 63°C/W                                |  |  |  |

| 8.5°C/W                               |  |  |  |

| Thermal Resistance, Four-Layer Board: |  |  |  |

| 41°C/W                                |  |  |  |

| 8.5°C/W                               |  |  |  |

|                                       |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                            | SYMBOL             | CONDITIONS                                                                    | MIN                      | TYP  | MAX                      | UNITS |

|------------------------------------------------------|--------------------|-------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| POWER SUPPLY                                         |                    |                                                                               | •                        |      |                          |       |

| Supply Voltage                                       | $V_{DD}$           | ( <u>Note 1</u> )                                                             | 1.62                     | 3.3  | 3.63                     | V     |

| Max Total Current,<br>Active Mode                    | I <sub>A</sub>     | T <sub>A</sub> = +25°C                                                        |                          | 1.28 | 3                        | mA    |

| Idle Current                                         | I <sub>IDLE</sub>  | T <sub>A</sub> = +25°C                                                        |                          | 0.4  |                          | mA    |

| V <sub>DD</sub> Low-Power Mode<br>Current            | I <sub>PDWN</sub>  | $T_A = +25^{\circ}C$ , $V_{PDWN} = 0V$ , $V_{DD} = 1.8V$<br>( <u>Note 2</u> ) |                          | 100  |                          | nA    |

| Input Low Voltage for All Inputs                     | V <sub>IL_IO</sub> |                                                                               |                          |      | 0.3 x<br>V <sub>DD</sub> | V     |

| Input High Voltage for<br>All Inputs Except<br>POWER | V <sub>IH_IO</sub> |                                                                               | 0.7 x<br>V <sub>DD</sub> |      |                          | V     |

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +105°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                                     | SYMBOL             | CONDITIONS                                       | MIN                      | TYP                 | MAX                      | UNITS   |

|---------------------------------------------------------------|--------------------|--------------------------------------------------|--------------------------|---------------------|--------------------------|---------|

| Output Low Voltage for All Outputs                            | V <sub>OL_IO</sub> | I <sub>SINK</sub> = 2mA                          |                          | 0.2                 | 0.4                      | V       |

| Output High Voltage for All Outputs                           | V <sub>OH_IO</sub> | I <sub>SOURCE</sub> = 2mA                        | V <sub>DD</sub> - 0.4    |                     |                          | V       |

| Input Pullup Resistor for<br>All Inputs in Pullup<br>Mode     | R <sub>PU</sub>    |                                                  |                          | 22                  |                          | kΩ      |

| Input Pulldown Resistor<br>for All Inputs in Pulldown<br>Mode | R <sub>PD</sub>    |                                                  |                          | 22                  |                          | kΩ      |

| NONVOLATILE MEMORY                                            | <b>(</b>           |                                                  | ·                        |                     |                          |         |

| Flash Erase Time                                              | tp_erase           | Page erase                                       |                          | 10                  |                          | ms      |

| Flash Programming<br>Time per Word                            | t <sub>PROG</sub>  |                                                  |                          | 8                   |                          | μs      |

| Flash Endurance                                               | N <sub>END</sub>   |                                                  | 10                       |                     |                          | kcycles |

| Data Retention                                                | t <sub>RET</sub>   | T <sub>A</sub> = +125°C                          | 10                       |                     |                          | years   |

| FUNCTIONAL TIMING                                             |                    |                                                  |                          |                     |                          |         |

| Operation Time                                                | t <sub>OP</sub>    |                                                  |                          |                     | 1                        | ms      |

| Wake-Up Time                                                  | twakeup            |                                                  |                          |                     | 120                      | ms      |

| DIGITAL I/O: GENERAL                                          |                    |                                                  | ·                        |                     |                          |         |

| Output Voltage High (SPIS_MISO)                               | V <sub>OH</sub>    | I <sub>SOURCE</sub> = 2mA                        | V <sub>DD</sub> - 0.4    |                     |                          | V       |

| Output Voltage Low (SPIS_MISO)                                | V <sub>OL</sub>    | I <sub>SINK</sub> = 2mA                          |                          |                     | 0.4                      | V       |

| Input Voltage High<br>(SPIS_SCK, SPIS_SS,<br>SPIS_MOSI)       | V <sub>IH</sub>    |                                                  | 0.7 x<br>V <sub>DD</sub> |                     |                          | V       |

| Input Voltage Low<br>(SPIS_SCK, SPIS_SS,<br>SPIS_MOSI)        | $V_{IL}$           |                                                  |                          |                     | 0.3 x<br>V <sub>DD</sub> | V       |

| Input Leakage Current<br>Low                                  | I <sub>IL</sub>    | V <sub>DD</sub> = 3.63V, V <sub>IN</sub> = 0V    | -500                     |                     | +500                     | nA      |

| Input Leakage Current<br>High                                 | l <sub>IH</sub>    | V <sub>DD</sub> = 3.63V, V <sub>IN</sub> = 3.63V | -500                     |                     | +500                     | nA      |

| SPI SLAVE                                                     |                    |                                                  |                          |                     |                          | •       |

| Operating Frequency                                           | f <sub>SCK</sub>   |                                                  |                          |                     | 10                       | MHz     |

| Clock Period                                                  | t <sub>SCK</sub>   |                                                  |                          | 1/f <sub>SCK</sub>  |                          | μs      |

| Clock Input High Time                                         | tsch               | ( <u>Note 3</u> )                                |                          | t <sub>SCK</sub> /2 |                          | μs      |

| Clock Input Low Time                                          | t <sub>SCL</sub>   | ( <u>Note 3</u> )                                |                          | t <sub>SCK</sub> /2 |                          | μs      |

| SS Active Setup Time                                          | t <sub>SSE</sub>   |                                                  |                          | 10                  |                          | ns      |

| Data Input Setup Time                                         | tsis               |                                                  |                          | 5                   |                          | ns      |

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A = +25$ °C and  $T_A = +105$ °C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                          | SYMBOL           | CONDITIONS | MIN | TYP                | MAX | UNITS |

|------------------------------------|------------------|------------|-----|--------------------|-----|-------|

| Data Input Hold Time               | t <sub>SIH</sub> |            |     | 1                  |     | ns    |

| Clock Edge to Data<br>Output Valid | tsov             |            |     | 5                  |     | ns    |

| SS Inactive Setup Time             | t <sub>SSD</sub> |            |     | 10                 |     | ns    |

| SS Inactive Time                   | tssh             |            |     | 1/f <sub>SCK</sub> |     | μs    |

| Output Disable Time                | t <sub>SLH</sub> |            |     | 10                 |     | ns    |

| Clock Stable to SS<br>Active       | t <sub>SAD</sub> |            |     | 10                 |     | ns    |

Note 1: System requirement.

Note 2: Refer to Maxim <u>Application Note 7466: Hardware Requirements for Lowest Power Consumption in Power-Down Mode for the MAXQ1065</u> for ultra-low-power hardware requirements.

**Note 3:**  $t_{SCH} + t_{SCL} \ge 1/f_{SCK}$  (max)

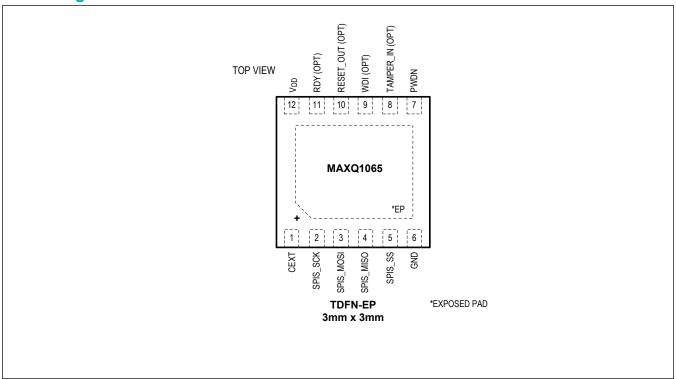

## **Pin Configuration**

## **Pin Description**

| PIN       | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER     |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1         | CEXT            | External Capacitor. Connect to ground through a 1µF external ceramic chip capacitor. Place the capacitor as close as possible to the CEXT pin. No other components should be connected to the CEXT pin.                                                                                                                                                                                                                           |

| 6         | GND             | Digital Ground. Connect directly to the ground plane.                                                                                                                                                                                                                                                                                                                                                                             |

| 7         | PDWN            | Power Down. Controls the power state of the MAXQ1065. Setting this pin to GND places the MAXQ1065 into power-down mode. In power-down mode, all volatile/ephemeral registers and data are erased. Set this pin high prior to communicating with the device. This pin should remain in a high state for the duration of any cryptography computations and as long as any ephemeral data/keys are required by the host application. |

| 12        | V <sub>DD</sub> | Supply Voltage. Connect to the external power supply for the MAXQ1065. Bypass to ground with 4.7µF and 0.1µF capacitors in parallel as close as possible to the V <sub>DD</sub> pin.                                                                                                                                                                                                                                              |

| _         | EP              | Exposed Pad. Solder evenly to the board's ground plane for proper operation. Refer to Maxim<br><u>Application Note 3273: Exposed Pads: A Brief Introduction</u> for additional information.                                                                                                                                                                                                                                       |

| SPI SLAVE |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2         | SPIS_SCK        | Slave Clock (SCK). The SPI clock input from an external SPI master controller.                                                                                                                                                                                                                                                                                                                                                    |

| 3         | SPIS_MOSI       | Master Out Slave In (MOSI). This is the SPI data input line from the SPI master.                                                                                                                                                                                                                                                                                                                                                  |

| 4         | SPIS_MISO       | Master In Slave Out (MISO). This is the SPI data output line for data going from the MAXQ1065 to an external SPI master.                                                                                                                                                                                                                                                                                                          |

## **Pin Description (continued)**

| PIN     | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | SPIS_SS   | Slave Select (SS). An input from a SPI master to select the MAXQ1065 for communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CONTROL |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |           | Tamper Detect Input (Optional Use). Defaults to an active-low input with strong pullup to V <sub>DD</sub> . Externally driving this pin low (0) triggers an optional tamper response. The tamper response is user configurable; for example, zeroization of the secret keys. If tamper detection is required, connect this pin to an external tamper sensor such as a switch triggered by unauthorized opening of the system enclosure.                                                                                                                                                                                                                                                             |

| 8       | TAMPER_IN | The tamper response is only detected if the MAXQ1065 is powered on, the PDWN pin is not asserted, and the part is in valid operating conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |           | When enabled, a tamper response is triggered if the tamper pin is driven low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |           | When not enabled, the pin can be left unconnected. TAMPER_IN is disabled by default.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10      | RESET_OUT | Reset Output (Optional Use). The output level is either asserted or pulsed when selected events occur (refer to the <i>MAXQ1065 User Guide</i> ).  The pin can output a user-configurable pulse to reset another microcontroller when the function is enabled. When not enabled (default), the RESET_OUT can be left unconnected (since it has a pullup). When enabled, the RESET_OUT is configured as an open-drain input at all times. However, when an event triggers the RESET_OUT, the RESET_OUT pin is driven low or high by the MAXQ1065, depending on the configuration, for a duration that can also be configured through a command. Then, it is released and returns to open-drain mode. |

| 9       | WDI       | Watchdog Input (Optional Use). When the watchdog function is enabled, the MAXQ1065 monitors this pin. Watchdog is disabled by default. This pin can be left unconnected when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11      | RDY       | Ready Output (Optional Use). The pin is set to a low level (0) when the MAXQ1065 is not ready to receive a new command, or is not ready to answer to the last command (the command is being processed).  This pin is asserted by the MAXQ1065 (high level: 1):  After boot when the MAXQ1065 is ready to receive a new command,  Or after the reception of a command when the processing is finished, and the response can be read by the host.                                                                                                                                                                                                                                                     |

|         |           | This pin can be left unconnected when not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

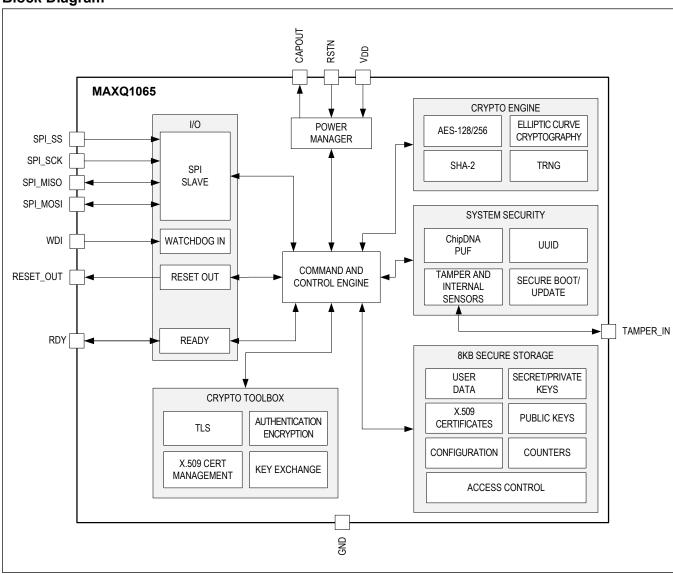

## **Functional Diagram**

#### **Block Diagram**

### **Detailed Description**

The MAXQ1065 is a proven and efficient hardware root of trust for embedded systems. It guarantees the confidentiality, authenticity, and integrity of critical assets and private data, and it helps preserve software intellectual property and revenue models. It can be used in a wide range of industrial, medical, network, and computer peripheral devices such as IoT embedded devices, SCADA devices, PLC, IoT gateways and sensor nodes, network appliances, medical equipment, and wearables.

The MAXQ1065 is controlled over an SPI interface. Its low pin count, reduced package size, low power consumption, and adaptable voltage range makes it easy to integrate into an existing board design. Its lifetime also makes it compatible with long-term deployments.

The software development kit (SDK) facilitates the integration of the MAXQ1065 functionality into the host microcontroller's firmware, without the need to deeply understand the communication protocol at the bit level.

The MAXQ1065 cryptographic toolbox supports an array of security needs. Simpler systems may require as little as the provided key generation and storage. For high levels of security, full TLS/DTLS support offers a high level of abstraction. This includes TLS/DTLS 1.2 client-side key negotiation (PSK, ECDH, ECDHE), ECDSA-based TLS/DTLS authentication, digital signature generation and verification, root and device X.509 certificate storage, on-chip peer certificate verification (ECDSA), TLS/DTLS packet encryption, and signature (AES-GCM/CCM). It can also serve as a secure bootloader for the host microcontroller of the system. In addition, it can bring device-level physical security through its tamper detection input, secure inputs/outputs, secure boot, and firmware updates.

The MAXQ1065 user-programmable nonvolatile memory securely stores certificates, public, private and secret keys, monotonic counters, and arbitrary data. Access rights are fully customizable and can be granted to separate stakeholders (device manufacturer, end-user, authenticated host processor, and key importer).

The MAXQ1065 life cycle management allows flexible access control rules during the major life cycle stages of the device. Secure key loading protocol and secure factory provisioning are available.

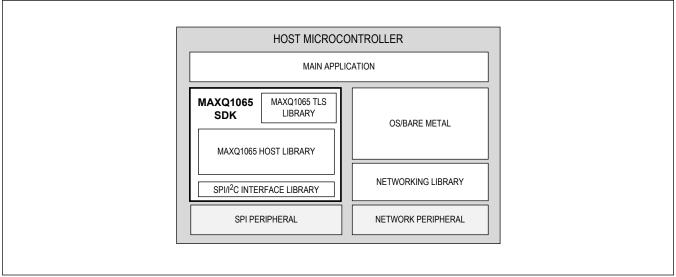

#### **Software Collateral**

#### **Software Ecosystem**

The MAXQ1065 comes with a complete software ecosystem in an SDK, enabling seamless software integration into the host microcontroller.

Figure 1. Software Offering

# Ultra Low-Power Cryptographic Controller with ChipDNA<sup>TM</sup> for Embedded Devices

The SDK includes a complete host software solution including the host library, TLS libraries, and the SPI/I<sup>2</sup>C interface library.

The host library maps the SPI commands of the MAXQ1065 into a convenient application programming interface in C language. The SPI/I<sup>2</sup>C interface library manages the communication protocol between the host microcontroller and the MAXQ1065.

On top of this host library, the MAXQ1065 TLS library is actually a choice between the Arm<sup>®</sup> Mbed<sup>®</sup> TLS or OpenSSL TLS libraries, both providing TLS1.2/DTLS 1.2 in client or server modes. In these TLS libraries, the security-sensitive processing of the TLS protocol is delegated to the MAXQ1065; therefore, the host microcontroller does not need to manipulate or store sensitive/secret data. The Mbed TLS and OpenSSL cryptographic libraries also use the MAXQ1065 as a "cryptographic engine," storing keys and certificates and running cryptographic algorithms in lieu of the host processor. This allows the main microcontroller's firmware to use the standard cryptographic APIs proposed by Mbed TLS or OpenSSL while taking advantage of the MAXQ1065 high-security and convenient provisioning.

The complete host software is implemented in C language, dependent only on the standard C library, with no dependence on the OS. In addition, the software SPI/I<sup>2</sup>C interface library layer, needed to interface physically with the MAXQ1065 through SPI and GPIOs, is clearly separated so it can be easily ported. The complete host software is adapted to bare-metal environments, the Arduino<sup>®</sup> development environment, Arm Mbed OS, Windows<sup>®</sup>, and Linux<sup>®</sup> (the provided software only runs in UserLAnd), and can easily be adapted to other environments.

The EV kit board allows easy interfacing with any existing system for rapid evaluation and prototyping. It connects to typical single board computers or microcontroller evaluation boards through standard connectors.

The SDK also includes:

- A simple PKI management and provisioning tool for testing purposes

- · Basic examples and use cases

- TLS communication examples

The source code is accessible and reusable with nonconstraining software licenses.

Arduino is a registered trademark of Arduino, LLC.

Arm and Mbed are registered trademarks and service marks of Arm Limited.

Linux is a registered trademark of Linus Torvalds.

Windows is a registered trademark of Microsoft Corporation.

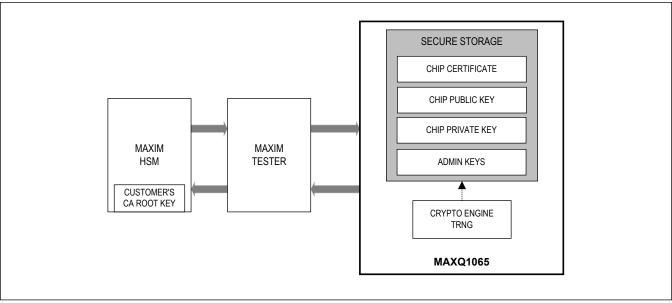

#### **Provisioning Service**

Maxim Integrated can preprogram each MAXQ1065 with unique key pairs and certificates, in addition to a set of common static data, to remove the complexity of deploying a certificate issuance system at the customer's factory. During this factory-programming process, key pairs are generated onboard the MAXQ1065, the private key never leaving the MAXQ1065. The public key is extracted and certified using a standard certificate signing request sent to a dedicated hardware security module (HSM) at the factory that contains the certification authority private signing key. The certificate is loaded back into the MAXQ1065 with additional static data and customer-specific administration keys. As a result, the MAXQ1065's ownership is transferred to the customer, and the system using the MAXQ1065 is able to connect through TLS to the targeted network infrastructure.

Figure 2. Provisioning

#### **Software Integration**

The MAXQ1065 comes with software for the host microcontroller that makes integration into any system very easy. The software enables a higher level of abstraction of the command set and the communication protocol.

#### **Device Features**

#### Cryptographic Toolbox for TLS

The MAXQ1065 cryptographic toolbox increases the security of TLS/DTLS based applications by providing:

- Verification of peer certificates and certificate revocation lists against trustworthy root certificates; root certificates are stored in the internal secure storage and can be securely updated

- ECDSA-based mutual authentication with other peers without exposing device private keys

- TLS handshake (PSK, ECDH, ECDHE) performed without revealing session keys

- Encryption/decryption and signature/verification of messages of the TLS record protocol with session keys

- TLS/DTLS supported algorithms

- TLS/DTLS key handshake

- ECDSA-based mutual authentication

- ECDSA X.509 on-board certificate verification

- TLS/DTLS packet encryption and signature (AES AEAD modes)

- Note: ECC algorithms run on the elliptic curve secp256r1

- Detailed list of supported TLS/DTLS 1.2 cipher suites:

- RFC 5487:

- TLS\_PSK\_WITH\_AES\_128\_GCM\_SHA256

- RFC 6655:

- TLS\_PSK\_WITH\_AES\_128\_CCM

- · TLS PSK WITH AES 256 CCM

- TLS\_PSK\_WITH\_AES\_128\_CCM\_8

- · TLS PSK WITH AES 256 CCM 8

- RFC 5289:

- TLS\_ECDHE\_ECDSA\_WITH\_AES\_128\_GCM\_SHA256

# Ultra Low-Power Cryptographic Controller with ChipDNA<sup>TM</sup> for Embedded Devices

- TLS\_ECDH\_ECDSA\_WITH\_AES\_128\_GCM\_SHA256

- RFC 7251:

- · TLS ECDHE ECDSA WITH AES 128 CCM

- · TLS ECDHE ECDSA WITH AES 256 CCM

- · TLS ECDHE ECDSA WITH AES 128 CCM 8

- TLS\_ECDHE\_ECDSA\_WITH\_AES\_256\_CCM\_8

#### **Generic Cryptographic Services**

The hardware crypto engine of the MAXQ1065 provides:

- Symmetric-key algorithms:

- AES-128/256 (ECB, CBC, CCM, GCM)

- Ellipctic-curve cryptography on curves:

- ECC NIST secp-256r1

- Secure hash algorithms:

- SHA-256

- MAC digest algorithms:

- AES-CBC-MAC

- AES-CMAC

- HMAC-SHA-256

- Signature schemes:

- · ECDSA signature and verification

- Key exchange algorithms:

- TLS 1.2 ECDH ECDSA, ECDHE ECDSA, and PSK

- SP800-56A-r3 static ECC CDH Diffie-Hellman with SP800-56A-r3 one-step KDF

- On-chip key generation:

- ECC

- AES

- Random number generation:

- NIST SP800-90A/B/C

- · Direct conditioned entropy output with health tests

#### **Unique Identifier**

Each MAXQ1065 comes with a unique ID, allowing unique identification of the system that contains the MAXQ1065 over a network. A dedicated private key allows for verification of the authenticity of the MAXQ1065.

#### **Secure Channel**

The optional secure channel provides confidentiality and integrity of commands and responses exchanged with the host processor on the SPI bus through:

- Key exchange between the host processor and the MAXQ1065, using preshared symmetric keys or ECC DH key exchange

- Signature and encryption of the commands and the responses

#### **Tamper Detection**

External tamper detection ensures information security at the system level. External tamper detection can selectively erase chosen data and can also assert the RESET\_OUT pin if enabled.

Internal consistency checks also guarantee a safe processing of sensitive information within the MAXQ1065. An internal consistency error generates an immediate tamper response.

The TAMPER\_IN pin can be connected to a user-defined tamper sensor, such as a switch, indicating a breach of the

# Ultra Low-Power Cryptographic Controller with ChipDNA<sup>TM</sup> for Embedded Devices

system enclosure.

#### **Reset Output**

A secure output can be controlled when user-configurable events occur, such as failure to perform a secure boot, failure to authenticate to a server, tamper event, internal consistency error, or positive events such as the successful initiation of a secure channel with the host processor or successful TLS authentication. The secure output can control device subsystems such as the system's host microcontroller's reset signal or an LED without requiring the host microcontroller intervention. The possible triggers can be one or more of the following:

- Secure boot failure/success

- Secure channel error/success

- Tamper detection

- Internal consistency error

- Power-on reset of the MAXQ1065

- Watchdog timer expiration

The MAXQ1065 can, therefore, act as an external security watchdog.

#### Secure Boot, Secure Update

The integrity of the host processor's data and code can be verified through the digital signature verification mechanism. The security policy of the MAXQ1065 can leverage this verification to grant or deny access to some assets, such as the MAXQ1065 specific private key used for TLS authentication, making the system unable to initiate a TLS connection if the firmware is not trusted.

#### Life Cycle Management

A managed life cycle changes functions and properties over time, as shown in <u>Table 1</u>. At each state of the life cycle, the device and parties are granted initialization, read, or modification rights to specific information. Transitions are always initiated by the administrator using a dedicated command. The life cycle is a useful tool to manage the security policy across the various life cycle stages. Selected keys can be zeroized when moving the life cycle backwards.

#### **Key Loading Protocol**

A secure key loading using encryption and authentication protocol allows key importation into the MAXQ1065 secure storage.

#### Watchdog

An optional watchdog feature can be enabled. When enabled, the MAXQ1065 monitors the WDI input pin for a regular toggling from the main devices' microcontroller. The absence of toggling within a defined time frame means that the main microcontroller is not operating properly.

#### Field Update

In a fast-moving security landscape, the internal firmware of the MAXQ1065 can be securely updated in order to secure long-term deployments, thanks to its secure update and secure boot mechanisms.

#### **Secure Storage and Access Control**

Secure storage is organized in a set of objects of different types as detailed in <u>Table 1</u>. In addition to the type, objects can be defined as volatile or nonvolatile, and also objects can get erased or not on an external tamper event. To be resistant to power loss during write operations, object modification is atomic. That means if a write operation is interrupted, the object will revert to its previous value and does not remain in an intermediate, corrupted state. Objects can be allocated and deallocated at will, and the free space is reclaimed.

Objects are stored with their own user-programmable, role-based, and life cycle state-dependent access conditions. Role authentication is based on challenge-response public key strong authentication. Roles all come with dedicated secure channels providing confidentiality, integrity, and anti-replay over the command interface. The security policy of an object is defined by the administrator using the Create Object command.

#### **Key Storage**

Key objects are stored in an integrity-protected manner and can never be read in the clear. They are automatically verified before use. Key pairs can be generated internally and stored in a persistent key pair object. Key pairs can also be generated externally and imported after successful signature verification using an imported public key present in the module. Arbitrary key pairs cannot be used; verification is mandatory.

#### **Certificate Storage**

Certificates are stored in an integrity-protected manner. They are automatically verified using one or more parent certificates in the certification chain (certificates already stored in the MAXQ1065). The device verifies the digital signature of the certificates and can extract their public key.

Arbitrary certificates cannot be stored; verification by a parent certificate or by a dedicated public key is mandatory. Since the device has limited certificate-parsing capabilities, the complete parsing of the X.509 certificates is done by the host processor when required.

#### **Storable Objects**

#### **Table 1. Storable Objects**

| TYPE                    | READABLE<br>(*)                            | COMMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Secret Key              | No                                         | Arbitrary symmetric keys are used in cryptographic algorithms. They can be imported or generated in place. They can be exported in an encrypted form using strict access control that uses authentication and encryption.                                                                                                                                                                                                                                                                                        |

| Public Key              | Yes                                        | Arbitrary public keys are used for the verification of key or root certificate importation requests, or for administrator authentication. Importation of public keys is strictly controlled with authentication.                                                                                                                                                                                                                                                                                                 |

| Key Pair                | Yes (public<br>key)<br>No (private<br>key) | Arbitrary public and private key pairs are used in asymmetric cryptography algorithms. These key pairs can be imported into the MAXQ1065 or generated in place. The public key can be read out, but the private key is always protected against disclosure. Importation of key pairs is strictly controlled with authentication and encryption.                                                                                                                                                                  |

| Transparent             | Yes                                        | Arbitrary user data for anything else.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Monotonic<br>Counter    | Yes                                        | Increasing counter or decreasing counter. Used for implementing complementary life cycle system or managing number of system errors. Up to 10k write cycles are supported. Counters can be tied to key usage.                                                                                                                                                                                                                                                                                                    |

| X.509 v3<br>Certificate | Yes                                        | Certificates can be the MAXQ1065's own certificates (that should have been signed by a certification authority, and that can be matched with a key pair type of object also present in the object storage) or they can come from other entities such as PKI Certification authorities or other network peers. Certificates are used to reliably mutually authenticate with other peers. Certificates are protected against modification. Importation of certificates is strictly controlled with authentication. |

#### **Communication Interfaces and Power**

Command and data transfer occurs over the SPI. Data transfer is verified when writing and reading by a 16-bit cyclic redundancy check (CRC-16).

#### **Ready Output**

The command/response protocol can work using polling or using the MAXQ1065 ready output pin (RDY). When using polling, the host has to periodically send a polling request over the communication interface after the transmission of a command in order to be informed of its completion. The host can alternatively use the RDY pin (optionally using an interrupt-capable GPIO) to get informed of this event.

#### SPI

The serial peripheral interface (SPI) is a four-wire bus that provides fast, synchronous, full-duplex communication between the MAXQ1065 and the host system. The peripheral provides the following features:

# Ultra Low-Power Cryptographic Controller with ChipDNA<sup>TM</sup> for Embedded Devices

- Slave mode operation

- Active-low SSEL

- 10MHz (max) SPI slave clock speed

- · Characters transmitted LSB first

- Data protocol uses SPI Mode 0

#### **Low-Power Mode**

The MAXQ1065 automatically enters a low-power mode upon reception of a dedicated command. While in low-power mode, the external tamper detection is still active. The MAXQ1065 wakes up automatically when the host starts sending a command to the MAXQ1065 through the selected communication interface or when a tamper event occurs.

#### **Shutdown Mode**

The MAXQ1065 enters shutdown when the PDWN pin is asserted. When resuming, the internal state of the MAXQ1065 is reset.

#### **ChipDNA Physically Unclonable Function (PUF)**

ChipDNA PUF security technology provides an exponential increase in protection against the invasive and reverse engineering attacks that hackers use. Attempts to probe or observe ChipDNA operation modifies the underlying circuit characteristics, preventing the discovery of the unique value used by the chip cryptographic functions. Similarly, more exhaustive reverse-engineering attempts are defeated due to the factory conditioning required to make the ChipDNA PUF circuitry operational. The per-device unique key is generated by the ChipDNA PUF circuitry only when needed for cryptographic operations and is then instantaneously deleted.

Most importantly, the ChipDNA secure key never resides statically in registers or memory, nor does it ever leave the electrical boundary of the IC. In addition to the protection benefits, ChipDNA simplifies or eliminates the need for secure IC key management.

#### **Development and Technical Support**

Designers must have the following documents to use all the features of this device:

- This data sheet, which contains pin descriptions, feature overviews, and electrical specifications

- The device-appropriate user guide, which contains detailed information about the device features and operation

- Errata sheets for specific revisions noting deviations from published specifications

- The MAXQ1065 host library software and its inline documentation

#### **SPI Modes**

The MAXQ1065 supports SPI communications running in either of the following two SPI modes:

- Mode 0 (CPOL = 0, CPHA = 0): Data is sampled at the leading rising edge of the clock.

- Mode 3 (CPOL = 1, CPHA =1): Data is sampled on the trailing rising edge of the clock.

Details of the timing are described in Figure 3.

If enabled, an autodetect feature is available to detect between Mode 0 and Mode 3. The feature works by checking if the SPIS\_SCK signal is low (Mode 0) or high (Mode 3) before the falling edge of the SPIS\_SS signal during the t<sub>SAD</sub> time. Mode 1 and Mode 2 are not supported.

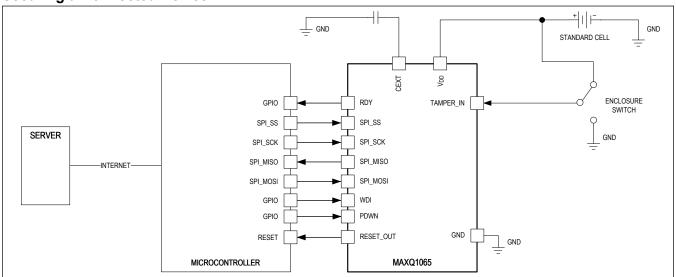

## **Typical Application Circuit**

### **Securing a Connected Device**

## **Ordering Information**

| PART          | PIN-PACKAGE |

|---------------|-------------|

| MAXQ1065GTC+T | 12 TDFN     |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel. Full reel.

# Ultra Low-Power Cryptographic Controller with ChipDNA<sup>TM</sup> for Embedded Devices

### **Revision History**

| REVISION NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|-----------------|---------------|-----------------|------------------|

| 0               | 5/21          | Initial release | _                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.