# CIC61508

Functional Safety Companion Chip

Data Sheet V1.2 2011-06

Edition 2011-06

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2011 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# CIC61508

Functional Safety Companion Chip

Data Sheet V1.2 2011-06

## CIC61508 Data Sheet

Revision History: V1.2 2011-06

| Previous ' | Versions: | V1   | ٠0. | V1.1  |  |

|------------|-----------|------|-----|-------|--|

| rievious   | versions. | V I. | .υ. | v 1.1 |  |

| Page | Subjects (major changes since last revision)                |  |

|------|-------------------------------------------------------------|--|

| 20   | Typical SPI timing parameters are replaced by limit values. |  |

|      |                                                             |  |

| -    |                                                             |  |

|      |                                                             |  |

|      |                                                             |  |

## We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

Data Sheet V1.2, 2011-06

# **Table of Contents**

# **Table of Contents**

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Overview1Features1Ordering Information1Functional Summary1Pin Configuration2Power Supply and Reset5 |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|

| 2                                    | Electrical Parameters 7                                                                             |

| 2.1                                  | General Parameters 7                                                                                |

| 2.1.1                                | Parameter Interpretation                                                                            |

| 2.1.2                                | Absolute Maximum Rating                                                                             |

| 2.1.3                                | Operating Conditions                                                                                |

| 2.2                                  | DC Parameters                                                                                       |

| 2.2.1                                | Input/Output Characteristics                                                                        |

| 2.2.2                                | Supply Threshold Characteristics                                                                    |

| 2.2.3                                | Voltage Monitor Characteristics                                                                     |

| 2.2.4                                | Power Supply Current                                                                                |

| 2.3                                  | AC Parameters                                                                                       |

| 2.3.1                                | Testing Waveforms                                                                                   |

| 2.3.2                                | Output Rise/Fall Times                                                                              |

| 2.3.3                                | Reset Timing                                                                                        |

| 2.3.4                                | SPI Timing                                                                                          |

| <b>3</b><br>3.1                      | Package and Quality Declaration                                                                     |

| 3.1<br>3.2                           | Package Parameters                                                                                  |

|                                      | Package Outline                                                                                     |

| 3.3                                  | Quality Declaration                                                                                 |

## **Functional Safety Companion Chip**

CIC61508

## 1 Overview

## 1.1 Features

The CIC61508 has the following features:

- Power supply monitor for over- and under-voltage

- Sequencer

- · Task monitor

- Data comparison and verification functions

- SPI communication monitor

- Safety path control (enable/disable)

- Configurable Wake-Up Timer

- Wide range of voltage supply supported (3.3V or 5.0V +/-10%)

- TSSOP-38 package available

# 1.2 Ordering Information

For the available ordering codes for the CIC61508, please refer to your responsible sales representative or your local distributor.

This document decribes the device types shown in Table 1-1.

Table 1-1 CIC61508 Device Types

| Device Type          | Power Supply | Ambient Temperature Range |  |  |

|----------------------|--------------|---------------------------|--|--|

| SAA-CIC61508-OSRF 5V | 5.0 V        | -40 to 140 °C             |  |  |

| SAA-CIC61508-OSRF 3V | 3.3 V        | -40 to 140 °C             |  |  |

# 1.3 Functional Summary

The CIC61508 is a Companion Safety Monitor Chip to build up functional safety applications; examples include airbag, Electrical Powered Steering (EPS) and damping systems. The chip is responsible for monitoring the host microcontroller's behaviour. It can monitor the host microcontroller's power supply and verify the host microcontroller's requests. It therefore serves as an independent diagnostic monitoring device to allow the host microcontroller system to be SIL3 approved.

Data Sheet 1 V1.2, 2011-06

# 1.4 Pin Configuration

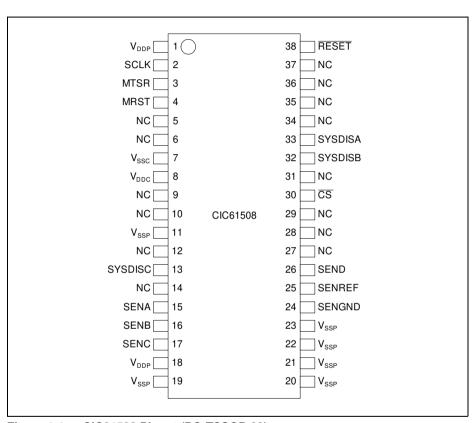

Figure 1-1 CIC61508 Pinout (PG-TSSOP-38)

Table 1-2 Pin Definitions and Functions (PG-TSSOP-38)

| Pin<br>Number | Туре | Reset<br>State <sup>1)</sup> | Symbol    | Function       |

|---------------|------|------------------------------|-----------|----------------|

| 1             | -    | -                            | $V_{DDP}$ | Voltage Supply |

| 2             | I    | Hi-Z                         | SCLK      | SPI Clock      |

| 3             | I    | Hi-Z                         | MTSR      | SPI Input      |

| 4             | 0    | Hi-Z                         | MRST      | SPI Output     |

| 5             | -    | -                            | NC        | Not connected  |

Table 1-2 Pin Definitions and Functions (PG-TSSOP-38)

| Pin<br>Number | Туре | Reset<br>State <sup>1)</sup> | Symbol           | Function                     |

|---------------|------|------------------------------|------------------|------------------------------|

| 6             | -    | -                            | NC               | Not connected                |

| 7             | -    | -                            | V <sub>SSC</sub> | Supply Ground (Digital)      |

| 8             | -    | -                            | $V_{DDC}$        | Core Supply Monitor          |

| 9             | -    | -                            | NC               | Not connected                |

| 10            | -    | -                            | NC               | Not connected                |

| 11            | -    | -                            | $V_{SSP}$        | Supply Ground                |

| 12            | -    | -                            | NC               | Not connected                |

| 13            | 0    | PU                           | SYSDISC          | System Disable C             |

| 14            | -    | -                            | NC               | Not connected                |

| 15            | I    | Hi-Z                         | SENA             | Analog Input A               |

| 16            | I    | Hi-Z                         | SENB             | Analog Input B               |

| 17            | I    | Hi-Z                         | SENC             | Analog Input C               |

| 18            | -    | -                            | $V_{DDP}$        | Voltage Supply               |

| 19            | -    | -                            | $V_{\rm SSP}$    | Supply Ground                |

| 20            | -    | -                            | $V_{SSP}$        | Supply Ground                |

| 21            | -    | -                            | $V_{SSP}$        | Supply Ground                |

| 22            | -    | -                            | V <sub>SSP</sub> | Supply Ground                |

| 23            | -    | -                            | $V_{\rm SSP}$    | Supply Ground                |

| 24            | -    | -                            | SENGND           | Analog Ground                |

| 25            | -    | -                            | SENREF           | Analog Reference             |

| 26            | I    | Hi-Z                         | SEND             | Analog Input D               |

| 27            | -    | -                            | NC               | Not connected                |

| 28            | -    | -                            | NC               | Not connected                |

| 29            | -    | -                            | NC               | Not connected                |

| 30            | I/O  | PD                           | CS               | Chip Select / Wake-Up Output |

| 31            | -    | -                            | NC               | Not connected                |

| 32            | 0    | Hi-Z                         | SYSDISB          | System Disable B             |

| 33            | 0    | Hi-Z                         | SYSDISA          | System Disable A             |

| 34            | -    | -                            | NC               | Not connected                |

| 35            | -    | -                            | NC               | Not connected                |

Table 1-2 Pin Definitions and Functions (PG-TSSOP-38)

| Pin<br>Number | Туре | Reset<br>State <sup>1)</sup> | Symbol | Function      |

|---------------|------|------------------------------|--------|---------------|

| 36            | -    | -                            | NC     | Not connected |

| 37            | -    | -                            | NC     | Not connected |

| 38            | I    | PU                           | RESET  | Reset Input   |

<sup>1)</sup> Abbreviations: PU - Pull up; PD - Pull down; Hi-Z - High impedance.

## 1.5 Power Supply and Reset

The power supply to the CIC61508 is regulated by the internal voltage regulator that comes with detection circuitries to ensure that the supplied voltages are within the specified operating range.

The CIC61508 microcontroller requires a power supply voltage level ( $V_{\rm DDP}$ ) of 3.3 V or 5.0 V, which must be provided from the external power supply pin.

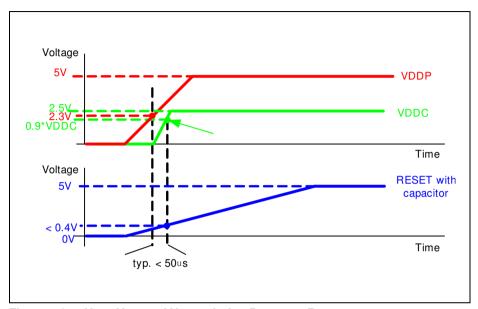

$V_{\rm DDP}$  is used to power up the CIC61508. In order to power up the chip properly, the external reset pin  $\overline{\rm RESET}$  must be asserted until the internal working voltage ( $V_{\rm DDC}$ ) reaches 90% of its intended voltage of 2.5 V. The delay of external reset can be realized by an external capacitor at  $\overline{\rm RESET}$  pin. This capacitor value must be selected so that  $V_{\rm RESET}$  reaches 0.4 V, but not before  $V_{\rm DDC}$  reaches 0.9\*  $V_{\rm DDC}$ .

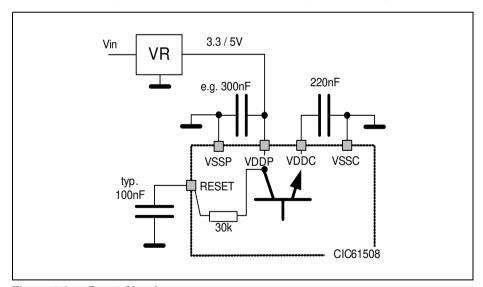

A typical application example is shown in Figure 1-2.  $V_{\rm DDP}$  capacitor value is 300 nF.  $V_{\rm DDC}$  capacitor value is 220 nF. The capacitor connected to RESET pin is 100 nF.

Typically, the time taken for  $V_{\rm DDC}$  to reach  $0.9^*V_{\rm DDC}$  is less than 50  $\mu \rm s$  once  $V_{\rm DDP}$  reaches 2.3V. Hence, based on the condition that 10% to 90%  $V_{\rm DDP}$  (slew rate) is less than 500  $\mu \rm s$ , the RESET pin should be held low for 500  $\mu \rm s$  typically. See Figure 1-3.

Figure 1-2 Reset Circuitry

Figure 1-3  $V_{DDP}$ ,  $V_{DDC}$  and  $V_{RESET}$  during Power-on Reset

An external hardware reset is triggered when the reset input pin  $\overline{\text{RESET}}$  is asserted and held low for at least 100 ns.

$V_{\rm DDC}$  detector in the internal voltage regulator detects brownout when the core supply voltage  $V_{\rm DDC}$  dips below the threshold voltage  $V_{\rm DDC\_TH}$  (2.1 V). The brownout will cause the device to be reset.

Both the hardware reset and the brownout reset have the same effect as a power-on reset, therefore the SYSDISx pins will be reset to their default states shown in **Table 1-2**.

# 2 Electrical Parameters

**Chapter 2** provides the characteristics of the electrical parameters which are implementation-specific for the CIC61508.

## 2.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 2.2** and **Section 2.3**.

# 2.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the CIC61508 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

## · cc

These parameters indicate Chip Characteristics, which are distinctive features of the CIC61508 and must be regarded for a system design.

#### • SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the system in which the CIC61508 is designed in.

# 2.1.2 Absolute Maximum Rating

Maximum ratings are the extreme limits to which the CIC61508 can be subjected to without permanent damage.

Table 1 Absolute Maximum Rating Parameters

| Parameter                                                                                                             | Symbol       | Limit | Values                           | Unit | Notes                 |

|-----------------------------------------------------------------------------------------------------------------------|--------------|-------|----------------------------------|------|-----------------------|

|                                                                                                                       |              | min.  | max.                             |      |                       |

| Ambient temperature                                                                                                   | $T_{A}$      | -40   | 140                              | °C   | under bias            |

| Storage temperature                                                                                                   | $T_{\rm ST}$ | -65   | 150                              | °C   |                       |

| Junction temperature                                                                                                  | $T_{J}$      | -40   | 150                              | °C   | under bias            |

| $\begin{tabular}{lll} \hline & Voltage on power supply pin with \\ & respect to $V_{\rm SS}$ \\ \hline \end{tabular}$ | $V_{DDP}$    | -0.5  | 6                                | ٧    |                       |

| Voltage on any pin with respect to $V_{\rm SS}$                                                                       | $V_{IN}$     | -0.5  | V <sub>DDP</sub> + 0.5 or max. 6 | V    | whichever is<br>lower |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions  $(V_{\rm IN} > V_{\rm DDP} \ {\rm or} \ V_{\rm IN} < V_{\rm SS})$  the voltage on  $V_{\rm DDP}$  pin with respect to ground  $(V_{\rm SS})$  must not exceed the values defined by the absolute maximum ratings.

# 2.1.3 Operating Conditions

The following operating conditions must not be exceeded in order to ensure correct operation of the CIC61508. All parameters mentioned in the following table refer to these operating conditions, unless otherwise noted.

Table 2 Operating Condition Parameters

| Parameter                               | Symbol    | L    | imit Val | Unit | Notes/ |                 |

|-----------------------------------------|-----------|------|----------|------|--------|-----------------|

|                                         |           | min. | typ.     | max. |        | Conditions      |

| Digital power supply voltage            | $V_{DDP}$ | 3.0  | -        | 3.6  | V      | 3.3V<br>Variant |

| Digital power supply voltage            | $V_{DDP}$ | 4.5  | -        | 5.5  |        | 5.0V<br>Variant |

| Digital ground voltage                  | $V_{SS}$  | 0    |          |      | V      |                 |

| Operating Clock Frequency <sup>1)</sup> | $f_{CLK}$ | -    | 26.7     | -    | MHz    |                 |

| Ambient temperature                     | $T_{A}$   | -40  | -        | 140  | °C     |                 |

Some parts of the CIC61508 run at 80 MHz frequency. These frequencies are internal working frequencies of the CIC61508.

## 2.2 DC Parameters

The electrical characteristics of the DC Parameters are detailed in this section.

# 2.2.1 Input/Output Characteristics

Table 3 provides the characteristics of the input/output pins of the CIC61508.

Table 3 Input/Output Characteristics (Operating Conditions apply)

| Parameter                                   | Symbol        |    | Limit                   | Limit Values                |    | Test Conditions                                                         |  |

|---------------------------------------------|---------------|----|-------------------------|-----------------------------|----|-------------------------------------------------------------------------|--|

|                                             |               |    |                         | max.                        |    |                                                                         |  |

| $V_{\rm DDP}$ = 5 V Range                   |               |    |                         |                             |    |                                                                         |  |

| Output low voltage                          | $V_{OL}$      | CC | _                       | 1.0                         | V  | $I_{\rm OL}$ = 15 mA                                                    |  |

|                                             |               |    | _                       | 0.4                         | V  | $I_{\rm OL}$ = 5 mA                                                     |  |

| Output high voltage                         | $V_{OH}$      | CC | V <sub>DDP</sub> - 1.0  | _                           | V  | I <sub>OH</sub> = -15 mA                                                |  |

|                                             |               |    | V <sub>DDP</sub> - 0.4  | _                           | V  | I <sub>OH</sub> = -5 mA                                                 |  |

| Input low voltage on port pins              | $V_{ILP}$     | SR | _                       | $0.3 	imes V_{	extsf{DDP}}$ | V  | CMOS Mode                                                               |  |

| Input low voltage on RESET pin              | $V_{ILR}$     | SR | _                       | $0.3 	imes V_{	extsf{DDP}}$ | V  | CMOS Mode                                                               |  |

| Input high voltage on port pins             | $V_{IHP}$     | SR | $0.7 	imes V_{ m DDP}$  | _                           | V  | CMOS Mode                                                               |  |

| Input high voltage on RESET pin             | $V_{IHR}$     | SR | $0.7 	imes V_{ m DDP}$  | _                           | V  | CMOS Mode                                                               |  |

| Input Hysteresis on port pins <sup>1)</sup> | HYSP          | CC | $0.08 	imes V_{ m DDP}$ | _                           | V  | CMOS Mode                                                               |  |

| Pull-up current                             | $I_{PU}$      | SR | _                       | -10                         | μА | $V_{IH,min}$                                                            |  |

|                                             |               |    | -150                    | _                           | μА | $V_{IL,max}$                                                            |  |

| Pull-down current                           | $I_{PD}$      | SR | _                       | 10                          | μА | $V_{IL,max}$                                                            |  |

|                                             |               |    | 150                     | _                           | μА | $V_{IH,min}$                                                            |  |

| Input leakage current <sup>2)3)</sup>       | $I_{\rm OZ1}$ | CC | -0.5                    | 0.5                         | μА | $ 0 < V_{\rm IN} < V_{\rm DDP}, \\ T_{\rm A} \le 140 ^{\circ} {\rm C} $ |  |

| Overload current on any pin                 | $I_{OV}$      | SR | -5                      | 5                           | mA |                                                                         |  |

Table 3 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                                                                                                | Symbol            |    | Limit Values                                                        |                             | Unit | <b>Test Conditions</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----|---------------------------------------------------------------------|-----------------------------|------|------------------------|

|                                                                                                                                                          |                   |    | min.                                                                | max.                        |      |                        |

| Absolute sum of overload currents                                                                                                                        | $\Sigma  I_{OV} $ | SR | _                                                                   | 25                          | mA   | 3)                     |

| Voltage on any pin during $V_{\rm DDP}$ power off                                                                                                        | $V_{PO}$          | SR | _                                                                   | 0.3                         | V    | 4)                     |

| Maximum current per pin (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )                                                                                      | $I_{M} SR$        | SR | _                                                                   | 15                          | mA   |                        |

| $\label{eq:maximum} \begin{array}{l} \text{Maximum current for all} \\ \text{pins (excluding } V_{\text{DDP}} \\ \text{and } V_{\text{SS}}) \end{array}$ | $\Sigma  I_{M} $  | SR | -                                                                   | 60                          | mA   |                        |

| $\begin{tabular}{ll} \hline \textbf{Maximum current into} \\ V_{\rm DDP} \\ \hline \end{tabular}$                                                        | $I_{MVDDP}$       | SR | _                                                                   | 80                          | mA   |                        |

| $\frac{\text{Maximum current out of}}{V_{\text{SS}}}$                                                                                                    | $I_{MVSS}$        | SR | _                                                                   | 80                          | mA   |                        |

| $V_{\mathrm{DDP}}$ = 3.3 V Range                                                                                                                         |                   |    |                                                                     |                             |      |                        |

| Output low voltage                                                                                                                                       | $V_{OL}$          | CC | _                                                                   | 1.0                         | V    | $I_{\rm OL}$ = 8 mA    |

|                                                                                                                                                          |                   |    | _                                                                   | 0.4                         | V    | $I_{\rm OL}$ = 2.5 mA  |

| Output high voltage                                                                                                                                      | $V_{OH}$          | CC | $V_{\mathrm{DDP}}$ - 1.0                                            | _                           | V    | $I_{\rm OH}$ = -8 mA   |

|                                                                                                                                                          |                   |    | $V_{ m DDP}$ - 0.4                                                  | _                           | V    | $I_{\rm OH}$ = -2.5 mA |

| Input low voltage on port pins                                                                                                                           | $V_{ILP}$         | SR | _                                                                   | $0.3 \times \\ V_{\rm DDP}$ | ٧    | CMOS Mode              |

| Input low voltage on RESET pin                                                                                                                           | $V_{ILR}$         | SR | _                                                                   | $0.3 	imes V_{ m DDP}$      | V    | CMOS Mode              |

| Input high voltage on port pins                                                                                                                          | $V_{IHP}$         | SR | $V_{ m DDP}$                                                        | _                           | V    | CMOS Mode              |

| Input high voltage on RESET pin                                                                                                                          | $V_{IHR}$         | SR | $V_{ m DDP}$                                                        | _                           | V    | CMOS Mode              |

| Input Hysteresis <sup>1)</sup>                                                                                                                           | HYS               | СС | $\begin{array}{c} \text{0.03} \times \\ V_{\text{DDP}} \end{array}$ | _                           | V    | CMOS Mode              |

| Pull-up current                                                                                                                                          | $I_{PU}$          | SR | _                                                                   | -5                          | μА   | $V_{IH,min}$           |

|                                                                                                                                                          |                   |    | -50                                                                 | _                           | μΑ   | $V_{IL,max}$           |

Table 3 Input/Output Characteristics (Operating Conditions apply) (cont'd)

| Parameter                                                                                                                                                     | Symbol            |    | Limit Values |      | Unit | <b>Test Conditions</b>                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----|--------------|------|------|---------------------------------------------------------------------------------------------------------|

|                                                                                                                                                               |                   |    | min.         | max. |      |                                                                                                         |

| Pull-down current                                                                                                                                             | $I_{PD}$          | SR | -            | 5    | μА   | $V_{IL,max}$                                                                                            |

|                                                                                                                                                               |                   |    | 50           | _    | μА   | $V_{IH,min}$                                                                                            |

| Input leakage current <sup>2)3)</sup>                                                                                                                         | $I_{\rm OZ1}$     | CC | -0.5         | 0.5  | μА   | $ \begin{aligned} 0 &< V_{\rm IN} < V_{\rm DDP}, \\ T_{\rm A} &\leq 140^{\circ} {\rm C} \end{aligned} $ |

| Overload current on any pin                                                                                                                                   | $I_{OV}$          | SR | -5           | 5    | mA   |                                                                                                         |

| Absolute sum of overload currents                                                                                                                             | $\Sigma  I_{OV} $ | SR | _            | 25   | mA   | 3)                                                                                                      |

| Voltage on any pin during $V_{\rm DDP}$ power off                                                                                                             | $V_{PO}$          | SR | _            | 0.3  | V    | 4)                                                                                                      |

| Maximum current per pin (excluding $V_{\rm DDP}$ and $V_{\rm SS}$ )                                                                                           | I <sub>M</sub> SR | SR | _            | 15   | mA   |                                                                                                         |

| $\begin{array}{l} \mbox{Maximum current for all} \\ \mbox{pins (excluding } V_{\mbox{\scriptsize DDP}} \\ \mbox{and } V_{\mbox{\scriptsize SS}}) \end{array}$ | $\Sigma  I_{M} $  | SR | _            | 60   | mA   |                                                                                                         |

| $\begin{tabular}{ll} \hline \textbf{Maximum current into} \\ V_{\rm DDP} \\ \hline \end{tabular}$                                                             | $I_{MVDDP}$       | SR | _            | 80   | mA   |                                                                                                         |

| $\begin{array}{c} \text{Maximum current out of} \\ V_{\text{SS}} \end{array}$                                                                                 | $I_{MVSS}$        | SR | _            | 80   | mA   |                                                                                                         |

Not subjected to production test, verified by design/characterization. Hysteresis is implemented to avoid meta stable states and switching due to internal ground bounce. It cannot be guaranteed that it suppresses switching due to external system noise.

An additional error current (I<sub>INJ</sub>) will flow if an overload current flows through an adjacent pin. RESET pin has internal pull devices and is not included in the input leakage current characteristic.

<sup>3)</sup> Not subjected to production test, verified by design/characterization.

<sup>4)</sup> Not subjected to production test, verified by design/characterization. However, for applications with strict low power-down current requirements, it is mandatory that no active voltage source is supplied at any pin when V<sub>DDP</sub> is powered off.

# 2.2.2 Supply Threshold Characteristics

Table 4 provides the characteristics of the supply threshold in the CIC61508.

Note:  $V_{\rm DDC}$  is an internal working voltage used by some parts of the CIC61508.

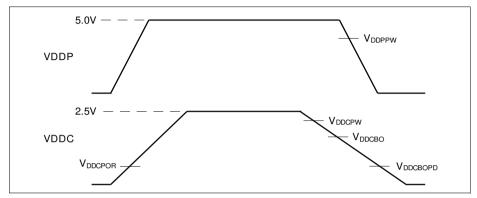

Figure 1 Supply Threshold Parameters

Table 4 Supply Threshold Parameters (Operating Conditions apply)

| Parameters                                                     | Symbol           |    |      | Unit |      |   |

|----------------------------------------------------------------|------------------|----|------|------|------|---|

|                                                                |                  |    | min. | typ. | max. |   |

| $\overline{V_{\text{DDC}}}$ prewarning voltage <sup>1)</sup>   | $V_{DDCPW}$      | CC | 2.2  | 2.3  | 2.4  | V |

| $V_{ m DDC}$ brownout voltage in active $ m mode^{1)}$         | $V_{ m DDCBO}$   | CC | 2.0  | 2.1  | 2.2  | V |

| $V_{ m DDC}$ brownout voltage in power-down mode <sup>2)</sup> | $V_{ m DDCBOPD}$ | CC | 1.3  | 1.5  | 1.7  | V |

| $\overline{V_{\mathrm{DDP}}}$ prewarning voltage <sup>3)</sup> | $V_{DDPPW}$      | CC | 3.4  | 4.0  | 4.65 | V |

| Power-on reset voltage <sup>2)</sup>                           | $V_{DDCPOR}$     | CC | 1.3  | 1.5  | 1.7  | V |

<sup>1)</sup> Detection is disabled in power-down mode.

<sup>2)</sup> Detection is enabled in both active and power-down mode.

Detection is enabled for external power supply of 5.0V.

Detection is disabled for external power supply of 3.3V.

# 2.2.3 Voltage Monitor Characteristics

All ground pins  $(V_{\rm SS})$  must be externally connected to one single star point in the system. The voltage difference between the ground pins must not exceed 200mV.

Table 1 Voltage Monitor Characteristics (Operating Conditions apply)

| Parameter                                           | Symbol           |    | Lir                      | nit Val   | ues                     | Unit | Test Conditions/ |  |

|-----------------------------------------------------|------------------|----|--------------------------|-----------|-------------------------|------|------------------|--|

|                                                     |                  |    | min.                     | typ.      | max.                    |      | Remarks          |  |

| Analog reference voltage                            | $V_{AREF}$       | SR | V <sub>AGND</sub><br>+ 1 | $V_{DDP}$ | V <sub>DDP</sub> + 0.05 | V    |                  |  |

| Analog reference ground                             | $V_{AGND}$       | SR | V <sub>SS</sub> - 0.05   | $V_{SS}$  | V <sub>AREF</sub> - 1   | V    |                  |  |

| Analog input<br>voltage range                       | $V_{AIN}$        | SR | $V_{AGND}$               | _         | $V_{AREF}$              | V    |                  |  |

| Total unadjusted                                    | TUE              | CC | _                        | _         | 2                       | LSB  | 5V variant       |  |

| error (for 10-bit conversion                        |                  |    | -                        | -         | 3                       | LSB  | 3.3V variant     |  |

| Switched capacitance at the reference voltage input | $C_{AREFSW}$     | CC | _                        | 10        | 20                      | pF   | 1)2)             |  |

| Switched capacitance at the analog voltage inputs   | $C_{AINSW}$      | CC | _                        | 5         | 7                       | pF   | 1)3)             |  |

| Input resistance of the reference input             | $R_{AREF}$       | CC | _                        | 1         | 2                       | kΩ   | 1)               |  |

| Input resistance of the selected analog channel     | R <sub>AIN</sub> | CC | _                        | 1         | 1.5                     | kΩ   | 1)               |  |

<sup>1)</sup> Not subject to production test, verified by design/characterization.

<sup>2)</sup> This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

The sampling capacity of the conversion C-Network is pre-charged to V<sub>AREF</sub>/2 before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than V<sub>AREF</sub>/2.

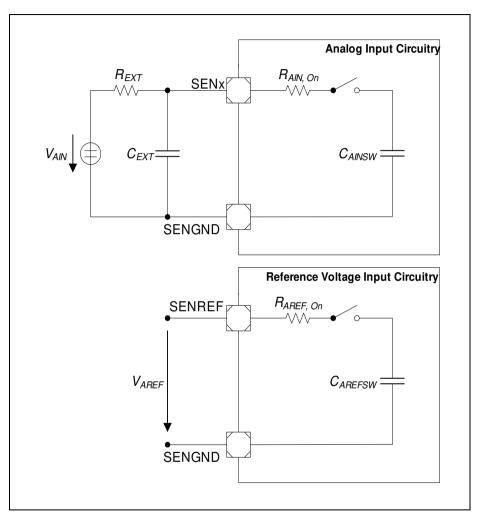

Figure 2 Voltage Monitor Input Circuits

# 2.2.4 Power Supply Current

Table 2 provides the characteristics of the power supply current in the CIC61508.

Table 2 Power Supply Current Parameters (Operating Conditions apply)

| Parameter                                            | Symbol    | Limit  | Values             | Unit | <b>Test Condition</b> |

|------------------------------------------------------|-----------|--------|--------------------|------|-----------------------|

|                                                      |           | typ.1) | max. <sup>2)</sup> |      |                       |

| Active Mode                                          | $I_{DDP}$ | 22.6   | 24.5               | mA   |                       |

| Periodic Wake-up (low current)<br>Mode <sup>3)</sup> | $I_{PWU}$ | 4.1    | -                  | mA   | 4)                    |

<sup>1)</sup> The typical current values are based on preliminary measurements and are to be used as reference only. These values are periodically measured at  $T_{\rm A}$  = + 25 °C and  $V_{\rm DDP}$  = 5.0 V.

<sup>2)</sup> The maximum current values are measured under worst case conditions ( $T_A = +140$  °C and  $V_{DDP} = 5.5$  V).

<sup>3)</sup> The periodic wake-up or low current mode is entered once the wake-up timer functionality is enabled.

<sup>4)</sup> Not subjected to production test, verified by design/characterization.

## 2.3 AC Parameters

The electrical characteristics of the AC Parameters are detailed in this section.

# 2.3.1 Testing Waveforms

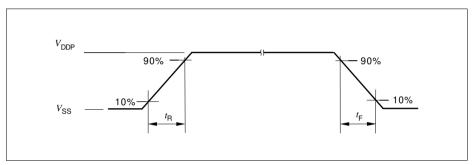

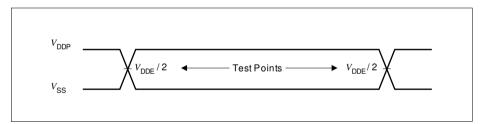

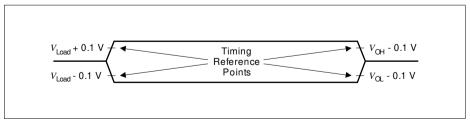

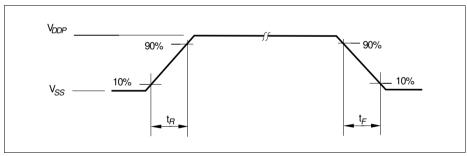

The testing waveforms for rise/fall time, output delay and output high impedance are shown in Figure 3, Figure 4 and Figure 5.

Figure 3 Rise/Fall Time Parameters

Figure 4 Testing Waveform, Output Delay

Figure 5 Testing Waveform, Output High Impedance

# 2.3.2 Output Rise/Fall Times

Table 1 provides the characteristics of the output rise/fall times in the CIC61508.

Table 1 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter 5                      | Symbol     | Limit<br>Values |      | Unit | Test Conditions      |  |  |

|----------------------------------|------------|-----------------|------|------|----------------------|--|--|

|                                  |            | min.            | max. |      |                      |  |  |

| $V_{\rm DDP}$ = 5V Range         | <u> </u>   |                 |      |      |                      |  |  |

| Rise/fall times <sup>1) 2)</sup> | $t_R, t_F$ | _               | 10   | ns   | 20 pF. <sup>3)</sup> |  |  |

| $V_{\rm DDP}$ = 3.3V Range       | 1          | '               |      | 1    | 1                    |  |  |

| Rise/fall times 1) 2)            | $t_R, t_F$ | _               | 10   | ns   | 20 pF. <sup>4)</sup> |  |  |

<sup>1)</sup> Rise/Fall time measurements are taken with 10% - 90% of pad supply.

- 3) Additional rise/fall time valid for  $C_1 = 20 pF 100 pF @ 0.125 ns/pF$ .

- 4) Additional rise/fall time valid for  $C_1 = 20 pF 100 pF @ 0.225 ns/pF$ .

Figure 6 Rise/Fall Times Parameters

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

# 2.3.3 Reset Timing

Table 3 provides the characteristics of the reset timing in the CIC61508.

Table 2 Reset Timing (Operating Conditions apply)

| Parameter                                                         | Symbol           |    | Limit Values |      |      | Unit | <b>Test Conditions</b> |

|-------------------------------------------------------------------|------------------|----|--------------|------|------|------|------------------------|

|                                                                   |                  |    | min.         | typ. | max. |      |                        |

| Start-up time from an immediate wake-up timer reset <sup>1)</sup> | t <sub>SWU</sub> | CC | _            | 55.8 | _    | ms   | 2)                     |

The start-up time is measured from the time the immediate wake-up timer reset is triggered to the time the start-up BIST is completed. The immediate wake-up timer reset is triggered by a SFR write command to the WAKERELOAD SFR while WAKEPRESCALAR SFR is configured with the value 8X<sub>H</sub>.

<sup>2)</sup> Not subjected to production test, verified by design/characterization.

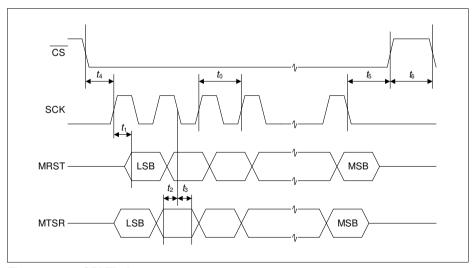

# 2.3.4 SPI Timing

Table 3 provides the characteristics of the SPI timing in the CIC61508.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Table 3 SPI Timing (Operating Conditions apply; CL = 50 pF)

| Syr   | nbol                          | Lim                                          | Unit                                                                                           |                                                                                                                                          |

|-------|-------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|       |                               | min.                                         | max.                                                                                           |                                                                                                                                          |

| $t_0$ | SR                            | 500                                          | 2000                                                                                           | ns                                                                                                                                       |

| $t_1$ | CC                            | 0                                            | _                                                                                              | ns                                                                                                                                       |

| $t_2$ | SR                            | 22                                           | _                                                                                              | ns                                                                                                                                       |

| $t_3$ | SR                            | 0                                            | _                                                                                              | ns                                                                                                                                       |

| $t_4$ | SR                            | 2.0                                          | 3.5                                                                                            | μS                                                                                                                                       |

| $t_5$ | SR                            | 0                                            | 2.8                                                                                            | μS                                                                                                                                       |

| $t_6$ | SR                            | 60.7                                         | 65                                                                                             | μS                                                                                                                                       |

|       | $t_0$ $t_1$ $t_2$ $t_3$ $t_4$ | $t_1$ CC $t_2$ SR $t_3$ SR $t_4$ SR $t_5$ SR | $t_0$ SR     500 $t_1$ CC     0 $t_2$ SR     22 $t_3$ SR     0 $t_4$ SR     2.0 $t_5$ SR     0 | min.     max. $t_0$ SR 500 2000     2000 $t_1$ CC 0 —     — $t_2$ SR 22 —     — $t_3$ SR 0 —     — $t_4$ SR 2.0 3.5     — $t_5$ SR 0 2.8 |

<sup>1)</sup> The typical value is based on 8 consecutive 16-bit data transfers per heartbeat, at a baud rate of 2 Mbaud.

Figure 4 SPI Timing

## Package and Quality Declaration

# 3 Package and Quality Declaration

Chapter 3 provides the information of the CIC61508 package and reliability section.

## 3.1 Package Parameters

Table 3 provides the thermal characteristics of the package used in CIC61508.

Table 3 Thermal Characteristics of the Package

| Parameter                                      | Symbol    |           | Lim | nit Values | Unit | Notes |  |

|------------------------------------------------|-----------|-----------|-----|------------|------|-------|--|

|                                                |           | Min. Max. |     | Max.       |      |       |  |

| PG-TSSOP-38                                    |           |           | 1   | 1          |      |       |  |

| Thermal resistance junction case <sup>1)</sup> | $R_{TJC}$ | CC        | -   | 15.7       | K/W  | -     |  |

| Thermal resistance junction lead <sup>1)</sup> | $R_{TJL}$ | CC        | -   | 39.2       | K/W  | -     |  |

<sup>1)</sup> The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  are to be combined with the thermal resistances between the junction and the case  $(R_{TJC})$ , the junction and the lead  $(R_{TJL})$  given above, in order to calculate the total thermal resistance between the junction and the ambient  $(R_{TJA})$ . The thermal resistances between the case and the ambient  $(R_{TCA})$ , the lead and the ambient  $(R_{TLA})$  depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J = T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient, while  $P_D$  is given by the multiplication of the max.  $V_{DDP}$  and max.  $I_{DDP}$ . The total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

## **Package and Quality Declaration**

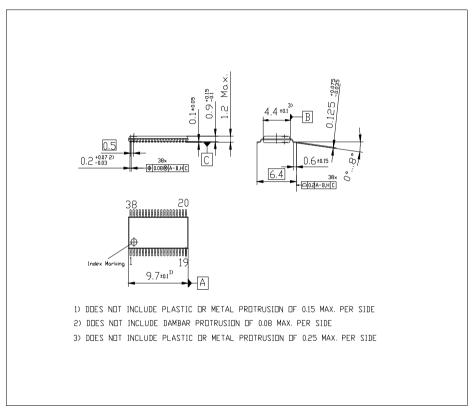

# 3.2 Package Outline

Figure 7 show the package outline of the CIC61508.

Figure 7 PG-TSSOP-38 Package Outline

## **Package and Quality Declaration**

# 3.3 Quality Declaration

Table 4 shows the characteristics of the quality parameters in the CIC61508.

Table 4 Quality Parameters<sup>1)</sup>

| Parameter                                                                                   | Symbol           | Limit | Values |        | Unit  | Notes                                  |  |

|---------------------------------------------------------------------------------------------|------------------|-------|--------|--------|-------|----------------------------------------|--|

|                                                                                             |                  | Min.  | Тур.   | Max.   |       |                                        |  |

| Operation Lifetime when the device is used                                                  | t <sub>OP</sub>  | -     | -      | 1500   | hours | T <sub>A</sub> = 140°C                 |  |

|                                                                                             |                  | -     | -      | 2000   | hours | <i>T</i> <sub>A</sub> = 125°C          |  |

| at the four stated $T_{\rm A}^{\ \ 2)}$                                                     |                  | -     | -      | 10000  | hours | <i>T</i> <sub>A</sub> = 85°C           |  |

|                                                                                             |                  | -     | -      | 1500   | hours | <i>T</i> <sub>A</sub> = -40°C          |  |

| Operation Lifetime                                                                          | t <sub>OP2</sub> | -     | -      | 18000  | hours | $T_{\rm A} = 108^{\circ}{\rm C}$       |  |

| when the device is used at the two stated $T_{\rm A}^{\ 2)}$                                |                  | -     | -      | 130000 | hours | T <sub>A</sub> = 27°C                  |  |

| Weighted Average<br>Temperature <sup>3)</sup>                                               | $T_{WA}$         | -     | 106    | -      | °C    | For 15000 hours                        |  |

| ESD susceptibility according to Human Body Model (HBM) for all pins (except $V_{\rm DDC}$ ) | $V_{HBM}$        | -     | -      | 2000   | V     | Conforming to<br>EIA/JESD22-<br>A114-B |  |

| ESD susceptibility according to Human Body Model (HBM) for $V_{\mathrm{DDC}}$               | $V_{HBMC}$       |       |        | 600    |       | Conforming to<br>EIA/JESD22-<br>A114-B |  |

| ESD susceptibility<br>according to Charged<br>Device Model (CDM)<br>pins                    | $V_{CDM}$        | -     | -      | 750    | V     | Conforming to JESD22-C101-C            |  |

<sup>1)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

<sup>2)</sup> This lifetime refers only to the time when the device is powered-on.

<sup>3)</sup> This parameter is derived based on the Arrhenius model.

www.infineon.com

Published by Infineon Technologies AG