### ISL9122A

Ultra-Low Io Buck-Boost Regulator With Bypass

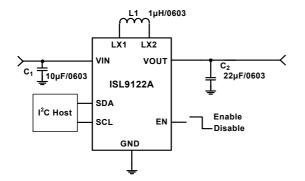

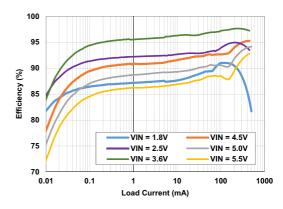

The ISL9122A is a highly integrated non-inverting buck-boost switching regulator that accepts input voltages both above or below the regulated output voltage. It features an extremely low quiescent current consumption of 1300nA in Regulation mode, 120nA in Forced Bypass mode, and 8nA in Shutdown mode. It provides 84% efficiency at  $10\mu A \log (V_{IN} = 3.6V)$ , V<sub>OUT</sub> = 3.3V) and has peak efficiency greater than 97% ( $V_{IN} = 3.6V$ ,  $V_{OLIT} = 3.3V$ ). It supports input voltages from 1.8V to 5.5V.

The ISL9122A has automatic bypass functionality for situations in which the input voltage is close to the output voltage, and it automatically transitions between Buck and Boost modes without significant output disturbance. In addition to the automatic bypass functionality, the Forced Bypass power saving mode can be chosen if voltage regulation is not required. Forced Bypass power saving mode is accessible using the I<sup>2</sup>C interface bus.

The ISL9122A is capable of delivering up to 500mA of output current (V<sub>IN</sub> > V<sub>OUT</sub> > 2.5V) and provides excellent efficiency because of its adaptive frequency hysteretic control architecture.

The ISL9122A is designed for stand-alone applications and supports a default output voltage at Power-On Reset (POR). After POR, the output voltage can be adjusted in the range of 1.8V to 5.375V by using the I<sup>2</sup>C interface bus. Specific default output voltages are available upon request.

The ISL9122A requires only a single EIA 0603 size inductor and a minimum of two external capacitors. Power supply solution size is minimized by a 1.8mmx1.0mm 8 Bump WLCSP and it is also available in a 3.0mmx2.0mm 8 Ld plastic DFN.

Figure 1. Typical Application (Minimum Derated  $C_2 = 6\mu F$ )

FN8947 Rev.1.01

Mar 17, 2022

#### **Features**

- · 1300nA quiescent current

- 84% efficiency at 10µA load (V<sub>IN</sub> = 3.6V,  $V_{OUT} = 3.3V$

- 97% peak efficiency (V<sub>IN</sub> = 3.6V, V<sub>OUT</sub> = 3.3V)

- · Input voltage range: 1.8V to 5.5V

- Output voltage range: 1.8V to 5.375V

- Output current: up to 500mA (V<sub>IN</sub> > V<sub>OUT</sub> > 2.5V)

- · Selectable Forced and Auto Bypass power saving modes

- Seamless PWM/PFM and buck/boost transition

- I<sup>2</sup>C control and voltage adjustability

- · Hysteretic controller

- Small 1.8mmx1.0mm 8 Bump WLCSP and 3.0mm x 2.0mm 8 Ld DFN packages

### Applications

- · Smart watches and wristband devices

- · Wireless earphones

- Internet of Things (IoT) devices

- · Water, gas, and oil meters

- · Portable medical devices

- · Hearing aid devices

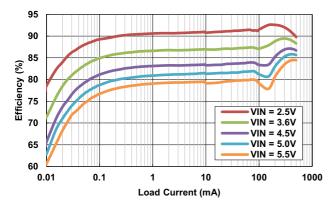

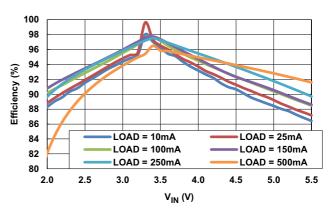

Figure 2. Efficiency vs Load Current: V<sub>OUT</sub> = 3.3V,  $T_{\Delta} = +25^{\circ}C$

## **Contents**

| 1.   | Overview                                                 | 3  |

|------|----------------------------------------------------------|----|

| 1.1  | Block Diagram                                            | 3  |

| 1.2  | Ordering Information                                     | 4  |

| 2.   | Pin Information                                          | Ę  |

| 2.1  | Pin Assignments                                          | 5  |

| 2.2  | Pin Descriptions                                         | 5  |

| 3.   | Specifications                                           | 6  |

| 3.1  | Absolute Maximum Ratings                                 | 6  |

| 3.2  | Thermal Information                                      | 6  |

| 3.3  | Recommended Operating Conditions                         | 6  |

| 3.4  | Analog Specifications                                    | 7  |

| 3.5  | I <sup>2</sup> C Interface Timing Specifications         | 8  |

| 4.   | Typical Performance Graphs                               | 10 |

| 4.1  | Line/Load Transient Waveforms                            | 15 |

| 5.   | Functional Description                                   | 19 |

| 5.1  | Enable Input                                             | 19 |

| 5.2  | Soft Discharge                                           | 19 |

| 5.3  | Start-Up 1                                               | 19 |

| 5.4  | Overcurrent/Short-Circuit Protection                     | 19 |

| 5.5  | Thermal Shutdown                                         | 19 |

| 5.6  | Buck-Boost Conversion Topology                           | 19 |

| 5.7  | Pulse Width Modulation (PWM) Operation                   | 20 |

| 5.8  | Pulse Frequency Modulation (PFM) Operation               | 20 |

| 5.9  | Operation With V <sub>IN</sub> Close to V <sub>OUT</sub> | 21 |

| 5.10 | D Forced Operating Modes                                 | 21 |

| 5.1  |                                                          |    |

| 5.12 |                                                          |    |

| 5.13 | '                                                        |    |

| 5.14 | -1                                                       |    |

| 5.1  | 5 Register Descriptions                                  | 24 |

| 6.   | Revision History                                         | 26 |

| 7.   | Package Outline Drawings                                 | 27 |

ISL9122A 1. Overview

## 1. Overview

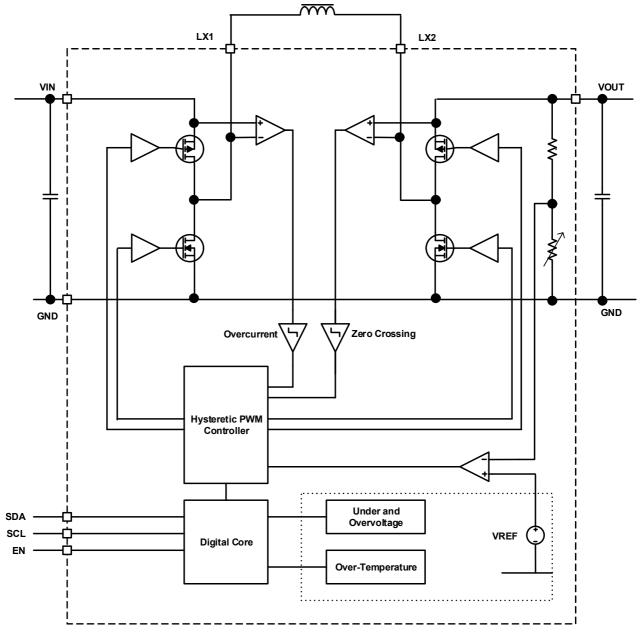

## 1.1 Block Diagram

Figure 3. Block Diagram

ISL9122A 1. Overview

## 1.2 Ordering Information

| Part Number (Note 4)      | Part<br>Marking                   | Default<br>V <sub>OUT</sub> (V) | I <sup>2</sup> C<br>Address | Package Description (RoHS Compliant) | Pkg.<br>Dwg. # | Carrier Type<br>(Note 1) | Temp Range   |

|---------------------------|-----------------------------------|---------------------------------|-----------------------------|--------------------------------------|----------------|--------------------------|--------------|

| ISL9122AIINZ-T (Note 2)   | 122A                              | 3.3V                            | 0x18                        | 8 Bump WLCSP                         | W2x4.8         | Reel, 3k                 | -40 to +85°C |

| ISL9122AIINZ-T7A (Note 2) |                                   |                                 |                             |                                      |                | Reel, 250                |              |

| ISL9122AIRNZ-T (Note 3)   | A22 3.3\                          |                                 |                             | 8 Ld DFN                             | L8.2x3         | Reel, 6k                 |              |

| ISL9122AIRNZ-T7A (Note 3) |                                   |                                 |                             |                                      |                | Reel, 250                |              |

| ISL9122AIIN-EVZ           | Evaluation Board for ISL9122AIINZ |                                 |                             |                                      |                |                          |              |

| ISL9122AIRN-EVZ           | Evaluation                        | n Board for                     | ISL9122AI                   | RNZ                                  |                |                          |              |

#### Notes:

- 1. See <u>TB347</u> for details about reel specifications.

- These Pb-free WLCSP packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAgCu - e1 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Pb-free WLCSP packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 3. These Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J-STD-020.

- 4. For Moisture Sensitivity Level (MSL), see the ISL9122A device page. For more information on MSL, see TB363.

ISL9122A 2. Pin Information

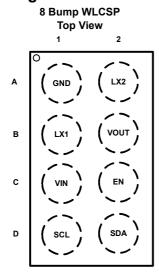

## 2. Pin Information

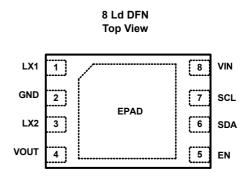

## 2.1 Pin Assignments

## 2.2 Pin Descriptions

| WLCSP Pin # | DFN Pin # | Pin Names | Description                                                                              |

|-------------|-----------|-----------|------------------------------------------------------------------------------------------|

| B2          | 4         | VOUT      | Buck-boost output                                                                        |

| A2          | 3         | LX2       | Inductor connection, output side                                                         |

| A1          | 2         | GND       | Ground connection                                                                        |

| B1          | 1         | LX1       | Inductor connection, input side                                                          |

| C1          | 8         | VIN       | Power supply input                                                                       |

| C2          | 5         | EN        | Logic input, drive HIGH to enable device. Do not leave floating.                         |

| D2          | 6         | SDA       | I <sup>2</sup> C data input. Pull down to GND if not being used. Do not leave floating.  |

| D1          | 7         | SCL       | I <sup>2</sup> C clock input. Pull down to GND if not being used. Do not leave floating. |

| N/A         | 9         | EPAD      | Exposed Pad. Must be soldered to PCB GND.                                                |

## 3. Specifications

## 3.1 Absolute Maximum Ratings

**CAUTION:** Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

| Parameter                                       | Minimum | Maximum | Unit |

|-------------------------------------------------|---------|---------|------|

| VIN, VOUT                                       | -0.3    | 6.5     | V    |

| LX1, LX2                                        | -0.3    | 6.5     | V    |

| LX1, LX2 (less than 10ns)                       | -2.0    | 8.0     | V    |

| All Other Pins                                  | -0.3    | 6.5     | V    |

| ESD Rating                                      | Va      | Unit    |      |

| Human Body Model (Tested per JS-001-2017)       | 2       | 2       | kV   |

| Charged Device Model (Tested per JS-002-2018)   | ,       | 1       | kV   |

| Latch-Up (Tested per JESD78E; Class 2, Level A) | 10      | 00      | mA   |

### 3.2 Thermal Information

| Thermal Resistance (Typical)      | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) | θ <sub>JB</sub> (°C/W) |

|-----------------------------------|------------------------|------------------------|------------------------|

| 8 Bump WLCSP Package (Notes 5, 6) | 110                    | -                      | 28                     |

| 8 Ld 2x3 DFN Package (Notes 5, 7) | 72                     | 21                     | -                      |

#### Notes:

<sup>7.</sup> For  $\theta_{JC}$ , the case temperature location is the center of the exposed metal pad on the package underside. See <u>TB379</u>.

| Parameter                    | Minimum | Maximum          | Unit |

|------------------------------|---------|------------------|------|

| Maximum Junction Temperature |         | +125             | °C   |

| Storage Temperature Range    | -65     | +150             | °C   |

| Pb-Free Reflow Profile       |         | see <u>TB493</u> |      |

## 3.3 Recommended Operating Conditions

| Parameter                                        | Minimum | Maximum              | Unit |

|--------------------------------------------------|---------|----------------------|------|

| Ambient Temperature (T <sub>A</sub> ) Range      | -40     | +85                  | °C   |

| Supply Voltage (V <sub>IN</sub> ) Range          | 1.8     | 5.5                  | V    |

| Output Voltage (V <sub>OUT</sub> ) Range         | 1.8     | 5.375                | V    |

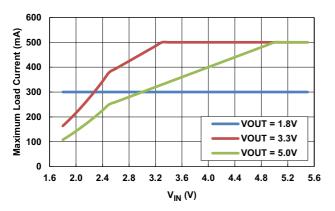

| Load Current (I <sub>OUT</sub> ) Range (DC)      | 0       | See <u>Figure 16</u> | mA   |

| Effective Output Capacitance (C <sub>OUT</sub> ) | 6       |                      | μF   |

| Effective Input Capacitance (C <sub>IN</sub> )   | 5       |                      | μF   |

<sup>5.</sup> θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with direct attach features. See TB379

<sup>6.</sup> For  $\theta_{JB}$ , the board temperature is taken on the board near the edge of the package, on a copper trace at the center of one side.

## 3.4 Analog Specifications

$V_{IN} = V_{EN} = 3.6 \text{V}, V_{OUT} = 3.3 \text{V}, I^2 \text{C}$  pull-up voltage = 3.6 V,  $L_1 = 1 \mu \text{H}, C_1 = 10 \mu \text{F}, C_2 = C_{OUT}$  (Effective) =  $6 \mu \text{F}, T_A = +25 ^{\circ} \text{C}$ . Boldface limits apply across the recommended operating temperature range (-40  $^{\circ} \text{C}$  to +85  $^{\circ} \text{C}$ ) and input voltage range (1.8V to 5.5V), unless specified otherwise.

| Parameter                                                                                              | Symbol               | Test Conditions                                                                                                           | Min<br>( <u>Note 8</u> ) | Тур                       | Max<br>( <u>Note 8</u> ) | Unit  |

|--------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|--------------------------|-------|

| Power Supply                                                                                           |                      |                                                                                                                           |                          |                           |                          |       |

| Input Voltage Range                                                                                    | V <sub>IN</sub>      |                                                                                                                           | 1.8                      |                           | 5.5                      | V     |

| V <sub>IN</sub> Undervoltage Lockout<br>Threshold                                                      | V <sub>UVLO</sub>    | V <sub>IN</sub> Rising                                                                                                    |                          |                           | 1.79                     | V     |

| V <sub>UVLO</sub> Hysteresis                                                                           | HYST <sub>UVLO</sub> |                                                                                                                           |                          | 40                        |                          | mV    |

| V <sub>IN</sub> Quiescent Current                                                                      | ΙQ                   | V <sub>IN</sub> = 3.6V, I <sub>OUT</sub> = 0A ( <u>Note 9</u> )                                                           |                          | 1300                      | 1800                     | nA    |

| V <sub>IN</sub> Supply Current, Shutdown                                                               | I <sub>SD</sub>      | V <sub>IN</sub> = 3.6V, V <sub>EN</sub> pulled to GND                                                                     |                          | 8                         | 450                      | nA    |

| V <sub>IN</sub> Supply Current, Soft<br>Shutdown                                                       | I <sub>SSD</sub>     | V <sub>IN</sub> = 3.6V, Shutdown using I <sup>2</sup> C register.<br>EN_AND = CONV_CFG[7] = 0                             |                          | 40                        | 450                      | nA    |

| V <sub>IN</sub> Supply Current, Forced<br>Bypass Mode                                                  | I <sub>BYP</sub>     | V <sub>IN</sub> = 3.6V, I <sub>OUT</sub> = 0A. Forced Bypass using I <sup>2</sup> C register. FMODE = CONV_CFG[3:2] = 0x3 |                          | 120                       | 850                      | nA    |

| Output Voltage Regulation                                                                              |                      |                                                                                                                           |                          |                           | •                        |       |

| Output Voltage Range                                                                                   | V <sub>OUT</sub>     | 1.8V < V <sub>IN</sub> < 5.5V, I <sub>OUT</sub> = 1mA                                                                     | 1.8                      |                           | 5.375                    | V     |

| Output Voltage Accuracy                                                                                |                      |                                                                                                                           |                          |                           |                          |       |

| ISL9122AIINZ, ISL9122AIRNZ                                                                             | V <sub>OUT_ACC</sub> | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 3.3V, I <sub>OUT</sub> = 0A, forced PWM                                        | -2.5                     |                           | +2.5                     | %     |

|                                                                                                        |                      | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 3.3V, I <sub>OUT</sub> = 1mA, PFM                                              | -3.6                     |                           | +3.6                     | %     |

| Soft-Start and Soft Discharge                                                                          |                      |                                                                                                                           |                          |                           | •                        |       |

| Time to Read OTP                                                                                       | t <sub>OTP</sub>     | Time from when V <sub>IN</sub> > V <sub>UVLO</sub> and EN signal asserts until switching starts                           |                          | 125                       |                          | μs    |

| V <sub>OUT</sub> Ramp Rate for Soft-Start                                                              | DVSRATE              | Default at POR                                                                                                            |                          | 3.125                     |                          | mV/μs |

| and During Dynamic Voltage<br>Scaling (applicable only for V <sub>OUT</sub><br>ramp-up, not ramp-down) |                      | Programmable using I <sup>2</sup> C after POR                                                                             |                          | 6.25<br>0.78125<br>1.5625 |                          | mV/μs |

| V <sub>OUT</sub> Soft Discharge ON-<br>Resistance                                                      | r <sub>DISCHG</sub>  | V <sub>EN</sub> pulled to GND                                                                                             |                          | 160                       |                          | Ω     |

| Power MOSFET (WLCSP Packa                                                                              | ge)                  |                                                                                                                           |                          |                           | l                        |       |

| P-Channel MOSFET<br>ON-Resistance (Buck)                                                               | r <sub>DSON_A</sub>  | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 3.6V                                                                           |                          | 52                        |                          | mΩ    |

| N-Channel MOSFET<br>ON-Resistance (Buck)                                                               | r <sub>DSON_B</sub>  |                                                                                                                           |                          | 50                        |                          | mΩ    |

| P-Channel MOSFET<br>ON-Resistance (Boost)                                                              | r <sub>DSON_D</sub>  |                                                                                                                           |                          | 55                        |                          | mΩ    |

| N-Channel MOSFET<br>ON-Resistance (Boost)                                                              | r <sub>DSON_C</sub>  |                                                                                                                           |                          | 51                        |                          | mΩ    |

| Power MOSFET (DFN Package)                                                                             |                      | ,                                                                                                                         |                          |                           |                          |       |

| P-Channel MOSFET ON-<br>Resistance (Buck)                                                              | r <sub>DSON_A</sub>  | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 3.6V                                                                           |                          | 52                        |                          | mΩ    |

| N-Channel MOSFET ON-<br>Resistance (Buck)                                                              | r <sub>DSON_B</sub>  |                                                                                                                           |                          | 51                        |                          | mΩ    |

| P-Channel MOSFET ON-<br>Resistance (Boost)                                                             | r <sub>DSON_D</sub>  |                                                                                                                           |                          | 54                        |                          | mΩ    |

| N-Channel MOSFET ON-<br>Resistance (Boost)                                                             | r <sub>DSON_C</sub>  |                                                                                                                           |                          | 51                        |                          | mΩ    |

| Bypass Mode                                                                                            |                      |                                                                                                                           |                          |                           |                          |       |

$V_{IN} = V_{EN} = 3.6 \text{V}$ ,  $V_{OUT} = 3.3 \text{V}$ ,  $I^2\text{C}$  pull-up voltage = 3.6 V,  $L_1 = 1 \mu\text{H}$ ,  $C_1 = 10 \mu\text{F}$ ,  $C_2 = C_{OUT}$  (Effective) =  $6 \mu\text{F}$ ,  $T_A = +25 ^{\circ}\text{C}$ . Boldface limits apply across the recommended operating temperature range (-40  $^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ) and input voltage range (1.8V to 5.5V), unless specified otherwise. (Continued)

| Parameter                   | Symbol                | Test Conditions                                                          | Min<br>( <u>Note 8</u> ) | Тур                        | Max<br>(Note 8) | Unit |

|-----------------------------|-----------------------|--------------------------------------------------------------------------|--------------------------|----------------------------|-----------------|------|

| Auto Bypass Thresholds      | V <sub>IN_BYP</sub>   | Auto bypass thresholds - input voltage range. I <sub>OUT</sub> = 10mA    |                          | ±1% V <sub>OUT</sub>       |                 | V    |

| Inductor Peak Current Limit |                       |                                                                          |                          |                            |                 |      |

| Peak Current Limit          | I <sub>LIM</sub>      | 2.5V < V <sub>IN</sub> < 5.5V                                            |                          | 2.5                        |                 | Α    |

|                             |                       | 1.8V < V <sub>IN</sub> < 2.5V                                            |                          | 2.5*(V <sub>IN</sub> /2.5) |                 | Α    |

| Efficiency                  |                       |                                                                          |                          |                            |                 |      |

| Efficiency                  | η                     | I <sub>OUT</sub> = 50mA, V <sub>IN</sub> = 3.7V, V <sub>OUT</sub> = 3.3V |                          | 97                         |                 | %    |

|                             |                       | I <sub>OUT</sub> = 10μA, V <sub>IN</sub> = 3.7V, V <sub>OUT</sub> = 3.3V |                          | 84                         |                 | %    |

| Switching Frequency         |                       |                                                                          |                          |                            |                 |      |

| Switching Frequency         | f <sub>SW</sub>       | $V_{IN}$ = 3.6V, $V_{OUT}$ = 1.8V, $I_{OUT}$ = 1mA, Forced PWM           |                          | 2.5                        |                 | MHz  |

| Hiccup Mode                 | •                     |                                                                          | •                        |                            |                 |      |

| Hiccup Time                 | t <sub>FLT_WAIT</sub> | Time from OCP shutdown to restart                                        |                          | 100                        |                 | ms   |

| Thermal Protection          | •                     |                                                                          | •                        |                            |                 |      |

| Thermal Shutdown Threshold  | T <sub>SD</sub>       | Rising Temperature                                                       |                          | 130                        |                 | °C   |

| Thermal Shutdown Hysteresis | T <sub>SD_HYS</sub>   |                                                                          |                          | 25                         |                 | °C   |

| Logic Levels                |                       |                                                                          |                          |                            |                 |      |

| Input Leakage               | I <sub>LEAK</sub>     | EN pin                                                                   |                          | 9                          | 300             | nA   |

|                             |                       | SCL pin                                                                  |                          | 8                          | 300             | nA   |

|                             |                       | SDA pin                                                                  |                          | 8                          | 300             | nA   |

| EN Input HIGH Voltage       | EN <sub>IH</sub>      | V <sub>IN</sub> = 3.6V                                                   | 1.6                      |                            |                 | V    |

| EN Input LOW Voltage        | EN <sub>IL</sub>      |                                                                          |                          |                            | 0.36            | V    |

| SCL/SDA Input HIGH Voltage  | SCL/SDA <sub>IH</sub> |                                                                          | 1.45                     |                            |                 | V    |

| SCL/SDA Input LOW Voltage   | SCL/SDA <sub>IL</sub> |                                                                          |                          |                            | 0.36            | V    |

#### Notes:

- 8. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 9. Quiescent current measurements are taken when the device is not switching.

## 3.5 I<sup>2</sup>C Interface Timing Specifications

Applicable to SCL and SDA in the Fast mode I<sup>2</sup>C operation, unless otherwise specified.

| Parameter                                          | Symbol              | Test Conditions                                                                                                          | Min<br>( <u>Note 10</u> ) | Тур | Max<br>( <u>Note 10</u> ) | Unit |

|----------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| I <sup>2</sup> C Frequency Capability              | f <sub>I2C</sub>    |                                                                                                                          | 0                         |     | 400                       | kHz  |

| Pulse Width Suppression Time at SDA and SCL Inputs | t <sub>SP</sub>     | Any pulse narrower than the maximum specification is suppressed                                                          |                           |     | 50                        | ns   |

| Data Valid Time                                    | t <sub>VD;DAT</sub> | Time from SCL falling edge crossing $SCL_{IL}$ to SDA exiting the $SDA_{IL}$ to $SDA_{IH}$ window                        |                           |     | 900                       | ns   |

| Data Valid Acknowledge Time                        | t <sub>VD;ACK</sub> | Time from SCL falling edge crossing $SCL_{IL}$ to SDA exiting the $SDA_{IL}$ to $SDA_{IH}$ window, during acknowledgment |                           |     | 900                       | ns   |

| Bus Free Time Between a STOP and START Condition   | t <sub>BUF</sub>    | Time from SDA crossing SDA <sub>IH</sub> at STOP to SDA crossing SDA <sub>IH</sub> at the following START                | 1300                      |     |                           | ns   |

| SCL Low Time                                       | t <sub>LOW</sub>    | Measured at the SCL <sub>IL</sub> crossing                                                                               | 1300                      |     |                           | ns   |

Applicable to SCL and SDA in the Fast mode I<sup>2</sup>C operation, unless otherwise specified. (Continued)

| Parameter                   | Symbol              | Test Conditions                                                                                                          | Min<br>( <u>Note 10</u> ) | Тур | Max<br>( <u>Note 10</u> ) | Unit |

|-----------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| SCL High Time               | t <sub>HIGH</sub>   | Measured at the SCL <sub>IH</sub> crossing                                                                               | 600                       |     |                           | ns   |

| START Condition Set-Up Time | t <sub>SU;STA</sub> | Time from SCL rising edge crossing SCL <sub>IH</sub> to SDA falling edge crossing SDA <sub>IH</sub>                      | 600                       |     |                           | ns   |

| START Condition Hold Time   | t <sub>HD;STA</sub> | Time from SDA falling edge crossing SDA $_{\rm IL}$ to SCL falling edge crossing SCL $_{\rm IH}$                         | 600                       |     |                           | ns   |

| Data Set-Up Time            | t <sub>SU;DAT</sub> | Time from SDA exiting the SDA $_{\rm IL}$ to SDA $_{\rm IH}$ window to SCL rising edge crossing SCL $_{\rm IL}$          | 100                       |     |                           | ns   |

| Data Hold Time              | t <sub>HD;DAT</sub> | Time from SCL falling edge crossing SCL $_{\rm IL}$ to SDA entering the SDA $_{\rm IL}$ to SDA $_{\rm IL}$ window        | 50                        |     |                           | ns   |

| STOP Condition Set-Up Time  | t <sub>SU;STO</sub> | Time from SCL rising edge crossing $\mathrm{SCL}_{\mathrm{IH}}$ to SDA rising edge crossing $\mathrm{SDA}_{\mathrm{IL}}$ | 600                       |     |                           | ns   |

| SCL/SDA Capacitive Loading  | C <sub>b</sub>      | Capacitive load for each bus line                                                                                        |                           |     | 400                       | pF   |

#### Note:

10. Limits established by design and are not production tested.

## 4. Typical Performance Graphs

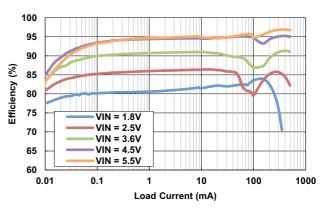

Figure 4. Efficiency vs Load Current: V<sub>OUT</sub> = 1.8V

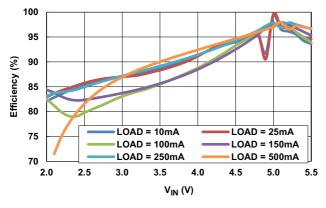

Figure 5. Efficiency vs Load Current: V<sub>OUT</sub> = 5.0V

Figure 6. Efficiency vs Input Voltage: V<sub>OUT</sub> = 1.8V

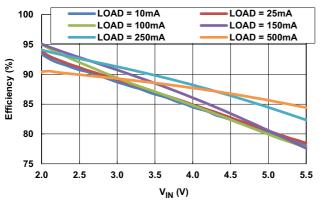

Figure 7. Efficiency vs Input Voltage: V<sub>OUT</sub> = 3.3V

Figure 8. Efficiency vs Input Voltage: V<sub>OUT</sub> = 5V

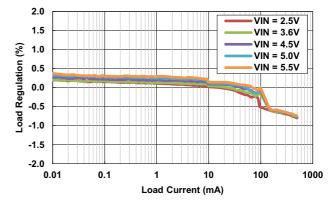

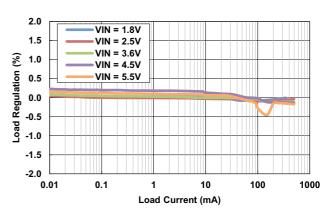

Figure 9. Output Voltage Accuracy vs Load Current: V<sub>OUT</sub> = 1.8V

Figure 10. Output Voltage Accuracy vs Load Current: V<sub>OUT</sub> = 3.3V

Figure 11. Output Voltage Accuracy vs Load Current:  $V_{OUT} = 5V$

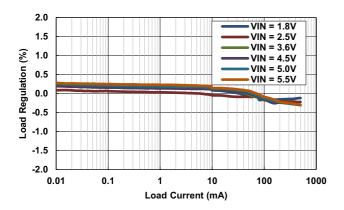

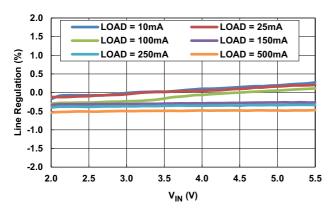

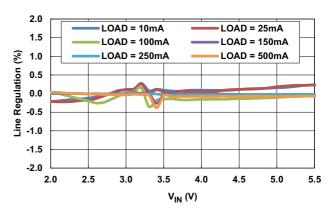

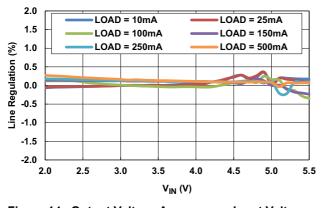

Figure 12. Output Voltage Accuracy vs Input Voltage:  $V_{OUT} = 1.8V$

Figure 13. Output Voltage Accuracy vs Input Voltage: V<sub>OUT</sub> = 3.3V

Figure 14. Output Voltage Accuracy vs Input Voltage:  $V_{OUT} = 5V$

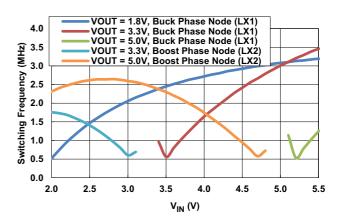

Figure 15. Switching Frequency vs Input Voltage: LOAD = 0mA, Forced PWM

Figure 16. Maximum Load Current vs Input Voltage

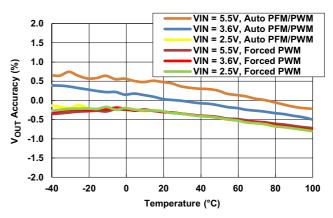

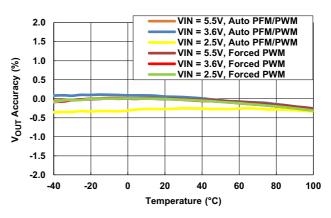

Figure 17. Output Voltage Accuracy vs Temperature: V<sub>SET</sub> = 1.8V, LOAD = 25mA

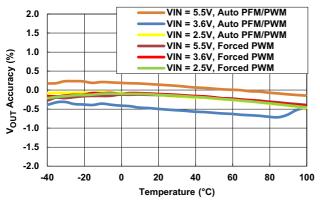

Figure 18. Output Voltage Accuracy vs Temperature: V<sub>SET</sub> = 3.3V, LOAD = 25mA

Figure 19. Output Voltage Accuracy vs Temperature: V<sub>SET</sub> = 5V, LOAD = 25mA

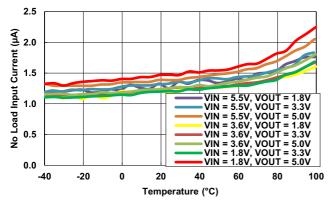

Figure 20. Quiescent Current vs Temperature

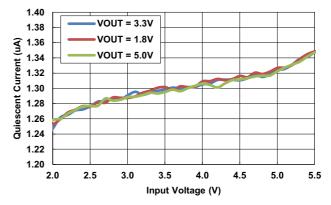

Figure 21. Quiescent Current vs Input Voltage

V<sub>OUT</sub> (1V/Div)

V<sub>IN</sub> (2V/Div)

4

40ms/Div

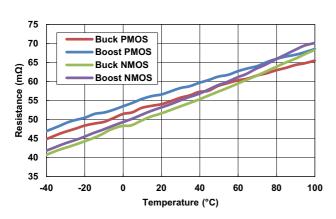

Figure 22. Switch Resistance vs Temperature

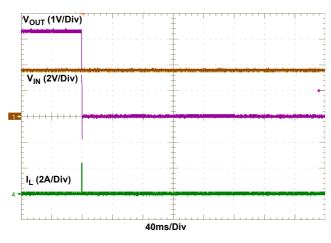

Figure 23. Output Short-Circuit Behavior (Hiccup Mode)

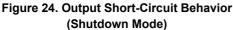

Figure 25. Output Short-Circuit Behavior (Current Limit Mode)

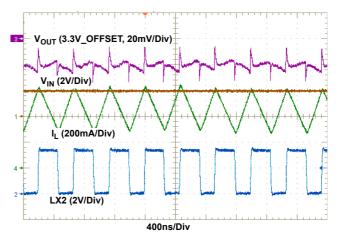

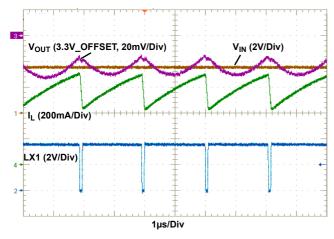

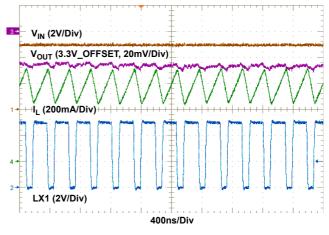

Figure 26. Steady-State Operation in PFM:  $V_{IN}$  = 2.0V,  $V_{OUT}$  = 3.3V, No Load

Figure 27. Steady-State Operation in PFM:  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 3.3V, No Load

Figure 28. Steady-State Operation in PFM:  $V_{IN}$  = 5.0V,  $V_{OUT}$  = 3.3V, No Load

Figure 29. Steady-State Operation in PWM:  $V_{IN}$  = 2.0V,  $V_{OUT}$  = 3.3V, 200mA

Figure 30. Steady-State Operation in PWM:  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 3.3V, 500mA

Figure 31. Steady-State Operation in PWM:  $V_{IN}$  = 5.0V,  $V_{OUT}$  = 3.3V, 500mA

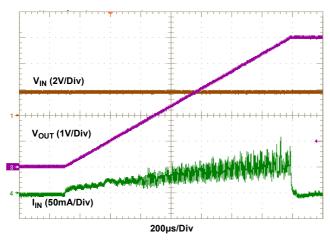

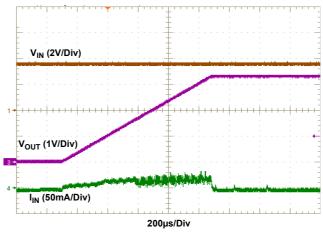

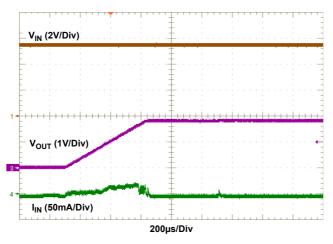

Figure 32. Soft-Start:  $V_{IN}$  = 1.8V,  $V_{SET}$  = 5.0V, No Load

Figure 33. Soft-Start:  $V_{IN}$  = 3.6V,  $V_{SET}$  = 3.3V, No Load

Figure 34. Soft-Start:  $V_{IN}$  = 5.5V,  $V_{SET}$  = 1.8V, No Load

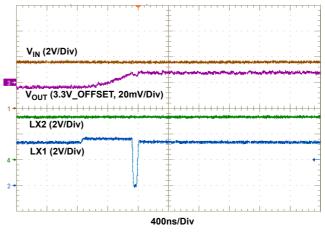

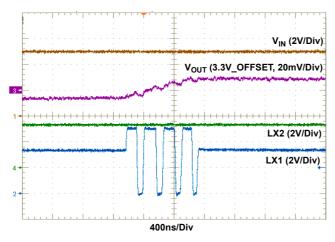

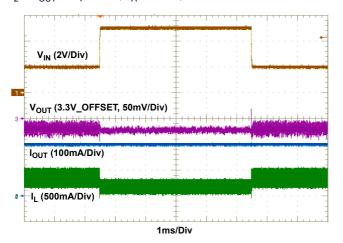

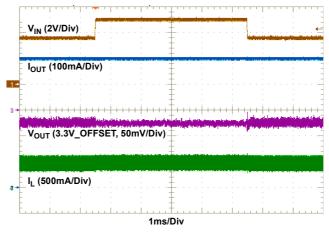

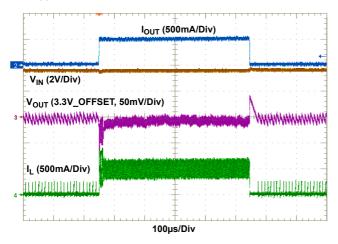

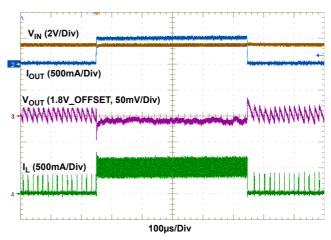

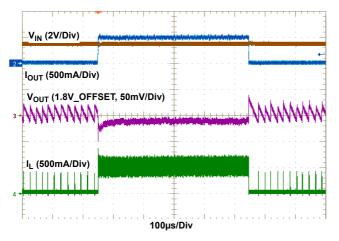

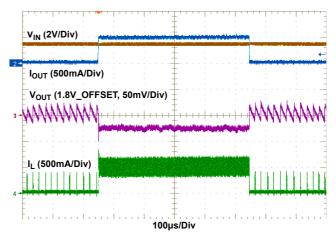

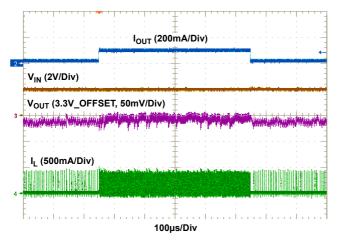

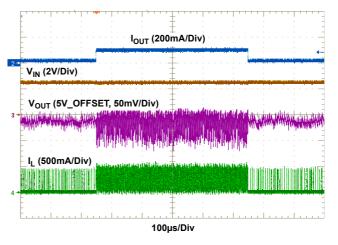

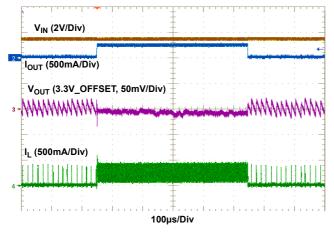

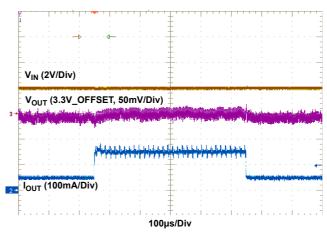

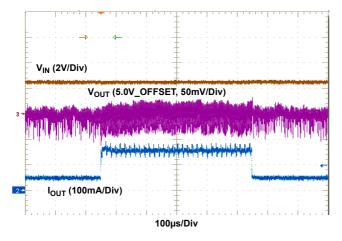

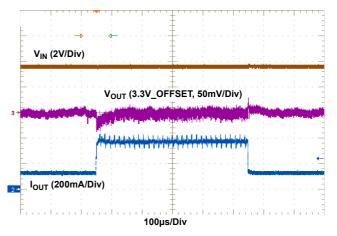

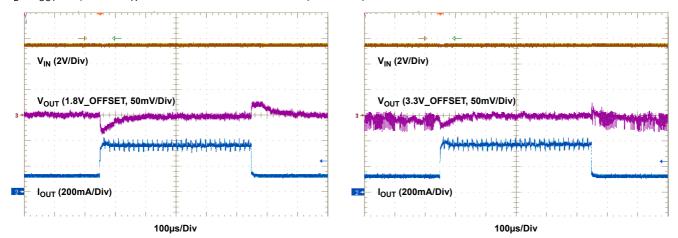

#### 4.1 Line/Load Transient Waveforms

$V_{IN} = V_{EN} = 3.6 \text{V}, V_{OUT} = 3.3 \text{V}, I^2 \text{C pull-up voltage} = 3.6 \text{V}, \text{Type II Error Amplifier L1} = 1 \mu \text{H}/0603, C_1 = C_{IN} = 10 \mu \text{F}/0603, C_2 = C_{OUT} = 22 \mu \text{F}/0603, T_A = +25 ^{\circ} \text{C}, \text{ unless otherwise stated.}$

Figure 35. Line Transient:  $V_{IN}$  = 2.0V to 5.0V, Slew Rate = 0.5V/ $\mu$ s,  $V_{OUT}$  = 3.3V, Load = 200mA

Figure 36. Line Transient:  $V_{IN}$  = 3.6V to 5.0V, Slew Rate = 0.5V/ $\mu$ s,  $V_{OUT}$  = 3.3V, Load = 500mA

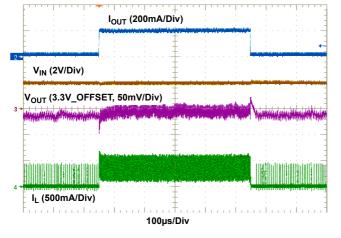

Figure 37. Load Transient:  $V_{IN}$  = 2.0V,  $V_{OUT}$  = 3.3V, Load = 0.01A to 0.20A, Slew Rate = 1A/ $\mu$ s

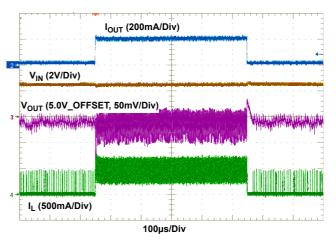

Figure 38. Load Transient:  $V_{IN}$  = 2.5V,  $V_{OUT}$  = 5.0V, Load = 0.01A to 0.20A, Slew Rate = 1A/ $\mu$ s

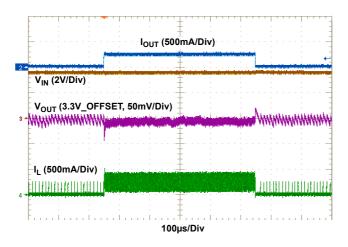

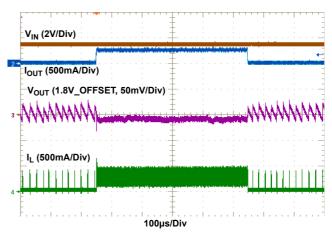

$V_{IN} = V_{EN} = 3.6 \text{V}, V_{OUT} = 3.3 \text{V}, I^2\text{C pull-up voltage} = 3.6 \text{V}, \text{Type II Error Amplifier L1} = 1 \mu\text{H}/0603, C_1 = C_{IN} = 10 \mu\text{F}/0603, C_2 = C_{OUT} = 22 \mu\text{F}/0603, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise stated.}$  (Continued)

Figure 39. Load Transient:  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 3.3V, Load = 0.01A to 0.50A, Slew Rate = 1A/ $\mu$ s

Figure 40. Load Transient:  $V_{IN}$  = 5.5V,  $V_{OUT}$  = 3.3V, Load = 0.01A to 0.50A, Slew Rate = 1A/ $\mu$ s

Figure 41. Load Transient:  $V_{IN}$  = 5.5V,  $V_{OUT}$  = 1.8V, Load = 0.01A to 0.50A, Slew Rate = 1A/ $\mu$ s

Figure 42. Load Transient:  $V_{IN}$  = 5.5V,  $V_{OUT}$  = 1.8V, Load = 0.01A to 0.50A, Slew Rate = 1A/ $\mu$ s

Figure 43. Load Transient:  $V_{IN}$  = 2.0V,  $V_{OUT}$  = 3.3V, Load = 0.01A to 0.10A, Slew Rate = 1A/ $\mu$ s

Figure 44. Load Transient:  $V_{IN}$  = 2.5V,  $V_{OUT}$  = 5.0V, Load = 0.01A to 0.10A, Slew Rate = 1A/ $\mu$ s

$V_{IN} = V_{EN} = 3.6 \text{V}, V_{OUT} = 3.3 \text{V}, I^2 \text{C pull-up voltage} = 3.6 \text{V}, \text{Type II Error Amplifier L1} = 1 \mu \text{H}/0603, C_1 = C_{IN} = 10 \mu \text{F}/0603, C_2 = C_{OUT} = 22 \mu \text{F}/0603, T_A = +25 ^{\circ} \text{C}, \text{ unless otherwise stated.}$

Figure 45. Load Transient:  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 3.3V, Load = 0.01A to 0.25A, Slew Rate = 1A/ $\mu$ s

Figure 46. Load Transient:  $V_{IN}$  = 5.5V,  $V_{OUT}$  = 1.8V, Load = 0.01A to 0.25A, Slew Rate = 1A/ $\mu$ s

Figure 47. Load Transient:  $V_{IN}$  = 5.5V,  $V_{OUT}$  = 3.3V, Load = 0.01A to 0.25A, Slew Rate = 1A/ $\mu$ s

Figure 48. Load Transient:  $V_{IN}$  = 2.0V,  $V_{OUT}$  = 3.3V, Load = 0.05A to 0.15A, Slew Rate = 1A/ $\mu$ s

Figure 49. Load Transient:  $V_{IN}$  = 2.5V,  $V_{OUT}$  = 5.0V, Load = 0.05A to 0.15A, Slew Rate = 1A/ $\mu$ s

Figure 50. Load Transient:  $V_{IN}$  = 3.6V,  $V_{OUT}$  = 3.3V, Load = 0.125A to 0.375A, Slew Rate = 1A/ $\mu$ s

$V_{IN} = V_{EN} = 3.6 \text{V}, V_{OUT} = 3.3 \text{V}, I^2 \text{C pull-up voltage} = 3.6 \text{V}, \text{Type II Error Amplifier L1} = 1 \mu \text{H}/0603, C_1 = C_{IN} = 10 \mu \text{F}/0603, C_2 = C_{OUT} = 22 \mu \text{F}/0603, T_A = +25 ^{\circ} \text{C}, \text{ unless otherwise stated.}$

Figure 51. Load Transient:  $V_{IN}$  = 5.5V,  $V_{OUT}$  = 1.8V, Load = 0.125A to 0.375A, Slew Rate = 1A/ $\mu$ s

Figure 52. Load Transient:  $V_{IN}$  = 5.5V,  $V_{OUT}$  = 3.3V, Load = 0.125A to 0.375A, Slew Rate = 1A/ $\mu$ s

## 5. Functional Description

The ISL9122A implements a complete buck-boost switching regulator, with PWM controller, internal switches, references, protection circuitry, and control inputs. See the <u>Block Diagram</u>.

The PWM controller automatically switches between Buck and Boost modes as necessary, to maintain a steady output voltage with changing input voltages and dynamic external loads.

### 5.1 Enable Input

The device is enabled by asserting the EN pin HIGH. Driving EN LOW invokes Power-Down mode, in which most internal device functions are disabled. EN must remain LOW for at least 50µs for the device to be disabled. When the device is disabled by driving EN LOW, the output discharges naturally based on the load current.

## 5.2 Soft Discharge

Whenever the converter is disabled over  $I^2C$ , an internal discharge resistor between VOUT and GND can be activated to slowly discharge the output capacitor. This internal discharge resistor has a typical resistance of  $160\Omega$ . The soft discharge function is accessed using  $I^2C$  while keeping the EN pin high. Using the CONV\_CFG register, set the DISCH bit to 1 and disable the IC by setting the EN AND bit to 0. (See Table 5 for details).

### 5.3 Start-Up

When the input voltage rises above the undervoltage lockout threshold and EN is asserted high, the power-on sequence starts. First, the IC is initialized and its One-Time Programmable (OTP) memory is read. After the OTP has been read and the controller knows the target output voltage and ramp rate, soft-start begins and the output voltage rises at the programmed ramp rate until it reaches the target output voltage.

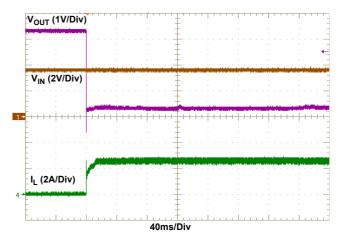

### 5.4 Overcurrent/Short-Circuit Protection

The ISL9122A provides overcurrent protection by monitoring the inductor current. When the peak inductor current hits its current limit, the IC enters Hiccup mode, Shutdown, or Current Limit mode according to the setting of the OC\_FAULT\_MODE bits in the INT\_FLAG\_MASK register.

During Hiccup mode, the IC shuts down for 100ms and then tries to restart. If it encounters the overcurrent condition again, it shuts down and tries to restart after another 100ms. This cycle keeps repeating until there is no overcurrent and VOUT can then come back up.

In Shutdown mode, the IC shuts down whenever overcurrent is encountered and the only way to bring the output voltage up is to restart the part by either cycling VIN, or EN, or by resetting and then setting the EN\_AND bit in the CONV\_CFG register, to mimic EN cycling behavior.

In Current Limit mode, the IC provides the maximum current it can, while respecting the peak current limit. If the load demand is even more, the IC starts dropping the output voltage while supplying the same maximum current.

#### 5.5 Thermal Shutdown

The ISL9122A features a thermal shutdown that protects the device from damage because of overheating. An integrated temperature sensor circuit monitors the internal IC temperature. When the temperature exceeds  $T_{SD}$ , the device stops switching and waits for the temperature to fall. When the temperature falls by  $T_{SDHYS}$ , the controller first goes through the soft-start phase and then starts regulating at the target output voltage as defined by the I<sup>2</sup>C register value.

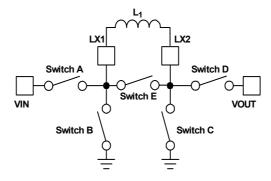

#### 5.6 Buck-Boost Conversion Topology

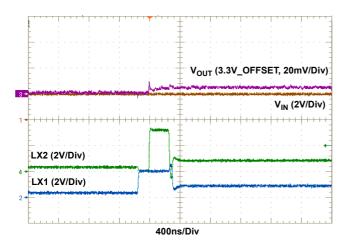

The ISL9122A operates in either a pure Buck or a pure Boost mode. When operating in conditions in which  $V_{IN}$  is close to  $V_{OUT}$ , the ISL9122A alternates between Buck and Boost modes, as necessary, to provide a regulated output voltage.

Figure 53. Buck-Boost Topology

Figure 53 shows a simplified diagram of the internal switches and external inductor.

### 5.7 Pulse Width Modulation (PWM) Operation

In Buck PWM mode, Switch D is kept permanently closed and Switch C permanently open. Switches A and B operate as in a synchronous buck converter. Initially Switch A is turned ON and this ramps up the inductor current with a slope of  $(V_{IN} - V_{OUT})/L$  (in buck mode,  $V_{IN} > V_{OUT}$ ). When the inductor current hits the upper threshold, as dictated by the hysteretic controller, Switch A is turned OFF. This is followed by a small dead-time where both the switches are OFF. During this interval, the inductor current keeps flowing, finding its path through the body diode of Switch B. When the dead-time is over, Switch B is turned ON and the inductor current ramps down with a slope of - $(V_{OUT})/L$ . When it hits the lower hysteretic threshold, Switch B is turned OFF, followed by another dead-time interval. After this, Switch A is turned ON again and the entire sequence repeats.

In Boost PWM mode, Switch A is kept permanently closed and switch B permanently open. Switches C and D operate as in a synchronous boost converter. Initially Switch C is turned ON and this ramps up the inductor current with a slope of  $V_{IN}/L$ . When the inductor current hits the upper threshold, as dictated by the hysteretic controller, Switch C is turned OFF. This is followed by a small dead-time where both the switches are OFF. During this interval, the inductor current keeps flowing, finding its path through the body diode of Switch D. When the dead-time is over, Switch D is turned ON and the inductor current ramps down with a slope of  $(V_{IN} - V_{OUT})/L$  (in boost mode,  $V_{IN} < V_{OUT}$ ). When it hits the lower hysteretic threshold, Switch D is turned OFF, followed by another dead-time interval. After this, Switch C is turned ON again and the entire sequence repeats.

The converter operates in PWM mode under two conditions: load is sufficiently high in the Normal Mode (Auto PFM/PWM mode) OR Forced PWM mode is enabled by setting the FMODE bits in CONV\_CFG register to 0x2.

The optimal switching frequency is determined by the hysteretic controller and is centered around 2.5MHz, for  $V_{IN} = 3.6V$  and  $V_{OLT} = 1.8V$ .

### 5.8 Pulse Frequency Modulation (PFM) Operation

During PFM operation in Buck mode, Switch D is kept permanently closed, and Switch C permanently open. Switches A and B operate in Discontinuous Conduction Mode (DCM). Just like the Buck PWM operation, Switch A is turned ON followed by a dead-time and then Switch B is turned ON. The inductor current ramps up and down respectively, and the energy contained in this current pulse charges up  $V_{OUT}$ . After this, unlike the PWM operation, both switches remain OFF until  $V_{OUT}$  discharges down to the lower threshold of the hysteretic controller. The switching cycle repeats after that.

During PFM operation in Boost mode, unlike Buck mode, Switch A is not kept permanently closed, although Switch B does remain permanently open. Switches C and D operate in DCM. At the start of the PFM pulse, Switch A is turned ON. Then, just like the Boost PWM operation, Switch C is turned ON followed by a dead-time and then Switch D is turned ON. The inductor current ramps up and down respectively, and the energy contained in this current pulse charges up V<sub>OUT</sub>. After this, unlike the PWM operation, both switches remain OFF and even Switch A is turned OFF, until V<sub>OUT</sub> discharges down to the lower threshold of the hysteretic controller. The switching cycle repeats after that.

In most operating conditions, multiple switching pulses are needed to charge up the output capacitor. These pulses continue until  $V_{OUT}$  has achieved the upper threshold of the PFM hysteretic controller. Switching then stops and remains stopped until  $V_{OUT}$  decays to the lower threshold. As load increases, the frequency of PFM pulses increases as  $V_{OUT}$  gets discharged faster and needs to be recharged more often. This continues until the PFM pulses start bunching together and the part then enters sustained PWM operation. The converter operates in PFM mode under only one condition: load is light enough in the Normal Mode (Auto PFM/PWM mode).

The PFM-PWM transition, going from light to heavy load and then back to light load, has a hysteretic band. This allows for a seamless PFM to PWM and PWM to PFM transition.

## 5.9 Operation With V<sub>IN</sub> Close to V<sub>OUT</sub>

When the output voltage is close to the input voltage, the ISL9122A rapidly and smoothly switches between Boost, Bypass, and Buck modes to maintain the regulated output voltage. This behavior provides excellent efficiency and low output voltage ripple.

**Note:** For output voltages greater than 5.0V, the input voltage needs to be less than 4.5V to ensure low IQ operation.

## 5.10 Forced Operating Modes

Forced operating modes include Forced PWM mode and Forced Bypass mode. Forced operating modes are selected using the FMODE bits in the CONV\_CFG register (See <u>Table 5</u> for details). The power-up default mode is Normal operation with automatic mode transitions to optimize efficiency.

Forced PWM mode can be selected to minimize the switching frequency variation and to obtain a tight V<sub>OUT</sub> accuracy, although this comes at the expense of increased input current.

Forced Bypass mode can be selected to minimize power losses when output voltage regulation is not required. When the device enters Bypass mode, both Switches A and D are turned ON, providing a direct path from the input to output through the inductor. In Bypass mode, all other blocks, except POR and I<sup>2</sup>C, are turned off to minimize quiescent current consumption. If the part has to repeatedly bounce between the Forced Bypass and Regulation modes, there should be at least 1ms delay between the successive mode setting I<sup>2</sup>C commands. **Note**: There is no overcurrent protection in Bypass mode.

### 5.11 I<sup>2</sup>C Serial Interface

The ISL9122A supports a bidirectional bus-oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter and the receiving device as the receiver. The device controlling the transfer is the master and the device being controlled is the slave. The master always initiates data transfers and provides the clock for both transmit and receive operations. Therefore, the ISL9122A operates as a slave device in all applications.

The IC supports the following data transfers rates and modes as defined in the I<sup>2</sup>C specification:

- · Up to 100kbit/s in Standard mode

- · Up to 400kbit/s in Fast mode

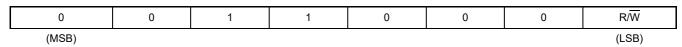

All communication over the I<sup>2</sup>C interface is conducted by sending the MSB of each byte of data first.

#### 5.12 Protocol Conventions

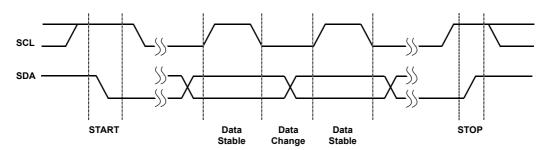

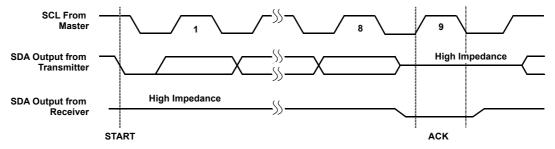

Data states on the SDA line can change only during SCL LOW periods. The SDA state changes during SCL HIGH are reserved for indicating START and STOP conditions (see <u>Figure 54</u>). At power-up of the ISL9122A, the SDA pin is in input mode.

All I<sup>2</sup>C interface operations must begin with a START condition, which is a HIGH to LOW transition of SDA while SCL is HIGH. The ISL9122A continuously monitors the SDA and SCL lines for the START condition and does not respond to any command until this condition is met (see <u>Figure 54</u>). A START condition is ignored during the power-up sequence and when EN input is low.

All I<sup>2</sup>C interface operations must be terminated by a STOP condition, which is a LOW to HIGH transition of SDA while SCL is HIGH (see <u>Figure 54</u>). A STOP condition at the end of a write operation initiates the reconfiguration of the ISL9122A voltage feedback loop as necessary to provide the programmed output voltage.

An acknowledge (ACK) is a software convention used to indicate a successful data transfer. The transmitting device, either master or slave, releases the SDA bus after transmitting eight bits. During the ninth clock cycle, the receiver pulls the SDA line LOW to acknowledge the reception of the eight bits of data (see <u>Figure 55</u>).

The ISL9122A responds with an ACK after recognizing a START condition followed by a valid 7-bit slave address, and once again after successful receipt of a register address byte. The ISL9122A again responds with an ACK after receiving a data byte of a write operation. The master must respond with an ACK after receiving a data byte of a read operation.

For the base version, the 7-bit slave address is set in trim to 0x18. The 7-bit address is followed by a Read/Write bit whose value is 1 for a Read operation, and 0 for a Write operation (see <u>Table 1</u>).

Table 1. 7-Bit Address Format

Figure 54. Valid Data Changes, Start, and Stop Conditions

Figure 55. Acknowledge Response from Receiver

### 5.13 Write Operation

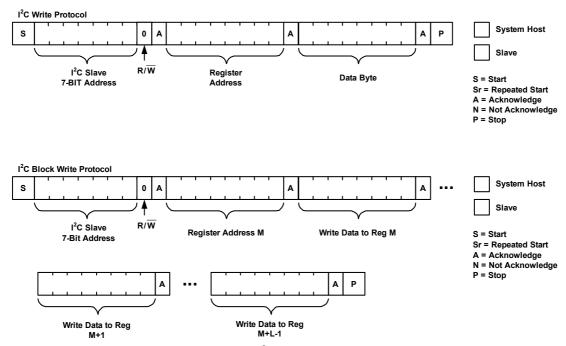

Write operations are shown in Figure 56. A write operation requires a START condition, followed by a valid 7-bit slave address with the R/W bit set to 0, a valid register address byte, one or more data bytes, and a STOP condition. After each of the bytes, the ISL9122A responds with an ACK. After each data byte is acknowledged, the ISL9122A increments its register address to support block writes. The master sends a STOP to complete the command.

STOP conditions that terminate write operations must be sent by the master after sending at least one full data byte and its associated ACK signal. If a STOP condition is issued in the middle of a data byte, or before one full data byte + ACK is sent, the ISL9122A ignores the command and does not change the output voltage or other settings.

Figure 56. I<sup>2</sup>C Register Write Protocols

## 5.14 Read Operation

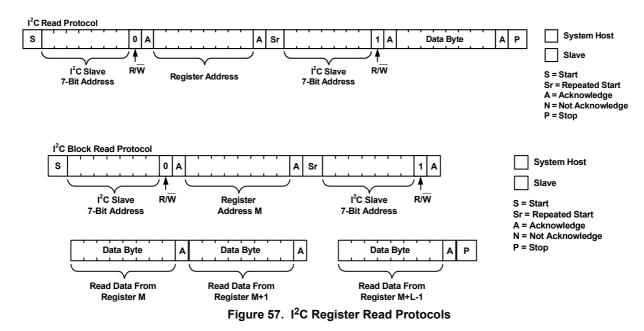

Read operations are shown in <u>Figure 57</u>. They consist of fo<u>ur</u> or more bytes. The host generates a START condition, then transmits the 7-bit slave address with the R/W bit set to 0. The ISL9122A responds with an ACK. The host then transmits the register address byte, and the ISL9122A responds with another ACK.

The host then generates a repeat START condition and transmits the 7-bit slave address with the  $R/\overline{W}$  bit set to 1. The ISL9122A responds with an ACK, indicating it is ready to provide the requested data.

The ISL9122A then transmits the data byte by asserting control of the SDA pin while the host generates clock pulses on the SCL pin. After each data byte is complete, the host generates an ACK condition, and the ISL9122A increments its register address to support block reads. After the last data byte is complete and acknowledged, the host sends a STOP condition. This completes the I<sup>2</sup>C Read operation.

### 5.15 Register Descriptions

The ISL9122A has five I $^2$ C accessible control registers whose functions are described in <u>Table 2</u> through <u>Table 6</u>. These registers can be accessed any time the ISL9122A is enabled. When the ISL9122A is disabled (EN = LOW), attempts to communicate through its I $^2$ C interface are not supported.

### 5.15.1 RO REG1

The RO REG1 register contains the hardware identification bits as described in Table 2.

Table 2. Register Address 0x02: RO\_REG1

| Bit | Name           | Туре | Reset | Description                                                                    |

|-----|----------------|------|-------|--------------------------------------------------------------------------------|

| 7:6 | FAMILY_ID[1:0] | R    | 0x0   | Chip family identifier 0x0 = ISL9122 stand-alone converter family              |

| 5:3 | HW_REV[2:0]    | R    | 0x3   | Chip revision level 0x3 = Hardware revision D                                  |

| 2:0 | RAIL_VAR[2:0]  | R    | 0x0   | Converter variant identifier<br>0x0 = High voltage input Buck-Boost (ISL9122A) |

### **5.15.2 INTFLG REG**

The INTFLG\_REG register contains fault flags. Each bit represents a different type of fault as described in <a href="Table 3">Table 3</a>. A 0 indicates no fault, and a 1 indicates a fault. Each bit is set by a fault event and is cleared when read.

Table 3. Register Address 0x03: INTFLG\_REG

| Bit | Name | Туре | Reset | Description                 |

|-----|------|------|-------|-----------------------------|

| 3   | INT3 | R    | 0x0   | Voltage setting under range |

| 2   | INT2 | R    | 0x0   | Voltage setting over range  |

| 1   | INT1 | R    | 0x0   | Over-temperature            |

| 0   | INT0 | R    | 0x0   | Overcurrent                 |

### 5.15.3 **VSET**

The VSET register contains the output voltage setting in 25mV steps as shown in <u>Equation 1</u>. VSET can be changed after the IC is enabled and operating. When the output voltage is changed, it ramps at the rate set in the DVSRATE bits of CONV\_CFG register.

The output voltage range is digitally limited to be between the minimum and maximum values shown in <u>Table 4</u>. Setting values above or below the limits results in the output voltage ramping to the limit and the appropriate overvoltage or undervoltage interrupt flag in INTFLG\_REG being set.

(EQ. 1)

$$V_{OUT} = VSET \times 0.025V$$

Table 4. Register Address 0x11: VSET

| ı | Bit | Name      | Type | Reset | Description                                                        |

|---|-----|-----------|------|-------|--------------------------------------------------------------------|

| - | 7:0 | VSET[7:0] | R/W  |       | Output voltage setting Minimum limit = 1.8V Maximum limit = 5.375V |

## 5.15.4 CONV\_CFG

The CONV\_CFG register settings are described in <u>Table 5</u>.

Table 5. Register Address 0x12: CONV\_CFG

| Bit | Name         | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EN_AND       | R/W  | 0x1   | Enable bit. ANDed with the enable input $0x0 = EN$ pin going high wakes up the $I^2C$ , but does not start the converter. The converter is started by writing 1 to this bit using $I^2C$ while the EN pin is high $0x1 = EN$ pin going high wakes up the $I^2C$ and starts the converter <b>Note</b> : EN pin low always disables the converter and $I^2C$                   |

| 6   | DISCH        | R/W  | 0x0   | 0x0 = No discharge resistor present when converter is disabled over I <sup>2</sup> C 0x1 = Discharge resistor present when converter is disabled over I <sup>2</sup> C                                                                                                                                                                                                       |

| 5:4 | DVSRATE[1:0] | R/W  | 0x0   | Dynamic Voltage Scaling slew rate applied when the output voltage setting is changed. $0x0 = 3.125 \text{mV/}\mu\text{s}$ $0x1 = 6.25 \text{mV/}\mu\text{s}$ $0x2 = 0.78125 \text{mV/}\mu\text{s}$ $0x3 = 1.5625 \text{mV/}\mu\text{s}$                                                                                                                                      |

| 3:2 | FMODE[1:0]   | R/W  | 0x0   | Forced operating modes  0x0 = Normal operation with automatic mode transitions  0x1 = RESERVED. DO NOT USE this combination  0x2 = Forced PWM mode with no PFM operation  0x3 = Forced bypass. Disables switching. If the Forced Bypass mode is selected and the part is disabled over I <sup>2</sup> C (CONV_CFG[7] = EN_AND = 0x0), the converter remains in Forced Bypass |

| 1   | CONV_RSVD    | R/W  | 0x0   | Reserved                                                                                                                                                                                                                                                                                                                                                                     |

| 0   | TYPE1        | R/W  | 0x1   | 0x0 = Type I error amplifier for best transient response with voltage positioning 0x1 = Type II error amplifier for best steady state voltage accuracy. <b>DO NOT USE</b> Type II error amplifier if overcurrent fault handling is disabled (INTFLG_MASK[7] = OC_FAULT_MODE = 0x2 or 0x3)                                                                                    |

## 5.15.5 INTFLG\_MASK

The INTFLG\_MASK register settings are described in <u>Table 6</u>.

Table 6. Register Address 0x13: INTFLG\_MASK

| Bit | Name               | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                     |

|-----|--------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | OC_FAULT_MODE[1:0] | R/W  | 0x0   | Overcurrent fault handling modes  0x0 = Hiccup mode with 100ms wait  0x1 = Shutdown mode. Requires restart over I <sup>2</sup> C or EN pin  0x2 = Current limit with no fault action taken. USE ONLY with Type I error amplifier  (CONV_CFG[0] = TYPE1 = 0x0)  0x3 = Reserved. USE ONLY with Type I error amplifier (CONV_CFG[0] = TYPE1 = 0x0) |

| 5   | EN_OR              | R/W  | 0x0   | Enable override bit for $I^2C$ control of the converter. Implements push-button ON operation; the button pulls EN high and the part starts. If EN_OR is set from OTP or over $I^2C$ , the part remains enabled when the button is released $0x0$ = Controlled by the EN pin $0x1$ = Held in enable state - EN pin is ignored                    |

ISL9122A 6. Revision History

# 6. Revision History

| Rev. | Date         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.01 | Mar 17, 2022 | Updated page 1 description. Removed Related Literature section. Updated Features bullets. Updated the figure titles for Figure 1 and Figure 2. Updated Ordering Information table by updating formatting. Added Abs max for LX1, LX2 (less than 10ns). Added three more rows to the recommend operating conditions table. Updated Conditions in the Analog Specifications header. Updated Test Conditions for several parameters in the Analog Specification table. Updated the Peak Current Limit (1.8V < V <sub>IN</sub> < 2.5V) specification typical value from 2.5A to 2.5*(V <sub>IN</sub> /2.5). Updated the typical values for the Power MOSFET On-Resistance. Updated the following sections: Typical Performance Graphs, Line/Load Transient Waveforms, Enable Input, Soft Discharge, Start-Up, Overcurrent/Short-Circuit Protection, Thermal Shutdown, Buck-Boost Conversion Topology, Pulse Width Modulation (PWM) Operation, Pulse Frequency Modulation (PFM) Operation, Operation With VIN Close to VOUT, Forced Operating Modes, I2C Serial Interface, Protocol Conventions, Write Operation, Read Operation, and Register Descriptions Updated links throughout. Updated Pin descriptions for SDA and SCL. |

| 1.00 | Sep 14, 2020 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

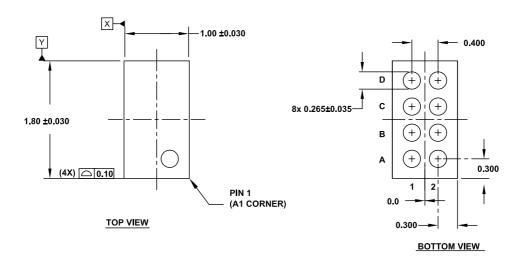

## 7. Package Outline Drawings

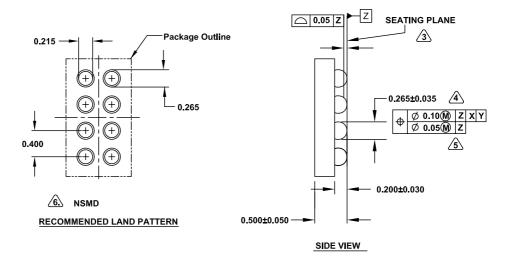

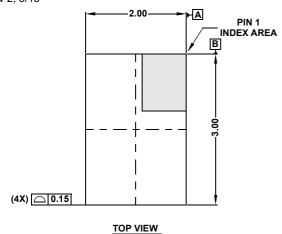

For the most recent package outline drawing, see <u>W2x4.8</u>.

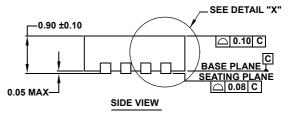

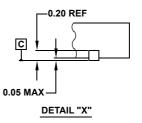

W2x4.8 8 Ball Wafer Level Chip Scale Package (WLCSP) 0.4mm Pitch Rev 0, 6/17

#### NOTES:

- 1. All dimensions are in millimeters.

- 2. Dimensions and tolerances per ASMEY 14.5-1994

- A Primary datum Z and seating plane are defined by the spherical crowns of the bump.

- Dimension is measured at the maximum bump diameter parallel to primary datum Z.

- Bump position designation per JESD 95-1, SPP-010.

- 6 NSMD refers to non-solder mask defined pad design per Intersil Techbrief. http://www.intersil.com/data/tb/tb451.pdf

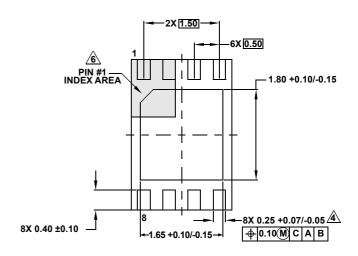

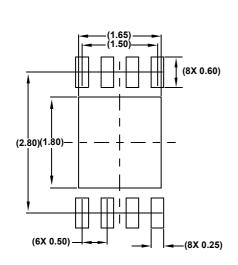

For the most recent package outline drawing, see <u>L8.2x3</u>.

L8.2x3 8 Lead Dual Flat No-Lead Plastic Package Rev 2, 3/15

**BOTTOM VIEW**

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance: Decimal ± 0.05

- <u>A</u> Dimension applies to the metallized terminal and is measured between 0.25mm and 0.30mm from the terminal tip.

- Tiebar shown (if present) is a non-functional feature and may be located on any of the 4 sides (or ends).

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Complies to JEDEC MO-229 VCED-2.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Rev.1.0 Mar 2020)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit:

www.renesas.com/contact/