### Features

- High-performance, Low-power 32-bit Atmel® AVR® Microcontroller

- Compact Single-cycle RISC Instruction Set Including DSP Instructions

- Read-modify-write Instructions and Atomic Bit Manipulation

- Performance

- Up to 64DMIPS Running at 50MHz from Flash (1 Flash Wait State)

- Up to 36DMIPS Running at 25MHz from Flash (0 Flash Wait State)

- Memory Protection Unit (MPU)

- Secure Access Unit (SAU) providing User-defined Peripheral Protection

- picoPower<sup>®</sup> Technology for Ultra-low Power Consumption

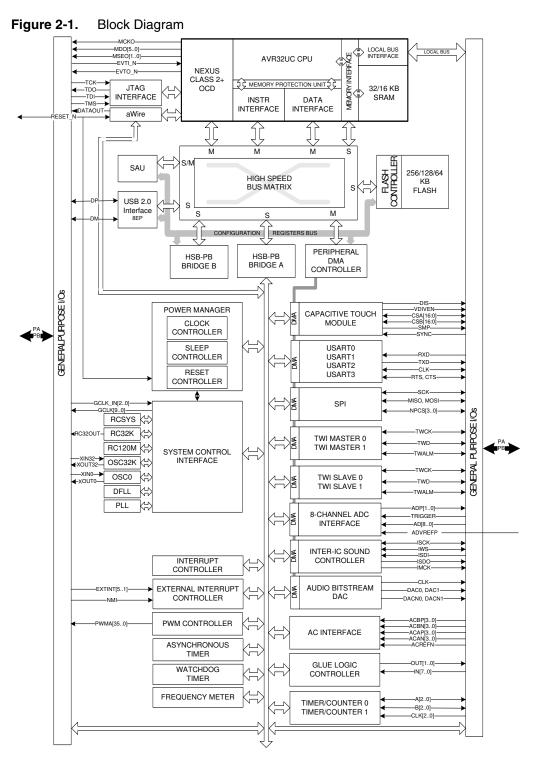

- Multi-hierarchy Bus System

- High-performance Data Transfers on Separate Buses for Increased Performance

- 12 Peripheral DMA Channels improve Speed for Peripheral Communication

- Internal High-speed Flash

- 256 Kbytes, 128 Kbytes, and 64 Kbytes Versions

- Single-cycle Access up to 25MHz

- FlashVault Technology Allows Pre-programmed Secure Library Support for End User Applications

- Prefetch Buffer Optimizing Instruction Execution at Maximum Speed

- 100,000 Write Cycles, 15-year Data Retention Capability

- Flash Security Locks and User-defined Configuration Area

- Internal High-speed SRAM, Single-cycle Access at Full Speed

- 32Kbytes (256Kbytes and 128Kbytes Flash) and 16Kbytes (64Kbytes Flash)

- Interrupt Controller (INTC)

- Autovectored Low-latency Interrupt Service with Programmable Priority

- External Interrupt Controller (EIC)

- Peripheral Event System for Direct Peripheral to Peripheral Communication

- System Functions

- Power and Clock Manager

- SleepWalking Power Saving Control

- Internal System RC Oscillator (RCSYS)

- 32 KHz Oscillator

- Multipurpose Oscillator, Phase Locked Loop (PLL), and Digital Frequency Locked Loop (DFLL)

Atmel

- Windowed Watchdog Timer (WDT)

- Asynchronous Timer (AST) with Real-time Clock Capability

- Counter or Calendar Mode Supported

- Frequency Meter (FREQM) for Accurate Measuring of Clock Frequency

- Universal Serial Bus (USBC)

- Full Speed and Low Speed USB Device Support

- Multi-packet Ping-pong Mode

- Six 16-bit Timer/Counter (TC) Channels

- External Clock Inputs, PWM, Capture, and Various Counting Capabilities

- 36 PWM Channels (PWMA)

- 12-bit PWM with a Source Clock up to 150MHz

- Four Universal Synchronous/Asynchronous Receiver/Transmitters (USART)

- Independent Baudrate Generator, Support for SPI

- Support for Hardware Handshaking

# Atmel

32-bit Atmel AVR Microcontroller

ATUC256L3U ATUC128L3U ATUC64L3U ATUC256L4U ATUC128L4U ATUC64L4U

# Summary

32142DS-06/2013

# ATUC64/128/256L3/4U

- One Master/Slave Serial Peripheral Interface (SPI) with Chip Select Signals

Up to 15 SPI Slaves can be Addressed

- Two Master and Two Slave Two-wire Interfaces (TWI), 400 kbit/s I<sup>2</sup>C-compatible

- One 8-channel Analog-to-digital Converter (ADC) with up to 12 Bits Resolution

Internal Temperature Sensor

- Eight Analog Comparators (AC) with Optional Window Detection

- Capacitive Touch (CAT) Module

- Hardware-assisted Atmel<sup>®</sup> AVR<sup>®</sup> QTouch<sup>®</sup> and Atmel<sup>®</sup> AVR<sup>®</sup> QMatrix Touch Acquisition

- Supports QTouch and QMatrix Capture from Capacitive Touch Sensors

- QTouch Library Support

- Capacitive Touch Buttons, Sliders, and Wheels

- QTouch and QMatrix Acquisition

- Audio Bitstream DAC (ABDACB) Suitable for Stereo Audio

- Inter-IC Sound (IISC) Controller

- Compliant with Inter-IC Sound (I<sup>2</sup>S) Specification

- On-chip Non-intrusive Debug System

- Nexus Class 2+, Runtime Control, Non-intrusive Data and Program Trace

- aWire Single-pin Programming Trace and Debug Interface, Muxed with Reset Pin

- NanoTrace Provides Trace Capabilities through JTAG or aWire Interface

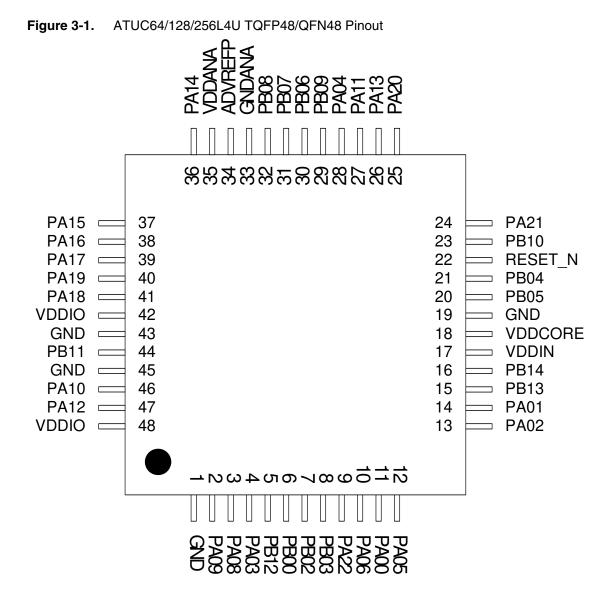

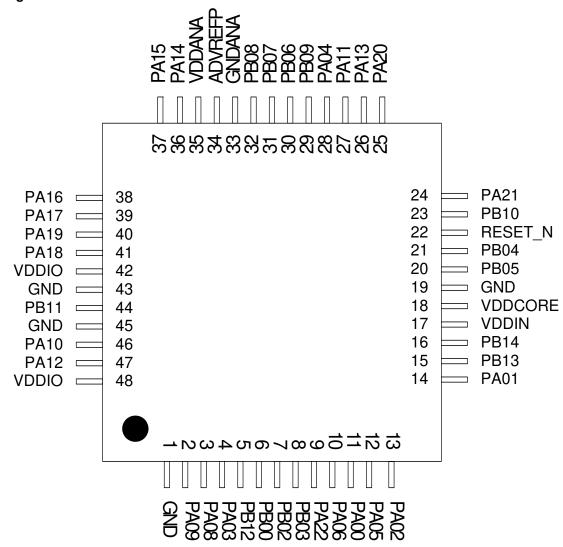

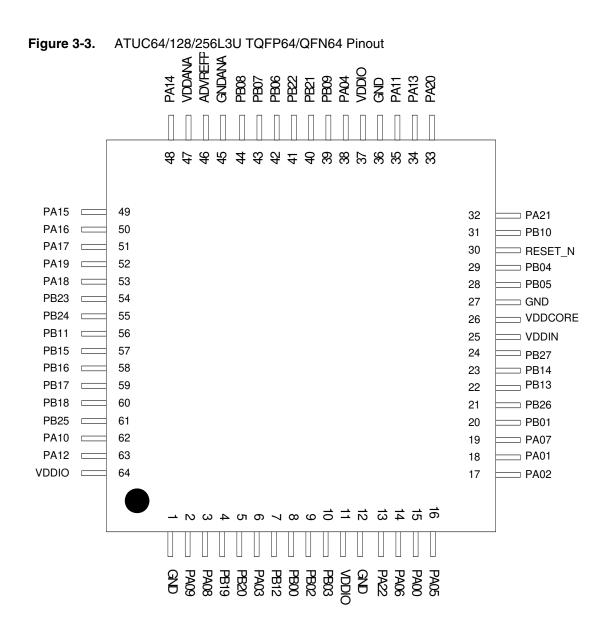

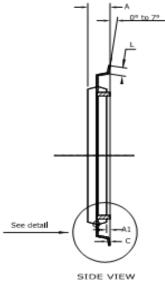

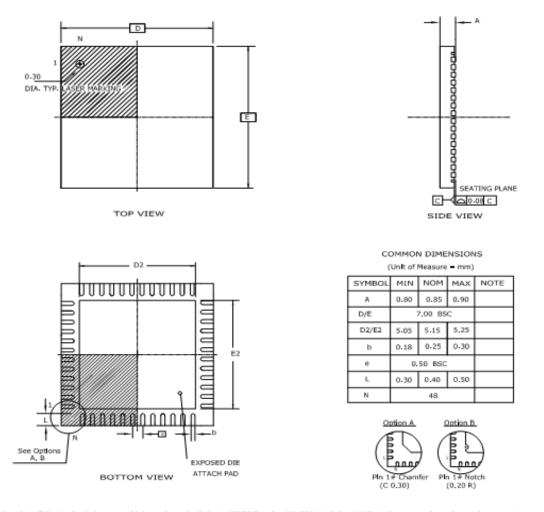

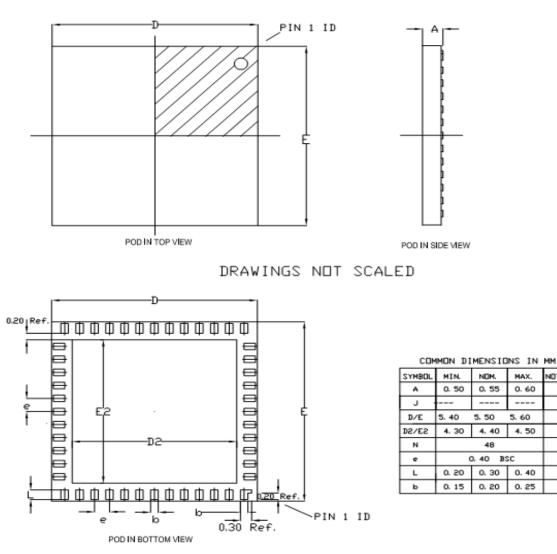

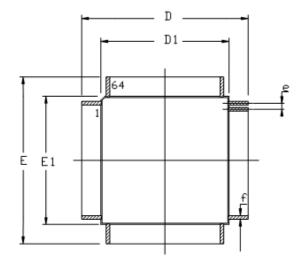

- 64-pin TQFP/QFN (51 GPIO Pins), 48-pin TQFP/QFN/TLLGA (36 GPIO Pins)

- Six High-drive I/O Pins (64-pin Packages), Four High-drive I/O Pins (48-pin Packages)

- Single 1.62-3.6V Power Supply

#### 1. Description

The Atmel<sup>®</sup> AVR<sup>®</sup> ATUC64/128/256L3/4U is a complete system-on-chip microcontroller based on the AVR32 UC RISC processor running at frequencies up to 50MHz. AVR32 UC is a highperformance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density, and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern and real-time operating systems. The Secure Access Unit (SAU) is used together with the MPU to provide the required security and integrity.

Higher computation capability is achieved using a rich set of DSP instructions.

The ATUC64/128/256L3/4U embeds state-of-the-art picoPower technology for ultra-low power consumption. Combined power control techniques are used to bring active current consumption down to  $174\mu$ A/MHz, and leakage down to 220nA while still retaining a bank of backup registers. The device allows a wide range of trade-offs between functionality and power consumption, giving the user the ability to reach the lowest possible power consumption with the feature set required for the application.

The Peripheral Direct Memory Access (DMA) controller enables data transfers between peripherals and memories without processor involvement. The Peripheral DMA controller drastically reduces processing overhead when transferring continuous and large data streams.

The ATUC64/128/256L3/4U incorporates on-chip Flash and SRAM memories for secure and fast access. The FlashVault technology allows secure libraries to be programmed into the device. The secure libraries can be executed while the CPU is in Secure State, but not read by non-secure software in the device. The device can thus be shipped to end customers, who will be able to program their own code into the device to access the secure libraries, but without risk of compromising the proprietary secure code.

The External Interrupt Controller (EIC) allows pins to be configured as external interrupts. Each external interrupt has its own interrupt request and can be individually masked.

The Peripheral Event System allows peripherals to receive, react to, and send peripheral events without CPU intervention. Asynchronous interrupts allow advanced peripheral operation in low power sleep modes.

The Power Manager (PM) improves design flexibility and security. The Power Manager supports SleepWalking functionality, by which a module can be selectively activated based on peripheral events, even in sleep modes where the module clock is stopped. Power monitoring is supported by on-chip Power-on Reset (POR), Brown-out Detector (BOD), and Supply Monitor (SM). The device features several oscillators, such as Phase Locked Loop (PLL), Digital Frequency Locked Loop (DFLL), Oscillator 0 (OSC0), and system RC oscillator (RCSYS). Either of these oscillators can be used as source for the system clock. The DFLL is a programmable internal oscillator from 20 to 150MHz. It can be tuned to a high accuracy if an accurate reference clock is running, e.g. the 32KHz crystal oscillator.

The Watchdog Timer (WDT) will reset the device unless it is periodically serviced by the software. This allows the device to recover from a condition that has caused the system to be unstable.

The Asynchronous Timer (AST) combined with the 32KHz crystal oscillator supports powerful real-time clock capabilities, with a maximum timeout of up to 136 years. The AST can operate in counter or calendar mode.

The Frequency Meter (FREQM) allows accurate measuring of a clock frequency by comparing it to a known reference clock.

The Full-speed USB 2.0 device interface (USBC) supports several USB classes at the same time, thanks to the rich end-point configuration.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

The Pulse Width Modulation controller (PWMA) provides 12-bit PWM channels which can be synchronized and controlled from a common timer. 36 PWM channels are available, enabling applications that require multiple PWM outputs, such as LCD backlight control. The PWM channels can operate independently, with duty cycles set individually, or in interlinked mode, with multiple channels changed at the same time.

The ATUC64/128/256L3/4U also features many communication interfaces, like USART, SPI, and TWI, for communication intensive applications. The USART supports different communication modes, like SPI Mode and LIN Mode.

A general purpose 8-channel ADC is provided, as well as eight analog comparators (AC). The ADC can operate in 10-bit mode at full speed or in enhanced mode at reduced speed, offering up to 12-bit resolution. The ADC also provides an internal temperature sensor input channel. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

The Capacitive Touch (CAT) module senses touch on external capacitive touch sensors, using the QTouch technology. Capacitive touch sensors use no external mechanical components, unlike normal push buttons, and therefore demand less maintenance in the user application. The CAT module allows up to 17 touch sensors, or up to 16 by 8 matrix sensors to be interfaced. All touch sensors can be configured to operate autonomously without software interaction, allowing wakeup from sleep modes when activated.

Atmel offers the QTouch library for embedding capacitive touch buttons, sliders, and wheels functionality into AVR microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys as well as Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

The Audio Bitstream DAC (ABDACB) converts a 16-bit sample value to a digital bitstream with an average value proportional to the sample value. Two channels are supported, making the ABDAC particularly suitable for stereo audio.

The Inter-IC Sound Controller (IISC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with external audio devices. The controller is compliant with the Inter-IC Sound (I2S) bus specification.

The ATUC64/128/256L3/4U integrates a class 2+ Nexus 2.0 On-chip Debug (OCD) System, with non-intrusive real-time trace and full-speed read/write memory access, in addition to basic runtime control. The NanoTrace interface enables trace feature for aWire- or JTAG-based debuggers. The single-pin aWire interface allows all features available through the JTAG interface to be accessed through the RESET pin, allowing the JTAG pins to be used for GPIO or peripherals.

#### 2. Overview

#### 2.1 Block Diagram

### 2.2 Configuration Summary

**Table 2-1.**Configuration Summary

| Feature                 | ATUC256L3U | ATUC128L3U       | ATUC64L3U                                                                                                                                   | ATUC256L4U                                                                         | ATUC128L4U     | ATUC64L4U |  |

|-------------------------|------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------|-----------|--|

| Flash                   | 256 KB     | 128KB            | 64KB                                                                                                                                        | 256KB                                                                              | 128KB          | 64KB      |  |

| SRAM                    | 32         | 32KB 16KB 32KB 1 |                                                                                                                                             |                                                                                    |                |           |  |

| GPIO                    |            | 51               |                                                                                                                                             |                                                                                    | 36             |           |  |

| High-drive pins         |            | 6                |                                                                                                                                             |                                                                                    | 4              |           |  |

| External Interrupts     |            |                  | 6                                                                                                                                           | 3                                                                                  |                |           |  |

| TWI                     |            |                  | 2                                                                                                                                           | 2                                                                                  |                |           |  |

| USART                   |            |                  | 2                                                                                                                                           | 1                                                                                  |                |           |  |

| Peripheral DMA Channels |            |                  | 1                                                                                                                                           | 2                                                                                  |                |           |  |

| Peripheral Event System |            |                  | 1                                                                                                                                           | l                                                                                  |                |           |  |

| SPI                     |            |                  | 1                                                                                                                                           | I                                                                                  |                |           |  |

| Asynchronous Timers     |            |                  | 1                                                                                                                                           |                                                                                    |                |           |  |

| Timer/Counter Channels  |            |                  | 6                                                                                                                                           | 3                                                                                  |                |           |  |

| PWM channels            |            |                  | 3                                                                                                                                           | 6                                                                                  |                |           |  |

| Frequency Meter         |            |                  | 1                                                                                                                                           |                                                                                    |                |           |  |

| Watchdog Timer          |            |                  | 1                                                                                                                                           | l                                                                                  |                |           |  |

| Power Manager           |            |                  | 1                                                                                                                                           | l                                                                                  |                |           |  |

| Secure Access Unit      |            |                  | -                                                                                                                                           | l                                                                                  |                |           |  |

| Glue Logic Controller   |            |                  | -                                                                                                                                           | l                                                                                  |                |           |  |

| Oscillators             |            | PI<br>Ci         | requency Locked<br>nase Locked Loop<br>rystal Oscillator 0<br>Crystal Oscillator<br>RC Oscillator 12<br>RC Oscillator 11<br>RC Oscillator 3 | 9 40-240MHz (PL<br>45-16MHz (OSC<br>32KHz (OSC32K<br>0MHz (RC120M)<br>5kHz (RCSYS) | L)<br>0)       |           |  |

| ADC                     |            |                  | 8-chann                                                                                                                                     | el 12-bit                                                                          |                |           |  |

| Temperature Sensor      |            |                  | 1                                                                                                                                           | l                                                                                  |                |           |  |

| Analog Comparators      |            |                  | 8                                                                                                                                           | 3                                                                                  |                |           |  |

| Capacitive Touch Module |            |                  | 1                                                                                                                                           | I                                                                                  |                |           |  |

| JTAG                    |            | 1                |                                                                                                                                             |                                                                                    |                |           |  |

| aWire                   |            |                  | -                                                                                                                                           |                                                                                    |                |           |  |

| USB                     |            |                  | 1                                                                                                                                           |                                                                                    |                |           |  |

| Audio Bitstream DAC     |            | 1                |                                                                                                                                             |                                                                                    | 0              |           |  |

| IIS Controller          |            | 1                |                                                                                                                                             |                                                                                    | 0              |           |  |

| Max Frequency           |            |                  | 50N                                                                                                                                         | ИНz                                                                                |                |           |  |

| Packages                |            | TQFP64/QFN64     |                                                                                                                                             | TQF                                                                                | P48/QFN48/TLLC | GA48      |  |

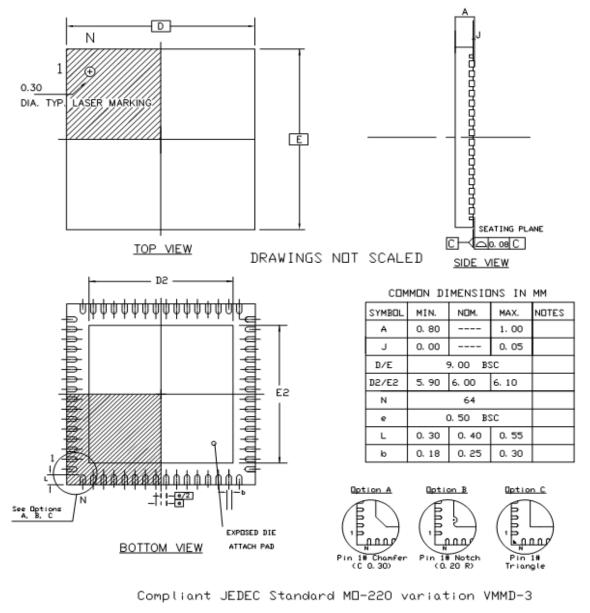

#### 3. Package and Pinout

#### 3.1 Package

The device pins are multiplexed with peripheral functions as described in Section .

Figure 3-2. ATUC64/128/256L4U TLLGA48 Pinout

### ATUC64/128/256L3/4U

Atmel

#### Peripheral Multiplexing on I/O lines

#### 3.1.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following table describes the peripheral signals multiplexed to the GPIO lines.

|            |            |             | G       |        |                                       |                  |                    |                  | GPIO F            | unction           |                   |                            |                |

|------------|------------|-------------|---------|--------|---------------------------------------|------------------|--------------------|------------------|-------------------|-------------------|-------------------|----------------------------|----------------|

| 48-<br>pin | 64-<br>pin | Pin<br>Name | PI<br>O | Supply | Pad<br>Type                           | Α                | в                  | С                | D                 | Е                 | F                 | G                          | н              |

| 11         | 15         | PA00        | 0       | VDDIO  | Normal<br>I/O                         | USART0-<br>TXD   | USART1-<br>RTS     | SPI-<br>NPCS[2]  |                   | PWMA-<br>PWMA[0]  |                   | SCIF-<br>GCLK[0]           | CAT-<br>CSA[2] |

| 14         | 18         | PA01        | 1       | VDDIO  | Normal<br>I/O                         | USART0-<br>RXD   | USART1-<br>CTS     | SPI-<br>NPCS[3]  | USART1-<br>CLK    | PWMA-<br>PWMA[1]  | ACIFB-<br>ACAP[0] | TWIMS0-<br>TWALM           | CAT-<br>CSA[1] |

| 13         | 17         | PA02        | 2       | VDDIO  | High-<br>drive I/O                    | USART0-<br>RTS   | ADCIFB-<br>TRIGGER | USART2-<br>TXD   | TC0-A0            | PWMA-<br>PWMA[2]  | ACIFB-<br>ACBP[0] | USART0-<br>CLK             | CAT-<br>CSA[3] |

| 4          | 6          | PA03        | 3       | VDDIO  | Normal<br>I/O                         | USART0-<br>CTS   | SPI-<br>NPCS[1]    | USART2-<br>TXD   | TC0-B0            | PWMA-<br>PWMA[3]  | ACIFB-<br>ACBN[3] | USART0-<br>CLK             | CAT-<br>CSB[3] |

| 28         | 38         | PA04        | 4       | VDDIO  | Normal<br>I/O                         | SPI-MISO         | TWIMS0-<br>TWCK    | USART1-<br>RXD   | TC0-B1            | PWMA-<br>PWMA[4]  | ACIFB-<br>ACBP[1] |                            | CAT-<br>CSA[7] |

| 12         | 16         | PA05        | 5       | VDDIO  | Normal<br>I/O (TWI)                   | SPI-MOSI         | TWIMS1-<br>TWCK    | USART1-<br>TXD   | TC0-A1            | PWMA-<br>PWMA[5]  | ACIFB-<br>ACBN[0] | TWIMS0-<br>TWD             | CAT-<br>CSB[7] |

| 10         | 14         | PA06        | 6       | VDDIO  | High-<br>drive I/O,<br>5V<br>tolerant | SPI-SCK          | USART2-<br>TXD     | USART1-<br>CLK   | ТС0-В0            | PWMA-<br>PWMA[6]  | EIC-<br>EXTINT[2] | SCIF-<br>GCLK[1]           | CAT-<br>CSB[1] |

|            | 19         | PA07        | 7       | VDDIO  | Normal<br>I/O (TWI)                   | SPI-<br>NPCS[0]  | USART2-<br>RXD     | TWIMS1-<br>TWALM | TWIMS0-<br>TWCK   | PWMA-<br>PWMA[7]  | ACIFB-<br>ACAN[0] | EIC-<br>NMI<br>(EXTINT[0]) | CAT-<br>CSB[2] |

| 3          | 3          | PA08        | 8       | VDDIO  | High-<br>drive I/O                    | USART1-<br>TXD   | SPI-<br>NPCS[2]    | TC0-A2           | ADCIFB-<br>ADP[0] | PWMA-<br>PWMA[8]  |                   |                            | CAT-<br>CSA[4] |

| 2          | 2          | PA09        | 9       | VDDIO  | High-<br>drive I/O                    | USART1-<br>RXD   | SPI-<br>NPCS[3]    | TC0-B2           | ADCIFB-<br>ADP[1] | PWMA-<br>PWMA[9]  | SCIF-<br>GCLK[2]  | EIC-<br>EXTINT[1]          | CAT-<br>CSB[4] |

| 46         | 62         | PA10        | 10      | VDDIO  | Normal<br>I/O                         | TWIMS0-<br>TWD   |                    | TC0-A0           |                   | PWMA-<br>PWMA[10] | ACIFB-<br>ACAP[1] | SCIF-<br>GCLK[2]           | CAT-<br>CSA[5] |

| 27         | 35         | PA11        | 11      | VDDIN  | Normal<br>I/O                         |                  |                    |                  |                   | PWMA-<br>PWMA[11] |                   |                            |                |

| 47         | 63         | PA12        | 12      | VDDIO  | Normal<br>I/O                         |                  | USART2-<br>CLK     | TC0-CLK1         | CAT-SMP           | PWMA-<br>PWMA[12] | ACIFB-<br>ACAN[1] | SCIF-<br>GCLK[3]           | CAT-<br>CSB[5] |

| 26         | 34         | PA13        | 13      | VDDIN  | Normal<br>I/O                         | GLOC-<br>OUT[0]  | GLOC-<br>IN[7]     | TC0-A0           | SCIF-<br>GCLK[2]  | PWMA-<br>PWMA[13] | CAT-SMP           | EIC-<br>EXTINT[2]          | CAT-<br>CSA[0] |

| 36         | 48         | PA14        | 14      | VDDIO  | Normal<br>I/O                         | ADCIFB-<br>AD[0] | TC0-CLK2           | USART2-<br>RTS   | CAT-SMP           | PWMA-<br>PWMA[14] |                   | SCIF-<br>GCLK[4]           | CAT-<br>CSA[6] |

| 37         | 49         | PA15        | 15      | VDDIO  | Normal<br>I/O                         | ADCIFB-<br>AD[1] | TC0-CLK1           |                  | GLOC-<br>IN[6]    | PWMA-<br>PWMA[15] | CAT-<br>SYNC      | EIC-<br>EXTINT[3]          | CAT-<br>CSB[6] |

| 38         | 50         | PA16        | 16      | VDDIO  | Normal<br>I/O                         | ADCIFB-<br>AD[2] | TC0-CLK0           |                  | GLOC-<br>IN[5]    | PWMA-<br>PWMA[16] | ACIFB-<br>ACREFN  | EIC-<br>EXTINT[4]          | CAT-<br>CSA[8] |

Table 3-1.

GPIO Controller Function Multiplexing

Table 3-1.

GPIO Controller Function Multiplexing

| Table 3 | -1. | GPIOC | ontro | lier Func | tion Multi                                       | piexing          |                   |                  |                    |                   |                         |                            |                 |

|---------|-----|-------|-------|-----------|--------------------------------------------------|------------------|-------------------|------------------|--------------------|-------------------|-------------------------|----------------------------|-----------------|

| 39      | 51  | PA17  | 17    | VDDIO     | Normal<br>I/O (TWI)                              |                  | TC0-A1            | USART2-<br>CTS   | TWIMS1-<br>TWD     | PWMA-<br>PWMA[17] | CAT-SMP                 | CAT-DIS                    | CAT-<br>CSB[8]  |

| 41      | 53  | PA18  | 18    | VDDIO     | Normal<br>I/O                                    | ADCIFB-<br>AD[4] | TC0-B1            |                  | GLOC-<br>IN[4]     | PWMA-<br>PWMA[18] | CAT-<br>SYNC            | EIC-<br>EXTINT[5]          | CAT-<br>CSB[0]  |

| 40      | 52  | PA19  | 19    | VDDIO     | Normal<br>I/O                                    | ADCIFB-<br>AD[5] |                   | TC0-A2           | TWIMS1-<br>TWALM   | PWMA-<br>PWMA[19] | SCIF-<br>GCLK_IN[<br>0] | CAT-SYNC                   | CAT-<br>CSA[10] |

| 25      | 33  | PA20  | 20    | VDDIN     | Normal<br>I/O                                    | USART2-<br>TXD   |                   | TC0-A1           | GLOC-<br>IN[3]     | PWMA-<br>PWMA[20] | SCIF-<br>RC32OUT        |                            | CAT-<br>CSA[12] |

| 24      | 32  | PA21  | 21    | VDDIN     | Normal<br>I/O (TWI,<br>5V<br>tolerant,<br>SMBus) | USART2-<br>RXD   | TWIMS0-<br>TWD    | TC0-B1           | ADCIFB-<br>TRIGGER | PWMA-<br>PWMA[21] | PWMA-<br>PWMAOD<br>[21] | SCIF-<br>GCLK[0]           | CAT-<br>SMP     |

| 9       | 13  | PA22  | 22    | VDDIO     | Normal<br>I/O                                    | USART0-<br>CTS   | USART2-<br>CLK    | TC0-B2           | CAT-SMP            | PWMA-<br>PWMA[22] | ACIFB-<br>ACBN[2]       |                            | CAT-<br>CSB[10] |

| 6       | 8   | PB00  | 32    | VDDIO     | Normal<br>I/O                                    | USART3-<br>TXD   | ADCIFB-<br>ADP[0] | SPI-<br>NPCS[0]  | TC0-A1             | PWMA-<br>PWMA[23] | ACIFB-<br>ACAP[2]       | TC1-A0                     | CAT-<br>CSA[9]  |

|         | 20  | PB01  | 33    | VDDIO     | High-<br>drive I/O                               | USART3-<br>RXD   | ADCIFB-<br>ADP[1] | SPI-SCK          | TC0-B1             | PWMA-<br>PWMA[24] |                         | TC1-A1                     | CAT-<br>CSB[9]  |

| 7       | 9   | PB02  | 34    | VDDIO     | Normal<br>I/O                                    | USART3-<br>RTS   | USART3-<br>CLK    | SPI-MISO         | TC0-A2             | PWMA-<br>PWMA[25] | ACIFB-<br>ACAN[2]       | SCIF-<br>GCLK[1]           | CAT-<br>CSB[11] |

| 8       | 10  | PB03  | 35    | VDDIO     | Normal<br>I/O                                    | USART3-<br>CTS   | USART3-<br>CLK    | SPI-MOSI         | TC0-B2             | PWMA-<br>PWMA[26] | ACIFB-<br>ACBP[2]       | TC1-A2                     | CAT-<br>CSA[11] |

| 21      | 29  | PB04  | 36    | VDDIN     | Normal<br>I/O (TWI,<br>5V<br>tolerant,<br>SMBus) | TC1-A0           | USART1-<br>RTS    | USART1-<br>CLK   | TWIMS0-<br>TWALM   | PWMA-<br>PWMA[27] | PWMA-<br>PWMAOD<br>[27] | TWIMS1-<br>TWCK            | CAT-<br>CSA[14] |

| 20      | 28  | PB05  | 37    | VDDIN     | Normal<br>I/O (TWI,<br>5V<br>tolerant,<br>SMBus) | TC1-B0           | USART1-<br>CTS    | USART1-<br>CLK   | TWIMS0-<br>TWCK    | PWMA-<br>PWMA[28] | PWMA-<br>PWMAOD<br>[28] | SCIF-<br>GCLK[3]           | CAT-<br>CSB[14] |

| 30      | 42  | PB06  | 38    | VDDIO     | Normal<br>I/O                                    | TC1-A1           | USART3-<br>TXD    | ADCIFB-<br>AD[6] | GLOC-<br>IN[2]     | PWMA-<br>PWMA[29] | ACIFB-<br>ACAN[3]       | EIC-<br>NMI<br>(EXTINT[0]) | CAT-<br>CSB[13] |

| 31      | 43  | PB07  | 39    | VDDIO     | Normal<br>I/O                                    | TC1-B1           | USART3-<br>RXD    | ADCIFB-<br>AD[7] | GLOC-<br>IN[1]     | PWMA-<br>PWMA[30] | ACIFB-<br>ACAP[3]       | EIC-<br>EXTINT[1]          | CAT-<br>CSA[13] |

| 32      | 44  | PB08  | 40    | VDDIO     | Normal<br>I/O                                    | TC1-A2           | USART3-<br>RTS    | ADCIFB-<br>AD[8] | GLOC-<br>IN[0]     | PWMA-<br>PWMA[31] | CAT-<br>SYNC            | EIC-<br>EXTINT[2]          | CAT-<br>CSB[12] |

| 29      | 39  | PB09  | 41    | VDDIO     | Normal<br>I/O                                    | TC1-B2           | USART3-<br>CTS    | USART3-<br>CLK   |                    | PWMA-<br>PWMA[32] | ACIFB-<br>ACBN[1]       | EIC-<br>EXTINT[3]          | CAT-<br>CSB[15] |

| 23      | 31  | PB10  | 42    | VDDIN     | Normal<br>I/O                                    | TC1-CLK0         | USART1-<br>TXD    | USART3-<br>CLK   | GLOC-<br>OUT[1]    | PWMA-<br>PWMA[33] | SCIF-<br>GCLK_IN[<br>1] | EIC-<br>EXTINT[4]          | CAT-<br>CSB[16] |

| 44      | 56  | PB11  | 43    | VDDIO     | Normal<br>I/O                                    | TC1-CLK1         | USART1-<br>RXD    |                  | ADCIFB-<br>TRIGGER | PWMA-<br>PWMA[34] | CAT-<br>VDIVEN          | EIC-<br>EXTINT[5]          | CAT-<br>CSA[16] |

| 5       | 7   | PB12  | 44    | VDDIO     | Normal<br>I/O                                    | TC1-CLK2         |                   | TWIMS1-<br>TWALM | CAT-<br>SYNC       | PWMA-<br>PWMA[35] | ACIFB-<br>ACBP[3]       | SCIF-<br>GCLK[4]           | CAT-<br>CSA[15] |

| 15      | 22  | PB13  | 45    | VDDIN     | USB I/O                                          | USBC-DM          | USART3-<br>TXD    |                  | TC1-A1             | PWMA-<br>PWMA[7]  | ADCIFB-<br>ADP[1]       | SCIF-<br>GCLK[5]           | CAT-<br>CSB[2]  |

| 16      | 23  | PB14  | 46    | VDDIN     | USB I/O                                          | USBC-DP          | USART3-<br>RXD    |                  | TC1-B1             | PWMA-<br>PWMA[24] |                         | SCIF-<br>GCLK[5]           | CAT-<br>CSB[9]  |

| Table 5 | -1. |      | JIIIO | lier Func |                    | pieking            |                |                 |          |                   |                         |                            |                 |

|---------|-----|------|-------|-----------|--------------------|--------------------|----------------|-----------------|----------|-------------------|-------------------------|----------------------------|-----------------|

|         | 57  | PB15 | 47    | VDDIO     | High-<br>drive I/O | ABDACB-<br>CLK     | IISC-<br>IMCK  | SPI-SCK         | TC0-CLK2 | PWMA-<br>PWMA[8]  |                         | SCIF-<br>GCLK[3]           | CAT-<br>CSB[4]  |

|         | 58  | PB16 | 48    | VDDIO     | Normal<br>I/O      | ABDACB-<br>DAC[0]  | IISC-ISCK      | USART0-<br>TXD  |          | PWMA-<br>PWMA[9]  |                         | SCIF-<br>GCLK[2]           | CAT-<br>CSA[5]  |

|         | 59  | PB17 | 49    | VDDIO     | Normal<br>I/O      | ABDACB-<br>DAC[1]  | IISC-IWS       | USART0-<br>RXD  |          | PWMA-<br>PWMA[10] |                         |                            | CAT-<br>CSB[5]  |

|         | 60  | PB18 | 50    | VDDIO     | Normal<br>I/O      | ABDACB-<br>DACN[0] | IISC-ISDI      | USART0-<br>RTS  |          | PWMA-<br>PWMA[12] |                         |                            | CAT-<br>CSA[0]  |

|         | 4   | PB19 | 51    | VDDIO     | Normal<br>I/O      | ABDACB-<br>DACN[1] | IISC-ISDO      | USART0-<br>CTS  |          | PWMA-<br>PWMA[20] |                         | EIC-<br>EXTINT[1]          | CAT-<br>CSA[12] |

|         | 5   | PB20 | 52    | VDDIO     | Normal<br>I/O      | TWIMS1-<br>TWD     | USART2-<br>RXD | SPI-<br>NPCS[1] | TC0-A0   | PWMA-<br>PWMA[21] | USART1-<br>RTS          | USART1-<br>CLK             | CAT-<br>CSA[14] |

|         | 40  | PB21 | 53    | VDDIO     | Normal<br>I/O      | TWIMS1-<br>TWCK    | USART2-<br>TXD | SPI-<br>NPCS[2] | TC0-B0   | PWMA-<br>PWMA[28] | USART1-<br>CTS          | USART1-<br>CLK             | CAT-<br>CSB[14] |

|         | 41  | PB22 | 54    | VDDIO     | Normal<br>I/O      | TWIMS1-<br>TWALM   |                | SPI-<br>NPCS[3] | TC0-CLK0 | PWMA-<br>PWMA[27] | ADCIFB-<br>TRIGGER      | SCIF-<br>GCLK[0]           | CAT-<br>CSA[8]  |

|         | 54  | PB23 | 55    | VDDIO     | Normal<br>I/O      | SPI-MISO           | USART2-<br>RTS | USART2-<br>CLK  | TC0-A2   | PWMA-<br>PWMA[0]  | CAT-SMP                 | SCIF-<br>GCLK[6]           | CAT-<br>CSA[4]  |

|         | 55  | PB24 | 56    | VDDIO     | Normal<br>I/O      | SPI-MOSI           | USART2-<br>CTS | USART2-<br>CLK  | TC0-B2   | PWMA-<br>PWMA[1]  | ADCIFB-<br>ADP[1]       | SCIF-<br>GCLK[7]           | CAT-<br>CSA[2]  |

|         | 61  | PB25 | 57    | VDDIO     | Normal<br>I/O      | SPI-<br>NPCS[0]    | USART1-<br>RXD |                 | TC0-A1   | PWMA-<br>PWMA[2]  | SCIF-<br>GCLK_IN[<br>2] | SCIF-<br>GCLK[8]           | CAT-<br>CSA[3]  |

|         | 21  | PB26 | 58    | VDDIO     | Normal<br>I/O      | SPI-SCK            | USART1-<br>TXD |                 | TC0-B1   | PWMA-<br>PWMA[3]  | ADCIFB-<br>ADP[0]       | SCIF-<br>GCLK[9]           | CAT-<br>CSB[3]  |

|         | 24  | PB27 | 59    | VDDIN     | Normal<br>I/O      |                    | USART1-<br>RXD |                 | TC0-CLK1 | PWMA-<br>PWMA[4]  | ADCIFB-<br>ADP[1]       | EIC-<br>NMI<br>(EXTINT[0]) | CAT-<br>CSA[9]  |

Table 3-1.

GPIO Controller Function Multiplexing

#### 3.2 See Section 3.3 for a description of the various peripheral signals.

Refer to "Electrical Characteristics" on page 991 for a description of the electrical properties of the pin types used.

#### 3.2.1 TWI, 5V Tolerant, and SMBUS Pins

Some normal I/O pins offer TWI, 5V tolerance, and SMBUS features. These features are only available when either of the TWI functions or the PWMAOD function in the PWMA are selected for these pins.

Refer to the "Electrical Characteristics" on page 991 for a description of the electrical properties of the TWI, 5V tolerance, and SMBUS pins.

#### 3.2.2 Peripheral Functions

Each GPIO line can be assigned to one of several peripheral functions. The following table describes how the various peripheral functions are selected. The last listed function has priority in case multiple functions are enabled on the same pin.

**Table 3-2.**Peripheral Functions

| Function                              | Description                               |

|---------------------------------------|-------------------------------------------|

| GPIO Controller Function multiplexing | GPIO and GPIO peripheral selection A to H |

| Nexus OCD AUX port connections        | OCD trace system                          |

| aWire DATAOUT                         | aWire output in two-pin mode              |

| JTAG port connections                 | JTAG debug port                           |

| Oscillators                           | OSC0, OSC32                               |

#### 3.2.3 JTAG Port Connections

If the JTAG is enabled, the JTAG will take control over a number of pins, irrespectively of the I/O Controller configuration.

| 48-pin | 64-pin | Pin name | JTAG pin |

|--------|--------|----------|----------|

| 11     | 15     | PA00     | ТСК      |

| 14     | 18     | PA01     | TMS      |

| 13     | 17     | PA02     | TDO      |

| 4      | 6      | PA03     | TDI      |

#### 3.2.4 Nexus OCD AUX Port Connections

If the OCD trace system is enabled, the trace system will take control over a number of pins, irrespectively of the I/O Controller configuration. Two different OCD trace pin mappings are possible, depending on the configuration of the OCD AXS register. For details, see the AVR32 UC Technical Reference Manual.

|        | Nexus OOB NOX |       |

|--------|---------------|-------|

| Pin    | AXS=1         | AXS=0 |

| EVTI_N | PA05          | PB08  |

| MDO[5] | PA10          | PB00  |

| MDO[4] | PA18          | PB04  |

| MDO[3] | PA17          | PB05  |

| MDO[2] | PA16          | PB03  |

| MDO[1] | PA15          | PB02  |

| MDO[0] | PA14          | PB09  |

Table 3-4.

Nexus OCD AUX Port Connections

| Pin     | AXS=1 | AXS=0 |

|---------|-------|-------|

| EVTO_N  | PA04  | PA04  |

| МСКО    | PA06  | PB01  |

| MSEO[1] | PA07  | PB11  |

| MSEO[0] | PA11  | PB12  |

Table 3-4. Nexus OCD AUX Port Connections

#### 3.2.5 Oscillator Pinout

The oscillators are not mapped to the normal GPIO functions and their muxings are controlled by registers in the System Control Interface (SCIF). Please refer to the SCIF chapter for more information about this.

#### Table 3-5.Oscillator Pinout

| 48-pin | 64-pin | Pin Name | Oscillator Pin |

|--------|--------|----------|----------------|

| 3      | 3      | PA08     | XINO           |

| 46     | 62     | PA10     | XIN32          |

| 26     | 34     | PA13     | XIN32_2        |

| 2      | 2      | PA09     | XOUT0          |

| 47     | 63     | PA12     | XOUT32         |

| 25     | 33     | PA20     | XOUT32_2       |

#### 3.2.6 Other Functions

The functions listed in Table 3-6 are not mapped to the normal GPIO functions. The aWire DATA pin will only be active after the aWire is enabled. The aWire DATAOUT pin will only be active after the aWire is enabled and the 2\_PIN\_MODE command has been sent. The WAKE\_N pin is always enabled. Please refer to Section 6.1.4.2 on page 45 for constraints on the WAKE\_N pin.

#### Table 3-6.Other Functions

| 48-pin | 64-pin | Pin Name | Function      |

|--------|--------|----------|---------------|

| 27     | 35     | PA11     | WAKE_N        |

| 22     | 30     | RESET_N  | aWire DATA    |

| 11     | 15     | PA00     | aWire DATAOUT |

#### 3.3 Signal Descriptions

The following table gives details on signal name classified by peripheral.

| Signal Name       | Function                             | Туре             | Active<br>Level | Comments |

|-------------------|--------------------------------------|------------------|-----------------|----------|

|                   | Audio Bitstream I                    | DAC - ABDACB     |                 |          |

| CLK               | D/A Clock out                        | Output           |                 |          |

| DAC1 - DAC0       | D/A Bitstream out                    | Output           |                 |          |

| DACN1 - DACN0     | D/A Inverted bitstream out           | Output           |                 |          |

|                   | Analog Comparator                    | Interface - ACIF | в               |          |

| ACAN3 - ACAN0     | Negative inputs for comparators "A"  | Analog           |                 |          |

| ACAP3 - ACAP0     | Positive inputs for comparators "A"  | Analog           |                 |          |

| ACBN3 - ACBN0     | Negative inputs for comparators "B"  | Analog           |                 |          |

| ACBP3 - ACBP0     | Positive inputs for comparators "B"  | Analog           |                 |          |

| ACREFN            | Common negative reference            | Analog           |                 |          |

|                   | ADC Interface                        | e - ADCIFB       |                 |          |

| AD8 - AD0         | Analog Signal                        | Analog           |                 |          |

| ADP1 - ADP0       | Drive Pin for resistive touch screen | Output           |                 |          |

| TRIGGER           | External trigger                     | Input            |                 |          |

|                   | aWire -                              | AW               |                 |          |

| DATA              | aWire data                           | I/O              |                 |          |

| DATAOUT           | aWire data output for 2-pin mode     | I/O              |                 |          |

|                   | Capacitive Touch                     | Module - CAT     |                 |          |

| CSA16 - CSA0      | Capacitive Sense A                   | I/O              |                 |          |

| CSB16 - CSB0      | Capacitive Sense B                   | I/O              |                 |          |

| DIS               | Discharge current control            | Analog           |                 |          |

| SMP               | SMP signal                           | Output           |                 |          |

| SYNC              | Synchronize signal                   | Input            |                 |          |

| VDIVEN            | Voltage divider enable               | Output           |                 |          |

|                   | External Interrupt                   | Controller - EIC |                 |          |

| NMI (EXTINT0)     | Non-Maskable Interrupt               | Input            |                 |          |

| EXTINT5 - EXTINT1 | External interrupt                   | Input            |                 |          |

|                   | Glue Logic Cont                      | troller - GLOC   | •               | •        |

| IN7 - IN0         | Inputs to lookup tables              | Input            |                 |          |

| OUT1 - OUT0       | Outputs from lookup tables           | Output           |                 |          |

|                   | Inter-IC Sound (I2S)                 | Controller - IIS | С               |          |

**Table 3-7.**Signal Descriptions List

| Table 3-7. Signal De  | escriptions List                        |                    |     |                                          |

|-----------------------|-----------------------------------------|--------------------|-----|------------------------------------------|

| IMCK                  | I2S Master Clock                        | Output             |     |                                          |

| ISCK                  | I2S Serial Clock                        | I/O                |     |                                          |

| ISDI                  | I2S Serial Data In                      | Input              |     |                                          |

| ISDO                  | I2S Serial Data Out                     | Output             |     |                                          |

| IWS                   | I2S Word Select                         | I/O                |     |                                          |

|                       | JTAG module                             | - JTAG             |     |                                          |

| ТСК                   | Test Clock                              | Input              |     |                                          |

| TDI                   | Test Data In                            | Input              |     |                                          |

| TDO                   | Test Data Out                           | Output             |     |                                          |

| TMS                   | Test Mode Select                        | Input              |     |                                          |

|                       | Power Manag                             | jer - PM           |     |                                          |

| RESET_N               | Reset                                   | Input              | Low |                                          |

|                       | Pulse Width Modulation                  | Controller - PV    | VMA |                                          |

| PWMA35 - PWMA0        | PWMA channel waveforms                  | Output             |     |                                          |

| PWMAOD35 -<br>PWMAOD0 | PWMA channel waveforms, open drain mode | Output             |     | Not all channels support open drain mode |

|                       | System Control Int                      | erface - SCIF      |     |                                          |

| GCLK9 - GCLK0         | Generic Clock Output                    | Output             |     |                                          |

| GCLK_IN2 - GCLK_IN0   | Generic Clock Input                     | Input              |     |                                          |

| RC32OUT               | RC32K output at startup                 | Output             |     |                                          |

| XIN0                  | Crystal 0 Input                         | Analog/<br>Digital |     |                                          |

| XIN32                 | Crystal 32 Input (primary location)     | Analog/<br>Digital |     |                                          |

| XIN32_2               | Crystal 32 Input (secondary location)   | Analog/<br>Digital |     |                                          |

| XOUT0                 | Crystal 0 Output                        | Analog             |     |                                          |

| XOUT32                | Crystal 32 Output (primary location)    | Analog             |     |                                          |

| XOUT32_2              | Crystal 32 Output (secondary location)  | Analog             |     |                                          |

|                       | Serial Peripheral Ir                    | nterface - SPI     |     |                                          |

| MISO                  | Master In Slave Out                     | I/O                |     |                                          |

| MOSI                  | Master Out Slave In                     | I/O                |     |                                          |

| NPCS3 - NPCS0         | SPI Peripheral Chip Select              | I/O                | Low |                                          |

| SCK                   | Clock                                   | I/O                |     |                                          |

|                       | Timer/Counter -                         | TC0, TC1           |     |                                          |

| A0                    | Channel 0 Line A                        | I/O                |     |                                          |

| A1                    | Channel 1 Line A                        | I/O                |     |                                          |

| A2                    | Channel 2 Line A                        | I/O                |     |                                          |

Table 3-7.Signal Descriptions List

| Channel 0 Line B                       | I/O                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel 1 Line B                       | I/O                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Channel 2 Line B                       | I/O                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Channel 0 External Clock Input         | Input                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Channel 1 External Clock Input         | Input                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Channel 2 External Clock Input         | Input                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Two-wire Interface - TW                | IMSO, TWIMS                                                                                                                                                                                                                                                                                                                                     | S1                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                    |

| SMBus SMBALERT                         | I/O                                                                                                                                                                                                                                                                                                                                             | Low                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Two-wire Serial Clock                  | I/O                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Two-wire Serial Data                   | I/O                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| ynchronous Asynchronous Receiver Trans | smitter - USA                                                                                                                                                                                                                                                                                                                                   | RT0, USART                                                                                                                                                                                                                                                                                                                         | 1, USART2, USART3                                                                                                                                                                                                                                                                                                                                                                                  |

| Clock                                  | I/O                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Clear To Send                          | Input                                                                                                                                                                                                                                                                                                                                           | Low                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Request To Send                        | Output                                                                                                                                                                                                                                                                                                                                          | Low                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Receive Data                           | Input                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| Transmit Data                          | Output                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | Channel 1 Line B<br>Channel 2 Line B<br>Channel 0 External Clock Input<br>Channel 1 External Clock Input<br>Channel 2 External Clock Input<br>Two-wire Interface - TW<br>SMBus SMBALERT<br>Two-wire Serial Clock<br>Two-wire Serial Data<br>(nchronous Asynchronous Receiver Trans<br>Clock<br>Clear To Send<br>Request To Send<br>Receive Data | Channel 1 Line BI/OChannel 2 Line BI/OChannel 0 External Clock InputInputChannel 1 External Clock InputInputChannel 1 External Clock InputInputChannel 2 External Clock InputInputSMBus SMBALERTI/OTwo-wire Serial ClockI/OTwo-wire Serial ClockI/OTwo-wire Serial DataI/OOrder To SendInputRequest To SendOutputReceive DataInput | Channel 1 Line BI/OChannel 2 Line BI/OChannel 0 External Clock InputInputChannel 1 External Clock InputInputChannel 2 External Clock InputInputChannel 2 External Clock InputInputTwo-wire Interface - TWIMSO, TWIMS1SMBus SMBALERTI/OTwo-wire Serial ClockI/OTwo-wire Serial ClockI/OTwo-wire Serial DataI/OI/OLowInputInputClockI/OClockI/OClockInputLowRequest To SendReceive DataInputInputLow |

Table 3-7.Signal Descriptions List

Note: 1. ADCIFB: AD3 does not exist.

| Signal Name Function |                                              | Туре                  | Active<br>Level | Comments                                                                  |

|----------------------|----------------------------------------------|-----------------------|-----------------|---------------------------------------------------------------------------|

|                      | Power                                        |                       |                 |                                                                           |

| VDDCORE              | Core Power Supply / Voltage Regulator Output | Power<br>Input/Output |                 | 1.62V to 1.98V                                                            |

| VDDIO                | I/O Power Supply                             | Power Input           |                 | 1.62V to 3.6V. VDDIO should<br>always be equal to or lower than<br>VDDIN. |

| VDDANA               | Analog Power Supply                          | Power Input           |                 | 1.62V to 1.98V                                                            |

| ADVREFP              | Analog Reference Voltage                     | Power Input           |                 | 1.62V to 1.98V                                                            |

| VDDIN                | Voltage Regulator Input                      | Power Input           |                 | 1.62V to 3.6V <sup>(1)</sup>                                              |

| GNDANA               | Analog Ground                                | Ground                |                 |                                                                           |

| GND                  | Ground                                       | Ground                |                 |                                                                           |

|                      | Auxiliary Port -                             | AUX                   |                 |                                                                           |

| МСКО                 | Trace Data Output Clock                      | Output                |                 |                                                                           |

| MDO5 - MDO0          | Trace Data Output                            | Output                |                 |                                                                           |

| Signal Name   | Function                           | Туре    | Active<br>Level | Comments |

|---------------|------------------------------------|---------|-----------------|----------|

| MSEO1 - MSEO0 | Trace Frame Control                | Output  |                 |          |

| EVTI_N        | Event In                           | Input   | Low             |          |

| EVTO_N        | Event Out                          | Output  | Low             |          |

|               | General Purpose                    | I/O pin |                 |          |

| PA22 - PA00   | Parallel I/O Controller I/O Port 0 | I/O     |                 |          |

| PB27 - PB00   | Parallel I/O Controller I/O Port 1 | I/O     |                 |          |

#### Table 3-8. Signal Description List, Continued

Note: 1. See Section 6. on page 40

#### 3.4 I/O Line Considerations

#### 3.4.1 JTAG Pins

The JTAG is enabled if TCK is low while the RESET\_N pin is released. The TCK, TMS, and TDI pins have pull-up resistors when JTAG is enabled. The TCK pin always has pull-up enabled during reset. The TDO pin is an output, driven at VDDIO, and has no pull-up resistor. The JTAG pins can be used as GPIO pins and multiplexed with peripherals when the JTAG is disabled. Please refer to Section 3.2.3 on page 13 for the JTAG port connections.

#### 3.4.2 PA00

Note that PA00 is multiplexed with TCK. PA00 GPIO function must only be used as output in the application.

#### 3.4.3 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIN. As the product integrates a power-on reset detector, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

The RESET\_N pin is also used for the aWire debug protocol. When the pin is used for debugging, it must not be driven by external circuitry.

#### 3.4.4 TWI Pins PA21/PB04/PB05

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with spike filtering. When used as GPIO pins or used for other peripherals, the pins have the same characteristics as other GPIO pins. Selected pins are also SMBus compliant (refer to Section on page 10). As required by the SMBus specification, these pins provide no leakage path to ground when the ATUC64/128/256L3/4U is powered down. This allows other devices on the SMBus to continue communicating even though the ATUC64/128/256L3/4U is not powered.

After reset a TWI function is selected on these pins instead of the GPIO. Please refer to the GPIO Module Configuration chapter for details.

Atmel

#### 3.4.5 TWI Pins PA05/PA07/PA17

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and inputs with spike filtering. When used as GPIO pins or used for other peripherals, the pins have the same characteristics as other GPIO pins.

After reset a TWI function is selected on these pins instead of the GPIO. Please refer to the GPIO Module Configuration chapter for details.

#### 3.4.6 GPIO Pins

All the I/O lines integrate a pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up resistors disabled, except PA00 which has the pull-up resistor enabled. PA20 selects SCIF-RC32OUT (GPIO Function F) as default enabled after reset.

#### 3.4.7 High-drive Pins

The six pins PA02, PA06, PA08, PA09, PB01, and PB15 have high-drive output capabilities. Refer to Section 34. on page 991 for electrical characteristics.

#### 3.4.8 USB Pins PB13/PB14

When these pins are used for USB, the pins are behaving according to the USB specification. When used as GPIO pins or used for other peripherals, the pins have the same behaviour as other normal I/O pins, but the characteristics are different. Refer to Section 34. on page 991 for electrical characteristics.

To be able to use the USB I/O the VDDIN power supply must be 3.3V nominal.

#### 3.4.9 RC32OUT Pin

#### 3.4.9.1 Clock output at startup

After power-up, the clock generated by the 32kHz RC oscillator (RC32K) will be output on PA20, even when the device is still reset by the Power-On Reset Circuitry. This clock can be used by the system to start other devices or to clock a switching regulator to rise the power supply voltage up to an acceptable value.

The clock will be available on PA20, but will be disabled if one of the following conditions are true:

- PA20 is configured to use a GPIO function other than F (SCIF-RC32OUT)

- PA20 is configured as a General Purpose Input/Output (GPIO)

- The bit FRC32 in the Power Manager PPCR register is written to zero (refer to the Power Manager chapter)

The maximum amplitude of the clock signal will be defined by VDDIN.

Once the RC32K output on PA20 is disabled it can never be enabled again.

#### 3.4.9.2 XOUT32\_2 function

PA20 selects RC32OUT as default enabled after reset. This function is not automatically disabled when the user enables the XOUT32\_2 function on PA20. This disturbs the oscillator and may result in the wrong frequency. To avoid this, RC32OUT must be disabled when XOUT32\_2 is enabled.

#### 3.4.10 ADC Input Pins

These pins are regular I/O pins powered from the VDDIO. However, when these pins are used for ADC inputs, the voltage applied to the pin must not exceed 1.98V. Internal circuitry ensures that the pin cannot be used as an analog input pin when the I/O drives to VDD. When the pins are not used for ADC inputs, the pins may be driven to the full I/O voltage range.

### 4. Mechanical Characteristics

### 4.1 Thermal Considerations

#### 4.1.1 Thermal Data

Table 4-1 summarizes the thermal resistance data depending on the package.