# Automotive-grade 12-channel LED driver with open detection, local dimming, bus driven and standalone operations

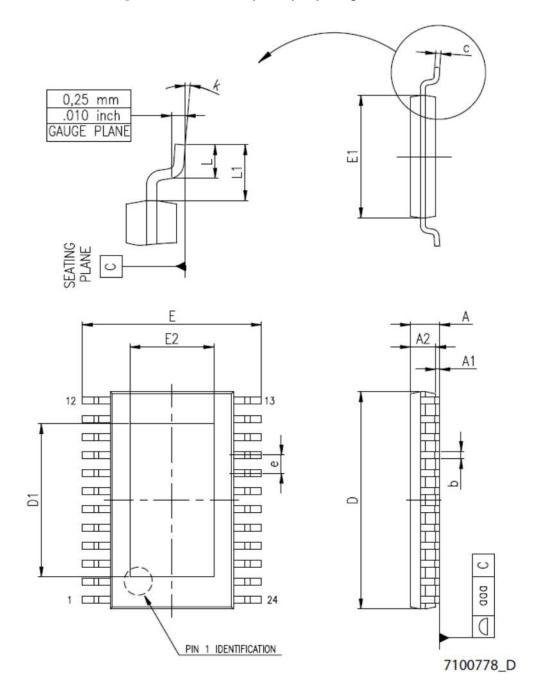

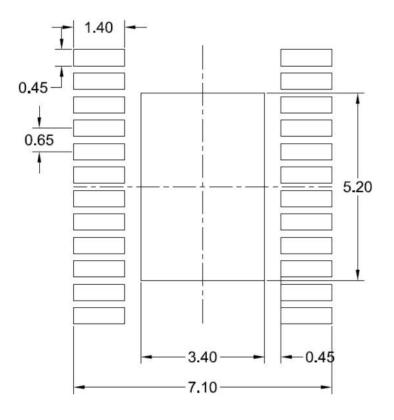

HTSSOP24 exposed pad

#### **Features**

- · Designed for automotive applications

- 12 constant current output channels

- 19 V current generator rated voltage

- Output current: from 6 mA to 60 mA

- · Current programmable by a single external resistor

- 7-bit PWM local brightness control

- · Slow turn-on/off time, gradual output delay and dithered clock for EMI reduction

- Error detection for open LEDs

- Supply voltage: from 5.5 V to 38 V

- Thermal shutdown and overtemperature alert

- · Standalone and bus-driven mode

- · Custom configuration by OTP with Redundancy and ECC

- 400 kHz fast I<sup>2</sup>C interface with selectable extended Hamming encoding

- · Wired-OR error flag connection

#### **Applications**

- · Automotive rear lights

- Automotive interior lighting

#### Maturity status link

ALED1262ZT

| Device summary |                      |  |  |  |  |

|----------------|----------------------|--|--|--|--|

| Order code     | ALED1262ZT           |  |  |  |  |

|                | ALED1262ZTTR         |  |  |  |  |

| Package        | HTSSOP24 exposed pad |  |  |  |  |

| Packing        | 62 parts per tube    |  |  |  |  |

|                | 2500 parts per reel  |  |  |  |  |

#### **Description**

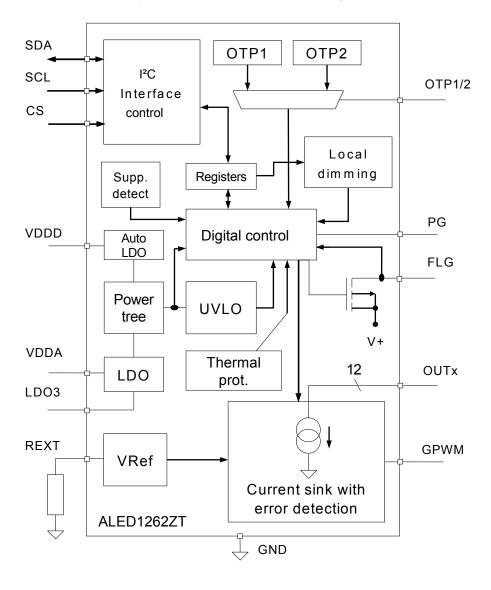

The ALED1262ZT is a monolithic 12 output LED driver designed for automotive exterior and interior lighting applications. The ALED1262ZT guarantees 19 V output driving capability allowing users to connect several LEDs in series. In the output stage, twelve regulated current sources provide from 6 mA to 60 mA constant current to drive LEDs. The current is programmed by a single external resistor. In the ALED1262ZT, LED open error detection is available.

The brightness can be adjusted separately for each channel through a 7-bit grayscale control. A slow turn-on and turn-off time improves the system low noise generation performance. Moreover the gradual output delay reduces the inrush current. To further increase EMI performance, this device implements an internal clock dithering to have a spread spectrum noise reduction.

Thermal management is equipped with overtemperature data alert and the output thermal shutdown (170  $^{\circ}$ C). The I²C high clock frequency, up to 400 kHz, makes the device suitable for high data rate transmissions. The supply voltage range is between 5.5 V and 38 V avoiding any external pre-regulation or additional load dump protection on the power supply stage.

This device can operate in bus-driven mode (BDM) using  $I^2C$  interface or in standalone mode (SAM) using internal custom configuration by OTP.

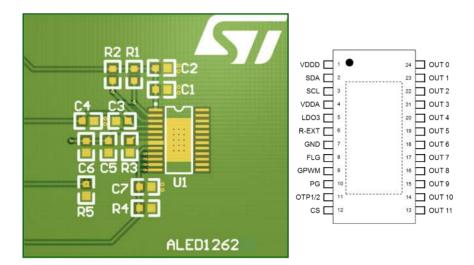

# 1 Pin description

VDDD OUT 0 24 SDA 2 OUT 1 23 SCL 3 22 OUT 2 VDDA OUT 3 21 LDO3 5 OUT 4 R-EXT 6 19 OUT 5 GND | 7 OUT 6 18 FLG | 8 OUT 7 17 GPWM [ 16 OUT8 PG 15 OUT 9 OTP1/2 **OUT 10** 11 cs **OUT 11** 12 13

Figure 1. HTSSOP24 pinout

AMG090320171202MT

Table 1. Pin description

| HTSSOP24                   | Symbol        | Name and function                                                                                                             |

|----------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1                          | VDDD          | Digital supply terminal                                                                                                       |

| 2                          | SDA           | I <sup>2</sup> C serial data input terminal                                                                                   |

| 3                          | SCL           | I²C clock input terminal                                                                                                      |

| 4                          | VDDA          | Analog supply terminal and internal LDO input                                                                                 |

| 5                          | LDO3          | 3.3 V internal LDO output                                                                                                     |

| 6                          | R-EXT         | Terminal for external resistor for constant current programming                                                               |

| 7                          | GND           | Ground terminal                                                                                                               |

| 8                          | FLG           | Fault flag: open-drain PMOS output for wired-OR connection                                                                    |

| 9                          | GPWM          | Global PWM control. To be connected to LDO3 if it is not used                                                                 |

| 10                         | PG            | Power Good pin. Connect to an external resistor divider to set a proper power supply voltage threshold for detection enabling |

| 11                         | OTP1/2        | Digital input for internal OTP register selection                                                                             |

| 12                         | CS            | Chip-select and power supply (15 V) for OTP burning                                                                           |

| 13 to 24                   | OUT0 to OUT11 | Output terminals (low-side current generators)                                                                                |

| Exposed pad <sup>(1)</sup> | -             | Additional device ground terminal to be connected to pin 7 (GND)                                                              |

The device exposed pad must be connected to GND, moreover it should be soldered directly to a PCB copper area to maximize thermal dissipation.

DS12631 - Rev 4 page 2/69

# 2 Absolute maximum ratings

Stressing the device above the ratings listed on Table 2. Absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute maximum ratings

| Symbol              | Parameter                                  | Value                                   | Unit     |  |

|---------------------|--------------------------------------------|-----------------------------------------|----------|--|

| V <sub>DDA</sub>    | Analog supply voltage 0 to 40              |                                         |          |  |

| V <sub>DDD</sub>    | Digital supply voltage                     | 0 to 7                                  |          |  |

| V <sub>PG</sub>     | Power Good pin                             |                                         |          |  |

| V <sub>GPWM</sub>   | Global PWM dimming                         |                                         |          |  |

| V <sub>OTP1/2</sub> | OTP register selection                     | -0.3 to 20                              | V        |  |

| V <sub>OUT</sub>    | Output channel voltage                     |                                         | V        |  |

| CS                  | Chip select and OTP burning                |                                         |          |  |

| V <sub>I/O</sub>    | Digital I/O pin: SDA, SCL                  | -0.5 to V <sub>DDD</sub>                |          |  |

| V <sub>LDO3</sub>   | LDO3 output voltage                        | 0 to 4.6                                |          |  |

| V <sub>FLG</sub>    | I/O flag: FLG                              | -0.3 to V <sub>DDD</sub> <sup>(1)</sup> |          |  |

| I <sub>O</sub>      | Output current                             | 70                                      | mA       |  |

|                     | Electrostatic discharge protection         | ±2.0                                    | kV       |  |

|                     | HBM (human body model)                     | 12.0                                    | IX V     |  |

| ESD                 | Electrostatic discharge protection         | ±500                                    |          |  |

| LOD                 | CDM (charged device model)                 | 1000                                    | V        |  |

|                     | Electrostatic discharge protection ±750    |                                         | <b>'</b> |  |

|                     | CDM (charged device model) for corner pins | 1100                                    |          |  |

<sup>1.</sup> If  $V_{DDD}$  is not plugged AMR must be decreased to 3.3 V.

DS12631 - Rev 4 page 3/69

# 3 Thermal characteristics

**Table 3. Thermal characteristics**

| Symbol               | Parameter                            |                     | Value               | Unit |

|----------------------|--------------------------------------|---------------------|---------------------|------|

| T <sub>OPR</sub>     | Operative junction temperature range | -40 to +150         | °C                  |      |

| T <sub>STG</sub>     | Storage ambient temperature range    |                     | -55 to +150         |      |

| R <sub>thj-amb</sub> | Thermal resistance junction-ambient  | 37.5 <sup>(2)</sup> |                     |      |

| R <sub>thj-b</sub>   | Thermal resistance junction-board    | 22.8 <sup>(2)</sup> | °C/W                |      |

| R <sub>thj-c</sub>   | Thermal resistance junction-case     |                     | 14.6 <sup>(2)</sup> |      |

<sup>1.</sup> The exposed pad must be attached to a metal land electrically connected to ground. To get the thermal benefits it should be soldered directly to a PCB copper area.

DS12631 - Rev 4 page 4/69

<sup>2.</sup> Jedec test conditions on 2S2P board (4 layers).

# 4 Electrical characteristics

Table 4. Electrical characteristics ( $V_{DDA}$  = 12 V,  $V_{DDD}$  = 5 V, Tj = -40 to 125 °C, unless otherwise specified)

| Symbol                | Parameter                                         | Conditions                                                    | Min.                 | Тур.  | Max.                 | Unit |

|-----------------------|---------------------------------------------------|---------------------------------------------------------------|----------------------|-------|----------------------|------|

| $V_{DDA}$             | Supply voltage                                    |                                                               | 5.5                  |       | 38                   |      |

| $V_{DDD}$             | Supply voltage                                    |                                                               | 4.5                  |       | 5.5                  |      |

| V <sub>OUT</sub>      | Output voltage                                    | OUT0 - OUT11                                                  |                      |       | 19                   |      |

| $V_{IH}$              | CDA CCI digital threeholds                        | V plugged                                                     | 0.7•V <sub>DDD</sub> |       | V <sub>DDD</sub>     |      |

| $V_{IL}$              | SDA, SCL digital thresholds                       | V <sub>DDD</sub> plugged                                      | -0.5                 |       | 0.3•V <sub>DDD</sub> |      |

| $V_{\text{IH2}}$      | FLG digital input threshold with V <sub>DDD</sub> |                                                               |                      | 1.70  | 1.90                 |      |

| V <sub>IL2</sub>      | not active                                        |                                                               | 1.30                 | 1.45  |                      |      |

| V <sub>I2_Hys</sub>   | FLG hysteresis                                    |                                                               |                      | 0.25  |                      | V    |

| V <sub>IH3</sub>      | ODWA there should                                 | V plugged                                                     |                      |       | 2.00                 |      |

| $V_{IL3}$             | GPWM threshold                                    | V <sub>DDA</sub> plugged                                      | 1.70                 |       |                      |      |

| $V_{IH4}$             | OTD4/O three should                               |                                                               |                      |       | 1.90                 |      |

| V <sub>IL4</sub>      | OTP1/2 threshold                                  |                                                               | 1.30                 |       |                      |      |

| V <sub>IH5</sub>      | DO there also let                                 |                                                               |                      | 1.9   | 2.00                 |      |

| $V_{\text{IL5}}$      | PG threshold                                      |                                                               | 1.70                 | 1.8   |                      |      |

| V <sub>I5_Hys</sub>   | PG hysteresis                                     |                                                               |                      | 0.1   |                      |      |

| R <sub>CS</sub>       | CS pull-down                                      |                                                               |                      | 160   |                      | kΩ   |

| I <sub>LGPWM</sub>    | GPWM pin input current                            | V <sub>GPWM</sub> = GND or 2 V                                | -1                   |       | +1                   |      |

| I <sub>I_OTP1/2</sub> | OTP1/2 pin input current                          | V <sub>OTP1/2</sub> = GND or 2 V                              | -1                   |       | +1                   | μA   |

| I <sub>LPG</sub>      | PG pin input current                              | V <sub>PG</sub> = GND or 2 V                                  | -1                   |       | +1                   |      |

| I <sub>OL_SDA</sub>   | SDA sink current                                  | V <sub>DDD</sub> = 4.5 V; V <sub>OL</sub> = 0.4 V             | 3                    |       |                      |      |

| I <sub>OL_SCL</sub>   | SCL sink current                                  | V <sub>DDD</sub> = 4.5 V; V <sub>OL</sub> = 0.4 V             | 3                    |       |                      | mA   |

| I <sub>Dleak</sub>    | SDA, SCL leakage current                          | V <sub>I</sub> = GND or V <sub>DDD</sub>                      | -10                  |       | +10                  |      |

| l <sub>Oleak</sub>    | Output channel leakage current                    | V <sub>OUT</sub> = 19 V, all outputs OFF                      |                      |       | 0.5                  | μA   |

|                       |                                                   | V <sub>DDD</sub> plugged VOH = V <sub>DDD</sub> -0.4V         |                      |       |                      |      |

| I <sub>OH_FLG</sub>   | FLG source current                                | V <sub>DDD</sub> not plugged<br>VOH = V <sub>LDO3</sub> -0.4V | 3                    |       |                      | mA   |

| $V_{\text{UVLO}}$     | V <sub>DDA</sub> UVLO threshold (falling)         |                                                               | 1.7                  | 1.85  |                      |      |

| V                     | Global_EN V <sub>DDA</sub> threshold (rising)     |                                                               |                      | 3.8   | 4.0                  |      |

| $V_{G\_EN}$           | Global_EN V <sub>DDA</sub> threshold (falling)    | GPWM = LDO3                                                   | 3.40                 | 3.6   |                      |      |

| H <sub>G_EN</sub>     | Global_EN hysteresis                              |                                                               |                      | 0.2   |                      | V    |

| V <sub>ref</sub>      | R <sub>EXT</sub> reference voltage                |                                                               |                      | 1.233 |                      |      |

| $V_{LDO}$             | LDO3 output voltage                               | External maximum load current: I <sub>load</sub> = 200 µA     | 3.231                | 3.328 | 3.428                |      |

| I <sub>LDO</sub>      | LDO short-circuit output current                  | V <sub>DDA</sub> = 5.5 V                                      |                      | 110   |                      | mA   |

DS12631 - Rev 4 page 5/69

| Symbol                | Parameter                                           | Conditions                                                            | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------------------------------------------|-----------------------------------------------------------------------|------|------|------|------|

| _                     |                                                     | $V_{OUT} = 0.65 \text{ V}; R_{EXT} = 49.9 \text{ k}\Omega;$           |      |      | .45  |      |

| ∆IOL1                 |                                                     | Io ≈ 6 mA; $T_j \le 90$ °C; (outage)                                  |      |      | ±15  |      |

|                       | Output current precision channel to                 | $V_{OUT}$ = 1.05 V; $R_{EXT}$ = 24.9 k $\Omega$ ;                     |      |      |      |      |

| $\Delta_{IOL2}$       | channel (all outputs ON) (1)                        | I <sub>O</sub> ≈ 12 mA; (outage)                                      |      |      | ±10  | %    |

| $\Delta_{IOL3}$       |                                                     | $V_{OUT}$ = 1.35 V; $R_{EXT}$ = 4.99 kΩ; $I_O \approx$ 60 mA (outage) |      |      | ±3   | 70   |

|                       | Output current precision device to                  | V <sub>OUT</sub> = 1.35 V; R <sub>EXT</sub> = 4.99 KΩ;                |      |      |      |      |

| $\Delta_{IOL2a}$      | device (all outputs ON) (1)                         | I <sub>O</sub> ≈ 60 mA; (outage)                                      |      |      | ±6   |      |

| 0//4\/                | Output current vs output voltage                    | V <sub>OUT</sub> from 1.35 V to 3.35 V;                               |      | 0.4  |      | %/V  |

| %/dV <sub>OUT</sub>   | regulation                                          | R <sub>EXT</sub> = 4.99 kΩ; $I_O \approx 60$ mA                       |      | 0.1  |      |      |

| R <sub>EXT</sub>      | External current set-up resistance                  |                                                                       | 4.99 |      | 49.9 | kΩ   |

|                       | V <sub>DDD</sub> supply current no dimming          | $R_{EXT} = 4.99 \text{ k}\Omega;$                                     |      |      | 1.0  |      |

| $I_{DDD}$             |                                                     | No I <sup>2</sup> C data transfer                                     |      | 0.7  |      |      |

|                       |                                                     | OUT0 to 11 = ON (outage)                                              |      |      |      |      |

| I <sub>DDA(OFF)</sub> | V <sub>DDA</sub> supply current (OFF)<br>GPWM = GND | $R_{EXT}$ = 4.99 k $\Omega$ ;                                         |      | 0.3  | 0.6  |      |

| IDDA(OFF)             |                                                     | OUT0 to 11 = OFF                                                      |      | 0.3  |      |      |

| I <sub>DDA(ON1)</sub> | V <sub>DDA</sub> supply current (ON) no dimming     | $R_{EXT}$ = 24.9 k $\Omega$ ; $I_{O}$ ≈ 12 mA;                        |      | 2    | 2.5  | mA   |

| 'DDA(ON1)             | VDDA Sapply Salletti (STV) tie allitting            | OUT0 to 11 = ON (outage)                                              |      |      | 2.0  |      |

| I <sub>DDA(ON2)</sub> | V <sub>DDA</sub> supply current (ON) no dimming     | R <sub>EXT</sub> = 4.99 kΩ; $I_O \approx 60$ mA                       |      | 4    | 5.5  |      |

| IDDA(ON2)             | VDDA Supply current (OIV) no uniming                | OUT0 to 11 = ON (outage)                                              |      |      | 5.5  |      |

| I <sub>DDA(REC)</sub> | VDDA supply current                                 | $R_{EXT}$ = 4.99 k $\Omega$ ;                                         |      |      | 1.2  |      |

| iDDA(REC)             | VDDA supply current                                 | SAM recovery condition                                                |      |      | 1.2  |      |

| $T_{flg}$             | Thermal flag                                        |                                                                       |      | 140  |      |      |

| T <sub>flg-hy</sub>   | Thermal flag hysteresis                             |                                                                       |      | 10   |      | °C   |

| T <sub>sd</sub>       | Thermal shutdown                                    |                                                                       |      | 170  |      |      |

| T <sub>sd-hy</sub>    | Thermal shutdown hysteresis                         |                                                                       |      | 15   |      |      |

<sup>1.</sup> Tested with just one output loaded.

2.  $((I_{On} - I_{Oavg1-12})/I_{Oavg1-12}) \times 100$

3.

$$\Delta(\%/V) = \frac{(I_{On}@V_{OUTn} = 3.35V) - (I_{On}@V_{OUTn} = 1.35V)}{(I_{On}@V_{OUTn} = 1.35V)} \cdot \frac{100}{3.35 - 1.35}$$

DS12631 - Rev 4 page 6/69

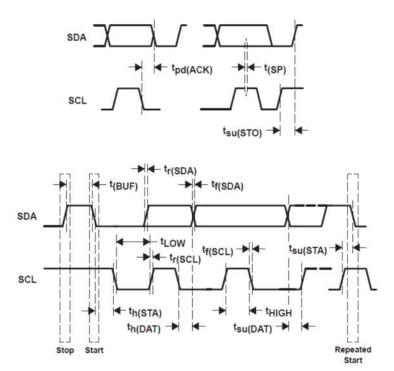

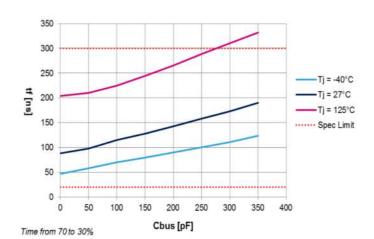

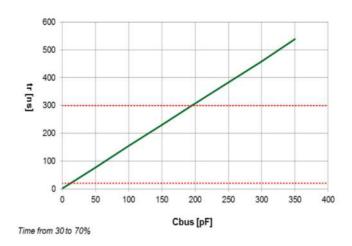

# 4.1 Switching characteristics

Table 5. Switching characteristics ( $V_{DDA} = 12 \text{ V}, V_{DDD} = 5 \text{ V}, Tj = 25 ^{\circ}\text{C}$ , unless otherwise specified)

| Symbol                 | Parameter                                                                                           | Conditions                                                                                    | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| f <sub>SCL</sub>       | I <sup>2</sup> C clock frequency                                                                    |                                                                                               | 100  |      | 400  | kHz  |

| f <sub>PWM</sub>       | GPWM frequency                                                                                      |                                                                                               |      |      | 500  | Hz   |

| t <sub>PWM</sub>       | Output minimum ton by GPWM                                                                          | GPWM <sub>HIGH</sub> = 20 μs                                                                  | 5    |      |      | μs   |

| f <sub>PWM_local</sub> | Local dimming frequency (1)                                                                         |                                                                                               | 200  | 220  | 240  | Hz   |

| t <sub>PWM_local</sub> | Local dimming minimum ton                                                                           |                                                                                               |      | 5    |      | μs   |

| t <sub>(SP)</sub>      | Pulse width of spikes that must be suppressed by the input filter                                   |                                                                                               |      |      | 50   | ns   |

| t <sub>(BUF)</sub>     | Bus free time between a STOP and START condition                                                    |                                                                                               | 1.3  |      |      |      |

| t <sub>pd(ACK)</sub>   | SCL low to data out valid (acknowledge)                                                             |                                                                                               |      |      | 0.9  | μs   |

| $t_{LOW}$              | SCL low time                                                                                        |                                                                                               | 1.3  | 1.3  |      |      |

| t <sub>HIGH</sub>      | SCL high time                                                                                       |                                                                                               | 0.6  |      |      |      |

| t <sub>su(DAT)</sub>   | SDA / SCL set-up time                                                                               |                                                                                               | 100  |      |      |      |

| t <sub>su(STA)</sub>   | Set-up time for START condition                                                                     |                                                                                               | 600  |      |      |      |

| t <sub>su(STO)</sub>   | Set-up time for STOP condition                                                                      |                                                                                               | 600  |      |      |      |

| t <sub>h(DAT)</sub>    | Data input hold time                                                                                |                                                                                               |      |      | 900  | ns   |

| t <sub>h(STA)</sub>    | START condition hold time                                                                           |                                                                                               | 600  |      |      |      |

| t <sub>r</sub>         | Rise time both of SDA and SCL signals                                                               |                                                                                               | 20   |      | 300  |      |

| t <sub>f</sub>         | Fall time both of SDA and SCL signals                                                               |                                                                                               | 20   |      | 300  |      |

| t <sub>on</sub>        | Output current turn-on time                                                                         | $R_{EXT} = 4.99 \text{ k}\Omega \text{ I}_{O} = 60 \text{ mA}$                                |      | 1.7  |      |      |

| t <sub>off</sub>       | Output current turn-off time                                                                        | $V_{DROP} = 1.35 \text{ V}$ RL = 50 $\Omega$ CL= 10 pF                                        |      | 1.4  |      | μs   |

| t <sub>n-reg</sub>     | Delay time from global_EN to output current regulation ( $V_{\text{LED}}$ is enough for regulation) | $R_{EXT} = 4.99 \text{ k}\Omega \text{ I}_{O} = 60 \text{ mA}$<br>$V_{DROP} = 1.35 \text{ V}$ |      |      | 60   | μs   |

| t <sub>n-err</sub>     | Delay time from PG to output error detection                                                        | RL = 50 Ω CL = 10 pF                                                                          |      |      | 70   |      |

<sup>1.</sup> Using prescaler bit (Faulty\_ch\_1 register bit[7]) local dimming frequency value can be reduced by half (typ. = 110 Hz)

DS12631 - Rev 4 page 7/69

Figure 2. I<sup>2</sup>C timing definition

DS12631 - Rev 4 page 8/69

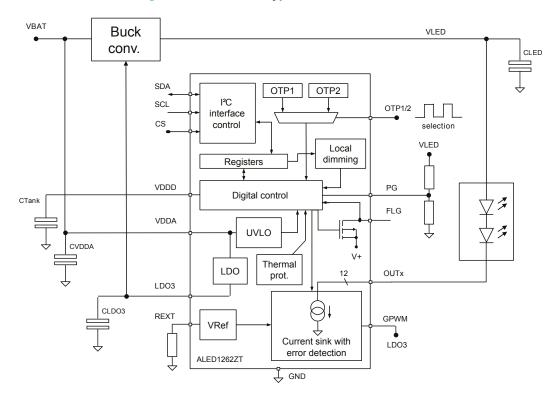

Figure 3. Simplified internal block diagram

DS12631 - Rev 4 page 9/69

### **Device pin functions**

A detailed description about each pin function as follows:

SDA – I<sup>2</sup>C is the bidirectional data line, it must be pulled up with an external resistor connected to MCU power

SCL - clock line, coming from MCU I2C bus, must be pulled up with an external resistor connected to MCU power supply.

CS - chip-select pin used exclusively to address each device during one time register programming (OTP). This procedure is carried out at the end of customer production line to set the device default configuration. CS pin has an internal pull-down resistor of about 160 kΩ. This pin is also used to supply 15 V during factory programming to set internal OTP registers.

The CS pin cannot be connected to GND, neither directly nor through passive components. The only allowed Note: polarization is floating or positive voltage (up to 15 V).

> V<sub>DDD</sub> – digital power supply coming from MCU section together with I<sup>2</sup>C bus. When V<sub>DDD</sub> is below a threshold of about 2.9 V (typ. falling) or 3.0 V (typ. rising) the device goes automatically to SAM. Besides, providing the digital power supply V<sub>DDD</sub> only (V<sub>DDA</sub> not connected), the device I<sup>2</sup>C bus is active and internal registers can be programmed, the only restriction is related to  $V_{DDA}$  impedance to GND that must be higher than 4.7 k $\Omega$ . In case of a lower impedance, the device digital interface starts on the first V<sub>DDA</sub> voltage rising edge. The allowed slew rate for this pin is below 0.17 V/ $\mu$ s (0 to 5 V; 30  $\mu$ s  $\leq$  t<sub>rise</sub>).

Fast V<sub>DDD</sub> edges can cause internal regulator overvoltage spikes that may provoke electrical stresses in the Note: device.

> V<sub>DDA</sub> – analog power supply coming from car body system. This is the main supply voltage for the driver and it can be dimmed to change LED brightness (100 or 200 Hz at 10% as minimum duty cycle, V<sub>DDA</sub> = 0 to 12 V). Allowed slew rates for this pin are the following: from 0.4 to 1.2 V/ $\mu$ s (0 to 12 V; 10  $\mu$ s  $\leq$   $t_{rise/fall} \leq$  30  $\mu$ s) in normal operation, from 6.8 to 8.4 V/ms for load dump conditions.

If the  $I^2C$  is programmed to only provide the digital power supply  $V_{DDD}$  ( $V_{DDA}$  not connected), a subsequent  $V_{DDA}$  plug or unplug with edges faster than those allowed ( $t_{rise/fall}$  < 10  $\mu$ s) may induce the internal register reset.

LDO3 – internal regulator output pin to be connected to an external capacitor (minimum value 1 µF). The output voltage is about 3.3 V ±3% and it is used as an external reference voltage and the device internal supply. The capacitor connected on this pin is also used as "tank capacitor" to maintain internal volatile register data during V<sub>DDA</sub> pulsed dimming function (if required).

REXT - this resistor is used to program the regulated output current. The relationship between REXT value and the output current is given by the following equation:

$$I_{Ox} = \frac{V_{BG}}{R_{EXT}} \cdot K$$

The current gain factor "K" is about 240. The  $V_{BG}$  voltage is normally at 1.233 V used to get the reference current trough R-EXT pin; this current is mirrored by a precise circuit to generate the reference for the driver stage. On R-EXT pin, any filter capacitor can be connected.

GND - ground pin, it must be connected to a package exposed pad. Exposed pad should be soldered directly to the PCB to see the thermal benefits (see the device thermal management section).

GPWM - a variable duty cycle square wave on this pin allows all channels brightness to be fixed simultaneously (PWM global dimming). If this pin is not used, it must be connected to LDO3. GPWM control requires a square wave with a HIGH level longer than 20 µs caused by a 15 µs delay needed to power on all internal blocks before the channel activation. With 20 µs HIGH level, the real output activation is around 5 µs. The maximum allowed slew-rate on this pin is 1.9 V/µs.

OUTx - the ALED1262ZT has 12 current regulated low-side outputs. The output stage is a sinker, which is able to stand till 19 V, this is to use more than one LED series connected. The internal current generator turn-on and turnoff time has been slowed down to decrease as much as possible EMI noise.

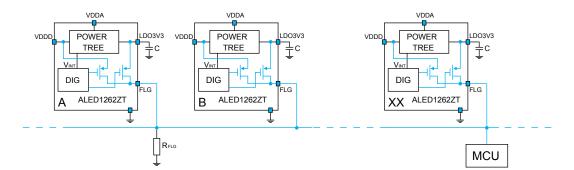

FLG – this is the fault flag I/O pin used in wired-OR among those devices sharing the same application. In wired-OR connection, all FLG pins are connected together to a single pull-down resistor, this signal can also be read by an MCU to detect any fault condition. If the device receives an external error status, it reacts according to the internal configuration (see Section 13.1 BDM\_conf\_1 / Enable\_CH\_1 register, Section 13.2 BDM\_conf\_2 /

Note:

DS12631 - Rev 4

Enable\_CH\_2 register and Section 13.11 OTP/BA\_n\_SAM\_setting register). This pin can be configured by setting internal registers and may combine error detection results and the overtemperature protection. The devices sharing the same FLG line must have the same supply domain. Different supply domains on the same FLG bus need to be managed externally according to the used voltage level (i.e., level shifter).

As soon as one device forces current on the external pull-down resistor ( $R_{FLG}$ ) through the integrated high-sides, the digital information is generated. The internal high-side pull-up is connected to two different power lines to get the correct voltage level according to the external configuration:

- V<sub>DDD</sub> is plugged: an internal high-side transistor is connected to the V<sub>DDD</sub> (5 V). In this case the high level

on FLG pin/bus is forced to V<sub>DDD</sub> and it is compliant to fault information coming directly from the MCU as

well.

- V<sub>DDD</sub> is not plugged: a high-side transistor is connected to the internal regulated voltage 3V3 (LDO3). In

this case there is not any external interrupt coming from MCU to be managed (5 V V<sub>DDD</sub> is not available).

The voltage level is among chips connected to the same power domain.

The power line selection for the FLG analog MUX is a matter of  $V_{DDD}$  comparator used to detect the  $V_{DDD}$  plugin.

Figure 4. FLG pin connection

In case of dimming functions and FLG pin at high logic level due to one output in open condition (and/or thermal shutdown and/or R<sub>EXT</sub> short), FLG behavior is different according to running dimming mode:

- Faulty channel, dimming by GPWM pin: FLG blinks according to GPWM external square wave and error detection conditions.

- Faulty channel, dimming by PWM register (BDM): FLG is constantly high according to the error detection conditions.

PG – this pin is the LED driver Power Good, it must be connected by a proper resistor divider to the main voltage coming from car body system (V<sub>DDA</sub>) or to LED power supply. Starting from the internal threshold overcoming (above 1.95 V), the ALED1262ZT has a valid detection available in less than 70 μs. The maximum allowed slew-rate on this pin is 1.9 V/μs.

OTP1/2 – in standalone mode, it is possible to select two possible output configurations. Each configuration is stored in non-volatile cells (shadowed by SAM\_conf\_\* registers). This pin can be also connected to a switched voltage coming from car body system ( $V_{DDA}3$ ) by a resistor divider. When OTP1/2 is at logic level LOW, output configurations are related to SAM\_conf\_1 register. Conversely, when OTP1/2 is at logic level HIGH, output configurations are related to SAM\_conf\_2 register (see register description for more details). The maximum allowed slew-rate on this pin is 1.9 V/ $\mu$ s.

DS12631 - Rev 4 page 11/69

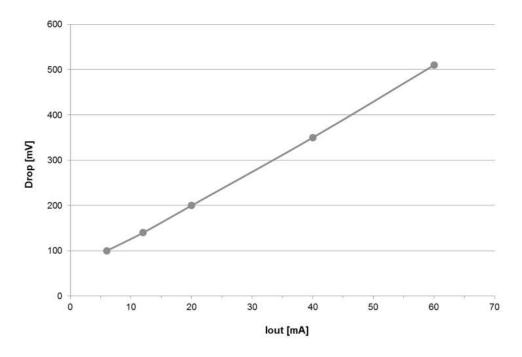

### 6 Driver dropout voltage

In order to correctly regulate the channel current, a minimum output voltage (V<sub>DROP</sub>) across each current generator must be guaranteed.

Figure 5. Channel dropout voltage vs output current (Tj = 25 °C), Table 6. Minimum dropout voltage for certain current values (Tj = 25 °C; worst case simulated at target minus 3%) and Table 7. Minimum dropout voltage at 60 mA (worst case simulated at target minus 3%) show the minimum slightly less than the target value (output MOS transistor in triode region); these measurements have been recorded with just one output ON. When more than one output is active, the drop voltage increases. At 60 mA per channel, all channels ON, output voltage must be increased by about 110 mV (worst case at Tj = 125 °C). If the V<sub>DROP</sub> is lower than the minimum recommended, the regulation of a current is lower than the expected one. However an excess of V<sub>DROP</sub> increases the power dissipation.

Figure 5. Channel dropout voltage vs output current (Tj = 25 °C)

Table 6. Minimum dropout voltage for certain current values (Tj = 25 °C; worst case simulated at target minus 3%)

| Target output current [mA] | V <sub>DROP</sub> [mV] |

|----------------------------|------------------------|

| 6                          | 100                    |

| 12                         | 140                    |

| 20                         | 200                    |

| 40                         | 350                    |

| 60                         | 510                    |

DS12631 - Rev 4 page 12/69

Table 7. Minimum dropout voltage at 60 mA (worst case simulated at target minus 3%)

| тј [°С] | V <sub>DROP</sub> [mV] |

|---------|------------------------|

| 125     | 630                    |

| 25      | 510                    |

| -40     | 440                    |

Table 8. Typical output current vs  $R_{\text{EXT}}$  value

| lout target value (mA) | R <sub>EXT</sub> calculated value (Ω) | R <sub>EXT</sub> - E96 1% nearest commercial value (Ω) |

|------------------------|---------------------------------------|--------------------------------------------------------|

| 6                      | 49360                                 | 49900                                                  |

| 12                     | 24680                                 | 24900                                                  |

| 15                     | 19744                                 | 19600                                                  |

| 20                     | 14808                                 | 14700                                                  |

| 25                     | 11846                                 | 11800                                                  |

| 30                     | 9872                                  | 9760                                                   |

| 35                     | 8462                                  | 8450                                                   |

| 40                     | 7404                                  | 7320                                                   |

| 45                     | 6581                                  | 6650                                                   |

| 50                     | 5923                                  | 5900                                                   |

| 55                     | 5385                                  | 5360                                                   |

| 60                     | 4936                                  | 4990                                                   |

DS12631 - Rev 4 page 13/69

### 7 Device functional description

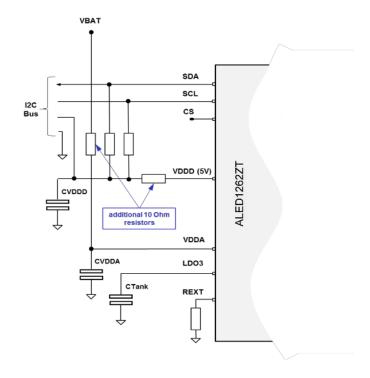

The ALED1262ZT has been designed to be very flexible so to meet application needs. In a very basic connection, the ALED1262ZT is supplied only by  $V_{DDA}$  pin (with a continuous voltage), and a resistor connected between R-EXT pin and GND (placed as near as possible to the device) programs the current sunk from outputs, GPWM is not used (to LDO3) and output channels connected to external LED cathodes.

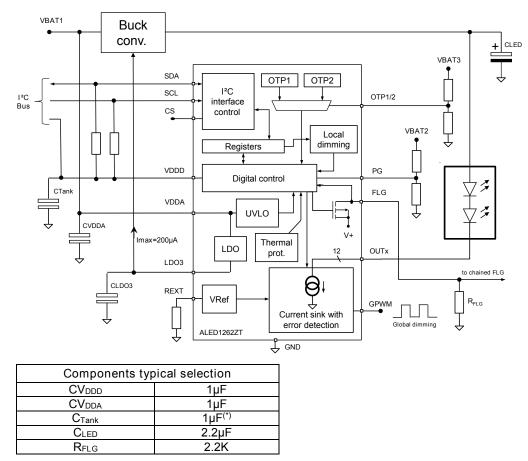

Figure 6. ALED1262ZT typical connection scheme

Furthermore, the Power Good pin (PG) can be connected to an external resistor divider. This divider supplied by  $V_{LED}$  provides the internal trigger signal when  $V_{LED}$  has a value enough for the device current regulation and consistent error detection. Fault flag pin (FLG) can be floating or connected to a pull-down resistor or in a wired-OR configuration to all FLG pins of additional devices sharing the same application. LDO3 is the internal regulator output supplied by  $V_{LED}$ , the output voltage is 3.3 V and it is used as the device internal block supply and, if necessary, as external reference voltage.

By changing the external circuit, more and more functions of the device can be used. The ALED1262ZT in a full feature configuration is connected using the I<sup>2</sup>C interface and OTP1/2 output configurations as fail-safe recovery in case of bus accidental disconnection (see the following diagram).

DS12631 - Rev 4 page 14/69

Figure 7. The ALED1262ZT full connection

(\*) Any de-rating included

On all applications where LEDs are dimmed using the main power line (VBAT1 on schematic) it's mandatory to rectify the V<sub>DDA</sub> voltage to supply the device. In this condition GPWM pin must be connected, by a resistor divider, to the power line (on VBAT1 before rectifier diode) to allow channels to switch off during main power supply dimming falling edge. For right operations, resistor dividers must be calculated to have GPWM threshold lower than Power Good (PG) threshold. The placement of external capacitors and minimum capacitance values are always mandatory, in this particular case they are essential for the device steady setup (see "component typical selection" table).

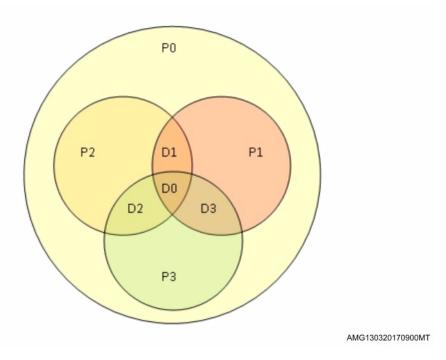

As mentioned, the ALED1262ZT has been designed to work in two possible application architectures: standalone mode (SAM) and bus-driven mode (BDM). Some details about these two operation modes are the following:

SAM - In standalone mode configuration, the device is not connected to an MCU or a controller board so I<sup>2</sup>C bus leaves floating (SDA, SCL pins). In this condition,  $V_{DDD}$  is not supplied and an internal comparator senses this pin to set properly the device and to release the I<sup>2</sup>C bus.

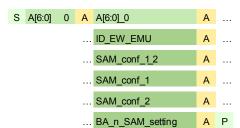

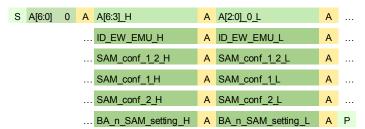

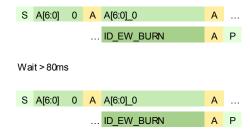

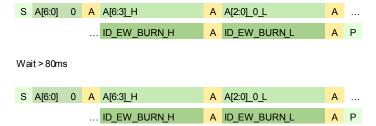

In this mode, the device refers to four internal registers mimic the content of non-volatile memory: SAM\_conf\_1, SAM\_conf\_2, SAM\_conf\_1\_2 and BA\_n\_SAM\_setting. In the rest of the document we can refer to these registers as non-volatile registers, just for sake of simplicity. SAM\_conf\_x represent the output ON/OFF status in two possible configurations that can be selected on the application by OTP1/2 pin. Error detection system is adequate to the activated outputs.

According to BA\_n\_SAM\_setting register, the device runs continuously an error detection indicating, if required, the error status to all other devices connected on the same board by fault flag chain. All these four registers can be preset during - one time programming phase - at the end of customer production line using the chip-select pin (CS – see OTP programming section).

**BDM** - In bus-driven mode configuration, the device is connected to an MCU or to a controller board, so  $I^2C$  bus is active.  $V_{DDD}$  is also supplied in this condition and an internal comparator senses this voltage to switch

DS12631 - Rev 4 page 15/69

automatically to SAM in case of bus unintentional disconnection. In this mode, we refer to one non-volatile register and six volatile registers:

- Non-volatile BA\_n\_SAM\_setting register, it is programmed during one time programming phase, using chip-select pin (CS – see OTP programming section).

- Volatile BDM\_conf 1 and 2, BDM\_status, Faulty\_ch 1 and 2, PWM\_gain registers.

BA\_n\_SAM\_setting register sets the device I²C address on 31 possible selections (all zeros is valid only for fresh devices) and the communication protection mode; BDM\_conf 1 and 2 set the output ON/OFF status; BDM\_conf 1 also contains information about the error detection device behavior, diagnostic function and local dimming activation; BDM\_status contains information about the diagnostic results, thermal protection and general driver status; Faulty\_ch 1 and 2 contain indications about branches in which a fault is detected; PWM\_gain represents the dimming value for each of 12 outputs (for more details see register description paragraph). Through bit BDM\_Flag of the BDM\_conf\_1 register, we can force the device from SAM to BDM according to the following table:

Table 9. Operative status

| V <sub>DDA</sub> | V <sub>DDD</sub> | BDM_FLAG | STATUS | Notes                                                                                                                                                                                                           |

|------------------|------------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF              | OFF              | X        | OFF    | The device is not supplied                                                                                                                                                                                      |

| OFF              | ON               | 0        | SAM    | Analog part is OFF but the current regulation can be re-established quickly as soon as $V_{DDA}$ is plugged and output configuration is related to SAM OTP registers, I <sup>2</sup> C registers are accessible |

| OFF              | ON               | 1        | BDM    | Analog part is OFF but the current regulation can be re-established quickly as soon as $V_{DDA}$ is plugged and output configuration is related to BDM registers, I²C registers are accessible                  |

| ON               | OFF              | 0        | SAM    | Analog part is active and the output configuration is related to SAM_conf_* registers (OTP), I²C registers are supplied, I²C module is OFF                                                                      |

| ON               | OFF              | 1        | SAM    | BDM_FLAG is reset and the device comes back on the previous configuration (BDM_FLAG=0)                                                                                                                          |

| ON               | ON               | 0        | SAM    | Analog part is active and output configuration is related to SAM_conf_* registers (OTP), I²C registers are supplied, I²C module is ON                                                                           |

| ON               | ON               | 1        | BDM    | Analog part is active and output configuration is related to BDM_conf_* registers (volatile), I²C registers are supplied, I²C module is ON                                                                      |

DS12631 - Rev 4 page 16/69

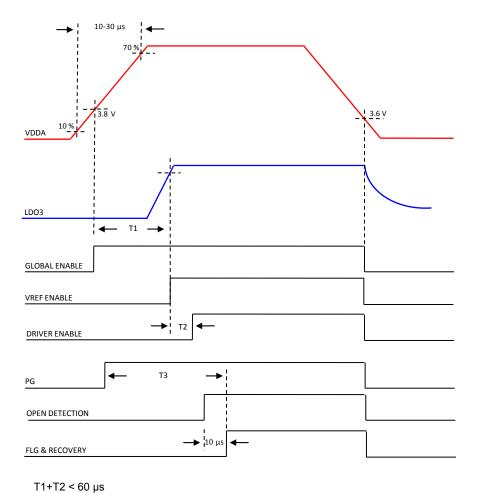

Figure 8. Power supply internal signal behavior

AMG090320171208MT

DS12631 - Rev 4 page 17/69

T3 < 70 µs

#### 8 Error detection

If Power Good threshold is asserted (PG pin voltage above 1.95 V), the ALED1262ZT runs continuously the output open detection. If the current flowing through the active channels is less than the half of the programmed one, the device reports an error that is managed according to BDM\_conf register (see register description paragraph). Please note that all error flags: Rext\_fault, Ext\_fault, Led\_fault, have a time delay mask (debounce), it means that a fault with duration lower than debounce time does not generate any type of interrupt. Time delay mask is about 10 µs on Rext\_fault and LED\_fault and 20 µs on Ext\_fault signal. At the same time, if LED power-on time is less than 15 µs (delay mask + detection delay), no output detection can be available.

For the same reason, no output detection is available in case of dimmed channels with LED  $t_{on}$ -time less than 15 µs (below step 20 on non-linear dimming table). If recovery condition has been set on BDM\_conf register and LED output channels are dimmed, in case of open condition detected, faulty channel duty cycle is brought to 100% till faulty retrieval. During recovery, the output current is typically regulated at 30 mA (value just as reference because channel is open condition). As soon as open channel is reconnected, the device sinks the recovery current for 10  $\mu$ s, subsequently all active channels are switched OFF to have, 15  $\mu$ s later, a new channel power-ON in normal regulation.

Furthermore, R-EXT pin is indirectly continuously monitored and any short-to-ground condition can be detected stopping output activities. In this case the parameter is indirectly the channel output current, above 65 to 95 mA (it depends on number of active channels and junction temperature) an internal comparator warns the  $R_{EXT}$  failure. In case of  $R_{EXT}$  short the outputs are in power-off. After 620  $\mu$ s (typ.) channels are reactivated for 10  $\mu$ s (typ.) to check again faulty condition. In other words, a physical short condition on  $R_{EXT}$  generates periodic pulsing on FLG pin at 630  $\mu$ s period.

All error conditions are reported on BDM\_status and Faulty\_ch\_1/2 registers (see register description paragraph) and on fault flag pin. A fault condition summarizing table is shown below:

| Type of fault                 | FLG       |            | Detection                                      |                              |  |

|-------------------------------|-----------|------------|------------------------------------------------|------------------------------|--|

| Type of fault                 | Driven    | Undriven   | Outage                                         | Recovery <sup>(1)</sup>      |  |

|                               |           |            |                                                | All good channels OFF        |  |

| Open LED                      | Active    | Not active | No action                                      | The device in low power mode |  |

|                               |           |            |                                                | Open channel in recovery     |  |

| Fault flag input line         |           | -          | No action                                      | All channels disabled        |  |

| R <sub>EXT</sub> short-to-GND | A         | ctive      | Turn off all LED branches                      |                              |  |

| Thermal warning               | No action |            | Communicated by bus message only               |                              |  |

| Thermal shutdown              | Active    |            | Communicated by bus message + all channels OFF |                              |  |

| Message error on bus          | No        | action     | Communicated by bus message if Hamming ON only |                              |  |

Table 10. Type of fault and device behavior

DS12631 - Rev 4 page 18/69

<sup>1.</sup> If PG is not asserted, FLG and/or load diagnosis are ignored.

# 9 Gradual output delay

An additional feature implemented on the ALED1262ZT is the gradual output delay. It consists of turning on gradually the current generators avoiding all channels to be turned on at the same time. In other words, enabling the device channels, the outputs can be turned ON with a staggered delay. The delay among each output is summarized on the following table, it is expressed in number of clock periods (typical internal clock frequency average value is  $3.3 \text{ MHz} \equiv 303 \text{ ns period}$ ):

Table 11. Gradual output delay

| Channels  | Added delay (number of CLK period) |

|-----------|------------------------------------|

| ch0/ch1   | 1                                  |

| ch1/ch2   | 1                                  |

| ch2/ch3   | 1                                  |

| ch3/ch4   | 1                                  |

| ch4/ch5   | 2                                  |

| ch5/ch6   | 7                                  |

| ch6/ch7   | 1                                  |

| ch7/ch8   | 1                                  |

| ch8/ch9   | 1                                  |

| ch9/ch10  | 1                                  |

| ch10/ch11 | 1                                  |

Between first and last channel the cumulative delays are 18 internal clock periods. This feature also prevents large inrush current and reduces the bypass capacitor value on LED voltage rail. This function is activated in local dimming condition (BDM) only.

DS12631 - Rev 4 page 19/69

# 10 Thermal warning and protection

The device has a thermal control logic providing a digital flag status (warning) when the internal temperature exceeds 140 °C. If thermal alert is asserted, error data is uploaded into BDM\_status register and this error notification is ready to stream through I²C bus. If temperature increases over 170 °C a thermal shutdown protects the device (all 12 channels OFF) and external fault flag (FLG) drives high.

DS12631 - Rev 4 page 20/69

AMG090320171210MT

### 11 Device local dimming function

The brightness of each channel can be adjusted through a 7-bit PWM grayscale brightness control according to local dimming register PWM gain x.

PWM\_EN

PWM\_GAINX\_bit7

AMG090320171209MT

Figure 9. Device local dimming function logic

Brightness data are loaded through I<sup>2</sup>C bus, PWM signal for each channel is generated by comparing the content of the brightness register to a 7-bit counter. The counter's clock source is provided by 3.3 MHz internal oscillator. Brightness register default configuration is all "0" (0x00) this means minimum LED brightness.

Note:

PWM\_gain\_x registers are made visible internally to the PWM generator, after an I<sup>2</sup>C transaction, when the internal 7-bit counter reaches the value 7Fh. Internal 7-bit counter stops when exiting PWM local dimming configuration (PWM\_En and/or BDM\_Flag set to '0'). When re-entering in PWM local dimming configuration 7-bit counter restarts from previous stopped value (unless HW reset), so first period of PWM waveform could be shorter.

The schematic below summarizes this functionality.

VLED 200Hz PWM Compares the value signal that generated by the drives the counter and the value current stored in the brightness generator reg is ter Channel x Brightness register #2 internal counter Counts from 0 to 127 (7bit) internal Internal os cillator feeds the c o unte r oscillator

Figure 10. Channel dimming feature

DS12631 - Rev 4 page 21/69

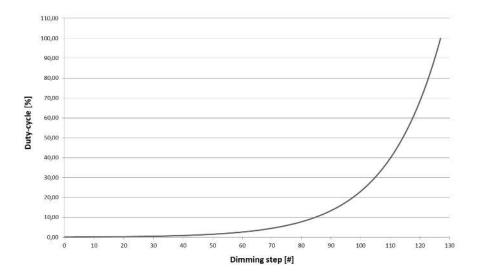

The ALED1262ZT implements 128 non-linear dimming steps to adequate LED brightness change to human eye light perception, giving in this way the impression of brightness linear variation. The exponential law used to calculate the dimming steps is the following:

$$ton_i = PWM\_period \cdot \alpha^{(N-i)}$$

Where  $ton_i$  is the LED ON-time during step number "i", PWM\_period = 5 ms or 10 ms (max. values), this means that minimum dimming frequency can be 200 Hz or 100 Hz according to Faulty\_ch\_1 register bit[7] (see register description), N = 127 (7-bit resolution),  $0 \le i \le 127$ ,  $\alpha \approx 0.9471$ .

DS12631 - Rev 4 page 22/69

# 12 Local dimming non-linear step table

The following table is related to the ALED1262ZT 7-bit local dimming non-linear steps. LED brightness can be changed in 128 paces with duty cycle between 0.1% and 100% ( $t_{ON}$  and duty cycle real values can be slightly different respect to tabulated numbers. Values are referred to minimum high range frequency:  $f_{PWM}$  = 200 Hz).

Table 12. Local dimming step

| Step number | t <sub>ON</sub> (µs) | Duty cycle (%) | Step number | t <sub>ON</sub> (µs) | Duty cycle (%) | Step number | t <sub>ON</sub> (µs) | Duty cycle (%) |

|-------------|----------------------|----------------|-------------|----------------------|----------------|-------------|----------------------|----------------|

| 0           | 5.00                 | 0.10           | 43          | 51.95                | 1.04           | 86          | 538.79               | 10.78          |

| 1           | 5.33                 | 0.11           | 44          | 54.95                | 1.10           | 87          | 568.76               | 11.38          |

| 2           | 5.67                 | 0.11           | 45          | 57.94                | 1.16           | 88          | 600.40               | 12.01          |

| 3           | 6.00                 | 0.12           | 46          | 61.27                | 1.23           | 89          | 634.03               | 12.68          |

| 4           | 6.33                 | 0.13           | 47          | 64.60                | 1.29           | 90          | 669.33               | 13.39          |

| 5           | 6.67                 | 0.13           | 48          | 68.27                | 1.37           | 91          | 706.63               | 14.13          |

| 6           | 7.00                 | 0.14           | 49          | 71.93                | 1.44           | 92          | 745.92               | 14.92          |

| 7           | 7.33                 | 0.15           | 50          | 75.92                | 1.52           | 93          | 787.55               | 15.75          |

| 8           | 7.67                 | 0.15           | 51          | 80.25                | 1.61           | 94          | 831.83               | 16.64          |

| 9           | 8.33                 | 0.17           | 52          | 84.92                | 1.70           | 95          | 878.45               | 17.57          |

| 10          | 8.66                 | 0.17           | 53          | 89.58                | 1.79           | 96          | 927.41               | 18.55          |

| 11          | 8.99                 | 0.18           | 54          | 94.57                | 1.89           | 97          | 979.02               | 19.58          |

| 12          | 9.66                 | 0.19           | 55          | 99.90                | 2.00           | 98          | 1033.63              | 20.67          |

| 13          | 10.32                | 0.21           | 56          | 105.23               | 2.10           | 99          | 1091.57              | 21.83          |

| 14          | 10.66                | 0.21           | 57          | 111.22               | 2.22           | 100         | 1152.51              | 23.05          |

| 15          | 11.32                | 0.23           | 58          | 117.55               | 2.35           | 101         | 1217.12              | 24.34          |

| 16          | 11.99                | 0.24           | 59          | 123.88               | 2.48           | 102         | 1285.05              | 25.70          |

| 17          | 12.65                | 0.25           | 60          | 130.87               | 2.62           | 103         | 1356.64              | 27.13          |

| 18          | 13.32                | 0.27           | 61          | 138.20               | 2.76           | 104         | 1432.23              | 28.64          |

| 19          | 13.99                | 0.28           | 62          | 145.85               | 2.92           | 105         | 1512.49              | 30.25          |

| 20          | 14.99                | 0.30           | 63          | 154.18               | 3.08           | 106         | 1597.07              | 31.94          |

| 21          | 15.65                | 0.31           | 64          | 162.84               | 3.26           | 107         | 1685.98              | 33.72          |

| 22          | 16.65                | 0.33           | 65          | 172.16               | 3.44           | 108         | 1780.22              | 35.60          |

| 23          | 17.65                | 0.35           | 66          | 181.82               | 3.64           | 109         | 1879.79              | 37.60          |

| 24          | 18.65                | 0.37           | 67          | 191.81               | 3.84           | 110         | 1984.68              | 39.69          |

| 25          | 19.65                | 0.39           | 68          | 202.46               | 4.05           | 111         | 2095.57              | 41.91          |

| 26          | 20.65                | 0.41           | 69          | 213.79               | 4.28           | 112         | 2212.79              | 44.26          |

| 27          | 21.65                | 0.43           | 70          | 225.77               | 4.52           | 113         | 2336.33              | 46.73          |

| 28          | 22.98                | 0.46           | 71          | 238.43               | 4.77           | 114         | 2466.53              | 49.33          |

| 29          | 24.31                | 0.49           | 72          | 251.75               | 5.03           | 115         | 2604.39              | 52.09          |

| 30          | 25.64                | 0.51           | 73          | 265.73               | 5.31           | 116         | 2749.91              | 55.00          |

| 31          | 26.97                | 0.54           | 74          | 280.72               | 5.61           | 117         | 2903.76              | 58.08          |

| 32          | 28.64                | 0.57           | 75          | 296.37               | 5.93           | 118         | 3065.60              | 61.31          |

DS12631 - Rev 4 page 23/69

| Step number | t <sub>ON</sub> (µs) | Duty cycle (%) | Step number | t <sub>ON</sub> (µs) | Duty cycle (%) | Step number | t <sub>ON</sub> (µs) | Duty cycle (%) |

|-------------|----------------------|----------------|-------------|----------------------|----------------|-------------|----------------------|----------------|

| 33          | 30.30                | 0.61           | 76          | 312.69               | 6.25           | 119         | 3237.09              | 64.74          |

| 34          | 31.97                | 0.64           | 77          | 330.34               | 6.61           | 120         | 3417.58              | 68.35          |

| 35          | 33.63                | 0.67           | 78          | 348.65               | 6.97           | 121         | 3608.72              | 72.17          |

| 36          | 35.63                | 0.71           | 79          | 367.97               | 7.36           | 122         | 3810.19              | 76.20          |

| 37          | 37.63                | 0.75           | 80          | 388.61               | 7.77           | 123         | 4022.97              | 80.46          |

| 38          | 39.63                | 0.79           | 81          | 410.26               | 8.21           | 124         | 4247.75              | 84.95          |

| 39          | 41.96                | 0.84           | 82          | 433.23               | 8.66           | 125         | 4484.84              | 89.70          |

| 40          | 44.29                | 0.89           | 83          | 457.21               | 9.14           | 126         | 4735.59              | 94.71          |

| 41          | 46.62                | 0.93           | 84          | 482.85               | 9.66           | 127         | 5000.00              | 100.00         |

| 42          | 49.28                | 0.99           | 85          | 510.16               | 10.20          |             |                      |                |

Figure 11. Local dimming duty cycle vs dimming steps

DS12631 - Rev 4 page 24/69

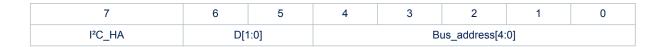

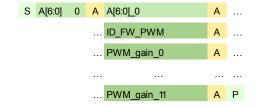

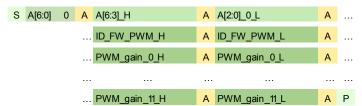

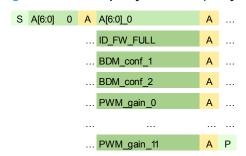

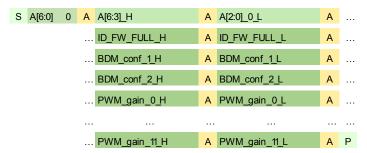

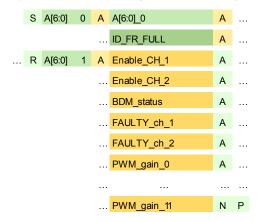

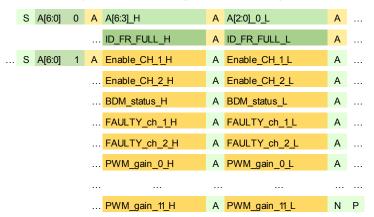

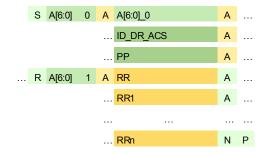

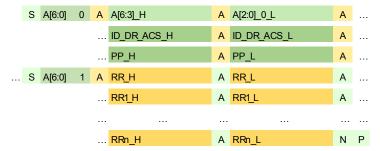

# 13 Register descriptions

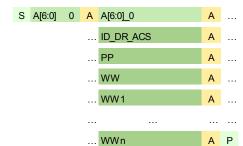

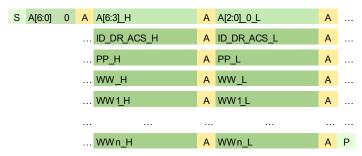

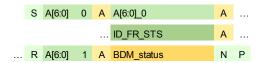

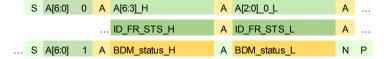

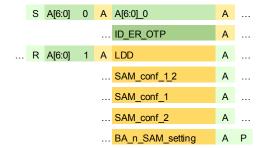

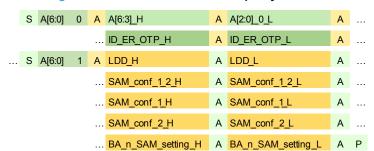

Table 13. Embedded register list and direct address table

| #       | Register name (one byte content)                | R/W | Functions                                                                                | Reg. direct<br>address <sup>(1)</sup> |

|---------|-------------------------------------------------|-----|------------------------------------------------------------------------------------------|---------------------------------------|

| BDM reg | isters                                          |     |                                                                                          |                                       |

| 1       | BDM_conf_1 (bus-driven mode config. 1)          | R/W | BDM/SAM selection, FLG and detection behavior, PWM ON or OFF, channels 11 to 8 ON or OFF | 0x00                                  |

| 2       | BDM_conf_2 (bus-driven mode config. 2)          | R/W | Channels 7 to 0 ON or OFF                                                                | 0x01                                  |

| 3       | BDM_status (bus-driven mode status)             | R   | Rext_fault, msg_err, global_en, diag_en, T_alert, T_fail, ext_fault, LED_fault           | 0x02                                  |

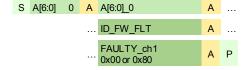

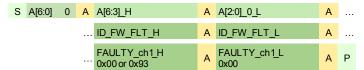

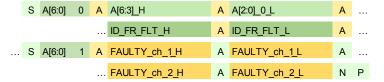

| 4       | Faulty_ch_1 (faulty channels 1+PWM frequency)   | R/W | PWM 110 or 220 Hz, faulty_ch 11 to 8                                                     | 0x03                                  |

| 5       | Faulty_ch_2<br>(faulty channels 2)              | R   | Faulty_ch 7 to 0                                                                         | 0x04                                  |

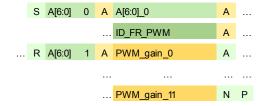

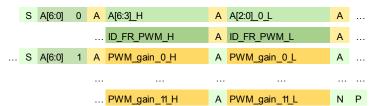

| 6 to 17 | PWM_gain_x<br>(channel PWM gain)                | R/W | PWM chx ON or OFF, PWM chx gain (first byte is related to ch0)                           | 0x05 to 0x10                          |

| 18      | LDD (LED driver device)                         | R   | Versioning: driver ID and revision ID                                                    | -                                     |

|         |                                                 |     | SAM registers (OTP)                                                                      | ,                                     |

| 1       | SAM_conf_1_2 (standalone mode out config. 1/2)  | R/W | OTP1/2=L channels 11 to 8 ON or OFF OTP1/2=H channels 11 to 8 ON or OFF                  | 0x20                                  |

| 2       | SAM_conf_2 (standalone mode out config. 2)      | R/W | OTP1/2=L channels 7 to 0 ON or OFF                                                       | 0x21                                  |

| 3       | SAM_conf_2 (standalone mode out config. 2)      | R/W | OTP1/2=H channels 7 to 0 ON or OFF                                                       | 0x22                                  |

| 4       | BA_n_SAM_setting (device bus ADDR and settings) | R/W | Hamming ON or OFF, FLG and detection behavior, I <sup>2</sup> C bus address              | 0x23                                  |

Direct address can be used with 0x81 command (see the command table). Please note that register address must be

maintained inside the allowed intervals: 0x00 ≤ direct ADDR ≤ 0x10 (BDM) and 0x20 ≤ direct ADDR ≤ 0x23 (SAM). Outside

these intervals, all other addresses are forbidden.

DS12631 - Rev 4 page 25/69

Accessing read only registers (BDM\_status and Faulty\_ch\_2) in write mode with direct address command could affect the register content.

Safer way to address registers is using the specific commands reported in Table 29. Command representation and description, they are fully controlled by internal state machine.

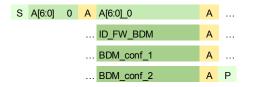

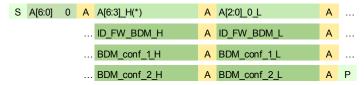

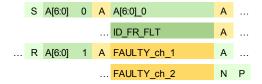

# 13.1 BDM\_conf\_1 / Enable\_CH\_1 register

Reg. name: BDM\_conf\_1 / Enable\_CH\_1

Reg. default value: 0x00 Reg. direct address: 0x00 Command involved: 0x00/0x02 Reg. access mode: R/W

|   | 7        | 6      | 5    | 4       | 3              | 2       | 1        | 0 |

|---|----------|--------|------|---------|----------------|---------|----------|---|

| W | PDM Flog | Dt     | 1.01 | DIAMA E | BDM_conf[11:8] |         |          |   |

| R | BDM_Flag | D[1:0] |      | PWM_En  |                | Enable_ | CH[11:8] |   |

Table 14. BDM\_conf\_1 field descriptions

| Field    |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Description                                                            |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

|          | Used to push th                                                                                                                                                                                                                                                                                                                                                                                                     | Used to push the LED driver to BDM mode when VDDD is high <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                     |                                                                        |  |  |  |  |  |

| BDM_Flag | 0: SAM                                                                                                                                                                                                                                                                                                                                                                                                              | 0: SAM                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                        |  |  |  |  |  |

|          | 1: BDM                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                        |  |  |  |  |  |

|          | Used to configu or undriven).                                                                                                                                                                                                                                                                                                                                                                                       | re the LED open I                                                                                                                                                                                                                                                                                                                                                                                                                                            | oad circuit diagnosis response and associated FLG pin behavior (driven |  |  |  |  |  |

|          | Available respon                                                                                                                                                                                                                                                                                                                                                                                                    | nses are:                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                        |  |  |  |  |  |

|          | detected, the LE recovered, the LE outputs are swit                                                                                                                                                                                                                                                                                                                                                                 | <b>Recovery</b> : When set, and PG is asserted, the LED open load diagnosis is performed. When a fault is detected, the LED driver imposes a current on the faulty branch, switching OFF the others. When a fault is recovered, the LED driver returns to normal operation. If the FLG pin is triggered externally, the LED driver outputs are switched OFF and the low power mode is entered. If PG is not asserted, FLG and/or load diagnosis are ignored. |                                                                        |  |  |  |  |  |

|          | <b>Outage</b> : When set, the LED open load diagnostic is performed by the LED driver and Faulty_ch_1/2 registers are updated accordingly. When a fault is detected no action is taken on the current regulation. If the FLG pin is triggered externally, no action is taken.                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                        |  |  |  |  |  |