# NDBA100N10B

www.onsemi.com

# **Power MOSFET** 100V, 6.9mΩ, 100A, N-Channel

#### **Features**

- Low On-Resistance

- Low Gate Charge

- High Speed Switching

- 100% Avalanche Tested

- Pb-Free, Halogen Free and RoHS Compliance

#### **VDSS** R<sub>DS</sub>(on) Max ID Max 6.9 mΩ@15V 100V 100A 8.2 mΩ@10V

## **Specifications**

### **Absolute Maximum Ratings** at Ta = 25°C

| Parameter                                                             | Symbol           | Value       | Unit |

|-----------------------------------------------------------------------|------------------|-------------|------|

| Drain to Source Voltage                                               | V <sub>DSS</sub> | 100         | V    |

| Gate to Source Voltage                                                | V <sub>GSS</sub> | ±20         | V    |

| Drain Current (DC)                                                    | ID               | 100         | Α    |

| Drain Current (Pulse)<br>PW≤10μs, duty cycle≤1%                       | I <sub>DP</sub>  | 400         | Α    |

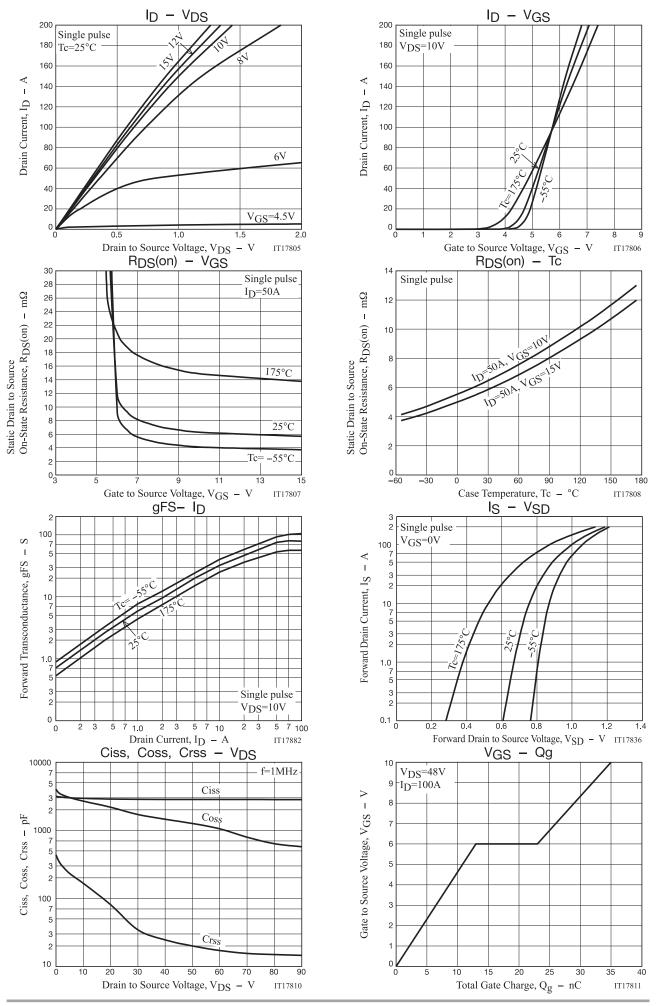

| Power Dissipation<br>Tc=25°C                                          | PD               | 110         | W    |

| Junction Temperature                                                  | Tj               | 175         | °C   |

| Storage Temperature                                                   | Tstg             | –55 to +175 | °C   |

| Source Current (Body Diode)                                           | Is               | 100         | Α    |

| Avalanche Energy (Single Pulse) *1                                    | EAS              | 147         | mJ   |

| Lead Temperature for Soldering Purposes, 3mm from Case for 10 Seconds | TL               | 260         | °C   |

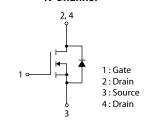

## **Electrical Connection** N-Channel

**TO-263 CASE 418AJ**

#### Packing Type: TL **Thermal Resistance Ratings**

| Parameter                     | Symbol            | Value | Unit |

|-------------------------------|-------------------|-------|------|

| Junction to Case Steady State | R <sub>θ</sub> JC | 1.36  | 0000 |

| Junction to Ambient *2        | R <sub>0.IA</sub> | 62.5  | °C/W |

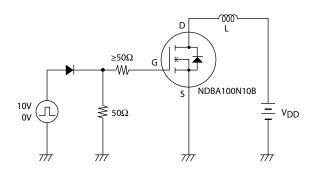

Note : \*1  $V_{DD}$ =48V, L=100 $\mu$ H,  $I_{AV}$ =40A (Fig.1)

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 5 of this data sheet.

<sup>\*2</sup> Surface mounted on FR4 board using recommended footprint

## **NDBA100N10B**

### **Electrical Characteristics** at Ta = 25°C

| Description                                | O. mala al            | O object                                                                       | Value |       |      | 11.2 |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------------------|-------|-------|------|------|

| Parameter Symbol                           |                       | Conditions                                                                     | min   | typ   | max  | Unit |

| Drain to Source Breakdown Voltage          | V(BR)DSS              | I <sub>D</sub> =10mA, V <sub>GS</sub> =0V                                      | 100   |       |      | ٧    |

| Zero-Gate Voltage Drain Current            | IDSS                  | V <sub>DS</sub> =100V, V <sub>GS</sub> =0V                                     |       |       | 10   | μΑ   |

| Gate to Source Leakage Current             | IGSS                  | V <sub>GS</sub> =±20V, V <sub>DS</sub> =0V                                     |       |       | ±100 | nA   |

| Gate Threshold Voltage                     | V <sub>GS</sub> (th)  | V <sub>DS</sub> =10V, I <sub>D</sub> =1mA                                      | 2     |       | 4    | ٧    |

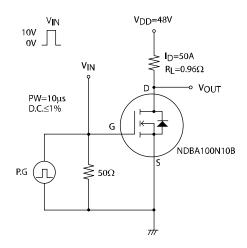

| Forward Transconductance                   | 9FS                   | V <sub>DS</sub> =10V, I <sub>D</sub> =50A                                      |       | 75    |      | S    |

| Otatia Dania ta Carras On Otata Daniatarra | R <sub>DS</sub> (on)1 | I <sub>D</sub> =50A, V <sub>GS</sub> =15V                                      |       | 5.7   | 6.9  | mΩ   |

| Static Drain to Source On-State Resistance | R <sub>DS</sub> (on)2 | I <sub>D</sub> =50A, V <sub>GS</sub> =10V                                      |       | 6.3   | 8.2  | mΩ   |

| Input Capacitance                          | Ciss                  |                                                                                |       | 2,950 |      | pF   |

| Output Capacitance                         | Coss                  | V <sub>DS</sub> =50V, f=1MHz                                                   |       | 1,250 |      | pF   |

| Reverse Transfer Capacitance               | Crss                  |                                                                                |       | 20    |      | pF   |

| Turn-ON Delay Time                         | t <sub>d</sub> (on)   |                                                                                |       | 40    |      | ns   |

| Rise Time                                  | t <sub>r</sub>        | See Fig.2                                                                      |       | 385   |      | ns   |

| Turn-OFF Delay Time                        | t <sub>d</sub> (off)  |                                                                                |       | 68    |      | ns   |

| Fall Time                                  | t <sub>f</sub>        |                                                                                |       | 52    |      | ns   |

| Total Gate Charge                          | Qg                    |                                                                                |       | 35    |      | nC   |

| Gate to Source Charge                      | Qgs                   | V <sub>DS</sub> =48V, V <sub>GS</sub> =10V, I <sub>D</sub> =100A               |       | 13    |      | nC   |

| Gate to Drain "Miller" Charge              | Qgd                   | ]                                                                              |       | 10    |      | nC   |

| Forward Diode Voltage                      | V <sub>SD</sub>       | I <sub>S</sub> =100A, V <sub>GS</sub> =0V                                      |       | 1.1   | 1.5  | V    |

| Reverse Recovery Time                      | t <sub>rr</sub>       | See Fig.3                                                                      |       | 130   |      | ns   |

| Reverse Recovery Charge                    | Q <sub>rr</sub>       | I <sub>S</sub> =100A, V <sub>GS</sub> =0V, V <sub>DD</sub> =50V, di/dt=100A/μs |       | 400   |      | nC   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

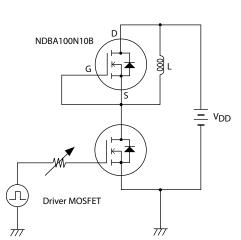

Fig.1 Unclamped Inductive Switching Test Circuit

Fig.3 Reverse Recovery Time Test Circuit

## Fig.2 Switching Time Test Circuit

## **NDBA100N10B**

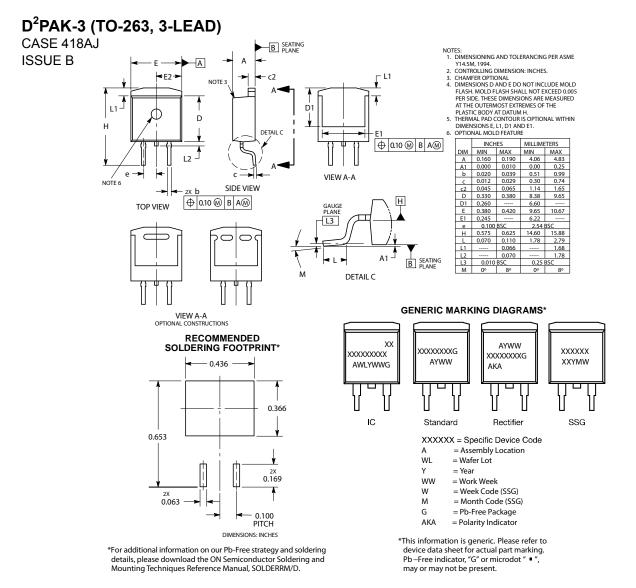

## **Package Dimensions**

NDBA100N10BT4H

### ORDERING INFORMATION

| Device         | Package                                  | Shipping               | note                     |  |

|----------------|------------------------------------------|------------------------|--------------------------|--|

| NDBA100N10BT4H | D <sup>2</sup> PAK-3<br>(TO-263, 3-LEAD) | 800 pcs. / Tape & Reel | Pb-Free and Halogen Free |  |

<sup>†</sup> For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. http://www.onsemi.com/pub\_link/Collateral/BRD8011-D.PDF

Note on usage: Since the NDBA100N10B is a MOSFET product, please avoid using this device in the vicinity of highly charged objects.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent re