## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

### TIBPAL20L10-25M. TIBPAL20X4-25M, TIBPAL20X8-25M, TIBPAL20X10-25M TIBPAL20L10-20C. TIBPAL20X4-20C. TIBPAL20X8-20C. TIBPAL20X10-20C HIGH-PERFORMANCE EXCLUSIVE OR IMPACT ™PAI® CIRCUITS

D2920, OCTOBER 1985-REVISED DECEMBER 1987

- High Performance . . . 35 MHz Min

- Preload Capability on Output Registers Simplifies Testing

- Power-Up Clear on Registered Devices

- Package Options Include Both Plastic and Ceramic Chip Carriers in Addition to Plastic and Ceramic DIPs

| DEVICE    | INPUTS | 3-STATE<br>O OUTPUTS | REGISTERED<br>a outputs | I/O<br>PORTS |

|-----------|--------|----------------------|-------------------------|--------------|

| 'PAL20L10 | 12     | 2                    | 0                       | 8            |

| 'PAL20X4  | 10     | 0                    | 4 (3-state buffers)     | 6            |

| 'PAL20X8  | 10     | 0                    | 8 (3-state buffers)     | 2            |

| 'PAL20X10 | 10     | 0                    | 10 (3-state buffers)    | D            |

### description

These programmable array logic devices feature high speed and functional equivalency when compared with currently available devices. These IMPACT™ circuits combine the latest Advanced Low-Power Schottky† technology with proven titanium-tungsten fuses to provide reliable, high-performance substitutes for conventional TTL logic. Their easy programmability allows for quick design of custom functions and typically results in a more compact circuit board. In addition, chip carriers are available for further reduction in board space.

All of the registered outputs are set to a low level during power-up. In addition, extra circuitry has been provided to allow loading of each register asynchronously to either a high or low state. This feature simplifies testing because the registers can be set to an initial state prior to executing the test sequence.

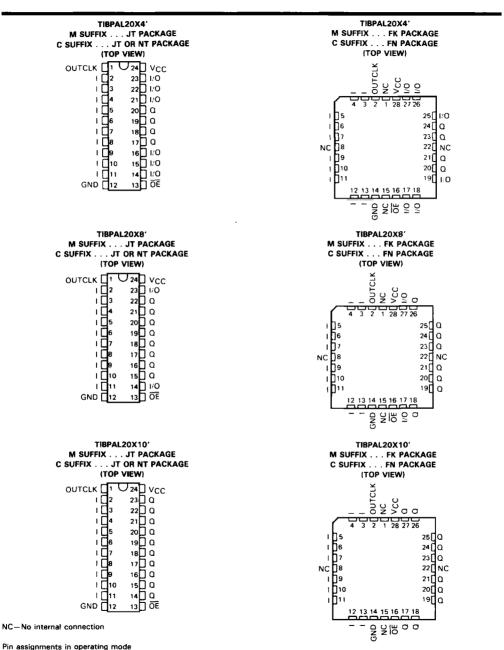

TIBPAL20L10 M SUFFIX . . . JT PACKAGE C SUFFIX . . . JT OR NT PACKAGE (TOP VIEW)

TIBPAL20L10 M SUFFIX . . . FK PACKAGE C SUFFIX . . . FN PACKAGE (TOP VIEW)

NC-No internal connection

Pin assignments in operating mode

The PAL20' M series is characterized for operation over the full military temperature range of -55°C to 125 °C. The PAL20' C series is characterized for operation from 0 °C to 75 °C.

IMPACT is a trademark of Texas Instruments Incorporated. PAL is a registered trademark of Monolithic Memories Inc. integrated Schottky-Barrier diode-clamped transistor is patented by Taxas Instruments, U.S. Patent Number 3,463,975.

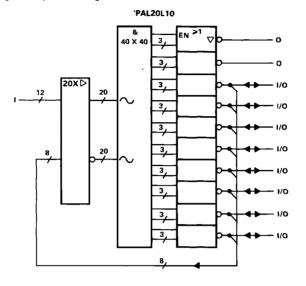

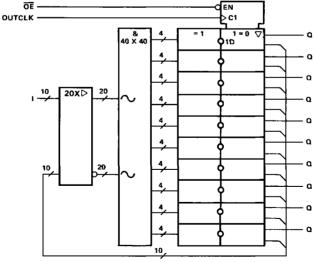

### functional block diagrams (positive logic)

'PAL20X4

→ denotes fused inputs

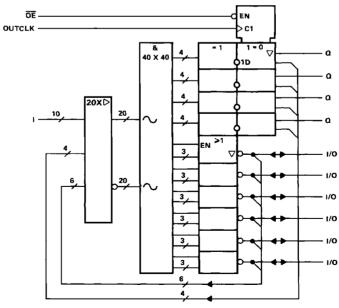

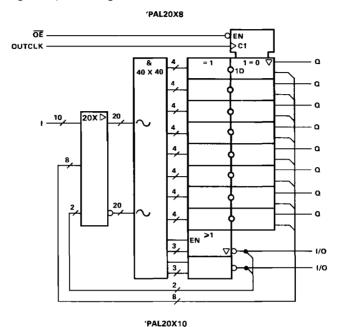

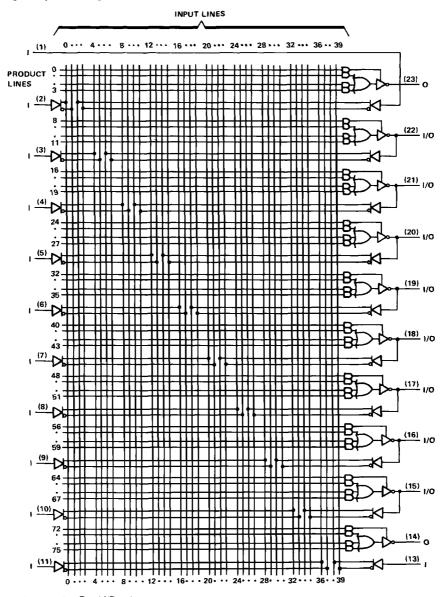

### functional block diagrams (positive logic)

PALZUX II

→ denotes fused inputs

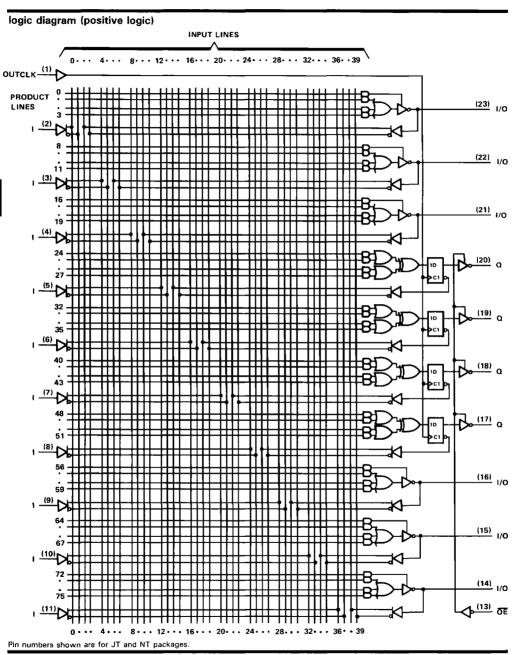

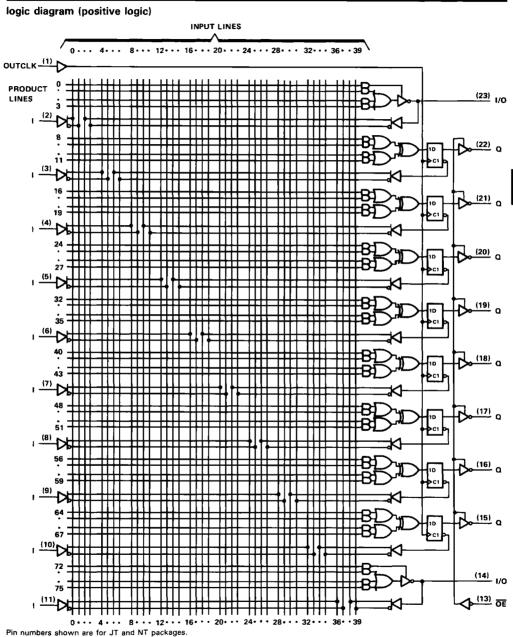

### logic diagram (positive logic)

Pin numbers shown are for JT and NT packages.

logic diagram (positive logic) INPUT LINES 0 - - - 4 - - - 8 - - - 12 - - - 16 - - - 20 - - - 24 - - - 28 - - - 32 - - - 36 - - 39 OUTCLK (1) PRODUCT LINES (22)27 (<u>18)</u> Q (<u>17)</u> Q (15) Q (10) 4 · · · 8 · · · 12 · · · 16 · · · 20 · · · 24 · · · 28 · · · 32 · · · 36 · · 39

Pin numbers shown are for JT and NT packages

### TIBPAL20L10-25M, TIBPAL20X4-25M, TIBPAL20X8-25M, TIBPAL20X10-25M TIBPAL20L10-20C, TIBPAL20X4-20C, TIBPAL20X8-20C, TIBPAL20X10-20C HIGH-PERFORMANCE EXCLUSIVE OR IMPACT ™PAI® CIRCUITS

| absolute maximum ratings over operating free-air temperature range (unless | otherwise noted) |

|----------------------------------------------------------------------------|------------------|

| Supply voltage, VCC (see Note 1)                                           | 7 V              |

| Input voltage (see Note 1)                                                 | 5.5 V            |

| Voltage applied to a disabled output (see Note 1)                          | 5.5 V            |

| Operating free-air temperature range: M suffix                             | 55°C to 125°C    |

| C suffix                                                                   | 0°C to 75°C      |

| Storage temperature range                                                  | 65°C to 150°C    |

NOTE 1: These ratings apply except for programming pins during a programming cycle.

### recommended operating conditions

| DADAMETER         |                                              |      | i   | 25M |      |     | -20C |     |      |

|-------------------|----------------------------------------------|------|-----|-----|------|-----|------|-----|------|

| PARAMETER         |                                              |      |     | NOM | MAX  | MIN | NOM  | MAX | UNIT |

| Vcc               | Supply voltage                               | 4.5  | 5   | 5.5 | 4.75 | 5   | 5.25 | V   |      |

| VIH               | High-level input voltage                     | 2    |     | 5.5 | 2    |     | 5.5  | V   |      |

| VIL               | Low-level input voltage                      |      |     | 0.8 |      |     | 0.8  | V   |      |

| ГОН               | High-level output current                    |      |     | -2  |      |     | -3.2 | mA  |      |

| lOL               | Low-level output current                     |      |     |     | 12   |     |      | 24  | mA   |

| fclock            | Clock frequency                              |      | 0   |     | 25   | 0   |      | 35  | MHz  |

| _                 | D to describe that are Note 2                | High | 15  |     |      | 10  |      |     | ns   |

| t <sub>w</sub> Pu | Pulse duration, clock, see Note 2            | Low  | 20  |     |      | 14  |      |     | ns   |

| t <sub>su</sub>   | Setup time, input or feedback before OUTCLK1 |      |     |     |      | 20  |      |     | ns   |

| th                | Hold time, input or feedback after OU        | CLK† | 7 0 |     |      | 0   |      |     | ns   |

| TA                | Operating free-air temperature               |      | -55 |     | 125  | 0   |      | 75  | °C   |

NOTE 2: The high and low clock pulse durations cannot both be at the minimum values specified. Their sum must be equal to or greater than the minimum clock period, which is the reciprocal of the maximum recommended clock frequency.

### electrical characteristics over recommended free-air operating temperature range

| PARAMETER |                      | TEST CONDITIONS†       |                        |     | 25M  |       |          | -20C             |      |      |

|-----------|----------------------|------------------------|------------------------|-----|------|-------|----------|------------------|------|------|

|           |                      |                        |                        | MIN | TYP‡ | MAX   | MIN      | TYP <sup>‡</sup> | MAX  | UNIT |

| VIK       |                      | V <sub>CC</sub> = MIN, | lj = -18 mA            |     |      | -1.2  |          |                  | -1.2 | i v  |

| VOH       |                      | V <sub>CC</sub> = MIN, | IOH = MAX              | 2.4 | 3.2  |       | 2.4      | 3.3              |      | V    |

| VOL       |                      | VCC = MIN,             | IOL = MAX              | T   | 0.25 | 0.4   |          | 0.35             | 0,5  | V    |

|           | Outputs              | V MAY                  | V <sub>O</sub> = 2.7 V |     |      | 20    |          |                  | 20   |      |

| OZH       | I/O ports            | ACC = MAY              |                        |     |      | 100   |          |                  | 100  | μΑ   |

| . 1       | Outputs              | V <sub>CC</sub> = MAX, | V <sub>O</sub> = 0.4 V |     |      | - 20  | <u> </u> |                  | - 20 |      |

| IOZL      | ZL I/O ports         |                        |                        |     |      | -250  |          |                  | 250  | μA   |

| 4         |                      | V <sub>CC</sub> = MAX, | V <sub>I</sub> = 5.5 V |     |      | 0.1   |          |                  | 0.1  | mΑ   |

| ΉΗ        |                      | VCC = MAX,             | V <sub>1</sub> = 2.7 V |     |      | 20    |          |                  | 20   | μА   |

| IIL.      |                      | V <sub>CC</sub> = MAX, | V <sub>I</sub> = 0.4 V |     |      | -0.25 | i        |                  | 0.25 | m.A  |

| los§      |                      | V <sub>CC</sub> = 5 V, | Vo = 0                 | -30 |      | - 130 | -30      |                  | -130 | mA   |

|           | '20X4, '20X8, '20X10 | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 0     |     | 120  | 180   |          | 120              | 180  |      |

| 'cc       | ′20L10               |                        |                        |     | 120  | 165   |          | 120              | 165  | mA   |

<sup>&</sup>lt;sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

<sup>&</sup>lt;sup>‡</sup> All typical values are V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

<sup>§</sup> Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

## TIBPAL20L10-25M, TIBPAL20X4-25M, TIBPAL20X8-25M, TIBPAL20X10-25M TIBPAL20L10-20C, TIBPAL20X4-20C, TIBPAL20X8-20C, TIBPAL20X10-20C HIGH-PERFORMANCE EXCLUSIVE-OR IMPACT PAL® CIRCUITS

switching characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER        | FROM        | то     | TEST CONDITIONS        | -25M |                  |     | -20C |     |     |      |

|------------------|-------------|--------|------------------------|------|------------------|-----|------|-----|-----|------|

|                  |             |        |                        | MIN  | TYP <sup>†</sup> | MAX | MIN  | TYP | MAX | UNIT |

| fmax             |             |        |                        | 25   |                  |     | 35   |     |     | MHz  |

| _tpd             | 1, 1/0      | 0, 1/0 |                        |      | 12               | 25  |      | 12  | 20  | ns   |

| t <sub>pd</sub>  | OUTCLK†     | Q      | R1 = 200 $\Omega$ ,    |      | 10               | 20  |      | 10  | 15  | ns   |

| _ten             | <u>OE</u>   | Q      | $R2 = 390 \Omega$ ,    |      | 7                | 20  |      | 7   | 15  | ns   |

| <sup>t</sup> dis | <u>ŌĒ</u> ↑ | a      | C <sub>L</sub> = 50 pF |      | 7                | 20  |      | 7   | 15  | ns   |

| t <sub>en</sub>  | I, I/O      | 0, 1/0 |                        |      | 15               | 25  |      | 15  | 20  | ns   |

| t <sub>dis</sub> | 1, 1/0      | 0, 1/0 |                        |      | 15               | 25  |      | 15  | 20  | ns   |

<sup>&</sup>lt;sup>†</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

### programming information

Texas Instruments Programmable Logic Devices can be programmed using widely available software and inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and firmware are available upon request. Information on programmers capable of programming Texas Instruments Programmable Logic is also available, upon request, from the nearest TI field sales office, local authorized TI distributor, or by calling Texas Instruments at (214) 995-5762.

### PARAMETER MEASUREMENT INFORMATION

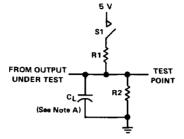

### LOAD CIRCUIT FOR THREE-STATE OUTPUTS

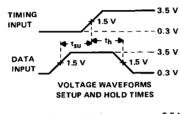

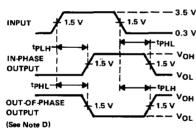

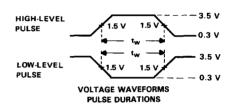

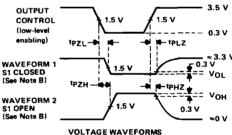

### VOLTAGE WAVEFORMS PROPAGATION DELAY TIMES

ENABLE AND DISABLE TIMES. THREE-STATE OUTPUTS

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control.

Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq 1$  MHz,  $t_T = t_f = 2$  ns, duty cycle = 50%.

- D. When measuring propagation delay times of 3-state outputs, switch S1 is closed.

# TIBPAL20L10-25M, TIBPAL20X4-25M, TIBPAL20X8-25M, TIBPAL20X10-25M TIBPAL20L10-20C, TIBPAL20X4-20C, TIBPAL20X8-20C, TIBPAL20X10-20C HIGH-PERFORMANCE EXCLUSIVE-OR IMPACT \*\*PAL\*\*\* CIRCUITS

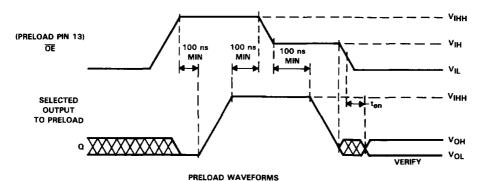

#### preload procedures

#### preload procedure for registered outputs

- Step 1 With V<sub>CC</sub> at 5 volts, raise Pin 13 (OE) to V<sub>IHH</sub> to disable the outputs and clear the registers (output goes low). Since the outputs are low, only high levels need be preloaded.

- Step 2 Raise the selected output to be preloaded high to VIHH.

- Step 3 Lower Pin 13 to VIH.

- Step 4 Remove the voltages applied to the outputs. (At least a 100-ns wait is required between step 3 and step 4)

- Step 5 Lower Pin 13 to VIL to verify preload.

### security fuse programming

NOTE: Pin numbers shown apply only for the DIP package. If a chip carrier socket adaptor is not used, pin numbers must be changed accordingly.