SCBS881E –JANUARY 2010–REVISED OCTOBER 2018

TMS3705

# TMS3705 Transponder Base Station IC

### 1 Device Overview

#### 1.1 Features

- Base Station IC for TI-RFid™ RF Identification Systems

- · Drives Antenna

- · Sends Modulated Data to Antenna

- Detects and Demodulates Transponder Response (FSK)

- · Short-Circuit Protection

- Diagnosis

- Sleep-Mode Supply Current: 0.2 mA

- · Designed for Automotive Requirements

- 16-Pin SOIC (D) Package

### 1.2 Applications

- Car Access

- Immobilization

- Building Access

- Livestock Reader

### 1.3 Description

The TMS3705 transponder base station IC is used to drive the antenna of a TI-RFid transponder system, to send data modulated on the antenna signal, and to detect and demodulate the response of the transponder. The response of the transponder is a frequency shift keyed (FSK) signal. The high or low bits are coded in two different high-frequency signals (134.2 kHz for low bits and 123 kHz for high bits, nominal). The transponder induces these signals in the antenna coil according an internally stored code. The energy that the transponder needs to send out the data is stored in a charge capacitor in the transponder. The antenna field charges this capacitor in a preceding charge phase. The IC has an interface to an external microcontroller.

There are two configurations for the clock supply to both the microcontroller and the base station IC:

- 1. The microcontroller and base station IC are supplied with a clock signal derived from only one resonator: The resonator is attached to the microcontroller. The base station IC is supplied with a clock signal driven by the digital clock output of the microcontroller. The clock frequency is either 4 MHz or 2 MHz, depending on the selected microcontroller type.

- 2. The microcontroller and the base station each have their own resonator.

The base station IC has an on-chip PLL that generates a clock frequency of 16 MHz for internal clock supply only. Only TMS3705DDRQ1 is recommended in combination with AES transponder products (for example, TRPWS21GTEA or RF430F5xxx). TMS3705EDRQ1 is recommended for best performance in combination with DST40, DST80, MPT transponders (for example, TMS37145TEAx, TMS37126xx, TMS37x128xx, TMS37x136xx, TMS37x158xx, RI-TRP-DR2B-xx, RI-TRP-BRHP-xx) and cannot be used in combination with AES transponder products.

### Device Information<sup>(1)</sup>

| PART NUMBER  | PACKAGE   | BODY SIZE (2)    |

|--------------|-----------|------------------|

| TMS3705EDRQ1 | SOIC (16) | 9.9 mm × 3.91 mm |

| TMS3705DDRQ1 | SOIC (16) | 9.9 mm × 3.91 mm |

- (1) For the most current part, package, and ordering information for all available devices, see the Package Option Addendum in Section 9, or see the TI website at www.ti.com.

- (2) The sizes shown here are approximations. For the package dimensions with tolerances, see the Mechanical Data in Section 9.

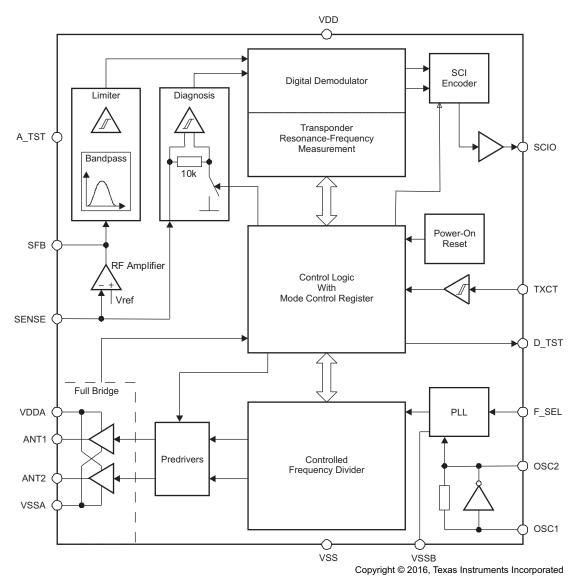

### 1.4 Functional Block Diagram

Figure 1-1 shows the functional block diagram.

Figure 1-1. Functional Block Diagram

### **Table of Contents**

| 1 | Devi | ice Overview 1                                  |   | 6.5  | RF Amplifier                                | . 11       |

|---|------|-------------------------------------------------|---|------|---------------------------------------------|------------|

|   | 1.1  | Features 1                                      |   | 6.6  | Band-Pass Filter and Limiter                | 12         |

|   | 1.2  | Applications 1                                  |   | 6.7  | Diagnosis                                   | 12         |

|   | 1.3  | Description 1                                   |   | 6.8  | Power-on Reset                              | 12         |

|   | 1.4  | Functional Block Diagram 2                      |   | 6.9  | Frequency Divider                           | 12         |

| 2 | Revi | ision History 3                                 |   | 6.10 | Digital Demodulator                         | 12         |

| 3 | Devi | ice Characteristics4                            |   | 6.11 | Transponder Resonance-Frequency Measurement | 13         |

|   | 3.1  | Related Products 4                              |   | 6.12 | SCI Encoder                                 | 13         |

| 4 | Tern | ninal Configuration and Functions5              |   | 6.13 | Control Logic                               | 14         |

|   | 4.1  | Pin Diagram 5                                   |   | 6.14 | Test Pins                                   | 16         |

|   | 4.2  | Signal Descriptions 5                           | 7 | Appl | lications, Implementation, and Layout       | 17         |

| 5 | Spec | cifications 6                                   |   | 7.1  | Application Diagram                         | 17         |

|   | 5.1  | Absolute Maximum Ratings 6                      | 8 | Devi | ce and Documentation Support                | 18         |

|   | 5.2  | ESD Ratings6                                    |   | 8.1  | Getting Started and Next Steps              | 18         |

|   | 5.3  | Recommended Operating Conditions 6              |   | 8.2  | Device Nomenclature                         | 18         |

|   | 5.4  | Electrical Characteristics 7                    |   | 8.3  | Tools and Software                          | 19         |

|   | 5.5  | Thermal Resistance Characteristics for D (SOIC) |   | 8.4  | Documentation Support                       | 19         |

|   |      | Package <u>8</u>                                |   | 8.5  | Community Resources                         | 20         |

|   | 5.6  | Switching Characteristics                       |   | 8.6  | Trademarks                                  | 20         |

|   | 5.7  | Timing Diagrams 9                               |   | 8.7  | Electrostatic Discharge Caution             | . 20       |

| 6 | Deta | iled Description 11                             |   | 8.8  | Export Control Notice                       |            |

|   | 6.1  | Power Supply <u>11</u>                          |   | 8.9  | Glossary                                    | 20         |

|   | 6.2  | Oscillator                                      | 9 | Mec  | hanical, Packaging, and Orderable           |            |

|   | 6.3  | Predrivers <u>11</u>                            |   |      | mation                                      | <b>2</b> 1 |

|   | 6.4  | Full Bridge                                     |   |      |                                             |            |

## 2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from October 19, 2016 to October 31, 2018

Page

#### 3 Device Characteristics

Table 3-1 lists the characteristics of the TMS3705.

**Table 3-1. Device Characteristics**

| Characteristic              | TMS3705        |

|-----------------------------|----------------|

| Data rate (maximum)         | 8 kbps         |

| Frequency                   | 134.2 kHz      |

| Required antenna inductance | 100 to 1000 μH |

| Supply voltage              | 4.5 to 5.5 Vdc |

| Transmission principle      | HDX, FSK       |

#### 3.1 Related Products

For information about other devices in this family of products or related products, see the following links.

Products for Wireless Connectivity Connect more - Industry's broadest wireless connectivity portfolio

Products for NFC / RFID Texas Instruments provides one of the industry's largest, most differentiated NFC product portfolios enabling lower power solutions to meet a broad range of RF connectivity needs.

Companion Products for TMS3705 Review products that are frequently purchased or used with this product.

Reference Designs The TI Designs Reference Design Library is a robust reference design library that spans analog, embedded processor, and connectivity. Created by TI experts to help you jump start your system design, all TI Designs include schematic or block diagrams, BOMs, and design files to speed your time to market.

## 4 Terminal Configuration and Functions

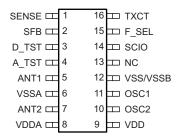

### 4.1 Pin Diagram

Figure 4-1 shows the pinout of the 16-pin D (SOIC) package.

NC – No connection

Figure 4-1. 16-Pin D Package (Top View)

### 4.2 Signal Descriptions

Table 4-1 describes the device signals.

**Table 4-1. Signal Descriptions**

| TERMINAL |          | TYPE           | DECORIDEION                                                    |  |

|----------|----------|----------------|----------------------------------------------------------------|--|

| NO.      | NAME     | ITPE           | DESCRIPTION                                                    |  |

| 1        | SENSE    | Analog input   | Input of the RF amplifier                                      |  |

| 2        | SFB      | Analog output  | Output of the RF amplifier                                     |  |

| 3        | D_TST    | Digital output | Test output for digital signals                                |  |

| 4        | A_TST    | Analog output  | Test output for analog signals                                 |  |

| 5        | ANT1     | Driver output  | Antenna output 1                                               |  |

| 6        | VSSA     | Supply input   | Ground for the full bridge drivers                             |  |

| 7        | ANT2     | Driver output  | Antenna output 2                                               |  |

| 8        | VDDA     | Supply input   | Voltage supply for the full bridge drivers                     |  |

| 9        | VDD      | Supply input   | Voltage supply for nonpower blocks                             |  |

| 10       | OSC2     | Analog output  | Oscillator output                                              |  |

| 11       | OSC1     | Analog input   | Oscillator input                                               |  |

| 12       | VSS/VSSB | Supply input   | Ground for nonpower blocks and PLL                             |  |

| 13       | NC       |                | Not connected                                                  |  |

| 14       | SCIO     | Digital output | Data output to the microcontroller                             |  |

| 15       | F_SEL    | Digital input  | Control input for frequency selection (default value is high)  |  |

| 16       | TXCT     | Digital input  | Control input from the microcontroller (default value is high) |  |

## 5 Specifications

### 5.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                     |                                                  |                           | MIN  | MAX            | UNIT |

|---------------------|--------------------------------------------------|---------------------------|------|----------------|------|

| $V_{DD}$            | Supply voltage range                             | VDD, VSS/VSSB, VDDA, VSSA | -0.3 | 7              | V    |

| $V_{OSC}$           | Voltage range                                    | OSC1, OSC2                | -0.3 | $V_{DD} + 0.3$ | V    |

| V <sub>inout</sub>  | Voltage range                                    | SCIO, TXCT, F_SEL, D_TST  | -0.3 | $V_{DD} + 0.3$ | V    |

| I <sub>inout</sub>  | Overload clamping current                        | SCIO, TXCT, F_SEL, D_TST  | -5   | 5              | mA   |

| $V_{ANT}$           | Output voltage                                   | ANT1, ANT2                | -0.3 | $V_{DD} + 0.3$ | V    |

| I <sub>ANT</sub>    | Output peak current                              | ANT1, ANT2                | -1.1 | 1.1            | Α    |

| V <sub>analog</sub> | Voltage range                                    | SENSE, SFB, A_TST         | -0.3 | $V_{DD} + 0.3$ | V    |

| I <sub>SENSE</sub>  | SENSE input current                              | SENSE, SFB, A_TST         | -5   | 5              | mA   |

| I <sub>SFB</sub>    | Input current in case of overvoltage             | SFB                       | -5   | 5              | mA   |

| T <sub>A</sub>      | Operating ambient temperature                    |                           | -40  | 85             | °C   |

| T <sub>stg</sub>    | Storage temperature                              |                           | -55  | 150            | °C   |

| P <sub>D</sub>      | Total power dissipation at T <sub>A</sub> = 85°C |                           |      | 0.5            | W    |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 5.2 ESD Ratings

|           |                              | VALUE | UNIT |

|-----------|------------------------------|-------|------|

| $V_{ESD}$ | ESD protection (MIL STD 883) | ±2000 | V    |

## 5.3 Recommended Operating Conditions

|                 |                           |                           | MIN                 | NOM | MAX                 | UNIT |

|-----------------|---------------------------|---------------------------|---------------------|-----|---------------------|------|

| $V_{DD}$        | Supply voltage            | VDD, VSS/VSSB, VDDA, VSSA | 4.5                 | 5   | 5.5                 | V    |

| $f_{osc}$       | Oscillator frequency      | OSC1, OSC2                |                     | 4   |                     | MHz  |

| $V_{IH}$        | High-level input voltage  | F_SEL, TXCT, OSC1         | 0.7 V <sub>DD</sub> |     |                     | V    |

| V               | Low-level input voltage   | TXCT, OSC1                |                     |     | $0.3~V_{DD}$        | V    |

| V <sub>IL</sub> |                           | F_SEL                     |                     |     | 0.2 V <sub>DD</sub> | V    |

| $I_{OH}$        | High-level output current | SCIO, D_TST               | -1                  |     |                     | mA   |

| $I_{OL}$        | Low-level output current  | SCIO, D_TST               |                     |     | 1                   | mA   |

### **Electrical Characteristics**

$V_{DD} = 4.5 \text{ V}$  to 5.5 V,  $f_{osc} = 4 \text{ MHz}$ ,  $F\_SEL = high$ , over operating free-air temperature range (unless otherwise noted)

|                                         | PARAMETER                                                                                 | TEST CONDITIONS                                                                                                                 | MIN                 | TYP   | MAX                 | UNIT |

|-----------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|---------------------|------|

| Power S                                 | Supply (VDD, VSS/VSSB, VDDA, VSSA)                                                        |                                                                                                                                 |                     |       |                     |      |

| I <sub>DD</sub>                         | Supply current                                                                            | Sum of supply currents in Charge phase, without antenna load                                                                    |                     | 8     | 20                  | mA   |

| I <sub>Sleep</sub>                      | Supply current, Sleep state                                                               | Sum of supply currents in Sleep state, without I/O currents                                                                     |                     | 0.015 | 0.2                 | mA   |

| Oscillate                               | or (OSC1, OSC2)                                                                           |                                                                                                                                 |                     |       |                     |      |

| g <sub>osc</sub>                        | Transconductance                                                                          | $f_{\rm osc} = 4$ MHz, 0.5 $V_{\rm pp}$ at OSC1                                                                                 | 0.5                 | 2     | 5                   | mA/V |

| C <sub>in</sub>                         | Input capacitance at OSC1 (1)                                                             |                                                                                                                                 |                     |       | 10                  | pF   |

| C <sub>out</sub>                        | Output capacitance at OSC2 <sup>(1)</sup>                                                 |                                                                                                                                 |                     |       | 10                  | pF   |

| Logic In                                | puts (TXCT, F_SEL, OSC1)                                                                  |                                                                                                                                 |                     |       |                     |      |

| R <sub>pullup</sub>                     | Pullup resistance                                                                         | TXCT<br>F_SEL                                                                                                                   | 120<br>10           |       | 500<br>500          | kΩ   |

| Logio O                                 | utputs (SCIO, D_TST)                                                                      | I _OLL                                                                                                                          | 10                  |       | 300                 |      |

|                                         | High-level output voltage                                                                 |                                                                                                                                 | 0.8 V <sub>DD</sub> |       |                     | V    |

| V <sub>OH</sub>                         | Low-level output voltage                                                                  |                                                                                                                                 | O.O VDD             |       | 0.2 V <sub>DD</sub> | V    |

|                                         | dge Outputs (ANT1, ANT2)                                                                  |                                                                                                                                 |                     |       | U.Z V <sub>DD</sub> |      |

| ruii-Bric                               | age Outputs (ANTT, ANTZ)                                                                  | Full bridge N. shannel and D. shannel                                                                                           |                     |       |                     | 1    |

| $\Sigma R_{ds\_on}$                     | Sum of drain-source resistances                                                           | Full-bridge N-channel and P-channel MOSFETs at driver current I <sub>ant</sub> = 50 mA                                          |                     | 7     | 14                  | Ω    |

|                                         | Duty cycle                                                                                | P-channel MOSFETs of full bridge                                                                                                | 38%                 | 40%   | 42%                 |      |

| t <sub>on1</sub> /t <sub>on2</sub>      | Symmetry of pulse durations for the<br>P-channel MOSFETs of full bridge                   |                                                                                                                                 | 96%                 |       | 104.5%              |      |

| l <sub>oc</sub>                         | Threshold for overcurrent protection                                                      |                                                                                                                                 | 220                 |       | 1100                | mA   |

| t <sub>oc</sub>                         | Switch-off time of overcurrent protection                                                 | Short to ground with 3 $\Omega$                                                                                                 | 0.25                |       | 10                  | μs   |

| t <sub>doc</sub>                        | Delay for switching on the full bridge after an overcurrent                               |                                                                                                                                 | 2                   | 2.05  | 2.1                 | ms   |

| I <sub>leak</sub>                       | Leakage current                                                                           |                                                                                                                                 |                     |       | 1                   | μΑ   |

| Analog                                  | Module (SENSE, SFB, A_TST)                                                                | •                                                                                                                               | •                   |       |                     |      |

| I <sub>SENSE</sub>                      | Input current                                                                             | SENSE, In charge phase                                                                                                          | -2                  |       | 2                   | mA   |

| V <sub>DCREF</sub> /<br>V <sub>DD</sub> | DC reference voltage of RF amplifier, related to VDD                                      |                                                                                                                                 | 9.25%               | 10%   | 11%                 |      |

| GBW                                     | Gain-bandwidth product of RF amplifier                                                    | At 500 kHz with external components to achieve a voltage gain of minimum 4-mV <sub>pp</sub> and 5-mV <sub>pp</sub> input signal | 2                   |       |                     | MHz  |

| ФΟ                                      | Phase shift of RF amplifier                                                               | At 134 kHz with external components to achieve a voltage gain of 5-mV <sub>pp</sub> and 20-mV <sub>pp</sub> input signal        |                     |       | 16                  | 0    |

| V <sub>sfb</sub>                        | Peak-to-peak input voltage of band pass at which the limiter comparator should toggle (2) | At 134 kHz (corresponds to a minimal total gain of 1000)                                                                        | 5                   |       |                     | mV   |

| f <sub>low</sub>                        | Lower cut-off frequency of band-pass filter <sup>(3)</sup>                                |                                                                                                                                 | 24                  | 60    | 100                 | kHz  |

| f <sub>high</sub>                       | Higher cut-off frequency of band-pass filter (3)                                          |                                                                                                                                 | 160                 | 270   | 500                 | kHz  |

| $\Delta V_{hys}$                        | Hysteresis of limiter                                                                     | A_TST pin used as input, D_TST pin as output, offset level determined by band-pass stage                                        | 25                  | 50    | 135                 | mV   |

| Diagnos                                 | sis (SENSE)                                                                               |                                                                                                                                 |                     |       |                     |      |

| I <sub>diag</sub>                       | Current threshold for operating antenna (4)                                               |                                                                                                                                 | 80                  |       | 240                 | μΑ   |

Specified by design

Specified by design; functional test done for input voltage of 90 mV<sub>pp</sub>. Band-pass filter tested at three different frequencies:  $f_{mid} = 134$  kHz and gain > 30 dB;  $f_{low} = 24$  kHz;  $f_{high} = 500$  kHz. Attenuation < -3dB (reference = measured gain at f<sub>mid</sub> = 134 kHz).

Internal resistance switched on and much lower than external SENSE resistance.

### **Electrical Characteristics (continued)**

$V_{DD} = 4.5 \text{ V}$  to 5.5 V,  $f_{osc} = 4 \text{ MHz}$ ,  $F\_SEL = high$ , over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                      | TEST CONDITIONS                        | MIN    | TYP | MAX     | UNIT |  |

|--------------------|--------------------------------|----------------------------------------|--------|-----|---------|------|--|

| Phase-L            | Phase-Locked Loop (D_TST)      |                                        |        |     |         |      |  |

| f <sub>pll</sub>   | PLL frequency                  |                                        | 15.984 | 16  | 16.0166 | MHz  |  |

| $\Delta f/f_{pll}$ | Jitter of the PLL frequency    |                                        |        |     | 6%      |      |  |

| Power-0            | Power-On Reset (POR)           |                                        |        |     |         |      |  |

| V <sub>por_r</sub> | POR threshold voltage, rising  | V <sub>DD</sub> rising with low slope  | 1.9    |     | 3.5     | ٧    |  |

| $V_{por\_f}$       | POR threshold voltage, falling | V <sub>DD</sub> falling with low slope | 1.3    |     | 2.6     | V    |  |

### 5.5 Thermal Resistance Characteristics for D (SOIC) Package

|                 | PARAMETER                                              | VALUE | UNIT |

|-----------------|--------------------------------------------------------|-------|------|

| $R_{\theta JA}$ | Thermal resistance, junction to ambient <sup>(1)</sup> | 130   | °C/W |

<sup>(1)</sup> The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, High-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

### 5.6 Switching Characteristics

$V_{DD} = 4.5 \text{ V}$  to 5.5 V,  $f_{osc} = 4 \text{ MHz}$ ,  $F\_SEL = high$ , over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                                                    | TEST CONDITIONS                                                                                                                 | MIN | TYP  | MAX                   | UNIT |

|-----------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|------|-----------------------|------|

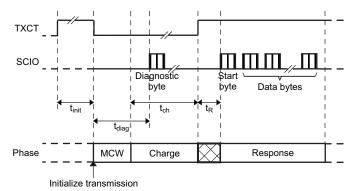

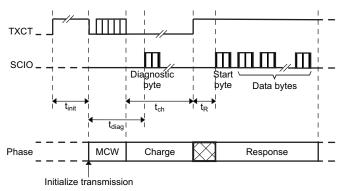

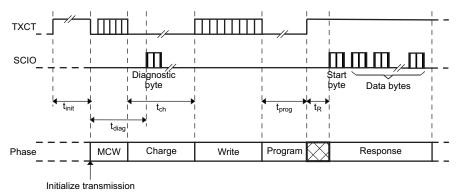

| t <sub>init min</sub> | Time for TXCT high to initialize a new transmission                                          | From start of the oscillator after power on or waking up until reaching the Idle state (see Figure 5-1, Figure 5-2, Figure 5-3) | 2   | 2.05 | 2.2                   | ms   |

| t <sub>diag</sub>     | Delay between leaving Idle state and start of diagnosis byte at SCIO                         | Normal operation (see Figure 5-1, Figure 5-2, Figure 5-3)                                                                       | 2   | 2.12 | 2.2                   | ms   |

| t <sub>R</sub>        | Delay between end of charge or end of program and start of transponder data transmit on SCIO | See Figure 5-1, Figure 5-2, Figure 5-3.                                                                                         |     | 3    |                       | ms   |

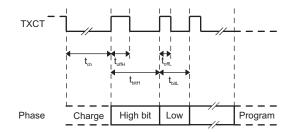

| t <sub>off</sub>      | Write pulse pause                                                                            | See Figure 5-5.                                                                                                                 | 0.1 |      |                       | ms   |

| t <sub>dwrite</sub>   | Signal delay on TXCT for controlling the full bridge                                         | Write mode                                                                                                                      | 73  | 79   | 85                    | μs   |

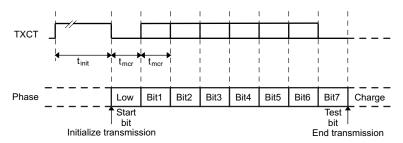

| t <sub>mcr</sub>      | NRZ bit duration for mode control register                                                   | See Figure 5-4.                                                                                                                 | 121 | 128  | 135                   | μs   |

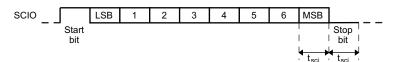

| t <sub>sci</sub>      | NRZ bit duration on SCIO                                                                     | Asynchronous mode (see Figure 5-6)                                                                                              | 63  | 64   | 65                    | μs   |

| t <sub>dstop</sub>    | Low signal delay on TXCT to stop                                                             | Synchronous mode                                                                                                                | 128 |      | 800                   | μs   |

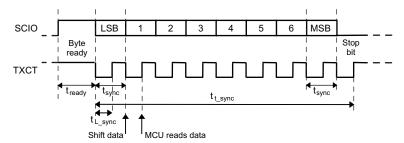

| t <sub>t_sync</sub>   | Total TXCT time for reading data on SCIO                                                     | Synchronous mode (see Figure 5-7)                                                                                               |     |      | 900                   | μs   |

| t <sub>sync</sub>     | TXCT period for shifting data on SCIO                                                        | Synchronous mode (seeFigure 5-7)                                                                                                | 4   | 64   | 100                   | μs   |

| t <sub>L_sync</sub>   | Low phase on TXCT                                                                            | Synchronous mode (see Figure 5-7)                                                                                               | 2   | 32   | t <sub>sync</sub> – 2 | μs   |

| t <sub>ready</sub>    | Data ready for output after SCIO goes high                                                   | Synchronous mode (see Figure 5-7)                                                                                               | 1   |      | 127                   | μs   |

### 5.7 Timing Diagrams

NOTE: MCW = Mode control write (to write into the mode control register)

Figure 5-1. Default Mode (Read Only, No Writing Into Mode Control Register)

NOTE: MCW = Mode control write (to write into the mode control register)

Figure 5-2. Read-Only Mode (Writing Into Mode Control Register)

NOTE: MCW = Mode control write (to write into the mode control register)

Figure 5-3. Write/Read Mode (Writing Into Mode Control Register)

Figure 5-4. Mode Control Write Protocol (NRZ Coding)

Figure 5-5. Transponder Write Protocol

Figure 5-6. Transmission on SCIO in Asynchronous Mode (NRZ Coding)

Figure 5-7. Transmission on SCIO in Synchronous Mode (NRZ Coding) (For Diagnosis Byte and Data Bytes)

## 6 Detailed Description

### 6.1 Power Supply

The device is supplied with 5 V by an external voltage regulator through two supply pins, one for providing the driver current for the antenna and the analog part in front of the digital demodulator and one for supplying the other blocks.

The power supply supplies a power-on reset that brings the control logic into Idle state as soon as the supply voltage drops under a certain value.

In Sleep state, the sum of both supply currents is reduced to 0.2 mA. The base station device falls into Sleep state 100 ms after TXCT has changed to high. When TXCT changes to low or is low, the base station IC immediately goes into and remains in normal operation.

#### 6.2 Oscillator

The oscillator generates the clock of the base station IC of which all timing signals are derived. Between its input and output a crystal or ceramic resonator is connected that oscillates at a typical frequency of 4 MHz. If a digital clock signal with a frequency of 4 MHz or 2 MHz is supplied to pin OSC1, the signal can be used to generate the internal operation frequency of 16 MHz.

The oscillator block contains a PLL that generates the internal clock frequency of 16 MHz from the input clock signal. The PLL multiplies the input clock frequency depending on the logic state of the input pin F\_SEL by a factor of 4 (F\_SEL is high) or by a factor of 8 (F\_SEL is low).

In the Sleep state, the oscillator is off.

#### 6.3 Predrivers

The predrivers generate the signals for the four power transistors of the full bridge using the carrier frequency generated by the frequency divider. The gate signals of the P-channel power transistors (active low) have the same width (±1 cycle of the 16 MHz clock), the delay between one P-channel MOSFET being switched off and the other one being switched on is defined to be 12 cycles of the 16-MHz clock. In write mode the first activation of a gate signal after a bit pause is synchronized to the received transponder signal by a phase shift of 18°.

### 6.4 Full Bridge

The full bridge drives the antenna current at the carrier frequency during the charge phase and the active time of the write phase. The minimal load resistance the full bridge sees between its outputs in normal operation at the resonance frequency of the antenna is  $43.3~\Omega$ . When the full bridge is not active, the two driver outputs are switched to ground.

Both outputs of the full bridge are protected independently against short circuits to ground.

In case of an occurring short circuit, the full bridge is switched off in less than 10 µs to avoid a drop of the supply voltage. After a delay time of less than 10 ms the full bridge is switched on again to test if the short circuit is still there. An overcurrent due to a resistive short to ground that is higher than the maximum current in normal operation but lower than the current threshold for overcurrent protection does not need to be considered.

### 6.5 RF Amplifier

The RF amplifier is an operational amplifier with a fixed internal voltage reference and a voltage gain of 5 defined by external resistors. The RF amplifier has a high gain-bandwidth product of at least 2 MHz to show a phase shift of less than 16° for the desired signal and to give the possibility to use it as a low-pass filter by adapting additional external components.

The input signal of the RF amplifier is DC coupled to the antenna. The amplitude of the output signal of the RF amplifier is higher than 5 mV peak-to-peak.

#### 6.6 Band-Pass Filter and Limiter

The band-pass filter provides amplification and filtering without external components. The lower cut-off frequency is approximately a factor of 2 lower than the average signal frequency of 130 kHz, the higher cut-off frequency is approximately a factor of 2 higher than 130 kHz.

The limiter converts the analog sine-wave signal to a digital signal. The limiter provides a hysteresis depending on the minimal amplitude of its input signal. The duty cycle of its digital output signal is between 40% and 60%. The band-pass filter and the limiter together have a high gain of at least 1000.

### 6.7 Diagnosis

The diagnosis is carried out during the charge phase to detect whether the full bridge and the antenna are working. When the full bridge drives the antenna, the voltage across the coil exceeds the supply voltage so that the voltage at the input of the RF amplifier is clamped by the ESD-protection diodes. For diagnosis, the SENSE pin is loaded on-chip with a switchable resistor to ground so that the internal switchable resistor and the external SENSE resistor form a voltage divider, while the internal resistor is switched off in read mode. When the voltage drop across the internal resistor exceeds a certain value, the diagnosis block passes the frequency of its input signal to the digital demodulator. The frequency of the diagnosis signal is accepted if eight subsequent times can be detected, all with their counter state within the range of 112 to 125, during the diagnosis time (at most 0.1 ms). The output signal is used only during the charge phase, otherwise it is ignored.

When the short-circuit protection switches off one of the full-bridge drivers, the diagnosis also indicates an improper operation of the antenna by sending the same diagnostic byte to the microcontroller as for the other failure mode.

During diagnosis, the antenna drivers are active. In synchronous mode the antenna drivers remain active up to 1 ms after the diagnosis is performed, without any respect to the logic state of the signal at TXCT (thus enabling the microcontroller to clock out the diagnosis byte).

### 6.8 Power-on Reset

The power-on reset generates an internal reset signal to allow the control logic to start up in the defined way.

### 6.9 Frequency Divider

The frequency divider is a programmable divider that generates the carrier frequency for the full-bridge antenna drivers. The default value for the division factor is the value 119 needed to provide the nominal carrier frequency of 134.45 kHz generated from 16 MHz. The resolution for programming the division factor is one divider step that corresponds to a frequency shift of approximately 1.1 kHz. The different division factors needed to cover the range of frequencies for meeting the resonance frequency of the transponder are 114 to 124.

#### 6.10 Digital Demodulator

The input signal of the digital demodulator comes from the limiter and is frequency-coded according to the high- and low-bit sequence of the transmitted transponder code. The frequency of the input signal is measured by counting the oscillation clock for the time period of the input signal. As the high-bit and low-bit frequencies are specified with wide tolerances, the demodulator is designed to distinguish the high-bit and the low-bit frequency by the shift between the two frequencies and not by the absolute values. The threshold between the high-bit and the low-bit frequency is defined to be 6.5 kHz lower than the measured low-bit frequency and has a hysteresis of ±0.55 kHz.

The demodulator is controlled by the control logic. After the charge phase (that is during read or write phase) it measures the time period of its input signal and waits for the transponder resonance-frequency measurement to determine the counter state for the threshold between high-bit and low-bit frequency. Then the demodulator waits for the occurrence of the start bit. For that purpose, the results of the comparisons between the measured time periods and the threshold are shifted in a 12-bit shift register. The detection of the start bit comes into effect when the contents of the shift register matches a specific pattern, indicating 8 subsequent periods below the threshold immediately followed by 4 subsequent periods above the threshold. A 2-period digital filter is inserted in front of the 12-bit shift register to make a start bit detection possible in case of a nonmonotonous progression of the time periods during a transition from low- to high-bit frequency.

The bit stream detected by the input stage of the digital demodulator passes a digital filter before being evaluated. After demodulation, the serial bit flow received from the transponder is buffered byte-wise before being sent to the microcontroller by SCI encoding.

### 6.11 Transponder Resonance-Frequency Measurement

During the prebit reception phase, the bits the transponder transmits show the low-bit frequency, which is the resonance frequency of the transponder. The time periods of the prebits are evaluated by the demodulator counter. Based on the counter states, an algorithm is implemented that ensures a correct measurement of the resonance frequency of the transponder:

- 1. A time period of the low-bit frequency has a counter state between 112 and 125.

- 2. The measurement of the low-bit frequency (the average of eight subsequent counter states) is accepted during the write mode, when the eight time periods have counter states in the defined range. The measurement during write mode is started with the falling edge at TXCT using the fixed delay time at which end the full bridge is switched on again.

- 3. The counter state of the measured low-bit frequency results in the average counter state of an accepted measurement and can be used to update the register of the programmable frequency divider.

- 4. The measurement of the low-bit frequency (the average of eight subsequent counter states) is accepted during the read mode, when the eight time periods have counter states in the defined range. The start of the measurement during read mode is delayed to use a stable input signal for the measurement.

- 5. The threshold to distinguish between high-bit and low-bit frequency is calculated to be by a value of 5 or 7 (see hysteresis in threshold) higher than the counter state of the measured low-bit frequency.

### 6.12 SCI Encoder

An SCI encoder performs the data transmission to the microcontroller. As the transmission rate of the transponder is lower than the SCI transmission rate, the serial bit flow received from the transponder is buffered after demodulation and before SCI encoding.

The SCI encoder uses an 8-bit shift register to send the received data byte-wise (least significant bit first) to the microcontroller with a transmission rate of 15.625 kbaud (±1.5 %), 1 start bit (high), 1 stop bit (low), and no parity bit (asynchronous mode indicated by the SYNC bit of the Mode Control register is permanently low). The data bits at the SCIO output are inverted with respect to the corresponding bits sent by the transponder.

The transmission starts after the reception of the start bit. The start byte detection is initialized with the first rising edge. Typical values for the start byte are 81\_H or 01\_H (at SCIO). The start byte is the first byte to be sent to the microcontroller. The transmission stops and the base station returns to the Idle state when TXCT becomes low or 20 ms after the beginning of the read phase. TXCT remains low for at least 128 µs to stop the read phase and less than 900 µs to avoid starting the next transmission cycle.

The SCI encoder also sends the diagnostic byte 2 ms after beginning of the charge phase. In case of a normal operation of the antenna, the diagnostic byte AF\_H is sent. If no antenna oscillation can be measured or if at least one of the full-bridge drivers is switched off due to a detected short circuit, the diagnostic byte FF H is sent to indicate the failure mode.

The SCI encoder can be switched into a synchronous data transmission mode by setting the mode control register bit SYNC to high. In this mode, the output SCIO indicates by a high state that a new byte is ready to be transmitted. The microcontroller can receive the 8 bits at SCIO when sending the eight clock signals (falling edge means active) for the synchronous data transmission through pin TXCT to the SCI encoder.

### 6.13 Control Logic

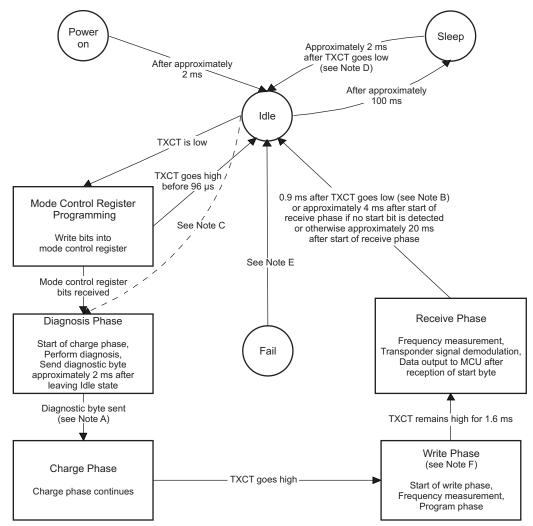

The control logic is the core of the TMS3705 circuit. This circuit contains a sequencer or a state machine that controls the global operations of the base station (see Figure 6-1). This block has a default mode configuration but can also be controlled by the microcontroller through the TXCT serial input pin to change the configuration and to control the programmable frequency divider. For that purpose a mode control register is implemented in this module that can be written by the microcontroller.

- A. In SCI synchronous mode, this transition always occurs approximately 3 ms after leaving Idle state. Diagnostic byte transmission is complete before the transition.

- B. A falling edge on TXCT interrupts the receive phase after a delay of 0.9 ms. TXCT must remain low for at least 128 μs. If TXCT is still low after the 0.9-ms delay, the base station enters the Idle state and then the Diagnosis phase one clock cycle later (see the dotted line marked with "See Note C"). No mode control register can be written, and only the default mode is fully supported in this case. Otherwise, if TXCT returns high and remains high during the delay, the base station stays in Idle state and waits for TXCT to go low (which properly starts a new mode control register programming operation) or waits for 100 ms to enter the Sleep state.

- C. This transition occurs only in a special case, as described in Note B.

- D. A falling edge on TXCT interrupts the Sleep state. Only the default mode is fully supported when starting an operation from the Sleep state with only one falling edge on TXCT, because of the 2-ms delay. For proper mode control register programming, TXCT must return to high and remain high during this delay.

- E. Idle state is the next state in case of undefined states (fail-safe state machine).

- F. Frequency measurement is available for the TMS3705EDRQ1 only.

### Figure 6-1. Operational State Diagram for the Control Logic

The default mode is a read-only mode that uses the default frequency as the carrier frequency for the full bridge. Therefore the mode control register does not need to be written (it is filled with low states), and the communication sequence between microcontroller and base station starts with TXCT being low for a fixed time to initiate the charge phase. When TXCT becomes high again, the module enters the read phase and the data transmission through the SCIO pin to the microcontroller starts.

There is another read-only mode that differs from the default mode only in the writing of the mode control register before the start of the charge phase. The method to fill the mode control register and the meaning of its contents is described in the following paragraphs.

The write-read mode starts with the programming of the mode control register. Then the charge phase starts with TXCT being low for a fixed time. When TXCT becomes high again, the write phase begins in which the data are transmitted from the microcontroller to the transponder through the TXCT pin, the control logic, the predrivers, and the full bridge by amplitude modulation of 100% with a fixed delay time. After the write phase TXCT goes low again to start another charge or program phase. When TXCT becomes high again, the read phase begins.

The contents of the mode control register (see Table 6-1) define the mode and the way that the carrier frequency generated by the frequency divider is selected to meet the transponder resonance frequency as closely as possible.

BIT RESET **DESCRIPTION** VALUE NAME NO. START\_BIT Bit 0 0 START BIT = 0 The start bit is always low and does not need to be stored.  $DATA_BIT[4:1] = 0000$ Microcontroller selects division factor 119 DATA BIT1 Bit 1 0  $DATA_BIT[4:1] = 1111$ Division factor is adapted automatically (1)  $DATA_BIT[4:1] = 0001$ Microcontroller selects division factor 114 DATA BIT2 Bit 2 0  $DATA_BIT[4:1] = 0010$ Microcontroller selects division factor 115 DATA BIT3 0 Bit 3  $DATA_BIT[4:1] = 0110$ Microcontroller selects division factor 119 DATA BIT4 Bit 4 0  $DATA_BIT[4:1] = 1011$ Microcontroller selects division factor 124  $SCI_SYNC = 0$ Asynchronous data transmission to the microcontroller SCI\_SYNC Bit 5 0 SCI\_SYNC = 1 Synchronous data transmission to the microcontroller  $RX_AFC = 0$ Demodulator threshold is adapted automatically RX AFC Bit 6 0  $RX_AFC = 1$ Demodulator threshold is defined by DATA\_BIT[4:1]  $TEST_BIT = 0$ No further test bytes

Table 6-1. Mode Control Register (7-Bit Register)

Bit 7

0

$TEST_BIT = 1$

The TMS3705EDRQ1 can adjust the carrier frequency to the transponder resonance frequency automatically by giving the counter state of the transponder resonance-frequency measurement directly to the frequency divider by setting the first 4 bits in high state. The other combinations of the first 4 bits allow the microcontroller to select the default carrier frequency or to use another frequency. The division factor can be selected to be between 114 and 124.

Further test byte follows for special test modes

Some bits are included for testability reasons. The default value of these test bits for normal operation is low. Bit 7 (TEST\_BIT) is low for normal operation; otherwise, the base station may enter one of the test modes.

The control logic also controls the demodulator, the SCI encoder, the diagnosis, and the transmission of the diagnosis byte during the charge phase.

The state diagram in Figure 6-1 shows the general behavior of the state machine (the state blocks drawn can contain more than one state). All given times are measured from the moment when the state is entered if not specified otherwise.

#### 6.14 Test Pins

TEST BIT

The IC has an analog test pin A\_TST for the analog part of the receiver. The digital output pin D\_TST is used for testing the internal logic. Connecting both pins is not required.

<sup>(1)</sup> Setting is not allowed for TMS3705DDRQ1.

### 7 Applications, Implementation, and Layout

#### **NOTE**

Information in the following Applications section is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 7.1 Application Diagram

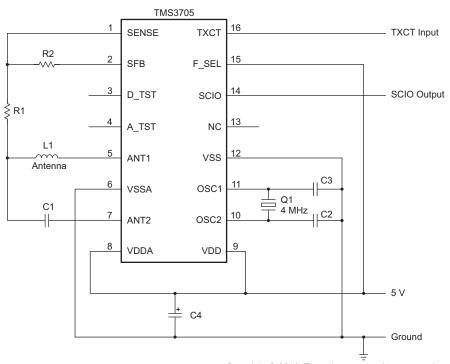

Figure 7-1 shows a typical application diagram.

Copyright © 2016, Texas Instruments Incorporated

Figure 7-1. Application Diagram

Table 7-1 lists the bill of materials for the application in Figure 7-1.

Table 7-1. Bill of Materials (BOM)

| COMPONENT | VALUE                | COMMENTS                                                                                        |

|-----------|----------------------|-------------------------------------------------------------------------------------------------|

| R1        | 47 kΩ                |                                                                                                 |

| R2        | 150 kΩ               |                                                                                                 |

| L1        | 422 μH at<br>134 kHz | Sumida part number: Vogt 581 05 042 40                                                          |

| C1        | 3 nF                 | NPO , COG (high Q types). Voltage rating must be 100 V or higher depending on Q factor.         |

| C2        | 220 pF               | NPO                                                                                             |

| C3        | 220 pF               | NPO                                                                                             |

| C4        | 22 μF                | Low ESR                                                                                         |

| Q1        | 4-MHz resonator      | muRata part number: CSTCR4M00G55B-R0. See resonator data sheet (load capacitance is important). |

### 8 Device and Documentation Support

#### 8.1 Getting Started and Next Steps

RFID products from TI provide the ultimate solution for a wide range of applications. With its patented HDX technology, TI RFID offers unmatched performance in read range, read rate and robustness. For more information, see Overview for NFC / RFID.

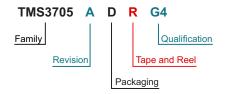

### 8.2 Device Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of devices. Each device has one of three prefixes: X, P, or null (no prefix) (for example, *TMS3705*).

Device development evolutionary flow:

- **X** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- P Prototype device that is not necessarily the final silicon die and may not necessarily meet final electrical specifications.

**null** Production version of the silicon die that is fully qualified.

X and P devices are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices have been characterized fully, and the quality and reliability of the device have been demonstrated fully. Tl's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. TI recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

TI device nomenclature also includes a suffix with the device family name. This suffix indicates the package type (for example, *D*). Figure 8-1 provides a legend for reading the complete device name.

For orderable part numbers of *TMS3705* devices in the *D* package types, see the *Package Option Addendum* in Section 9, the TI website, or contact your TI sales representative.

| Family        | TMS3705 = Transponder base station IC                  |

|---------------|--------------------------------------------------------|

| Revision      | A1, B, C, D = Silicon revision                         |

| Packaging     | http://www.ti.com/packaging                            |

| Tape and Reel | R = Large reel                                         |

| Qualification | G4 = Green (RoHS and no Sb, Br)<br>Q1 = Q100 Qualified |

Figure 8-1. Device Nomenclature

#### 8.3 **Tools and Software**

#### **Design Kits and Evaluation Modules**

- Low-Frequency Demo Reader The ADR2 Evaluation Kit contains a low-frequency reader required to evaluate and operate the TI Car Access products. The kit comes with a reader base board, LF antenna, and a USB-RS232 adapter. Together with the PC software available online, all functions of the reader can be controlled and all automotive transponders, remote keyless entry, and passive entry devices can be addressed. Operation of transponder functions and also passive entry communication is supported by the same system without component changes.

- PaLFI, Passive Low-Frequency Evaluation Kit TMS37157 The PaLFI Evaluation kit contains all components required to evaluate and operate the TMS37157. The kit comes with an eZ430 MSP430F1612 USB development stick, and an MSP430 target board including an MSP430F2274 plus the TMS37157 PaLFI. A battery board for active operation in addition to an RFID base station reader/writer provide the infrastructure for various evaluation setups.

#### 8.4 **Documentation Support**

The following documentation describes the transponder, related peripherals, and other technical collateral.

#### **Receiving Notification of Document Updates**

To receive notification of documentation updates—including silicon errata—go to the TMS3705 product folder. In the upper right corner, click the "Alert me" button. This registers you to receive a weekly digest of product information that has changed (if any). For change details, check the revision history of any revised document.

#### **Application Reports**

- Resonant Trimming Sequence This application report presents an efficient and precise method on how to achieve the desired resonant frequency of configuring the trim array with only a few iterations and measuring the resonant frequency.

- TMS3705 Range Extender Power Solution Using UCC27424-Q1 This application report provides supplementary information about the TI 134.2-kHz RFID Base Station IC TMS3705x in combination with an external driver IC. In particular, the document shows a low cost and easy-to-implement solution to improve the communication distance between the transaction processor (TRP) and the Reader unit.

- TMS3705 Passive Antenna Solution The TI low-frequency transponder technology provides the possibility to use a simple passive antenna in combination with various antenna cable lengths. This solution significantly reduces system costs because the active part of the transceiver can be added to the already existing host system; for example, the body control module (BCM) of a vehicle.

- Integrated TIRIS RF Module TMS3705A Introduction to Low Frequency Reader A TIRIS setup consists of one or more Transponders and a Reader. The Reader described in this application note normally contains the Reader Antenna, the RF Module and the Control Module.

#### **More Literature**

- Wireless Connectivity Tri-fold Overview At TI, we are committed to delivering a broad portfolio of wireless connectivity solutions which consume the lowest power and are the easiest to use. With TI innovation supporting your designs, you can share, monitor and manage data wirelessly for applications in wearables, home and building automation, manufacturing, smart cities, healthcare and automotive.

- MSP430™ Ultra-Low-Power MCUs and TI-RFid Devices The TI portfolio of MSP430 microcontrollers and TI-RFid devices is an ideal fit for low-power, robust RFID reader and transponder solutions. Together, MSP430 and TI-RFid devices help RF designers achieve low power consumption, best-in-class read range and reliable performance at a competitive price.

### 8.5 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community The TI engineer-to-engineer (E2E) community was created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

TI Embedded Processors Wiki Established to help developers get started with Embedded Processors from Texas Instruments and to foster innovation and growth of general knowledge about the hardware and software surrounding these devices.

#### 8.6 Trademarks

TI-RFid, MSP430, E2E are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

### 8.7 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 8.8 Export Control Notice

Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from disclosing party under nondisclosure obligations (if any), or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorization from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws.

### 8.9 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

Submit Documentation Feedback

Product Folder Links: TMS3705

## 9 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGE OPTION ADDENDUM

21-Nov-2018

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | _       | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| TMS3705BDRG4     | ACTIVE | SOIC         | D       | 16   |         | TBD                        | Call TI          | Call TI             | -40 to 85    | TMS3705B       | Samples |

| TMS3705DDRQ1     | ACTIVE | SOIC         | D       | 16   | 2500    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | TMS3705DQ1     | Samples |

| TMS3705EDRQ1     | ACTIVE | SOIC         | D       | 16   | 2500    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | TMS3705EQ1     | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## **PACKAGE OPTION ADDENDUM**

21-Nov-2018

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

PACKAGE MATERIALS INFORMATION

www.ti.com 22-Nov-2018

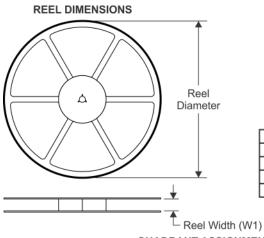

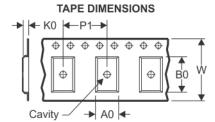

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

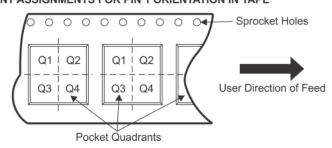

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TMS3705EDRQ1 | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

www.ti.com 22-Nov-2018

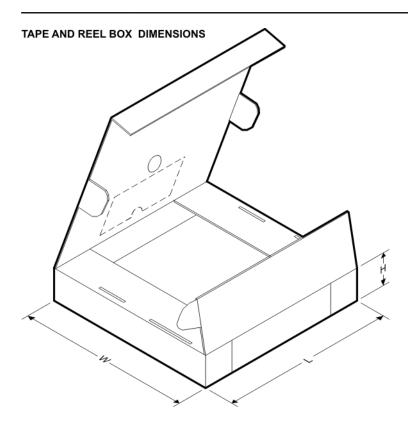

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TMS3705EDRQ1 | SOIC         | D               | 16   | 2500 | 367.0       | 367.0      | 38.0        |

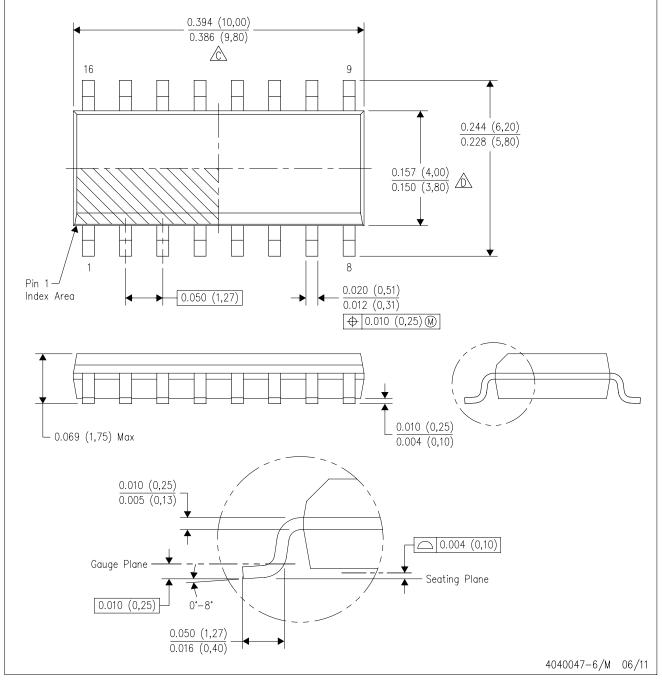

## D (R-PDS0-G16)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AC.

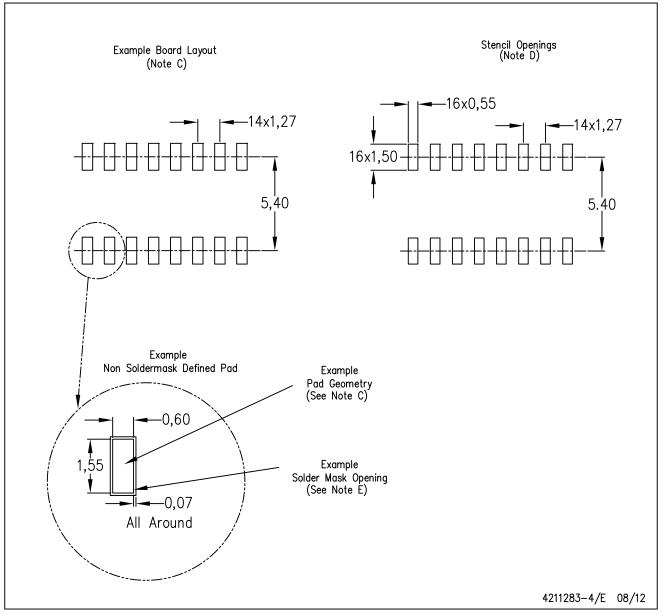

# D (R-PDSO-G16)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

Tl's products are provided subject to Tl's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such Tl products. Tl's provision of these resources does not expand or otherwise alter Tl's applicable warranties or warranty disclaimers for Tl products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated