Document Number: MC33814

Rev. 5.0, 6/2013

# Two Cylinder Small Engine Control IC

The 33814 is an engine control analog power IC intended for two cylinder motorcycle and other small engine control applications. The IC consists of six integrated low side drivers, three pre-drivers, a Variable Reluctance Sensor (VRS) input circuit, a voltage pre-regulator using an external pass transistor, and two 5 volt internal regulators, one for the microcontroller unit (MCU) VCC supply, and one for use as a protected sensor supply. Also included is an MCU reset control circuit with watchdog, an ISO 9141 K-Line interface for diagnostic communication and a Serial Peripheral Interface (SPI). The six low side drivers are intended for driving two fuel injectors, a lamp, two relays or other loads, and a tachometer. The predrivers are intended to drive IGBT or MOSFET transistors to control ignition coils, and a HEGO heater. The device is packaged in a 48 pin LQFP-EP with an exposed pad. This device is powered by SMARTMOS technology.

#### Features:

- Operates over supply voltage range of 4.5 V ≤ V<sub>PWR</sub> ≤ 36 V

- · Logic stability guaranteed down to 2.5 V

- · Two fuel injector drivers typical of 1.3 A each

- · Two ignition IGBT or general purpose gate pre-drivers

- · One O2 sensor (HEGO) heater general purpose gate pre-driver

- Relay 1 driver, typically 2.0 A, can be used for fuel pump control

- Relay 2 driver, typically 1.0 A, can be used as power relay control

- · Lamp driver, typically 1.0 A can also be used to drive an LED

- V<sub>PROT</sub> protected sensor supply tracks V<sub>CC</sub> +5.0 V regulator

- MCU reset generator system integrity monitor (watchdog)

- V<sub>PP</sub> pre-regulator provides power for V<sub>CC</sub> and V<sub>PROT</sub> regulators

- Independent fault protection with all faults reported via the SPI

ISO 9141 K-line interface for communicating diagnostic messages

- Start-up/shut-down control and power sequence logic

- · Interfaces directly to MCU using a 5.0 V SPI and logic I/O

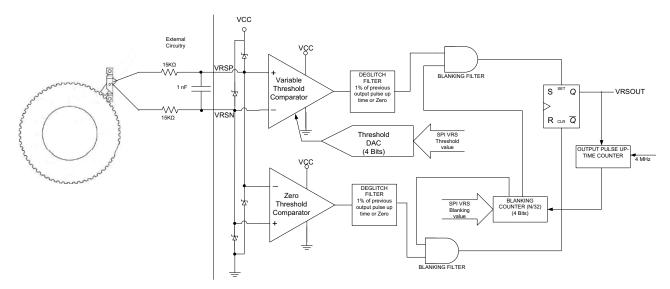

- Differential/single-ended VRS conditioning circuit with auto/manual selected thresholds and filter times with digital and tachometer outputs

#### 33814

# TWO CYLINDER SMALL ENGINE CONTROL IC

#### Applications:

Small Engine Control for:

- · Lawn Mowers

- · Motor Scooters

- Small Motorcycles

- · Lawn Trimmers

- Snow Blowers

- Chain SawsGasoline-driven Electrical Generators

- · Outboard Motors

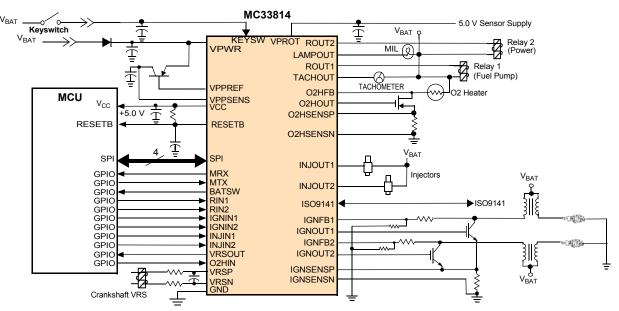

Figure 1. 33814 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product.

Specifications and information herein are subject to change without notice.

# 1 Orderable Parts

#### **Table 1. Orderable Part Variations**

| Part Number <sup>(1)</sup> | Notes | Temperature (T <sub>A</sub> ) | Package    |

|----------------------------|-------|-------------------------------|------------|

| MC33814AE                  |       | -40 to 125 °C                 | 48 LQFP-EP |

#### Notes

1. To Order parts in Tape & Reel, add the R2 suffix to the part number.

# **Table of Contents**

| 1 | Orderable Parts                                               | 2  |

|---|---------------------------------------------------------------|----|

| 2 | Internal Block Diagram                                        | 2  |

| 3 | Pin Connections                                               | Ę  |

|   | 3.1 Pinout Diagram                                            | Ę  |

|   | 3.2 Pin Definitions                                           | Ę  |

| 4 | General Product Characteristics                               | 8  |

|   | 4.1 Maximum Ratings                                           | 8  |

|   | 4.2 Static Electrical Characteristics                         | 10 |

|   | 4.3 Dynamic Electrical Characteristics                        | 15 |

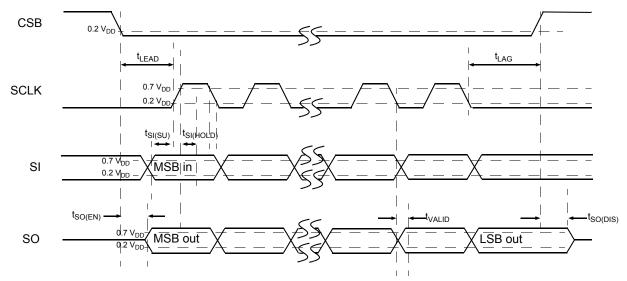

|   | 4.4 Timing Diagrams                                           | 17 |

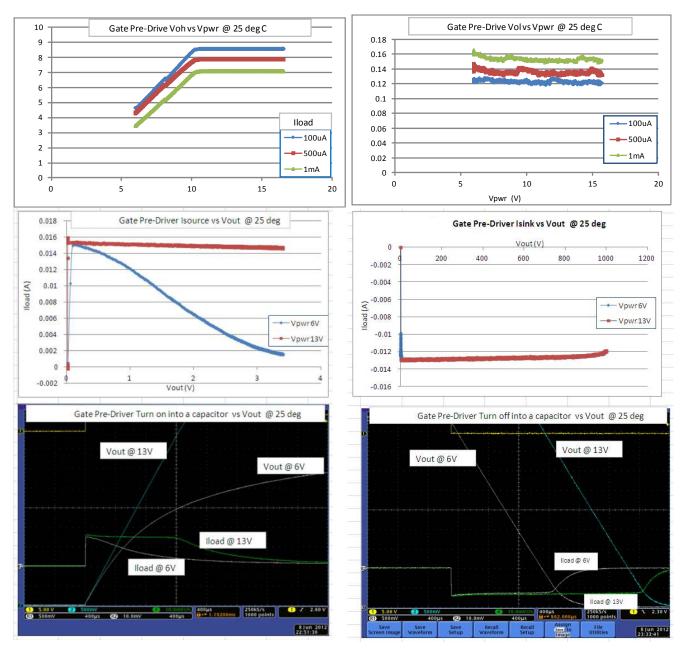

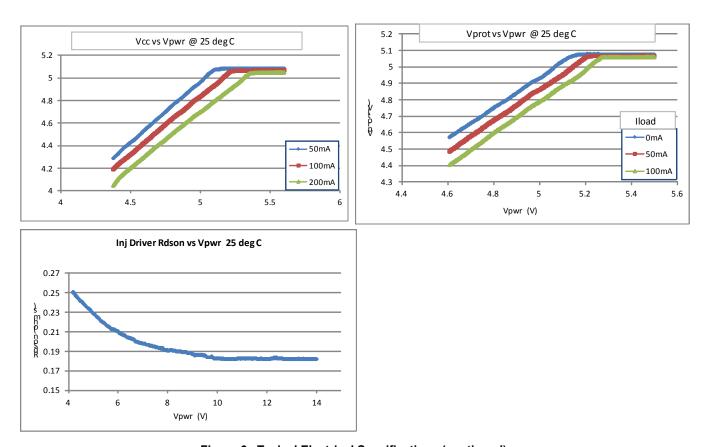

|   | 4.5 Typical Electrical Characteristics                        | 18 |

| 5 | General IC Functional Description and Application Information | 20 |

|   | 5.1 Functional Pin Description                                | 20 |

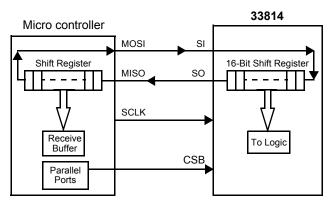

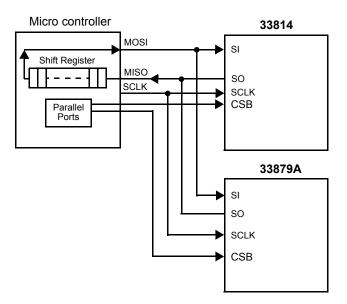

|   | 5.2 MCU SPI Interface Description                             | 31 |

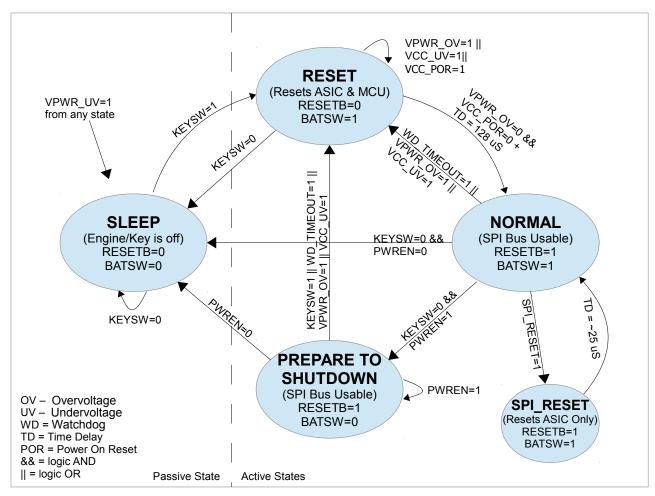

|   | 5.3 Functional Device Operation                               | 32 |

| 6 | Typical Applications                                          | 44 |

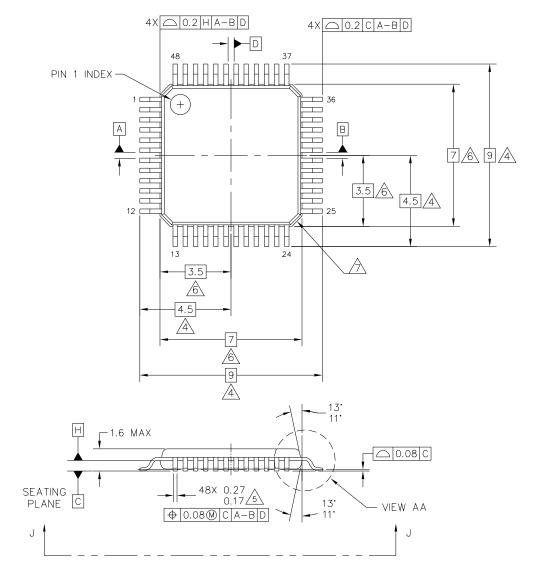

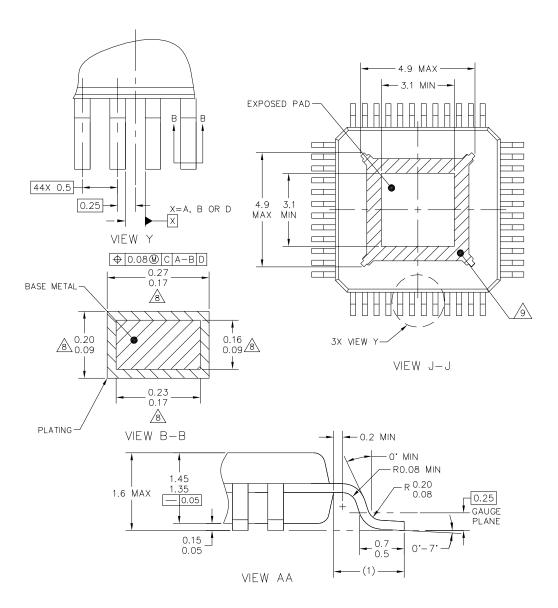

| 7 | Packaging                                                     | 45 |

|   | 7.1 Package Mechanical Dimensions                             | 45 |

| 8 | Revision History                                              | 49 |

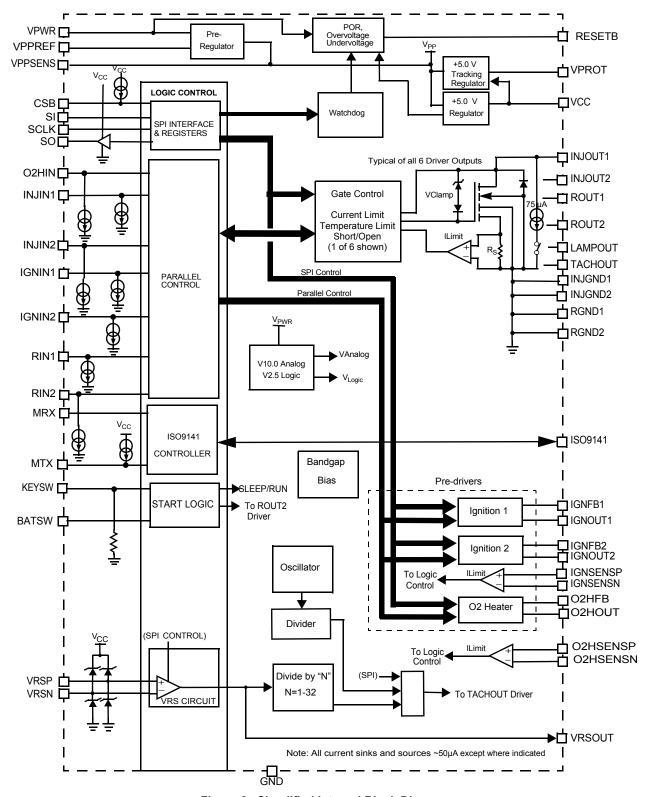

# 2 Internal Block Diagram

Figure 2. Simplified Internal Block Diagram

# 3 Pin Connections

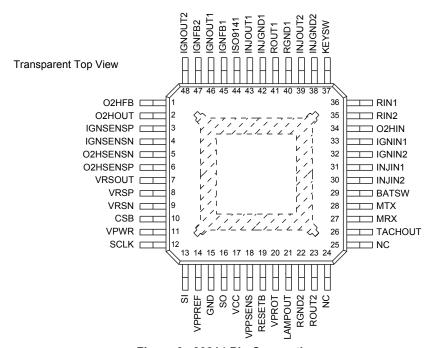

## 3.1 Pinout Diagram

Figure 3. 33814 Pin Connections

## 3.2 Pin Definitions

Table 2. 33814 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 20.

| Pin | Pin Name | Pin<br>Function | Formal Name                               | Description                                                                                                                                            |

|-----|----------|-----------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | O2HFB    | Input           | O2 Sensor Heater<br>Feedback Input        | Voltage feedback from drain of O2 Sensor Heater driver FET                                                                                             |

| 2   | O2HOUT   | Output          | O2 Sensor Heater<br>Output                | Pre-driver output for O2 Sensor Heater driven by SPI input or O2HIN pin                                                                                |

| 3   | IGNSENSP | Input           | Ignition Current<br>Sense Input Positive  | Positive input to the ignition current sense differential amplifier Used to measure current in IGBT emitter resistor for IGNOUT1 and IGNOUT2, if used. |

| 4   | IGNSENSN | Input           | Ignition Current<br>Sense Input Negative  | Negative input to the ignition current sense differential amplifier Used to measure current in IGBT emitter resistor for IGNOUT1 and IGNOUT2, if used  |

| 5   | O2HSENSN | Input           | O2 Heater Current<br>Sense Input Negative | Negative input to the O2 heater current sense differential amplifier Used to measure current in of O2 heater driver MOSFET source resistor, if used.   |

#### Table 2. 33814 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 20.

| Pin | Pin Name | Pin<br>Function | Formal Name                                     | Description                                                                                                                                                                                                                    |

|-----|----------|-----------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | O2HSENSP | Input           | O2 Heater Current<br>Sense Input Positive       | Positive input to the O2 heater current sense differential amplifier Used to measure current in of O2 heater driver MOSFET source resistor, if used.                                                                           |

| 7   | VRSOUT   | Output          | VRS Conditioned<br>Output                       | 5.0 V Logic Level Output from conditioned VRS differential inputs VRSP, VRSN                                                                                                                                                   |

| 8   | VRSP     | Input           | Variable Reluctance<br>Sensor Positive Input    | The VRSP and VRSN form a differential input for the Variable Reluctance Sensor attached to the crankshaft toothed wheel.                                                                                                       |

| 9   | VRSN     | Input           | Variable Reluctance<br>Sensor Negative<br>Input | The VRSP and VRSN form a differential input for the Variable Reluctance Sensor attached to the crankshaft toothed wheel.                                                                                                       |

| 10  | CSB      | Input           | SPI Chip Select                                 | The Chip Select input pin is an active low signal sent by the MCU to indicate that the device is being addressed.                                                                                                              |

| 11  | VPWR     | Supply Input    | Main Voltage Supply<br>Input                    | VPWR is the main voltage supply input for the device. Connected to a 12 Volt battery (Should have reverse battery protection and adequate transient protection.)                                                               |

| 12  | SCLK     | Input           | SPI Clock Input                                 | The SCLK input pin is used to clock in and out the serial data on the SI and SO pins while being addressed by the CSB.                                                                                                         |

| 13  | SI       | Input           | SPI Data Input                                  | The SI input pin is used to receive serial data into the device from the MCU.                                                                                                                                                  |

| 14  | VPPREF   | Output          | VPP Reference Base<br>Drive                     | Base drive for external PNP pass transistor                                                                                                                                                                                    |

| 15  | GND      | Ground          | Ground                                          | Ground pin, return for all voltage supplies                                                                                                                                                                                    |

| 16  | SO       | Output          | SPI Data Output                                 | The SO output pin is used to transmit serial data from the device to the MCU.                                                                                                                                                  |

| 17  | VCC      | Supply          | VCC Supply<br>Protected Output                  | 5.0 Volt supply output for MCU $V_{CC}$ . This output supplies the $V_{CC}$ voltage for 5.0 Volt MCUs. It is short-circuit and overcurrent protected.                                                                          |

| 18  | VPPSENS  | Input           | Voltage Sense from<br>VPP                       | Feedback to internal $V_{PP}$ 6.5 Volt regulator from external pass transistor                                                                                                                                                 |

| 19  | RESETB   | Output          | RESETB Output to MCU                            | 5.0 V Logic level reset signal used to reset the MCU during under and overvoltage conditions and for initial power-up, down and watchdog timeouts                                                                              |

| 20  | VPROT    | Output          | Sensor Supply<br>Protected Output               | The VPROT Output is a protected 5.0 Volt output that tracks the $V_{CC}$ voltage but isolates the VCC output against shorts to ground and to battery. It is intended to supply sensors which are located off of the ECU board. |

| 21  | LAMPOUT  | Output          | Warning Lamp Output                             | Low side driver output for MIL (warning lamp) driven by SPI input command                                                                                                                                                      |

| 22  | RGND2    | Ground          | ROUT2 Power<br>Ground                           | Ground connection for ROUT 2 low side driver. Must be tied to VPWR Ground.                                                                                                                                                     |

| 23  | ROUT2    | Output          | Relay Driver 2 Output                           | Low side relay driver output # 2 driven by SPI input command or RIN2 logic input                                                                                                                                               |

| 24  | N.C.     | No Connect      | Unused pin                                      | For future expansion                                                                                                                                                                                                           |

| 25  | N.C.     | No Connect      | Unused pin                                      | For future expansion                                                                                                                                                                                                           |

| 26  | TACHOUT  | Output          | Tachometer output                               | This pin provides the low side drive for a tachometer gauge or alternatively as a SPI controlled low side driver, or oscillator output.                                                                                        |

| 27  | MRX      | Output          | Low Side Driver<br>Output                       | Output 5.0 V logic level ISO9141 data to the MCU from the ISO9141 IN/OUT pin                                                                                                                                                   |

| 28  | MTX      | Input           | ISO9141 MCU Data<br>Input                       | Input 5.0 V logic level ISO9141 data from the MCU to the ISO9141 IN/OUT pin                                                                                                                                                    |

Table 2. 33814 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 20.

| Pin | Pin Name | Pin<br>Function | Formal Name                                           | Description                                                                                                                                                                                                                                                                                                                                             |

|-----|----------|-----------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

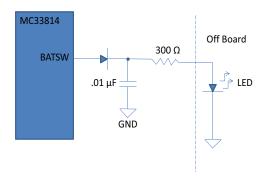

| 29  | BATSW    | Output          | Battery Switch                                        | This output is a 5.0 V logic level that is high when KEYSW is high. It is only low when KEYSW is low. It can also be controlled via the SPI. The BATSW output may not be present in a different package but it's function can be read by the SPI.                                                                                                       |

| 30  | INJIN2   | Input           | Injector Driver Input 2                               | 5.0 V logic level input from the MCU to control the injector 2 driver output. (Can also be controlled via the SPI)                                                                                                                                                                                                                                      |

| 31  | INJIN1   | Input           | Injector Driver Input 1                               | 5.0 V logic level input from the MCU to control the injector 1 driver output. (Can also be controlled via the SPI)                                                                                                                                                                                                                                      |

| 32  | IGNIN2   | Input           | Ignition Input 2                                      | 5.0 V logic level input from MCU controlling the ignition coil # 2 current flow and spark. (Can also be controlled via the SPI)                                                                                                                                                                                                                         |

| 33  | IGNIN1   | Input           | Ignition Input 1                                      | 5.0 V logic level input from MCU controlling the ignition coil # 1 current flow and spark. (Can also be controlled via the SPI)                                                                                                                                                                                                                         |

| 34  | O2HIN    | Input           | O2 Sensor Heater<br>Input                             | 5.0 V logic level input used to turn on and off the O2HOUT driver. The O2HOUT driver can also be turned on and off via the SPI if this pin is not present in a different package.                                                                                                                                                                       |

| 35  | RIN2     | Input           | Relay Driver Input 2                                  | 5.0 V logic level input from the MCU to control the relay 2 driver output ROUT2. The ROUT2 driver can also be turned on and off via the SPI if this pin is not present in a different package.                                                                                                                                                          |

| 36  | RIN1     | Input           | Relay Driver Input 1                                  | 5.0 V logic level input from the MCU to control the relay 1 driver output ROUT1. The ROUT1 driver can also be turned on and off via the SPI if this pin is not present in a different package.                                                                                                                                                          |

| 37  | KEYSW    | Input           | Key Switch Input                                      | The Key Switch Input is a $V_{PWR}$ level signal that indicates that the Key is inserted and turned to the ON/OFF position. In the ON position the (KEYSW = $V_{BAT}$ ) the IC is enabled and BATSW = HIGH (Relay 2 ON if programmed in the SPI). In the OFF position the IC is in Sleep mode, only when the PWREN bit in the SPI register is also low. |

| 38  | INJGND2  | Ground          | Injector Driver 2<br>Ground                           | Ground connection for injector 2 low side driver. Must be tied to VPWR ground.                                                                                                                                                                                                                                                                          |

| 39  | INJOUT2  | Output          | Injector Driver 2<br>Output                           | Low side driver output for injector 2 driven by the SPI input or by parallel input INJIN2                                                                                                                                                                                                                                                               |

| 40  | RGND1    | Ground          | ROUT1 Power<br>Ground                                 | Ground connection for ROUT 1 low side driver. Must be tied to VPWR ground.                                                                                                                                                                                                                                                                              |

| 41  | ROUT1    | Output          | Relay Driver 1 Output                                 | Low side relay driver output # 1 driven by the SPI input command or RIN1 logic input                                                                                                                                                                                                                                                                    |

| 42  | INJGND1  | Ground          | Injector Driver 1<br>Ground                           | Ground connection for injector 1 low side driver. Must be tied to VPWR ground.                                                                                                                                                                                                                                                                          |

| 43  | INJOUT1  | Output          | Injector Driver 1<br>Output                           | Low side driver output for injector 1 driven by the SPI input or by parallel input INJIN1                                                                                                                                                                                                                                                               |

| 44  | ISO9141  | Input/Output    | ISO9141 K-Line<br>Bidirectional Serial<br>Data Signal | ISO9141 pin is $V_{PWR}$ level IN/OUT signal which is connected to an external ECU tester that uses the ISO9141 protocol. The output is open drain and the Input is a ratiometric $V_{PWR}$ level threshold comparator.                                                                                                                                 |

| 45  | IGNFB1   | Input           | Feedback from<br>Collector 1                          | Voltage feedback from collector of ignition # 1 driver IGBT through 10:1 voltage divider (9R:1R)                                                                                                                                                                                                                                                        |

| 46  | IGNOUT1  | Output          | Ignition Output 1                                     | Output to gate of IGBT or GPGD for ignition # 1                                                                                                                                                                                                                                                                                                         |

| 47  | IGNFB2   | Input           | Feedback from<br>Collector 2                          | Voltage feedback from collector of ignition # 2 driver IGBT through 10:1 voltage divider (9R:1R)                                                                                                                                                                                                                                                        |

| 48  | IGNOUT2  | Output          | Ignition Output 2                                     | Output to gate of IGBT or GPGD for ignition # 2                                                                                                                                                                                                                                                                                                         |

# 4 General Product Characteristics

# 4.1 Maximum Ratings

Table 3. MAXIMUM RATINGS

All voltages are with respect to ground, unless mentioned otherwise. Exceeding these ratings may cause malfunction or permanent device damage.

| Parameter                                                                                                                                                                                   | Symbol                                                 | Min.         | Max.               | Unit            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------|--------------------|-----------------|

| ELECTRICAL RATINGS                                                                                                                                                                          |                                                        |              |                    |                 |

| V <sub>PWR</sub> Supply Voltage                                                                                                                                                             | $V_{PWR}$                                              | -0.3         | 45                 | V <sub>DC</sub> |

| V <sub>PP</sub> Supply Voltage (If supplied externally and not using internal VPP regulator)  • VPP <sub>REF</sub> • VPP <sub>SENSE</sub>                                                   | V <sub>PP_Ext</sub>                                    | -0.3<br>-0.3 | 45<br>10           | V <sub>DC</sub> |

| V <sub>PROT</sub> Regulator                                                                                                                                                                 | V <sub>PROT</sub>                                      | -0.3         | $V_{PWR}$          | $V_{DC}$        |

| SPI Interface and Logic Input Voltage ( $V_{SI}$ , $V_{SCLK}$ , $V_{CSB}$ , $V_{RIN1}$ , $V_{RIN2}$ , $V_{INJIN1}$ , $V_{INJIN2}$ , $V_{IGNIN1}$ , $V_{IGNIN2}$ , $V_{O2HIN}$ , $V_{MTX}$ ) | $V_{IL}, V_{IH}$                                       | -0.3         | V <sub>CC</sub>    | V <sub>DC</sub> |

| SPI Interface and Logic Output Voltage ( $V_{SO}$ , $V_{BATSW}$ , $V_{MRX}$ , $V_{VRSOUT}$ )                                                                                                | V <sub>IL</sub> , V <sub>IH</sub>                      | -0.3         | V <sub>CC</sub>    | $V_{DC}$        |

| All Low Side Drivers Drain Voltage ( $V_{INJOUT1}$ , $V_{INJOUT2}$ , $V_{ROUT1}$ , $V_{ROUT2}$ , $V_{LAMPOUT}$ , $V_{TACHOUT}$ )                                                            | V <sub>OUTX</sub>                                      | -0.3         | V <sub>CLAMP</sub> | V <sub>DC</sub> |

| All Pre-drivers Output Voltage (V <sub>IGNOUT1</sub> , V <sub>IGNOUT2</sub> , V <sub>O2HOUT</sub> )                                                                                         | $V_{GDX}$                                              | -0.3         | 10                 | $V_{DC}$        |

| All Pre-driver Feedback Inputs Voltage (V <sub>IGNFB1</sub> , V <sub>IGNFB2</sub> , V <sub>O2HFB</sub> )                                                                                    | $V_{GDFB}$                                             | -1.5         | 60                 | $V_{DC}$        |

| All Pre-driver Current Sense Inputs Voltage (VIGNSENSN, VIGNSENSP, VO2HSENSN, VO2HSENSP)                                                                                                    | V <sub>ISENS</sub>                                     | -0.3         | 1.0                | V <sub>DC</sub> |

| KEYSW Input Voltage (V <sub>KEYSW</sub> )                                                                                                                                                   | V <sub>KEYSW</sub>                                     | -18          | $V_{PWR}$          | $V_{DC}$        |

| RESETB Output Voltage (V <sub>RESETB</sub> )                                                                                                                                                | V <sub>RESETB</sub>                                    | -0.3         | V <sub>CC</sub>    | V <sub>DC</sub> |

| ISO9141 Input/Output Voltage (V <sub>ISO9141</sub> )                                                                                                                                        | V <sub>ISO9141</sub>                                   | -18          | $V_{PWR}$          | $V_{DC}$        |

| Output Continuous Current (INJOUT1, INJOUT2)  • T <sub>JUNCTION</sub> = 150 °C                                                                                                              | l <sup>OC</sup> INJX                                   | _            | 1.3                | А               |

| Output Continuous Current (ROUT1)  • T <sub>JUNCTION</sub> = 150 °C                                                                                                                         | I <sub>OC_R1</sub>                                     | _            | 2.0                | А               |

| Output Continuous Current (ROUT2)  • T <sub>JUNCTION</sub> = 150 °C                                                                                                                         | I <sub>OC_R2</sub>                                     | -            | 1.0                | А               |

| Output Continuous Current (LAMPOUT)  • T <sub>JUNCTION</sub> = 150 °C                                                                                                                       | I <sub>OC_LAMP</sub>                                   | -            | 1.0                | А               |

| Output Continuous Current (TACHOUT)  • T <sub>JUNCTION</sub> = 150 °C                                                                                                                       | I <sub>OC_TACH</sub>                                   | _            | 50                 | mA              |

| Maximum Voltage for VRSN and VRSP inputs to ground                                                                                                                                          | V <sub>VRS_IN</sub>                                    | -0.5         | 6.0                | $V_{DC}$        |

| Maximum Current for VRSN and VRSP inputs (internal diodes limit voltage)                                                                                                                    | I <sub>VRSX_IN</sub>                                   | _            | 15                 | mA              |

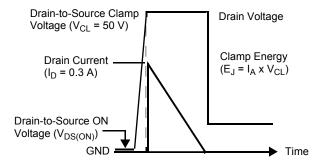

| Output Clamp Energy (INJOUT1, INJOUT2, ROUT1)(Single Pulse)  • T <sub>JUNCTION</sub> = 150 °C, I <sub>OUT</sub> = 1.0 A                                                                     | E <sub>CLAMP_INJ_SP</sub><br>E <sub>CLAMP_REL_SP</sub> | _            | 100                | mJ              |

#### Table 3. MAXIMUM RATINGS

All voltages are with respect to ground, unless mentioned otherwise. Exceeding these ratings may cause malfunction or permanent device damage.

| Parameter                                                                                                                          | Symbol                    | Min. | Max.   | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|--------|------|

| ELECTRICAL RATINGS (CONTINUED)                                                                                                     |                           |      |        |      |

| Output Clamp Energy (INJOUT1, INJOUT2)(Continuous operation)                                                                       | E <sub>CLAMP_INJ_CP</sub> |      |        | mJ   |

| <ul> <li>T<sub>JUNCTION</sub> = 125 °C, I<sub>OUT</sub> = 1.0 A, (Max injector frequency is 70 Hz, Max duty cycle =90%)</li> </ul> | E <sub>CLAMP_REL_CP</sub> | -    | 100    |      |

| Output Clamp Energy (LAMPOUT)(Single pulse)                                                                                        | E <sub>CLAMP_LAMP_</sub>  |      |        | mJ   |

| • T <sub>JUNCTION</sub> = 150 °C, I <sub>OUT</sub> = 0.5 A                                                                         | SP                        | -    | 35     |      |

| ESD Voltage (2)                                                                                                                    |                           |      |        | V    |

| Human Body Model (HBM)                                                                                                             | V <sub>ESD1</sub>         | _    | ±2000  |      |

| VPWR pin (only)                                                                                                                    |                           | -    | ±1500  |      |

| Charge Device Model (CDM) (corner pins)                                                                                            | V <sub>ESD2</sub>         | -    | ±750   |      |

| Charge Device Model (CDM)                                                                                                          | V <sub>ESD3</sub>         | -    | ±500   |      |

| THERMAL RATINGS                                                                                                                    |                           |      | •      |      |

| Operating Temperature (Automotive grade version)                                                                                   |                           |      |        | °C   |

| Ambient                                                                                                                            | T <sub>A</sub>            | -40  | 125    |      |

| Junction                                                                                                                           | $T_J$                     | -40  | 150    |      |

| • Case                                                                                                                             | T <sub>C</sub>            | -40  | 125    |      |

| Storage Temperature                                                                                                                | T <sub>STG</sub>          | -55  | 150    | °C   |

| Power Dissipation (T <sub>A</sub> = 25 °C)                                                                                         | P <sub>D</sub>            | _    | 3.0    | W    |

| Peak Package Reflow Temperature During Reflow (3),(4)                                                                              | T <sub>PPRT</sub>         | -    | Note 4 | °C   |

| THERMAL RESISTANCE AND PACKAGE DISSIPATION RATINGS                                                                                 | <u> </u>                  |      | •      |      |

| Thermal Resistance                                                                                                                 |                           |      |        | °C/W |

| Junction-to-Ambient (LQFP-48-EP Package) (Single Layer Board)                                                                      | $R_{	hetaJA}$             | 29   | 29     |      |

| Junction-to-Case (LQFP-48-EP Package)                                                                                              | $R_{	heta JC}$            | 2.4  | 2.4    |      |

#### Notes

- 2. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), and the Charge Device Model

- 3. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 4. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts (i.e. MC33xxxD enter 33xxx), and review parametrics.

### 4.2 Static Electrical Characteristics

#### **Table 4. Power Input Static Electrical Characteristics**

Characteristics noted under conditions of 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, and Calibrated Timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with V<sub>PWR</sub> = 14 V, T<sub>A</sub> = 25 °C.

| Characteristic                                                                                                                          | Symbol                      | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|------|------|

| POWER INPUT (VPWR)                                                                                                                      |                             |      |      |      | -    |

| Supply Voltage (measured at VPWR pin) <sup>(5)</sup>                                                                                    |                             |      |      |      | V    |

| Logic Stable Range                                                                                                                      | V <sub>PWR(LS)</sub>        | 2.5  | -    | 45   |      |

| Full Operational Range                                                                                                                  | V <sub>PWR(FO)</sub>        | 4.5  | -    | 36   |      |

| Full Parameter Specification Range                                                                                                      | V <sub>PWR(FP)</sub>        | 6.0  | _    | 18   |      |

| Supply Current                                                                                                                          | I <sub>VPWR(ON)</sub>       |      |      |      | mA   |

| <ul> <li>All Outputs Disabled (Normal Mode), excludes base current to the external pnp</li> </ul>                                       | , ,                         | -    | 10.0 | 14.0 |      |

| Sleep State Supply Current (Must have PWREN = 0 & KEYSW $\leq$ 0.8 V for sleep                                                          | I <sub>VPWR(SS)</sub>       |      |      |      | μΑ   |

| state),                                                                                                                                 | , ,                         | -    | 10   | 20   |      |

| • V <sub>PWR</sub> = 18 V                                                                                                               |                             |      |      |      |      |

| V <sub>PWR</sub> Overvoltage Shutdown Threshold Voltage (OV Reset) <sup>(6)</sup>                                                       | V <sub>PWR(OV)</sub>        | 37.5 | 39   | 42   | V    |

| V <sub>PWR</sub> Overvoltage Shutdown Hysteresis Voltage                                                                                | V <sub>PWR</sub>            | 0.5  | 1.5  | 3.0  | V    |

|                                                                                                                                         | (OV-HYS)                    |      |      | 4.0  |      |

| $V_{CC}$ Power On Reset Voltage Threshold (POR Power On Reset), rising $V_{T}$                                                          | V <sub>CC(POR)</sub>        | 3.9  | _    | 4.9  | V    |

| $V_{CC}$ Undervoltage Shutdown Threshold Voltage (UV Reset) <sup>(7)</sup> , falling $V_T$                                              | V <sub>CC(UV)</sub>         | 2.9  | _    | 3.9  | V    |

| V <sub>CC</sub> POR and Undervoltage Shutdown Hysteresis Voltage                                                                        | V <sub>CC(UV/POR-HYS)</sub> | 100  | _    | _    | mV   |

| V <sub>CC</sub> POR and Undervoltage Non-overlap (POR-UV)                                                                               | V <sub>CC</sub> ,           | 0.8  | 1.0  | 1.2  | V    |

|                                                                                                                                         | NONOVERLAP                  |      |      |      |      |

| VOLTAGE PRE-REGULATOR OUTPUT (VPPREF, VPPSENS)                                                                                          |                             |      |      |      |      |

| VPPREF Output Voltage                                                                                                                   | V <sub>PPREF</sub>          | 5.85 | 6.5  | 7.15 | V    |

| VPPREF Output Current (includes external PNP current)                                                                                   | I <sub>VPPREF</sub>         | _    | -5.0 | _    | mA   |

| VPPREF Current Limit                                                                                                                    | I <sub>VPPCL</sub>          | -5   | -15  | -20  | mA   |

| Output Capacitance External (ceramic)                                                                                                   | V <sub>OCE</sub>            | 2.2  | _    | 25   | μF   |

| VPPSENS Input Current                                                                                                                   | I <sub>VPPSENS</sub>        | _    | _    | 3    | mA   |

| Line Regulation $\rm I_{VCC}$ = 100 mA, $\rm I_{VPROT}$ = 50 mA 9.0 V < $\rm V_{PWR}$ < 18 V and Diodes Inc. FZT753TA PNP               | REGLINE_VPP                 | -    | 2.0  | 25   | mV   |

| Dropout Voltage (Minimal Input/Output Voltage, tracks input below) $I_{VCC}$ = 100 mA, $I_{VPROT}$ = 50 mA and Diodes Inc. FZT753TA PNP | V <sub>DROPOUT_PP</sub>     | -    | 1.05 | 1.4  | V    |

#### Notes

- 5. This parameter is guaranteed by design but is not production tested.

- 6. Overvoltage thresholds minimum and maximum include hysteresis.

- 7. Undervoltage thresholds minimum and maximum include hysteresis

#### **Table 4. Power Input Static Electrical Characteristics**

Characteristics noted under conditions of 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, and Calibrated Timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with V<sub>PWR</sub> = 14 V, T<sub>A</sub> = 25 °C.

| Characteristic                                                                                                                                                                                                                                                 | Symbol                                                                              | Min         | Тур           | Max           | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------|---------------|---------------|------|

| VOLTAGE REGULATOR OUTPUTS (VCC, VPROT)                                                                                                                                                                                                                         | •                                                                                   |             |               |               |      |

| VCC Output Voltage $0 \le I_{VCC} \le I_{VCC\_C}$                                                                                                                                                                                                              | V <sub>CC</sub>                                                                     | 4.9         | 5.0           | 5.1           | V    |

| VCC Output Current Continuous                                                                                                                                                                                                                                  | I <sub>VCC_C</sub>                                                                  | _           | _             | 200           | mA   |

| VPROT Output Voltage (tracks VCC)<br>I <sub>VCC</sub> = 100 mA, I <sub>VPROT</sub> = 50 mA 9.0 V < V <sub>PWR</sub> < 18 V                                                                                                                                     | I <sub>VCC</sub> -V <sub>PROT</sub>                                                 | _           | 1             | 25            | mV   |

| VPROT Output Current Continuous                                                                                                                                                                                                                                | I <sub>VPROT_C</sub>                                                                | _           | 1             | 100           | mA   |

| VCC Output Current Limiting                                                                                                                                                                                                                                    | I <sub>VCC_CL</sub>                                                                 | 200 (11)    | -             | 500           | mA   |

| VPROT Output Current Limiting                                                                                                                                                                                                                                  | I <sub>VPROT_CL</sub>                                                               | 110         | -             | 260           | mA   |

| Output Capacitance External (V <sub>CC</sub> and V <sub>PROT</sub> ) without reverse protection diode                                                                                                                                                          | V <sub>OCE</sub>                                                                    | 2.2         | _             | 47            | μF   |

| Line Regulation (Both $V_{CC}$ and $V_{PROT}$ ) $I_{VCC}$ =100 mA, $I_{PROT}$ = 50 mA, 9.0 V< $V_{PWR}$ < 18 V                                                                                                                                                 | REG <sub>LINE_VB</sub>                                                              | _           | 2.0           | 25            | mV   |

| Load Regulation (Both $V_{CC}$ and $V_{PROT})$ measured from 10% - 90% of $I_{VCC\_C}$ & $I_{PROT\_C},V_{PWR}$ = 13 V                                                                                                                                          | REG <sub>LOAD_VB</sub>                                                              | _           | 20            | 35            | mV   |

| Dropout Voltage (Both $\rm V_{CC}$ and $\rm V_{PROT})$ (Minimal Input/Output Voltage at full load, tracks input below)                                                                                                                                         | V <sub>DROPOUT</sub>                                                                | -           | 1.05          | 1.4           | V    |

| ALL LOW SIDE DRIVERS (INJ1, INJ2, ROUT1, ROUT2, LAMPOUT, TACHOU                                                                                                                                                                                                | Τ)                                                                                  |             |               |               | •    |

| Output Fault Detection Voltage Threshold <sup>(8)</sup> Outputs programmed OFF (Open Load) Outputs programmed ON (Short to Battery)                                                                                                                            | V <sub>OUT(FLT-TH)</sub>                                                            | 2.0         | 2.5           | 3.0           | V    |

| Output OFF Open Load Detection Current (INJ1, INJ2, RELAY1, RELAY2 & LAMP)  • V <sub>DRAIN</sub> = 18 V, Outputs Programmed OFF                                                                                                                                | I <sub>(OFF)</sub> OCO                                                              | 40          | 75            | 115           | μА   |

| Output OFF Open Load Detection Current TachOut                                                                                                                                                                                                                 | I <sub>(OFF)TACH</sub>                                                              | 10          | _             | 30            | μА   |

| Output Leakage Current  • V <sub>DRAIN</sub> = 24 V, Open Load Detection Disabled and Output commanded OFF                                                                                                                                                     | I <sub>OUT(LKG)</sub>                                                               | _           | -             | 20            | μА   |

| Overtemperature Shutdown (OT) (9)                                                                                                                                                                                                                              | T <sub>LIM</sub>                                                                    | 155         | _             | 185           | °C   |

| Overtemperature Shutdown Hysteresis <sup>(10)</sup>                                                                                                                                                                                                            | T <sub>LIM(HYS)</sub>                                                               | 5.0         | 10            | 15            | °C   |

| Output Clamp Voltage • I <sub>D</sub> = 20 mA                                                                                                                                                                                                                  | V <sub>oc</sub>                                                                     | 48          | 53            | 60            | V    |

| INJOUT1, INJOUT2                                                                                                                                                                                                                                               | J                                                                                   | l .         |               |               |      |

| Drain-to-Source ON Resistance  • $I_{OUT} = 1.0 \text{ A T}_{J} = 125 \text{ °C}, V_{PWR} = 13 \text{ V}$ • $I_{OUT} = 1.0 \text{ A T}_{J} = 25 \text{ °C}, V_{PWR} = 13 \text{ V}$ • $I_{OUT} = 1.0 \text{ A T}_{J} = -40 \text{ °C}, V_{PWR} = 13 \text{ V}$ | R <sub>DS</sub> (ON)_INJX<br>R <sub>DS</sub> (ON)_INJX<br>R <sub>DS</sub> (ON)_INJX | -<br>-<br>- | -<br>0.4<br>- | 0.6<br>-<br>- | Ω    |

| Continuous Current (not to exceed)                                                                                                                                                                                                                             | I <sub>OUT(CC)_INJx</sub>                                                           | _           | _             | 1.3           | Α    |

| Output Self Limiting Current                                                                                                                                                                                                                                   | I <sub>OUT(LIM)_INJx</sub>                                                          | 1.6         | -             | 3.0           | Α    |

#### Notes

- 8. These parameters are guaranteed by design. Production test equipment uses 1.0 MHz, 5.0 V SPI interface.

- 9. This parameter is guaranteed by design, however it is not production tested.

- 10. Programmable via SPI but variable with magnitude input frequency

- 11. Guaranteed at 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  18 V

MC33814

**Table 4. Power Input Static Electrical Characteristics**

Characteristics noted under conditions of 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, and Calibrated Timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with V<sub>PWR</sub> = 14 V, T<sub>A</sub> = 25 °C.

| Characteristic                                                                                       | Symbol                               | Min | Тур   | Max | Unit |

|------------------------------------------------------------------------------------------------------|--------------------------------------|-----|-------|-----|------|

| ROUT1                                                                                                | 1                                    |     |       |     |      |

| Driver Drain-to-Source ON Resistance                                                                 | R <sub>DS(ON)_R1</sub>               |     |       |     | Ω    |

| • I <sub>OUT</sub> = 700 mA, T <sub>J</sub> = 150 °C, V <sub>PWR</sub> = 13 V                        | - X- / <u>-</u>                      | _   | 0.3   | 0.4 |      |

| Continuous Current (not to exceed)                                                                   | I <sub>OUT(CC)_R1</sub>              | _   | _     | 2.0 | Α    |

| Output Self-limiting Current (Has inrush current timer)                                              | I <sub>OUT(LIM)_R1</sub>             | 3.0 | _     | 6.0 | Α    |

| ROUT2                                                                                                |                                      |     | I     | Į.  |      |

| Driver Drain-to-Source ON Resistance                                                                 |                                      |     |       |     | Ω    |

| • I <sub>OUT</sub> = 350 mA, T <sub>J</sub> = 150 °C, V <sub>PWR</sub> = 13 V                        | R <sub>DS (ON)_R2</sub>              | _   | _     | 1.5 |      |

| Continuous Current (not to exceed)                                                                   | I <sub>OUT(CC)_R2</sub>              | -   | -     | 1.0 | Α    |

| Output Self-limiting Current                                                                         | I <sub>OUT(LIM)_R2</sub>             | 1.2 | _     | 2.4 | Α    |

| LAMPOUT                                                                                              |                                      |     | I     | Į.  |      |

| Driver Drain-to-Source ON Resistance                                                                 | R <sub>DS (ON)_LAMP</sub>            |     |       |     | Ω    |

| • I <sub>OUT</sub> = 1.0 A, T <sub>J</sub> = 150 °C, V <sub>PWR</sub> = 13 V                         | - 5 (511)                            | _   | _     | 1.5 |      |

| Continuous Current                                                                                   | I <sub>OUT(CC)_LAMP</sub>            | -   | -     | 1.0 | Α    |

| Output Self-limiting Current (Has inrush current timer)                                              | I <sub>OUT(LIM)</sub> _<br>LAMP      | 1.2 | -     | 2.4 | Α    |

| TACHOUT                                                                                              | 1                                    |     | 1     |     |      |

| Driver Drain-to-Source ON Resistance                                                                 | R <sub>DS (ON)_TACH</sub>            |     |       |     | Ω    |

| • I <sub>OUT</sub> = 50 mA, T <sub>J</sub> = 150 °C, V <sub>PWR</sub> = 13 V                         | · ~_                                 | _   | _     | 20  |      |

| Continuous Current (not to exceed)                                                                   | I <sub>OUT(CC)_TACH</sub>            | _   | -     | 50  | mA   |

| Output Current Shutdown                                                                              | I <sub>OUT</sub> (SHUTDOWN)<br>_TACH | 60  | -     | 110 | mA   |

| ALL PRE-DRIVERS (IGNOUT1, IGNOUT2, AND O2HOUT)                                                       |                                      |     | 1     | •   |      |

| Pre-driver Output Voltage, V <sub>PWR</sub> = 13 V                                                   |                                      |     |       |     | V    |

| • I <sub>GD</sub> = 500 μA                                                                           | V <sub>GS(ON)</sub>                  | 7.0 | 8.0   | 9.0 |      |

| • I <sub>GD</sub> = -500 μA                                                                          | V <sub>GS(OFF)</sub>                 | 0.0 | 0.375 | 0.5 |      |

| IGNOUTx Output Source Current (IGNOUT1 and IGNOUT2 by default)                                       |                                      |     |       |     |      |

| • 1.0 ≤ V <sub>GD</sub> ≤ 3.0, V <sub>PWR</sub> = 13 V                                               | I <sub>IGN_GD_H</sub>                | 10  | _     | _   | mA   |

| Output OFF Open Load Detection Current                                                               | I <sub>(OFF)OCO</sub>                |     |       |     | μА   |

| V <sub>DRAIN</sub> = 18 V, Outputs Programmed OFF                                                    |                                      | 40  | 75    | 115 |      |

| GPGD Output Source Current (O2HOUT by default) at 1.0 $\leq$ V $_{GD}$ $\leq$ 3.0, V $_{PWR}$ = 13 V | I <sub>GPGD_GD_</sub> H              | 10  | _     | _   | mA   |

| Pre-driver short to battery fault threshold                                                          |                                      |     |       |     |      |

| • I <sub>GD</sub> = 500 μA                                                                           | V <sub>IGNFB(FLT-TH)</sub>           | 100 | 250   | 400 | mV   |

| • I <sub>GD</sub> = -500 μA                                                                          | V <sub>GPGD(FLT_TH)</sub>            | 1.0 | 2.5   | 4.0 | V    |

| Output Clamp Voltage                                                                                 | V <sub>CLAMP</sub>                   | 48  | 53    | 60  | V    |

| Overcurrent Voltage Threshold                                                                        |                                      |     |       |     |      |

| V <sub>O2HSENSN</sub> to V <sub>O2HSENSP</sub>                                                       | V <sub>SENS-TH</sub>                 | 180 | 200   | 220 | mV   |

#### **Table 4. Power Input Static Electrical Characteristics**

Characteristics noted under conditions of 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, and Calibrated Timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with V<sub>PWR</sub> = 14 V, T<sub>A</sub> = 25 °C.

| Characteristic                                                                                                                                       | Symbol                   | Min                                              | Тур     | Max                        | Unit                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------|---------|----------------------------|--------------------------------------------------|

| ALL PRE-DRIVERS (IGNOUT1, IGNOUT2, AND O2HOUT) (CONTINUED)                                                                                           |                          |                                                  |         |                            |                                                  |

| Overcurrent Voltage Threshold                                                                                                                        |                          |                                                  |         |                            |                                                  |

| <ul> <li>V<sub>IGNSENSN</sub> to V<sub>IGNSENSP</sub>) (IGNIN1 or IGNIN2 = 1)</li> </ul>                                                             | V <sub>SENS-TH</sub>     | 180                                              | 200     | 220                        | mV                                               |

| <ul> <li>V<sub>IGNSENSN</sub> to V<sub>IGNSENSP</sub>) (IGNIN1 and IGNIN2 = 1)</li> </ul>                                                            | V <sub>SENS-TH</sub>     | 360                                              | 400     | 440                        |                                                  |

| Current Sense Input Offset Current (IGNSENSP,IGNSENSN, O2H                                                                                           | I <sub>SENS-OFFSET</sub> | _                                                | -       | 15                         | μΑ                                               |

| Current Sense Input Bias Current                                                                                                                     | I <sub>SENS-BIAS</sub>   | -                                                | -       | 15                         | μΑ                                               |

| ISO-9141 TRANSCEIVER PARAMETERS (8.0 V < V <sub>PWR</sub> < 18 V)                                                                                    |                          |                                                  |         |                            |                                                  |

| Input Low Voltage at ISO I/O pin                                                                                                                     | V <sub>IL_ISO</sub>      | _                                                | -       | 0.3xV <sub>PWR</sub>       | V                                                |

| Input High Voltage at ISO I/O pin                                                                                                                    | V <sub>IH_ISO</sub>      | 0.7*V <sub>PWR</sub>                             | -       | _                          | V                                                |

| Input Hysteresis at ISO I/O pin                                                                                                                      | V <sub>HYST_ISO</sub>    | 0.15x<br>V <sub>PWR</sub>                        | _       | _                          | V                                                |

| Output Low-voltage at ISO I/O pin                                                                                                                    | V <sub>OL_ISO</sub>      | -                                                | _       | 0.2xV <sub>PWR</sub>       | V                                                |

| Output High-voltage at ISO I/O pin                                                                                                                   | V <sub>OH_ISO</sub>      | 0.8x<br>V <sub>PWR</sub> R                       | _       | _                          | V                                                |

| Output current limit at ISO I/O pin (MTX = 0)                                                                                                        | I <sub>LIM_ISO</sub>     | 50                                               | 100     | 150                        | mA                                               |

| Load capacitance at ISO I/O pin <sup>(12)</sup>                                                                                                      | C <sub>L_ISO</sub>       | 0.01                                             | 3.0     | 10                         | nF                                               |

| Output load current at ISO I/O pin (MTX = 0, RLOAD = 1.0 k $\Omega$ , $\pm$ 10%)                                                                     | I_ISO                    | -                                                | 12      | _                          | mA                                               |

| VRS CONDITIONER INPUT                                                                                                                                | •                        |                                                  |         |                            |                                                  |

| Comparator Thresholds                                                                                                                                | V <sub>VRS_THRESH</sub>  | _                                                |         | variable via<br>ynamically | mV                                               |

| Threshold Accuracy Steady State Condition (±20% only valid for VRS DAC thresholds 110 mV and higher.All other thresholds guaranteed monotonic only.) | Accu <sub>THRESH</sub>   | _                                                | _       | ±20                        | %                                                |

| Input Bias Current VRSP and VRSN (2.5 V common mode must be off)                                                                                     | I <sub>BIASRSX</sub>     | -5.0                                             |         | 5.0                        | μΑ                                               |

| VRS Positive Clamp Voltage at I <sub>CLAMP</sub> = 10 mA                                                                                             | V <sub>CLAMP_P</sub>     | 5.5                                              | _       | 5.8                        | V                                                |

| VRS Negative Clamp Voltage at I <sub>CLAMP</sub> = 10 mA                                                                                             | V <sub>CLAMP_N</sub>     | -0.45                                            | _       | -0.22                      | V                                                |

| DIGITAL INTERFACE (MRX, MTX,CSB, SI, SCLK, SO, RINX,O2HIN, INJINX, I                                                                                 | GNINX, BATSW,            | VRSOUT, F                                        | RESETB) | •                          |                                                  |

| Input Logic High-voltage Thresholds                                                                                                                  | V <sub>IH</sub>          | 0.7 x V <sub>CC</sub>                            | -       | V <sub>CC</sub> + 0.3      | V                                                |

| Input Logic Low-voltage Thresholds                                                                                                                   | V <sub>IL</sub>          | GND - 0.3                                        | _       | 0.2 x V <sub>CC</sub>      | V                                                |

|                                                                                                                                                      | +                        | <del>                                     </del> | +       | 1                          | <del>                                     </del> |

$V_{\text{HYS}}$

$C_{IN}$

I<sub>LOGIC</sub> ss

I<sub>LOGIC\_PD</sub>

500

-10

30

50

#### Notes

12. This parameter is guaranteed by design, however it is not production tested.

Input Logic Pull-down Current (12) INJIN1, INJIN2, RIN1, RIN2, SI, SCLK, IGNIN1,

MC33814

mV

рF

μΑ

μΑ

20

10

100

Input Logic Voltage Hysteresis

Sleep Mode Input Logic Current (12)

Input Logic Capacitance

• KEYSW = 0 V

• 0.8 V to 5.0 V

IGNIN2, O2HIN

#### **Table 4. Power Input Static Electrical Characteristics**

Characteristics noted under conditions of 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, and Calibrated Timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with V<sub>PWR</sub> = 14 V, T<sub>A</sub> = 25 °C.

| Characteristic                                                                      | Symbol                                        | Min                   | Тур       | Max              | Unit |

|-------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------|-----------|------------------|------|

| DIGITAL INTERFACE (MRX, MTX,CSB, SI, SCLK, SO, RINX,O2H                             | IN, INJINX, IGNINX, BATSW,                    | VRSOUT, R             | ESETB) (C | ONTINUED         | ))   |

| SO Tri-state Output (in Tri-state mode, CSB = 1)  • 0 V to 5.0 V                    | I <sub>TRISO</sub>                            | -10                   | -         | 10               | μА   |

| CSB Input Current  • CSB = V <sub>CC</sub>                                          | I <sub>CSB</sub>                              | -10                   | -         | 10               | μА   |

| Input Logic Pull-up Current - CSB and MTX  • 0.0 to 4.2 V                           | I <sub>LOGIC_PU</sub>                         | -20                   | -40       | -90              | μА   |

| CSB Leakage Current to V <sub>CC</sub> • CSB = 5.0 V, KEYSW = 0.0 V                 | I <sub>CSB(LKG)</sub>                         | _                     | -         | 10               | μА   |

| SO, MRX High-state Output Voltage (CSB =0 for SO)  • I <sub>SO-HIGH</sub> = -1.0 mA | V <sub>SO_HIGH</sub><br>V <sub>MRX_HIGH</sub> | V <sub>CC</sub> - 0.4 | -         | -                | V    |

| SO, MRX Low-state Output Voltage (CSB =0 for SO)  • I <sub>SO-LOW</sub> = 1.0 mA    | V <sub>SO_LOW</sub><br>V <sub>MRX_LOW</sub>   | -                     | -         | 0.4              | V    |

| BATSW High-state Output Voltage • I <sub>SO-HIGH</sub> = -10 mA                     | V <sub>BATSW_HIGH</sub>                       | V <sub>CC</sub> - 1.0 | _         | _                | V    |

| BATSW Low-state Output Voltage • I <sub>SO-LOW</sub> = 10 mA                        | V <sub>BATSW_LOW</sub>                        | _                     | -         | 1.0              | V    |

| KEYSW High-state Input Voltage                                                      | V <sub>KEYSW_HIGH</sub>                       | 4.5                   | _         | V <sub>PWR</sub> | V    |

| KEYSW Low-state Input Voltage                                                       | V <sub>KEYSW_LOW</sub>                        | -0.3                  | _         | 2.5              | V    |

| KEYSW Hysteresis                                                                    | V <sub>KEYSW_HYS</sub>                        | 100                   | _         | -                | mV   |

| VRS Low-state Output Voltage • I <sub>VRS-LOW</sub> = 1.0 mA                        | V <sub>VRSOUT_LOW</sub>                       | _                     | -         | 0.4              | V    |

| VRS High-state Output Voltage • I <sub>VRS-HIGH</sub> = 1.0 mA                      | V <sub>VRSOUT_HIGH</sub>                      | V <sub>CC</sub> -0.4  | -         | 5.0              | V    |

| RESET Low-state Output Voltage  • I <sub>RESET-LOW</sub> = 1.0 mA                   | V <sub>RESET_LOW</sub>                        | -                     | -         | 0.4              | V    |

| RESET High-state Leakage Current                                                    | I <sub>RESET_</sub><br>LEAKAGE_HIGH           | 10                    | -         | 25               | μА   |

| RESET Pull-down Resistor                                                            | R <sub>RESET</sub> _                          | 200                   | _         | 500              | kΩ   |

# 4.3 Dynamic Electrical Characteristics

Table 5. Dynamic Electrical Characteristics (14)

Characteristics noted under conditions of 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  18 V, -40 °C  $\leq$  T<sub>C</sub>  $\leq$  125 °C, and Calibrated Timers, unless otherwise noted. Where applicable, typical values reflect the parameter's approximate average value with V<sub>PWR</sub> = 14 V, T<sub>A</sub> = 25 °C.

| Characteristic                                                                                                                                                                  | Symbol                                | Min                 | Тур                | Max                | Unit |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------|--------------------|--------------------|------|--|

| POWER INPUT                                                                                                                                                                     |                                       |                     |                    |                    |      |  |

| Required Low State Duration on V <sub>CC</sub> for Power On Reset                                                                                                               | t <sub>RESET</sub>                    |                     |                    |                    | μS   |  |

| • V <sub>CC</sub> ≤ 0.2 V                                                                                                                                                       |                                       | 1.0                 | _                  | _                  |      |  |

| Power on RESET pulse width                                                                                                                                                      | t <sub>(POR)</sub>                    | 100                 | -                  | -                  | μS   |  |

| WATCHDOG TIMER                                                                                                                                                                  |                                       |                     |                    |                    |      |  |

| Maximum Time Value Watchdog can be loaded with (default time)                                                                                                                   | WDMAX                                 | _                   | _                  | 10                 | sec. |  |

| Minimum Time Value Watchdog can be loaded with                                                                                                                                  | WD <sub>MIN</sub>                     | 1.0                 | _                  | _                  | ms   |  |

| Reset Pulse Width when Watchdog times out                                                                                                                                       | WD <sub>RESET</sub>                   | 100                 | _                  | _                  | μS   |  |

| VRS CONDITIONING INPUT                                                                                                                                                          |                                       |                     |                    |                    |      |  |