# Fast Transient Response Regulator, VLDO, 1.5 A

The NCP57152 is a high precision, very low dropout (VLDO), low minimum input voltage and low ground current positive voltage regulator that is capable of providing an output current in excess of 1.5 A with a typical dropout voltage of 330 mV at 1.5 A load current and input voltage from 1.8 V and up. The devices are stable with ceramic output capacitors.

The device can withstand up to 18 V max input voltage. Internal protection features consist of output current limiting, in thermal shutdown and reverse output current protectiongic level enable and error flag pins are available.

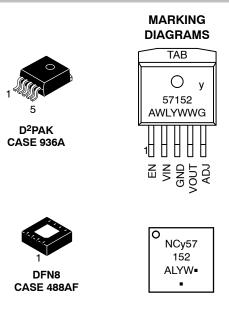

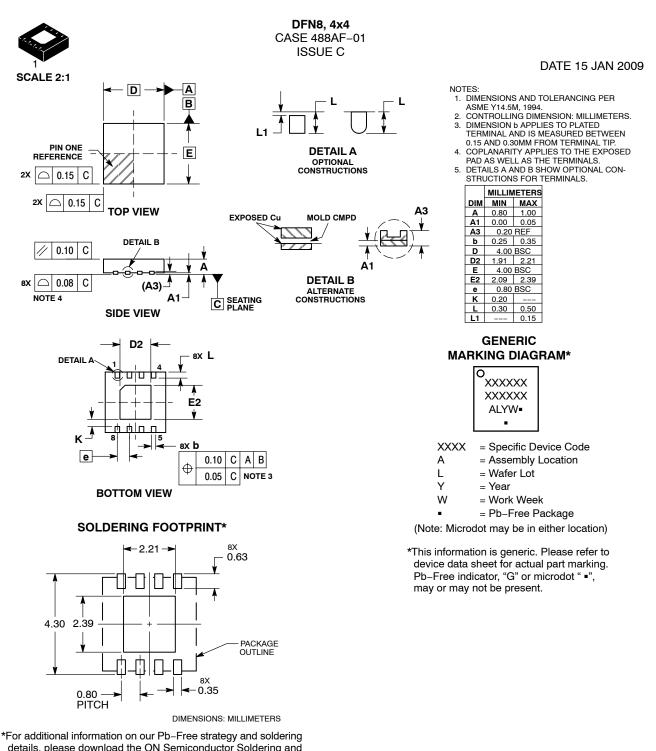

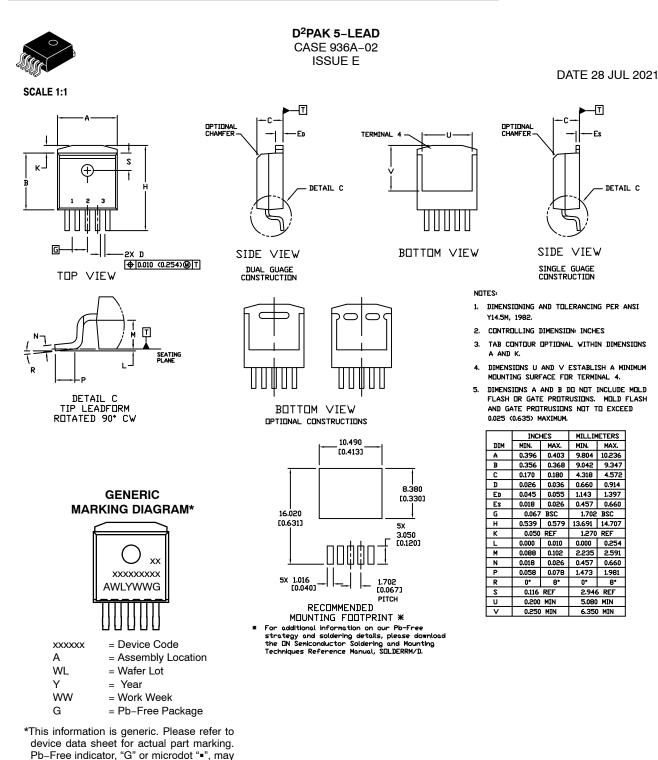

The NCP57152 is an Adjustable Voltage device and is available in D2PAK-5 and DFN8 packages.

## Features

- Output Current in Excess of 1.5 A

- Minimum Operating Input Voltage 1.8 V for Full 1.5 A Output Current

- 330 mV Typical Dropout Voltage at 1.5 A

- Adjustable Output Voltage Range from 1.24 V to 13 V

- Low Ground Current

- Fast Transient Response

- Stable with Ceramic Output Capacitor

- Logic Compatible Enable and Error Flag Pins

- Current Limit, Reverse Current and Thermal Shutdown Protection

- Operation up to 13.5 V Input Voltage

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These are Pb–Free Devices

## Applications

- Consumer and Industrial Equipment Point of Regulation

- Servers and Networking Equipment

- FPGA, DSP and Logic Power Supplies

- Switching Power Supply Post Regulation

- Battery Chargers

- Functional Replacement for Industry Standard MIC29150, MIC39150, MIC37150 with Improved Minimum Input Voltage Specification

# **ON Semiconductor®**

http://onsemi.com

(\*Note: Microdot may be in either location)

## **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

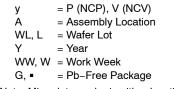

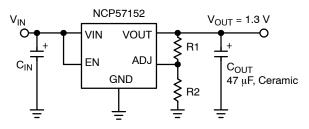

## **TYPICAL APPLICATIONS**

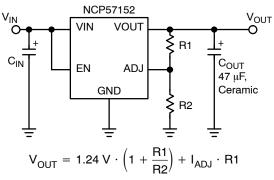

Figure 1. Adjustable Regulator

Figure 2. Adjustable Regulator in DFN Package

| Pin Number<br>D2PAK-5 | Pin Number<br>DFN8 | Pin Name       | Pin Function                                                                                     |  |  |

|-----------------------|--------------------|----------------|--------------------------------------------------------------------------------------------------|--|--|

| 1                     | 2                  | EN             | Enable Input: CMOS and TTL logic compatible. Logic high = enable; Logic low = shutdown.          |  |  |

| 2                     | 3                  | VIN            | Input voltage which supplies both the internal circuitry and the current to the output load.     |  |  |

| 3                     | 1                  | GND            | Ground                                                                                           |  |  |

| 4                     | 6                  | VOUT           | Linear Regulator Output.                                                                         |  |  |

| 5                     | 7                  | ADJ            | Adjustable Regulator Feedback Input.<br>Connect to output voltage resistor divider central node. |  |  |

| TAB                   | -                  | TAB            | TAB is connected to ground.                                                                      |  |  |

| -                     | 8                  | FLG            | Error Flag Open collector output.<br>Active-low indicates an output fault condition.             |  |  |

| -                     | EP                 | EXPOSED<br>PAD | PAD for removing heat from the device. Must be connected to GND.                                 |  |  |

| -                     | 4, 5               | NC             | Not internally connected.                                                                        |  |  |

## PIN FUNCTION DESCRIPTION

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol             | Rating                                       | Value                             | Unit                     |    |

|--------------------|----------------------------------------------|-----------------------------------|--------------------------|----|

| V <sub>IN</sub>    | Supply Voltage                               | 0 to 18                           | V                        |    |

| V <sub>EN</sub>    | Enable Input Voltage                         | 0 to 18                           | V                        |    |

| V <sub>FLG</sub>   | Error Flag Open Collector Output Maxin       | 0 to 18                           |                          |    |

| $V_{OUT} - V_{IN}$ | Reverse $V_{OUT} - V_{IN}$ Voltage (EN = Shu | 0 to 6.5                          | V                        |    |

| P <sub>D</sub>     | Power Dissipation (Notes 2 and 5)            | Internally Limited                |                          |    |

| TJ                 | Junction Temperature                         | $-40 \le T_J \le +125$            | °C                       |    |

| T <sub>S</sub>     | Storage Temperature                          |                                   | $-65 \le T_{J} \le +150$ | °C |

|                    | ESD Rating (Notes 3 and 4)                   | Human Body Model<br>Machine Model | 2000<br>200              | V  |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

NOTE: All voltages are referenced to GND pin unless otherwise noted.

- 1. The ENABLE pin input voltage must be  $\leq 0.8$  V or Vin must be connected to ground potential.

- P<sub>D(max)</sub> = (T<sub>J(max)</sub> T<sub>A</sub>) / R<sub>θJA</sub>, where R<sub>θJA</sub> depends upon the printed circuit board layout.

Devices are ESD sensitive. Handling precautions recommended..

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model (HBM) tested per AEC-Q100-002 (EIA/JESD22-A114C) ESD Machine Model (MM) tested per AEC-Q100-003 (EIA/JESD22-A115C) This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

- 5. This protection is not guaranteed outside the Recommended Operating Conditions.

## **RECOMMENDED OPERATING CONDITIONS** (Note 6)

| Symbol           | Rating                            | Value                    | Unit |

|------------------|-----------------------------------|--------------------------|------|

| V <sub>IN</sub>  | Supply Voltage                    | 1.8 to 13.5              | V    |

| V <sub>EN</sub>  | Enable Input Voltage              | 0 to 13.5                | V    |

| V <sub>FLG</sub> | Error Flag Open Collector Voltage | 0 to 13.5                | V    |

| TJ               | Junction Temperature              | $-40 \leq T_J \leq +125$ | °C   |

6. The device is not guaranteed to function outside it's Recommended operating conditions.

## **ELECTRICAL CHARACTERISTICS**

$T_J = 25^{\circ}C$  with  $V_{IN} = V_{OUT nominal} + 0.6 V$ ;  $V_{EN} = V_{IN}$ ;  $I_L = 10 \text{ mA}$ ; bold values indicate  $-40^{\circ}C < T_J < +125^{\circ}C$ , unless noted. (Note 7)

| Parameter                                                   | Conditions                                                                                             | Min                            | Тур            | Max                               | Unit    |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------|----------------|-----------------------------------|---------|

| Output Voltage Accuracy                                     | I <sub>L</sub> = 10 mA                                                                                 | -1                             |                | 1                                 | %       |

| DFN package                                                 | 10 mA < I_{OUT} < 1.5 A , V_{OUT nominal} + 0.6 $\leq$ V <sub>IN</sub> $\leq$ 13.5 V                   | -2                             |                | 2                                 | %       |

| Output Voltage Accuracy                                     | IL = 10 mA                                                                                             | -1.5                           |                | 1.5                               | %       |

| D2PAK package                                               | 10 mA < I <sub>OUT</sub> < 1.5 A , V <sub>OUT nominal</sub> + 0.6 $\leq$ V <sub>IN</sub> $\leq$ 13.5 V | -2.5                           |                | 2.5                               | %       |

| Output Voltage Line Regulation                              | $V_{IN} = V_{OUT nominal} + 0.6 V$ to 13.5 V; $I_L = 10 \text{ mA}$                                    |                                | 0.02           | 0.5                               | %       |

| Output Voltage Load Regulation                              | I <sub>L</sub> = 10 mA to 1.5 A                                                                        |                                | 0.2            | 1.0                               | %       |

| V <sub>IN</sub> – V <sub>OUT</sub> Dropout Voltage (Note 8) | I <sub>L</sub> = 500 mA (Note 9)                                                                       |                                | 180            | 295                               | mV      |

|                                                             | I <sub>L</sub> = 750 mA                                                                                |                                | 220            | 350                               | mV      |

|                                                             | I <sub>L</sub> = 1.0 A (Note 9)                                                                        |                                | 260            | 410                               | mV      |

|                                                             | I <sub>L</sub> = 1.5 A                                                                                 |                                | 330            | 520                               | mV      |

| Ground Pin Current (Note 10)                                | I <sub>L</sub> = 1.5 A                                                                                 |                                | 40             | 60<br><b>80</b>                   | mA      |

| Ground Pin Current in Shutdown                              | $V_{EN} \leq 0.5 V$                                                                                    |                                | 1.0            | 5.0                               | μA      |

| Overload Protection Current Limit                           | V <sub>OUT</sub> = 0 V                                                                                 |                                | 2.0            | 3.0                               | Α       |

| Start-up Time                                               | $V_{EN}$ = $V_{IN},V_{OUT}$ nominal = 2.5 V, $I_{OUT}$ = 10 mA, $C_{OUT}$ = 47 $\mu F$                 |                                | 100            | 500                               | μs      |

| Output Voltage Start-up Slope                               | $V_{EN} = V_{IN}$ , $I_{OUT} = 10$ mA, $C_{OUT} = 47 \ \mu\text{F}$ (Note 11)                          |                                | 40             | 200                               | μs/V    |

| Reference Voltage DFN Package D <sup>2</sup> PAK Package    |                                                                                                        | 1.228<br><b>1.215</b><br>1.221 | 1.240<br>1.240 | 1.252<br><b>1.265</b><br>1.259    | V       |

| Adjust Pin Bias Current                                     |                                                                                                        | 1.209                          | 100            | <b>1.271</b><br>200<br><b>350</b> | nA      |

| ENABLE INPUT                                                |                                                                                                        |                                |                |                                   | <u></u> |

| Enable Input Signal Levels                                  | Regulator Enable                                                                                       | 1.4                            |                |                                   | V       |

|                                                             | Regulator Shutdown                                                                                     | 1                              |                | 0.8                               | V       |

| Enable Pin Input Current                                    | $V_{EN} \leq 0.8 V$ (Regulator Shutdown)                                                               |                                |                | 2.0<br><b>4.0</b>                 | μΑ      |

|                                                             | $6.5 \text{ V} > \text{V}_{\text{EN}} \ge 1.4 \text{ V}$ (Regulator enable)                            |                                | 15             | 30<br><b>40</b>                   | μA      |

#### FLAG OUTPUT

| I <sub>FLG(leak)</sub> | V <sub>oh</sub> = 13.5 V, Flag OFF                        |    |     | 1.0<br><b>2.0</b> | μΑ |

|------------------------|-----------------------------------------------------------|----|-----|-------------------|----|

| V <sub>FLG(LO)</sub>   | V <sub>IN</sub> = 1.8 V, I <sub>FLG</sub> = 1 mA, Flag ON |    | 210 | 400<br><b>500</b> | mV |

| V <sub>FLG</sub>       | Low Threshold, % of particular V <sub>OUT</sub>           | 93 | 95  |                   | %  |

|                        | Hysteresis, % of particular V <sub>OUT</sub>              |    | 2   |                   | %  |

|                        | High Threshold, % of particular V <sub>OUT</sub>          |    | 97  | 99.2              | %  |

7.  $V_{OUTnominal}$  can be set by external resistor divider in the application. Tested for  $V_{OUTnominal} = 1.24$  V unless noted. 8.  $V_{DO} = V_{IN} - V_{OUT}$  when  $V_{OUT}$  decreases to 98% of its nominal output voltage with  $V_{IN} = V_{OUT} + 1$  V. Tested for  $V_{OUTnominal} = 2.5$  V. 9. Guaranteed by design.

| Package                   | Conditions / PCB Footprint                                     | Thermal Resistance               |  |

|---------------------------|----------------------------------------------------------------|----------------------------------|--|

| D2PAK-5, Junction-to-Case |                                                                | $R_{\theta JC} = 2.1^{\circ}C/W$ |  |

| D2PAK-5, Junction-to-Air  | PCB with 100 mm <sup>2</sup> 2.0 oz Copper Heat Spreading Area | $R_{\theta JA} = 52^{\circ}C/W$  |  |

| DFN8, Junction-to-Air     | PCB with 500 mm <sup>2</sup> 2.0 oz Copper Heat Spreading Area | $R_{\theta JA} = 75^{\circ}C/W$  |  |

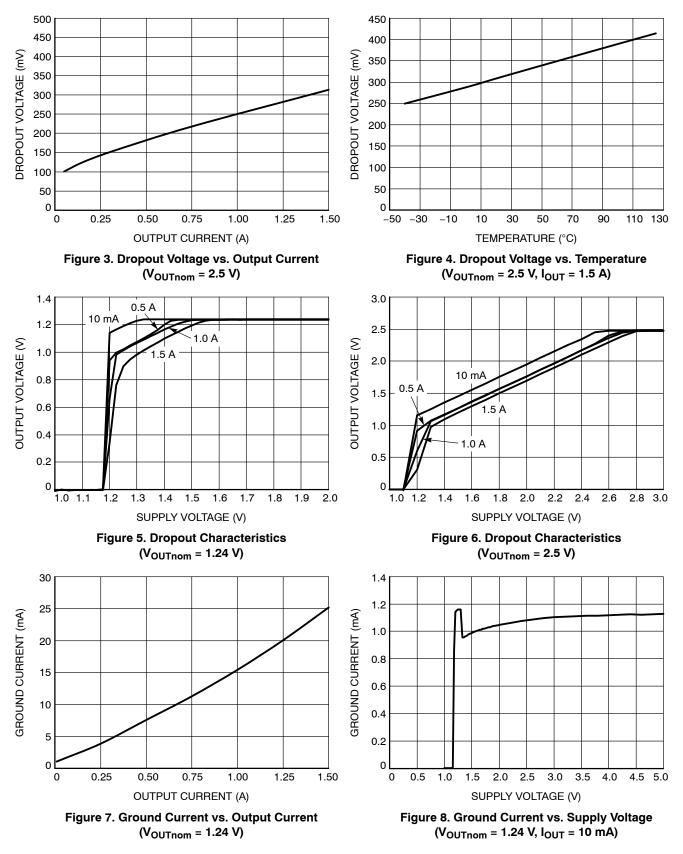

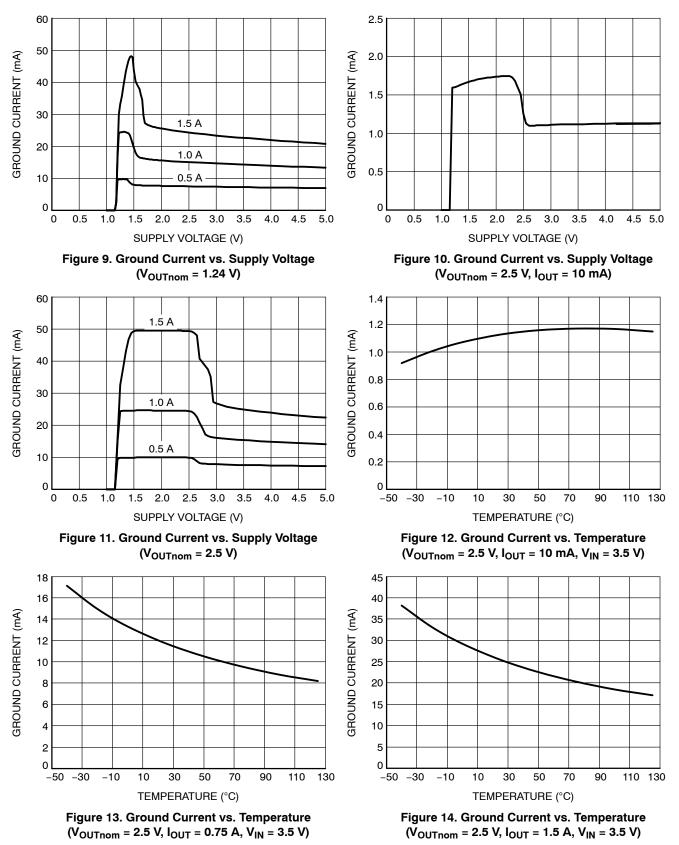

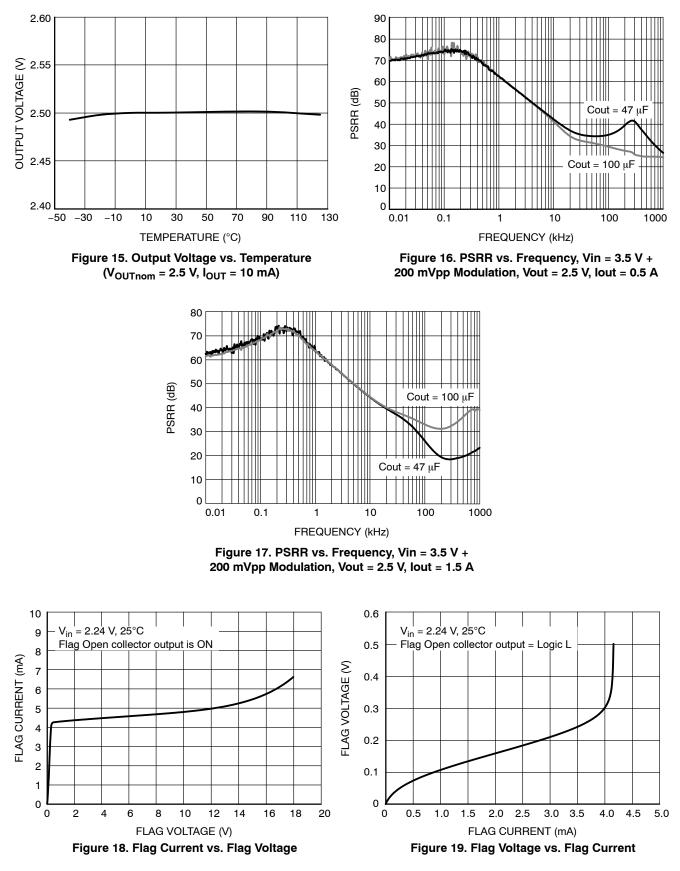

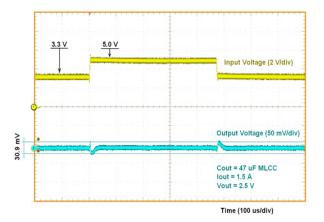

## **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS**

## TYPICAL CHARACTERISTICS

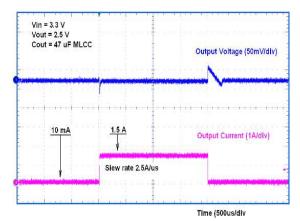

Figure 20. Line Transient Response

Figure 21. Load Transient Response

## **APPLICATIONS INFORMATION**

#### **Output Capacitor and Stability**

The NCP57152 device requires an output capacitor for stable operation. The NCP57152 is designed to operate with ceramic output capacitors. The recommended output capacitance value is 47  $\mu$ F or greater. Such capacitors help to improve transient response and noise reduction at high frequency.

#### Input Capacitor

An input capacitor of  $1.0 \,\mu\text{F}$  or greater is recommended when the device is more than 4 inches away from the bulk supply capacitance, or when the supply is a battery. Small, surface-mount chip capacitors can be used for the bypassing. The capacitor should be place within 1 inch of the device for optimal performance. Larger values will help to improve ripple rejection by bypassing the input of the regulator, further improving the integrity of the output voltage.

#### **Minimum Load Current**

The NCP57152 regulator is specified between finite loads. A 5 mA minimum load current is necessary for proper operation.

## Enable Input

NCP57152 regulators also feature an enable input for on/off control of the device. It's shutdown state draws "zero" current from input voltage supply (only microamperes of leakage). The enable input is TTL/CMOS compatible for simple logic interface, but can be connected up to  $V_{IN}$ .

## Error Flag

NCP57152 devices in DFN package feature an error flag circuit that monitors the output voltage and signals an error condition when the voltage is 5% below the nominal output voltage. The error flag is an open–collector output that can sink up to 5 mA typically during a  $V_{OUT}$  fault condition.

The FLG output is overload protected when a short circuit of the pullup load resistor occurs in the application. This is guaranteed in the full range of FLG output voltage Max ratings (see Max Ratings table). Please be aware operation in this mode is not recommended, power dissipated in the device can impact on output voltage precision and other device characteristics.

#### **Overcurrent and Reverse Output Current Protection**

The NCP57152 regulator is fully protected from damage due to output current overload and output short conditions. When NCP57152 output is overloaded, Output Current limiting is provided. This limiting is linear; output current during overload or output short conditions is constant. These features are advantageous for powering FPGAs and other ICs having current consumption higher than nominal during their startup.

Thermal shutdown disables the NCP57152 device when the die temperature exceeds the maximum safe operating temperature.

When NCP57152 is disabled and  $(V_{OUT} - V_{IN})$  voltage difference is less than 6.5 V in the application, the output structure of these regulators is able to withstand output voltage (backup battery as example) to be applied without reverse current flow. Of course the additional current flowing through the feedback resistor divider needs to be included in the backup battery discharging calculations.

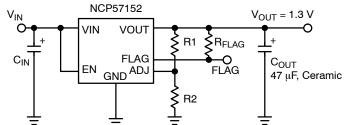

## Adjustable Voltage Design

The NCP/NCV57152 Adjustable voltage Device Output voltage is set by the ratio of two external resistors as shown in Figure 22.

The device maintains the voltage at the ADJ pin at 1.24 V referenced to ground. The current in R2 is then equal to 1.24 V / R2, and the current in R1 is the current in R2 plus

the ADJ pin bias current. The ADJ pin bias current flows from  $V_{OUT}$  through R1 into the ADJ pin.

Figure 22. Adjustable Voltage Operation

For the R2 resistor value up to 15 kOhm the  $I_{ADJ}$  current impact can be neglected and the R1 resistor value can be calculated by:

$$R1 = R2 \cdot ((V_{OUT}/1.24) - 1)$$

(eq. 1)

Where  $V_{OUT}$  is the desired nominal output voltage.

#### **Thermal Considerations**

The power handling capability of the device is limited by the maximum rated junction temperature ( $125^{\circ}C$ ). The P<sub>D</sub> total power dissipated by the device has two components, Input to output voltage differential multiplied by Output current and Input voltage multiplied by GND pin current.

$$\mathsf{P}_\mathsf{D} = \left(\mathsf{V}_\mathsf{IN} - \mathsf{V}_\mathsf{OUT}\right) \cdot \mathsf{I}_\mathsf{OUT} + \mathsf{V}_\mathsf{IN} \cdot \mathsf{I}_\mathsf{GND} \quad (\mathsf{eq. 2})$$

The GND pin current value can be found in Electrical Characteristics table and in Typical Characteristics graphs. The Junction temperature  $T_J$  is

$$T_{J} = T_{A} + P_{D} \cdot R_{\theta JA}$$

(eq. 3)

where  $T_A$  is ambient temperature and  $R_{\theta JA}$  is the Junction to Ambient Thermal Resistance of the NCP/NCV57152 device mounted on the specific PCB.

To maximize efficiency of the application and minimize thermal power dissipation of the device it is convenient to use the Input to output voltage differential as low as possible.

The static typical dropout characteristics for various output voltage and output current can be found in the Typical Characteristics graphs.

| Device            | Output<br>Current | Output<br>Voltage | Junction Temp. Range | Package               | Shipping <sup>†</sup> |

|-------------------|-------------------|-------------------|----------------------|-----------------------|-----------------------|

| NCP57152MNADJTYG  | 1.5 A             | ADJ               | –40°C to +125°C      | DFN8–4x4<br>(Pb–Free) | 4000 / Tape & Reel    |

| NCV57152MNADJTYG* | 1.5 A             | ADJ               | –40°C to +125°C      | DFN8-4x4<br>(Pb-Free) | 4000 / Tape & Reel    |

| NCP57152DSADJR4G  | 1.5 A             | ADJ               | –40°C to +125°C      | D2PAK–5<br>(Pb–Free)  | 800 / Tape & Reel     |

| NCV57152DSADJR4G* | 1.5 A             | ADJ               | –40°C to +125°C      | D2PAK–5<br>(Pb–Free)  | 800 / Tape & Reel     |

#### ORDERING INFORMATION

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable.

details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                        | 98AON15232D Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                            | DFN8, 4X4, 0.8P                                                                                                                                                                                 |  | PAGE 1 OF 1 |  |  |  |

| ON Semiconductor and 🔟 are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding |                                                                                                                                                                                                 |  |             |  |  |  |

ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

DOCUMENT NUMBER:

98ASH01006A

Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

DESCRIPTION:

D2PAK 5-LEAD

PAGE 1 OF 1

ON Semiconductor and use trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

or may not be present. Some products may

not follow the Generic Marking.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales