## Freescale Semiconductor

Data Sheet: Advanced Information

Document Number: LS1024A Rev. 0, 09/2014

# QorlQ LS1024A Data Sheet

The LS1024A product family addresses a wide variety of applications ranging from high-end VoIP and Video enabled home gateways, Small-to-Midsized Business (SMB) high performance security appliances to Ethernet powered 802.11ac enterprise access points and consumer networked storage products.

Building upon the field-hardened LS102MA, the LS1024A series of processors delivers vastly increased processing power and VoIP density, wire speed handling of small packets, DRM compliant security and enterprise grade VPN and SSL throughput. The new chip allows considerable system cost savings by integrating the new features that are now emerging in the CPE market.

LS1024A leverages the energy efficient core technology of ARM® and Freescale's low-power design process to achieve the lowest power consumption in its class. Additionally, the companion software development kit provides a rich set of power management features to address the energy saving goals of service providers and product manufacturers worldwide.

In addition to providing high throughput IPSec and SSL CPU offload, the LS1024A's onboard security engine includes a powerful Deep Packet Inspection Engine with GZIP decompression capability. The device's three Ethernet interfaces allow for DMZ configuration providing further security for SOHO/SMB routers and gateways.

LS1024A I/O interfaces in conjunction with Freescale's innovative multi-layer bus architecture allows non-blocking concurrent transactions across all data interfaces, thus minimizing on-chip packet processing latency. The LS1024A's SATA-2 interfaces, along with

the powerful LRO/TSO and XOR Engine, provide an ideal solution for Network Attached Storage applications.

In order to provide performance scalability and maximum flexibility the LS1024A family of processors includes single and dual ARM® Cortex®-A9 core devices from 650 MHz to 1.2 GHz delivering up to 6000 DMIPS.

The LS1024A OpenWRT Linux-based SDK is optimized for both single- and dual-core operation. The software deliverable for the LS1024A dual core devices are backward compatible with the LS102MA and 100 line of products.

Additionally, Freescale's rich ecosystem delivers turnkey solutions that reduce time-to-market and lower development costs for VPN/SSL SMB routers, home gateway, Consumer NAS, and Enterprise Access Point manufacturers.

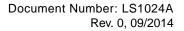

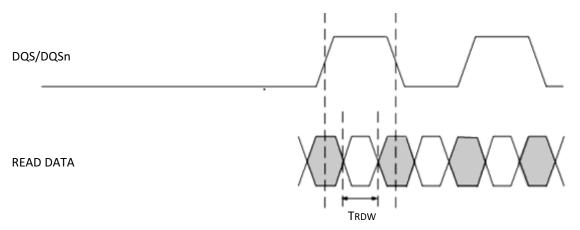

Figure 1-1 shows the block diagram of LS1024A device.

# Table of Contents

| Product Applications 1                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------|

| Features by Device Summary 1                                                                                                       |

| Technical Overview 3                                                                                                               |

| External Interfaces and Functional Blocks 3                                                                                        |

| Pinout and Signal Summary 7                                                                                                        |

| Ball Map7Signal Summary27Unused Interfaces41                                                                                       |

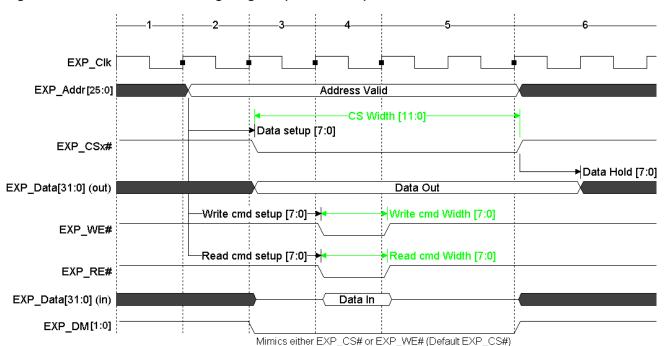

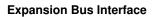

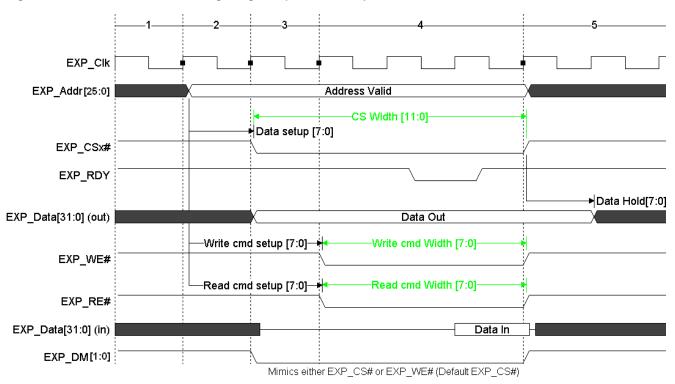

| Expansion Bus Interface                                                                                                            |

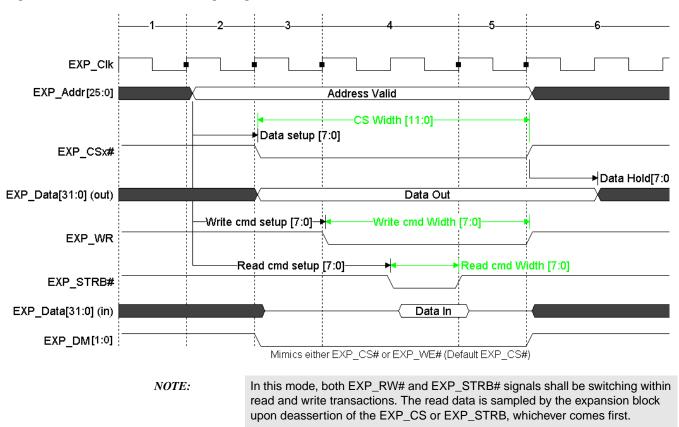

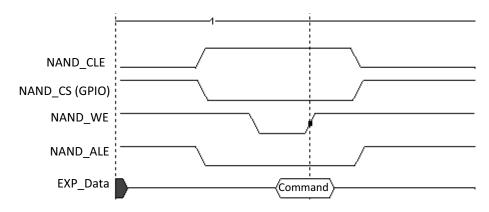

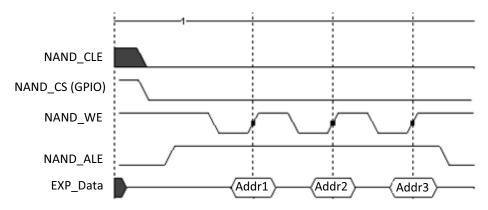

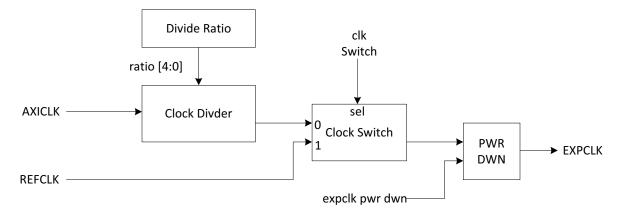

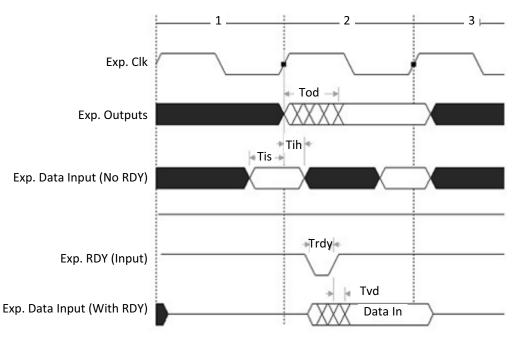

| Introduction45Features.45Block Overview46Block Functional Description.47Bootstrap Synchronization59Asynchronous Interface60        |

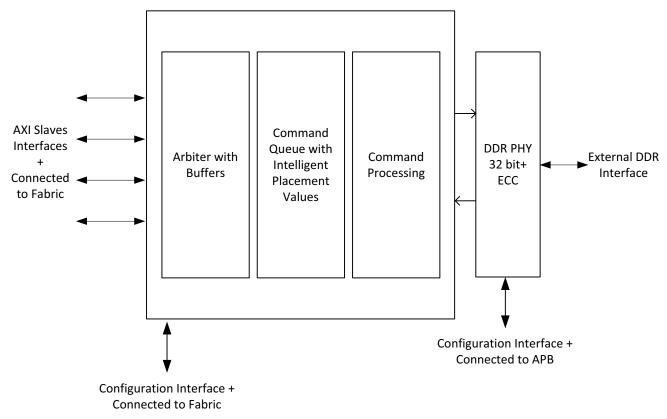

| DDR3 Controller                                                                                                                    |

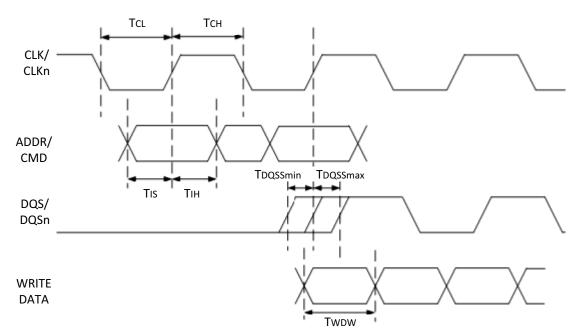

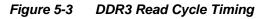

| Introduction61DDR3 Controller Features61Supported Memory Configurations61Functional Description62DDR3 SDRAM Interface Bus Timing64 |

| General Purpose Input Output                                                                                                       |

| Introduction67Features and Functions67                                                                                             |

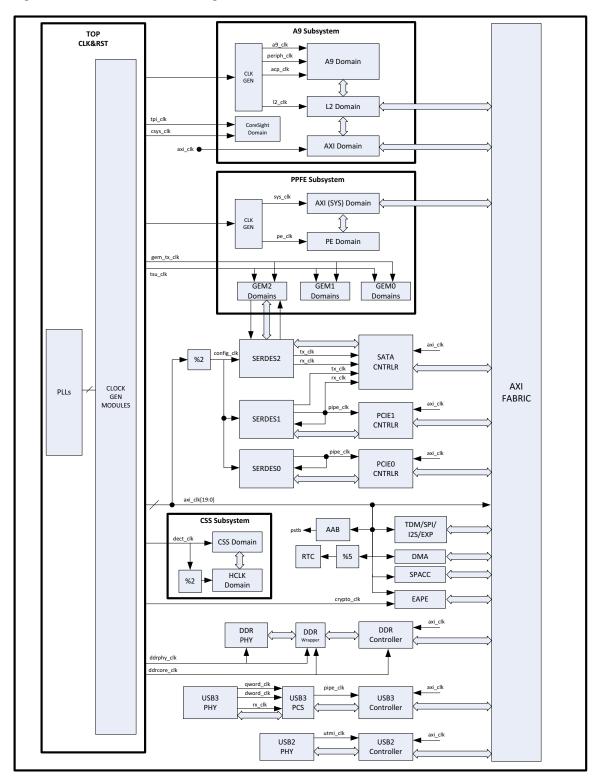

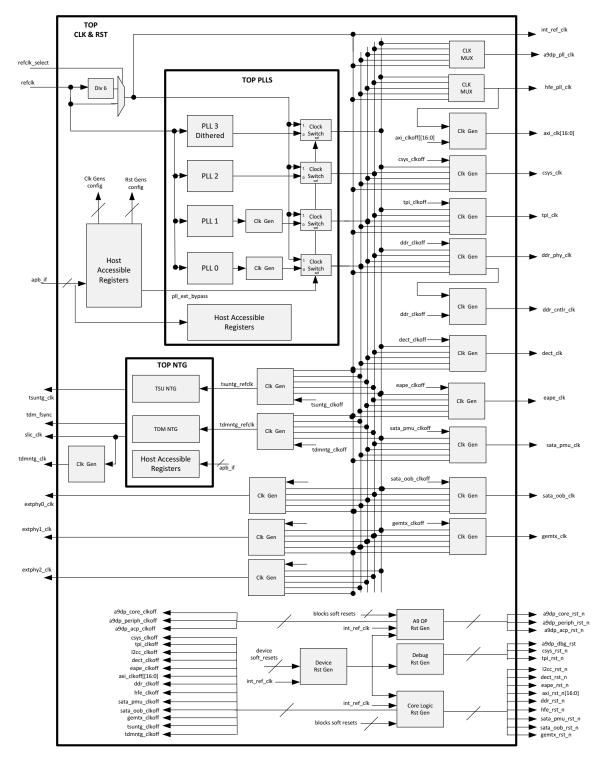

| Clock and Reset 69                                                                                                                 |

| Clock Features69Reset Features70Clock Functional Description70Reset Functional Description76Timing Parameters77                    |

| Real Time Clock 81                                                                                                                 |

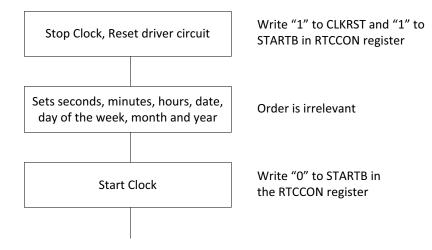

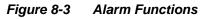

| Features.81Function Description82RTC Operation82                                                                                   |

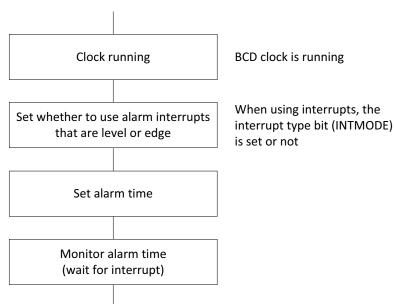

| Low  | Speed SPI                                                                                                                            | 35                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|      | Overview                                                                                                                             | 85<br>85             |

|      | Functional Description      Timing Parameters                                                                                        | 85<br>89             |

| Time | er                                                                                                                                   | 91                   |

|      | Introduction       Features         Features       Functional Description                                                            | 91                   |

| One  | Time Programmable Memory                                                                                                             | 95                   |

|      | Features                                                                                                                             |                      |

| PCI  | Express Interface                                                                                                                    | <del>)</del> 9       |

|      | Introduction       Introduction         Features       Introduction         PCI Express Electrical Specifications       Introduction | 99                   |

| Dual | Core SMP ARM® Cortex®-A9 10                                                                                                          | )5                   |

|      | ARM Cortex-A9 Features10L2 Cache Features10                                                                                          | 05<br>05<br>05<br>06 |

| AXI  | / AHB Cross Connect Fabric 10                                                                                                        | )9                   |

|      |                                                                                                                                      | 09<br>09             |

| DUS  | I Subsystem 11                                                                                                                       | 13                   |

|      | Functional Description                                                                                                               | 13<br>14<br>15<br>17 |

| Deep | Packet Inspection 12                                                                                                                 | 21                   |

|      |                                                                                                                                      | 21<br>21             |

| PPFE (Ethernet Interface) 123          |

|----------------------------------------|

| Introduction 123                       |

| Features 123                           |

| Functional Description                 |

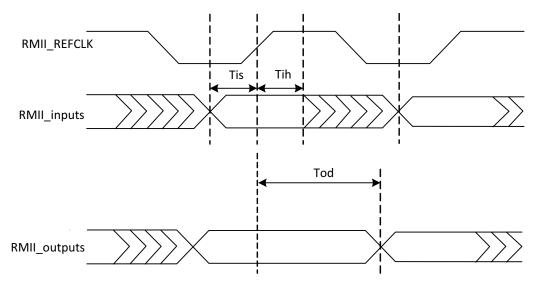

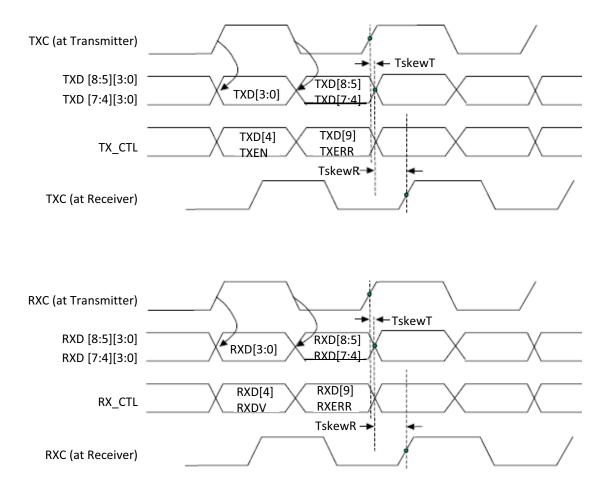

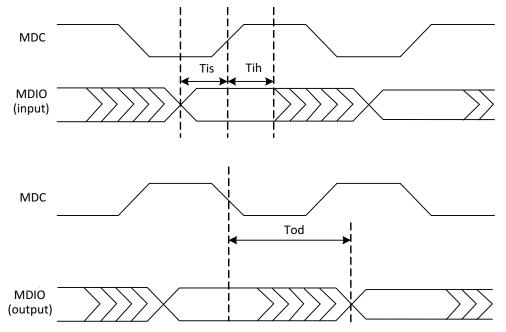

| Ethernet Interface Bus Timing 124      |

| DECT Communication Sub-System 131      |

| Introduction 131                       |

| Features 131                           |

| Timing Parameters 132                  |

| Security Accelerator 133               |

| Overview                               |

| Features                               |

| Functional Description 134             |

| TDM Bus Interface 137                  |

| Overview                               |

| Features                               |

| Functional Description 137             |

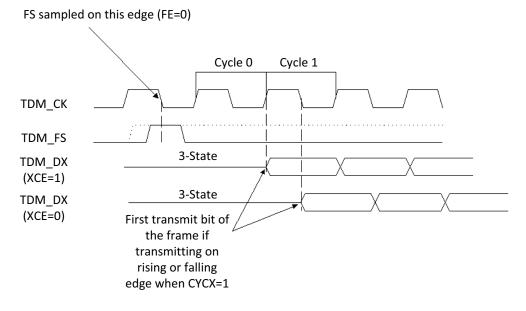

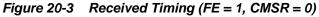

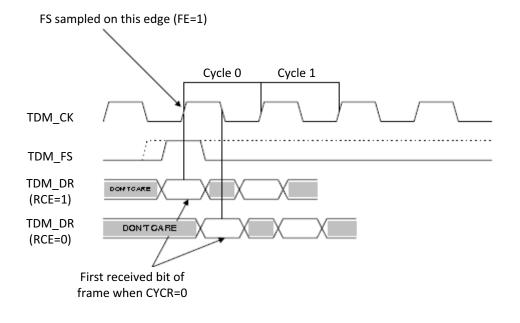

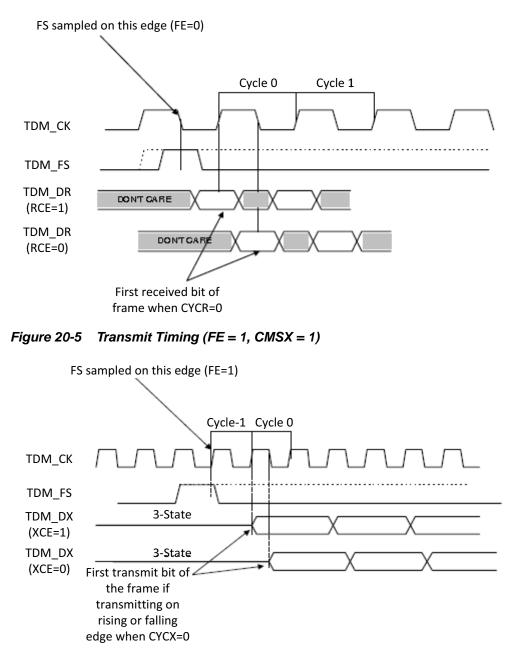

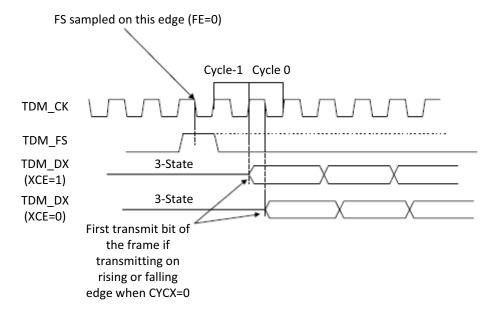

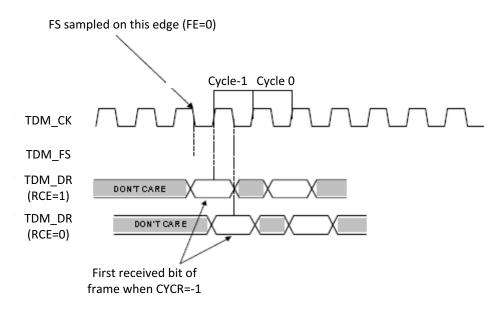

| TDM Bus Interface Timing 138           |

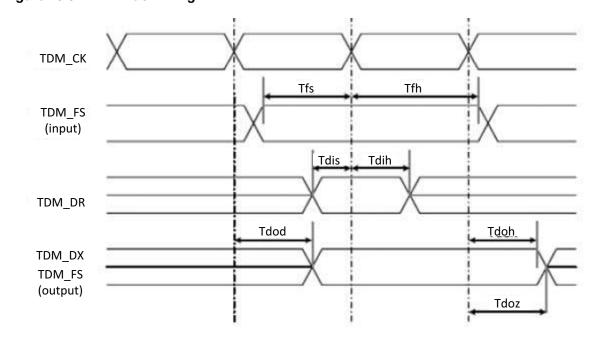

| TDM Interface Timing 142               |

| TDM Loopback Timing 143                |

| Microsemi ZSI Interface 145            |

| Features                               |

| SiLabs Integrated Serial Interface 147 |

| Features 147                           |

| ISI Initialization 147                 |

| SATA Interface 149                     |

| Features                               |

| Functional Description 149             |

| SATA Interface Timing 150              |

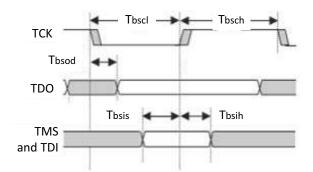

| Joint Test Action Group (JTAG) 153     |

| Introduction 153                       |

| Features 153                           |

| JTAG Muxing Options 153                |

| JTAG ID 154                            |

| Timing Parameters 154                  |

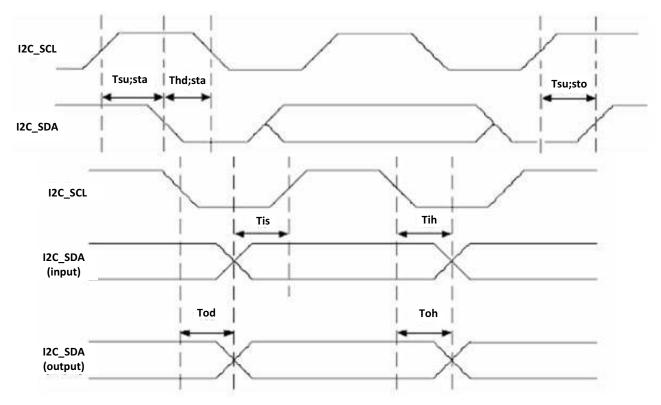

| Inter-IC Interface 155                 |

| Overview                               |

| Features 155                           |

| Functional Description 1                  | 55 |

|-------------------------------------------|----|

| I2C Timing 1                              | 55 |

| High Speed Mode 1                         | 57 |

| Clock Synchronization 1                   | 57 |

| Bus Arbitration 1                         | 57 |

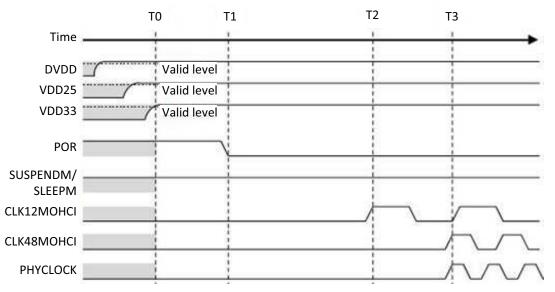

| USB 2.0 Interface 15                      | 59 |

| Introduction 1                            | 59 |

| Features 1                                | 59 |

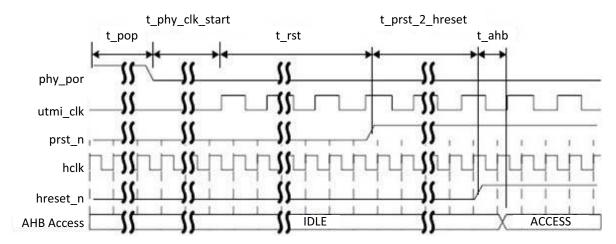

| Reset and Power Up Control Timing 1       | 60 |

| USB 3.0 Interface 10                      | 63 |

| Introduction 1                            | 63 |

| Features 1                                | 63 |

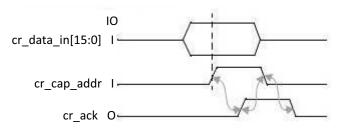

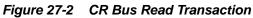

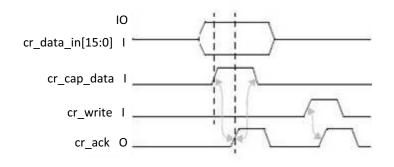

| USB3 PHY Control Register Access 1        | 64 |

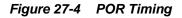

| USB3 PHY POR Timing 1                     | 65 |

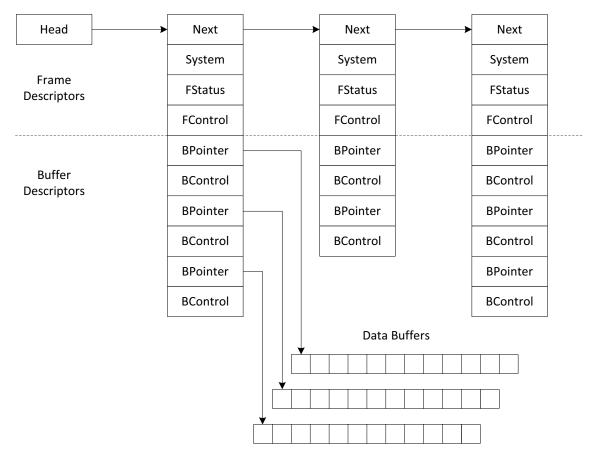

| XOR-DMA Controller 10                     | 67 |

| Features 1                                | 67 |

| DMA Data Structure 1                      | 67 |

| Power Supply 1                            | 69 |

| Operating Conditions 1                    | 70 |

| Absolute Maximum Continuous Ratings 1     | 72 |

| Power Specification 1                     | 72 |

| DC Electrical Characteristics 1           | 73 |

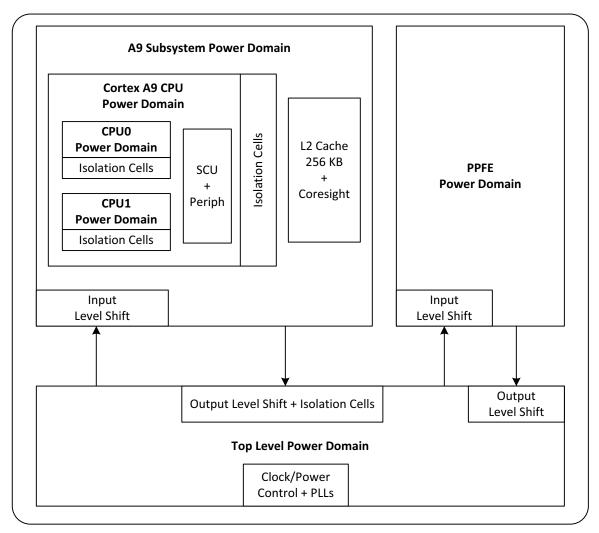

| Power Management 1                        | 75 |

| Power Management Features 1               | 75 |

| Power Management Functional Description 1 | 75 |

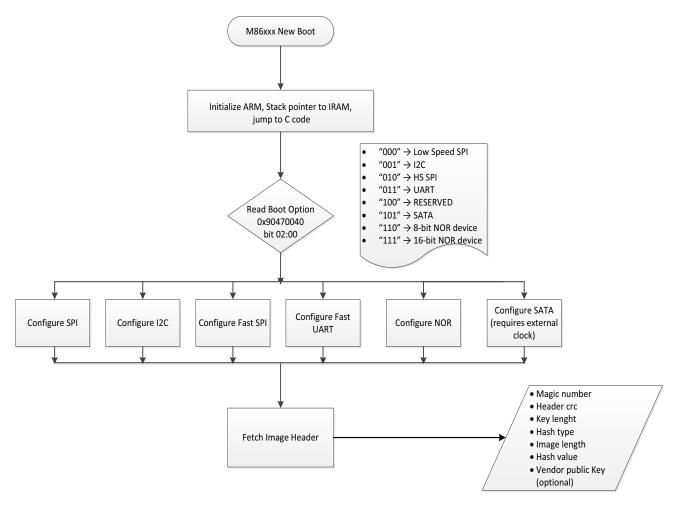

| Hardware Initialization                   | 81 |

| Internal Boot ROM 1                       | 81 |

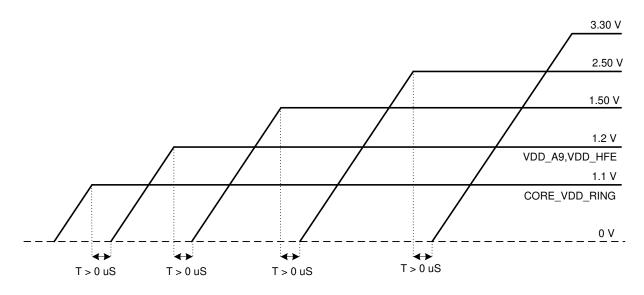

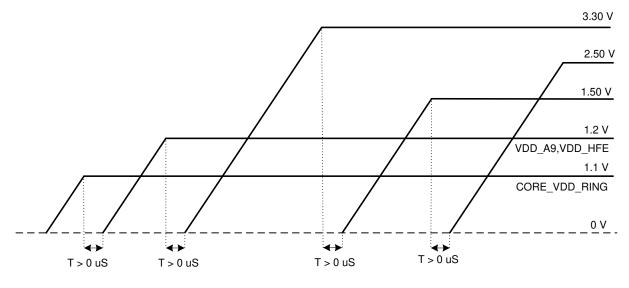

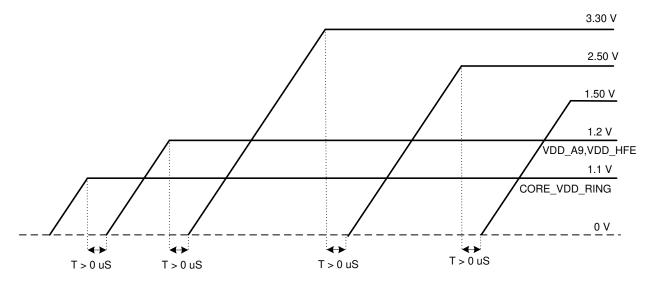

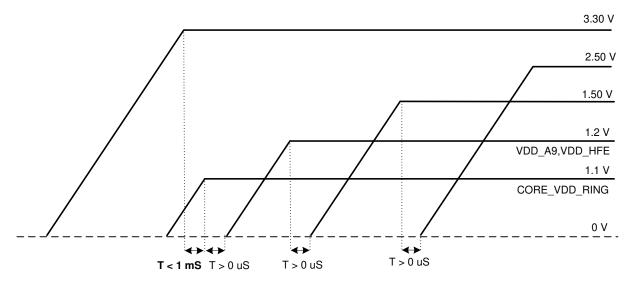

| Power Sequence 1                          | 88 |

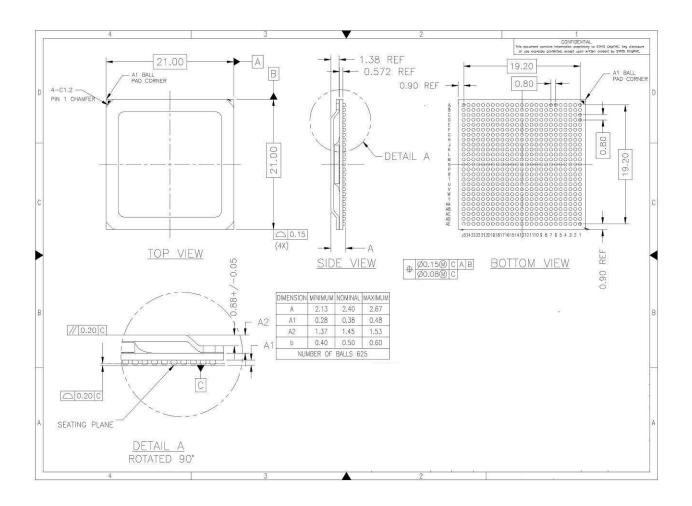

| Package Dimensions 19                     | 91 |

| Ordering Information 19                   | 93 |

#### **Product Applications**

Figure 1-1 LS1024A Block Diagram

# Product Applications

The LS1024A product family addresses a wide variety of applications ranging from high-end VoIP and Video enabled home gateways, Small-to-Midsized business (SMB) high performance security appliances to Ethernet powered 802.11ac Enterprise Access Points and Consumer Networked Storage products.

The LS1024A product family provides ideal solution for:

- SMB IP-PBX / VoIP Gateways

- SOHO and SMB VPN Routers

- VoIP Residential Gateways

- Video Distribution Gateways

- Enterprise WiFi Access Points

- Network Attached Storage .

- SMB VoIP Routers

- Secure Payment Terminals

- Mobile Broadband Routers

#### 1.1 **Features by Device Summary**

The LS1024A devices differ in the number of complex voice channels they support in Data and Voice mode.

#### **Product Applications**

CAUTION:

The device is screened for the specified frequency. Freescale cannot guarantee the operation if any changes are made in software. Any changes without prior approval from Freescale may cause unexpected results and void the warranty.

| Cortex-A9<br>Frequency | Number of Cortex-A9<br>Cores | Device Number | VoIP<br>Channels | DPI | DECT |

|------------------------|------------------------------|---------------|------------------|-----|------|

| 1.2GHz                 | 2                            | LS1024ASN7MLA | 16               | No  | No   |

|                        |                              | LS1024ASE7MLA | 16               | Yes | Yes  |

| 900MHz                 | 2                            | LS1024ASN7JLA | 16               | No  | No   |

|                        |                              | LS1024ASE7JLA | 16               | Yes | Yes  |

| 650MHz                 | 2                            | LS1024ASN7ELA | 8                | No  | No   |

|                        |                              | LS1024ASE7ELA | 8                | No  | Yes  |

Table 1.1Features by Device Summary

**Technical Overview**

# 2 Technical Overview

This section gives an overview of LS1024A device hardware interfaces, functional blocks, and software interfaces.

*CAUTION:* Freescale provides schematic and layout review. However, Freescale highly recommends customers to submit their designs to Freescale for a complete confidential review.

# 2.1 External Interfaces and Functional Blocks

## 2.1.1 External Interfaces

The LS1024A device provides the following external interfaces:

- DDR3 Controller 16/32-bit DDR3 memory interface up to 533MHz (DDR3-1066) with optional ECC support. For more details, refer to Section 5 "DDR3 Controller" on page 61.

- Peripheral Component Interconnect Express (PCIe) Controller The LS1024A device includes two single-lane PCIe interfaces conforming to the PCI Express Base Specification, Revision 2.1 and support Gen1 (2.5Gbps) and Gen2 (5Gbps) link rates. For more details, refer to Section 12 "PCI Express Interface" on page 99.

- Universal Serial Bus (USB) 2.0 Interface USB high speed (480Mbps) controller and PHY with backward compatibility to USB 1.1. For more details. refer to Section 26 "USB 2.0 Interface" on page 159.

- Universal Serial Bus (USB) 3.0 Interface USB super speed controller and PHY with dual-bus architecture to support concurrent USB2.0 (high speed, low speed and full speed) and USB3.0 (SuperSpeed) operations. For more details, refer to Section 27 "USB 3.0 Interface" on page 163.

- Serial Advanced Technology Attachment (SATA Controller) Two (2) 3-Gbps SATA-2 interfaces. For more details, refer to Section 23 "SATA Interface" on page 149.

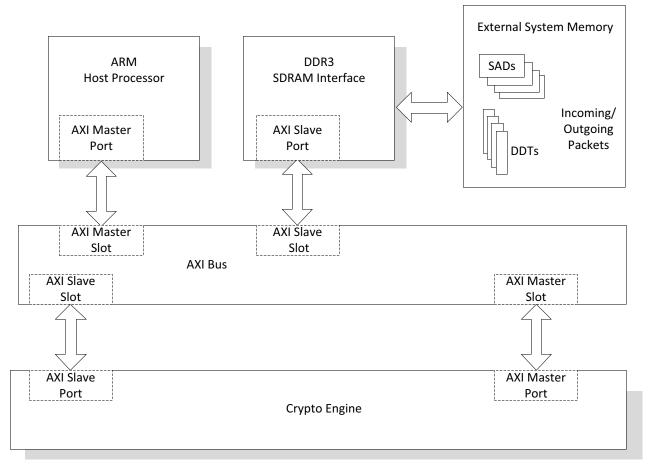

- Time-Division Multiplexing (TDM) Bus Full duplex serial TDM bus supporting up to 128 time slots at 8.192MHz. For more details, refer to Section 20 "TDM Bus Interface" on page 137.

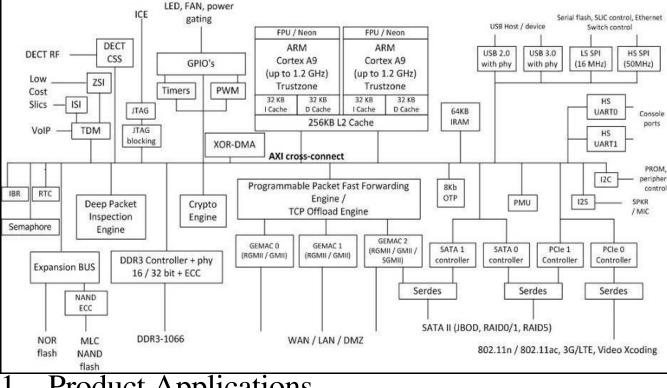

- Expansion Bus Provides address, data, and control lines for connection to system peripheral devices. The Expansion Bus provides chip selects for system peripheral devices such as Flash memory, Boot ROM, and so on. The expansion bus supports 5 chip-selects: one for NAND and four for general purpose. For more details, refer to Section 4 "Expansion Bus Interface" on page 45.

- Inter-IC (I<sup>2</sup>C) Bus Supporting master, slave or multi-master modes. The I<sup>2</sup>C bus can be used for booting. For more details. refer to Section 25 "Inter-IC Interface" on page 155.

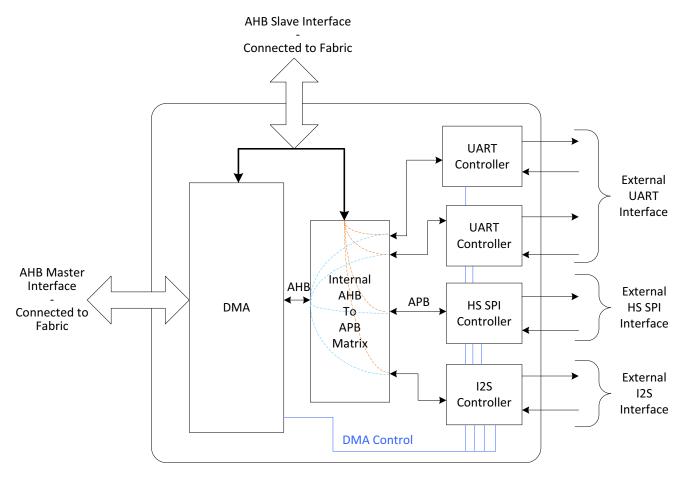

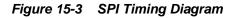

- High-Speed Serial Peripheral Interface (HS-SPI) Up to 50MHz, with 2 slave select. For more details, refer to Section 15 "DUSI Subsystem" on page 113.

- Low Speed Serial Peripheral Interface (LS-SPI) Up to 16MHz, with 3 slave select. The LS-SPI interface can be used for booting. For more details, refer to Section 9 "Low Speed SPI" on page 85.

- General Purpose Input Output (GPIO) Interface Up to 64 GPIOs. Eight (8) of the GPIOS can be configured to receive interrupts. Six (6) of the GPIOs can be pulse-width modulated. For more details, refer to Section 6 "General Purpose Input Output" on page 67.

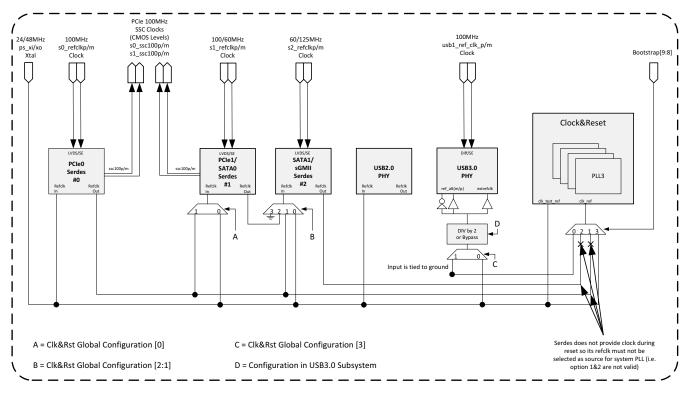

- SerDes Three programmable SerDes interfaces up to 5 Gbps.

- SerDes #0 PCIe0

- SerDes #1 PCIe1 or SATA0 selection through bootstrap

QorIQ LS1024A Data sheet, Rev 0

#### **Technical Overview**

- SerDes #2 SATA1 or SGMII selection through bootstrap

- Silicon Labs Integrated Serial Interface (ISI)— 3-pin interface for reduced cost designs using Silabs SLICs. For more details, refer to Section 22 "SiLabs Integrated Serial Interface" on page 147.

- Microsemi ZSI Interface 4-pin interface for reduced cost designs using Microsemi SLICs. For more details, refer to Section 21 "Microsemi ZSI Interface" on page 145.

- Dual Universal Asynchronous Receiver/Transmitter (UART) With support for RS-232 and flow control. UART0 is Bluetooth capable with frequency up to 3Mbps. For more details, refer to Section 15 "DUSI Subsystem" on page 113.

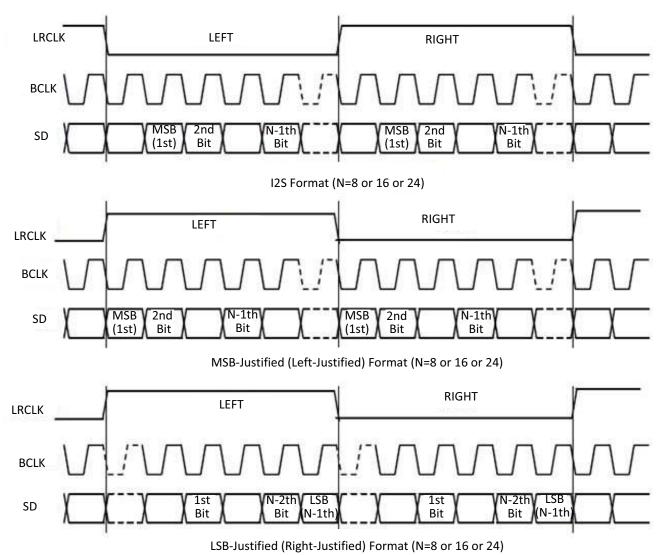

- Inter-IC Sound (I2S) Interface Master or slave, with sampling frequency up to 96kHz and 8/16 or 24 bits per channel. For more details, refer to Section 15 "DUSI Subsystem" on page 113.

- Joint Test Action Group (JTAG) Interface The JTAG interface provides access to both Cortex®-A9 cores. It supports IEEE 1149.1 and boundary scan for manufacturing and test. For more details, refer to Section 24 "Joint Test Action Group (JTAG)" on page 153.

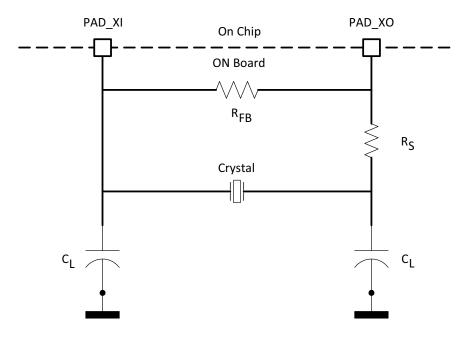

- Reference Clock Using a single oscillator/crystal at 48MHz or 24MHz. For more details, refer to Section 7 "Clock and Reset" on page 69.

### 2.1.2 Functional Blocks

The LS1024A device provides the following functional blocks:

- Dual Core SMP ARM® Cortex®-A9 Up to 1.2GHz, with two Neon® floating point DSPs, ARM Trustzone®, Coresight®, 32kB of I-Cache, 32kB of D-Cache and 256kB of L2 cache. Section 13, Dual Core SMP ARM® Cortex®-A9

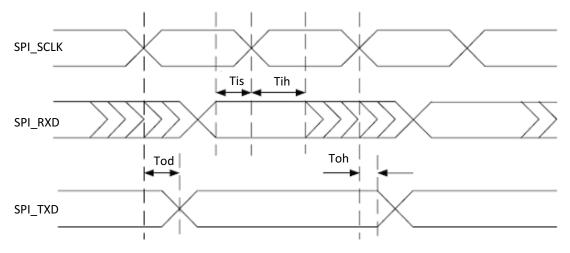

- Hardware Packet Forwarding Engine also knows as Programmable Packet Forwarding Engine (PPFE) Fully

programmable engine for protocol handling, QoS, classification, ingress and egress control, and TCP offload.

For more details, refer to Section 17 "PPFE (Ethernet Interface)" on page 123.

- Deep Packet Inspection (DPI) High performance DPI engine to allow options such as antivirus, content blocking, copyright and policy enforcement and application aware QoS. For more details, refer to Section 16 "Deep Packet Inspection" on page 121.

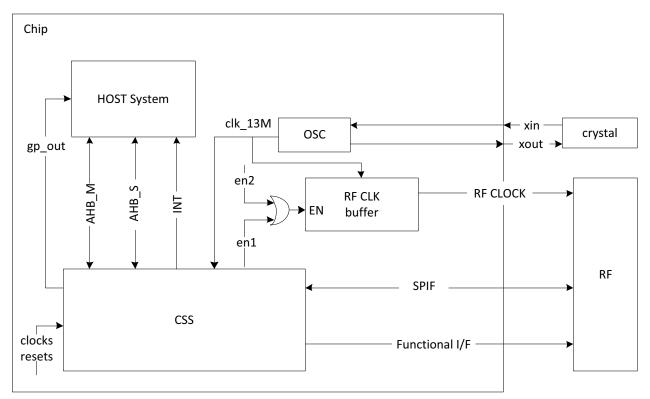

- Security Engines NIST- Certified, integrated hardware crypto engine for IPSEC and SSL/TLS offloads.

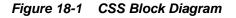

- Communication Sub-System (CSS) DECT digital processor supporting CATiq 2.0, 2.1 and 3.0 and DECT-ULE for home automation. For more details, refer to Section 18 "DECT Communication Sub-System" on page 131.

- Power Management Unit (PMU) Always-on, low power, programmable controller interruptible by PCIe, GMAC, PPFE, USB, SATA, UART, GPIO, timer and SLIC. Manages power states, clock domains and DVFS regulation based on processor load and traffic.Section 30 "Power Management" on page 175.

- XOR-DMA Controller Multi-purpose DMA controller. Processes blocks up to 15 blocks of 4kB. For more details, refer to Section 28 "XOR-DMA Controller" on page 167.

- AXI / AHB Cross Connect Fabric Multi-layer, 64-bit bus with support for ARM Trustzone® and multi-master mode. Section 14, AXI / AHB Cross Connect Fabric.

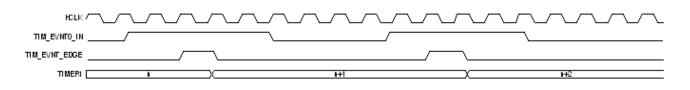

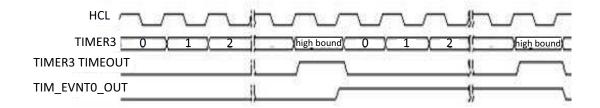

- Timer Block Includes six general purpose interrupt capable timers. Two of the timers connect to I/O pins to drive an external output or allow an external signal to increment the timer. For more details, refer to Section 10 "Timer" on page 91.

- Internal Boot ROM (IBR) 32kB of internal boot ROM with secondary boot from NOR flash, serial flash (SPI), EEPROM (I2C) or SATA. Section 31.1 "Internal Boot ROM" on page 181

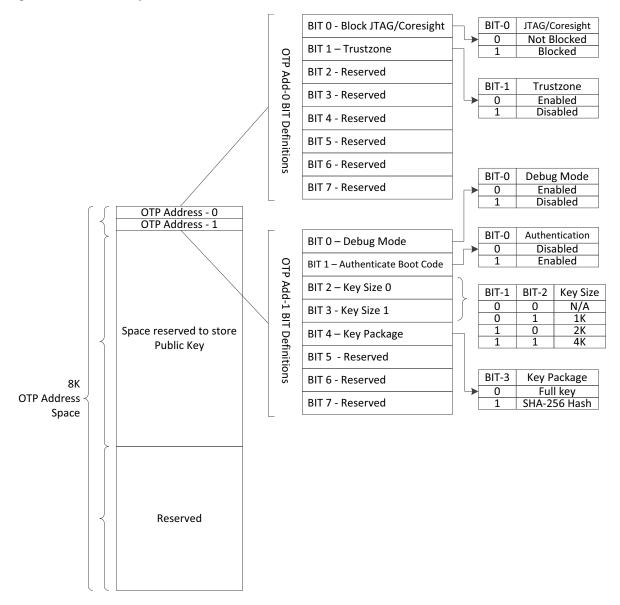

- One Time Programmable Memory (OTPM) High reliability, permanent, 8KBits memory for secure key or certificate storage. Section 11 "One Time Programmable Memory" on page 95.

- Internal SRAM (IRAM) 64kBytes.

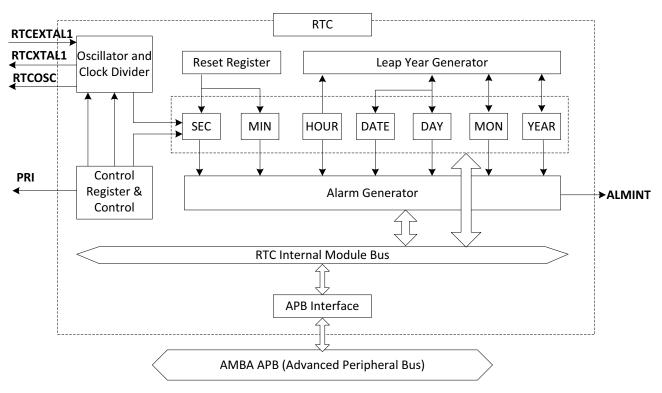

- Real Time Clock (RTC) Battery operated, running from a 32.768 kHz crystal. Section 8, Real Time Clock

- Hardware Semaphore

#### **Technical Overview**

This chapter gives a list of pinouts and a summary of device signal tables and its description.

# 3.1 Ball Map

Figure 3-1 illustrates the ball map (looking through the top of the package). Table 3-1 shows the ball name and location of the pins.

Figure 3-1 LS1024A Ball Map

#### Table 3-1LS1024A Pinout List

| Location | Signal Symbol  | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|----------------|-----------|--------|----------|-------|----------|

| Al       | VSS_RING       |           |        |          |       |          |

| A2       | VSS_RING       |           |        |          |       |          |

| A3       | S0_CK_100P     | 0         |        | 1.1 V    |       |          |

| A4       | S0_CK_100M     | 0         |        | 1.1 V    |       |          |

| A5       | PS_XI          | Ι         | OSCL   | 3.3 V    |       |          |

| A6       | SPI_2_SS0_N    | 0         | LVCMOS | 3.3 V    |       | 11 mA    |

| A7       | VSS_RING       |           |        |          |       |          |

| A8       | USB0_DVSS      |           |        |          |       |          |

| A9       | USB0_DP        | I/O       | ANLG   |          |       |          |

| A10      | USB0_VSSA      |           |        |          |       |          |

| A11      | USB1_RX_P      | Ι         |        |          |       |          |

| A12      | VSS_RING       |           |        |          |       |          |

| A13      | USB1_TX_P      | 0         |        |          |       |          |

| A14      | USB1_DP        | I/O       | ANLG   |          |       |          |

| A15      | DDR_ECC_DATA_7 | I/O       | SSTL   |          |       |          |

| A16      | DDR_ECC_DATA_4 | I/O       | SSTL   |          |       |          |

| A17      | DDR_ECC_DATA_3 | I/O       | SSTL   |          |       |          |

| A18      | DDR_DATA_31    | I/O       | SSTL   |          |       |          |

| A19      | DDR_DATA_28    | I/O       | SSTL   |          |       |          |

| A20      | DDR_DATA_27    | I/O       | SSTL   |          |       |          |

| A21      | DDR_DM_2       | 0         | SSTL   |          |       |          |

| A22      | DDR_DATA_16    | I/O       | SSTL   |          |       |          |

| A23      | DDR_DATA_21    | I/O       | SSTL   |          |       |          |

| A24      | VSS_RING       |           |        |          |       |          |

| A25      | VSS_RING       |           |        |          |       |          |

| B1       | VSS_RING       |           |        |          |       |          |

| B2       | VSS_RING       |           |        |          |       |          |

#### QorlQ LS1024A Data sheet, Rev 0

| Location | Signal Symbol   | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|-----------------|-----------|--------|----------|-------|----------|

| B3       | S1_CK_100P      | 0         |        | 1.1 V    |       |          |

| B4       | S1_CK_100M      | 0         |        | 1.1 V    |       |          |

| B5       | PS_XO           | 0         | OSCL   | 3.3 V    |       |          |

| B6       | SPI_2_SS1_N     | 0         | LVCMOS | 3.3 V    |       | 11 mA    |

| B7       | VSS_RING        |           |        |          |       |          |

| B8       | TM_TESTMODE_N_1 | I         | LVCMOS | 3.3 V    | PU    |          |

| B9       | USB0_DM         | I/O       | ANLG   |          |       |          |

| B10      | USB0_VSSAC      |           |        |          |       |          |

| B11      | USB1_RX_M       | Ι         |        |          |       |          |

| B12      | VSS_RING        |           |        |          |       |          |

| B13      | USB1_TX_M       | 0         |        |          |       |          |

| B14      | USB1_DM         | I/O       | ANLG   |          |       |          |

| B15      | DDR_ZQ          | 0         | SSTL   |          |       |          |

| B16      | DDR_ECC_DATA_6  | I/O       | SSTL   |          |       |          |

| B17      | DDR_ECC_DATA_2  | I/O       | SSTL   |          |       |          |

| B18      | DDR_VDDQ        |           |        |          |       |          |

| B19      | DDR_DATA_30     | I/O       | SSTL   |          |       |          |

| B20      | DDR_DATA_26     | I/O       | SSTL   |          |       |          |

| B21      | DDR_VDDQ        |           |        |          |       |          |

| B22      | DDR_DATA_18     | I/O       | SSTL   |          |       |          |

| B23      | DDR_DATA_22     | I/O       | SSTL   |          |       |          |

| B24      | DDR_BA_0        | 0         | SSTL   |          |       |          |

| B25      | VSS_RING        |           |        |          |       |          |

| C1       | S0_RXP          | Ι         | ANLG   |          |       |          |

| C2       | S0_RXM          | Ι         | ANLG   |          |       |          |

| C3       | VSS_RING        |           |        |          |       |          |

| C4       | TM_TESTMODE_N_2 | I         | LVCMOS | 3.3 V    | PU    |          |

| C5       | GPIO00          | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| C6       | SPI_2_TXD       | 0         | LVCMOS | 3.3 V    |       | 11 mA    |

| C7       | VSS_RING        |           |        |          |       |          |

| C8       | VSS_RING        |           |        |          |       |          |

| C9       | USB0_VDD33      |           |        |          |       |          |

| C10      | UP_XI           | I         | OSCL   | 3.3 V    |       |          |

| C11      | USB0_REXT       | I/O       | ANLG   |          |       |          |

| C12      | USB1_RESREF     | I/O       | ANLG   |          |       |          |

| C13      | VSS_RING        |           |        |          |       |          |

| Location | Signal Symbol   | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|-----------------|-----------|--------|----------|-------|----------|

|          |                 | Direction | TJPC   | Torrait  | 10/10 | Sungui   |

| C14      | VSS_RING        |           |        |          |       |          |

| C15      | DDR_VDDQZQ      |           |        |          |       |          |

| C16      | DDR_ECC_DATA_5  | I/O       | SSTL   |          |       |          |

| C17      | DDR_ECC_DM      | 0         | SSTL   |          |       |          |

| C18      | VSS_RING        |           |        |          |       |          |

| C19      | DDR_DATA_29     | I/O       | SSTL   |          |       |          |

| C20      | DDR_DM_3        | 0         | SSTL   |          |       |          |

| C21      | VSS_RING        |           |        |          |       |          |

| C22      | DDR_DATA_19     | I/O       | SSTL   |          |       |          |

| C23      | DDR_DATA_20     | I/O       | SSTL   |          |       |          |

| C24      | DDR_BA_2        | 0         | SSTL   |          |       |          |

| C25      | DDR_BA_1        | 0         | SSTL   |          |       |          |

| D1       | S0_TXM          | 0         | ANLG   |          |       |          |

| D2       | S0_TXP          | 0         | ANLG   |          |       |          |

| D3       | VSS_RING        |           |        |          |       |          |

| D4       | GPIO07          | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| D5       | SPI_2_RXD       | Ι         | LVCMOS | 3.3 V    | PD    |          |

| D6       | SPI_2_SCLK      | 0         | LVCMOS | 3.3 V    |       | 11 mA    |

| D7       | TM_TESTMODE_N_0 | Ι         | LVCMOS | 3.3 V    | PU    |          |

| D8       | PLL3_FILTER     | Ι         | ANLG   | 3.3 V    |       |          |

| D9       | USB0_VBUS       | Ι         | ANLG   | 5 V      |       |          |

| D10      | UP_XO           | 0         | OSCL   | 3.3 V    |       |          |

| D11      | VSS_RING        |           |        |          |       |          |

| D12      | USB1_REF_CLK_M  | Ι         | ANLG   |          |       |          |

| D13      | USB1_REF_CLK_P  | Ι         | ANLG   |          |       |          |

| D14      | USB1_VBUS       | I/O       | ANLG   | 5 V      |       |          |

| D15      | DDR_VSSQZQ      |           |        |          |       |          |

| D16      | DDR_ECC_DATA_1  | I/O       | SSTL   |          |       |          |

| D17      | DDR_ECC_DATA_0  | I/O       | SSTL   |          |       |          |

| D18      | DDR_VDDQ        |           |        |          |       |          |

| D19      | DDR_DATA_25     | I/O       | SSTL   |          |       |          |

| D20      | DDR_DATA_24     | I/O       | SSTL   |          |       |          |

| D21      | DDR_VDDQ        |           |        |          |       |          |

| D22      | DDR_DATA_17     | I/O       | SSTL   |          |       |          |

| D23      | DDR_DATA_23     | I/O       | SSTL   |          |       |          |

| D24      | DDR_A_11        | 0         | SSTL   |          |       |          |

#### Table 3-1LS1024A Pinout List (continued)

QorIQ LS1024A Data sheet, Rev 0

| Location | Signal Symbol    | Direction | Туре   | Tolerant | PU/PD | Strengtl |

|----------|------------------|-----------|--------|----------|-------|----------|

| D25      | DDR_A_14         | 0         | SSTL   |          |       |          |

| E1       | S0_REFCLKP       | I         | ANLG   |          |       |          |

| E2       | S0_REFCLKM       | I         | ANLG   |          |       |          |

| E3       | VSS_RING         |           |        |          |       |          |

| E4       | GPIO06           | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| E5       | TM_LEGACY_MODE_N | I         | LVCMOS | 3.3 V    | PU    |          |

| E6       | IO_VDD_RING      |           |        |          |       |          |

| E7       | VSS_RING         |           |        |          |       |          |

| E8       | VSS_RING         |           |        |          |       |          |

| E9       | VSS_RING         |           |        |          |       |          |

| E10      | USB0_VDD33       |           |        |          |       |          |

| E11      | USB0_ATEST       | I/O       | ANLG   |          |       |          |

| E12      | UPOSC_DVDD       |           |        |          |       |          |

| E13      | VSS_RING         |           |        |          |       |          |

| E14      | VSS_RING         |           |        |          |       |          |

| E15      | VSS_RING         |           |        |          |       |          |

| E16      | DDR_ECC_DQS_N    | I/O       | SSTL   |          |       |          |

| E17      | DDR_ECC_DQS      | I/O       | SSTL   |          |       |          |

| E18      | VSS_RING         |           |        |          |       |          |

| E19      | DDR_DQS_N_3      | I/O       | SSTL   |          |       |          |

| E20      | DDR_DQS_3        | I/O       | SSTL   |          |       |          |

| E21      | VSS_RING         |           |        |          |       |          |

| E22      | DDR_DQS_N_2      | I/O       | SSTL   |          |       |          |

| E23      | DDR_DQS_2        | I/O       | SSTL   |          |       |          |

| E24      | VSS_RING         |           |        |          |       |          |

| E25      | DDR_A_12         | 0         | SSTL   |          |       |          |

| F1       | VSS_RING         |           |        |          |       |          |

| F2       | VSS_RING         |           |        |          |       |          |

| F3       | VSS_RING         |           |        |          |       |          |

| F4       | GPIO14           | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| F5       | IO_VDD_RING      |           |        |          |       |          |

| F6       | PCIE1_CLKO       | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| F7       | PLL0_AVDD        |           |        |          |       |          |

| F8       | PLL3_AVSS        |           |        |          |       |          |

| F9       | PLL3_AVDD        |           |        |          |       |          |

| F10      | USB0_DVDD        |           |        |          |       |          |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| F11      | CORE_VDD_RING |           |        |          |       |          |

| F12      | USB1_ID       | I/O       | ANLG   |          |       |          |

| F13      | CORE_VDD_RING |           |        |          |       |          |

| F14      | VSS_RING      |           |        |          |       |          |

| F15      | E_DVDD        |           |        |          |       |          |

| F16      | DDR_VDDQ      |           |        |          |       |          |

| F17      | VSS_RING      |           |        |          |       |          |

| F18      | DDR_VDDQ      |           |        |          |       |          |

| F19      | DDR_VDDQ      |           |        |          |       |          |

| F20      | VSS_RING      |           |        |          |       |          |

| F21      | DDR_VDDQ      |           |        |          |       |          |

| F22      | DDR_VDDQ      |           |        |          |       |          |

| F23      | DDR_CKE       | 0         | SSTL   |          | PD    |          |

| F24      | DDR_ODT_1     | 0         | SSTL   |          |       |          |

| F25      | DDR_A_13      | 0         | SSTL   |          |       |          |

| G1       | S1_RXP        | I         | ANLG   |          |       |          |

| G2       | S1_RXM        | I         | ANLG   |          |       |          |

| G3       | VSS_RING      |           |        |          |       |          |

| G4       | PSOSC_DVDD    |           |        |          |       |          |

| G5       | VSS_RING      |           |        |          |       |          |

| G6       | PCIE0_CLKO    | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| G7       | PLL0_AVSS     |           |        |          |       |          |

| G8       | FSOURCE_ECID  | I/O       | PWR    |          |       |          |

| G9       | CORE_VDD_RING |           |        |          |       |          |

| G10      | CORE_VDD_RING |           |        |          |       |          |

| G11      | CORE_VDD_RING |           |        |          |       |          |

| G12      | VSS_RING      |           |        |          |       |          |

| G13      | CORE_VDD_RING |           |        |          |       |          |

| G14      | VSS_RING      |           |        |          |       |          |

| G15      | DDR_VDDQ      |           |        |          |       |          |

| G16      | VSS_RING      |           |        |          |       |          |

| G17      | DDR_VDDQ      |           |        |          |       |          |

| G18      | VSS_RING      |           |        |          |       |          |

| G19      | DDR_VREF_RING |           |        |          |       |          |

| G20      | DDR_VDDQ      |           |        |          |       |          |

| G21      | VSS_RING      |           |        |          |       |          |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| G22      | DDR_A_2       | 0         | SSTL   |          |       |          |

| G23      | DDR_A_9       | 0         | SSTL   |          |       |          |

| G24      | DDR_A_8       | 0         | SSTL   |          |       |          |

| G25      | DDR_ODT_0     | 0         | SSTL   |          |       |          |

| H1       | S1_TXM        | 0         | ANLG   |          |       |          |

| H2       | S1_TXP        | 0         | ANLG   |          |       |          |

| H3       | VSS_RING      |           |        |          |       |          |

| H4       | GPIO15        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| Н5       | VSS_RING      |           |        |          |       |          |

| H6       | S0_ATEST      | 0         | ANLG   |          |       |          |

| H7       | PLL1_AVSS     |           |        |          |       |          |

| H8       | PLL1_AVDD     |           |        |          |       |          |

| H9       | CORE_VDD_RING |           |        |          |       |          |

| H10      | CORE_VDD_RING |           |        |          |       |          |

| H11      | CORE_VDD_RING |           |        |          |       |          |

| H12      | USB3_VDD_RING |           |        |          |       |          |

| H13      | CORE_VDD_RING |           |        |          |       |          |

| H14      | VSS_RING      |           |        |          |       |          |

| H15      | DDR_VDDQ      |           |        |          |       |          |

| H16      | VSS_RING      |           |        |          |       |          |

| H17      | DDR_VDDQ      |           |        |          |       |          |

| H18      | CORE_VDD_RING |           |        |          |       |          |

| H19      | CORE_VDD_RING |           |        |          |       |          |

| H20      | VSS_RING      |           |        |          |       |          |

| H21      | DDR_VDDQ      |           |        |          |       |          |

| H22      | DDR_A_4       | 0         | SSTL   |          |       |          |

| H23      | DDR_A_5       | 0         | SSTL   |          |       |          |

| H24      | DDR_A_6       | 0         | SSTL   |          |       |          |

| H25      | DDR_A_7       | 0         | SSTL   |          |       |          |

| J1       | S1_REFCLKP    | I         | ANLG   |          |       |          |

| J2       | S1_REFCLKM    | I         | ANLG   |          |       |          |

| J3       | VSS_RING      |           |        |          |       |          |

| J4       | S0_RESREF     | I/O       | ANLG   |          |       |          |

| J5       | VSS_RING      |           |        |          |       |          |

| J6       | S1_ATEST      | 0         | ANLG   |          |       |          |

| J7       | PLL2_AVSS     |           |        |          |       |          |

|          |               | -         | T      |          |       | G( (1    |

|----------|---------------|-----------|--------|----------|-------|----------|

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

| J8       | PLL2_AVDD     |           |        |          |       |          |

| J9       | IO_VDD_RING   |           |        |          |       |          |

| J10      | CORE_VDD_RING |           |        |          |       |          |

| J11      | VP            |           |        |          |       |          |

| J12      | USB3_VDD_RING |           |        |          |       |          |

| J13      | CORE_VDD_RING |           |        |          |       |          |

| J14      | VSS_RING      |           |        |          |       |          |

| J15      | DDR_VDDQ      |           |        |          |       |          |

| J16      | VSS_RING      |           |        |          |       |          |

| J17      | DDR_VDDQ      |           |        |          |       |          |

| J18      | CORESIGHT_D15 | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| J19      | CORESIGHT_D14 | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| J20      | DDR_VDDQ      |           |        |          |       |          |

| J21      | VSS_RING      |           |        |          |       |          |

| J22      | DDR_CS_N_0    | 0         | SSTL   |          |       |          |

| J23      | DDR_A_0       | 0         | SSTL   |          |       |          |

| J24      | DDR_A_1       | 0         | SSTL   |          |       |          |

| J25      | DDR_A_3       | 0         | SSTL   |          |       |          |

| K1       | S2_TXM        | 0         | ANLG   |          |       |          |

| K2       | S2_TXP        | 0         | ANLG   |          |       |          |

| К3       | S2_REFCLKM    | I         | ANLG   |          |       |          |

| K4       | S1_RESREF     | I/O       | ANLG   |          |       |          |

| K5       | VSS_RING      |           |        |          |       |          |

| K6       | S2_ATEST      | 0         | ANLG   |          |       |          |

| K7       | S0_VDDT_0     |           |        |          |       |          |

| K8       | S0_VDDA       |           |        |          |       |          |

| К9       | S0_VDDHA      |           |        |          |       |          |

| K10      | CORE_VDD_RING |           |        |          |       |          |

| K11      | VPTX0         |           |        |          |       |          |

| K12      | DVDD          |           |        |          |       |          |

| K13      | CORE_VDD_RING |           |        |          |       |          |

| K14      | VSS_RING      |           |        |          |       |          |

| K15      | DDR_VDDQ      |           |        |          |       |          |

| K16      | VSS_RING      |           |        |          |       |          |

| K17      | <br>DDR_VDDQ  |           |        |          |       |          |

| K18      | CORESIGHT_D13 | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| K19      | CORESIGHT_D12 | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| K20      | VSS_RING      |           |        |          |       |          |

| K21      | DDR_VDDQ      |           |        |          |       |          |

| K22      | DDR_GATE_I    | I         | SSTL   |          |       |          |

| K23      | DDR_GATE_O    | 0         | SSTL   |          |       |          |

| K24      | DDR_CLK_1     | 0         | SSTL   |          |       |          |

| K25      | DDR_CLK_N_1   | 0         | SSTL   |          |       |          |

| L1       | S2_RXP        | I         | ANLG   |          |       |          |

| L2       | S2_RXM        | I         | ANLG   |          |       |          |

| L3       | S2_REFCLKP    | I         | ANLG   |          |       |          |

| L4       | S2_RESREF     | I/O       | ANLG   |          |       |          |

| L5       | VSS_RING      |           |        |          |       |          |

| L6       | VSS_RING      |           |        |          |       |          |

| L7       | S1_VDDT_0     |           |        |          |       |          |

| L8       | S1_VDDA       |           |        |          |       |          |

| L9       | S1_VDDHA      |           |        |          |       |          |

| L10      | VSS_RING      |           |        |          |       |          |

| L11      | CORE_VDD_RING |           |        |          |       |          |

| L12      | CORE_VDD_RING |           |        |          |       |          |

| L13      | CORE_VDD_RING |           |        |          |       |          |

| L14      | VSS_RING      |           |        |          |       |          |

| L15      | DDR_VDDQ      |           |        |          |       |          |

| L16      | DDR_VDDQ      |           |        |          |       |          |

| L17      | DDR_VDDQ      |           |        |          |       |          |

| L18      | CORE_VDD_RING |           |        |          |       |          |

| L19      | CORE_VDD_RING |           |        |          |       |          |

| L20      | DDR_VDDQ      |           |        |          |       |          |

| L21      | VSS_RING      |           |        |          |       |          |

| L22      | DDR_CS_N_1    | 0         | SSTL   |          |       |          |

| L23      | DDR_WE_N      | 0         | SSTL   |          |       |          |

| L24      | DDR_CLK_0     | 0         | SSTL   |          |       |          |

| L25      | DDR_CLK_N_0   | 0         | SSTL   |          |       |          |

| M1       | VSS_RING      |           |        |          |       |          |

| M2       | VSS_RING      |           |        |          |       |          |

| M3       | VSS_RING      |           |        |          |       |          |

| M4       | GEM0_REFCLK   | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| able J-I | Lo 1024A l'induit List (continueu) |           |        |          |       |          |  |

|----------|------------------------------------|-----------|--------|----------|-------|----------|--|

| Location | Signal Symbol                      | Direction | Туре   | Tolerant | PU/PD | Strength |  |

| M5       | VSS_RING                           |           |        |          |       |          |  |

| M6       | VSS_RING                           |           |        |          |       |          |  |

| M7       | S2_VDDT_0                          |           |        |          |       |          |  |

| M8       | S2_VDDA                            |           |        |          |       |          |  |

| M9       | S2_VDDHA                           |           |        |          |       |          |  |

| M10      | VSS_RING                           |           |        |          |       |          |  |

| M11      | CORE_VDD_RING                      |           |        |          |       |          |  |

| M12      | CORE_VDD_RING                      |           |        |          |       |          |  |

| M13      | CORE_VDD_RING                      |           |        |          |       |          |  |

| M14      | CORE_VDD_RING                      |           |        |          |       |          |  |

| M15      | DDR_VDDQ                           |           |        |          |       |          |  |

| M16      | DDR_VDDQ                           |           |        |          |       |          |  |

| M17      | DDR_VDDQ                           |           |        |          |       |          |  |

| M18      | CORESIGHT_D10                      | 0         | LVCMOS | 3.3 V    |       | 28 mA    |  |

| M19      | CORESIGHT_D11                      | 0         | LVCMOS | 3.3 V    |       | 28 mA    |  |

| M20      | VSS_RING                           |           |        |          |       |          |  |

| M21      | DDR_VDDQ                           |           |        |          |       |          |  |

| M22      | DDR_RESET_N                        | 0         |        |          |       |          |  |

| M23      | DDR_CAS_N                          | 0         | SSTL   |          |       |          |  |

| M24      | DDR_A_10                           | 0         | SSTL   |          |       |          |  |

| M25      | DDR_RAS_N                          | 0         | SSTL   |          |       |          |  |

| N1       | GEM0_RXC                           | Ι         |        | 3.3 V    |       | 17 mA    |  |

| N2       | GEM0_RX_CTL                        | Ι         |        | 3.3 V    |       | 17 mA    |  |

| N3       | GEM0_RXD_3                         | Ι         |        | 3.3 V    |       | 17 mA    |  |

| N4       | GEM0_RXD_2                         | Ι         |        | 3.3 V    |       | 17 mA    |  |

| N5       | GEM0_RXD_1                         | Ι         |        | 3.3 V    |       | 17 mA    |  |

| N6       | VSS_RING                           |           |        |          |       |          |  |

| N7       | GEM0_DVDD                          |           |        |          |       |          |  |

| N8       | GEM0_DVDD                          |           |        |          |       |          |  |

| N9       | GEM0_DVDD                          |           |        |          |       |          |  |

| N10      | VDD_HFE                            |           |        |          |       |          |  |

| N11      | VDD_HFE                            |           |        |          |       |          |  |

| N12      | VDD_HFE                            |           |        |          |       |          |  |

| N13      | VDD_A9                             |           |        |          |       |          |  |

| N14      | VSS_RING                           |           |        |          |       |          |  |

| N15      | DDR_VDDQ                           |           |        |          |       |          |  |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| N16      | VSS_RING      |           |        |          |       |          |

| N17      | DDR_VDDQ      |           |        |          |       |          |

| N18      | CORESIGHT_D8  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| N19      | CORESIGHT_D9  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| N20      | DDR_VDDQ      |           |        |          |       |          |

| N21      | VSS_RING      |           |        |          |       |          |

| N22      | DDR_VDDQ      |           |        |          |       |          |

| N23      | VSS_RING      |           |        |          |       |          |

| N24      | DDR_VDDQ      |           |        |          |       |          |

| N25      | DDR_DATA_8    | I/O       | SSTL   |          |       |          |

| P1       | GEM0_RXD_0    | Ι         |        | 3.3 V    |       | 17 mA    |

| P2       | GEM0_TXC      | 0         |        | 3.3 V    |       | 17 mA    |

| P3       | GEM0_TX_CTL   | 0         |        | 3.3 V    |       | 17 mA    |

| P4       | GEM0_TXD_3    | 0         |        | 3.3 V    |       | 17 mA    |

| P5       | GEM0_TXD_2    | 0         |        | 3.3 V    |       | 17 mA    |

| P6       | VSS_RING      |           |        |          |       |          |

| P7       | GEM1_DVDD     |           |        |          |       |          |

| P8       | GEM0_DVDD     |           |        |          |       |          |

| Р9       | GEM0_DVDD     |           |        |          |       |          |

| P10      | VDD_HFE       |           |        |          |       |          |

| P11      | VDD_HFE       |           |        |          |       |          |

| P12      | VDD_HFE       |           |        |          |       |          |

| P13      | VDD_A9        |           |        |          |       |          |

| P14      | VSS_RING      |           |        |          |       |          |

| P15      | VDD_A9        |           |        |          |       |          |

| P16      | VSS_RING      |           |        |          |       |          |

| P17      | DDR_VDDQ      |           |        |          |       |          |

| P18      | VSS_RING      |           |        |          |       |          |

| P19      | VSS_RING      |           |        |          |       |          |

| P20      | VSS_RING      |           |        |          |       |          |

| P21      | DDR_DQS_1     | I/O       | SSTL   |          |       |          |

| P22      | DDR_DATA_9    | I/O       | SSTL   |          |       |          |

| P23      | DDR_DATA_11   | I/O       | SSTL   |          |       |          |

| P24      | DDR_DATA_10   | I/O       | SSTL   |          |       |          |

| P25      | DDR_DM_1      | 0         | SSTL   |          |       |          |

| R1       | GEM0_TXD_1    | 0         |        | 3.3 V    |       | 17 mA    |

#### Table 3-1 LS1024A Pinout List (continued)

QorIQ LS1024A Data sheet, Rev 0

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |  |  |

|----------|---------------|-----------|--------|----------|-------|----------|--|--|

| R2       | GEM0_TXD_0    | 0         |        | 3.3 V    |       | 17 mA    |  |  |

| R3       | VSS_RING      |           |        |          |       |          |  |  |

| R4       | VSS_RING      |           |        |          |       |          |  |  |

| R5       | VSS_RING      |           |        |          |       |          |  |  |

| R6       | VSS_RING      |           |        |          |       |          |  |  |

| R7       | GEM1_DVDD     |           |        |          |       |          |  |  |

| R8       | GEM1_DVDD     |           |        |          |       |          |  |  |

| R9       | GEM1_DVDD     |           |        |          |       |          |  |  |

| R10      | VDD_HFE       |           |        |          |       |          |  |  |

| R11      | VDD_A9        |           |        |          |       |          |  |  |

| R12      | VDD_HFE       |           |        |          |       |          |  |  |

| R13      | VDD_A9        |           |        |          |       |          |  |  |

| R14      | VSS_RING      |           |        |          |       |          |  |  |

| R15      | VDD_A9        |           |        |          |       |          |  |  |

| R16      | VSS_RING      |           |        |          |       |          |  |  |

| R17      | DDR_VDDQ      |           |        |          |       |          |  |  |

| R18      | CORESIGHT_D6  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |  |  |

| R19      | CORESIGHT_D7  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |  |  |

| R20      | DDR_VDDQ      |           |        |          |       |          |  |  |

| R21      | DDR_DQS_N_1   | I/O       | SSTL   |          |       |          |  |  |

| R22      | DDR_DATA_15   | I/O       | SSTL   |          |       |          |  |  |

| R23      | DDR_DATA_12   | I/O       | SSTL   |          |       |          |  |  |

| R24      | DDR_DATA_14   | I/O       | SSTL   |          |       |          |  |  |

| R25      | DDR_DATA_13   | I/O       | SSTL   |          |       |          |  |  |

| T1       | GEM1_RXC      | Ι         |        | 3.3 V    |       | 17 mA    |  |  |

| T2       | GEM1_RX_CTL   | I         |        | 3.3 V    |       | 17 mA    |  |  |

| T3       | GEM1_RXD_3    | I         |        | 3.3 V    |       | 17 mA    |  |  |

| T4       | GEM1_RXD_2    | I         |        | 3.3 V    |       | 17 mA    |  |  |

| T5       | GEM1_REFCLK   | 0         | LVCMOS | 3.3 V    |       | 8 mA     |  |  |

| T6       | VSS_RING      |           |        |          |       |          |  |  |

| T7       | GEM2_DVDD     |           |        |          |       |          |  |  |

| T8       | GEM2_DVDD     |           |        |          |       |          |  |  |

| T9       | GEM2_DVDD     |           |        |          |       |          |  |  |

| T10      | VDD_HFE       |           |        |          |       |          |  |  |

| T11      | VDD_A9        |           |        |          |       |          |  |  |

| T12      | VDD_HFE       |           |        |          |       |          |  |  |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| T13      | VDD_A9        |           |        |          |       |          |

| T14      | VSS_RING      |           |        |          |       |          |

| T15      | VDD_A9        |           |        |          |       |          |

| T16      | VSS_RING      |           |        |          |       |          |

| T17      | DDR_VDDQ      |           |        |          |       |          |

| T18      | CORESIGHT_D4  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| T19      | CORESIGHT_D5  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| T20      | DDR_VREF_RING | Ι         |        |          |       |          |

| T21      | VSS_RING      |           |        |          |       |          |

| T22      | DDR_VDDQ      |           |        |          |       |          |

| T23      | VSS_RING      |           |        |          |       |          |

| T24      | DDR_VDDQ      |           |        |          |       |          |

| T25      | DDR_DATA_7    | I/O       | SSTL   |          |       |          |

| U1       | GEM1_RXD_1    | Ι         |        | 3.3 V    |       | 17 mA    |

| U2       | GEM1_RXD_0    | Ι         |        | 3.3 V    |       | 17 mA    |

| U3       | GEM1_TXC      | 0         |        | 3.3 V    |       | 17 mA    |

| U4       | GEM1_TX_CTL   | 0         |        | 3.3 V    |       | 17 mA    |

| U5       | GEM1_TXD_3    | 0         |        | 3.3 V    |       | 17 mA    |

| U6       | VSS_RING      |           |        |          |       |          |

| U7       | VSS_RING      |           |        |          |       |          |

| U8       | GEM2_DVDD     |           |        |          |       |          |

| U9       | VSS_RING      |           |        |          |       |          |

| U10      | VSS_RING      |           |        |          |       |          |

| U11      | VSS_RING      |           |        |          |       |          |

| U12      | CORE_VDD_RING |           |        |          |       |          |

| U13      | VDD_A9        |           |        |          |       |          |

| U14      | VSS_RING      |           |        |          |       |          |

| U15      | VDD_A9        |           |        |          |       |          |

| U16      | VSS_RING      |           |        |          |       |          |

| U17      | DDR_VDDQ      |           |        |          |       |          |

| U18      | CORE_VDD_RING |           |        |          |       |          |

| U19      | CORE_VDD_RING |           |        |          |       |          |

| U20      | DDR_VDDQ      |           |        |          |       |          |

| U21      | DDR_DQS_N_0   | I/O       | SSTL   |          |       |          |

| U22      | DDR_DATA_1    | I/O       | SSTL   |          |       |          |

| U23      | DDR_DATA_5    | I/O       | SSTL   |          |       |          |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |  |  |

|----------|---------------|-----------|--------|----------|-------|----------|--|--|

| U24      | DDR_DATA_6    | I/O       | SSTL   |          |       |          |  |  |

| U25      | DDR_DATA_4    | I/O       | SSTL   |          |       |          |  |  |

| V1       | GEM1_TXD_2    | 0         |        | 3.3 V    |       | 17 mA    |  |  |

| V2       | GEM1_TXD_1    | 0         |        | 3.3 V    |       | 17 mA    |  |  |

| V3       | VSS_RING      |           |        |          |       |          |  |  |

| V4       | VSS_RING      |           |        |          |       |          |  |  |

| V5       | VSS_RING      |           |        |          |       |          |  |  |

| V6       | VSS_RING      |           |        |          |       |          |  |  |

| V7       | VSS_RING      |           |        |          |       |          |  |  |

| V8       | VSS_RING      |           |        |          |       |          |  |  |

| V9       | IO_VDD_RING   |           |        |          |       |          |  |  |

| V10      | VSS_RING      |           |        |          |       |          |  |  |

| V11      | IO_VDD_RING   |           |        |          |       |          |  |  |

| V12      | VSS_RING      |           |        |          |       |          |  |  |

| V13      | VDD_A9        |           |        |          |       |          |  |  |

| V14      | VSS_RING      |           |        |          |       |          |  |  |

| V15      | VDD_A9        |           |        |          |       |          |  |  |

| V16      | VSS_RING      |           |        |          |       |          |  |  |

| V17      | VSS_RING      |           |        |          |       |          |  |  |

| V18      | CORESIGHT_D3  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |  |  |

| V19      | CORESIGHT_D2  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |  |  |

| V20      | VSS_RING      |           |        |          |       |          |  |  |

| V21      | DDR_DQS_0     | I/O       | SSTL   |          |       |          |  |  |

| V22      | DDR_DATA_0    | I/O       | SSTL   |          |       |          |  |  |

| V23      | DDR_DM_0      | 0         | SSTL   |          |       |          |  |  |

| V24      | DDR_DATA_2    | I/O       | SSTL   |          |       |          |  |  |

| V25      | DDR_DATA_3    | I/O       | SSTL   |          |       |          |  |  |

| W1       | GEM1_TXD_0    | 0         |        | 3.3 V    |       | 17 mA    |  |  |

| W2       | GEM2_RXC      | I/O       |        | 3.3 V    |       | 17 mA    |  |  |

| W3       | GEM2_RX_CTL   | I/O       |        | 3.3 V    |       | 17 mA    |  |  |

| W4       | GEM2_RXD_3    | I/O       |        | 3.3 V    |       | 17 mA    |  |  |

| W5       | GEM2_RXD_2    | I/O       |        | 3.3 V    |       | 17 mA    |  |  |

| W6       | VSS_RING      |           |        |          |       |          |  |  |

| W7       | IO_VDD_RING   |           |        |          |       |          |  |  |

| W8       | VSS_RING      |           |        |          |       |          |  |  |

| W9       | IO_VDD_RING   |           |        |          |       |          |  |  |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| W10      | VSS_RING      |           |        |          |       |          |

| W11      | IO_VDD_RING   |           |        |          |       |          |

| W12      | VSS_RING      |           |        |          |       |          |

| W13      | VDD_A9        |           |        |          |       |          |

| W14      | VSS_RING      |           |        |          |       |          |

| W15      | VDD_A9        |           |        |          |       |          |

| W16      | VSS_RING      |           |        |          |       |          |

| W17      | VSS_RING      |           |        |          |       |          |

| W18      | CORESIGHT_D1  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| W19      | CORESIGHT_D0  | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| W20      | CORESIGHT_CLK | 0         | LVCMOS | 3.3 V    |       | 28 mA    |

| W21      | VSS_RING      |           |        |          |       |          |

| W22      | RTC_VDD       |           |        |          |       |          |

| W23      | OTP_VDDIO     |           |        |          |       |          |

| W24      | RTC_XI        | I         | OSCL   | 3.3 V    |       |          |

| W25      | RTC_XO        | 0         | OSCL   | 3.3 V    |       |          |

| Y1       | GEM2_RXD_1    | I/O       |        | 3.3 V    |       | 17 mA    |

| Y2       | GEM2_RXD_0    | I/O       |        | 3.3 V    |       | 17 mA    |

| ¥3       | GEM2_TXC      | I/O       |        | 3.3 V    |       | 17 mA    |

| Y4       | GEM2_TX_CTL   | I/O       |        | 3.3 V    |       | 17 mA    |

| Y5       | GEM2_TXD_3    | I/O       |        | 3.3 V    |       | 17 mA    |

| Y6       | VSS_RING      |           |        |          |       |          |

| Y7       | IO_VDD_RING   |           |        |          |       |          |

| Y8       | VSS_RING      |           |        |          |       |          |

| Y9       | IO_VDD_RING   |           |        |          |       |          |

| Y10      | VSS_RING      |           |        |          |       |          |

| Y11      | IO_VDD_RING   |           |        |          |       |          |

| Y12      | VSS_RING      |           |        |          |       |          |

| Y13      | IO_VDD_RING   |           |        |          |       |          |

| Y14      | VSS_RING      |           |        |          |       |          |

| Y15      | IO_VDD_RING   |           |        |          |       |          |

| Y16      | VSS_RING      |           |        |          |       |          |

| Y17      | IO_VDD_RING   |           |        |          |       |          |

| Y18      | VSS_RING      |           |        |          |       |          |

| Y19      | IO_VDD_RING   |           |        |          |       |          |

| Y20      | VSS_RING      |           |        |          |       |          |

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| Y21      | IO_VDD_RING   |           |        |          |       |          |

| Y22      | OTP_VDD       |           |        |          |       |          |

| Y23      | TM_EXT_RESET  | 0         | LVCMOS | 5 V      | PD    | 8 mA     |

| Y24      | GPIO04        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| Y25      | GPIO05        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AA1      | GEM2_TXD_2    | 0         |        | 3.3 V    |       | 17 mA    |

| AA2      | GEM2_TXD_1    | 0         |        | 3.3 V    |       | 17 mA    |

| AA3      | VSS_RING      |           |        |          |       |          |

| AA4      | VSS_RING      |           |        |          |       |          |

| AA5      | VSS_RING      |           |        |          |       |          |

| AA6      | VSS_RING      |           |        |          |       |          |

| AA7      | IO_VDD_RING   |           |        |          |       |          |

| AA8      | VSS_RING      |           |        |          |       |          |

| AA9      | IO_VDD_RING   |           |        |          |       |          |

| AA10     | VSS_RING      |           |        |          |       |          |

| AA11     | IO_VDD_RING   |           |        |          |       |          |

| AA12     | VSS_RING      |           |        |          |       |          |

| AA13     | IO_VDD_RING   |           |        |          |       |          |

| AA14     | VSS_RING      |           |        |          |       |          |

| AA15     | IO_VDD_RING   |           |        |          |       |          |

| AA16     | VSS_RING      |           |        |          |       |          |

| AA17     | IO_VDD_RING   |           |        |          |       |          |

| AA18     | VSS_RING      |           |        |          |       |          |

| AA19     | IO_VDD_RING   |           |        |          |       |          |

| AA20     | VSS_RING      |           |        |          |       |          |

| AA21     | IO_VDD_RING   |           |        |          |       |          |

| AA22     | SPI_SS3_N     | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| AA23     | JTAG_TMS      | I         | LVCMOS | 5 V      | PU    |          |

| AA24     | RESET_N       | I         | LVCMOS | 3.3 V    |       |          |

| AA25     | JTAG_TRST_N   | I         | LVCMOS | 5 V      | PU    |          |

| AB1      | GEM2_TXD_0    | 0         |        | 3.3 V    |       | 17 mA    |

| AB2      | GEM2_REFCLK   | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| AB3      | GEM_MDC       | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| AB4      | VSS_RING      |           |        |          |       |          |

| AB5      | EXP_NAND_RDY  | I         | LVCMOS | 5 V      | PU    |          |

| AB6      | DOSC_DVDD     |           |        |          |       |          |

#### Table 3-1LS1024A Pinout List (continued)

#### QorIQ LS1024A Data sheet, Rev 0

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| AB7      | EXP_DQ_3      | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AB8      | EXP_DQ_7      | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AB9      | EXP_DQ_11     | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AB10     | EXP_CLK       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB11     | EXP_RE_N      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB12     | EXP_DM_0      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB13     | EXP_A_0       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB14     | EXP_A_4       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB15     | EXP_A_8       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB16     | EXP_A_15      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB17     | EXP_A_19      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB18     | EXP_A_23      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AB19     | GPIO09        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AB20     | GPIO13        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AB21     | I2C_SDA       | I/O       | LVCMOS | 5 V      | PU    | 8 mA     |

| AB22     | SPI_SS0_N     | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| AB23     | JTAG_TDO      | 0         | LVCMOS | 5 V      |       | 12 mA    |

| AB24     | JTAG_TCK      | Ι         | LVCMOS | 5 V      | PU    |          |

| AB25     | JTAG_TDI      | Ι         | LVCMOS | 5 V      | PU    |          |

| AC1      | GEM_MDIO      | I/O       | LVCMOS | 3.3 V    | PD    | 8 mA     |

| AC2      | DECT_RSTN     | 0         | LVCMOS | 3.3 V    | PD    | 8 mA     |

| AC3      | GPIO03        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AC4      | GPIO01        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AC5      | EXP_NAND_CS   | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC6      | EXP_NAND_WE_N | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC7      | EXP_DQ_4      | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AC8      | EXP_DQ_8      | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AC9      | EXP_DQ_12     | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AC10     | EXP_DQ_15     | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AC11     | EXP_WE_N      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC12     | EXP_DM_1      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC13     | EXP_A_1       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC14     | EXP_A_5       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC15     | EXP_A_9       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC16     | EXP_A_14      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC17     | EXP_A_18      | 0         | LVCMOS | 5 V      |       | 8 mA     |

Table 3-1

LS1024A Pinout List (continued)

QorlQ LS1024A Data sheet, Rev 0

| Location | Signal Symbol | Direction | Туре   | Tolerant | PU/PD | Strength |

|----------|---------------|-----------|--------|----------|-------|----------|

| AC18     | EXP_A_22      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AC19     | GPIO08        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AC20     | GPIO12        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AC21     | I2C_SCL       | 0         | LVCMOS | 5 V      | PU    | 8 mA     |

| AC22     | SPI_SCLK      | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| AC23     | TDM_CK        | I/O       | LVCMOS | 3.3 V    |       | 12 mA    |

| AC24     | TDM_DX        | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| AC25     | TDM_DR        | Ι         | LVCMOS | 3.3 V    | PU    |          |

| AD1      | VSS_RING      |           |        |          |       |          |

| AD2      | DECT_BCLK     | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

| AD3      | GPIO02        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AD4      | DECT_XO       | 0         | OSCL   | 3.3 V    |       |          |

| AD5      | EXP_NAND_RE_N | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD6      | EXP_DQ_1      | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AD7      | EXP_DQ_5      | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AD8      | EXP_DQ_9      | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AD9      | EXP_DQ_13     | I/O       | LVCMOS | 5 V      |       | 8 mA     |

| AD10     | EXP_CS1_N     | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD11     | EXP_CS2_N     | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD12     | EXP_RDY       | Ι         | LVCMOS | 5 V      | PU    |          |

| AD13     | EXP_A_2       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD14     | EXP_A_6       | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD15     | EXP_A_10      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD16     | EXP_A_13      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD17     | EXP_A_17      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD18     | EXP_A_21      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD19     | EXP_A_25      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD20     | GPIO11        | I/O       | LVCMOS | 5 V      | PU    | 10 mA    |

| AD21     | UART1_TX      | 0         | LVCMOS | 5 V      |       | 8 mA     |

| AD22     | SPI_RXD       | I         | LVCMOS | 3.3 V    | PD    | 8 mA     |

| AD23     | SPI_SS2_N     | О         | LVCMOS | 3.3 V    |       | 8 mA     |

| AD24     | TDM_FS        | I/O       | LVCMOS | 3.3 V    |       | 8 mA     |

| AD25     | VSS_RING      |           |        |          |       |          |

| AE1      | VSS_RING      |           |        |          |       |          |

| AE2      | VSS_RING      |           |        |          |       |          |

| AE3      | DECT_SCLK     | 0         | LVCMOS | 3.3 V    |       | 8 mA     |

Table 3-1LS1024A Pinout List (continued)

QorIQ LS1024A Data sheet, Rev 0

| able 5-1 | LS 1024A Finour List (Continued) |           |        |          |       |          |  |  |

|----------|----------------------------------|-----------|--------|----------|-------|----------|--|--|

| Location | Signal Symbol                    | Direction | Туре   | Tolerant | PU/PD | Strength |  |  |

| AE4      | DECT_XI                          | I         | OSCL   | 3.3 V    |       |          |  |  |

| AE5      | EXP_DQ_0                         | I/O       | LVCMOS | 5 V      |       | 8 mA     |  |  |

| AE6      | EXP_DQ_2                         | I/O       | LVCMOS | 5 V      |       | 8 mA     |  |  |

| AE7      | EXP_DQ_6                         | I/O       | LVCMOS | 5 V      |       | 8 mA     |  |  |

| AE8      | EXP_DQ_10                        | I/O       | LVCMOS | 5 V      |       | 8 mA     |  |  |

| AE9      | EXP_DQ_14                        | I/O       | LVCMOS | 5 V      |       | 8 mA     |  |  |

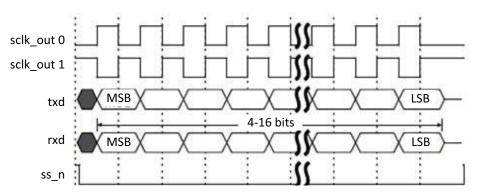

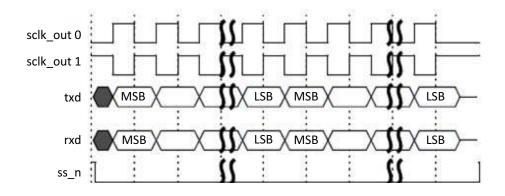

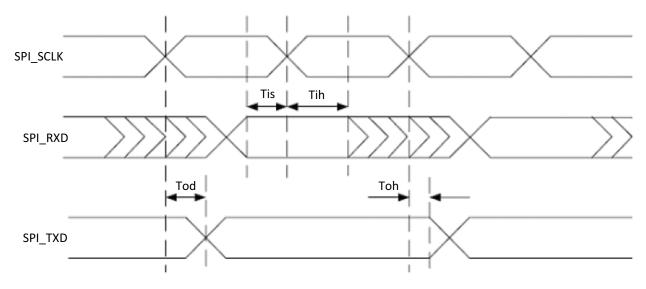

| AE10     | EXP_CS0_N                        | 0         | LVCMOS | 5 V      |       | 8 mA     |  |  |

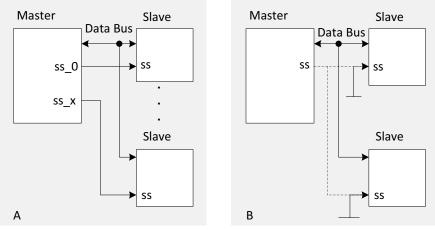

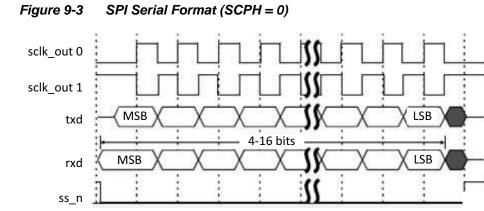

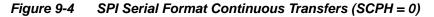

| AE11     | EXP_CS3_N                        | 0         | LVCMOS | 5 V      |       | 8 mA     |  |  |

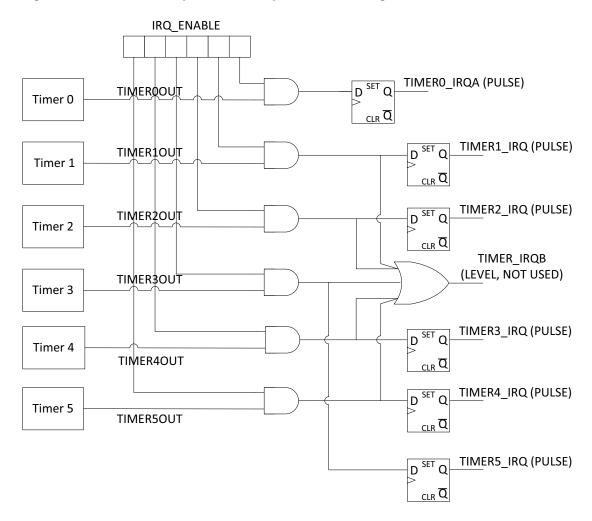

| AE12     | EXP_ALE                          | 0         | LVCMOS | 5 V      |       | 8 mA     |  |  |