#### AS5055

### Low Power 12-Bit Magnetic Rotary Encoder

## General Description

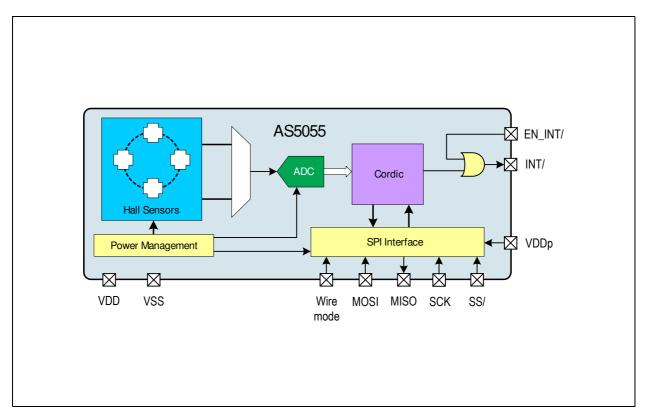

The AS5055 is a single-chip magnetic rotary encoder IC with low voltage and low power features.

It includes 4 integrated Hall elements, a high resolution ADC and a smart power management controller.

The angle position, alarm bits and magnetic field information are transmitted over a standard 3-wire or 4-wire SPI interface to the host processor.

The AS5055 is available in a small QFN 16-pin 4x4x0.85 mm package and specified over an operating temperature of -40°C to +85°C.

## 2 Key Features

- 12-bit resolution

- Standard SPI interface, 3 or 4 wire

- 3.0V to 3.6V core voltage, 1.8V to 3.6V peripheral supply voltage

- Automatic wake-up over SPI interface

- Interrupt output for conversion complete indication

- Low power mode:

- < 8mA (avg) @ 620µs readout interval

- < 5mA (avg) @ 1ms readout interval

- < 500µA (avg) @ 10ms readout interval

- < 53µA (avg) @ 100ms readout interval</li>

- Small size 16-pin QFN (4x4x0.85 mm)

## 3 Applications

The device is ideal for Servo motor control, Input device for battery operated portable devices, and Robotics.

Figure 1. AS5055 Block Diagram

#### Contents

| 2 Key Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4 Pin Assignments 4.1 Pin Descriptions  5 Absolute Maximum Ratings 6 Electrical Characteristics 6.1 Operating Conditions 6.2 System Parameters 6.3 DC/AC Characteristics  7 Detailed Description  7.1 Operating Modes  7.1.1 Power Supply Filter  7.1.2 Reading an Angle  7.1.3 Low Power Mode  7.1.4 Interrupt Chaining  7.2 SPI Communication  7.2.1 Command Package  7.2.2 Read Package (Value Read from AS5055)  7.2.3 Write Data Package (Value Written to AS5055)  7.2.4 Register Block  7.2.5 SPI Interface Commands  8 Application Information  8.1 SPI Interface  8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1)  8.1.2 SPI Timing  8.1.3 SPI Connection to the Host μC | 1  |

| 4.1 Pin Descriptions.  5 Absolute Maximum Ratings  6 Electrical Characteristics  6.1 Operating Conditions 6.2 System Parameters 6.3 DC/AC Characteristics  7 Detailed Description  7.1 Operating Modes  7.1.1 Power Supply Filter  7.1.2 Reading an Angle  7.1.3 Low Power Mode  7.1.4 Interrupt Chaining  7.2 SPI Communication  7.2.1 Command Package  7.2.2 Read Package (Value Read from AS5055)  7.2.3 Write Data Package (Value Written to AS5055)  7.2.4 Register Block  7.2.5 SPI Interface Commands  8 Application Information  8.1 SPI Interface  8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1)  8.1.2 SPI Timing  8.1.3 SPI Connection to the Host μC                | 1  |

| 5 Absolute Maximum Ratings. 6 Electrical Characteristics. 6.1 Operating Conditions. 6.2 System Parameters. 6.3 DC/AC Characteristics. 7 Detailed Description.  7.1 Operating Modes. 7.1.1 Power Supply Filter. 7.1.2 Reading an Angle. 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining.  7.2 SPI Communication. 7.2.1 Command Package. 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block. 7.2.5 SPI Interface Commands.  8 Application Information  8.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1). 8.1.2 SPI Timing. 8.1.3 SPI Connection to the Host μC                                                          | 3  |

| 5 Absolute Maximum Ratings. 6 Electrical Characteristics. 6.1 Operating Conditions. 6.2 System Parameters. 6.3 DC/AC Characteristics. 7 Detailed Description.  7.1 Operating Modes. 7.1.1 Power Supply Filter. 7.1.2 Reading an Angle. 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining.  7.2 SPI Communication. 7.2.1 Command Package. 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block. 7.2.5 SPI Interface Commands.  8 Application Information  8.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1). 8.1.2 SPI Timing. 8.1.3 SPI Connection to the Host μC                                                          | 3  |

| 6.1 Operating Conditions 6.2 System Parameters 6.3 DC/AC Characteristics 7 Detailed Description 7.1 Operating Modes 7.1.1 Power Supply Filter 7.1.2 Reading an Angle 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining 7.2 SPI Communication 7.2.1 Command Package 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block 7.2.5 SPI Interface Commands 8 Application Information 8.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1) 8.1.2 SPI Timing 8.1.3 SPI Connection to the Host μC                                                                                                                                      |    |

| 6.2 System Parameters 6.3 DC/AC Characteristics.  7 Detailed Description.  7.1 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  |

| 6.2 System Parameters 6.3 DC/AC Characteristics.  7 Detailed Description.  7.1 Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 6.3 DC/AC Characteristics.  7 Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 7 Detailed Description 7.1 Operating Modes 7.1.1 Power Supply Filter 7.1.2 Reading an Angle 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining 7.2 SPI Communication 7.2.1 Command Package 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block 7.2.5 SPI Interface Commands 8 Application Information 8.1 SPI Interface 8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1) 8.1.2 SPI Timing 8.1.3 SPI Connection to the Host μC                                                                                                                                                                                           |    |

| 7.1.1 Power Supply Filter 7.1.2 Reading an Angle 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining 7.2 SPI Communication 7.2.1 Command Package 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block 7.2.5 SPI Interface Commands 8 Application Information 8.1 SPI Interface 8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1) 8.1.2 SPI Timing 8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                      |    |

| 7.1.1 Power Supply Filter 7.1.2 Reading an Angle 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining 7.2 SPI Communication 7.2.1 Command Package 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block 7.2.5 SPI Interface Commands 8 Application Information 8.1 SPI Interface 8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1) 8.1.2 SPI Timing 8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                      | 7  |

| 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining 7.2 SPI Communication 7.2.1 Command Package 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block 7.2.5 SPI Interface Commands 8 Application Information 8.1 SPI Interface 8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1) 8.1.2 SPI Timing 8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                                                                       |    |

| 7.1.3 Low Power Mode 7.1.4 Interrupt Chaining 7.2 SPI Communication 7.2.1 Command Package 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block 7.2.5 SPI Interface Commands 8 Application Information 8.1 SPI Interface 8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1) 8.1.2 SPI Timing 8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                                                                       | 8  |

| 7.1.4 Interrupt Chaining  7.2 SPI Communication  7.2.1 Command Package  7.2.2 Read Package (Value Read from AS5055)  7.2.3 Write Data Package (Value Written to AS5055)  7.2.4 Register Block  7.2.5 SPI Interface Commands  8 Application Information  8.1 SPI Interface  8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1)  8.1.2 SPI Timing  8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                                                                                 |    |

| 7.2.1 Command Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 7.2.2 Read Package (Value Read from AS5055) 7.2.3 Write Data Package (Value Written to AS5055) 7.2.4 Register Block 7.2.5 SPI Interface Commands  8 Application Information 8.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1) 8.1.2 SPI Timing 8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                                                                                                                                                                                    | 9  |

| 7.2.3 Write Data Package (Value Written to AS5055)  7.2.4 Register Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9  |

| 7.2.3 Write Data Package (Value Written to AS5055)  7.2.4 Register Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9  |

| 7.2.4 Register Block 7.2.5 SPI Interface Commands  8 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 8 Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 8.1 SPI Interface  8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1)  8.1.2 SPI Timing  8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11 |

| 8.1.1 SPI Interface Signals (4-Wire Mode, Wire_mode = 1)  8.1.2 SPI Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 |

| 8.1.2 SPI Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

| 8.1.2 SPI Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15 |

| 8.1.3 SPI Connection to the Host µC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 0.0 Di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 8.2 Placement of the Magnet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19 |

| 9 Package Drawings and Markings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 10 Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

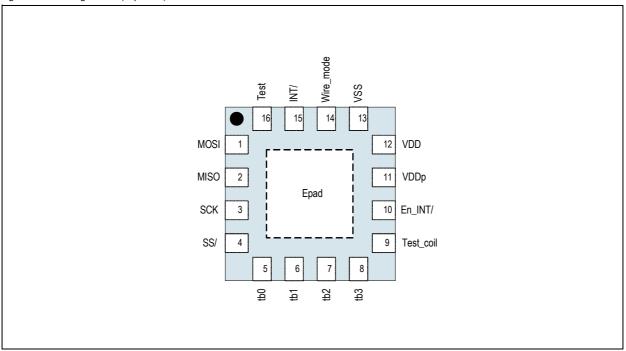

# 4 Pin Assignments

Figure 2. Pin Assignments (Top View)

#### 4.1 Pin Descriptions

Table 1. Pin Descriptions

| Pin Number | Pin Name  | Pin Type                         | Description                                               |  |  |  |  |  |  |

|------------|-----------|----------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

| 1          | MOSI      | Digital input                    | SPI bus data input                                        |  |  |  |  |  |  |

| 2          | MISO      | Digital output, tri-state buffer | SPI bus data output                                       |  |  |  |  |  |  |

| 3          | SCK       | Digital input Schmitt trigger    | SPI Clock Schmitt trigger                                 |  |  |  |  |  |  |

| 4          | SS/       | Digital input                    | SPI Slave Select, active LOW                              |  |  |  |  |  |  |

| 5          | tb0       |                                  |                                                           |  |  |  |  |  |  |

| 6          | tb1       | Analog I/O                       | Test pin, leave unconnected                               |  |  |  |  |  |  |

| 7          | tb2       | Analog I/O                       | rest piri, leave unconnected                              |  |  |  |  |  |  |

| 8          | tb3       |                                  |                                                           |  |  |  |  |  |  |

| 9          | Test coil | Supply                           | Test pin, connect to VSS                                  |  |  |  |  |  |  |

| 10         | En_INT/   | Digital input                    | Enable / disable Interrupt                                |  |  |  |  |  |  |

| 11         | VDDp      |                                  | Peripheral power supply, 1.8V ~ VDD                       |  |  |  |  |  |  |

| 12         | VDD       | Supply                           | Analog and digital power supply, 3.0 ~ 3.6V               |  |  |  |  |  |  |

| 13         | VSS       |                                  | Supply ground                                             |  |  |  |  |  |  |

| 14         | Wire_mode | Digital I/O                      | 0: 3-wire mode<br>1: 4-wire mode                          |  |  |  |  |  |  |

| 15         | INT/      | Digital output, tri-state buffer | Interrupt output. Active LOW, when conversion is finished |  |  |  |  |  |  |

| 16         | Test      | Digital I/O                      | Test pin, leave unconnected                               |  |  |  |  |  |  |

| Epad       | -         | -                                | Center pad not connected                                  |  |  |  |  |  |  |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 5 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Symbol            | Parameter                        | Min  | Max     | Units | Comments                                                                                                                                                                                                                                                                           |

|-------------------|----------------------------------|------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical P      | arameters                        |      |         |       |                                                                                                                                                                                                                                                                                    |

| VDD               | DC supply voltage                | -0.3 | 5.0     | V     | Value of these process dependent parameters to be taken from according Process Parameter document, current version                                                                                                                                                                 |

| VDDp              | Peripheral supply voltage        | -0.3 | VDD+0.3 | V     |                                                                                                                                                                                                                                                                                    |

| VIN               | Input pin voltage                | -0.3 | 5.0     | V     |                                                                                                                                                                                                                                                                                    |

| I <sub>scr</sub>  | Input current (latchup immunity) | -100 | 100     | mA    | Norm: Jedec 78                                                                                                                                                                                                                                                                     |

| Electrostati      | c Discharge                      |      |         |       |                                                                                                                                                                                                                                                                                    |

| ESD               | Electrostatic discharge          | ±1   | -       | kV    | Norm: MIL 883 E method 3015                                                                                                                                                                                                                                                        |

| ΘЈΑ               | Package thermal resistance       | -    | 33.5    | °C/W  | Velocity=0, Multi Layer PCB;<br>Jedec Standard Testboard                                                                                                                                                                                                                           |

| Continuous        | Power Dissipation                |      |         |       |                                                                                                                                                                                                                                                                                    |

| Pt                | Total power dissipation          |      | 36      | mW    |                                                                                                                                                                                                                                                                                    |

| Temperatur        | e Ranges and Storage Conditions  |      |         |       |                                                                                                                                                                                                                                                                                    |

| T <sub>strg</sub> | Storage temperature              | -55  | 125     | °C    |                                                                                                                                                                                                                                                                                    |

| TBODY             | Package body temperature         |      | 260     | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

|                   | Humidity non-condensing          | 5    | 85      | %     |                                                                                                                                                                                                                                                                                    |

| MSL               | Moisture Sensitive Level         |      | 3       |       | Represents a maximum floor life time of 168h                                                                                                                                                                                                                                       |

## 6 Electrical Characteristics

#### 6.1 Operating Conditions

Table 3. Operating Conditions

| Parameter                              | Conditions                               | Min  | Тур | Max       | Units |

|----------------------------------------|------------------------------------------|------|-----|-----------|-------|

| DC supply voltage                      | VDD                                      | 3.0  |     | 3.6       | V     |

| Peripheral supply voltage <sup>1</sup> | VDDp                                     | 1.8  |     | VDD       | V     |

| Input pin voltage                      | Vin                                      | -0.3 |     | VDDp +0.3 | V     |

| Ambient operating temperature          |                                          | -40  |     | 85        | °C    |

|                                        | Power supply filter, pin VDD             | 2.2  |     | 4.7       | μF    |

| External component                     | (refer to Power Supply Filter on page 7) | 15   |     | 33        | Ω     |

|                                        | Ceramic capacitor, pin VDDp to VSS       | 100  |     |           | nF    |

<sup>1.</sup> VDDp must not exceed VDD (protection diode between VDDp and VDD)

#### 6.2 System Parameters

Table 4. System Parameters

| Symbol         | Parameter                              | Conditions                                                                           | Min       | Тур   | Max   | Units  |

|----------------|----------------------------------------|--------------------------------------------------------------------------------------|-----------|-------|-------|--------|

| I_10           | Operating current                      | Average current @ 10 ms readout rate 1                                               |           |       | 0.5   | mA     |

| I_100          | Operating current                      | Average current @ 100 ms readout rate                                                |           |       | 53    | μA     |

| I_max          | Operating current                      | Maximum readout rate                                                                 |           |       | 8.5   | mA     |

|                | Readout rate                           | Time between READ ANGLE command and INTERRUPT                                        | 320       |       | 430   | μs     |

|                | Power down current                     | Power down current                                                                   |           |       | 3     | μA     |

| Rd             | Lateral displacement range             | Centre of the magnet to the centre of the die                                        | -         |       | ± 0.5 | mm     |

| B <sub>Z</sub> | Magnetic field strength                |                                                                                      | 30        | -     | 80    | mT     |

|                | Serial interface                       | SPI mode 0 (CPOL                                                                     | = 0 / CPH | A =0) |       |        |

|                | Resolution; magnetic field measurement |                                                                                      |           | 12    |       | bit    |

|                | Resolution; angle                      |                                                                                      |           | 12    |       | bit    |

|                | INL                                    | Best-fit line - over supply, displacement and temperature – but without quantization | -1.41     |       | 1.41  | degree |

|                | IC package                             | IC package QFN 4x4x0.85                                                              |           |       |       |        |

<sup>1.</sup> Without the time for the SPI interface

#### 6.3 DC/AC Characteristics

Digital pads: MISO, MOSI, SCK, SS/, EN\_INT/, INT/, Wire\_mode

Table 5. DC/AC Characteristics

| Symbol          | Parameter                 | Conditions  | Min        | Тур | Max         | Units |

|-----------------|---------------------------|-------------|------------|-----|-------------|-------|

| V <sub>IH</sub> | High level input voltage  |             | 0.7 * VDDp |     |             | ٧     |

| V <sub>IL</sub> | Low level input voltage   | VDDp > 2.7V |            |     | 0.3 * VDDp  | V     |

| V <sub>IL</sub> | Low level input voltage   | VDDp < 2.7V |            |     | 0.25 * VDDp | V     |

| ILEAK           | Input leakage current     |             |            |     | 1           | μA    |

| V <sub>OH</sub> | High level output voltage |             | VDDp - 0.5 |     |             | ٧     |

| V <sub>OL</sub> | Low level output voltage  |             |            |     | VSS + 0.4   | ٧     |

| CL              | Capacitive load           |             |            |     | 35          | pF    |

## 7 Detailed Description

#### User Programming.

The AS5055 does not require any programming by the user. A dedicated on-chip zero position programming is not implemented. If a zero position programming is required, it is recommended to store the zero position offset in the host controller.

#### 7.1 Operating Modes

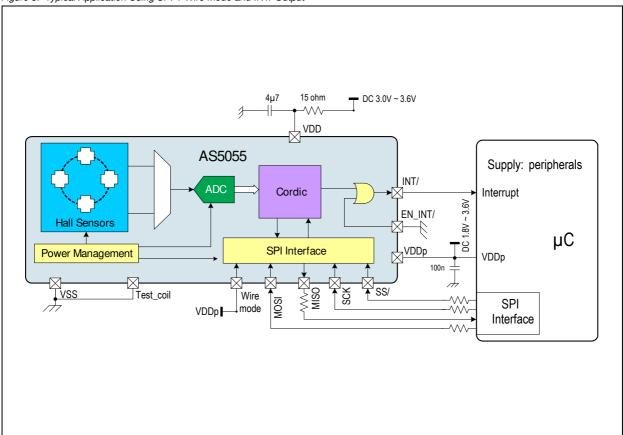

#### Typical Application.

The AS5055 requires only a few external components in order to operate immediately when connected to the host microcontroller. Only 6 wires are needed for a simple application using a single power supply: two wires for power and four wires for the SPI communication. A seventh connection can be added in order to send an interrupt to the host CPU to inform that a new valid angle can be read. For additional information on the layout and filtering of the SPI, please refer to the application note AN5000\_SPI\_Interface.

Figure 3. Typical Application Using SPI 4-Wire Mode and INT/ Output

Upon power-up, the AS5055 performs a full power-up sequence including one angle measurement. The completion of this cycle is indicated at the INT/ output pin and the angle value is stored in an internal register. Once this output is set, the AS5055 suspends to sleep mode.

#### 7.1.1 Power Supply Filter

Due to the sequential internal sampling of the Hall sensors, fluctuations on the analog power supply (pin#12: VDD) may cause additional jitter of the measured angle. This jitter can be avoided by providing a stable VDD supply.

The easiest way to achieve that is to add a RC filter:  $15\Omega + 4.7\mu F$  in the power supply line as shown in Figure 3.

Alternatively, a filter:  $33\Omega + 2.2\mu F$  may be used. However with this configuration, the minimum supply voltage is 3.15V.

#### 7.1.2 Reading an Angle

The external microcontroller can respond to the INT request by reading the angle value from the AS5055 over the SPI interface. Once the angle value is read, the INT output is cleared again.

Sending a "read angle" command by the SPI interface also automatically powers up the chip and starts another angle measurement. As soon ad the microcontroller has completed reading of the angle value, the INT output is cleared and a new result is stored in the angle register. The completion of the angle measurement is again indicated by setting the INT output and a corresponding flag in the status register.

Reducing the Angle Jitter. Due to the measurement principle of the chip, only a single angle measurement is performed in very short time (~600µs) after each power-up sequence. As soon as the measurement of one angle is completed, the chip suspends to power-down state. An on-chip filtering of the angle value by digital averaging is not implemented, as this would require more than one angle measurement and consequently, a longer power- up time which is not desired in low-power applications.

The angle jitter can be reduced by averaging of several angle samples in the external microcontroller. For example, an averaging of 4 samples reduces the jitter by 6dB (50%).

#### 7.1.3 Low Power Mode

After completing the readout of an angle value, the device is in very low power condition. The AS5055 remains in sleep mode until it receives another angle reading request over the SPI interface. The average power consumption therefore depends on the interval, at which the external controller reads an angle over the SPI Interface. The timing ratio between active and sleep phase:

(EQ 1)

$$I_{avg} = \frac{t_{on} * I_{on} + t_{off} * I_{off}}{t_{on} + t_{off}}$$

#### Where:

ton = Minimum on-time for power-up and angle measurement

600µs

toff = Pause interval between measurements, determined by the polling rate of the external microcontroller

Ion = Current consumption in active mode

8mA avg.

Ioff = Current consumption in sleep mode

3µA

#### Examples:

3000 measurements per second (continuous mode) I = 8mA 1000 measurements per second lavg = 5mA 100 measurements per second lavg =  $500\mu$ A 10 measurements per second lavg =  $53\mu$ A

**Note:** Even in low power mode, the power supply must be capable of supporting the active current at least for the time T<sub>on</sub>, until the AS5055 is suspended to sleep mode.

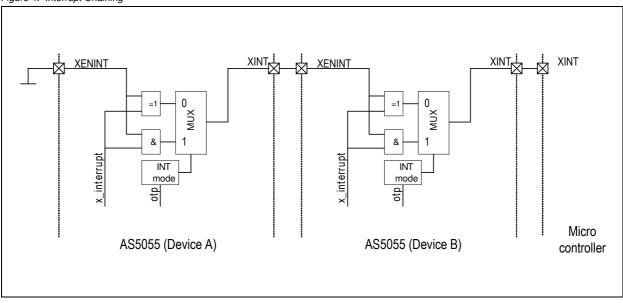

#### 7.1.4 Interrupt Chaining

Every chip contains a configurable gate to combine its own internally generated interrupt signal with a signal applied externally over the XENINT-pin. The INT-mode register is preset via an OTP register can be overwritten by the SPI interface.

#### Case A.

Device A is set to mode 0

Device B is set to mode 0

The micro controller recognizes an interrupt if both devices signalize that the computation is finished.

#### Case B.

Device A is set to mode 0

Device B is set to mode 1

The micro controller recognizes an interrupt if one of the two devices signalize that the computation is finished.

Figure 4. Interrupt Chaining

#### 7.2 SPI Communication

The transmitted data consists of 14-bit data, an Error-Flag and a Parity bit. When writing data to the chip, the Error-Flag is not applicable. The Parity is generated from the upper 15-bit and forms an even parity over the whole frame. The Error-Flag indicates that a failure occurred in a previous transmission.

#### 7.2.1 Command Package

Every command sent to the AS5055 is represented with the following layout.

Table 6. Command Package

| Bi | MSB | 14 | 13 | 12 | 11 | 10 | 9 | 8       | 7        | 6 | 5 | 4 | 3 | 2 | 1 | LSB |

|----|-----|----|----|----|----|----|---|---------|----------|---|---|---|---|---|---|-----|

|    | RWn |    |    |    |    |    |   | Address | s <13:0> |   |   |   |   |   |   | PAR |

| Bit     | Description                     |

|---------|---------------------------------|

| RWn     | Indicates read or write command |

| Address | 14-bit address code             |

| PAR     | Parity bit (EVEN)               |

#### 7.2.2 Read Package (Value Read from AS5055)

The read frame always contains two alarm bits, the error and parity flags and the addressed data of the previous read command.

Table 7. Read Package

| Bit | MSB         | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6   | 5 | 4 | 3 | 2 | 1 | LSB |

|-----|-------------|----|----|----|----|----|---|---|----|-----|---|---|---|---|---|-----|

|     | Data <13:0> |    |    |    |    |    |   |   | EF | PAR |   |   |   |   |   |     |

| Bit  | Description                                                                |

|------|----------------------------------------------------------------------------|

| Data | 14-bit addressed data                                                      |

| EF   | Error flag indicating a transmission error in a previous host transmission |

| PAR  | Parity bit (EVEN)                                                          |

#### 7.2.3 Write Data Package (Value Written to AS5055)

The write frame is compatible to the read frame and contains two additional bits, the don't care and parity flag.

If the previous command was a write command a second package has to be transmitted.

Table 8. Write Package

| Bit | MSB         | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6          | 5   | 4 | 3 | 2 | 1 | LSB |

|-----|-------------|----|----|----|----|----|---|---|---|------------|-----|---|---|---|---|-----|

|     | Data <13:0> |    |    |    |    |    |   |   |   | Don't care | PAR |   |   |   |   |     |

| Bit  | Description                                     |

|------|-------------------------------------------------|

| Data | 14-bit data to write to former selected address |

| PAR  | Parity bit (EVEN)                               |

#### 7.2.4 Register Block

Table 9. Register Block

| Register              | Bit            | Mode             | Reset Value | Bit     | Description                                                                                                         |

|-----------------------|----------------|------------------|-------------|---------|---------------------------------------------------------------------------------------------------------------------|

| Power ON Reset (PO    | R) Register -  | [0x3F22]         |             |         |                                                                                                                     |

| POR_OFF               | 8              | R/W              | 0x00        | <7:0>   | The POR cell is deactivated when the value 0x5A is written to this register (30µA reduction of current consumption) |

| Software Reset Regis  | ter - [0x3C0   | 0]               |             |         |                                                                                                                     |

| software_reset        | 14             | W                | 0x0         | <13:0>  | Refer to SOFTWARE RESET Command on page 13                                                                          |

| Clear Error Flag Regi | ster - [0x338  | 0]               | *           | *       |                                                                                                                     |

| clr_error_flag        | 14             | R                | 0x0         | <13:0>  | Refer to CLEAR ERROR FLAG Command on page 12                                                                        |

| No Operation Registe  | er - [0x0000]  |                  |             |         |                                                                                                                     |

| NOP                   | 14             | W                | 0x0         | <13:0>  | Refer to NOP Command on page 14                                                                                     |

| Automatic Gain Cont   | rol (AGC) Reg  | ister - [0x03FF8 | 3]          | II.     |                                                                                                                     |

| AGC                   | 6              | R/W              | 0x20        | <5:0>   | Automatic gain control: low values = strong magnetic field high values = weak magnetic field                        |

| Angular Data - [0x3F  | FF]            |                  | ·           |         |                                                                                                                     |

| Angle Value           | 12             | R                | 0x000       | <11:0>  | Measured angular value, 12-bit                                                                                      |

| Alarm LO              | 1              | R                | 0           | <12>    | Alarm bit indicating a too low magnetic field, active HIGH <sup>1</sup>                                             |

| Alarm HI              | 1              | R                | 0           | <13>    | Alarm bit indicating a too high magnetic field, active HIGH <sup>1</sup>                                            |

| System Configuration  | n Register 1 - | [0x3F20]         | ·           |         |                                                                                                                     |

| resolution            | 2              | R                | ,00,        | <13:12> | '00' indicates 12-bit resolution                                                                                    |

| chip ID               | 3              | R                | '001'       | <11:9>  | Silicon version 001                                                                                                 |

| invert_spinning       | 1              | R/W              | 0           | <8>     | Invert the channel voltage                                                                                          |

| FE_bw_setting         | 2              | R/W              | '00'        | <6:5>   | FE BW setting                                                                                                       |

| FE_gain_setting       | 2              | R/W              | '00'        | <4:3>   | FE gain setting                                                                                                     |

| break_AGC_loop        | 1              | R/W              | 0           | <2>     | Breaks the automatic gain control loop to use the AGC registers in a static mode                                    |

<sup>1.</sup> Both bits High: Alarm LO = Alarm Hi = 1 indicate a major system error (DAC overflow, CORDIC overflow or Hall current error).

#### 7.2.5 SPI Interface Commands

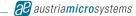

READ Command. For a single READ command two transmission sequences are necessary. The first package written to the AS5055 contains the READ command (MSB high) and the address the chip has to access, the second package transmitted to the AS5055 device can be any command the chip has to process next. The content of the desired register is available in the MISO register of the master device at the end of the second transmission cycle.

Figure 5. READ Command

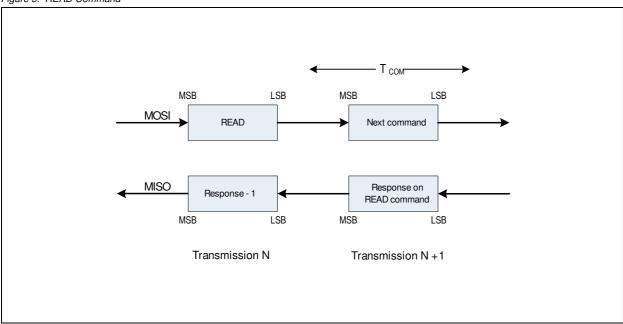

WRITE Command. A single WRITE command takes two transmission cycles. With a NOP command after the WRITE command you can verify the sent data with three transmission cycles because the data will be send back during the NOP command.

Figure 6. WRITE Command

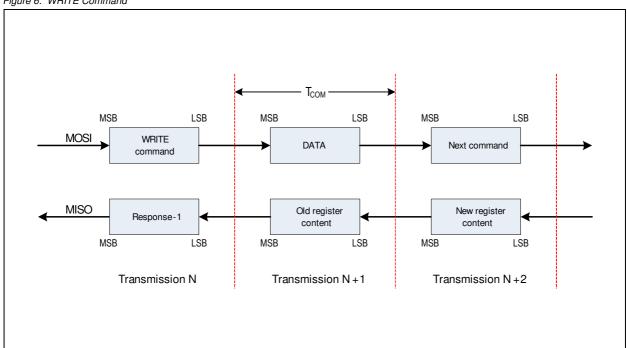

CLEAR ERROR FLAG Command. The CLEAR ERROR FLAG command is implemented as READ command. This command clears the ERROR FLAG which is contained in every READ frame. The READ data are 0x0000, which indicates a successful clear command.

Figure 7. CLEAR ERROR FLAG Command

The package necessary to perform a CLEAR ERROR FLAG is built up as follows.

Table 10. CLEAR ERROR FLAG Command

| Bit                      | MSB | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7   | 6 | 5 | 4 | 3 | 2 | 1 | LSB |

|--------------------------|-----|----|----|----|----|----|---|---|-----|---|---|---|---|---|---|-----|

|                          | 1   | 1  | 1  | 0  | 0  | 1  | 1 | 1 | 0   | 0 | 0 | 0 | 0 | 0 | 0 | PAR |

| CLEAR ERROR FLAG command |     |    |    |    |    |    |   |   | PAR |   |   |   |   |   |   |     |

Possible conditions which force the ERROR FLAG to be set:

- Wrong parity

- Wrong command

- Wrong number of clocks (no full transmission cycle or too many clocks)

Note: If the error flag is set to 'high' because of a communication problem the flag remains set until it will be cleared by an external command.

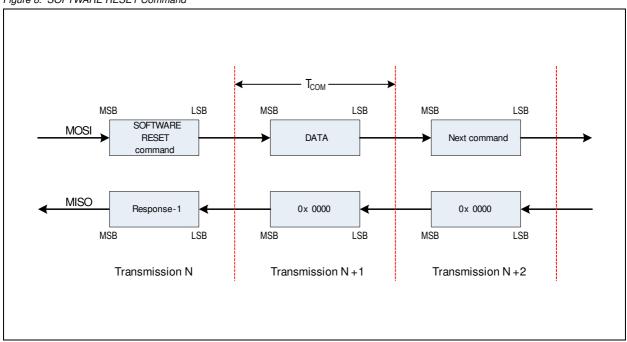

SOFTWARE RESET Command. The SOFTWARE RESET command is implemented as WRITE command. The bit 'RES SPI' of the DATA package indicates if the SPI registers should be reset as well. The soft reset resets the digital part ('RES SPI' is set to one) as well as the PPTRIM. A new PPTRIM auto-load is initiated and the reset values stored in the PPTRIM are loaded into the configuration registers. The command following the SOFTWARE RESET command can be any of the commands specified in this chapter.

After the data package is sent, the soft reset is generated. The fuses of the PPTRIM are loaded into the registers and a new conversion cycle will be started. If the device is in sleep mode the oscillator will be started first.

Figure 8. SOFTWARE RESET Command

In order to invoke a software reset on the AS5055 the following bit pattern has to be sent.

Table 11. SOFTWARE RESET Command

| Bit | MSB | 14 | 13 | 12 | 11 | 10 | 9     | 8      | 7       | 6   | 5 | 4 | 3 | 2 | 1 | LSB |

|-----|-----|----|----|----|----|----|-------|--------|---------|-----|---|---|---|---|---|-----|

|     | 0   | 1  | 1  | 1  | 1  | 0  | 0     | 0      | 0       | 0   | 0 | 0 | 0 | 0 | 0 | PAR |

|     |     | •  |    |    |    | SC | FTWAR | E RESE | T comma | and | , | , | , | • | , | PAR |

Table 12. Data Package

| Bit | MSB | 14 | 13 | 12 | 11 | 10 | 9         | 8 | 7 | 6 | 5 | 4 | 3 | 2       | 1          | LSB |

|-----|-----|----|----|----|----|----|-----------|---|---|---|---|---|---|---------|------------|-----|

|     |     |    |    |    |    |    | Oon't car | e |   |   |   |   |   | RES SPI | Don't care | PAR |

| Bit     | Description                                                 |

|---------|-------------------------------------------------------------|

| RES SPI | If set to one, SPI registers are reset as well <sup>1</sup> |

| PAR     | Parity bit (EVEN)                                           |

1. After a power on reset, the OTP will be read and hence OTP related registers are changed independent on the RES SPI flag.

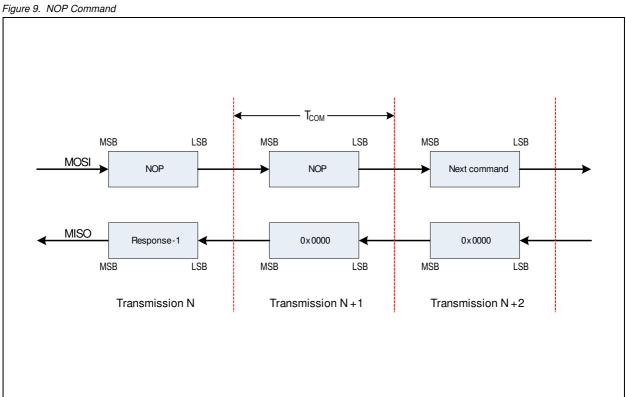

NOP Command. The NOP command represents a dummy write to the AS5055.

The NOP command frame looks like follows.

Table 13. NOP Command

| Bit | MSB | 14 | 13 | 12 | 11 | 10 | 9   | 8       | 7         | 6    | 5 | 4 | 3 | 2 | 1 | LSB |

|-----|-----|----|----|----|----|----|-----|---------|-----------|------|---|---|---|---|---|-----|

|     | 0   | 0  | 0  | 0  | 0  | 0  | 0   | 0       | 0         | 0    | 0 | 0 | 0 | 0 | 0 |     |

|     |     |    |    |    |    |    | NOI | o comma | and (0x00 | 000) |   |   |   | • |   |     |

The chip's response on this command is 0x0000 – if no error happens.

## 8 Application Information

The benefits of the AS5055 device are as follows:

- Complete system-on-chip

- Low power consumption

- Low operating voltage

- Easy to use SPI interface

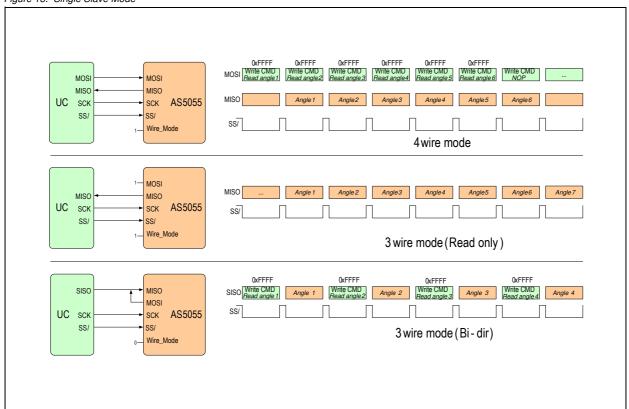

#### 8.1 SPI Interface

The 16-bit SPI Interface enables read / write access to the register blocks and is compatible to a standard micro controller interface. The SPI module is active as soon as /SS pin is pulled low. The AS5055 then reads the digital value on the MOSI (master out slave in) input with every falling edge of SCK and writes on its MISO (master in slave out) output with the rising edge. After 16 clock cycles /SS has to be set back to a high status in order to reset some parts of the interface core. The SPI Interface can be set in two different modes: 3-wire mode or 4-wire mode.

#### Notes:

- 1. The wire mode selection is read during the POWER-UP state and can be changed with a power on reset or a software reset command.

- 2. For more stability on the SPI Interface, it is very important to place filters. The filter must be placed close to the driving outputs. For further information, please refer to the application note AN5000\_SPI\_Interface.

Table 14. Wire Mode Selection

| Wire Mode Selection (pad 14) |             |  |  |  |  |

|------------------------------|-------------|--|--|--|--|

| wire_mode = LO               | 3-wire mode |  |  |  |  |

| wire_mode = HI               | 4-wire mode |  |  |  |  |

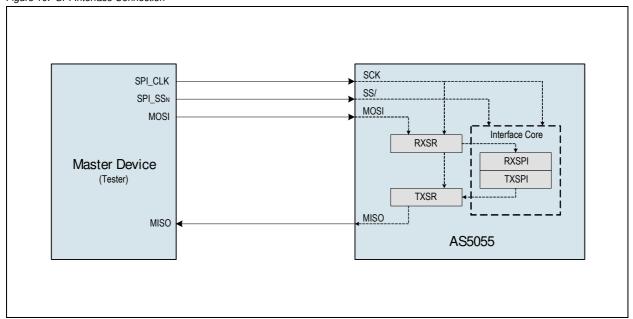

#### 8.1.1 SPI Interface Signals (4-Wire Mode, Wire mode = 1)

The AS5055 only supports slave operation mode. Therefore SCK for the communication as well as the /SS signal has to be provided by the test equipment. The following picture shows a basic interconnection diagram with one master and an AS5055 device and a principle schematic of the interface core.

Figure 10. SPI Interface Connection

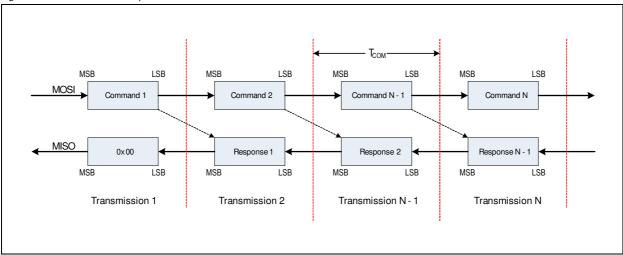

Because the interface has to decode the sent command before it can react and provide data the response of the chip to a specific command applied at a time T can be accessed in the next transmission cycle ending at T + TCOM.

The data are sent and read with MSB first. Every time the chip is accessed it is sending and receiving data.

Figure 11. SPI Command / Response Data Flow

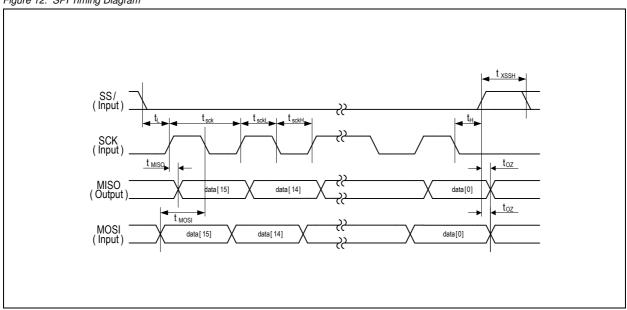

#### 8.1.2 SPI Timing

Figure 12. SPI Timing Diagram

Table 15. SPI Timing Characteristics

| Parameter         | Description                                       | Min                 | Max | Unit |

|-------------------|---------------------------------------------------|---------------------|-----|------|

| tL                | Time between SS/ falling edge and SCK rising edge | 10 (see note 1)     |     | ns   |

| tL                | Time between SS/ falling edge and SCK rising edge | 350<br>(see note 2) |     | ns   |

| tsck              | Serial clock period                               | 100                 |     | ns   |

| t <sub>SCKL</sub> | Low period of serial clock                        | 50                  |     | ns   |

| tscкн             | High period of serial clock                       | 50                  |     | ns   |

Table 15. SPI Timing Characteristics

| Parameter         | Description                                                  | Min                  | Max | Unit |

|-------------------|--------------------------------------------------------------|----------------------|-----|------|

| t <sub>H</sub>    | Time between last falling edge of SCK and rising edge of SS/ | t <sub>SCK</sub> / 2 |     | ns   |

| txssн             | High time of SS/ between two transmissions                   | 10<br>(see note 1)   |     | ns   |

| txssн             | High time of SS/ between two transmissions                   | 350<br>(see note 2)  |     | ns   |

| t <sub>MOSI</sub> | Data input valid to clock edge                               | 20                   |     | ns   |

| t <sub>MISO</sub> | SCK edge to data output valid                                |                      | 20  | ns   |

#### Notes:

- 1. No synchronization needed because the internal clock is inactive.

- 2. Synchronization with the internal clock  $\rightarrow$  2 \* t<sub>CLK\_SYS</sub> + 10ns (e.g. at 8 MHz  $\rightarrow$  253 ns).

#### 8.1.3 SPI Connection to the Host $\mu$ C

Single Slave Mode.

Figure 13. Single Slave Mode

Note: 3 Wire Mode (read only): If the ERROR FLAG is set the device must be externally reset.

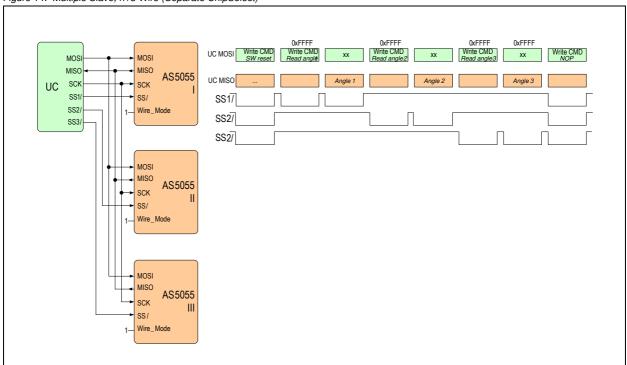

#### Multiple Slave, n+3 Wire (Separate ChipSelect).

Figure 14. Multiple Slave, n+3 Wire (Separate ChipSelect)

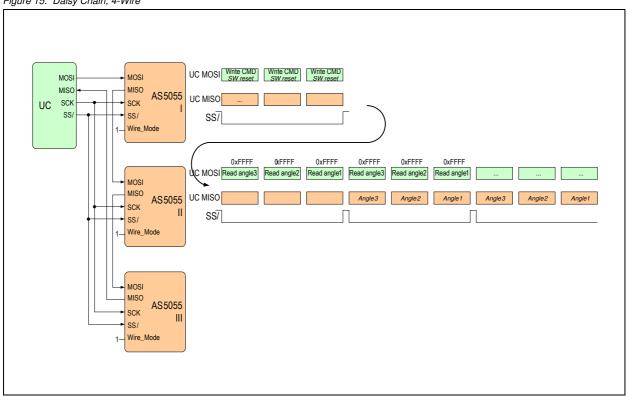

#### Daisy Chain, 4 Wire.

Figure 15. Daisy Chain, 4-Wire

#### 8.2 Placement of the Magnet

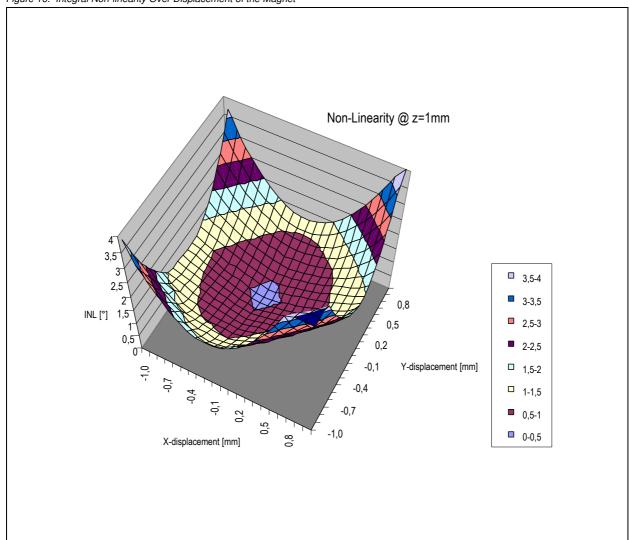

Non-Linearity Error over Displacement.

As shown in Figure 17, the recommended horizontal position of the magnet axis is over the diagonal center of the IC.

Figure 16 shows a typical error curve at a vertical magnet distance of 1.0mm, measured with a NdFeB N35H magnet with 6mm diameter and 2.5mm height.

The X- and Y- axis of the graph indicate the lateral displacement of the magnet center with respect to the IC center.

At X = Y = 0, the magnet is perfectly centered over the IC. The total displacement plotted on the graph is for ±1mm in both directions.

The Z-axis displays the worst case INL error over a full turn at each given X-and Y- displacement. The error includes the quantization error of  $\pm \frac{1}{2}$  LSB. At the sample shown in Figure 16, the accuracy for a centered magnet is better than 0.5°. Within a radius of 0.5mm, the accuracy is about 1.0° (spec = 1.41° over temperature).

Figure 16. Integral Non-linearity Over Displacement of the Magnet

## 9 Package Drawings and Markings

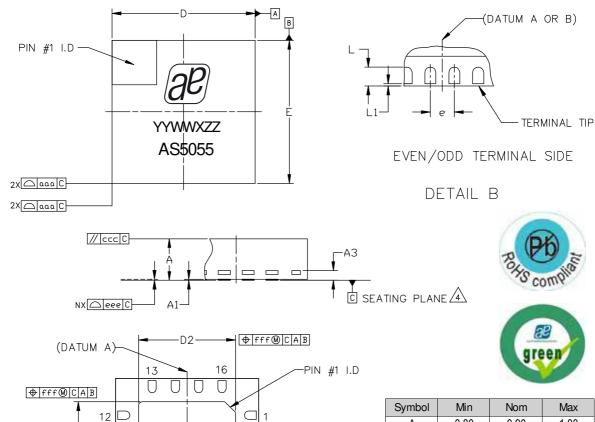

The device is available in a 16-pin QFN (4x4x0.85 mm) package.

Figure 17. Drawings and Dimensions

# SEE DETAIL B NX L NX b blobb@CAB ddd@C

#### Notes:

- 1. Dimensions and tolerancing conform to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. Angles are in degrees.

- 3. Dimension b applies to metallized terminal and is measured between 0.25mm and 0.30mm from terminal tip. Dimension L1 represents terminal full back from package edge up to 0.15mm is acceptable.

- 4. Coplanarity applies to the exposed heat slug as well as the terminal.

- 5. Radius on terminal is optional.

- 6. N is the total number of terminals.

| Symbol | Min      | Nom      | Max  |  |  |  |  |

|--------|----------|----------|------|--|--|--|--|

| Α      | 0.80     | 0.90     | 1.00 |  |  |  |  |

| A1     | 0        | 0.02     | 0.05 |  |  |  |  |

| A3     |          | 0.20 REF |      |  |  |  |  |

| L      | 0.45     | 0.50     | 0.55 |  |  |  |  |

| L1     | 0        | -        | 0.15 |  |  |  |  |

| b      | 0.25     | 0.30     | 0.35 |  |  |  |  |

| D      |          | 4.00 BSC |      |  |  |  |  |

| Е      |          | 4.00 BSC |      |  |  |  |  |

| е      | 0.65 BSC |          |      |  |  |  |  |

| D2     | 2.30     | 2.40     | 2.50 |  |  |  |  |

| E2     | 2.30     | 2.40     | 2.50 |  |  |  |  |

| aaa    | -        | 0.15     | -    |  |  |  |  |

| bbb    | -        | 0.10     | -    |  |  |  |  |

| CCC    | -        | 0.10     | -    |  |  |  |  |

| ddd    | -        | 0.05     | -    |  |  |  |  |

| eee    | -        | 0.08     | -    |  |  |  |  |

| fff    | - 0.10 - |          |      |  |  |  |  |

| N      | 16       |          |      |  |  |  |  |

#### Marking: YYWWXZZ.

| YY                      | ww   | X                         | ZZ                         |

|-------------------------|------|---------------------------|----------------------------|

| Year (i.e. 04 for 2004) | Week | Assembly plant identifier | Assembly traceability code |

## Revision History

| Revision | Date         | Owner | Description                                                                                                                                                             |

|----------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 23 Mar, 2010 | jja   | Initial revision of public release version                                                                                                                              |

| 1.1      | 8 Jun, 2010  | jlu   | Updated Pin Descriptions (pin 16), Typical Application, SPI Connection to the Host $\mu$ C, Figure 3, Figure 13, Figure 14, Figure 15.                                  |

| 1.11     | 3 Nov, 2010  | agt   | Updated Absolute Maximum Ratings, System Parameters, Pin Descriptions, Power Supply Filter, Table 9, SPI Connection to the Host $\mu$ C, Package Drawings and Markings. |

| 1.12     | 3 Nov, 2011  | mub   | Updated operating temperature range.                                                                                                                                    |

| 1.13     | 28 Dec, 2011 | rei   | Updated Figure 3, Table 9 and package drawings.                                                                                                                         |

**Note:** Typos may not be explicitly mentioned under revision history.

# 10 Ordering Information

The devices are available as the standard products shown in Table 16.

Table 16. Ordering Information

| Ordering Code | Description                              | Delivery Form | Package                  |

|---------------|------------------------------------------|---------------|--------------------------|

| AS5055 EQFT   | 12-bit low power magnetic rotary encoder | Tape & Reel   | 16-pin QFN (4x4x0.85 mm) |

Note: All products are RoHS compliant and austriamicrosystems green.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

Technical Support is available at http://www.austriamicrosystems.com/Technical-Support

For further information and requests, please contact us mailto: sales@austriamicrosystems.com or find your local distributor at http://www.austriamicrosystems.com/distributor

#### Copyrights

Copyright © 1997-2012, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### Contact Information

Headquarters

austriamicrosystems AG

Tobelbaderstrasse 30

A-8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact