### General Description

The DS26900 is a JTAG signal multiplexer providing connectivity between one of three master ports and up to 18 (36 in cascade configuration) secondary ports. The device is fully configurable from any one of the three master ports. The DS26900 can automatically detect the presence JTAG devices on the secondary ports.

The DS26900 can be used in multiple configurations including as a single device, two cascaded devices, or two redundant devices.

All device control and configuration is accomplished through standard JTAG operations via the selected master port.

#### Applications

MicroTCA® Chassis ATCA® Chassis AMC Carrier Cards JSM Modules System Level JTAG

#### MCH1 MASTER3 MCH2 MASTER2 MASTER2 MASTER1 MASTER3 AMC1 AMC2 AMC2 AMC2 AMC3 AMC4 AMC4 AMC4 AMC1

MicroTCA JSM Functional Diagram

MicroTCA and ATCA are registered trademarks of PICMG.

Features

- Efficient Solution for Star Architecture JTAG

- Provides Transparent Communications Between the Arbitrated Master and a Selected Secondary Port

- Single-Package Solution Provides 18 Secondary Ports

- Two-Package Cascade Configuration Provides 36 Secondary Ports

- Three Arbitrated Master Ports

- Autodetection of Port Presence

- Internal Pullup/Down Resistors

- Two 32-Bit Scratchpad Registers

- Four GPIO Pins for Read/Write Control and Signaling Applications

- Operation Up to 50MHz

- Signal Path Modification Options

- Redundancy with High-Impedance Pin

- Independent Periphery JTAG

- Configuration Mode Uses IEEE 1149.1 TAP

Controller

- Supports Live Insertion/Withdrawal

- 3.3V Operation

- Industrial Temperature Operation

- RoHS-Compliant Packaging

#### Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| DS26900LN+ | -40°C to +85°C | 144 LQFP    |

+Denotes a lead(Pb)-free/RoHS-compliant package.

#### M/IXI/M

Maxim Integrated Products 1

Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: <u>www.maxim-ic.com/errata</u>. For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# Table of Contents

| 1.  | BLOCK DIAGRAM                                                                                                                      | 6    |

|-----|------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.  | PIN DESCRIPTIONS                                                                                                                   | 7    |

| 3.  | FUNCTIONAL DESCRIPTION                                                                                                             | 19   |

| 4.  | DETAILED DESCRIPTION                                                                                                               | 20   |

| 4.1 | MODES OF OPERATION                                                                                                                 | 20   |

| 4.  | 1.1 Single-Package Mode                                                                                                            |      |

|     | 1.2 Cascade Configuration Modes                                                                                                    |      |

|     | 1.3 Deselect Mode and Redundancy                                                                                                   |      |

| 4.2 |                                                                                                                                    |      |

|     | <ul> <li>2.1 Missing Test Master or Unused Test Master Port.</li> <li>2.2 Detection of the Presence of Secondary Ports.</li> </ul> |      |

|     | 2.3 Selection of the Secondary Port                                                                                                |      |

|     | 2.4 Master Port/Secondary Port Path Timing Description                                                                             | . 24 |

| 4.3 | GPIO PINS—GENERAL-PURPOSE I/O                                                                                                      | 25   |

| 4.4 | PROGRAMMABLE PULLUP/PULLDOWN RESISTORS                                                                                             |      |

| 4.5 | SIGNAL PATH CONFIGURATION—INVERSIONS                                                                                               |      |

| 4.6 | SWITCH CONFIGURATION BY EXTERNAL TEST MASTER                                                                                       |      |

| 4.7 | SWITCH CONFIGURATION BY TEST MASTER 1 OR TEST MASTER 2                                                                             | 26   |

| 5.  | RESETS                                                                                                                             | 27   |

| 5.1 | GLOBAL RESET USAGE                                                                                                                 | 27   |

| 5.2 | SECONDARY PORT RESETS                                                                                                              |      |

| 6.  | CONFIGURATION MODE                                                                                                                 |      |

| 6.1 | SWITCH TAP CONTROLLER                                                                                                              |      |

| -   | 1.1 Switch Instructions                                                                                                            |      |

| 7.  | DEVICE REGISTERS.                                                                                                                  |      |

|     |                                                                                                                                    |      |

| 8.  | ADDITIONAL APPLICATION INFORMATION                                                                                                 |      |

| 8.1 | ACCESSING INDIVIDUAL DEVICE JTAG ON A BOARD                                                                                        |      |

| 8.2 | USING LED INDICATORS ON THE SSPI, ACT AND MCI PINS                                                                                 |      |

| 8.3 | USING 2.7V AND 1.8V LOGIC LEVELS WITH THE DS26900                                                                                  |      |

| 8.4 | SERIES TERMINATION RESISTORS                                                                                                       | 37   |

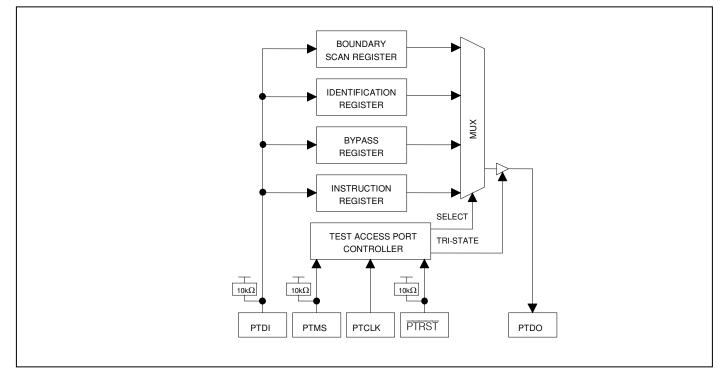

| 9.  | PERIPHERY JTAG                                                                                                                     | 38   |

| 9.1 | PERIPHERY JTAG DESCRIPTION                                                                                                         | 38   |

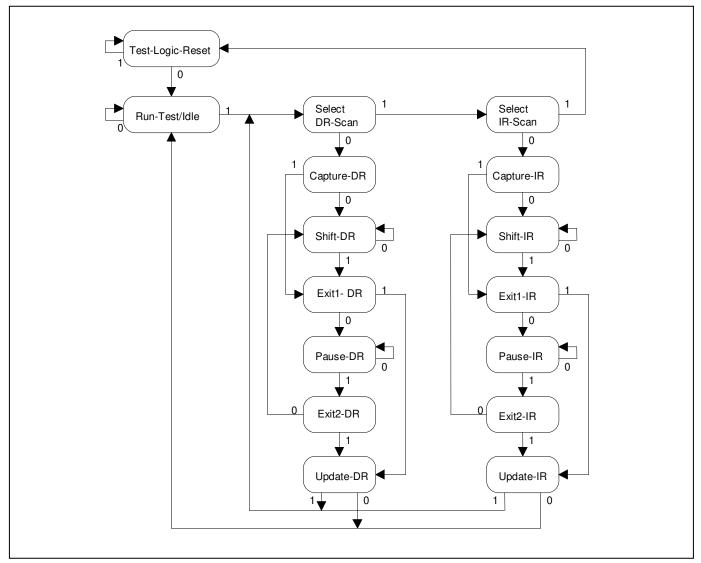

| 9.2 | JTAG TAP CONTROLLER STATE MACHINE DESCRIPTION                                                                                      | 39   |

| 9.3 | JTAG INSTRUCTION REGISTER AND INSTRUCTIONS                                                                                         |      |

|     | 3.1 SAMPLE/PRELOAD                                                                                                                 |      |

|     | 3.2 EXTEST                                                                                                                         |      |

|     | 3.3 BYPASS                                                                                                                         |      |

|     | 3.4 IDCODE                                                                                                                         |      |

|     | 3.6 CLAMP                                                                                                                          |      |

| 9.4 |                                                                                                                                    |      |

| 9.  | 4.1 Bypass Register                                                                                                                | . 42 |

|     | 4.2 Identification Register                                                                                                        |      |

| 9.  | 4.3 Boundary Scan Register                                                                                                         | . 42 |

| 10. | OPERATING PARAMETERS            |            |

|-----|---------------------------------|------------|

|     |                                 |            |

| 11. | AC TIMING                       |            |

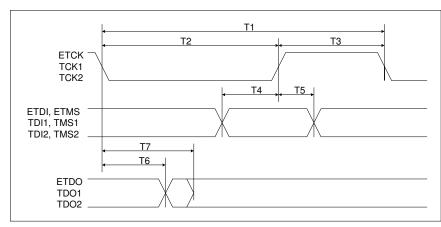

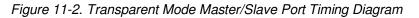

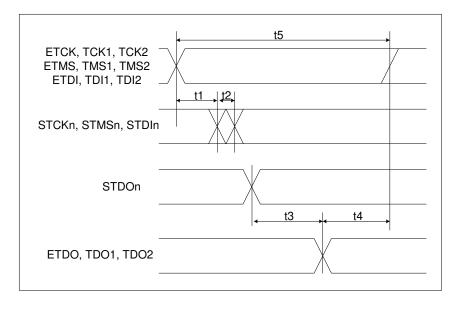

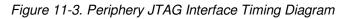

| 11. | 1.2 TRANSPARENT MODE MASTER/SLA | ACE TIMING |

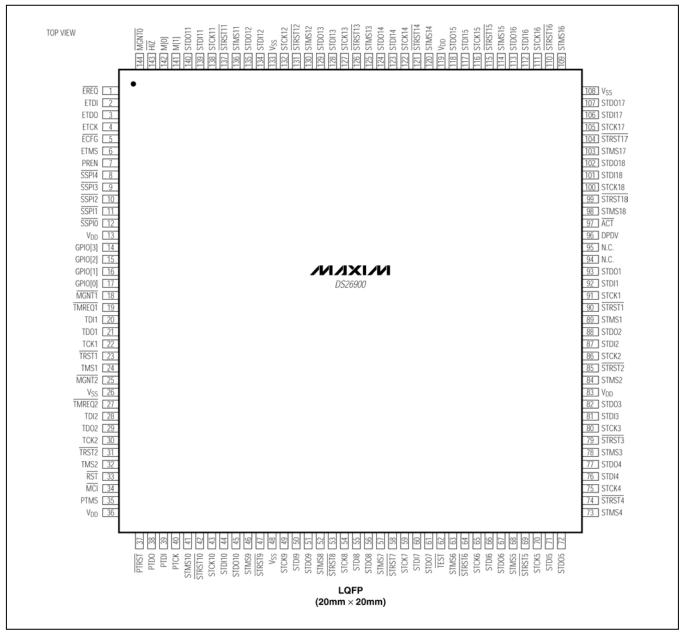

| 12. | PIN CONFIGURATION               |            |

| 13. | PACKAGE INFORMATION             |            |

| 14. | DOCUMENT REVISION HISTORY       |            |

# List of Figures

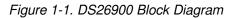

| Figure 1-1. DS26900 Block Diagram                              | 6  |

|----------------------------------------------------------------|----|

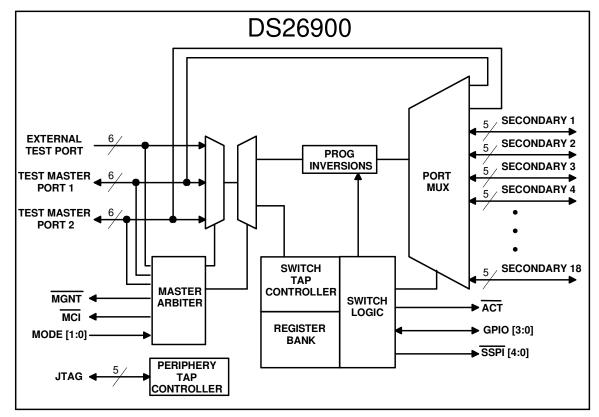

| Figure 4-1. Configuration for 3 Masters, 18 Secondary Ports    | 20 |

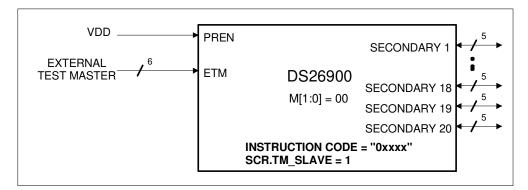

| Figure 4-2. Configuration for 1 Master, 20 Secondary Ports     | 20 |

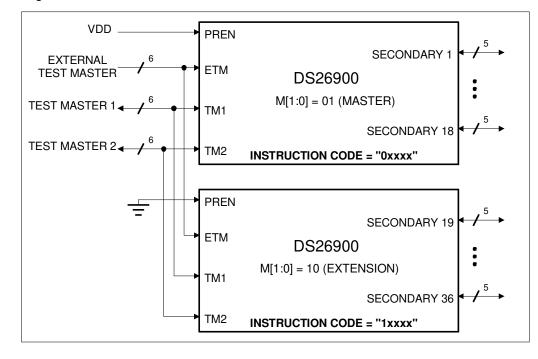

| Figure 4-3. Two Cascaded Devices                               | 21 |

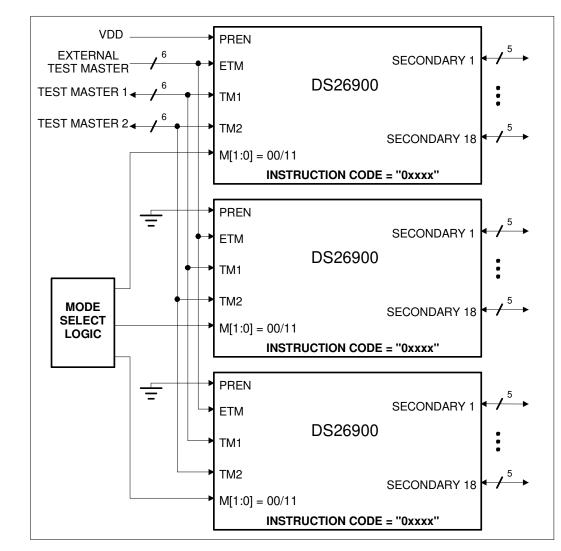

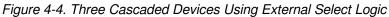

| Figure 4-4. Three Cascaded Devices Using External Select Logic | 22 |

| Figure 9-1. Periphery JTAG Block Diagram                       | 38 |

| Figure 9-2. JTAG TAP Controller State Machine                  | 39 |

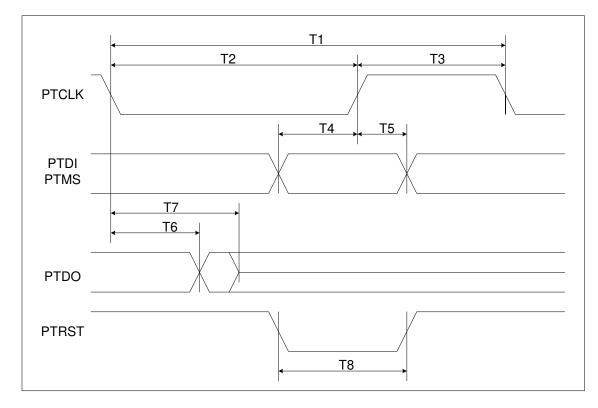

| Figure 11-1. Switch TAP Controller Interface Timing Diagram    | 44 |

| Figure 11-2. Transparent Mode Master/Slave Port Timing Diagram | 45 |

| Figure 11-3. Periphery JTAG Interface Timing Diagram           | 46 |

# List of Tables

| Table 2-1. Pin Descriptions (Sorted by Function)            | 7  |

|-------------------------------------------------------------|----|

| Table 2-2. Pin Description (Sorted by Pin Number)           | 13 |

| Table 4-1. Mode Pins                                        | 20 |

| Table 4-2. Master Arbitration                               | 23 |

| Table 4-3. ACT Output States                                | 24 |

| Table 6-1. Switch TAP Instruction Codes                     | 28 |

| Table 7-1. DS26900 List of Registers                        | 31 |

| Table 7-2. Secondary Port Selection Bits and Indicator Pins | 35 |

| Table 9-1. Periphery JTAG Instruction Codes                 | 41 |

| Table 10-1. Thermal Characteristics                         | 43 |

| Table 10-2. Recommended DC Operating Conditions             | 43 |

| Table 10-3. DC Electrical Characteristics                   | 43 |

| Table 11-1. Switch TAP Controller Interface Timing          | 44 |

| Table 11-2. Master/Slave Port Timing                        | 45 |

| Table 11-3. Periphery JTAG Interface Timing                 | 46 |

# 1. Block Diagram

# 2. Pin Descriptions

Table 2-1. Pin Descriptions (Sorted by Function)

| NAME  | PIN | TYPE       | FUNCTION                                                                                                                                                                                                                                                                                                                                |

|-------|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETCK  | 4   | lpd        | <b>External Test Master Clock.</b> In configuration mode, a falling edge on this pin clocks data in on the ETDI pin. A falling edge on this pin clocks data out on the ETDO pin.                                                                                                                                                        |

|       |     |            | When PREN = $V_{DD}$ , a 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                                                       |

| ETDI  | 2   | lpd        | <b>External Test Master Serial Data Input.</b> In configuration mode, data is clocked in on this pin on the falling edge of ETCK.                                                                                                                                                                                                       |

|       |     | -          | When PREN = $V_{DD}$ , a 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                                                       |

| ETDO  | 3   | O/<br>High | <b>External Test Master Serial Data Out.</b> (High Impedance) Data is clocked out on this pin on the falling edge of ETCK.                                                                                                                                                                                                              |

|       |     | Impedance  | When PREN = $V_{DD}$ , a 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                                         |

| ECFG  | 5   | lpu        | <b>External Test Master Configuration (Active Low).</b> Asserting this pin low along with EREQ asserted low allows the External Test Master to configure the DS26900, allowing access to the Switch TAP Controller. Toggling ECFG when EREQ is high has no effect.                                                                      |

|       |     |            | When PREN = $V_{DD}$ , a 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                                         |

| ETMS  | 6   | lpu        | <b>External Test Master Test Mode Select.</b> This pin is sampled on the rising edge of ETCK and is used to place the port into the various defined IEEE 1149.1 states.                                                                                                                                                                 |

|       |     |            | When PREN = $V_{DD}$ , a 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                                         |

| EREQ  | 1   | lpu        | <b>External Test Master Request (Active Low).</b> (Internal 10k $\Omega$ Pullup) When active, this pin selects the external test port as the master. When switching $\overline{\text{EREQ}}$ , none of the master clocks should be toggling.                                                                                            |

| MGNTO | 144 | 0          | Master Grant 0 (Active Low). Asserted low when the external test master is the arbitrated master.                                                                                                                                                                                                                                       |

|       |     |            | Test Master 1 Test Port Clock                                                                                                                                                                                                                                                                                                           |

| TCK1  | 22  | lpd/O      | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                                              |

|       |     |            | When PREN = $V_{DD}$ , an internal 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                                             |

|       |     |            | Test Master 1 Test Port Serial Data Input                                                                                                                                                                                                                                                                                               |

| TDI1  | 20  | lpu/O      | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                                              |

|       |     |            | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                               |

|       |     |            | Test Master 1 Test Port Serial Data Out                                                                                                                                                                                                                                                                                                 |

| TDO1  | 21  | I/O        | Master Mode = Output<br>Slave Mode = Input                                                                                                                                                                                                                                                                                              |

|       |     |            | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                               |

| TRST1 | 23  | lpu/O      | <b>Test Master 1 Test Port Test Reset (Active Low).</b> Asserting this pin low (when master) puts the DS26900 into configuration mode, allowing access to the Switch TAP Controller. Toggling TRST1 when not the arbitrated master has no effect. This pin does not directly affect secondary port resets.<br>Master Mode = TRST1 Input |

|       |     |            | Slave Mode = TRST1 Output                                                                                                                                                                                                                                                                                                               |

|       |     |            | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                               |

| NAME   | PIN | TYPE  | FUNCTION                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |

|--------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |     |       | Test Master 1 Test Port Test Mode Select                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |

| TMS1   | 24  | lpd/O | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                            |

|        |     |       | When PREN = $V_{DD}$ , an internal 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |

| TMREQ1 | 19  | lpu   | <b>Test Master 1 Master Request (Active Low).</b> (Internal $10k\Omega$ Pullup) When $\overline{\text{EREQ}}$ is inactive and $\overline{\text{TMREQ1}}$ is active, this pin selects the test master port 1 as the master. When switching $\overline{\text{TMREQ1}}$ , none of the master clocks should be toggling. |                                                                                                                                                                                                                                                                                                            |

| MGNT1  | 18  | 0     | Master Grant 1 (Active Low). Asserted low when Test Master 1 is the arbitrated master.                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |

|        |     |       | Test Master 2 Test Port Clock                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                            |

| TCK2   | 30  | lpd/O | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                            |

|        |     |       | When PREN = $V_{DD}$ , an internal 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |

|        |     |       | Test Master 2 Test Port Serial Data Input                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                            |

| TDI2   | 28  | lpu/O | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                            |

|        |     |       | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                            |

|        |     |       | Test Master 2 Test Port Serial Data Out                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                            |

| TDO2   | 29  | I/O   | Master Mode = Output<br>Slave Mode = Input                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                            |

|        |     |       | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                            |

| TRST2  | 31  | 31    | lpu/O                                                                                                                                                                                                                                                                                                                | <b>Test Master 2 Test Port Test Reset (Active Low).</b> Asserting this pin low (when master) puts the DS26900 into configuration mode, allowing access to the Switch TAP Controller. Toggling TRST2 when not the arbitrated master has no effect. This pin does not directly affect secondary port resets. |

|        |     |       | Master Mode = TRST2 Input<br>Slave Mode = TRST2 Output                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |

|        |     |       | When PREN = $V_{DD}$ , an internal $10k\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |

|        |     |       | Test Master 2 Test Port Test Mode Select                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |

| TMS2   | 32  | lpd/O | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                            |

|        |     |       | When PREN = $V_{DD}$ , an internal 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |

| TMREQ2 | 27  | lpu   | <b>Test Master 2 Master Request (Active Low)</b> (Internal 10k $\Omega$ Pullup) When EREQ and TMREQ1 are inactive and TMREQ2 is active, this pin selects the test master port 2 as the master. When switching TMREQ2, none of the master clocks should be toggling.                                                  |                                                                                                                                                                                                                                                                                                            |

| MGNT2  | 25  | 0     | Master Grant 2 (Active Low). Asserted low when Test Master 2 is the arbitrated master.                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                            |

| STCK1  | 91  | 0     | Secondary Port 1 Test Clock                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |

| STDI1  | 92  | 0     | Secondary Port 1 Serial Data In                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                            |

| STDO1  | 93  | lpu   | Secondary Port 1 Serial Data Out (Internal 10kΩ Pullup)                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                            |

| STRST1 | 90  | 0     | Secondary Port 1 Test Reset (Active Low)                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |

| STMS1  | 89  | 0     | Secondary Port 1 Test Mode Select (Internal 20kΩ Pulldown)                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                            |

| STCK2  | 86  | 0     | Secondary Port 2 Test Clock                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                            |

| STDI2  | 87  | 0     | Secondary Port 2 Serial Data Input                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                            |

| STDO2  | 88  | lpu   | Secondary port 2 Serial Data Out (Internal 10kΩ Pullup)                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                            |

| STRST2 | 85  | 0     | Secondary Port 2 Test Reset (Active Low)                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                            |

| NAME    | PIN | TYPE | FUNCTION                                                          |

|---------|-----|------|-------------------------------------------------------------------|

| STMS2   | 84  | 0    | Secondary Port 2 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK3   | 80  | 0    | Secondary Port 3 Test Clock                                       |

| STDI3   | 81  | 0    | Secondary Port 3 Serial Data Input                                |

| STDO3   | 82  | Ipu  | Secondary Port 3 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST3  | 79  | 0    | Secondary Port 3 Test Reset (Active Low)                          |

| STMS3   | 78  | 0    | Secondary Port 3 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK4   | 75  | 0    | Secondary Port 4 Test Clock                                       |

| STDI4   | 76  | 0    | Secondary Port 4 Serial Data Input                                |

| STDO4   | 77  | lpu  | Secondary Port 4 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST4  | 74  | 0    | Secondary Port 4 Test Reset (Active Low)                          |

| STMS4   | 73  | 0    | Secondary Port 4 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK5   | 70  | 0    | Secondary Port 5 Test Clock                                       |

| STDI5   | 71  | 0    | Secondary Port 5 Serial Data Input                                |

| STDO5   | 72  | Ipu  | Secondary Port 5 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST5  | 69  | 0    | Secondary Port 5 Test Reset (Active Low)                          |

| STMS5   | 68  | 0    | Secondary Port 5 Test Mode Select (Internal $20k\Omega$ Pulldown) |

| STCK6   | 65  | 0    | Secondary Port 6 Test Clock                                       |

| STDI6   | 66  | 0    | Secondary Port 6 Serial Data Input                                |

| STDO6   | 67  | Ipu  | Secondary Port 6 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST6  | 64  | 0    | Secondary Port 6 Test Reset (Active Low)                          |

| STMS6   | 63  | 0    | Secondary Port 6 Test Mode Select (Internal $20k\Omega$ Pulldown) |

| STCK7   | 59  | 0    | Secondary Port 7 Test Clock                                       |

| STDI7   | 60  | 0    | Secondary Port 7 Serial Data Input                                |

| STDO7   | 61  | lpu  | Secondary Port 7 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST7  | 58  | 0    | Secondary Port 7 Test Reset (Active Low)                          |

| STMS7   | 57  | 0    | Secondary Port 7 Test Mode Select (Internal $20k\Omega$ Pulldown) |

| STCK8   | 54  | 0    | Secondary Port 8 Test Clock                                       |

| STDI8   | 55  | 0    | Secondary Port 8 Serial Data Input                                |

| STDO8   | 56  | Ipu  | Secondary Port 8 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST8  | 53  | 0    | Secondary Port 8 Test Reset (Active Low)                          |

| STMS8   | 52  | 0    | Secondary Port 8 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK9   | 49  | 0    | Secondary Port 9 Test Clock                                       |

| STDI9   | 50  | 0    | Secondary Port 9 Serial Data Input                                |

| STDO9   | 51  | Ipu  | Secondary Port 9 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST9  | 47  | 0    | Secondary Port 9 Test Reset (Active Low)                          |

| STMS9   | 46  | 0    | Secondary Port 9 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK10  | 43  | 0    | Secondary Port 10 Test Clock                                      |

| STDI10  | 44  | 0    | Secondary Port 10 Serial Data Input                               |

| STDO10  | 45  | Ipu  | Secondary Port 10 Serial Data Out (Internal 10kΩ Pullup)          |

| STRST10 | 42  | 0    | Secondary Port 10 Test Reset (Active Low)                         |

| STMS10  | 41  | 0    | Secondary Port 10 Test Mode Select (Internal 20kΩ Pulldown)       |

| NAME    | PIN    | TYPE | FUNCTION                                                           |

|---------|--------|------|--------------------------------------------------------------------|

| STCK11  | 138    | 0    | Secondary Port 11 Test Clock                                       |

| STDI11  | 139    | 0    | Secondary Port 11 Serial Data Input                                |

| STDO11  | 140    | lpu  | Secondary Port 11 Serial Data Out (internal 10k pullup)            |

| STRST11 | 137    | 0    | Secondary Port 11 Test Reset (Active Low)                          |

| STMS11  | 136    | 0    | Secondary Port 11 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK12  | 132    | 0    | Secondary Port 12 Test Clock                                       |

| STDI12  | 134    | 0    | Secondary Port 12 Serial Data Input                                |

| STDO12  | 135    | lpu  | Secondary Port 12 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST12 | 131    | 0    | Secondary Port 12 Test Reset (Active Low)                          |

| STMS12  | 130    | 0    | Secondary Port 12 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK13  | 127    | 0    | Secondary Port 13 Test Clock                                       |

| STDI13  | 128    | 0    | Secondary Port 13 Serial Data Input                                |

| STDO13  | 129    | lpu  | Secondary Port 13 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST13 | 126    | 0    | Secondary Port 13 Test Reset (Active Low)                          |

| STMS13  | 125    | 0    | Secondary Port 13 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK14  | 122    | 0    | Secondary Port 14 Test Clock                                       |

| STDI14  | 123    | 0    | Secondary Port 14 Serial Data Input                                |

| STDO14  | 124    | lpu  | Secondary Port 14 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST14 | 121    | 0    | Secondary Port 14 Test Reset (Active Low)                          |

| STMS14  | 120    | 0    | Secondary Port 14 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK15  | 116    | 0    | Secondary Port 15 Test Clock                                       |

| STDI15  | 117    | 0    | Secondary Port 15 Serial Data Input                                |

| STDO15  | 118    | lpu  | Secondary Port 15 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST15 | 115    | 0    | Secondary Port 15 Test Reset (Active Low)                          |

| STMS15  | 114    | 0    | Secondary Port 15 Test Mode Select (Internal 20kΩ Pulldown)        |

| STCK16  | 111    | 0    | Secondary Port 16 Test Clock                                       |

| STDI16  | 112    | 0    | Secondary Port 16 Serial Data Input                                |

| STDO16  | 113    | lpu  | Secondary Port 16 Serial Data Out (internal 10k pullup)            |

| STRST16 | 110    | 0    | Secondary Port 16 Test Reset (Active Low)                          |

| STMS16  | 109    | 0    | Secondary Port 16 Test Mode Select (Internal $20k\Omega$ Pulldown) |

| STCK17  | 105    | 0    | Secondary Port 17 Test Clock                                       |

| STDI17  | 106    | 0    | Secondary Port 17 Serial Data Input                                |

| STDO17  | 107    | lpu  | Secondary Port 17 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST17 | 104    | 0    | Secondary Port 17 Test Reset (Active Low)                          |

| STMS17  | 103    | 0    | Secondary Port 17 Test Mode Select (Internal $20k\Omega$ Pulldown) |

| STCK18  | 100    | 0    | Secondary Port 18 Test Clock                                       |

| STDI18  | 101    | 0    | Secondary Port 18 Serial Data Input                                |

| STDO18  | 102    | lpu  | Secondary Port 18 Serial Data Out (Internal 10kΩ Pullup)           |

| STRST18 | 99     | 0    | Secondary Port 18 Test Reset (Active Low)                          |

| STMS18  | 98     | 0    | Secondary Port 18 Test Mode Select (Internal 20kΩ Pulldown)        |

| N.C.    | 94, 95 | _    | No Connection                                                      |

| NAME         | PIN | TYPE  | FUNCTION                                                                                                                                                                                                                                                                                |

|--------------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSP14        | 8   | 0     | Selected Secondary Port Indicator Bit 4 (Active Low). Along with pins SSPI3, SSPI2, SSPI1, and SSPI0, this pin provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                                |

| SSP13        | 9   | Ο     | Selected Secondary Port Indicator Bit 3 (Active Low). Along with pins SSPI4, SSPI2, SSPI1, and SSPI0, this pin provides a hardware indication of the selected secondary port. See Table 7-2 for more information.                                                                       |

| SSP12        | 10  | Ο     | Selected Secondary Port Indicator Bit 2 (Active Low). Along with pins SSPI4, SSPI3, SSPI1, and SSPI0, this provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                                    |

| SSPI1        | 11  | Ο     | Selected Secondary Port Indicator Bit 1 (Active Low). Along with pins SSPI4, SSPI3, SSPI2, and SSPI0, this pin provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                                |

| <b>SSPIO</b> | 12  | 0     | Selected Secondary Port Indicator Bit 0 (Active Low). Along with pins SSPI4, SSPI3, SSPI2, and SSPI1, this pin provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                                |

| GPIO[3]      | 14  | lpd/O | <b>General-Purpose Input/Output Bit 3.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                                           |

| GPIO[2]      | 15  | lpd/O | <b>General-Purpose Input/Output Bit 2.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                                           |

| GPIO[1]      | 16  | lpd/O | <b>General-Purpose Input/Output Bit 1.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                                           |

| GPIO[0]      | 17  | lpd/O | <b>General-Purpose Input/Output Bit 0.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                                           |

| RST          | 33  | lpu   | <b>Global Reset (Active Low).</b> (Internal $10k\Omega$ Pullup) A low state on this pin provides an asynchronous reset for global registers and logic. RST should be tied high for normal operation.                                                                                    |

| TEST         | 62  | lpu   | <b>Test Enable (Active Low).</b> (Internal $10k\Omega$ Pullup) Factory test input. TEST must be tied high or unconnected for normal operation.                                                                                                                                          |

| HIZ          | 143 | I     | <b>Output High-Impedance Enable (Active Low).</b> When this pin is asserted low, internal pullup and pulldown resistors are disabled, all outputs are put into high-impedance mode, and master request inputs (EREQ, TMREQ1, TMREQ2) are disabled. PTRST must also be asserted logic 0. |

| M[1]         | 141 | lpd   | <b>Mode Select Bit 1.</b> (Internal 20kΩ Pulldown) Selects mode of operation of the device (Single-Package, Cascade-Master, Cascade-Extension, or Deselect.                                                                                                                             |

| M[0]         | 142 | lpd   | <b>Mode Select Bit 0.</b> (Internal $20k\Omega$ Pulldown) Selects mode of operation of the device (Single-Package, Cascade-Master, Cascade-Extension, or Deselect).                                                                                                                     |

| MCI          | 34  | 0     | Master Conflict Indicator (Active Low). Indicates that more than one device is<br>requesting to be master.Asserted low when more than one of the EREQ, TMREQ1, or TMREQ2 signals is<br>asserted low.                                                                                    |

| DPDV         | 96  | 0     | <b>Deselected Port Data Value.</b> This pin directly indicates the state of the DPDV bit in the Device Configuration Register ( <u>DCR</u> ).                                                                                                                                           |

| PTCK         | 40  | I     | <b>Periphery JTAG Chain Test Clock.</b> This input must be driven to a logic level during normal operation.                                                                                                                                                                             |

| PTDI         | 39  | I     | <b>Periphery JTAG Chain Serial Data Input.</b> This input must be driven to a logic level during normal operation.                                                                                                                                                                      |

| PTDO         | 38  | 0     | Periphery JTAG Chain Serial Data Out                                                                                                                                                                                                                                                    |

| NAME            | PIN                    | TYPE | FUNCTION                                                                                                                                                                                                                                                                                          |

|-----------------|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTRST           | 37                     | Ι    | <b>Periphery JTAG Chain Test Reset (Active Low).</b> During normal operation, this signal is asserted low.                                                                                                                                                                                        |

| PTMS            | 35                     | lpu  | <b>Periphery JTAG Chain Test Mode Select.</b> This input must be driven to a logic level during normal operation.                                                                                                                                                                                 |

| ACT             | 97                     | 0    | Active (Active Low). Indicates that this device is active when low. An active device is determined by the MSB of the instruction code and the state of the mode pins M0 and M1.                                                                                                                   |

| PREN            | 7                      | I    | Pull-Resistor Enable. When connected to VDD, the following pull resistors are<br>enabled:20kΩ pulldown on TCK1, TCK2, ETDI, ETCK, TMS1, TMS2<br>10kΩ pullup on TDI1, TDI2, ETDO, TDO1, TDO2, TRST1, TRST2, ECFG, ETMSWhen connected to VSS, the pull resistors on the signals above are disabled. |

|                 |                        |      | When multiple devices are connected in parallel only one device should have PREN connected = $V_{DD}$ .                                                                                                                                                                                           |

| V <sub>DD</sub> | 13, 36,<br>83, 119     | Р    | <b>Positive Supply.</b> 3.3V $\pm$ 5%. All V <sub>DD</sub> signals should be tied together.                                                                                                                                                                                                       |

| V <sub>SS</sub> | 26, 48,<br>108,<br>133 | Р    | Ground Reference. All V <sub>SS</sub> signals should be tied together.                                                                                                                                                                                                                            |

Configuration Mode. The master is communicating with the Switch TAP Controller in the DS26900.

Transparent Mode. The master is communicating directly with the selected secondary port.

All pins are I/O in periphery JTAG mode except the TEST, TMREQ1, TMREQ2, EREQ, M1, M0, HIZ, RST, PTRST, PTCK, PTDI, PTDO, and PTMS pins. All outputs are rated at 8mA.

Unused inputs must be tied to logic 1 or 0 if not used and a pullup/pulldown is not present.

O = Output

I = Input

lpu = Input with an internal pullup

lpd = Input with an internal pulldown

P = Power

Table 2-2. Pin Description (Sorted by Pin Number)

| NAME            | PIN                | TYPE       | FUNCTION                                                                                                                                                                                                                                                           |

|-----------------|--------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EREQ            | 1                  | lpu        | <b>External Test Master Request (Active Low).</b> (Internal 10k $\Omega$ Pullup) When active, this pin selects the external test port as the master. When switching EREQ, none of the master clocks should be toggling.                                            |

| ETDI            | 2                  | lpd        | <b>External Test Master Serial Data Input.</b> In configuration mode, data is clocked in on this pin on the falling edge of ETCK.                                                                                                                                  |

|                 |                    |            | When PREN = $V_{DD}$ , a 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                  |

| ETDO            | 3                  | O/<br>High | <b>External Test Master Serial Data Out.</b> (High Impedance) Data is clocked out on this pin on the falling edge of ETCK.                                                                                                                                         |

|                 |                    | Impedance  | When PREN = $V_{DD}$ , a 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                    |

| ETCK            | 4                  | lpd        | <b>External Test Master Clock.</b> In configuration mode, a falling edge on this pin clocks data in on the ETDI pin. A falling edge on this pin clocks data out on the ETDO pin.                                                                                   |

|                 |                    |            | When PREN = $V_{DD}$ , a 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                  |

| ECFG            | 5                  | lpu        | <b>External Test Master Configuration (Active Low).</b> Asserting this pin low along with EREQ asserted low allows the External Test Master to configure the DS26900, allowing access to the Switch TAP Controller. Toggling ECFG when EREQ is high has no effect. |

|                 |                    |            | When PREN = $V_{DD}$ , a 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                    |

| ETMS            | 6                  | lpu        | <b>External Test Master Test Mode Select.</b> This pin is sampled on the rising edge of ETCK and is used to place the port into the various defined IEEE 1149.1 states.                                                                                            |

|                 |                    |            | When PREN = $V_{DD}$ , a 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                    |

|                 |                    |            | <b>Pull-Resistor Enable.</b> When connected to $V_{DD}$ , the following pull resistors are enabled:                                                                                                                                                                |

| PREN            | 7                  | I          | 20k $\Omega$ pulldown on TCK1, TCK2, ETDI, ETCK, TMS1, TMS2<br>10k $\Omega$ pullup on TDI1, TDI2, ETDO, TDO1, TDO2, TRST1, TRST2, ECFG, ETMS                                                                                                                       |

|                 |                    |            | When connected to $V_{SS}$ , the pull resistors on the signals above are disabled.                                                                                                                                                                                 |

|                 |                    |            | When multiple devices are connected in parallel only one device should have PREN connected = $V_{DD}$ .                                                                                                                                                            |

| SSP14           | 8                  | О          | Selected Secondary Port Indicator Bit 4 (Active Low). Along with pins SSPI3, SSPI2, SSPI1 and SSPI0, provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                     |

| SSP13           | 9                  | 0          | Selected Secondary Port Indicator Bit 3 (Active Low). Along with pins SSPI4, SSPI2, SSPI1 and SSPI0, provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                     |

| SSPI2           | 10                 | 0          | Selected Secondary Port Indicator Bit 2 (Active Low). Along with pins SSPI4, SSPI3, SSPI1 and SSPI0, provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                     |

| SSPI1           | 11                 | Ο          | Selected Secondary Port Indicator Bit 1 (Active Low). Along with pins SSPI4, SSPI3, SSPI2 and SSPI0, provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                     |

| <b>SSPIO</b>    | 12                 | 0          | Selected Secondary Port Indicator Bit 0 (Active Low). Along with pins SSPI4, SSPI3, SSPI2 and SSPI1, provides a hardware indication of the selected secondary port. See <u>Table 7-2</u> for more information.                                                     |

| V <sub>DD</sub> | 13, 36, 83,<br>119 | Р          | <b>Positive Supply.</b> 3.3V $\pm$ 5%. All V <sub>DD</sub> signals should be tied together.                                                                                                                                                                        |

| GPIO[3]         | 14                 | lpd/O      | <b>General-Purpose Input/Output Bit 3.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                      |

| NAME            | PIN                 | TYPE    | FUNCTION                                                                                                                                                                                                                                                                                                                                              |  |

|-----------------|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GPIO[2]         | 15                  | Ipd/O   | <b>General-Purpose Input/Output Bit 2.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                                                                                                         |  |

| GPIO[1]         | 16                  | Ipd/O   | <b>General-Purpose Input/Output Bit 1.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                                                                                                         |  |

| GPIO[0]         | 17                  | Ipd/O   | <b>General-Purpose Input/Output Bit 0.</b> (Internal $20k\Omega$ Pulldown) This pin is a general-<br>purpose input/output, which can be read or driven via a register bit. This pin is in input<br>mode after a global reset.                                                                                                                         |  |

| MGNT1           | 18                  | 0       | Master Grant 1 (Active Low). Asserted low when Test Master 1 is the arbitrated master.                                                                                                                                                                                                                                                                |  |

| TMREQ1          | 19                  | lpu     | <b>Test Master 1 Master Request (Active Low).</b> (Internal $10k\Omega$ Pullup) When $\overline{\text{EREQ}}$ is inactive and $\overline{\text{TMREQ1}}$ is active, this pin selects the test master port 1 as the master. When switching $\overline{\text{TMREQ1}}$ , none of the master clocks should be toggling.                                  |  |

|                 |                     |         | Test Master 1 Test Port Serial Data Input                                                                                                                                                                                                                                                                                                             |  |

| TDI1            | 20                  | lpu/O   | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                                                            |  |

|                 |                     |         | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                                             |  |

|                 |                     |         | Test Master 1 Test Port Serial Data Out                                                                                                                                                                                                                                                                                                               |  |

| TDO1            | 21                  | I/O     | Master Mode = Output<br>Slave Mode = Input                                                                                                                                                                                                                                                                                                            |  |

|                 |                     |         | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                                             |  |

|                 |                     |         | Test Master 1 Test Port Clock                                                                                                                                                                                                                                                                                                                         |  |

| TCK1            | 22                  | lpd/O   | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                                                            |  |

|                 |                     |         | When PREN = $V_{DD}$ , an internal 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                                                           |  |

| TRST1           | 23                  | lpu / O | <b>Test Master 1 Test Port Test Reset (Active Low).</b> Asserting this pin low (when master) puts the DS26900 into configuration mode, allowing access to the Switch TAP Controller. Toggling TRST1 when not the arbitrated master has no effect. This pin does not directly affect secondary port resets.                                            |  |

| morr            | 20                  | ipu / O | Master Mode = TRST1 Input<br>Slave Mode = TRST1 Output                                                                                                                                                                                                                                                                                                |  |

|                 |                     |         | When PREN = $V_{DD}$ , an internal 10k $\Omega$ pullup resistor is connected to this pin.                                                                                                                                                                                                                                                             |  |

|                 |                     |         | Test Master 1 Test Port Test Mode Select                                                                                                                                                                                                                                                                                                              |  |

| TMS1            | 24                  | lpd/O   | Master Mode = Input<br>Slave Mode = Output                                                                                                                                                                                                                                                                                                            |  |

|                 |                     |         | When PREN = $V_{DD}$ , an internal 20k $\Omega$ pulldown resistor is connected to this pin.                                                                                                                                                                                                                                                           |  |

| MGNT2           | 25                  | 0       | Master Grant 2 (Active Low). Asserted low when Test Master 2 is the arbitrated master.                                                                                                                                                                                                                                                                |  |

| V <sub>SS</sub> | 26, 48,<br>108, 133 | Р       | Ground Reference. All V <sub>SS</sub> signals should be tied together.                                                                                                                                                                                                                                                                                |  |

| TMREQ2          | 27                  | lpu     | <b>Test Master 2 Master Request (Active Low).</b> (Internal 10k $\Omega$ Pullup) When $\overline{\text{EREQ}}$ and $\overline{\text{TMREQ1}}$ are inactive and $\overline{\text{TMREQ2}}$ is active, this pin selects the test master port 2 as the master. When switching $\overline{\text{TMREQ2}}$ , none of the master clocks should be toggling. |  |