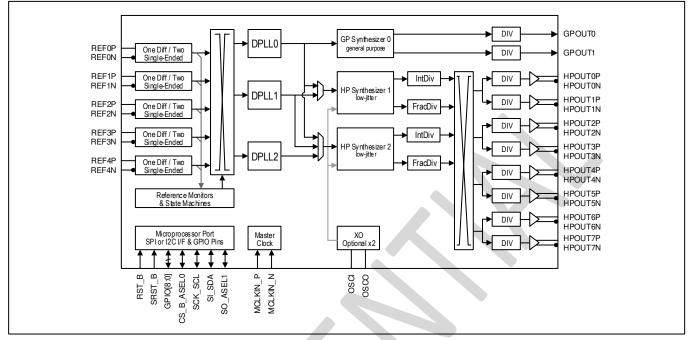

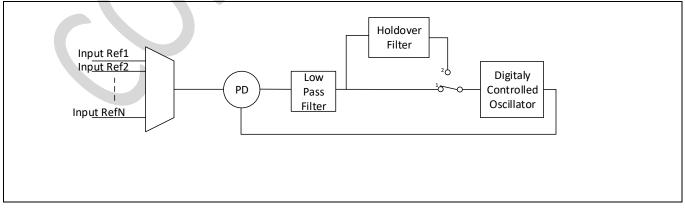

Block Diagram page 7. Register Map section 9.3

# ZL30256 3-Channel, 10-Input, 18-Output General-Purpose Jitter Attenuator

Data Sheet October 2020

# **Features**

- One, Two or Three DPLL Channels

- Programmable bandwidth, 14Hz to 470Hz

- Freerun or holdover on loss of all inputs

- Hitless reference switching

- High-resolution holdover averaging

- Per-DPLL phase adjustment, 1ps resolution

- Programmable tracking range, phase-slope limiting, frequency-change limiting and other advanced features

- Input Clocks

- Accepts up to 10 differential or CMOS inputs

- Any input frequency from 1kHz to 900MHz

- · Per-input activity and frequency monitoring

- Automatic or manual reference switching

- Revertive or nonrevertive switching

- Input-input phase measurement, 1ps resolution

- Input-DPLL phase measurement, 1ps resolution

- Per-input phase adjustment, 1ps resolution

#### Output Clock Frequency Generation

- Any output frequency from 1Hz to 1045MHz (180MHz max for Synth0)

- High-resolution fractional frequency conversion

with 0ppm error

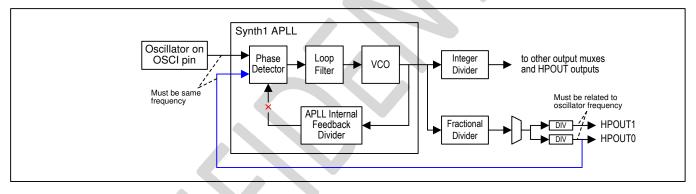

- Synthesizers 1 & 2 have integer and fractional dividers to make a total of 5 frequency families

- Output jitter from Synth 1 & 2 is <0.3ps RMS

- Output jitter from fractional dividers is typically < 1ps RMS, many frequencies <0.5ps RMS

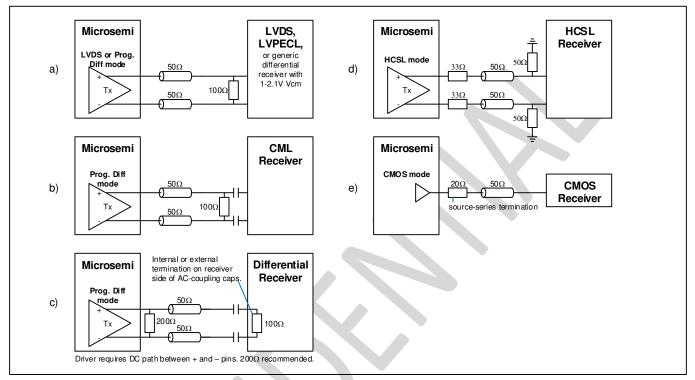

- Each HPOUTP/N pair can be LVDS, LVPECL, HCSL, 2xCMOS, HSTL or programmable diff.

- In 2xCMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz)

- Four output banks each with VDDO pin; CMOS output voltages from 1.5V to 3.3V

- Per-synthesizer phase adjust, 1ps resolution

- Per-output programmable duty cycle

#### **Ordering Information**

Trays

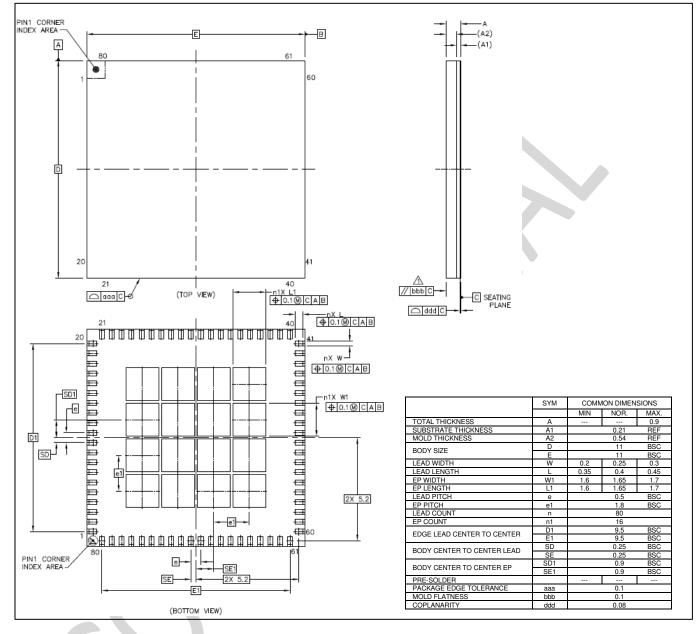

ZL30256LFG7 80-lead LGA NiAu (Pb-free) Package size: 11 x 11 mm

-40°C to +85°C

- Precise output alignment circuitry and peroutput phase adjustment

- Per-output enable/disable and glitchless start/stop (stop high or low)

- Local Oscillator

- Operates from a single low-cost XO: 23.75-25MHz, 47.5-50MHz, 114.285-125MHz

- General Features

- Automatic self-configuration at power-up from internal Flash memory

- Input-to-output alignment <200ps (ext feedback)

- Internal compensation (1ppt) for local oscillator frequency error in DPLLs and input monitors

- Numerically controlled oscillator behavior in each DPLL and each fractional output divider

- Easy-to-configure design requires no external VCXO or loop filter components

- 7 GPIO pins with many possible behaviors

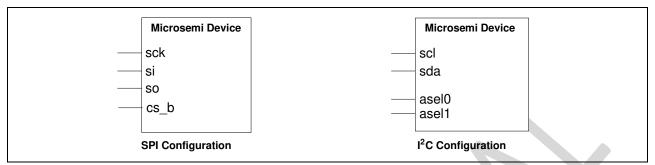

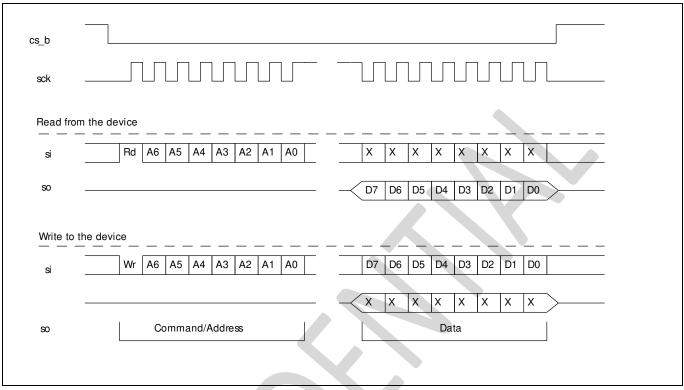

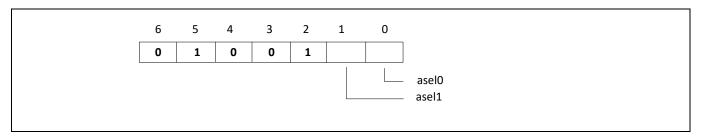

- SPI or I<sup>2</sup>C processor Interface

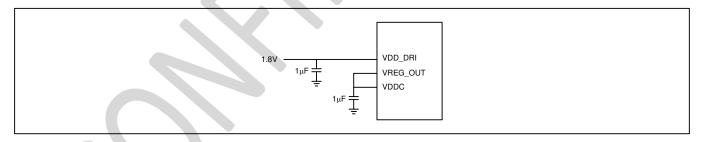

- 1.8V and 3.3V core VDD voltages

- Power: 1.3W for 2 inputs, 1 synth, 6 LVDS out

- Easy-to-use evaluation/programming software

#### **Applications**

• Jitter attenuation, frequency conversion, and frequency synthesis in a wide variety of system types

1

# Table of Contents

| 1.         | BLOCK DIAGRAM                                                                 | 7  |

|------------|-------------------------------------------------------------------------------|----|

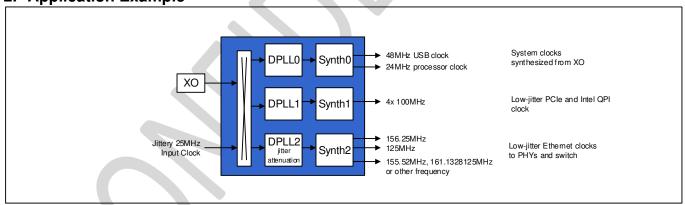

| 2.         | APPLICATION EXAMPLE                                                           | 7  |

| 3.         | DETAILED FEATURES                                                             |    |

|            |                                                                               | _  |

| 3.1        | INPUT BLOCK FEATURES                                                          | -  |

| 3.2        | DPLL FEATURES                                                                 |    |

| 3.3        | SYNTHESIZER FEATURES                                                          |    |

| 3.4        | LOW-JITTER OUTPUT CLOCK FEATURES                                              |    |

| 3.5        | GENERAL-PURPOSE OUTPUT CLOCK FEATURES                                         |    |

| 3.6        |                                                                               |    |

| 3.7        | GENERAL FEATURES                                                              |    |

| 3.8        | EVALUATION SOFTWARE                                                           |    |

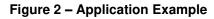

| 4.         | PIN DIAGRAM                                                                   |    |

| 5.         | PIN DESCRIPTIONS                                                              |    |

| 6.         | FUNCTIONAL DESCRIPTION                                                        | 14 |

| 6.1        | INPUT REFERENCES                                                              |    |

|            | 1.1 Input Sources                                                             | 14 |

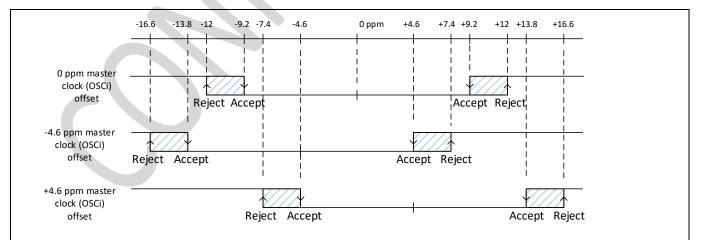

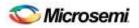

| -          | 1.2 Input Reference Monitoring                                                | 14 |

|            | 1.3 Input Gapped Clocks                                                       | 18 |

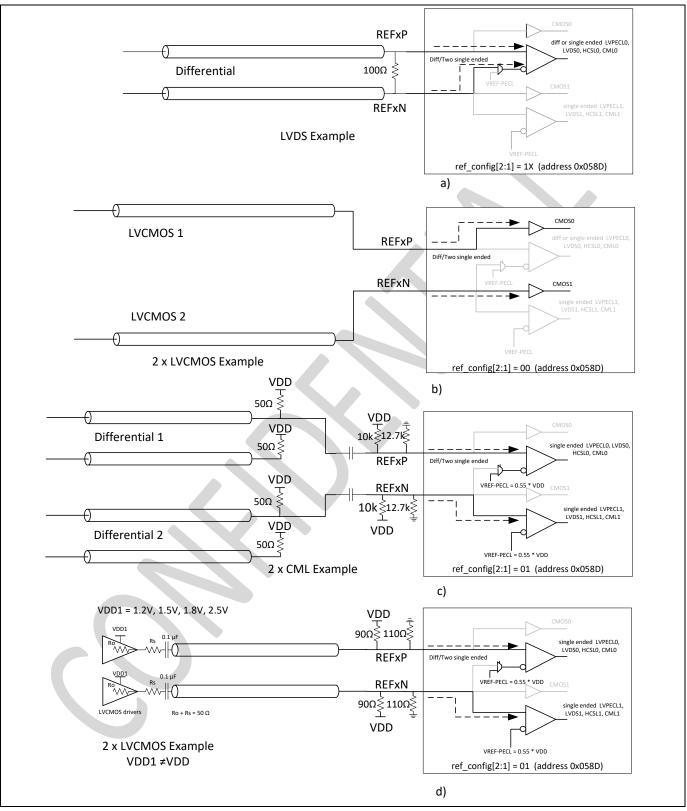

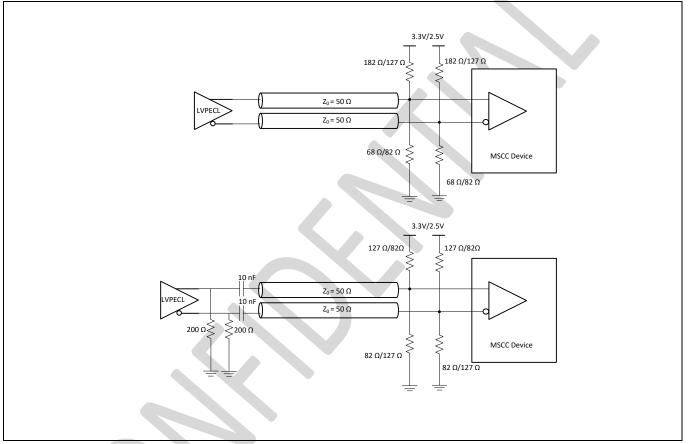

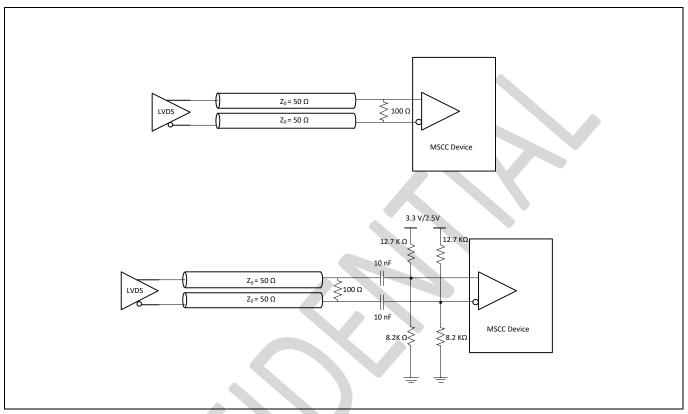

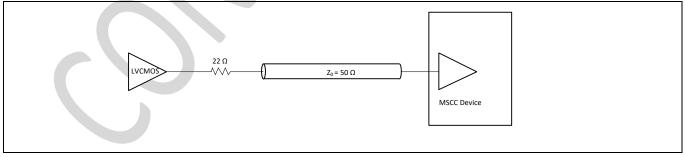

|            | 1.4 Input Buffers                                                             | 18 |

| 6.         | 1.5 Input-to-Input Phase Offset Measurement                                   | 21 |

| 6.         | 1.6 Input-to-DPLL Phase Offset Measurement                                    | 22 |

| 6.         | 1.7 Input Phase Adjustment                                                    | 22 |

| 6.2        | INPUT-OUTPUT SPECIAL FORMATS                                                  | 23 |

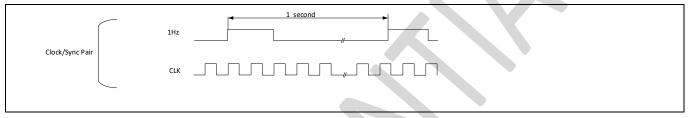

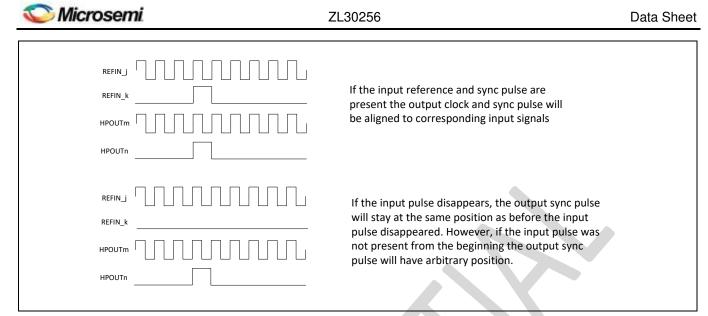

|            | 2.1 Input-Output Reference-Sync Pair                                          |    |

| 6.3        |                                                                               |    |

|            | 3.1 DPLL Input Monitoring Masks                                               |    |

| -          | 3.2 DPLL Input Reference Priority                                             |    |

|            | 3.3 DPLL Input Pull-In, Hold-In Range                                         |    |

|            | 3.4 DPLL Input Tolerance Criteria                                             |    |

|            | 3.5 DPLL Input Advance and Delay                                              |    |

|            | <ul> <li>3.6 DPLL Phase Slope Limiter</li> <li>3.7 DPLL Core Modes</li> </ul> |    |

|            | 3.8 DPLL Status Indicators                                                    |    |

|            | 3.9 DPLL Bandwidth (Jitter/Wander Transfer)                                   |    |

|            | 3.10 DPLL Programmable Damping                                                |    |

|            | 3.11 DPLL Lock Time and Fast Lock Methods                                     |    |

|            | 3.12 DPLL Hitless Reference Switching                                         |    |

| 6.         | 3.13 DPLL Holdover Capability                                                 |    |

| 6.         | 3.14 DPLL Output Frequency Offset and Master Clock Frequency Adjustment       | 29 |

| <u>6</u> . | 3.15 DPLL Supervision & Management                                            |    |

|            | 3.16 DPLL Jitter/Wander Generation                                            |    |

|            | 3.17 DPLL Frequency and Phase Reporting                                       |    |

| 6.4        |                                                                               |    |

|            | 4.1 Input-to-Output and Output-to-Output Phase Alignment                      |    |

|            | 4.2 Rate Conversion Function and FEC Support                                  |    |

|            | 4.3 Mapping DPLLs to Synthesizers                                             |    |

| 6.5        | OUTPUT FREQUENCY SYNTHESIZERS                                                 |    |

|            | 5.1 Synth0 Frequency Offset                                                   |    |

| ь.         | 5.2 Synth1 and Synth2 Fractional Dividers                                     | 34 |

🛇 Microsemi.

| 6.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3 NCO Behavior in the Fractional Dividers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <i>6.5</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <i>6.5.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.6.<br>6.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

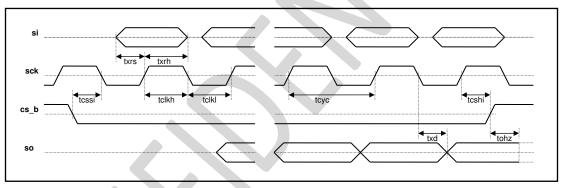

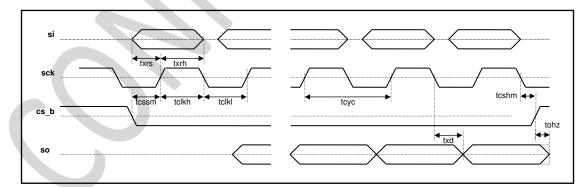

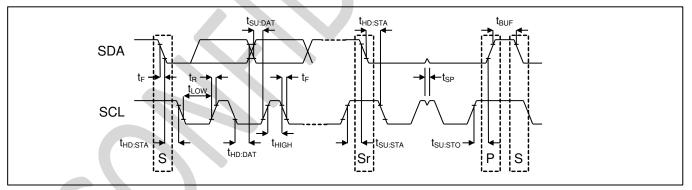

| 6.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |