# XVF3610 Voice Processor - Datasheet

Release: 5.7.2

Publication Date: 2023/01/23

# **Table of Contents**

| 1 | •            | features                                                   |

|---|--------------|------------------------------------------------------------|

|   | 1.1          | Voice Processing                                           |

|   | 1.2          | Device Interfaces                                          |

|   | 1.3          | Firmware Management                                        |

|   | 1.4          | Package                                                    |

|   | 1.5          | Power Consumption                                          |

| 2 | Prod         | luct overview                                              |

|   | 2.1          | Scope                                                      |

|   | 2.2          | Audio Processing                                           |

|   | 2.3          | Peripheral interfaces                                      |

|   | 2.4          | System firmware                                            |

| 3 | Aud          | io Processing                                              |

| 3 | 3.1          | Signal processing pipeline                                 |

|   | 3.1          | Reference signal delay                                     |

|   | 3.3          | Example applications                                       |

|   | 3.3          | Example applications                                       |

| 4 | Pin          | diagram 13                                                 |

|   | 4.1          | Pin configuration                                          |

|   | 4.2          | Signal description                                         |

| 5 | Devi         | ce interfaces 1                                            |

|   | 5.1          | PDM microphone inputs                                      |

|   | 5.2          | QSPI Boot mode                                             |

|   | 5.3          | SPI Interface                                              |

|   |              | 5.3.1 Peripheral component control                         |

|   |              | 5.3.2 SPI slave boot                                       |

|   | 5.4          | Integrated USB interface                                   |

|   | 5.5          | I2S Audio Interface                                        |

|   | 5.6          | I <sup>2</sup> C Control interface                         |

|   | 5.7          | General Purpose Input/Output                               |

| 6 | Davi         | ce operation 23                                            |

| 0 | 6.1          | ce operation   23     Power supplies   23                  |

|   | 6.2          | Clocks                                                     |

|   | 6.3          | Reset                                                      |

|   | 6.4          | Boot modes                                                 |

|   | 0.4          | 6.4.1 Slave boot mode                                      |

|   |              | 6.4.2 QSPI master boot mode                                |

|   | 6.5          | QSPI flash support                                         |

|   | 6.6          | Device firmware                                            |

|   |              |                                                            |

| 7 | <b>Dev</b> i | ce characteristics  Cleatrical and Thermal sharestaristics |

|   | /. l         | Electrical and Thermal characteristics                     |

| 8 | Swit         | ching characteristics 20                                   |

|   | 8.1          | QSPI Master (External flash for boot image storage)        |

|    | 8.3 | I2S Slave                               | 29 |

|----|-----|-----------------------------------------|----|

|    |     | kage information  Device markings       | _  |

|    | 9.2 | Order codes  Moisture Sensitivity Level | 3  |

|    |     | Hazardous Materials                     |    |

| 10 | Cop | pyright & Disclaimer                    | 33 |

The VocalFusion® XVF3610 is a high-performance voice processor, derived from XMOS xcore.ai, that is optimised for integrated and accessory voice interface applications.

**Important:** The information in this datasheet should be read in conjunction with the **XU316-1024-QF60(A/B)** datasheets which contains electrical, design and integration data for the base processor.

xcore.ai base datasheet links:

XU316-1024-QF60A

XU316-1024-QF60B

Contents:

## 1 Key features

The VocalFusion<sup>®</sup> XVF3610 is a high-performance voice processor that is optimised for integrated applications. The XVF3610 has the following key features:

### 1.1 Voice Processing

- · Two PDM microphone interfaces

- · Digital signal processing pipeline

- · Full duplex, stereo, Acoustic Echo Cancellation (AEC)

- Reference audio via I<sup>2</sup>S with automatic bulk delay insertion

- · Point noise suppression via interference canceller

- · Switchable stationary noise suppressor

- Programmable Automatic Gain Control (AGC)

- · Flexible audio output routing and filtering

- Independent audio paths for communications and Automatic Speech Recognition (ASR)

#### 1.2 Device Interfaces

- Full speed USB2.0 compliant device supporting USB Audio Class (UAC) 1.0

- · USB HID and Endpoint 0 control interfaces

- Flexible Peripheral Interfaces

- Programmable digital general-purpose inputs and outputs

- I<sup>2</sup>C interface for system control and local peripheral control

- I<sup>2</sup>S slave interface input & output of audio data

- SPI master interface for control and interrogation of a local SPI slave devices

## 1.3 Firmware Management

- · Boot from QSPI Flash

- Default firmware image for power-on operation

- · Update image delivered via USB

- · Persistent user data maintained across firmware upgrade cycles

- User-programmable setup for SPI peripherals

- Option to boot from a local host processor via SPI

- Device Firmware Update (DFU) via I<sup>2</sup>C or USB

## 1.4 Package

• 7mm x 7mm 60pin QFN package

## 1.5 Power Consumption

• Typical power consumption 300-350mW

#### 2.1 Scope

The XMOS VocalFusion® XVF3610 voice processor uses microphone array processing to capture clear, high-quality audio from anywhere in the room. XVF3610 processors use highly optimised digital signal processing algorithms to implement 'barge-in', suppress point noise sources and reduce ambient noise levels increasing the effective Signal to Noise Ratio (SNR) to achieve a reliable voice interface whatever the environment.

The processor is designed for seamless integration into consumer electronic products requiring voice interfaces for Automatic Speech Recognition (ASR), or communication and conferencing. In addition to the class-leading voice processing, XVF3610 processor implements specific features and interfaces required for use in closely integrated applications such and incorporated into a TV or set-top box.

Three modes of operation are supported by the XVF3610:

- XVF3610-UA (U-SB A-ccessory) Audio and control via a USB2.0 interface

- XVF3610-UA-HYBRID (**U**-SB **A**-ccessory **HYBRID**) Audio to the host and control via a USB2.0 interface, audio from the host via I<sup>2</sup>S master interface

- XVF3610-INT (**INT**-egrated) Audio via I<sup>2</sup>S and control over I<sup>2</sup>C interfaces

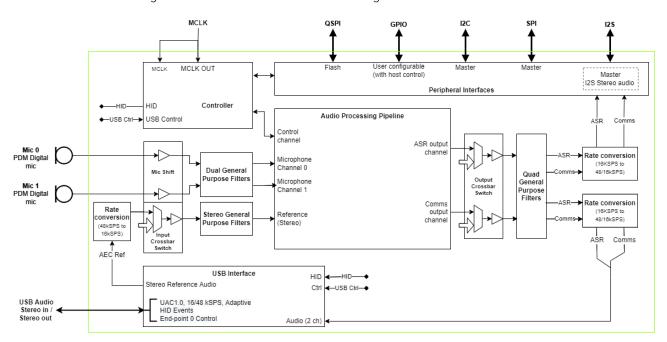

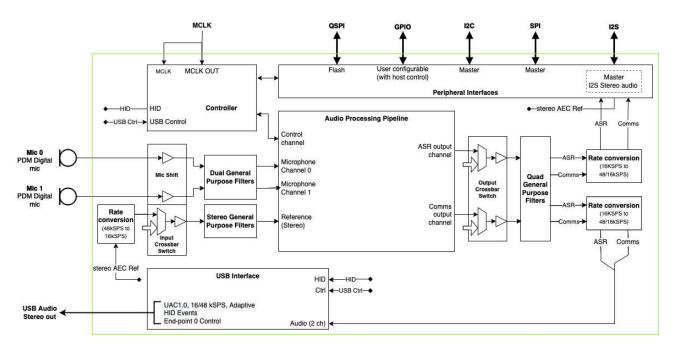

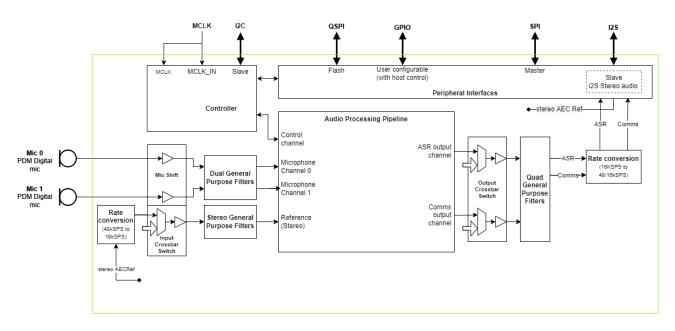

The functional block diagram of the XVF3610 is shown in the figures below:

Fig. 2.1: Functional block diagram of XVF3610 in UA configuration

Fig. 2.2: Functional block diagram of XVF3610 in UA-HYBRID configuration

Fig. 2.3: Functional block diagram of XVF3610 in INT configuration

#### 2.2 Audio Processing

The VocalFusion® XVF3610 voice processor converts and enhances audio captured using a pair of low-cost digital microphones. Processed audio streams are suitable for use in Automatic Speech Recognition or voice communications applications and benefit from a range of configurable audio processing techniques to allow customisation to the use case. The embedded audio processing provides the following features:

- 2 microphone far-field operation.

- Full 360-degree operation in "coffee table" applications or 180 degree for operation in edge-of-room products such as smart TVs.

- 16kHz voice processing, with optional 16kHz and 48kHz interface sample rates.

- Full duplex, Stereo, Acoustic Echo cancellation with a maximum tail length of 225ms accommodating highly reverberant environments. (Reference audio for cancellation provided via I<sup>2</sup>S Slave interface).

- Automatic bulk delay insertion, of up to 150ms, to account for positive or negative reference audio delays ensuring optimal echo cancellation with all audio output paths.

- Cancellation of point noise sources via a 256-frequency band Interference Canceller.

- · Switchable stationary noise suppressor.

- · Adjustable gain over a 60dB range with automatic gain control.

- · Audio output filtering and range limiter.

- · Independent audio processing paths and control of parameters for communications and ASR audio.

### 2.3 Peripheral interfaces

The VocalFusion® XVF3610 voice processor provides the following additional interfaces to increase usability and reduce total system cost:

- 4 General Purpose Output pins. These can be configured as simple digital I/O pins, Pulse Width Modulated (PWM) outputs and rate adjustable LED flashers.

- 4 General Purpose Input pins. These can be used as simple logic inputs or event capture (edge detection).

- SPI master interface to control and interrogate an SPI slave device, such as ADCs, DACs or external keyword detection devices.

### 2.4 System firmware

**Note:** The three XVF3610 configurations; one providing  $I^2S/I^2C$  interface (XVF3610-INT) and two providing a USB interface (XVF3610-UA and XVF3610-UA-HYBRID) are delivered as separate sets of firmware.

The VocalFusion® XVF3610 voice processor can be booted over SPI by a local host processor or from a separate, user-supplied, QSPI Flash memory. When operating with flash, the memory can be used for the following functions:

- A default firmware image for power-on operation.

- An upgrade image. Upgrades are provided via I<sup>2</sup>C or USB providing a host-controlled upgrade process for over-the-air device management.

- A persistent user information space to allow user-configured data such as board identifiers and serial numbers to be maintained across multiple firmware upgrade cycles.

- An upgradable user command space. Commands stored in this space are executed at boot time allowing the definition of start-up behaviour, VocalFusion<sup>®</sup> XVF3610 configuration and setup of SPI peripheral devices connected to it.

With the exception of the persistent user information the contents of the flash, and therefore the configuration of the system, can be upgraded and configured using the Device Firmware Upgrade (DFU) mechanism from the host processor.

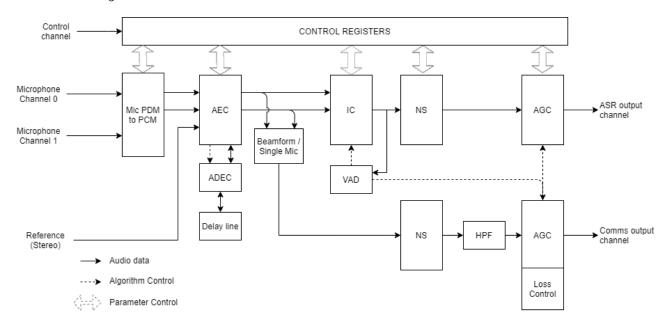

### 3.1 Signal processing pipeline

The XVF3610 audio processing pipeline takes inputs from a pair of MEMS Pulse Density Modulation (PDM) microphones and uses advanced signal processing to create audio streams suitable for use in Automatic Speech Recognition (ASR) and voice communication applications. The block diagram of this audio processing pipeline is shown in the figure below.

Fig. 3.1: The XVF3610 audio processing pipeline

The pipeline enhances the captured audio stream using a set of complementary signal enhancement and noise reduction processes:

- Microphone PDM to Pulse Code Modulation (PCM) conversion: converts the PDM audio input from the microphones into PCM format allowing further processing.

- Acoustic Echo Cancellation (AEC): enables the XVF3610 to detect voice signals in the presence of high

volume, stereo audio from the product into which it is integrated. This process takes the stereo audio

from the product as a reference signal and models the echo characteristics between each speaker and

microphone caused by the acoustic environment of the device and room. These four models are used to

continuously remove the echoes from out the audio outputs from the microphone audio input. The models

are continuously adapted to the acoustic environment to accommodate changes in the room created by

events such as doors opening or closing and people moving in the room.

- The Automatic Delay Estimation Control (ADEC): automatically monitors and manages the delay between the reference audio and the echo received by the microphone to ensure optimal AEC cancellation when the audio output latency is variable or non-zero.

- Interference Cancellation (IC): suppresses static noise from point sources such as cooker hoods, washing machines, or radios for which there is no reference audio signal available. When an internal Voice Activity

Detector (VAD) indicates the absence of voice, the IC adapts to suppress point noise sources in the environment. When voice is detected adaption is suspended maintaining suppression of the interfering noise source.

- **Noise Suppression (NS):** suppresses diffuse noise from sources whose frequency characteristics do not change rapidly over time such as air conditioning or city background noise.

- Automatic Gain Control (AGC): tunes separate AGC channels for Automatic Speech Recognition and communications output. The internal VAD is used to prevent gain changes in the ASR output channel during speech to improve speech recognition performance.

#### 3.2 Reference signal delay

As shown above, the XVF3610 includes an Automatic Delay Estimator Control(ADEC) which is used to time-align the reference and microphone signals, allowing the Acoustic Echo Canceller (AEC) to work effectively. This is an essential aspect of device operation for situations where the audio output path is unknown, such as in TVs and set-top box architectures.

The ADEC applies a time shift to one of the signals based on an automatic estimate between them, or a user-defined delay, to deliver a synchronised input to the AEC.

A delay of between 0-150ms can be applied to either the reference signal or microphone input, equivalent to 0-2400 samples at 16kHz sample frequency.

The ADEC runs in one of three modes:

- 1. **Automatic** the ADEC runs immediately after the device starts. It constantly monitors the reference signal and microphone input for changes of time alignment and automatically adjusts its delay as necessary.

- 2. **Manual** in this mode, the ADEC waits in a disabled state until the device is manually triggered by the host. The delay is estimated at the trigger point, or a selected fixed delay applied. The delay set will be used until it is changed by:

- manually applying a different fixed delay.

- · manually triggering a new delay estimate.

- switching to automatic mode.

- 3. **Estimate on Start-up** (default) The ADEC runs immediately after the device starts, calculates the delay between the two signals and applies that delay to all subsequent signals. After making the initial delay estimate and delay setting, no further changes will be made unless manually triggered or automatic mode is selected.

For further information on the usage of ADEC please refer to the XVF3610 User Guide.

## 3.3 Example applications

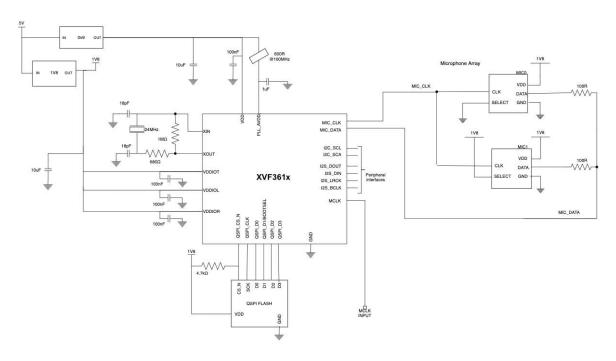

The essential components and signals for a XVF3610-INT application using QSPI flash memory with 1V8 I/0 is shown in the figure below.

Fig. 3.2: Essential components of an XVF3610-INT application with VDDIO = 1V8

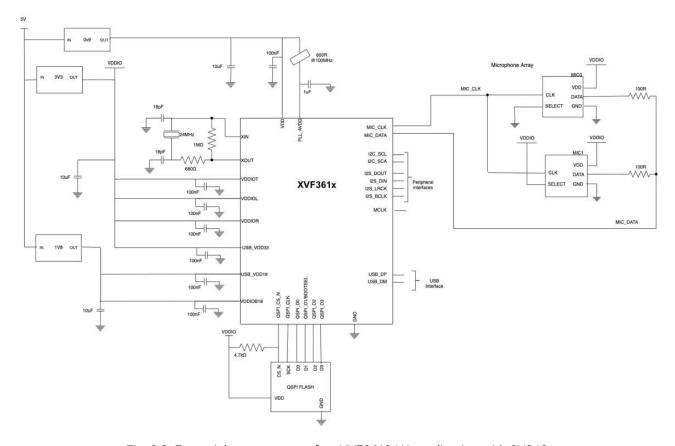

The essential components and signals for a XVF3610-UA application with 3V3 I/O is shown in the figure below.

Fig. 3.3: Essential components of an XVF3610-UA application with 3V3 IO

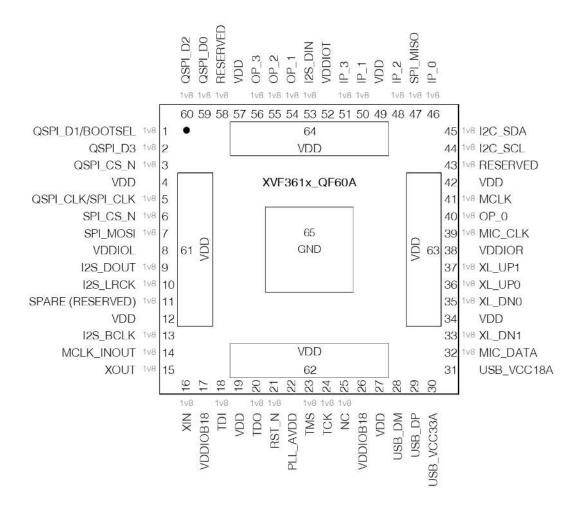

## 4 Pin diagram

### 4.1 Pin configuration

The pinout of the XVF3610, including all optional interfaces, is shown in the figure below.

Pins marked RESVD are internally connected and should remain unconnected.

Fig. 4.1: XVF3610-QF60A pin configuration

#### Note:

Two package variants are available:

```

XVF3610-QF60A - (1V8 I/0) - VDDIOT, VDDIOL and VDDIOR should be connected a 1V8 supply XVF3610-QF60B - (3V3 I/0) - VDDIOT, VDDIOL and VDDIOR should be connected a 3V3 supply

```

In both variants, VDDIO18 must be connected to a 1V8 supply and all VDD pins must be connected to a 0V9 supply. All package paddles (pins 61 to 65) must be connected. It is advised that vias be placed under paddles to connect directly to PCB supply planes

### 4.2 Signal description

The table below lists the functions of all the pins shown in Figure 2-1 above in the order they appear around the package.

#### Note:

The function of some pins changes depending on the firmware configuration loaded during boot (INT/UA).

Description Comments Pin Port Name Di-Power recrail tion X0D05 QSPI Data Line 1 IOL QSPI\_D1 / If pin is tied high via a 4.7k ohm 1/0 1 BOOTSEL and boot selection resistor on startup the device will start in SPI slave boot mode. If the pin is left floating or connected to a quad SPI D1 pin on a memory memory device, the device will start in QSPI master mode and attempt to boot from the QSPI flash memory. X0D07 2 OSPI D3 OSPI Data Line 3 1/0 IOI X0D01 QSPI\_CS\_N QSPI Boot Flash -Pull high externally to the device us-0 IOL Chip Select ing a 4.7k ohm resistor X0D10 5 OSPI CLK OSPI Clock 0 IOL / SPI\_CLK X0D00 SPI\_CS\_N Slave SPI boot / Pe-Pull high externally to the device us-IOL 6 ripheral SPI Master ing a 4.7k ohm resistor Chip Select X0D11 SPI Master Out IOI SPI MOSI Slave In 8 VDDIOI VDDIOI I/O Power Supply All VDD pins must be connected. PWR NA (1v8)I2S Data Out 9 X1D00 I2S\_DOUT Audio data out to host processor IOL 0

Table 4.1: XVF3610-QF60A pin table

continues on next page

Table 4.1 – continued from previous page

| Pin | Port      | Name            | Description                 | Comments                                                             | Di-     | Power |

|-----|-----------|-----------------|-----------------------------|----------------------------------------------------------------------|---------|-------|

|     |           | - Turing        | Decempus.                   |                                                                      | rec-    | rail  |

|     |           |                 |                             |                                                                      | tion    |       |

| 10  | X1D01     | I2S_LRCK        | I2S Left/Right clock        | 48kHz or 16KHz clock derived as                                      | 0       | IOL   |

|     |           |                 |                             | I2S_BLCK/64.                                                         | (mas-   |       |

|     |           |                 |                             |                                                                      | ter), I |       |

|     |           |                 |                             |                                                                      | (slave) |       |

| 11  | X1D09     | SPARE           |                             |                                                                      |         | IOL   |

|     |           | (RE-<br>SERVED) |                             |                                                                      |         |       |

| 13  | X1D10     | I2S_BCLK        | I2S bit synchronisa-        | Configurable for 16KHz (1.024MHz)                                    | 0       | IOL   |

| 13  | AIDIO     | IZS_DULK        | tion clock                  | and 48KHz (3.072MHz) sample                                          | (mas-   | IOL   |

|     |           |                 | tion clock                  | rates                                                                | ter), I |       |

|     |           |                 |                             | rates                                                                | (slave) |       |

| 14  | X1D11     | MCLK_INOL       | ITMaster audio clock        | Input in INT and Hybrid config; Out-                                 | 1/0     | IOL   |

|     |           | _               |                             | put in USB Config. Should be con-                                    | , -     |       |

|     |           |                 |                             | nected to Pin 41                                                     |         |       |

| 15  | XOUT      | XOUT            | Crystal oscillator          | Note that this pin should be left                                    | 0       | IOB   |

|     |           |                 | output                      | floating when using the CMOS                                         |         |       |

|     |           |                 |                             | clock input                                                          |         |       |

| 16  | XIN       | XIN             | Crystal oscillator in-      | alternatively this can be used as a                                  |         | IOB   |

|     |           |                 | put or CMOS clock           | clock input                                                          |         |       |

| 17  | 1/0010010 | \/DDI0D10       | input                       | All VDD size as at least a second of                                 | DIME    | N I A |

| 17  | VDDIOB18  | VDDIOB18        | I/O Power Supply            | All VDD pins must be connected.                                      | PWR     | NA    |

| 18  | TDI       | TDI             | (1v8)<br>JTAG test data in- | This pin has a weak internal pull-up.                                |         | IOB   |

| 18  | וטו       | וטו             | put                         | See note on debug headers.                                           |         | IOB   |

| 20  | TDO       | TDO             | JTAG test data out-         | See note on debug headers.                                           | 0       | IOB   |

| 20  | 100       | 100             | put                         | See Hote off debug fledders.                                         |         | 100   |

| 21  | RST_N     | RST_N           | Device reset                | Active low. This pin has a Schmitt                                   |         | IOB   |

|     |           |                 |                             | trigger input and an internal weak                                   |         |       |

|     |           |                 |                             | pull up                                                              |         |       |

| 22  | PLL_AVDD  | PLL_AVDD        | Analogue power              | Use a filtered version of the core                                   | PWR     |       |

|     |           |                 | supply for core and         | supply, as per the XU316-1024-                                       |         |       |

|     |           |                 | application PLL.            | QF60A datasheet.                                                     |         |       |

| 23  | TMS       | TMS             | JTAG test mode se-          | This pin has a weak internal pull-up.                                |         | IOB   |

| 24  | TCK       | TOK             | lect                        | See note on debug headers                                            |         | IOD   |

| 24  | IUK       | TCK             | JTAG test clock in-         | This pin has a Schmitt trigger input and an internal weak pull-down. |         | IOB   |

|     |           |                 | put                         | See note on debug headers.                                           |         |       |

| 25  | NC        | NC              |                             | Not connected. This pin should                                       |         | IOB   |

| 25  |           | .,0             |                             | NOT be connected to any net                                          |         | .05   |

| 26  | VDDIOB18  | VDDIOB18        | I/O Power Supply            | All VDD pins must be connected.                                      | PWR     | NA    |

|     |           |                 | (1v8)                       |                                                                      |         |       |

| 28  | USB_DM    | USB_DM          | ,                           | USB D- line. May be left floating if                                 |         |       |

|     |           |                 |                             | USB is not required                                                  |         |       |

| 29  | USB_DP    | USB_DP          |                             | USB D+ line. May be left floating if                                 |         |       |

|     |           |                 |                             | USB is not required                                                  |         |       |

| 30  | USB       | USB             |                             | USB 3.3V power for the USB                                           | PWR     |       |

|     | _VDD33A   | _VCC33A         |                             | transceiver. May be left floating if                                 |         |       |

|     |           |                 |                             | USB is not required                                                  |         |       |

continues on next page

Table 4.1 – continued from previous page

| Pin | Port           | Name          | Description                               | Comments                                                           | Di-  | Power |

|-----|----------------|---------------|-------------------------------------------|--------------------------------------------------------------------|------|-------|

|     |                |               |                                           |                                                                    | rec- | rail  |

|     |                |               |                                           |                                                                    | tion |       |

| 31  | USB            | USB           |                                           | USB 1.8V power for the USB                                         | PWR  |       |

|     | _VDD18A        | _VCC18A       |                                           | transceiver. May be left floating if                               |      |       |

|     |                |               |                                           | USB is not required                                                |      |       |

| 32  | X1D13          | MIC_DATA      | PDM microphone                            | Note that this is a DDR input per-                                 |      | IOR   |

|     |                |               | input                                     | mitting a pair of digital DDR micro-<br>phones to share this input |      |       |

| 33  | X1D16          | XL_DN1        | XLINK                                     | These 4 signals form a single 2-wire                               |      | IOR   |

|     |                |               |                                           | xlink connection for advanced de-                                  |      |       |

|     |                |               |                                           | bug only. Do not connect in produc-                                |      |       |

|     |                |               |                                           | tion desings.                                                      |      |       |

| 35  | X1D17          | XL_DN0        | XLINK                                     |                                                                    | I    | IOR   |

| 36  | X1D18          | XL_UP0        | XLINK                                     |                                                                    | 0    | IOR   |

| 37  | X1D19          | XL_UP1        | XLINK                                     |                                                                    | 0    | IOR   |

| 38  | VDDIOR         | VDDIOR        | I/O Power Supply (1v8)                    | All VDD pins must be connected.                                    | PWR  | NA    |

| 39  | X1D22          | MIC_CLK       | Microphone clock output.                  | 3.072MHz                                                           | 0    | IOR   |

| 40  | X0D29          | OP_0          | General purpose                           | Eval kit - Used as interupt to the                                 | 0    | IOR   |

|     |                |               | output                                    | RaPi, via an I2C expander.                                         |      |       |

| 41  | X0D35          | MCLK          | Master audio clock                        |                                                                    | I    | IOR   |

| 43  | X0D36          | RE-<br>SERVED |                                           | Leave this pin unconnected                                         | 1    | IOR   |

| 44  | X0D37          | I2C_SCL       | I2C serial clock line                     |                                                                    | 1/0  | IOR   |

|     |                |               | for receiving con-                        |                                                                    |      |       |

|     |                |               | trol command from                         |                                                                    |      |       |

| 4.5 | 1/0000         | 100.004       | I2C host                                  |                                                                    | 1.40 | 100   |

| 45  | X0D38          | I2C_SDA       | I2C serial data line                      |                                                                    | 1/0  | IOR   |

|     |                |               | for receiving control command from        |                                                                    |      |       |

|     |                |               | 12C host                                  |                                                                    |      |       |

| 46  | X0D40          | IP_0          | 120 11081                                 | Eval kit Mute                                                      |      | IOT   |

| 47  | X0D40<br>X0D39 | SPI_MISO      | SPI Master In Slave                       | May be left floating if not required                               | 0    | IOT   |

|     |                |               | Out                                       | , , , , , , , , , , , , , , , , , , , ,                            | 0    |       |

| 48  | X0D42          | IP_2          |                                           | General purpose input                                              | l    | IOT   |

| 50  | X0D41          | IP_1          |                                           | Eval kit BUTTON                                                    | l    | IOT   |

| 51  | X0D43          | IP_3          |                                           | General purpose input                                              |      | IOT   |

| 52  | VDDIOT         | VDDIOT        | I/O Power Supply (1v8)                    | All VDD pins must be connected.                                    | PWR  | NA    |

| 53  | X1D34          | I2S_DIN       | Peripheral I2S interface - I2S data input |                                                                    | I    | IOT   |

| 54  | X0D30          | OP_1          | General purpose output                    | Eval kit - LED_R                                                   | 0    | IOT   |

| 55  | X0D31          | OP_2          | General purpose output                    | Eval kit - LED_G                                                   | 0    | IOT   |

| 56  | X0D32          | OP_3          | General purpose output                    | Eval kit - Test point (and DAC reset if no-fit resistor fitted)    | 0    | IOT   |

| 58  | X0D33          | RE-<br>SERVED | ,                                         | Leave this pin unconnected                                         |      | IOT   |

continues on next page

Table 4.1 – continued from previous page

| Pin | Port  | Name    | Description       | Comments                            | Di-  | Power |

|-----|-------|---------|-------------------|-------------------------------------|------|-------|

|     |       |         |                   |                                     | rec- | rail  |

|     |       |         |                   |                                     | tion |       |

| 59  | X0D04 | QSPI_D0 | QSPI Boot Flash / |                                     | 1/0  | IOL   |

|     |       |         | QSPI Data Line 0  |                                     |      |       |

| 60  | X0D06 | QSPI_D2 | QSPI Data Line 2  |                                     | 1/0  | IOL   |

| 65  | GND   | GND     | Ground            | All package paddles must be con-    | GND  | NA    |

|     |       |         |                   | nected. It is advised that vias be  |      |       |

|     |       |         |                   | placed under paddles to connect di- |      |       |

|     |       |         |                   | rectly to PCB supply planes         |      |       |

| 61, | VDD   | VDD     | Core power supply | All package paddles must be con-    | PWR  | NA    |

| 62, |       |         | (0v9)             | nected. It is advised that vias be  |      |       |

| 63, |       |         |                   | placed under paddles to connect di- |      |       |

| 64  |       |         |                   | rectly to PCB supply planes         |      |       |

| 4,  | VDD   | VDD     | Core power supply | All VDD pins must be connected.     | PWR  | NA    |

| 12, |       |         | (0v9)             |                                     |      |       |

| 19, |       |         |                   |                                     |      |       |

| 27, |       |         |                   |                                     |      |       |

| 34, |       |         |                   |                                     |      |       |

| 42, |       |         |                   |                                     |      |       |

| 49, |       |         |                   |                                     |      |       |

| 57  |       |         |                   |                                     |      |       |

- A. All VDD pins must be connected, excluding the USB\_VDD supplies which can be left floating if USB is not required.

- B. Two package variants are available:

QF60A (1V8 I/0) VDDIOT, VDDIOL and VDDIOR must be connected a 1V8 supply

QF60B (3V3 I/0) VDDIOT, VDDIOL and VDDIOR must be connected a 3V3 supply

- C. In both variants, VDDIO18 must be connected to a 1V8 supply must be connected.

- D. All package paddles must be connected. It is advised that vias be placed under paddles to connect directly to PCB supply planes

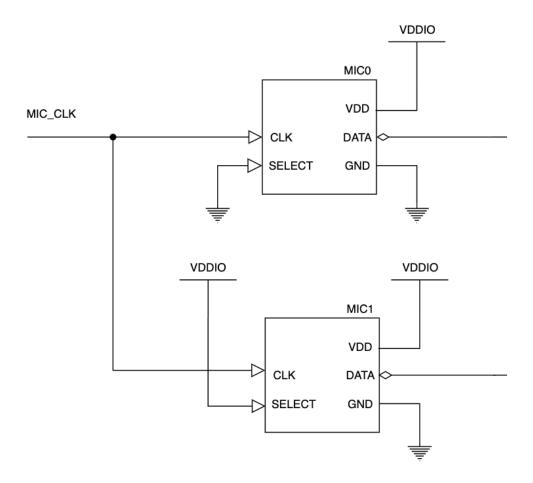

### 5.1 PDM microphone inputs

Two standard PDM MEMS microphones should be connected to the MIC\_DATA pin. The data input makes use of the left and right channel output capability of standard MEMS microphones and the microphone data is read on alternative edges of the MIC\_CLK signal. The XVF3610 reads one microphone on the positive edge of the microphone clock and the other microphone on the negative edge of the clock.

The XVF3610 outputs a microphone clock at 3.072MHz on the MIC\_CLK output, which must be fed directly to both microphones. This signal must be used to clock the microphone PDM output to avoid undefined artefacts in the processed audio stream. One microphone should be set to be left (output on rising edge of clock) and the other right (output on the falling edge of clock).

An example microphone circuit is shown in the figure below:

Fig. 5.1: PDM microphone schematic

The voice processor has been tested and characterised with microphones placed with a 71mm separation and connected to the product enclosure in such a way that the acoustic path to each microphone from outside the product is independent. The XVF3610 algorithms automatically adapt to alternative spacing, but differences in audio performance may occur and should be thoroughly characterised.

#### 5.2 QSPI Boot mode

When QSPI boot mode is enabled (default), the XVF3610 enables the six QSPI pins, see table below, and drives the QSPI clock as a QSPI Master. A READ command is issued with a 24-bit address 0x000000.

Table 5.1: QSPI signals

| Signal                 | Description      | Comment                                                                                                                                                                                                                                                                                                              | Pin | I/O |

|------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| QSPI_CS_N              | QSPI Chip Select | Pull high externally to the device using a 4.7k ohm resistor                                                                                                                                                                                                                                                         | 3   | 0   |

| QSPI_CLK /<br>SPI_CLK  | QSPI Clock       |                                                                                                                                                                                                                                                                                                                      | 50  |     |

| QSPI_D0                | QSPI Data Line 0 |                                                                                                                                                                                                                                                                                                                      | 59  | 1/0 |

| QSPI_D1 / B00T-<br>SEL | QSPI Data Line 1 | If pin is tied high via a 4.7k ohm resistor on startup and boot selection - the device will start in SPI slave boot mode. If the pin is left floating pulled low or connected to a quad SPI D1 pin on a memory device - the device will start in QSPI master mode and attempt to boot from a local QSPI flash memory | 1   | 1/0 |

| QSPI_D2                | QSPI Data Line 2 |                                                                                                                                                                                                                                                                                                                      | 60  | 1/0 |

| QSPI_D3                | QSPI Data Line 3 |                                                                                                                                                                                                                                                                                                                      | 2   | 1/0 |

The XVF3610 expects each byte to be transferred with the least-significant nibble first. Programmers that write bytes into a QSPI interface using the most significant nibble first may have to reverse the nibbles in each byte of the image stored in the QSPI device. When bulk programming flash devices the Quad Enable bit in the flash setting register should be set.

For further information about the boot sequence refer to the XU316-1024-QF60(A/B) datasheet.

#### 5.3 SPI Interface

The SPI interface can be utilised in both Master and Slave configurations for peripheral control of components like DACs and ADCs (Master), and SPI boot from host a host processor (Slave).

#### **5.3.1 Peripheral component control**

Once the XVF3610 has successfully booted, the SPI interface can be used to configure peripheral components such as DACs, ADCs and keyword detection devices. In this mode the SPI interface operates as a master, and transfers data held in flash, or received from the host over the control interface. The interface operates with the following specifications:

- 1MHz SPI clock

- Up to 128 bytes SPI write

- · Up to 56 bytes SPI read

For further information on this configuration consult the User Guide.

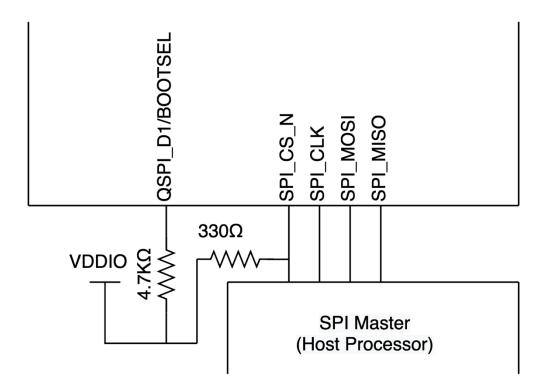

#### 5.3.2 SPI slave boot

To enable the SPI boot from an external host processor, the QSPI\_D1/B00TSEL should be pulled to VDDIO on power-up. This activates the SPI interface, which operates as a slave to the host processor for the transfer of the boot image, which is clocked in with the least significant bit first in each transferred byte.

This is an alternative to using an attached QSPI flash to automatically transfer boot data on start-up.

Fig. 5.2: XVF3610 SPI slave boot configuration

The SPI pins are shown below in the table below.

Table 5.2: SPI signals

| Signal   | Description                | Comment                                                      | Pin | I/O |

|----------|----------------------------|--------------------------------------------------------------|-----|-----|

| SPI_CLK  | SPI Clock                  |                                                              | 5   |     |

| SPI_CS_N | SPI Chip Select            | Pull high externally to the device using a 4.7k ohm resistor | 6   | Τ   |

| SPI_MOSI | SPI Master Out Slave<br>In |                                                              | 7   | Τ   |

| SPI_MISO | SPI Master In Slave<br>Out | May be left floating if not required                         | 47  | 0   |

### 5.4 Integrated USB interface

USB Audio Class 1.0 running at Full Speed (12Mbps) is used to deliver processed voice audio to the host processor, stereo reference audio from the host and as a control interface. In this mode the adaptive USB Audio endpoint is used to generate an MCLK synchronised to the USB host. This is driven out of MCLK.

The table below shows the signals required to implement a USB interface using the XVF3610.

Table 5.3: USB connections

| Name            | Description                                                                       | Pin |

|-----------------|-----------------------------------------------------------------------------------|-----|

| USB_DP          | Connect to USB connector                                                          | 29  |

| USB_DM          | Connect to USB connector                                                          | 28  |

| USB_VBUS<br>DET | Do not connect Self-powered operation is not supported by current device firmware | 43  |

| USB_VDD18       | 1.8V supply for USB-PHY - May be left floating if the USB interface is not used   | 31  |

| USB_VDD33       | 3.3V supply to the USB-PHY May be left floating if the USB interface is not used  | 30  |

**Note:** Currently the UA firmware only supports use in a bus powered configuration

#### 5.5 I2S Audio Interface

The XVF3610 operates as an  $I^2S$  slave outputting audio to the host processor and receiving reference audio signal. This bidirectional flow of audio samples must be synchronised to a single set of  $I^2S$  clocks, see table below:

Table 5.4: I<sup>2</sup>S signals

| Signal   | Description                                | Comment                                                             | Pin | I/O |

|----------|--------------------------------------------|---------------------------------------------------------------------|-----|-----|

| MCLK     | Master audio clock                         |                                                                     | 14  |     |

| I2S_BCLK | I <sup>2</sup> S bit synchronisation clock | Configurable for 16kHz (1.024MHz) and 48kHz (3.072MHz) sample rates | 13  | I   |

| I2S_LRCK | I <sup>2</sup> S Left/Right clock          | 48kHz or 16kHz clock derived as I2S_BLCK/64                         | 10  | 1   |

| I2S_DIN  | I <sup>2</sup> S Data In                   | Reference audio data from I <sup>2</sup> S device                   | 53  | 1   |

| I2S_DOUT | I <sup>2</sup> S Data Out                  | Audio data out to host processor                                    | 9   | 0   |

The  $I^2S$  audio samples are transmitted serially with a one  $I2S\_BCLK$  delay between the change of  $I2S\_LRCK$  phase and the start (MSB) of the audio sample for that channel. This the standard alignment for  $I^2S$  systems.

#### 5.6 I<sup>2</sup>C Control interface

The I<sup>2</sup>C Slave interface is used to control and configure the parameters on the XVF3610.

**Warning:**  $I^2C$  commands received prior to  $I^2S$  clocks being activated will not be processed and may result in undefined behaviour. Therefore, it is important to ensure that the  $I^2S$  interface is activated before parameterisation of the device is undertaken.

The interface operates with the following specifications:

- 100 kbps SCL clock speed

- Register read/write

- Up to 56 byte I<sup>2</sup>C read/write

For more information on control and configuration of the XVF3610 please refer to the User Guide.

The device I<sup>2</sup>C address is 0x2C, and the pin connections are shown below.

Table 5.5: I<sup>2</sup>C Slave Connections

| Signal  | Description                                                                                 | Comment | Pin | I/O |

|---------|---------------------------------------------------------------------------------------------|---------|-----|-----|

| I2C_SCL | I <sup>2</sup> C serial clock line for receiving control command from I <sup>2</sup> C host |         | 44  | 1/0 |

| I2C_SDA | I <sup>2</sup> C serial data line for receiving control command from I <sup>2</sup> C host  |         | 45  | 1/0 |

### 5.7 General Purpose Input/Output

Four input and four output pins are provided to allow general-purpose I/O such as LEDs and button controls. Input pins can be individually read by the host using the control interface and configured to detect edge events. The output pins can be individually set, and they have configurable Pulse Width Modulated (PWM) brightness control with blinking sequences.

The GPIO pins are shown in the table below.

Table 5.6: GPIO pin table

| Name | Description            | Pin | I/O |

|------|------------------------|-----|-----|

| IP_0 | General purpose input  | 46  | 1   |

| IP_1 | General purpose input  | 50  |     |

| IP_2 | General purpose input  | 48  |     |

| IP_3 | General purpose input  | 51  |     |

|      |                        |     |     |

| OP_0 | General purpose output | 40  | 0   |

| OP_1 | General purpose output | 54  | 0   |

| OP_2 | General purpose output | 55  | 0   |

| OP_3 | General purpose output | 56  | 0   |

For more information on configuring these inputs and outputs, please refer to the User Guide.

## 6 Device operation

### **6.1 Power supplies**

The XVF3610 has the following power supply pins:

Table 6.1: XVF3610 Power Pins

| Name      | Description                                                            | Pin           |

|-----------|------------------------------------------------------------------------|---------------|

| VDD       | Digital core power supply. 0.9V (nominal)                              | 4 12 19 27 34 |

|           |                                                                        | 42 49 57 61   |

|           |                                                                        | 64            |

| V_DDIOL   | Digital I/O power supply ** See Note A                                 | 8             |

| V_DDIOR   | Digital I/O power supply ** See Note A                                 | 38            |

| V_DDIOT   | Digital I/O power supply ** See Note A                                 | 52            |

| VDD IOB18 | Digital I/O power supply. 1.8V (nominal)                               | 17 - 26       |

| PLL_AVDD  | PLL analogue power. This 0.9V (nominal) PLL supply should be sepa-     | 22            |

|           | rated from the other supplies at the same voltage by a low pass filter |               |

| USB_VDD18 | Digital supply to the USB-PHY. 1.8V (nominal)                          | 31            |

| USB_VDD33 | Analogue supply to the USB-PHY. 3.3V (nominal)                         | 30            |

| VSS       | Device Ground                                                          | 65 (Paddle)   |

Warning: A: I/O voltage depends on package variant

- QF60A VDDIOx is 1.8V nominal pins 8, 38 and 52 should be connected to a 1.8V supply

- QF60B VDDIOx is 3.3V nominal pins 8, 38 and 52 should be connected to a 3.3V supply

For both variants, VDDIOB18 - pins 17 & 26 - must be connected to 1.8V

B: All VDD power pins must be connected.

C: USB\_VDDxx supplies can be left floating if USB is not used.

#### See also:

The XU316-1024-QF60(A/B) datasheets contain further information on power supplies and power on sequencing.

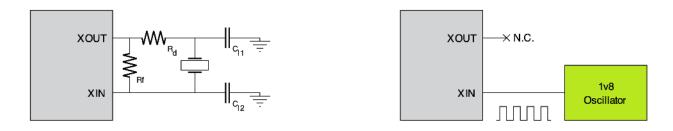

#### 6.2 Clocks

The XVF3610 device has an on-chip oscillator. To use the oscillator a crystal, two capacitors, and damping and feedback resistors to the device as shown below.

Table 6.2: XVF3610 crystal oscillator

| Signal | Description               | Comment | Pin | I/O |

|--------|---------------------------|---------|-----|-----|

| XIN    | Crystal oscillator input  |         | 16  |     |

| XOUT   | Crystal oscillator output |         | 15  | 0   |

Fig. 6.1: Crystal oscillator or clock input configurations

Alternatively, the XVF3610 can be provided with a 24MHz, 1V8 clock input on the XIN pin. The clock must be running when the chip comes out of reset.

Table 6.3: XVF3610 clock signals

| Signal | Description           | Comment                              | Pin | I/O |

|--------|-----------------------|--------------------------------------|-----|-----|

| XIN    | Master clock (system) | 24MHz 1V8 clock signal               | 16  |     |

| XOUT   | N/C                   | Leave floating if clock input on XIN | 15  | 0   |

#### See also:

For further information, and details on the calculation of  $R_f$  and  $R_d$ , please refer to the XU316-1024-QF60(A/B) datasheets.

#### 6.3 Reset

The XVF3610 device has an on-chip Power-on-Reset (POR). This keeps the chip in reset whilst the supplies are coming up.

See XU316-1024-QF60(A/B) datasheet for further information.

Table 6.4: Reset Signal

| Signal | Description  | Comment    | Pin | I/O |

|--------|--------------|------------|-----|-----|

| RST_N  | Device reset | Active low | 21  | 1   |

#### 6.4 Boot modes

On start-up and after a reset event, the XVF3610 is booted either using an externally connected QSPI flash memory or by transferring a boot image to the device via SPI from a host processor.

#### 6.4.1 Slave boot mode

The boot mode is specified using QSPI\_D1/BOOTSEL. If this pin is tied high via a 4.7k ohm resistor on start-up, the XVF3610 will enable SPI Slave boot mode and activate the pins shown below.

Table 6.5: SPI Slave boot pins

| Signal              |   | Description                | Comment                                                      | Pin | I/O |

|---------------------|---|----------------------------|--------------------------------------------------------------|-----|-----|

| QSPI_CLK<br>SPI_CLK | / | SPI Clock                  |                                                              | 5   | I   |

| SPI_CS_N            |   | SPI Chip Select            | Pull high externally to the device using a 4.7k ohm resistor | 6   | I   |

| SPI_MOSI            |   | SPI Master Out Slave<br>In |                                                              | 7   | I   |

| SPI_MISO            |   | SPI Master In Slave<br>Out |                                                              | 47  | 0   |

#### 6.4.2 QSPI master boot mode

If the QSPI\_D1/B00TSEL pin is connected to a QSPI\_D1 pin on a flash device, the XVF3610 will boot from a local QSPI flash in QSPI Master mode. The active pins are shown below.

Table 6.6: QSPI Master peripheral interface pins

| Name       | Description                                                                                         | Pin | I/O |

|------------|-----------------------------------------------------------------------------------------------------|-----|-----|

| QSPI_CS_N  | QSPI Chip Select. This pin should be pulled high externally to the device using a 4.7k ohm resistor | 3   | 1/0 |

| QSPI_D0    | QSPI Data Line 0                                                                                    | 59  | 1/0 |

| QSPI_D1 -  | QSPI Data Line 1 and boot selection. To activate QSPI master boot mode connect                      | 1   | 1/0 |

| BOOTSEL    | directly to QSPI Data Line 1 on Quad capable flash device                                           |     |     |

| QSPI_D2    | QSPI Data Line 2                                                                                    | 60  | 1/0 |

| QSPI_D3    | QSPI Data Line 3                                                                                    | 2   | 1/0 |

| QSPI_CLK / | QSPI Clock and SPI Clock                                                                            | 5   | 1/0 |

| SPI_CLK    |                                                                                                     |     |     |

### 6.5 QSPI flash support

Flash devices with the following specifications are supported by the XVF3610 (e.g. Winbond W25Q16JWSNIM).

Table 6.7: Flash device specification supported by XVF3610

| Device characteristic                | Description                                                               | Value                             |  |

|--------------------------------------|---------------------------------------------------------------------------|-----------------------------------|--|

| Page size                            | Size of flash page in bytes                                               | 256                               |  |

| Number of pages                      | Total number of pages                                                     | 8192                              |  |

| Address size                         | Number of bytes used to represent the address                             | 3                                 |  |

| Read ID operation code               | Operation code to read the device identification (ID) information         | 0x9F                              |  |

| Read ID dummy bytes                  | Number of dummy bytes after read command before ID is returned            | 0                                 |  |

| ID size                              | Size of ID in bytes                                                       | 3                                 |  |

| Sector Erase operation code          | Operation code for 4kB Erase                                              | 0x20                              |  |

| Sector information                   | Arrangement of sectors                                                    | Regular (all equally sized - 4kB) |  |

| Write Enable operation code          | Operation code for write enable                                           | 0x06                              |  |

| Write Disable operation code         | Operation code for write disable                                          | 0x04                              |  |

| Page Program operation code          | Operation code for page program                                           | 0x02                              |  |

| Fast Quad Read operation code        | Operation code for Fast Quad I/O Read                                     | 0xEB                              |  |

| Fast Quad Read Dummy<br>Bytes        | Number of dummy bytes after setup of fast quad read that data is returned | 1                                 |  |

| Read Status Register operation code  | Operation code for reading status register                                | 0x05                              |  |

| Write Status Register operation code | Operation code for write to the status register                           | 0x01                              |  |

| Write Status Register Busy<br>Mask   | Bit mask for operation in progress (device busy)                          | 0x01                              |  |

### 6.6 Device firmware

Device Firmware Upgrade (DFU) is supported for devices that have QSPI flash connected and loaded with a firmware image. If the DFU process fails, the boot process safely falls back to the factory image allowing the user to re-attempt the upgrade. Images loaded via DFU can also be removed allowing the device to revert to the factory image.

For further information on the operation of the DFU mechanism refer to the User Guide.

## 7 Device characteristics

### 7.1 Electrical and Thermal characteristics

For electrical and thermal characteristics, including Absolute Maximum ratings please refer to the XU316-1024-QF60(A/B) datasheets.

xcore.ai base datasheet links:

XU316-1024-QF60A

XU316-1024-QF60B

## 8 Switching characteristics

For clock, reset and JTAG timing refer to the XU316-1024-QF60(A/B) datasheet. XVF3610 specific interface timings are detailed below.

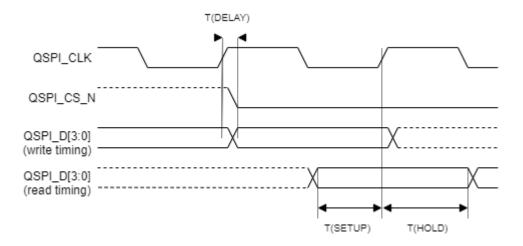

## 8.1 QSPI Master (External flash for boot image storage)

Fig. 8.1: QSPI Timing

Table 8.1: QSPI Timing Requirements

| Parameter                              | Symbol      | Min  | Typical | Max | Units |

|----------------------------------------|-------------|------|---------|-----|-------|

| QSPI Clock frequency                   | f(QSPI_CLK) | -    | TBC     | 50  | MHz   |

| QSPI_CLK to QSPI Data output delay     | T(DELAY)    | -2.7 | -       | 2.7 | ns    |

| QSPI Data input to QSPI_CLK Setup time | T(SETUP)    | 22   | -       | -   | ns    |

| QSPI Data input to QSPI_CLK hold time  | T(HOLD)     | -11  | -       | -   | ns    |

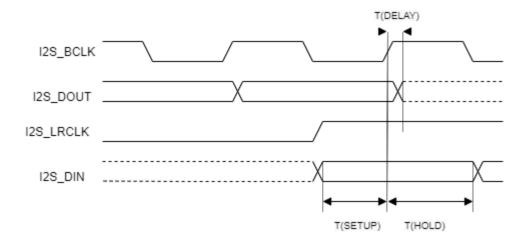

Fig. 8.2: I<sup>2</sup>S Slave timing

#### 8.2 **I2S Slave**

Table 8.2: I<sup>2</sup>S Slave Timing Requirements

| Parameter                                | Symbol      | Min   | Typical | Max    | Units | Notes |

|------------------------------------------|-------------|-------|---------|--------|-------|-------|

| Master clock input frequency             | f(MCLKin)   | TBC   | -       | 24.576 | MHz   | А     |

| I2S Bit Clock frequency input            | f(I2S_BCLK) | 1.024 | -       | 3.072  | MHz   |       |

| I2S Data Input (LRCLK) to                | T(SETUP)    | 0     | -       | -      | ns    | В     |

| I2S_BCLK setup time                      |             |       |         |        |       |       |

| I2S Data Input (LRCLK) to                | T(HOLD)     | 6     | -       | -      | ns    | В     |

| I2S_BCLK hold time                       |             |       |         |        |       |       |

| I2S_BCLK to I <sup>2</sup> S Data output | T(DELAY)    | 11    | -       | 21.3   | ns    |       |

| delay                                    |             |       |         |        |       |       |

A: Configurable input multiplier used to generate appropriate audio sample rates (16kHz / 48kHz)

B: Timing also applies to I<sup>2</sup>S Sample Clock (I2S\_LRCLK)

## 8.3 SPI Slave (External processor boot)

Table 8.3: SPI Slave Timing Requirements

| Parameter                                                  | Symbol     | Min | Typical | Max  | Units | Notes |

|------------------------------------------------------------|------------|-----|---------|------|-------|-------|

| SPI Clock frequency                                        | f(SPI_CLK) | -   | TBC     | TBC  | MHz   |       |

| SPI_CLK to MISO output delay                               | T(DELAY)   | 11  | -       | 21.3 | ns    |       |

| SPI Master Output Slave Input (MOSI) to SPI_CLK Setup time | T(SETUP)   | 0   | -       | -    | ns    |       |

| SPI Master Output Slave Input to (MOSI) SPI_CLK hold time  | T(HOLD)    | 6   | -       | -    | ns    |       |

A: Timing also applies to SPI Chip Select input (SPI\_CS\_N)

## 8.4 SPI Master (Peripheral control)

Table 8.4: SPI Slave Timing Requirements

| Parameter                                                  | Symbol     | Min | Typical | Max  | Units | Notes |

|------------------------------------------------------------|------------|-----|---------|------|-------|-------|

| SPI Clock frequency                                        | f(SPI_CLK) | -   | TBC     | TBC  | MHz   |       |

| SPI_CLK to MISO output delay                               | T(DELAY)   | 11  | -       | 21.3 | ns    |       |

| SPI Master Output Slave Input (MOSI) to SPI_CLK Setup time | T(SETUP)   | 0   | -       | -    | ns    |       |

| SPI Master Output Slave Input to (MOSI) SPI_CLK hold time  | T(HOLD)    | 6   | -       | -    | ns    |       |

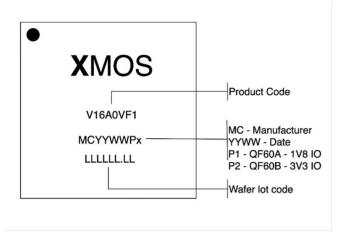

## 9.1 Device markings

Fig. 9.1: Part marking scheme

**Important:** The two variants of the package (1.8V and 3.3V I/O) are distinguished by a P1 or P2 code after the date code (YYWW) on the package

### 9.2 Order codes

Table 9.1: Ordering codes

| Product code    | Marking **            | Description                                                |

|-----------------|-----------------------|------------------------------------------------------------|

| XVF3610-QF60A-C | V16A0VF1<br>MCYYWWP1  | Commercial Temp range (0 – 70 degrees Celsius) - 1.8V IO   |

| XVF3610-QF60B-C | V16A0VF1<br>MCYYWWP2  | Commercial Temp range (0 – 70 degrees Celsius) - 3.3V IO   |

| XVF3610-QF60A-I | V16A0VF1I<br>MCYYWWP1 | Industrial Temp range (40 – 85 degrees Celsius) - 1.8V IO  |

| XVF3610-QF60B-I | V16A0VF1I<br>MCYYWWP2 | Industrial Temp range (40 – 85 degrees Celsius)) - 3.3V IO |

Note: \*\* MC - Manufacturer, YY - Year code, WW - Week code, Px - I/O volage

### 9.3 Moisture Sensitivity Level

The package moisture sensitivity level rating is MSL-3. Devices have a shelf life of 168 hours between removal from the packaging and reflow, provided they are stored below 30C and 60% RH. If devices have exceeded these values or an included moisture indicator card shows excessive levels of moisture, then the parts should be baked as appropriate before use. This is based on information from Joint IPC/JEDEC Standard for Moisture/Reflow Sensitivity Classification for Non-hermetic Solid-State Surface-Mount Devices (J-STD-020 Revision D).

#### 9.4 Hazardous Materials

This product complies with the Reduction of Hazardous Substances (RoHS) directive.

For details refer to https://www.xmos.ai/environmental.

## 10 Copyright & Disclaimer

Copyright © 2022 XMOS Ltd, All Rights Reserved.

XMOS Ltd is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS, VocalFusion<sup>®</sup> and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

Copyright © 2023, All Rights Reserved.

XMOS Ltd. is the owner or licensee of this design, code, or Information (collectively, the "Information") and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd makes no representation that the Information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS, XCORE, VocalFusion and the XMOS logo are registered trademarks of XMOS Ltd. in the United Kingdom and other countries and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.