# 18V Operation 0.5A Synchronous Step-Down DC/DC Converters

# **■GENERAL DESCRIPTION**

The IXD3263/64 series are 18V operation synchronous step-down DC/DC converter ICs with a built-in high-side/low-side driver transistor. The IXD3263/64 series has an operating voltage range of  $3.0V\sim18.0V$  and can support 0.5A as an output current with high-efficiency. It is compatible with low ESR capacitors such as ceramic capacitors for the load capacitor ( $C_L$ ). 0.75V reference voltage source is incorporated in the IC, and the output voltage can be set to a value from 1.0V to 15.0V using external resistors ( $R_{FB1}$ ,  $R_{FB2}$ ). 500 kHz or 1.2MHz or 2.2MHz can be selected for the switching frequency. In PWM/PFM automatic switchover control, IC can change the control method between PWM and PFM based on the output current requirement and as a result IC can achieve high efficiency over the full load range.

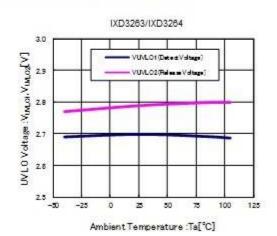

IXD3263/64 has a fixed internal soft start time which is 1.0ms (TYP.), additionally the time can be extended by using an external resistor and capacitor. With the built-in UVLO function, the driver transistor is forced OFF when input voltage goes down to 2.7V or lower. The output state can be monitored using the power good function. Over current protection, short-circuit protection and thermal shutdown are embedded and they secure a safety operation.

# **■**FEATURES

Input Voltage Range : 3~18V(Absolute Max 20V)

FB Voltage : 0.75V±1.5%

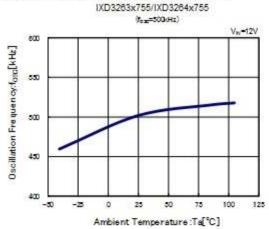

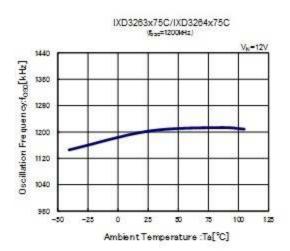

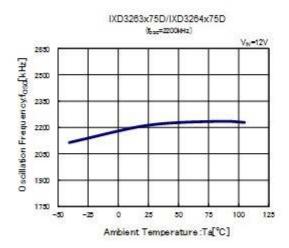

Oscillation Frequency : 500kHz, 1.2MHz, 2.2MHz

Output Current : 0.5A

Control Methods : PWM/PFM Auto

Efficiency 85%@12V→5V, 1mA

PWM control

Soft-start Time : Adjustable by RC

Protection Circuits : Over Current Protection

Automatic Recovery (IXD3263B/IXD3264B) Integral Latch Method (IXD3263A/IXD3264A) Thermal Shutdown

Low ESR Ceramic Capacitor : Ceramic Capacitor

Package : SOT-25 (no Power good)

USP-6C

Environmentally Friendly : EU RoHS Compliant, Pb Free

# ■ APPLICATIONS

- Hot water supply system

- Recorders, Camcorders

- Refrigerators, Air-conditioners

- Low Power Systems

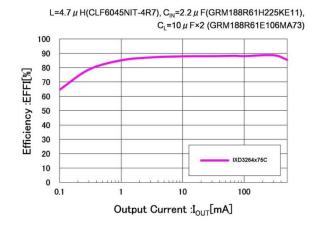

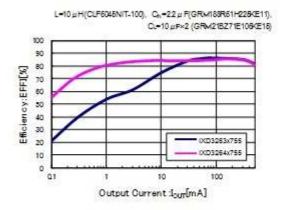

# ■TYPICAL PERFORMANCE CHARACTERISTICS

IXD3264x75C (V<sub>IN</sub>=12V, V<sub>OUT</sub>=5V, f<sub>OSC</sub>=1200kHz)

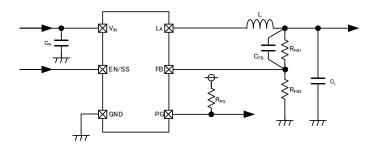

# TYPICAL APPLICATION CIRCUIT

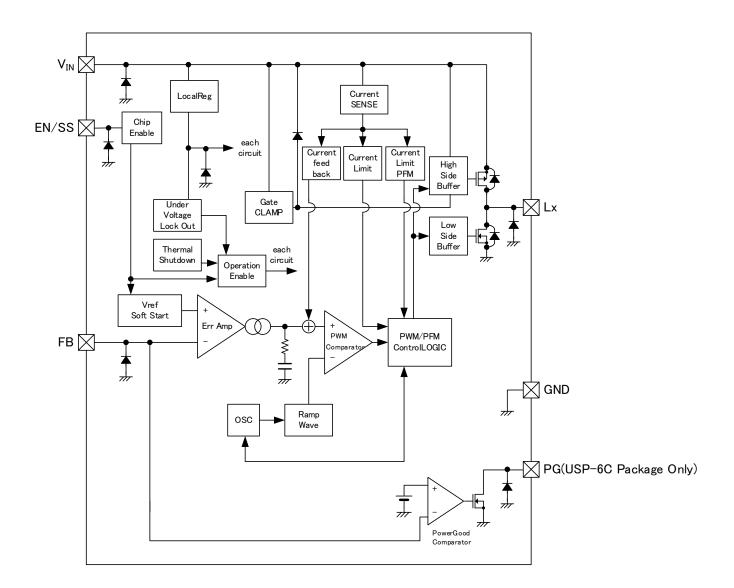

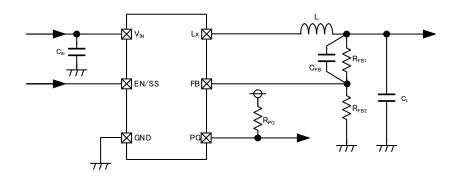

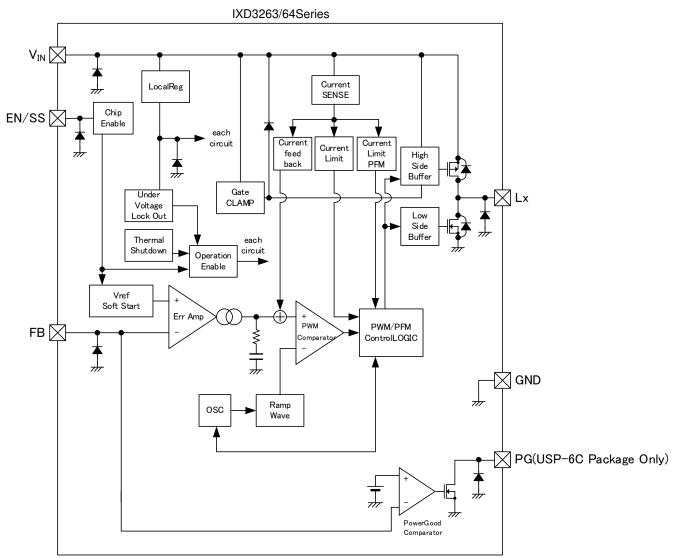

# **■BLOCK DIAGRAM**

### IXD3263/64Series

<sup>\*</sup>Diodes inside the circuit are ESD protection diodes and parasitic diodes.

# **■ PRODUCT CLASSIFICATION**

### Ordering Information

IXD3263①234⑤6-⑦<sup>(\*1)</sup> PWM control IXD3264①234⑤6-⑦<sup>(\*1)</sup> PWM/PFM Auto

| DESIGNATOR | ITEM                      | SYMBOL               | DESCRIPTION                                 |

|------------|---------------------------|----------------------|---------------------------------------------|

| ①          | Tuno                      | А                    | Refer to Selection Guide                    |

| U          | Туре                      | В                    | Refer to Selection Guide                    |

| 23         | Adjustable Output Voltage | 75                   | Output voltage can be adjusted in 1V to 15V |

|            |                           | 5                    | 500kHz                                      |

| 4          | Oscillation Frequency     | С                    | 1.2MHz                                      |

|            |                           | D                    | 2.2MHz                                      |

| EVE (7)    | Dooks and (Order Unit)    | MR-G <sup>(*1)</sup> | SOT-25 (3,000pcs/Reel)                      |

| 56-7       | Packages (Order Unit)     | ER-G <sup>(*1)</sup> | USP-6C (3,000pcs/Reel)                      |

The "-G" suffix denotes Halogen and Antimony free as well as being fully EU RoHS compliant.

#### Selection Guide

| TYPE | Packages | Current<br>Limitter | Automatic Recovery<br>(Current Limitter) | Latch Protection<br>(Current Limitter) | Chip Enable |

|------|----------|---------------------|------------------------------------------|----------------------------------------|-------------|

| Α    | MD.O     | YES                 | NO                                       | YES (*2)                               | YES         |

| В    | MR-G     | YES                 | YES                                      | NO                                     | YES         |

| TYPE | Packages | UVLO | Thermal<br>Shutdown | I Soft Start |    |

|------|----------|------|---------------------|--------------|----|

| Α    |          | YES  | YES                 | YES          | NO |

|      | MR-G     |      |                     | _            | _  |

| TYPE | Packages | Current<br>Limitter | Automatic Recovery<br>(Current Limitter) | Latch Protection<br>(Current Limitter) | Chip Enable |  |

|------|----------|---------------------|------------------------------------------|----------------------------------------|-------------|--|

| Α    | ED C     | YES                 | NO                                       | YES (*2)                               | YES         |  |

| В    | ER-G     | YES                 | YES                                      | NO                                     | YES         |  |

| TYPE | Packages | UVLO | Thermal<br>Shutdown | Soft Start | Power Good |

|------|----------|------|---------------------|------------|------------|

| Α    | ED C     | YES  | YES                 | YES        | YES        |

| В    | ER-G     | YES  | YES                 | YES        | YES        |

<sup>(\*2)</sup> The over-current protection latch is an integral latch type.

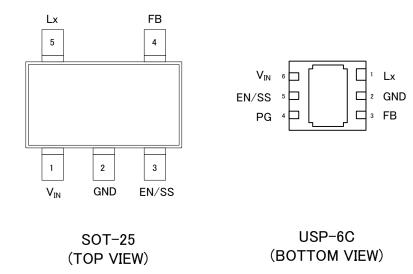

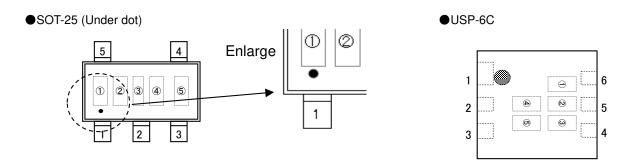

# ■ PIN CONFIGURATION

<sup>\*</sup> The dissipation pad for the USP-6C package should be solder-plated in recommended mount pattern and metal masking so as to enhance mounting strength and heat release. If the pad needs to be connected to other pins, it should be connected to the GND (No. 2) pin.

# **■ PIN ASSIGNMENT**

| PIN NU | JMBER  | PIN NAME     | FUNCTION             |

|--------|--------|--------------|----------------------|

| SOT-25 | USP-6C | FIIN INAIVIE | FUNCTION             |

| 1      | 6      | $V_{IN}$     | Power Input          |

| 3      | 5      | EN/SS        | Enable Soft-start    |

| -      | 4      | PG           | Power good Output    |

| 4      | 3      | FB           | Output Voltage Sense |

| 2      | 2      | GND          | Ground               |

| 5      | 1      | Lx           | Switching Output     |

# **■**FUNCTION CHART

| PIN NAME | SIGNAL | STATUS                          |

|----------|--------|---------------------------------|

|          | L      | Stand-by                        |

| EN/SS    | Н      | Active                          |

|          | OPEN   | Undefined State <sup>(*1)</sup> |

<sup>(\*1)</sup> Please do not leave the EN/SS pin open. Each should have a certain voltage.

# ■ ABSOLUTE MAXIMUM RATINGS

Ta=25°C

| PARA                | METER                   | SYMBOL             | RATINGS                                 | UNITS  |    |                            |    |

|---------------------|-------------------------|--------------------|-----------------------------------------|--------|----|----------------------------|----|

| V <sub>IN</sub> Pir | n Voltage               | $V_{IN}$           | -0.3 ∼ +20                              | V      |    |                            |    |

| EN/SS F             | Pin Voltage             | V <sub>EN/SS</sub> | -0.3 ~ +20                              | V      |    |                            |    |

| FB Pir              | n Voltage               | $V_{FB}$           | -0.3 ∼ +6.2                             | V      |    |                            |    |

| PG Pin              | Voltage <sup>(*1)</sup> | $V_{PG}$           | -0.3 ∼ +6.2                             | V      |    |                            |    |

| PG Pin              | Current (*1)            | I <sub>PG</sub>    | 8                                       | mA     |    |                            |    |

| Lx Pin              | Voltage                 | $V_{Lx}$           | -0.3 ~ V <sub>IN</sub> +0.3 or +20 (*1) | V      |    |                            |    |

| Lx Pir              | Current                 | I <sub>Lx</sub>    | 1800                                    | mA     |    |                            |    |

|                     | SOT-25                  |                    | 250                                     |        |    |                            |    |

| Power               | 501-25                  | 301-25             | 301-23                                  | 301-23 | Pd | 600(when mounted on board) | mW |

| Dissipation         | USP-6C                  | Pu                 | 120                                     | IIIVV  |    |                            |    |

|                     | USP-6C                  |                    | 1000(when mounted on board)             | ]      |    |                            |    |

| Operating Amb       | pient Temperature       | Topr               | -40 ~ +105                              | °C     |    |                            |    |

| Storage T           | emperature              | Tstg               | -55 <b>∼</b> +125                       | °C     |    |                            |    |

<sup>\*</sup> All voltages are described based on the GND pin.

<sup>(\*1)</sup> For the USP-6C Package only.

The maximum value should be either  $V_{\text{IN}}$ +0.3 or 20 in the lowest.

# ■ELECTRICAL CHARACTERISTICS

IXD3263/IXD3264 Ta=25°C

| IXD3263/IXD3264                              |                          |                                                                               |             |       |          |       |                                       | Ta=25°0 |  |

|----------------------------------------------|--------------------------|-------------------------------------------------------------------------------|-------------|-------|----------|-------|---------------------------------------|---------|--|

| PARAMETER                                    | SYMBOL                   | CONDITIONS                                                                    |             |       | TYP      | MAX   | UNIT                                  | CIRCUIT |  |

| FB Voltage                                   | V <sub>FB</sub>          | $V_{FB}$ =0.739V $\rightarrow$ 0.761V $V_{FB}$ Voltage when Lx pin oscillates |             | 0.739 | 0.750    | 0.761 | V                                     | 2       |  |

| Output Voltage Setting Range <sup>(*1)</sup> | V <sub>OUTSET</sub>      | V <sub>FB</sub> voltage when Lx pin oscillates                                |             | 1     | _        | 15    | V                                     |         |  |

| Operating Voltage Range                      | VOUTSET                  |                                                                               |             | 3     | -        | 18    | V                                     |         |  |

| Operating voitage hange                      | VIN                      | $V_{IN}$ :2.8V $\rightarrow$ 2.6V, $V_{FB}$ =0.675V                           |             | 3     | -        | 10    | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |         |  |

| UVLO Detect Voltage                          | V <sub>UVLO1</sub>       | V <sub>IN</sub> Voltage when Lx pin voltage chan                              | nes from    | 2.60  | 2.70     | 2.80  | V                                     | 2       |  |

| OVEO Detect Voltage                          | V UVLO1                  | "H" level to "L" level                                                        | ges nom     | 2.00  | 2.70     | 2.00  | *                                     | •       |  |

|                                              |                          | V <sub>IN</sub> :2.7V→2.9V, V <sub>FB</sub> =0.675V                           |             |       |          |       |                                       |         |  |

| UVLO Release Voltage                         | V <sub>UVLO2</sub>       | V <sub>IN</sub> Voltage when Lx pin voltage chang                             | ges from    | 2.70  | 2.80     | 2.90  | V                                     | 2       |  |

| ŭ                                            | 0,102                    | "L" level to "H" level                                                        | ,           |       |          |       |                                       |         |  |

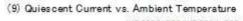

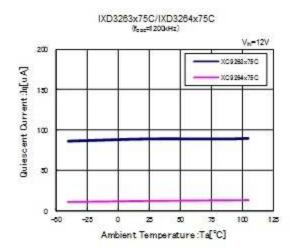

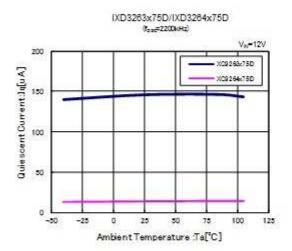

|                                              |                          |                                                                               | IXD3264x755 | -     | 11.5     | 16.5  | μA                                    | 4       |  |

| Quiescent Current                            | l <sub>q</sub>           | V <sub>FB</sub> =0.825V                                                       | IXD3264x75C | -     | 12.5     | 17.5  | μA                                    | 4       |  |

|                                              |                          |                                                                               | IXD3264x75D | -     | 13.5     | 18.5  | μA                                    | 4       |  |

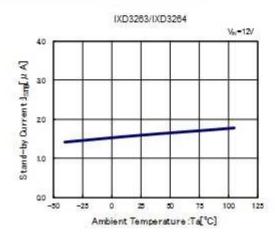

| Stand-by Current                             | I <sub>STB</sub>         | V <sub>EN/SS</sub> =0V                                                        | 1           | -     | 1.65     | 2.5   | μA                                    | (5)     |  |

| ·                                            |                          |                                                                               | IXD326xx755 | 458   | 500      | 542   | kHz                                   | 1       |  |

| Oscillation Frequency                        | f <sub>osc</sub>         | Connected to external components,                                             | IXD326xx75C | 1098  | 1200     | 1302  | kHz                                   | (1)     |  |

| , ,                                          |                          | I <sub>OUT</sub> =100mA                                                       | IXD326xx75D | 2013  | 2200     | 2387  | kHz                                   | (1)     |  |

| Minimum Duty Cycle                           | D <sub>MIN</sub>         | V <sub>FB</sub> =0.825V                                                       | 1           | -     | -        | 0     | %                                     | 2       |  |

| Maximum Duty Cycle                           | D <sub>MAX</sub>         | V <sub>FB</sub> =0.675V                                                       |             | 100   | -        | -     | %                                     | 2       |  |

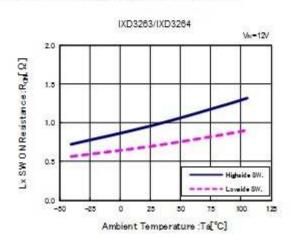

|                                              | _                        |                                                                               | USP-6C      | -     | 0.95     | 1.10  | Ω                                     | 2       |  |

| Lx SW "H" On Resistance                      | R <sub>LxH</sub>         | V <sub>FB</sub> =0.675V, I <sub>LX</sub> =200mA                               | SOT-25      | -     | 0.99     | 1.14  | Ω                                     | 2       |  |

|                                              |                          |                                                                               | USP-6C      | -     | 0.69(*2) | -     | Ω                                     | 2       |  |

| Lx SW "L" On Resistance                      | R <sub>LxL</sub>         | V <sub>FB</sub> =0.825V, I <sub>LX</sub> =200mA                               | SOT-25      | -     | 0.73(*2) | -     | Ω                                     | 2       |  |

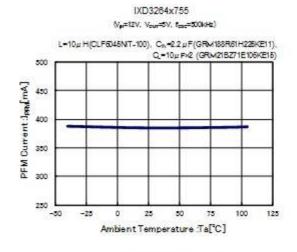

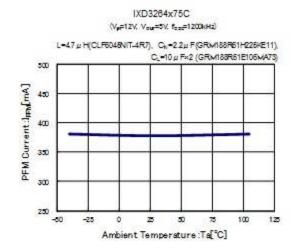

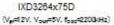

|                                              |                          |                                                                               | IXD3264x755 | -     | 380      | -     | mA                                    |         |  |

| PFM Switch Current                           | I <sub>PFM</sub>         | Connected to external components,                                             | IXD3264x75C | -     | 320      | -     | mA                                    | 1       |  |

|                                              |                          | I <sub>OUT</sub> =1mA                                                         | IXD3264x75D | -     | 200      | -     | mA                                    |         |  |

| High-side Current Limit (*3)                 | I <sub>LIMH</sub>        | V <sub>FB</sub> =0.675V                                                       |             | 920   | 1100     | -     | mA                                    | 2       |  |

|                                              |                          | Type A only, Connected to external co                                         | omponents.  | 0.5   | 4.0      | 4 7   |                                       |         |  |

| Latch Time                                   | t <sub>LAT</sub>         | V <sub>FB</sub> =0V                                                           |             | 0.5   | 1.0      | 1.7   | ms                                    | 6       |  |

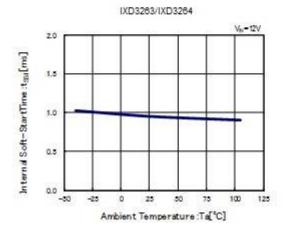

| Internal Soft-Start Time                     | t                        | $V_{EN/SS}$ =0V $\rightarrow$ 12V $_{V_{FB}}$ =0.675V                         |             | 0.5   | 1.0      | 1.7   | ms                                    | 2       |  |

| internal Soit-Start Time                     | t <sub>SS1</sub>         | Time until Lx pin oscillates                                                  |             | 0.5   | 1.0      | 1.7   | 1115                                  | 2       |  |

|                                              |                          | $V_{EN/SS}$ =0V $\rightarrow$ 12V $_{\star}$ V <sub>FB</sub> =0.675V          |             |       |          |       |                                       |         |  |

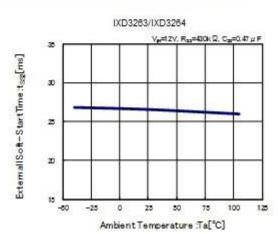

| External Soft-Start Time                     | t <sub>SS2</sub>         | $R_{SS}$ =430KΩ, $C_{SS}$ =0.47 $\mu$ F                                       |             | 17    | 26       | 35    | ms                                    | 3       |  |

|                                              |                          | Time until Lx pin oscillates                                                  |             |       |          |       |                                       |         |  |

| (44)                                         |                          | $V_{FB}$ =0.712V $\rightarrow$ 0.638V, $R_{PG}$ :100k $\Omega$ pul            | -           |       |          |       |                                       | _       |  |

| PG Detect Voltage <sup>(*4)</sup>            | $V_{PGDET}$              | V <sub>FB</sub> Voltage when PG pin voltage cha                               | nges from   | 0.638 | 0.675    | 0.712 | V                                     | 2       |  |

| (*4)                                         |                          | "H" level to "L" level                                                        |             |       |          |       |                                       |         |  |

| PG Output Voltage <sup>(*4)</sup>            | $V_{PG}$                 | V <sub>FB</sub> =0.6V, I <sub>PG</sub> =1mA                                   |             | -     | -        | 0.3   | V                                     | 2       |  |

| Efficiency (*5)                              | EFFI                     | Connected to external components,                                             |             | -     | 85       | _     | %                                     | 1       |  |

|                                              |                          | V <sub>OUT</sub> =5V, I <sub>OUT</sub> =1mA                                   |             |       |          |       | ,,,                                   | •       |  |

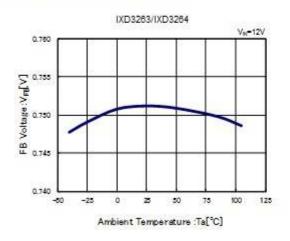

| FB Voltage                                   | $\Delta V_{FB}$ /        | -40°C≦Ta≦105°C                                                                |             | -     | ±100     |       | ppm/°C                                | 2       |  |

| Temperature Characteristics                  | (ΔTopr∙V <sub>FB</sub> ) | 10 0 = 14 = 100 0                                                             |             |       | _100     |       | PP:://                                | •       |  |

PS039901-1017 PRELIMINARY

Test Condition: Unless otherwise stated,  $V_{IN}$ =12V,  $V_{EN/SS}$ =12V (\*1): Please use within the range of  $V_{OUT}/V_{IN} \ge 0.12$  (fosc=500kHz),  $V_{OUT}/V_{IN} \ge 0.14$  (fosc=1.2MHz),  $V_{OUT}/V_{IN} \ge 0.17$  (fosc=2.2MHz)

<sup>(\*2):</sup> Design reference value. This parameter is provided only for reference.

(\*3): Current limit denotes the level of detection at peak of coil current.

(\*4): For the USP-6C Package only.

(\*5): EFFI = {(output voltage) x (output current)} / {(input voltage) x (input current)} x 100

# ■ ELECTRICAL CHARACTERISTICS (Continued)

IXD3263/IXD3264 Ta=25°C

| PARAMETER                    | SYMBOL              | CONDITIONS                                                                                                                                            | MIN  | TYP | MAX | UNIT | CIRCUIT |

|------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|---------|

| FB 'H' Current               | I <sub>FBH</sub>    | $V_{IN}=V_{EN/SS}=18V$ , $V_{FB}=3.0V$                                                                                                                | -0.1 | -   | 0.1 | μA   | 4       |

| FB 'L' Current               | I <sub>FBL</sub>    | $V_{IN}=V_{EN/SS}=18V$ , $V_{FB}=0V$                                                                                                                  | -0.1 | -   | 0.1 | μA   | 4       |

| EN/SS 'H' Current            | I <sub>EN/SSH</sub> | $V_{IN} = V_{EN/SS} = 18V$ , $V_{FB} = 0.825V$                                                                                                        | -    | 0.1 | 0.3 | μA   | 4       |

| EN/SS 'L' Current            | I <sub>EN/SSL</sub> | V <sub>IN</sub> =18V, V <sub>EN/SS</sub> =0V, V <sub>FB</sub> =0.825V                                                                                 | -0.1 | -   | 0.1 | μA   | 4       |

| EN/SS 'H' Voltage            | $V_{EN/SSH}$        | $V_{\text{EN/SS}}{=}0.3V{\to}2.5V\text{, }V_{\text{FB}}{=}0.71V$ $V_{\text{EN/SS}}\text{ Voltage when Lx pin voltage changes from }$ "L" level to "H" | ·=   |     | 18  | V    | 2       |

| EN/SS 'L' Voltage            | V <sub>EN/SSL</sub> | V <sub>EN/SS</sub> =2.5V→0.3V, V <sub>FB</sub> =0.71V<br>V <sub>EN/SS</sub> Voltage when Lx pin voltage changes from<br>"H" level to "L"              | -    | -   | 0.3 | V    | 2       |

| Thermal Shutdown Temperature | $T_{TSD}$           | Junction Temperature                                                                                                                                  | -    | 150 | -   | °C   | _       |

| Hysteresis Width             | T <sub>HYS</sub>    | Junction Temperature                                                                                                                                  | -    | 25  | -   | °C   | _       |

Test Condition: Unless otherwise stated,  $V_{\text{IN}}$ =12V,  $V_{\text{EN/SS}}$ =12V

# **■**TEST CIRCUITS

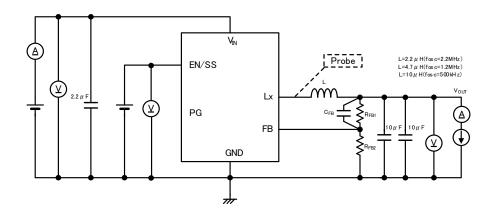

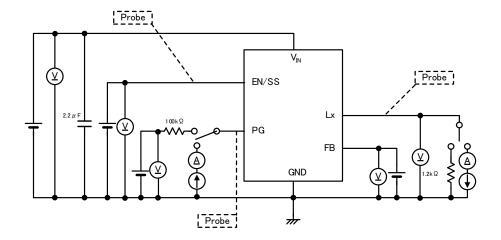

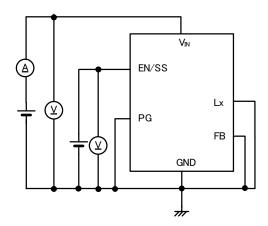

### CIRCUIT①

### CIRCUIT②

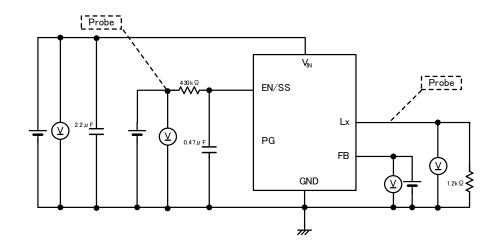

### CIRCUIT®

<sup>\*</sup> PG Pin is USP-6C Package only.

PS039901-1017 PRELIMINARY 8

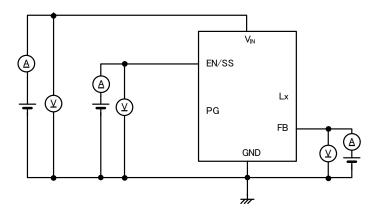

# ■TEST CIRCUITS (Continued)

### CIRCUIT4

### CIRCUIT®

### CIRCUIT®

<sup>\*</sup> PG Pin is USP-6C Package only.

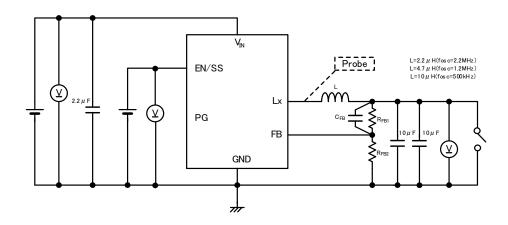

# **■TYPICAL APPLICATION CIRCUIT**

#### [Typical Examples]

| ***/p********************************* |                       |              |                   |                      |  |  |  |

|----------------------------------------|-----------------------|--------------|-------------------|----------------------|--|--|--|

|                                        | Oscillation Frequency | MANUFACTURER | PRODUCT NUMBER    | VALUE                |  |  |  |

|                                        | 500kHz                | TDK          | CLF6045NIT-100M   | 10µH                 |  |  |  |

| L                                      | 1.2MHz                | TDK          | CLF6045NIT-4R7N   | 4.7μH                |  |  |  |

|                                        | 2.2MHz                | TDK          | CLF6045NIT-2R2N   | 2.2µH                |  |  |  |

| C <sub>IN</sub>                        | 500kHz、1.2MHz、2.2MHz  | Murata       | GRM188R61H225KE11 | 2.2µF / 50V          |  |  |  |

| 6                                      | 500kHz                | Murata       | GRM21BZ71E106KE15 | 10µF / 25V 2parallel |  |  |  |

| C <sub>L</sub>                         | 1.2MHz、2.2MHz         | Murata       | GRM188R61E106MA73 | 10μF / 25V 2parallel |  |  |  |

#### <Output voltage setting>

The output voltage can be set by adding an external dividing resistor.

The output voltage is determined by the equation below based on the values of R<sub>FB1</sub> and R<sub>FB2</sub>.

$$\begin{aligned} V_{\text{OUT}} = & V_{\text{FB}} \times (R_{\text{FB1}} + R_{\text{FB2}}) / R_{\text{FB2}} \\ & \text{With } R_{\text{FB1}} + R_{\text{FB2}} \leqq 1 \text{M} \Omega \end{aligned}$$

### <C<sub>FB</sub> setting>

Adjust the value of the phase compensation speed-up capacitor C<sub>FB</sub> using the equation below.

$$C_{FB} = \frac{1}{2\pi \times fz fb \times R_{FB1}}$$

\* When fosc=500kHz or 1.2MHz, a target value for fzfb of about  $\frac{1}{2\pi\sqrt{C_L imes L}}$  is optimum.

### [Setting Example]

To set output voltage to 5V with fosc=500kHz,  $C_L{=}20\mu F,\, L{=}10\mu H$

When  $R_{FB1}=680k\Omega,~R_{FB2}=120k\Omega,~V_{OUT}=0.75V\times(680k\Omega+120k\Omega)$  /  $120k\Omega=5.0V$  And fzfb is set to a target of 11.25kHz using the above equation,  $C_{FB}=1/(2\times\pi\times11.25kHz\times680k\Omega)=20.8pF$

The condition  $V_{\text{OUT}}/V_{\text{IN}} \ge 0.12$  (fosc=500kHz),  $V_{\text{OUT}}/V_{\text{IN}} \ge 0.14$  (fosc=1.2MHz),  $V_{\text{OUT}}/V_{\text{IN}} \ge 0.17$  (fosc=2.2MHz) must be satisfied.

<sup>\*</sup> When fosc=2.2MHz, a target value for fzfb of about 5kHz is optimum.

# ■TYPICAL APPLICATION CIRCUIT (Continued)

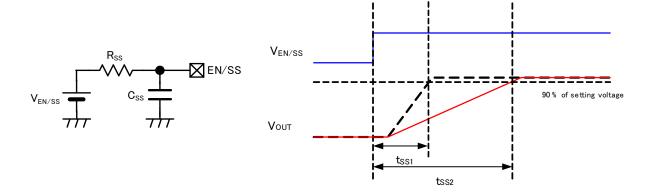

### <Soft-start Time Setting>

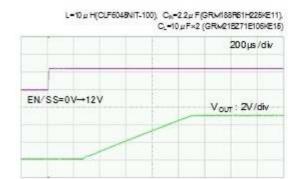

The soft-start time can be adjusted by adding a capacitor and a resistor to the EN/SS pin. Soft-start time ( $t_{ss2}$ ) is approximated by the equation below according to values of  $V_{\text{EN/SS}}$ ,  $R_{\text{SS}}$ , and  $C_{\text{SS}}$ .

$$t_{ss2}$$

= $C_{ss}$ × $R_{ss}$ × $($ -In $($ ( $V_{EN/SS}$ -1.45)/ $V_{EN/SS}$  $)$  $)$

### [Setting Example]

When  $C_{SS}$ =0.47 $\mu$ F,  $R_{SS}$ =430 $k\Omega$  and  $V_{EN/SS}$ =12V,  $t_{SS2}$ =0.47x10 $^{-6}$ x 430 x 10 $^{3}$  x (-In((12-1.45)/12))=26ms (Approx.)

\*The soft-start time is the time from the start of  $V_{\text{EN/SS}}$  until the output voltage reaches 90% of the set voltage. If the EN/SS pin voltage rises steeply without connecting  $C_{\text{SS}}$  and  $R_{\text{SS}}$  ( $R_{\text{SS}}$ =0 $\Omega$ ), Output rises with taking the soft-start time of  $t_{\text{ss1}}$ =1.0ms (TYP.) which is fixed internally.

### **■**OPERATIONAL EXPLANATION

The IXD3263/64 series consists internally of a reference voltage supply with soft-start function, error amp, PWM comparator, ramp wave circuit, oscillator (OSC) circuit, phase compensation (Current feedback) circuit, current limiting circuit, current limit PFM circuit, High-side driver Tr., Low-side driver Tr., buffer drive circuit, internal power supply (LocalReg) circuit, under-voltage lockout (UVLO) circuit, gate clamp (CLAMP) circuit, thermal shutdown (TSD) circuit, power good comparator, control block and other elements.

The voltage feedback from the FB pin is compared to the internal reference voltage by the error amp, the output from the error amp is phase compensated, and the signal is input to the PWM comparator to determine the ON time of switching during PWM operation. The output signal from the error amp is compared to the ramp wave by the PWM comparator, and the output is sent to the buffer drive circuit and output from the LX pin as the duty width of switching. This operation is performed continuously to stabilize the output voltage.

The driver transistor current is monitored at each switching by the phase compensation (Current feedback) circuit, and the output signal from the error amp is modulated as a multi-feedback signal. This allows a stable feedback system to be obtained even when a low ESR capacitor such as a ceramic capacitor is used, and this stabilizes the output voltage.

\*Diodes inside the circuit are ESD protection diodes and parasitic diodes.

#### <Reference voltage source>

The reference voltage source provides the reference voltage to ensure stable output voltage of the DC/DC converter.

### <Oscillator circuit>

The ramp wave circuit determines switching frequency. 500kHz or 1.2MHz or 2.2MHz is available for the switching frequency. Clock pulses generated in this circuit are used to produce ramp waveforms needed for PWM operation.

### <Error amplifier>

The error amplifier is designed to monitor output voltage. The amplifier compares the reference voltage with the feedback voltage divided by the internal voltage divider, RFB1 and RFB2. When a voltage is lower than the reference voltage, then the voltage is fed back, the output voltage of the error amplifier increases. The error amplifier output is fixed internally to deliver an optimized signal to the mixer.

# ■ OPERATIONAL EXPLANATION (Continued)

#### <Current limiting>

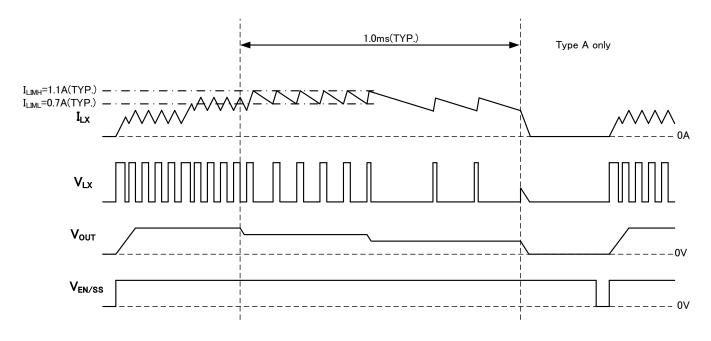

The current limiting circuit of the IXD3263/64 series monitors the current that flows through the High-side driver transistor and Low-side driver transistor, and when over-current is detected, the current limiting function activates.

#### ① Low-side driver Tr. current limiting

The current in the Low-side driver Tr. is detected to equivalently monitor the bottom value of the coil current. The Low-side driver Tr. current limiting function prohibits the High-side driver Tr. from turning on in an over-current state where the bottom value of the coil current is higher than the Low-side driver Tr. current limit value  $I_{LIML}$ . Control to lower the switching frequency  $f_{OSC}$  is also performed. When the over-current state is released, normal operation resumes.

#### ② High-side driver Tr. current limiting

The current in the High-side driver Tr. is detected to equivalently monitor the peak value of the coil current. The High-side driver Tr. current limiting function forcibly turns off the High-side driver Tr. when the peak value of the coil current reaches the High-side driver current limit value  $I_{\text{LIMH}}$ .  $I_{\text{LIMH}}$  is set inside the IC, and therefore the Low-side driver Tr. current limiting function of ① above also detects the over-current state at this time. When the over-current state is released, normal operation resumes.

#### ③ Over-current latch (Type A)

Type A turns off the High-side and Low-side driver Tr. when state ① or ② continues for 1.0ms (TYP.). The LX pin is latch-stopped at the GND level (0V).

The latch-stopped state only stops the pulse output from the Lx pin; the internal circuitry of the IC continues to operate. To restart after latch-stopping, L level and then H level must be input into the EN/SS pin, or VIN pin re-input must be performed (after lowering the voltage below the UVLO detection voltage) to resume operation by soft start.

The over-current latch function may occasionally be released from the current limit detection state by the effects of ambient noise, and it may also happen that the latch time becomes longer or latching does not take place due to board conditions. For this reason, place the input capacitor as close as possible to the IC.

Type B is an automatic recovery type that performs the operation of ① or ② until the over-current state is released.

Low side driver Tr. current limit value I<sub>LIML</sub>=0.7A (TYP.) High-side driver Tr. current limit value I<sub>LIMH</sub>=1.1A (TYP.)

**Current Limiting Timing Chart**

# ■OPERATIONAL EXPLANATION (Continued)

#### <Soft-start function>

The reference voltage applied to the error amplifier is restricted by the start-up voltage of the EN/SS pin. This ensures that the error amplifier operates with its two inputs in balance, thereby preventing ON-time signal from becoming longer than necessary. Therefore, start-up time of the EN/SS pin becomes the set-time of soft-start. The soft-start time can be adjusted by adding a capacitor and a resistor to the EN/SS pin. If the EN/SS pin voltage rises steeply without connecting C<sub>SS</sub> and R<sub>SS</sub> (R<sub>SS</sub>=0Ω), Output rises with taking the soft-start time of t<sub>ss1</sub>=1.0ms (TYP.) which is fixed internally.

The soft-start function operates when the voltage at the EN/SS pin is between 0.3V to 2.5V. If the voltage at the EN/SS pin does not start from 0V but from a middle level voltage when the power is switched on, the soft-start function will become ineffective and the possibilities of large inrush currents and ripple voltages occurring will be increased.

#### <Thermal shutdown>

The thermal shutdown (TSD) as an over current limit is built in the IXD3263/64 series.

When the junction temperature reaches the detection temperature, the driver transistor is forcibly turned off. When the junction temperature falls to the release temperature while in the output stop state, restart takes place by soft-start.

#### <UVLO>

When the V<sub>IN</sub> pin voltage falls below 2.7V (TYP.), the driver transistor is forcibly turned off to prevent false pulse output due to instable operation of the internal circuits. When the V<sub>IN</sub> pin voltage rises above 2.8V (TYP.), the UVLO function is released, the soft-start function activates, and output start operation begins. Stopping by UVLO is not shutdown; only pulse output is stopped and the internal circuits continue to operate.

<Power good>

On USP-6C Package, the output state can be monitored using the power good function.

When the FB voltage drops below 90% (TYP.), the PG pin outputs an "L" signal.

The PG pin is an Nch open drain output, therefore a pull-up resistance (approx.  $100k\Omega$ ) must be connected to the PG pin.

### ■NOTE ON USE

- 1) For the phenomenon of temporal and transitional voltage decrease or voltage increase, the IC may be damaged or deteriorated if IC is used beyond the absolute MAX. specifications.

- 2) Make sure that the absolute maximum ratings of the external components and of this IC are not exceeded.

- 3) The DC/DC converter characteristics depend greatly on the externally connected components as well as on the characteristics of this IC, so refer to the specifications and standard circuit examples of each component when carefully considering which components to select. Be especially careful of the capacitor characteristics and use B characteristics (JIS standard) or X7R, X5R (EIA standard) ceramic capacitors.

The capacitance decrease caused by the bias voltage may become remarkable depending on the external size of the capacitor.

- 4) If there is a large dropout voltage, then there might be pulse-skip during light loads even with PWM control.

- 5) The DC/DC converter of this IC uses a current-limiting circuit to monitor the coil peak current. If the potential dropout voltage is large or the load current is large, the peak current will increase, which makes it easier for current limitation to be applied which in turn could cause the operation to become unstable. When the peak current becomes large, adjust the coil inductance and sufficiently check the operation.

The following formula is used to show the peak current.

Peak Current: Ipk =  $(V_{IN} - V_{OUT}) \times OnDuty / (2 \times L \times f_{OSC}) + I_{OUT}$

L: Coil Inductance [H]

fosc: Oscillation Frequency [Hz]

I<sub>OUT</sub>: Load Current [A]

- 6) If there is a large dropout voltage, a circuit delay could create the ramp-up of coil current with staircase waveform exceeding the current limit.

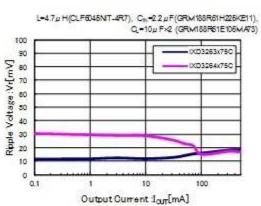

- 7) The ripple voltage could be increased when switching from discontinuous conduction mode to Continuous conduction mode. Please evaluate IC well on customer's PCB.

- 8) The operation of the IC becomes unstable below the minimum operating voltage.

- 9) If the voltage at the EN/SS Pin does not start from 0V but it is at the midpoint potential when the power is switched on, the soft start function may not work properly and it may cause the larger inrush current and bigger ripple voltages.

- 10) The effects of ambient noise and the state of the circuit board may cause release from the current limiting state, and the latch time may lengthen or latch operation may not take place. Please evaluate IC well on customer's PCB.

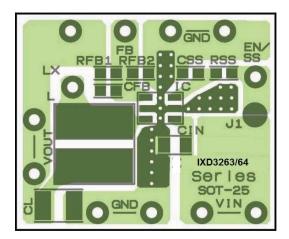

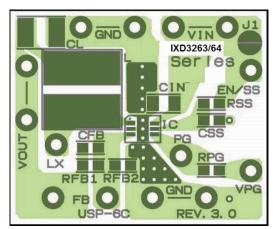

- 11) Instructions of pattern layouts

- The operation may become unstable due to noise and/or phase lag from the output current when the wire impedance is high, Place the input capacitor  $(C_{IN})$  and the output capacitor  $(C_{L})$  as close to the IC as possible.

- (1) In order to stabilize  $V_{IN}$  voltage level, we recommend that a by-pass capacitor  $(C_{IN})$  be connected as close as possible to the  $V_{IN}$  and GND pins.

- (2) Please mount each external component as close to the IC as possible.

- (3) Wire external components as close to the IC as possible and use thick, short connecting traces to reduce the circuit impedance.

- (4) Make sure that the GND traces are as thick as possible, as variations in ground potential caused by high ground currents at the time of switching may result in instability of the IC.

- (5) Please note that internal driver transistors bring on heat because of the load current and ON resistance of High-side driver transistor, Low-side driver transistor

# ■ NOTE ON USE (Continued)

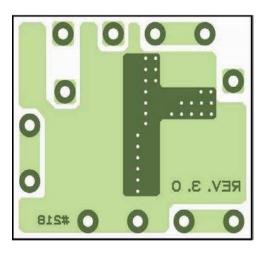

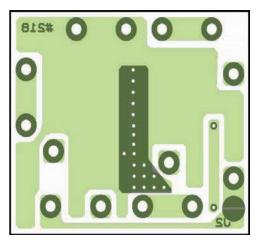

<Reference Pattern Layout>

SOT-25(Front)

USP-6C (Front)

SOT-25 (Back)

USP-6C(Back)

12) Zilog places an importance on improving our products and their reliability. We request that users incorporate fail-safe designs and post-aging protection treatment when using Zilog products in their systems.

# **■TYPICAL PERFORMANCE CHARACTERISTICS**

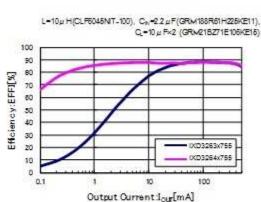

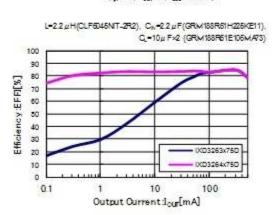

#### (1) Efficiency vs. Output current

IXD3263x755/IXD3264x755 (V<sub>M</sub>=12V, V<sub>Sur</sub>=33V, f<sub>Sac</sub>=500044z)

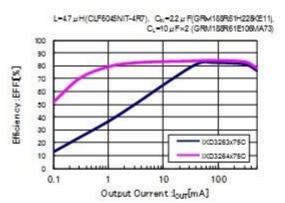

#### IXD3263x75C/IXD3264x75C (V<sub>p</sub>=12V, V<sub>our</sub>=3.3V, f<sub>our</sub>=1200kHz)

IXD3263x75C/IXD3264x75C (Vp=12V, Vour=5V, fooc=1200442)

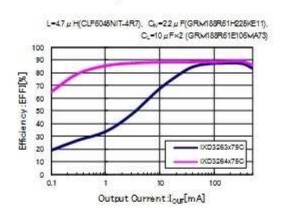

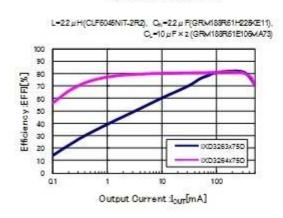

#### IXD3263x75D/IXD3264x75D (V<sub>p</sub>=12V, V<sub>pu</sub>=3.3V, f<sub>pu</sub>=2200kHz)

IXD3263x75D/IXD3264x75D (V<sub>b</sub>=12/, V<sub>bur</sub>=5/, f<sub>bur</sub>=2200kHz)

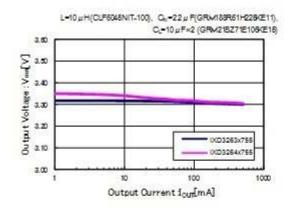

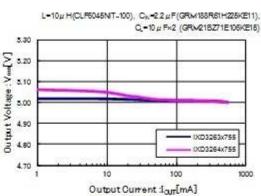

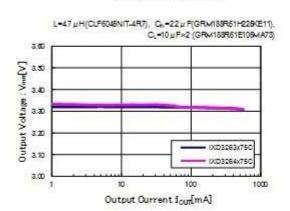

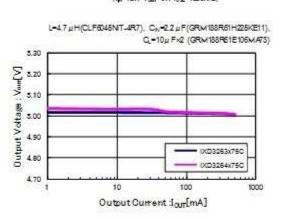

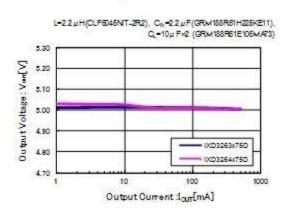

# (2) Output Voltage vs. Output Current

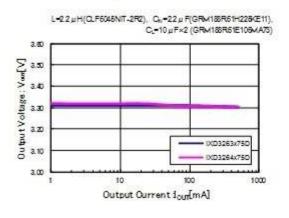

IXD3263x755/IXD3264x755 (V<sub>p</sub>=1,2V, V<sub>our</sub>=3,3V, f<sub>our</sub>=500kHz)

IXD3263x755/IXD3264x755 V<sub>pr</sub>=1zv. V<sub>pur</sub>=5v, 6<sub>30</sub>=500k/k)

IXD3263x75C/IXD3264x75C (V<sub>H</sub>=12V, V<sub>GH</sub>=3.3V, f<sub>GH</sub>=12000Hz)

IXD3263x75C/IXD3264x75C (V<sub>H</sub>=12V, V<sub>SH</sub>=5V, f<sub>SH</sub>=1200kHz)

IXD3263x75D/IXD3264x75D (V<sub>p</sub>=12v, V<sub>our</sub>=33v, f<sub>our</sub>=22000Hz)

IXD3263x75D/IXD3264x75D (V<sub>p</sub>=12V, V<sub>our</sub>=5V, t<sub>our</sub>=2200kHz)

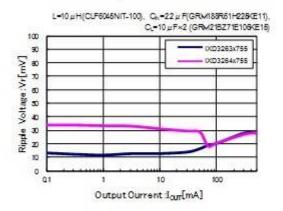

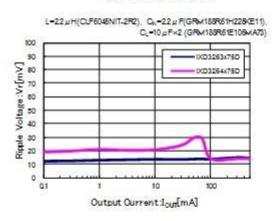

#### (3) Ripple Voltage vs. Output Current

IXD3263x755/IXD3264x755 (V<sub>pr</sub>=12V, V<sub>pur</sub>=5V, f<sub>pac</sub>=500kHz)

# IXD3263x75D/IXD3264x75D \V<sub>P</sub>=1.2\v, V<sub>mP</sub>=3\v, T<sub>0.30</sub>=2.2\text{LMHZ}

#### (4) FB Voltage vs. Ambient Temperature

#### (5) UVLO Voltage vs. Ambient Temperature

### (6) Oscillation Frequency vs. Ambient Temperature

### (7) Stand-by Current vs. Ambient Temperature

#### (8) Lx SW ON Resistance vs. Ambient Temperature

### (10) Internal Soft-Start Time vs. Ambient Temperature

### (11) External Soft-Start Time vs. Ambient Temperature

(12) PFM Current vs. Ambient Temperature

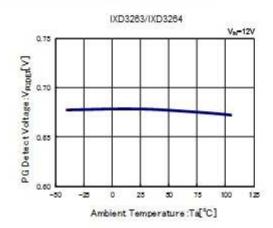

(13) PG Detect Voltage vs. Ambient Temperature

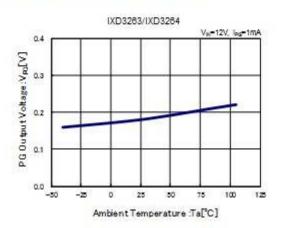

(14) PG Output Voltage vs. Ambient Temperature

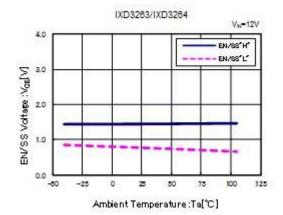

### (15) EN/SS Voltage vs. Ambient Temperature

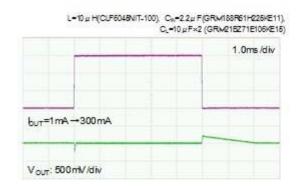

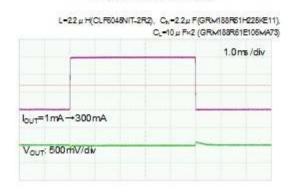

#### (16) Load Transient Response

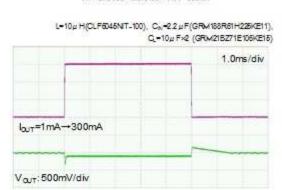

IXD3263x755, f<sub>080</sub>=500kHz Vw=12V, Vou=5.0V, lou=1mA→300mA

IXD3284x755, f<sub>080</sub>=500kHz Vn=12V, Vour=5.0V, lour=1mA=300mA

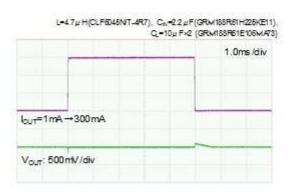

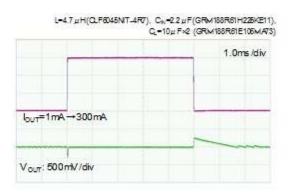

IXD3263x75C \_ f<sub>080</sub>=1200kHz Viv=12V, Vou=5.0V, lour=1mA=300mA

IXD3264x75C , f<sub>090</sub>=1200kHz Vw=12V, Vour=5.0V, lour=1mA-300mA

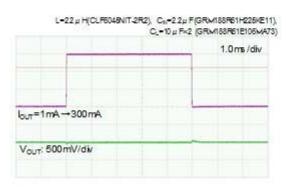

IXD3263x75D, f<sub>080</sub>=2200kHz W=12/, Vout=50V, lout=1mA→300mA

IXD3264x75D , f<sub>080</sub>=2200kHz Viv=12V, Vout=5.0V, lout=1mA=300mA

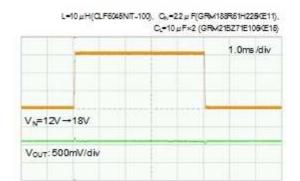

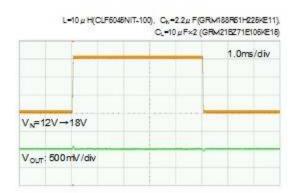

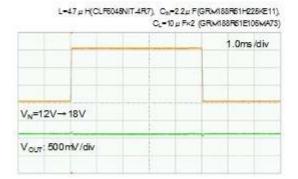

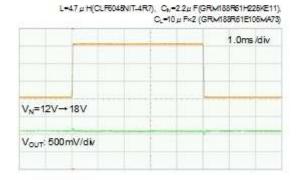

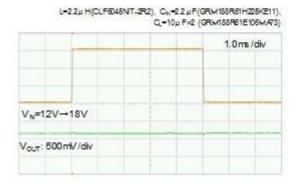

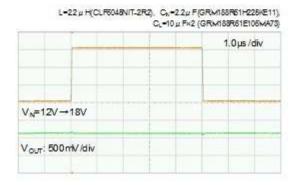

#### (17) Input Transient Response

IXD3263x755 \_ f<sub>09C</sub>=500kHz Vn=12V=18V, Var=9V, lar=300mA

IXD3264x755, f<sub>080</sub>=500kHz Vn=12V→18V, Vox=5V, Iox=300mA

IXD3283x75C, f<sub>030</sub>=1200kHz Vw=12V-18/, Vax=5/, lax=300mA

IXD3284x75C , f<sub>OSC</sub>=1200kHz Vw=12V→18/, Vox=9/, lox=300mA

IXD3283x75D , f<sub>080</sub>=2200kHz V<sub>N</sub>=12V-18V, V<sub>O</sub>T=9V, I<sub>O</sub>T=300mA

IXD3264x75D, f<sub>080</sub>=2200kHz Vw=12V--18V, Vox=5V, lox=300mA

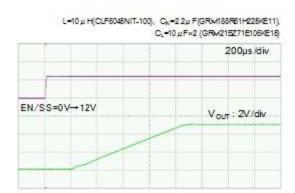

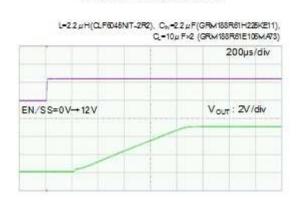

(18) EN/SS Rising Response

IXD3263x755 , f<sub>080</sub>=50.0kHz Vw=12V, Vo=0~12V, Vour=5V, lour=300mA

IXD3284x755 、f<sub>080</sub>=500kHz Vk=12V, Vc=0→12V, Vour=5V, lour=300mA

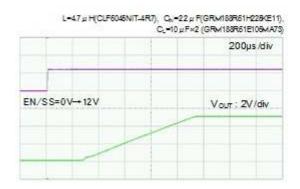

IXD3263x75C . fosc=1200kHz Vw=12/, Vos=0--12/, Vou=5/, lou=300mA

IXD3264x75C 、fcsc=1200kHz Vw=12V, Vcc=0=12V, Vocr=5V, locr=300mA

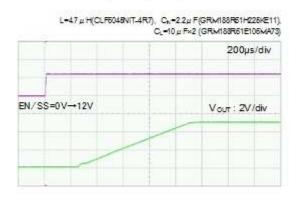

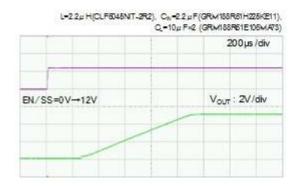

|XD3283x75D, f<sub>090</sub>=2200kHz |Vw=12/, Vos=0→12/, Vos=5V, los=300mA

IXD3284x75D , f<sub>OSC</sub>=2200kHz Vw=12V, Vox=0=12V, Vox=5V, lox=300nA

# **■PACKAGING INFORMATION**

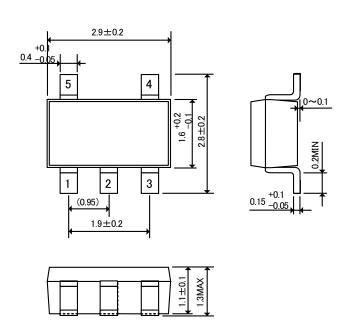

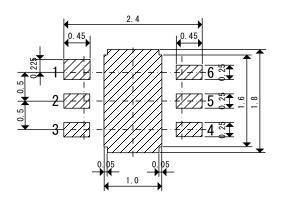

●SOT-25 (unit : mm)

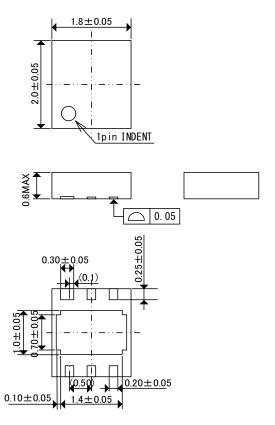

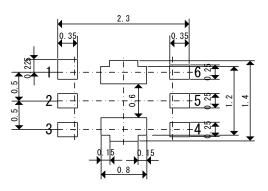

●USP-6C (unit:mm)

# ■ PACKAGING INFORMATION (Continued)

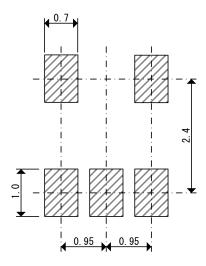

●SOT-25 Reference Pattern Layout (unit: mm)

●USP-6C Reference Pattern Layout (unit: mm)

●USP-6C Reference Metal Mask Design (unit: mm)

### ■MARKING RULE

### ●SOT-25 / USP-6C

(\*) SOT-25 has a dot mark, which is printed under MARK 1 (refer to drawings below).

123 represents products series, products type, Oscillation Frequency

|   | _         | •   | •       |      |                       | •               |

|---|-----------|-----|---------|------|-----------------------|-----------------|

| 1 | MARI<br>② | (3) | SERIES  | TYPE | OSCILLATION FREQUENCY | PRODUCT SERIES  |

| 1 | 1         | Α   | IXD3263 | Α    | 5                     | IXD3263A755xx-G |

| 1 | 1         | В   | IXD3263 | Α    | С                     | IXD3263A75Cxx-G |

| 1 | 1         | С   | IXD3263 | Α    | D                     | IXD3263A75Dxx-G |

| 1 | 1         | D   | IXD3263 | В    | 5                     | IXD3263B755xx-G |

| 1 | 1         | Е   | IXD3263 | В    | С                     | IXD3263B75Cxx-G |

| 1 | 1         | F   | IXD3263 | В    | D                     | IXD3263B75Dxx-G |

| 1 | 1         | Н   | IXD3264 | Α    | 5                     | IXD3264A755xx-G |

| 1 | 1         | K   | IXD3264 | Α    | С                     | IXD3264A75Cxx-G |

| 1 | 1         | L   | IXD3264 | Α    | D                     | IXD3264A75Dxx-G |

| 1 | 1         | М   | IXD3264 | В    | 5                     | IXD3264B755xx-G |

| 1 | 1         | Ν   | IXD3264 | В    | С                     | IXD3264B75Cxx-G |

| 1 | 1         | Р   | IXD3264 | В    | D                     | IXD3264B75Dxx-G |

<sup>45</sup> represents production lot number

01~09, 0A~0Z, 11~9Z, A1~A9, AA~AZ, B1~ZZ in order.

(G, I, J, O, Q, W excluded)

<sup>\*</sup> No character inversion used.

# **Customer Support**

To share comments, get your technical questions answered, or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>. To learn more about this product, find additional documentation, or to discover other fac-ets about Zilog product offerings, please visit the Zilog Knowledge Base at <a href="http://zilog.com/kb">http://zilog.com/kb</a> or consider participating in the Zilog Forum at <a href="http://zilog.com/forum">http://zilog.com/forum</a>. This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <a href="https://www.zilog.com">www.zilog.com</a>.

Warning: DO NOT USE THIS PRODUCT IN LIFE SUPPORT SYSTEMS.

**LIFE SUPPORT POLICY** ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

**As used herein** Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

**Document Disclaimer** ©2017 Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY.