## PD720210

ASSP (Four-port USB3.0 Hub Controller)

R19DS0070EJ0200 Rev.2.00 May 26, 2014

Data Sheet

# 1. OVERVIEW

The PD720210 is a USB 3.0 hub controller that complies with the Universal Serial Bus (USB) Specification Revision 3.0 and operates at up to 5 Gbps. The device incorporates Renesas' market proven design expertise in USB 3.0 interface technologies and market proven USB 2.0 hub core. The device is fully compatible with all prior versions of USB spec and 100% compatible with Renesas' industry standard USB 3.0 host controller. It comes in a small 76-pin QFN package and integrates several commonly required external components, making it ideally suited for applications with limited PCB space. In addition, the PD720210 incorporates Renesas' low-power technologies and supports all main-stream battery charging specifications.

### 1.1 Features

- Compliant with Universal Serial Bus 3.0 Specification Revision 1.0, which is released by USB Implementers Forum, Inc

- Supports the following speed data rates as follows: Low-speed (1.5 Mbps) / Full-speed (12 Mbps) / High-speed (480 Mbps) / Superspeed (5 Gbps)

- Supports USB 3.0 link power management (U0/U1/U2/U3)

- Supports USB 2.0 link power management (LPM: L0/L1/L2/L3)

- Configurable downstream port counts of 2, 3, or 4 ports

- Supports all VBUS control options

- Individual or global over-current detection

- Individual or ganged power control

- Supports USB 3.0/2.0 Compound (non-removable) devices by I/O pin configuration

- Supports clock output (24/12 MHz) for Compound (non-removal) device on downstream ports

- Supports Energy Star and EuP specifications for low-power PC peripheral system

- Single 5 V Power Supply

- On chip LDO for 3.3 V from 5 V input and Switching Regulator for 1.05 V from 5 V input

- System clock: 24 MHz Crystal or Oscillator

- Supports USB Battery Charging Specification Revision 1.2 and other portable devices

- DCP mode of BC 1.2

- CDP mode of BC 1.2

- China Mobile Phone Chargers

- EU Mobile Phone Chargers

- Apple iOS products

- Other major portable devices

- Supports SPI ROM for optional firmware and parameter data

- Small Footprint

- Small and low pin count package with simple pin assignment for PCB layout

- Integration of many peripheral components

- Direct routing of all USB signal traces to connector pins using one layer of the PCB

- Self/Bus-Powered modes can be set by pin strapping

- Integrated termination resistors for USB

- Provides SUSPEND status output

- Supports Port Indicator control (only Green color)

## 1.2 Applications

Stand-alone Hub, Monitor-Hub, Docking Station, Integrated Hub, etc.

## 1.3 Ordering Information

| _       | Part Number       | Package                  | Operating Temperature | Remark            |

|---------|-------------------|--------------------------|-----------------------|-------------------|

| <r></r> | μPD720210K8-BAF-A | 76-pin QFN (9 $	imes$ 9) | 0 to +70°C            | Lead-free product |

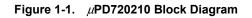

## 1.4 Block Diagram

| Block Name                  | Description                                                                                                |

|-----------------------------|------------------------------------------------------------------------------------------------------------|

| SS PHY                      | SuperSpeed Tx/Rx                                                                                           |

| HS/FS/LS PHY                | High-/Full-/Low-speed transceiver                                                                          |

| VBUS Monitor                | Monitors the VBUS voltage level of the upstream port.                                                      |

| SS US Port<br>Control       | Upstream port control logic for SuperSpeed                                                                 |

| HS/FS/LS US<br>Port Control | Upstream port control logic for High-/Full-/Low-speed                                                      |

| SS Hub Core                 | Central control logic for SS-Hub.                                                                          |

| HS/FS/LS Hub<br>Core        | Central control logic for HS/FS/LS-Hub.                                                                    |

| SS DS Port<br>Control       | Downstream port control logic for SuperSpeed                                                               |

| HS/FS/LS DS<br>Port Control | Downstream port control logic for HS/FS/LS                                                                 |

| VBUS Control                | Controls all the port power switches                                                                       |

| SPI Interface               | Connected to external serial ROM which can hold the optional firmware and hub settings                     |

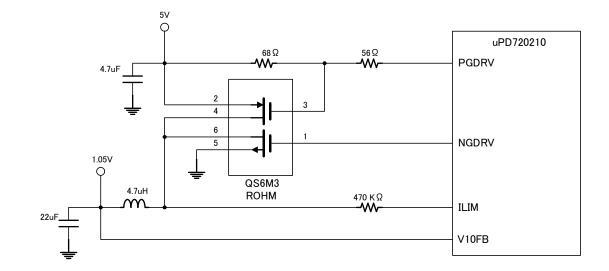

| SW-Regulator                | Switching regulator control logic to output 1.05 V power from 5 V input, utilizing the external transistor |

| LDO                         | Low Drop Out regulator integrated in this hub                                                              |

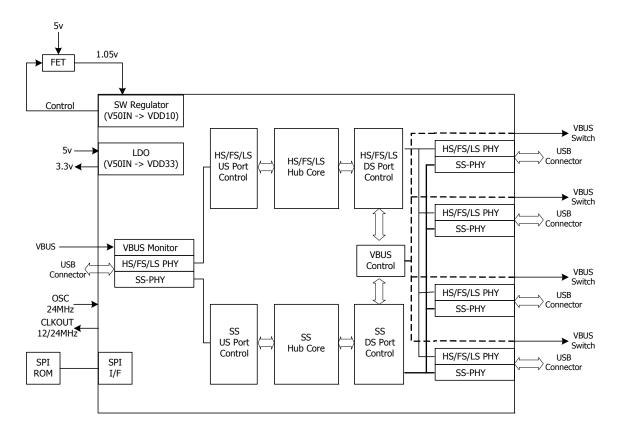

## 1.5 Pin Configuration

76-pin QFN (9 × 9) μPD720210K8-BAF-A

# 2. PIN FUNCTION

This section describes each pin functions.

Strapping information in the tables shows the pin can be used to configure the functional settings of this controller when it is pulled up/down. See  $\mu$ PD720210 User's Manual (R19UH0093E) for detail.

## 2.1 Power Supply

| Pin Name | Pin No.                                        | I/O<br>Type | Function                                                                                                                     |

|----------|------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| VDD10    | 5, 11, 14,<br>22, 28, 31,<br>47, 64, 67,<br>70 | Power       | 1.05 V power supply for Core Logic                                                                                           |

| VDD33    | 8, 17, 25,<br>34, 42, 61,<br>76                | Power       | 3.3 V power supply for IO buffer                                                                                             |

| AVDD33   | 71                                             | Power       | 3.3 V power supply for Analog circuit                                                                                        |

| V50IN    | 49                                             | Power       | LDO Regulator 5 V Input<br>Need to be connected to GND, when integrated LDO is not<br>used.                                  |

| V33OUT   | 48                                             | Power       | LDO 3.3 V Output<br>15 k $\Omega$ and 4.7 $\mu$ F are required between this pin and GND,<br>when integrated LDO is not used. |

| AVDD33R  | 50                                             | Power       | SW Regulator 3.3 V Input                                                                                                     |

| NGDRV    | 52                                             | -           | SW Regulator Nch FET Control Note                                                                                            |

| PGDRV    | 51                                             | -           | SW Regulator Pch FET Control Note                                                                                            |

| ILIM     | 53                                             | -           | SW Regulator Current Sense                                                                                                   |

| V10FB    | 54                                             | -           | SW Regulator Output Monitor                                                                                                  |

**Note** See section 3.10 for important information about the selection of FET.

## 2.2 Analog Interface

| Pin Name | Pin No. | I/О<br>Туре | Function                                                                                                                                                                                                                                                                                       |

|----------|---------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RREF     | 72      | -           | Reference Voltage Input for USB 2.0<br>RREF must be connected to a 1.6 k $\Omega$ resistor with a tolerance of +/- 1%.<br>It is strongly recommended to use a single resistor for 1.6 k $\Omega$ , versus the combined resistance with multiple resistors to achieve this value and tolerance. |

## 2.3 System Clock

| Pin Name | Pin No. | I/O<br>Type | Function                                                                                                                                |

|----------|---------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| XT1      | 74      | IN          | External Oscillator Input<br>Connect to 24 MHz crystal.<br>This pin can be a 3.3 V Oscillator input as well.                            |

| XT2      | 75      | OUT         | External Oscillator Output<br>Connect to 24 MHz crystal<br>When using single-ended clock input to XT1, this pin should be<br>left open. |

## <R> 2.4 System Interface Pins

| Pin Name        | Pin<br>No. | I/O<br>Type | Active<br>Level | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|------------|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUSPEND/NRDCLKO | 1          | OUT         | High/NA         | SUSPEND Output or CLKOUT depending on pin strap setting of SPICSB and OCI1B.         SUSPEND is Suspend state output         1: in suspend state         0: not in suspend state         [Note]         SUSPEND/NRDCLKO output level is Hi-z till this pin function is configured as SUSPEND output or clock output for non-removable device         SPICSB       OCI1B         Pin Function         Low       NRDCLKO         High       X         Depends on Serial ROM setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VBUSM           | 43         | IN          | High            | Upstream Port VBUS Monitor<br>Divide VBUS to 3.3V and connect to VBUSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BUSSEL          | 44         | IN          | N/A             | Power Mode Select Input<br>0: Bus-power setting<br>1: Self-power setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LED1B/SUSPEND   | 37         | OUT         | Low             | When the external ROM is not used (SPICSB is low),<br>LED1B/SUSPEND is used as LED function for LED1B pin<br>for port1 with the following pin strap settings. When the<br>external ROM is used (SPICSB is high) and SUSPEND<br>function is enabled in the ROM Writing Tool,<br>LED1B/SUSPEND is used as SUSPEND function. If the<br>SUSPEND function is not enabled, this pin is not functional<br>(Hi-Z).<br>[Function]<br>LED1B is LED control output signal to indicate port enable.<br>Note that PD720210 supports only Green Color of port<br>indicator.<br>0: Port is enabled<br>Hi-Z: Port is disabled<br>Suspend state is shown by the following pin level.<br>1: in suspend state<br>0: not in suspend state $SPICSB SPISCK' SPISO' SPISI' LED1B' FunctionLow High High High High LED1BLow Others High Reserved(Hi-Z)\boxed{Low X X X X Low Reserved(Hi-Z)\boxed{High X X X X SUSPEND or Hi-Z[Pin strapping option]This pin is used for pin strap option to select the belowfunctions. Refer to PD720210 User's Manual(R19UH0093E) for the following setting- LED function (Chapter 5.1.2)- Battery Charging mode (Chapter 5.1.6)- Address length of external ROM (Chapter 5.1.8)$ |

| RESETB          | 2          | IN          | Low             | Chip Reset Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## <R> 2.5 USB Port Control Pins

| Pin Name               | Pin No.       | I/O<br>Type | Active<br>Level | Function                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------|---------------|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCI1B                  | 45            | IN          | Low             | [Function]<br>Over Current Input<br>0: Over-current condition is detected.<br>1: Non over-current condition is detected.<br>[Pin strapping option]<br>OCI1B Pin Function<br>High Removable device setting<br>and Over current input.<br>Low Non-Removable setting.<br>This pin is used to select non-removable setting.                                                           |

| OCI2B, OCI3B,<br>OCI4B | 55, 57,<br>59 | IN          | Low             | [Function]         Over Current Input         0: Over-current condition is detected.         1: Non over-current condition is detected.         [Pin strapping option]         OCIXB       Pin Function         High       Removable device setting<br>and Over Current Input.         Low       Non-Removable setting.         This pin is used to select non-removable setting. |

| PPON1B/NRDRSTB         | 46            | 1/0         | Low             | [Function]<br>Port Power Control or NRDRSTB (Non-Removable<br>Device Reset) depending on pin strap setting of this<br>pin.<br>PPON1B/NRDRSTB Pin Function<br>High PPON1B<br>Low NRDRSTB<br>PPON1B is a Port Power Control signal<br>0: Power supply for VBUS is on.<br>1: Power supply for VBUS is off.<br>NRDRSTB is a reset signal for Non-Removable<br>device.                 |

| PPON2B                 | 56            | 1/0         | Low             | [Function]         This pin is a Port Power Control signal.         0: Power supply for VBUS is on.         1: Power supply for VBUS is off.         [Pin strapping option]         This pin is used for pin strapping option:         Gang/Individual Power Control of all ports.         PPON2B       Gang/Individual Mode         High       Individual         Low       Gang |

| Pin Name       | Pin No. | I/O<br>Type | Active<br>Level |                                               | Fu                                                            | nction |

|----------------|---------|-------------|-----------------|-----------------------------------------------|---------------------------------------------------------------|--------|

| PPON3B, PPON4B | 58, 60  | I/O         | Low             | 0: Power sup<br>1: Power sup<br>[Pin strappin | oply for VBUS<br>oply for VBUS<br>g option]<br>are used for p |        |

## 2.6 USB Data Pins

| Pin Name                                    | Pin No.           | I/O<br>Type | Function                                                  |

|---------------------------------------------|-------------------|-------------|-----------------------------------------------------------|

| U3TXDN1,<br>U3TXDN2,<br>U3TXDN3,<br>U3TXDN4 | 4, 13, 21,<br>30  | OUT         | USB 3.0 Downstream Transmit data D- signal for SuperSpeed |

| U3TXDNU                                     | 65                | OUT         | USB 3.0 Upstream Transmit data D- signal for SuperSpeed   |

| U3TXDP1,<br>U3TXDP2,<br>U3TXDP3,<br>U3TXDP4 | 3, 12, 20,<br>29  | OUT         | USB 3.0 Downstream Transmit data D+ signal for SuperSpeed |

| U3TXDPU                                     | 66                | OUT         | USB 3.0 Upstream Transmit data D+ signal for SuperSpeed   |

| U3RXDN1,<br>U3RXDN2,<br>U3RXDN3,<br>U3RXDN4 | 7, 16, 24,<br>33  | IN          | USB 3.0 Downstream Receive data D- signal for SuperSpeed  |

| U3RXDNU                                     | 68                | IN          | USB 3.0 Upstream Receive data D- signal for SuperSpeed    |

| U3RXDP1,<br>U3RXDP2,<br>U3RXDP3,<br>U3RXDP4 | 6, 15, 23,<br>32  | IN          | USB 3.0 Downstream Receive data D+ signal for SuperSpeed  |

| U3RXDPU                                     | 69                | IN          | USB 3.0 Upstream Receive data D+ signal for SuperSpeed    |

| U2DM1, U2DM2,<br>U2DM3, U2DM4               | 10, 19, 27,<br>36 | I/O         | USB 2.0 Downstream D- signal for High-/Full-/Low-speed    |

| U2DMU                                       | 63                | I/O         | USB 2.0 Upstream D- signal for High-/Full-/Low-speed      |

| U2DP1, U2DP2,<br>U2DP3, U2DP4               | 9, 18, 26,<br>35  | I/O         | USB 2.0 Downstream D+ signal for High-/Full-/Low-speed    |

| U2DPU                                       | 62                | I/O         | USB 2.0 Upstream D+ signal for High-/Full-/Low-speed      |

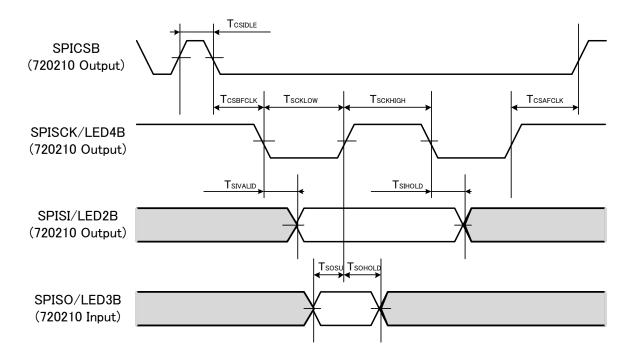

## <R>2.7 SPI Interface

| Pin Name     | Pin No. | I/O<br>Type | Active<br>Level | Function                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|---------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |         |             |                 | [Function]<br>External serial ROM Clock Output or LED output, depending on<br>pin strap setting.                                                                                                                                                                                                                                                                                           |

| SPISCK/LED4B | 41      | 1/0         | N/A             | <ul> <li>[Pin strapping option]</li> <li>This pin is used for pin strapping option to select the below functions. Refer to μPD720210 User's Manual (R19UH0093E)</li> <li>for the following setting</li> <li>LED function (Refer to Chapter 5.1.2)</li> <li>Battery Charging mode (Refer to Chapter 5.1.6)</li> </ul>                                                                       |

|              |         |             |                 | [Function]<br>External serial ROM Chip Select                                                                                                                                                                                                                                                                                                                                              |

| SPICSB       | 38      | 1/0         | Low             | [Pin strapping option]<br>This pin is used for pin strap option to select the below<br>functions. Refer to $\mu$ PD720210 User's Manual (R19UH0093E)<br>for the following setting<br>- External SPI ROM (Refer to Chapter 5.1.1)<br>- LED function (Refer to Chapter 5.1.2)<br>- Address length of external ROM (Refer to Chapter 5.1.8)                                                   |

|              | 40 I/O  |             |                 | [Function]<br>External serial ROM Data Input (to be connected to Serial Data<br>Output pin of the external ROM) or LED output, depending on<br>pin strap setting.                                                                                                                                                                                                                          |

| SPISO/LED3B  |         | 1/0         | N/A             | <ul> <li>[Pin strapping option]</li> <li>This pin is used for pin strap option to select the below functions. Refer to μPD720210 User's Manual (R19UH0093E) for the following setting</li> <li>LED function (Refer to Chapter 5.1.2)</li> <li>Battery Charging mode (Refer to Chapter 5.1.6)</li> <li>Address length of external ROM (Refer to Chapter 5.1.8)</li> </ul>                   |

|              |         |             |                 | [Function]<br>External serial ROM Data Output (to be connected to Serial<br>Data input pin of the external ROM) or LED output, depending<br>on pin strap setting.                                                                                                                                                                                                                          |

| SPISI/LED2B  | 39      | Ι/Ο         | N/A             | <ul> <li>[Pin strapping option]</li> <li>This pin is used for pin strap option to select the below</li> <li>functions. Refer to μPD720210 User's Manual (R19UH0093E)</li> <li>for the following setting</li> <li>LED function (Refer to Chapter 5.1.2)</li> <li>Battery Charging mode (Refer to Chapter 5.1.6)</li> <li>Address length of external ROM (Refer to Chapter 5.1.8)</li> </ul> |

## 2.8 Test Pin

| Pin Name | Pin No. | I/O<br>Type | Active<br>Level | Function                        |

|----------|---------|-------------|-----------------|---------------------------------|

| IC(L)    | 73      | IN          | High            | Test Pin to be connected to GND |

# 3. ELECTRICAL SPECIFICATIONS

### 3.1 Buffer List

• 3.3 V input buffer

IC(L)

• 3.3 V input Schmitt buffer

RESETB, OCI2B, OCI3B, OCI4B

- 3.3 V IOLH = 4 mA output buffer

- SUSPEND/NRDCLKO, SPICSB, PPON1B/NRDRSTB, PPON2B, PPON3B, PPON4B

- 3.3 V IOLH = 12 mA output buffer

LED1B/SUSPEND, SPISI/LED2B, SPISCK/LED4B

- 3.3 V IoL = 12 mA bi-directional buffer

### <R> SPISO/LED3B

• 5 V input Schmitt buffer

VBUSM, BUSSEL, OCI1B

• 3.3 V oscillator interface

XT1, XT2

- USB Classic interface

- U2DP(4:1, U), U2DM(4:1, U)

- USB SuperSpeed Serdes (Serializer-Deserializer)

- U3TXDP(4:1, U), U3TXDN(4:1, U), U3RXDP(4:1, U), U3RXDN(4:1, U)

- LDO Interface

V33OUT, V50IN

Switching Regulator Interface AVDD33R, PGDRV, NGDRV, ILIM, V10FB

## 3.2 Terminology

.

| Parameter            | Symbol                                                           | Meaning                                                                                                                                                        |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage | V <sub>DD33</sub> ,<br>V <sub>DD10</sub> ,<br>AV <sub>DD33</sub> | Indicates the voltage range within which damage or reduced reliability will not result when power is applied to a VDD pin.                                     |

| Input voltage        | VI                                                               | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an input pin.                                      |

| Output voltage       | Vo                                                               | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an output pin.                                     |

| Output current       | lo                                                               | Indicates absolute tolerance values for DC current to prevent<br>damage or reduced reliability when current flows out of or into<br>output pin.                |

| Storage temperature  | T <sub>stg</sub>                                                 | Indicates the element temperature range within which damage or<br>reduced reliability will not result while no voltage or current is<br>applied to the device. |

| Table 3-1. | Terms Used in Absolute Maximum Ratings |

|------------|----------------------------------------|

|------------|----------------------------------------|

| Parameter                | Symbol                                                           | Meaning                                                                                                                                                                      |

|--------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage     | V <sub>DD33</sub> ,<br>V <sub>DD10</sub> ,<br>AV <sub>DD33</sub> | Indicates the voltage range for normal logic operations occur when GND = 0 V.                                                                                                |

| High-level input voltage | Vih                                                              | Indicates the voltage, which is applied to the input pins of the device,<br>is the voltage indicates that the high level states for normal operation<br>of the input buffer. |

|                          |                                                                  | * If a voltage that is equal to or greater than the "Min." value is applied, the input voltage is guaranteed as high level voltage.                                          |

| Low-level input voltage  | VIL                                                              | Indicates the voltage, which is applied to the input pins of the device,<br>is the voltage indicates that the low level states for normal operation<br>of the input buffer.  |

|                          |                                                                  | * If a voltage that is equal to or lesser than the "Max." value is applied, the input voltage is guaranteed as low level voltage.                                            |

| Input rise time          | T <sub>ri</sub>                                                  | Indicates the limit value for the time period when an input voltage applied to the input pins of the device rises from 10% to 90%.                                           |

| Input fall time          | T <sub>fi</sub>                                                  | Indicates the limit value for the time period when an input voltage applied to the input pins of the device falls from 90% to 10%.                                           |

| Operating temperature    | T <sub>A</sub>                                                   | Indicates the ambient temperature range for normal logic operations.                                                                                                         |

### Table 3-2. Terms Used in Recommended Operating Range

### Table 3-3. Term Used in DC Characteristics

| Parameter                        | Symbol          | Meaning                                                                                                                                             |

|----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Off-state output leakage current | I <sub>OZ</sub> | Indicates the current that flows from the power supply pins when the rated power supply voltage is applied whena 3-state output has high impedance. |

| Input leakage current            | lı –            | Indicates the current that flows when the input voltage is supplied to the input pin.                                                               |

## 3.3 Absolute Maximum Ratings

| Parameter                    | Symbol                                    | Condition                                  | Rating       | Units |

|------------------------------|-------------------------------------------|--------------------------------------------|--------------|-------|

| Power supply voltage         | V <sub>DD33</sub> ,<br>AV <sub>DD33</sub> |                                            | -0.5 to +4.6 | V     |

|                              | V <sub>DD10</sub>                         |                                            | -0.5 to +1.4 | V     |

|                              | V50IN                                     |                                            | 5.5          | V     |

| Input voltage, 3.3 V buffer  | VI                                        | V <sub>I</sub> < V <sub>DD33</sub> + 0.5 V | -0.5 to +4.6 | V     |

| Output voltage, 3.3 V buffer | Vo                                        | V <sub>O</sub> <v<sub>DD33 + 0.5 V</v<sub> | -0.5 to +4.6 | V     |

| USB3.0 differential signals  | V <sub>I</sub> /V <sub>O</sub>            | $V_{l}/V_{O} < V_{DD10} + 0.5 V$           | -0.5 to +1.4 | V     |

| Input voltage, 5 V buffer    | VI                                        | V <sub>I</sub> < V <sub>DD33</sub> + 2.5 V | -0.5 to +6.6 | V     |

| Output current               | lo                                        | 4 mA Type                                  | 8            | mA    |

|                              | lo                                        | 12 mA Type                                 | 24           | mA    |

| Storage temperature          | T <sub>stg</sub>                          |                                            | -65 to +125  | °C    |

Table 3-4. Absolute Maximum Ratings

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameters. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded. The ratings and conditions indicated for DC characteristics and AC characteristics represent the quality assurance range during normal operation.

## 3.4 Recommended Operating Ranges

| Parameter                                                         | Symbol                                    | Condition      | Min.   | Тур. | Max.                   | Units |

|-------------------------------------------------------------------|-------------------------------------------|----------------|--------|------|------------------------|-------|

| Operating voltage<br>With external power source                   | V <sub>DD33</sub> ,<br>AV <sub>DD33</sub> |                | 3.0    | 3.3  | 3.6                    | V     |

|                                                                   | V <sub>DD10</sub>                         |                | 0.9975 | 1.05 | 1.1025                 | V     |

| Operating voltage                                                 | V50IN                                     |                | 4.75   | 5.0  | 5.25                   | V     |

| With on-chip Regulators                                           |                                           |                |        |      |                        |       |

| Available Current for external components (3.3 V) <sup>Note</sup> | V33OUT                                    |                |        |      | 30                     | mA    |

| High-level input voltage                                          | V <sub>IH</sub>                           |                | 2.0    |      | V <sub>DD33</sub> +0.3 | V     |

| Low-level input voltage                                           | V <sub>IL</sub>                           |                | -0.3   |      | +0.8                   | V     |

| Input rise time                                                   | T <sub>ri</sub>                           | Normal Buffer  | 0      |      | 200                    | ns    |

|                                                                   |                                           | Schmitt Buffer | 0      |      | 10                     | ms    |

| Input fall time                                                   | T <sub>fi</sub>                           | Normal Buffer  | 0      |      | 200                    | ns    |

|                                                                   |                                           | Schmitt Buffer | 0      |      | 10                     | ms    |

| Operating ambient temperature                                     | T <sub>A</sub>                            |                | 0      |      | +70                    | °C    |

Table 3-5.

Recommended Operating Ranges

## 3.5 DC Characteristics

### Table 3-6. DC Characteristics (V<sub>DD33</sub> = $3.3 \text{ V} \pm 10\%$ , V<sub>DD10</sub> = $1.05 \text{ V} \pm 5\%$ , T<sub>A</sub> = $-0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter                 | Symbol          | Condition                 | Min.                   | Max. | Units |

|---------------------------|-----------------|---------------------------|------------------------|------|-------|

| Off-state output current  | I <sub>oz</sub> | $V_{I} = V_{DD33}$ or GND |                        | ±10  | μA    |

| Input leakage current     | I <sub>I</sub>  | $V_{I} = V_{DD33}$ or GND |                        | ±10  | μA    |

| Low-level output voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 0 mA    |                        | 0.1  | V     |

| High-level output voltage | V <sub>OH</sub> | I <sub>ОН</sub> = 0 mA    | V <sub>DD33</sub> -0.1 |      | V     |

### Table 3-7. USB interface block

| Parameter                                                       | Symbol              | Conditions                      | Min. | Max. | Unit |

|-----------------------------------------------------------------|---------------------|---------------------------------|------|------|------|

| Output pin impedance                                            | Z <sub>HSDRV</sub>  |                                 | 40.5 | 49.5 | Ω    |

| Input Levels for Low-/Full-speed:                               |                     |                                 |      |      |      |

| High-level input voltage (drive)                                | V <sub>IH</sub>     |                                 | 2.0  |      | V    |

| High-level input voltage (floating)                             | V <sub>IHZ</sub>    |                                 | 2.7  | 3.6  | V    |

| Low-level input voltage                                         | VIL                 |                                 |      | 0.8  | V    |

| Differential input sensitivity                                  | V <sub>DI</sub>     | (D+) – (D–)                     | 0.2  |      | V    |

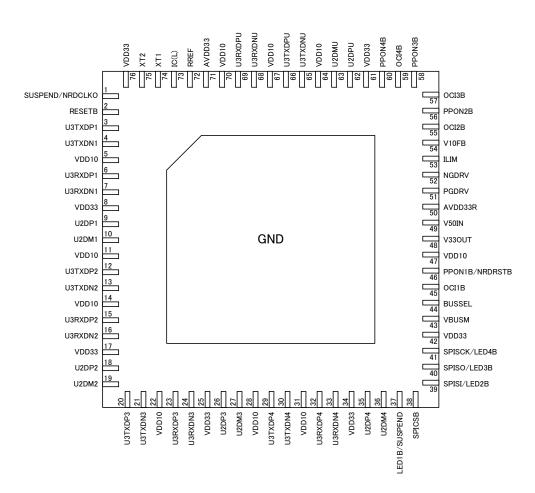

| Differential common mode range                                  | V <sub>CM</sub>     | Includes V <sub>DI</sub> range  | 0.8  | 2.5  | V    |

| Output Levels for Low-/Full-speed:                              |                     |                                 |      |      |      |

| High-level output voltage                                       | V <sub>OH</sub>     | RL of 14.25 k $\Omega$ to GND   | 2.8  | 3.6  | V    |

| Low-level output voltage                                        | V <sub>OL</sub>     | RL of 1.425 k $\Omega$ to 3.6 V | 0.0  | 0.3  | V    |

| SE1                                                             | V <sub>OSE1</sub>   |                                 | 0.8  |      | V    |

| Output signal crossover point voltage                           | V <sub>CRS</sub>    |                                 | 1.3  | 2.0  | V    |

| Input Levels for High-speed:                                    |                     |                                 |      |      |      |

| High-speed squelch detection threshold (differential signal)    | V <sub>HSSQ</sub>   |                                 | 100  | 150  | mV   |

| High-speed disconnect detection threshold (differential signal) | V <sub>HSDSC</sub>  |                                 | 525  | 625  | mV   |

| High-speed data signaling common mode voltage range             | V <sub>HSCM</sub>   |                                 | -50  | +500 | mV   |

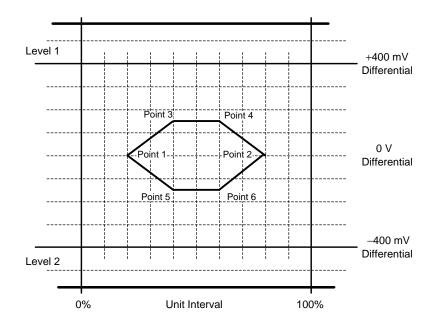

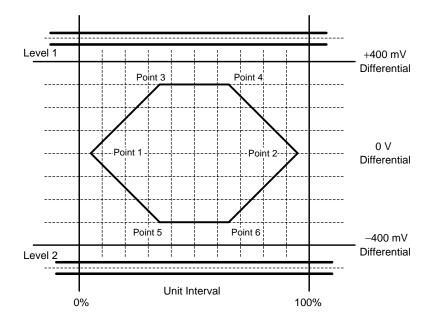

| High-speed differential input signaling level                   | See Figure          | 3-4                             |      |      |      |

| Output Levels for High-speed:                                   |                     |                                 |      |      |      |

| High-speed idle state                                           | V <sub>HSOI</sub>   |                                 | -10  | +10  | mV   |

| High-speed data signaling high                                  | V <sub>HSOH</sub>   |                                 | 360  | 440  | mV   |

| High-speed data signaling low                                   | V <sub>HSOL</sub>   |                                 | -10  | +10  | mV   |

| Chirp J level (differential signal)                             | V <sub>CHIRPJ</sub> |                                 | 700  | 1100 | mV   |

| Chirp K level (differential signal)                             | V <sub>CHIRPK</sub> |                                 | -900 | -500 | mV   |

Figure 3-1. Differential Input Sensitivity Range for Low-/Full-speed

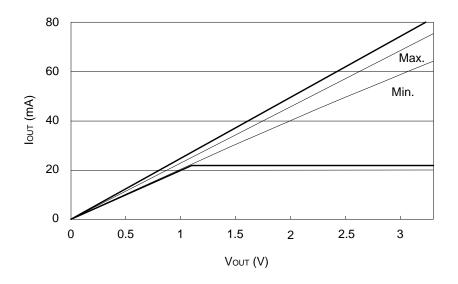

Figure 3-2. Full-speed Buffer VoH/IOH Characteristics for High-speed Capable Transceiver

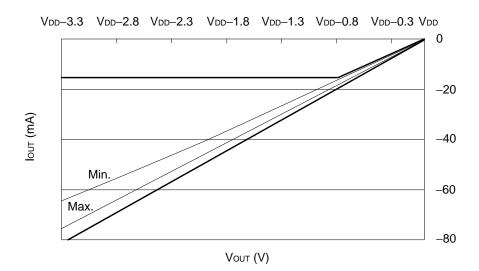

Figure 3-3. Full-speed Buffer VoL/IoL Characteristics for High-speed Capable Transceiver

Figure 3-4. Receiver Sensitivity for Transceiver at DP/DM

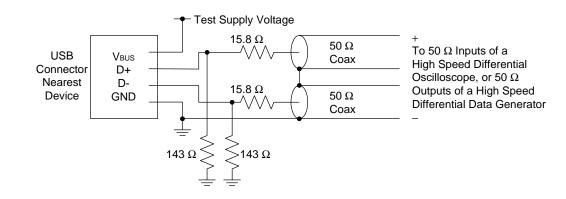

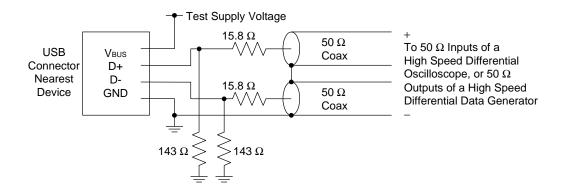

Figure 3-5 Receiver Measurement Fixtures

| Parameter                                     | Symbol               | Condition | Min. | Max. | Units |

|-----------------------------------------------|----------------------|-----------|------|------|-------|

| Cut-off current of on-chip Regulator (1.05 V) | I <sub>cutoff1</sub> | -         | 1.4  | 1.8  | A     |

| Cut-off current of on-chip Regulator (3.3 V)  | I <sub>cutoff3</sub> | -         | 0.8  | 1.2  | A     |

## 3.6 Pin Capacitance

| Parameter                     | Symbol           | Condition | Min. | Max. | Units |

|-------------------------------|------------------|-----------|------|------|-------|

| SPI Interface Pin capacitance | C <sub>SPI</sub> |           |      | 5    | pF    |

| Table 3-9. | Pin Capacitance  |

|------------|------------------|

|            | i in oupdoitance |

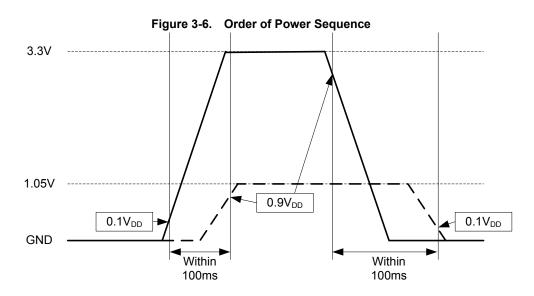

## 3.7 Sequence for Turning On or Off Power

When the external power source for 1.05 V and 3.3 V power is used, it is recommended that the time difference between the start of power-supply rise (3.3 V or 1.05 V) and the point where both power supplies are stabilized should be within 100 ms, regardless of the order of power sequence. A voltage of  $0.1V_{DD}$  has to be raised to  $0.9V_{DD}$  within the specified time.

When the on-chip LDO and the switching regulator are used, this timing is controlled by the internal circuit as defined here.

## 3.8 AC Characteristics

### 3.8.1 System Clock

### Table 3-10. System Clock (XT1/XT2) Ratings (V<sub>DD33</sub> = $3.3 \text{ V} \pm 10\%$ , V<sub>DD10</sub> = $1.05 \text{ V} \pm 5\%$ , T<sub>A</sub> = $-0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter        | Symbol            | Condition | Min. | Тур. | Max. | Units |

|------------------|-------------------|-----------|------|------|------|-------|

| Clock frequency  | F <sub>CLK</sub>  | Crystal   | -100 | 24   | +100 | MHz   |

|                  |                   |           | ppm  |      | ppm  |       |

| Clock duty cycle | T <sub>DUTY</sub> |           | 40   | 50   | 60   | %     |

**Remark** Required accuracy of crystal or oscillator block includes initial frequency accuracy, the spread of Crystal capacitor loading, supply voltage, temperature and aging, etc.

### 3.8.2 Reset and Clock Timing

#### <R>

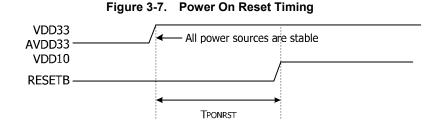

### Table 3-11. Power On Reset (RESETB) Timings

| Parameter           | Symbol  | Condition      | Min. | Max. | Units |

|---------------------|---------|----------------|------|------|-------|

| Power on reset time | TPONRST | See Figure 3-7 | 10   |      | ms    |

Remarks 1. No order in power-on VDD33, AVDD33, AVDD33 and VDD10.

- 2. All power sources should be stable within 100 ms from the earliest turned on power sources.

- 3. RESETB shall be de-asserted after all power sources and the system clock become stable.

# <R>

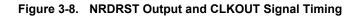

### Table 3-12. NRDRST Output and CLKOUT Signal Timing

| Parameter                                                    | Symbol                 | Condition      | Min. | Max. | Units |

|--------------------------------------------------------------|------------------------|----------------|------|------|-------|

| Clock out timing after Reset out ends                        | T <sub>RSTtoCLK</sub>  | See Figure 3-8 |      | 300  | s     |

| Reset timing for Non-Removable Device after Clock out starts | T <sub>CLKtoRSTE</sub> | See Figure 3-8 |      | 30   | ms    |

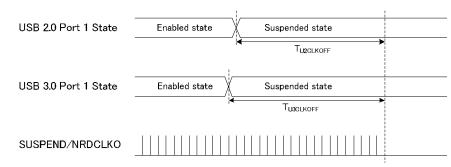

<R>Table 3-13, Figure 3-9 shows the stopping timing of clock output of SUSPNED/NRDCLKO pin. There are three cases for the timing. To stop the clock output, a setting of ROM Writing Tool is needed. Refer to µPD720210 User's Manual (R19UH0093E) in more detail.

Case 1: Non-removable device of Port 1 is a USB 2.0 device.

After a USB 2.0 non-removable device of Port1 transitions to suspend state and the wait time of " $T_{U2CLKOFF}$ " is satisfied, the clock output stops.

Case 2: Non-removable device of Port 1 is a USB 3.0 device except USB 3.0 hub. After a USB 3.0 non-removable device of Port1 transitions to suspend state and the wait time of "T<sub>U3CLKOFF</sub>" is satisfied, the clock output stops.

Case 3: Non-removable device of Port 1 is a USB 3.0 hub.

After a USB 3.0 non-removable hub of Port1 transitions to suspend state and the wait time of " $T_{U2CLKOFF}$ " and " $T_{U3CLKOFF}$ " is satisfied, the clock output stops.

<R>

### Table 3-13. NRDCLKO Clock Output Stop Timing

| Parameter                                                                                                       | Symbol                | Condition      | Min. | Max. | Units |

|-----------------------------------------------------------------------------------------------------------------|-----------------------|----------------|------|------|-------|

| Wait time of stopping Clock Output after Non-<br>Removable USB 2.0 Device transitions to<br>Suspend state Note1 | T <sub>U2CLKOFF</sub> | See Figure 3-9 |      | 50   | ms    |

| Wait time of stopping Clock Output after Non-<br>Removable USB 3.0 Device transitions to<br>Suspend state Note2 | T <sub>U3CLKOFF</sub> | See Figure 3-9 |      | 50   | ms    |

- **Notes 1.** If USB 2.0 Port 1 detects any resume signal during this wait time, μPD720210 doesn't stop the clock output for non-removable device.

- If USB 3.0 Port 1 detects U3exit during this wait time, μPD720210 doesn't stop the clock output for nonremovable device.

<R>

### Figure 3-9. NRDCLKO Clock Output Stop Timing

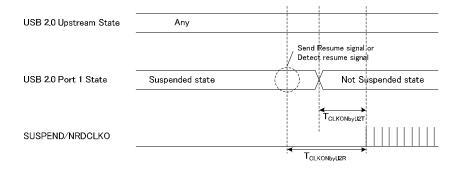

<R>Table 3-14, Figure 3-10, Figure 3-11 and Figure 3-12 shows the starting timing of clock output of SUSPNED/NRDCLKO pin after stopping the clock output. There are three cases for the timing.

Case 1: Non-removable device of Port 1 is a USB 2.0 device.

If "T<sub>CLKONbyU2R</sub>" or "T<sub>CLKONbyU2T</sub>" or "T<sub>CLKONbyU2Sta</sub>" is satisfied, the clock output is initiated.

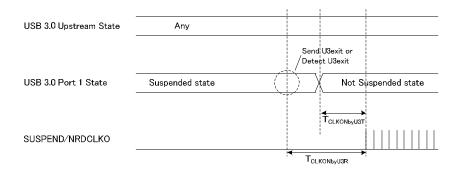

Case 2: Non-removable device of Port 1 is a USB 3.0 device except USB 3.0 hub.

If "T<sub>CLKONbyU3R</sub>" or "T<sub>CLKONbyU3T</sub>" is satisfied, the clock output is initiated.

Case 3: Non-removable device of Port 1 is a USB 3.0 hub.

If " $T_{CLKONbyU2R}$ " or " $T_{CLKONbyU2T}$ " or " $T_{CLKONbyU2Sta}$ " or " $T_{CLKONbyU3R}$ " or " $T_{CLKONbyU3T}$ " is satisfied, the clock output is initiated.

| <r></r> |  |

|---------|--|

|---------|--|

| Parameter                                                                                             | Symbol                    | Condition       | Min. | Max. | Units |

|-------------------------------------------------------------------------------------------------------|---------------------------|-----------------|------|------|-------|

| Start timing of Clock Output after sending resume signal or detecting resume signal on USB 2.0 Port 1 | T <sub>CLKONbyU2</sub> R  | See Figure 3-10 |      | 1    | ms    |

| Start timing of Clock Output after transitioning to not suspended state on USB 2.0 Port 1             | T <sub>CLKONbyU2T</sub>   | See Figure 3-10 |      | 1    | ms    |

| Start timing of Clock Output after transitioning to not suspended state on USB 2.0 Upstream           | T <sub>CLKONbyU2Sta</sub> | See Figure 3-11 |      | 1    | ms    |

| Start timing of Clock Output after sending U3exit<br>or detecting U3exit on USB 3.0 Port 1            | T <sub>CLKONby</sub> u3r  | See Figure 3-12 |      | 1    | ms    |

| Start timing of Clock Output after transitioning to not suspended state on USB 3.0 Port 1             | T <sub>CLKONbyU3T</sub>   | See Figure 3-12 |      | 1    | ms    |

### Table 3-14. NRDCLKO Clock Output Start Timing

<R>

### Figure 3-10. NRDCLKO Clock Output Start Timing by Resuming USB 2.0 Port 1

### <R> Figure 3-11. NRDCLKO Clock Output Initiate Timing by USB 2.0 Upstream State Transition

| USB 20 Upstream State | Suspended State | Not Suspended State |

|-----------------------|-----------------|---------------------|

| USB 2.0 Port 1 State  | Suspended state |                     |

|                       |                 |                     |

| SUSPEND/NRDCLKO       |                 |                     |

<R>

### Figure 3-12. NRDCLKO Clock Output Initiate Timing by Resuming USB 3.0 Port 1

## 3.8.3 USB3.0 SuperSpeed Interface – Differential Transmitter (TX) Specifications

### (Refer to Universal Serial Bus 3.0 Specification Revision 1.0 for more information)

| Parameter                                                      | Symbol                    | Min    | Max    | Units |

|----------------------------------------------------------------|---------------------------|--------|--------|-------|

| Unit Interval                                                  | UI                        | 199.94 | 200.06 | ps    |

| Differential p-p Tx voltage swing                              | V <sub>TX</sub> -DIFF-PP  | 0.8    | 1.2    | V     |

| Tx de-emphasis                                                 | VTX-DE-RATIO              | 3.0    | 4.0    | dB    |

| DC differential impedance                                      | RTX-DIFF-DC               | 72     | 120    | Ω     |

| The amount of voltage change allowed during Receiver Detection | VTX-RCV-DETECT            |        | 0.6    | V     |

| AC Coupling Capacitor                                          | CAC-COUPLING              | 75     | 200    | nF    |

| Maximum slew rate                                              | t <sub>CDR-SLEW-MAX</sub> |        | 10     | ms/s  |

| Table 3-15. Transmitter Normative Electrical Parameters | Table 3-15. |

|---------------------------------------------------------|-------------|

|---------------------------------------------------------|-------------|

| Table 3-16. | Transmitter Informative Electrical Parameters |

|-------------|-----------------------------------------------|

|             |                                               |

| Parameter                                                 | Symbol                           | Min   | Max   | Units |

|-----------------------------------------------------------|----------------------------------|-------|-------|-------|

| Deterministic min pulse                                   | t <sub>MIN-PULSE-Dj</sub>        | 0.96  |       | UI    |

| Tx min pulse                                              | t <sub>MIN-PULSE-Tj</sub>        | 0.90  |       | UI    |

| Transmitter Eye                                           | t <sub>TX-EYE</sub>              | 0.625 |       | UI    |

| Tx deterministic jitter                                   | t <sub>TX-DJ-DD</sub>            |       | 0.205 | UI    |

| Tx input capacitance for return loss                      | CTX-PARASITIC                    |       | 1.25  | pf    |

| Transmitter DC common mode<br>impedance                   | R <sub>TX-DC</sub>               | 18    | 30    | Ω     |

| Transmitter short-circuit current limit                   | I <sub>TX-SHORT</sub>            |       | 60    | mA    |

| Transmitter DC common-mode voltage                        | V <sub>TX-DC-CM</sub>            | 0     | 2.2   | V     |

| Tx AC common mode voltage                                 | V <sub>TX-CM-AC-PP-ACTIVE</sub>  |       | 100   | mVp-p |

| Absolute DC Common Mode Voltage between U1 and U0         | V <sub>TX-CM-DC-ACTIVE-</sub>    |       | 200   | mV    |

| Electrical Idle Differential Peak- Peak<br>Output voltage | V <sub>TX-IDLE</sub> -DIFF-AC-pp | 0     | 10    | mV    |

| DC Electrical Idle Differential Output Voltage            | V <sub>TX</sub> -IDLE-DIFF-DC    | 0     | 10    | mV    |

### 3.8.4 USB3.0 SuperSpeed Interface – Differential Receiver (RX) Specifications

### (Refer to Universal Serial Bus 3.0 Specification Revision 1.0 for more information)

| Parameter                                                         | Symbol                  | Min    | Max    | Units |

|-------------------------------------------------------------------|-------------------------|--------|--------|-------|

| Unit Interval                                                     | UI                      | 199.94 | 200.06 | ps    |

| Receiver DC common mode<br>impedance                              | R <sub>RX-DC</sub>      | 18     | 30     | Ω     |

| DC differential impedance                                         | R <sub>RX-DIFF-DC</sub> | 72     | 120    | Ω     |

| DC Input CM Input Impedance for<br>V>0 during Reset of Power down | Zrx-high-imp-dc-pos     | 25k    |        | Ω     |

| LFPS Detect Threshold                                             | VRX-LFPS-DET-DIFF-p-p   | 100    | 300    | mV    |

### Table 3-17. Receiver Normative Electrical Parameters

### Table 3-18. Receiver Informative Electrical Parameters

| Parameter                                                | Symbol                            | Min | Max   | Units  |

|----------------------------------------------------------|-----------------------------------|-----|-------|--------|

| Differential Rx peak-to-peak voltage                     | V <sub>RX-DIFF-PP-POST-EQ</sub>   | 30  |       | mV     |

| Max Rx inherent timing error                             | T <sub>RX-Tj</sub>                |     | 0.45  | UI     |

| Max Rx inherent deterministic timing error               | T <sub>RX-DJ-DD</sub>             |     | 0.285 | UI     |

| Rx input capacitance for return loss                     | C <sub>RX-PARASITIC</sub>         |     | 1.1   | pF     |

| Rx AC common mode voltage                                | V <sub>RX-CM-AC-P</sub>           |     | 150   | mVPeak |

| Rx AC common mode voltage during the U1 to U0 transition | VRX-CM-DC-ACTIVE-IDLE-<br>DELTA-P |     | 200   | mVPeak |

### 3.8.5 USB2.0 Interface

| Parameter                                                                                                                              | Symbol           | Conditions                               | Min.         | Max.         | Unit     |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------|--------------|--------------|----------|

| Low-speed Electrical Characteristics                                                                                                   |                  |                                          |              |              |          |

| Rise time (10% to 90%)                                                                                                                 | tlr              | C∟ = 200 pF to 600 pF                    | 75           | 300          | ns       |

| Fall time (90% to 10%)                                                                                                                 | t∟⊧              | C <sub>L</sub> = 200 pF to 600 pF        | 75           | 300          | ns       |

| Differential rise and fall time matching                                                                                               | <b>t</b> lrfm    | (t <sub>LR</sub> /t <sub>LF</sub> ) Note | 80           | 125          | %        |

| Low-speed data rate                                                                                                                    | <b>t</b> LDRATHS | Average bit rate                         | 1.49925      | 1.50075      | Mbps     |

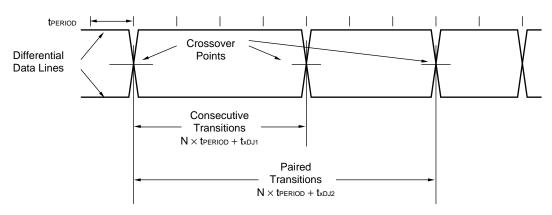

| Downstream facing port source jitter total<br>(including frequency tolerance) ( <b>Figure 3-</b><br><b>19</b> ):<br>To next transition | todji            |                                          | -25          | +25          | ns       |

| For paired transitions                                                                                                                 | tddj2            |                                          | -14          | +14          | ns       |

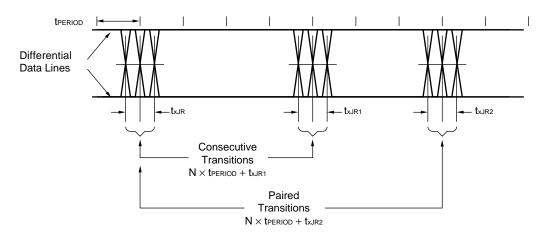

| Downstream facing port differential receiver<br>jitter total (including frequency tolerance)<br>(Figure 3-19):                         |                  |                                          |              |              |          |

| To next transition<br>For paired transitions                                                                                           | tujr1<br>tujr2   |                                          | -152<br>-200 | +152<br>+200 | ns<br>ns |

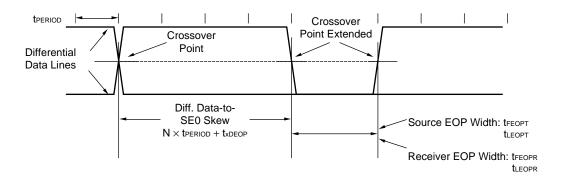

| Source SE0 interval of EOP (Figure 3-18)                                                                                               | <b>t</b> leopt   |                                          | 1.25         | 1.5          | μs       |

| Receiver SE0 interval of EOP (Figure 3-18)                                                                                             | <b>t</b> leopr   |                                          | 670          |              | ns       |

| Width of SE0 interval during differential transition                                                                                   | t∟s⊤             |                                          |              | 210          | ns       |

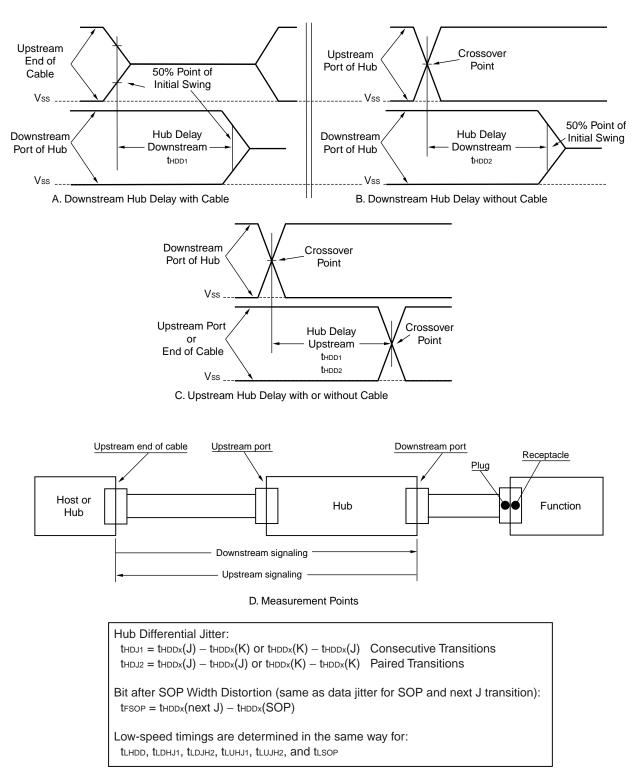

| Hub differential data delay (Figure 3-15)                                                                                              | <b>t</b> lhdd    |                                          |              | 300          | ns       |

| Hub differential driver jitter (including cable) (Figure 3-15):                                                                        |                  |                                          |              |              |          |

| Downstream facing port<br>To next transition<br>For paired transitions                                                                 | tldhj1<br>tldhj2 |                                          | 45<br>15     | +45<br>+15   | ns<br>ns |

| Upstream facing port<br>To next transition<br>For paired transitions                                                                   | tluhj1<br>tluhj2 |                                          | 45<br>45     | +45<br>+45   | ns<br>ns |

| Data bit width distortion after SOP (Figure 3-15)                                                                                      | <b>t</b> lsop    |                                          | -60          | +60          | ns       |

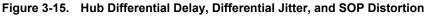

| Hub EOP delay relative to tHDD (Figure 3-<br>16)                                                                                       | <b>t</b> leopd   |                                          | 0            | 200          | ns       |

| Hub EOP output width skew (Figure 3-16)                                                                                                | <b>t</b> lhesk   |                                          | -300         | +300         | ns       |

| Full-speed Electrical Characteristics                                                                                                  |                  |                                          |              |              | •        |

| Rise time (10% to 90%)                                                                                                                 | <b>t</b> FR      | C∟ = 50 pF,<br>Rs = 36 Ω                 | 4            | 20           | ns       |

| Fall time (90% to 10%)                                                                                                                 | tff              | C∟ = 50 pF,<br>Rs = 36 Ω                 | 4            | 20           | ns       |

| Differential rise and fall time matching                                                                                               | <b>t</b> FRFM    | (tfr/tff)                                | 90           | 111.11       | %        |

| Full-speed data rate                                                                                                                   | <b>t</b> FDRATHS | Average bit rate                         | 11.9940      | 12.0060      | Mbps     |

| Frame interval                                                                                                                         | <b>t</b> FRAME   |                                          | 0.9995       | 1.0005       | ms       |

| Table 3-19. | USB Interface (1 of | f 4) |

|-------------|---------------------|------|

|             |                     | •••  |

**Note** Excluding the first transition from the Idle state.

| Parameter                                                                                         | Symbol           | Conditions          | Min.        | Max.                   | Unit         |

|---------------------------------------------------------------------------------------------------|------------------|---------------------|-------------|------------------------|--------------|

| Full-speed Electrical Characteristics (Conti                                                      | nued)            | Γ                   | 1           | 1                      | [            |

| Consecutive frame interval jitter                                                                 | trfi             | No clock adjustment |             | 42                     | ns           |

| Source jitter total (including frequency tolerance) ( <b>Figure 3-17</b> ):<br>To next transition | t <sub>DJ1</sub> | Note                | -3.5        | +3.5                   | ns           |

| For paired transitions                                                                            | t <sub>DJ2</sub> |                     | -4.0        | +4.0                   | ns           |

| Source jitter for differential transition to SE0 transition ( <b>Figure 3-18</b> )                | <b>t</b> FDEOP   |                     | -2          | +5                     | ns           |

| Receiver jitter ( <b>Figure 3-19</b> ):<br>To Next Transition<br>For Paired Transitions           | tjri<br>tjri     |                     | -18.5<br>-9 | +18.5<br>+9            | ns<br>ns     |

| Source SE0 interval of EOP (Figure 3-18)                                                          | <b>t</b> FEOPT   |                     | 160         | 175                    | ns           |

| Receiver SE0 interval of EOP (Figure 3-18)                                                        | <b>t</b> FEOPR   |                     | 82          |                        | ns           |

| Width of SE0 interval during differential transition                                              | test             |                     |             | 14                     | ns           |

| Hub differential data delay ( <b>Figure 3-15</b> )<br>(with cable)<br>(without cable)             | thdd1<br>thdd2   |                     |             | 70<br>44               | ns<br>ns     |

| Hub differential driver jitter (including cable)<br>( <b>Figure 3-15</b> ):<br>To next transition | tноj1            |                     | -3          | +3                     | ns           |

| For paired transitions                                                                            | thdj2            |                     | -1          | +1                     | ns           |

| Data bit width distortion after SOP ( <b>Figure</b><br><b>3-15</b> )                              | <b>t</b> fsop    |                     | -5          | +5                     | ns           |

| Hub EOP delay relative to thdd (Figure 3-16)                                                      | <b>t</b> FEOPD   |                     | 0           | 15                     | ns           |

| Hub EOP output width skew (Figure 3-16)                                                           | <b>t</b> FHESK   |                     | -15         | +15                    | ns           |

| High-speed Electrical Characteristics                                                             |                  |                     |             |                        |              |

| Rise time (10% to 90%)                                                                            | thsr             |                     | 500         |                        | ps           |

| Fall time (90% to 10%)                                                                            | thsp             |                     | 500         |                        | ps           |

| Driver waveform                                                                                   | See Figure       | 3-13.               |             |                        |              |

| High-speed data rate                                                                              | <b>t</b> hsdrat  |                     | 479.760     | 480.240                | Mbps         |

| Microframe interval                                                                               | <b>t</b> HSFRAM  |                     | 124.9375    | 125.0625               | μs           |

| Consecutive microframe interval difference                                                        | thsrfi           |                     |             | 4 HHigh-<br>speed      | Bit<br>times |

| Data source jitter                                                                                | See Figure       | 3-13                |             |                        |              |

| Receiver jitter tolerance                                                                         | See Figure       | 3-4.                |             |                        |              |

| Hub data delay (without cable)                                                                    | thshdd           |                     |             | 36 High-<br>speed+4 ns | Bit<br>times |

| Hub data jitter                                                                                   | See Figure       | 3-4, Figure 3-13.   |             |                        |              |

| Hub delay variation range                                                                         | <b>t</b> HSHDV   |                     |             | 5 HHigh-<br>speed      | Bit<br>times |

|                                                                                                   |                  |                     |             | 1                      |              |

Table 3-20. USB Interface (2 of 4)

**Note** Excluding the first transition from the Idle state.

| Parameter                                                                                                                 | Symbol           | Conditions                                        | Min. | Max.         | Unit            |

|---------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|------|--------------|-----------------|

| Hub Event Timings                                                                                                         | -                |                                                   |      | -<br>-       |                 |

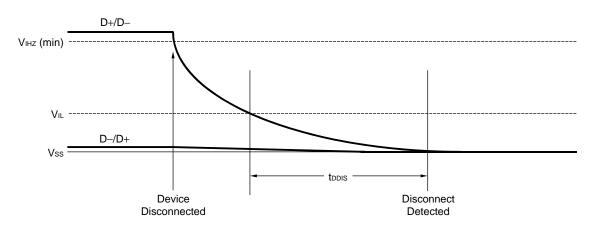

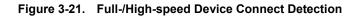

| Time to detect a downstream facing port<br>connect event ( <b>Figure 3-21</b> ):<br>Awake hub                             | tdcnn            |                                                   | 2.5  | 2000         | μs              |

| Suspended hub<br>Time to detect a disconnect event at a hub's                                                             | topis            |                                                   | 2.5  | 12000<br>2.5 | μs<br>μs        |

| downstream facing port (Figure 3-20)                                                                                      |                  |                                                   |      |              | <i>p</i>        |

| Duration of driving resume to a downstream port (only from a controlling hub)                                             | <b>t</b> drsmdn  |                                                   | 20   |              | ms              |

| Time from detecting downstream resume to rebroadcast                                                                      | tursm            |                                                   |      | 1.0          | ms              |

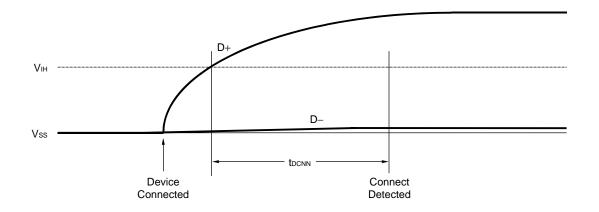

| Duration of driving reset to a downstream facing port ( <b>Figure 3-22</b> )                                              | <b>t</b> drst    | Only for a SetPortFeature<br>(PORT_RESET) request | 10   | 20           | ms              |

| Time to detect a long K from upstream                                                                                     | <b>t</b> urlk    |                                                   | 2.5  | 100          | μs              |

| Time to detect a long SE0 from upstream                                                                                   |                  |                                                   | 2.5  | 10000        | μs              |

| Duration of repeating SE0 upstream (for<br>Low-/Full-speed repeater)                                                      | turpse0          |                                                   |      | 23           | FS Bit<br>times |

| Inter-packet delay (for High-speed) of<br>packets traveling in same direction                                             | <b>t</b> HSIPDSD |                                                   | 88   |              | Bit<br>times    |

| Inter-packet delay (for High-speed) of<br>packets traveling in opposite direction                                         | <b>t</b> hsipdod |                                                   | 8    |              | Bit<br>times    |

| Inter-packet delay for device/root hub<br>response with detachable cable for High-<br>speed                               | thsrspipd1       |                                                   |      | 192          | Bit<br>times    |

| Time of which a Chirp J or Chirp K must be<br>continuously detected (filtered) by hub or<br>device during Reset handshake | tri∟⊤            |                                                   | 2.5  |              | μs              |

| Time after end of device Chirp K by which<br>hub must start driving first Chirp K in the<br>hub's chirp sequence          | twтосн           |                                                   |      | 100          | μs              |

| Time for which each individual Chirp J or<br>Chirp K in the chirp sequence is driven<br>downstream by hub during reset    | tоснвіт          |                                                   | 40   | 60           | μs              |

| Time before end of reset by which a hub<br>must end its downstream chirp sequence                                         | tdchse0          |                                                   | 100  | 500          | μs              |

| Time from internal power good to device<br>pulling D+ beyond V⊮z ( <b>Figure 3-22</b> )                                   | tsigatt          |                                                   |      | 100          | ms              |

| Debounce interval provided by USB system software after attach ( <b>Figure 3-22</b> )                                     | <b>t</b> attdb   |                                                   |      | 100          | ms              |

| Maximum duration of suspend averaging interval                                                                            | tsusavgi         |                                                   |      | 1            | S               |

| Period of idle bus before device can initiate resume                                                                      | twtrsm           |                                                   | 5    |              | ms              |

| Duration of driving require unstream                                                                                      |                  |                                                   | 4    | 15           |                 |

Table 3-21. USB Interface (3 of 4)

Duration of driving resume upstream

**t**DRSMUP

ms

15

1

| Parameter                                                                                                                                                                                                      | Symbol             | Conditions               | Min.   | Max.  | Unit         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|--------|-------|--------------|