## 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

#### **General Description**

The MAX11068 is a programmable, highly integrated, high-voltage, 12-channel, battery-monitoring smart data-acquisition interface. It is optimized for use with batteries used in automotive systems, hybrid electric battery packs, electric cars, and any system that stacks long series strings of secondary metal batteries. This highly integrated battery sensor incorporates a simple state machine and a high-speed I²C bus for SMBus™-laddered serial communication.

The MAX11068 analog front-end combines a 12-channel voltage measurement data-acquisition system with a highvoltage switch bank input. All measurements are done differentially across each cell. The full-scale measurement range is from 0 to 5.0V, with full stated accuracy guaranteed from 0.5V to 4.7V. The input mux/switch bank allows for differential measurement of each cell in a series stack. A high-speed, 12-bit successive approximation (SAR) A/D converter is used to digitize the cell voltages. All 12 cells can be measured in less than 107µs. The MAX11068 uses a two-scan approach for collecting cell measurements and correcting them for errors. The first phase of the scan is the acquisition phase where the voltages of all 12 cells are acquired. The second phase is the error-cancellation phase where the ADC input is chopped to remove errors. This two-phase approach yields excellent accuracy over temperature and in the face of extreme noise in the system. The MAX11068 incorporates an internal oscillator that generates a 6.0MHz system clock with ±3.0% accuracy.

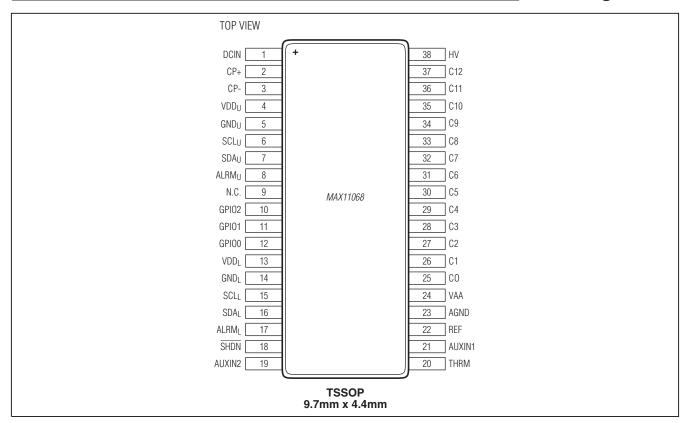

The MAX11068 consumes less than 2.0mA from the power supply while in data-acquisition modes. This current is reduced to  $75\mu\text{A}$  in standby mode and less than  $1\mu\text{A}$  in shutdown mode. The device is packaged in a 38-pin, 9.7mm x 4.4mm x 1.0mm TSSOP package that is lead free and RoHS compliant and is designed to operate over the AEC-Q100 Grade 2, -40°C to +105°C temperature range.

#### \_Applications

High-Voltage, Multicell Series-Stacked-Battery Systems

Electric and Hybrid Electric Vehicle (HEV) Battery Packs

Electric Bikes

High-Power Battery Backup Systems

SuperCap Backup Systems

**Power Tools**

SMBus is a trademark of Intel Corp.

#### Features

- ♦ 12-Cell Battery Voltage Measurement with Temperature Monitoring

- Up to 12 Lithium-Ion (Li+), NiMH, or Super-Cap Cells

- Two Auxiliary Analog Inputs for Temperature Measurement

- ♦ High-Accuracy I/Os

- Excellent ±0.25% Voltage-Measurement Accuracy

- ≤ 5mV Offset Voltage

- ♦ Integrated 12-Channel Data-Acquisition System

12-Channel High-Voltage Mux to ADC

Differential Cell-Voltage Measurement

12-Bit Precision, High-Speed SAR ADC

12 Cell Voltages Measured Within 107µs

- **♦** Battery-Fault Detection

- Overvoltage and Undervoltage Digital Threshold Detection

- Cell Sense Line Open-Circuit Detection High/Low Temperature Digital Threshold Detection

- ♦ 12 Integrated Cell-Equalization Switches Support Up to 200mA

- ♦ Integrated 6V to 70V Input Linear Regulator

- ♦ Integrated 25ppm/°C, 2.5V Precision Reference

- ♦ Integrated Level-Shifted, I<sup>2</sup>C-Compliant SMBus Ladder Interface

Supports Multiple Devices, Up to 31 SMBus-Ladder-Connected ICs

- Communications Protocol with Autoaddressing Fault-Tolerant Hardware Handshake and Data CRC Checking

- ♦ Three General-Purpose Digital I/O Lines

- Ultra-Low Power Dissipation

Standby Mode Quiescent Current Drain 75μA

Shutdown Mode Leakage Current 1μA

- ♦ Operating Temperature Range from -40°C to +105°C (AEC-Q100 Grade 2)

- ♦ 38-Pin, Lead-Free/RoHS-Compliant TSSOP Package (9.7mm x 4.4mm)

#### **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE |

|----------------|-----------------|-------------|

| MAX11068GUU+   | -40°C to +105°C | 38 TSSOP    |

| MAX11068GUU/V+ | -40°C to +105°C | 38 TSSOP    |

+Denotes a lead(Pb)-free/RoHS-compliant package. /V Denotes an automotive qualified part.

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

#### **ABSOLUTE MAXIMUM RATINGS**

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                     |

|-----------------------------------------|-------------------------------------|

| HV, VDDU, GNDU, DCIN to AGND            | 0.3V to +80V                        |

| HV to C12                               | 0.3V to +6V                         |

| C1-C12 to AGND                          | 0.3V to $(V_{HV} + 0.3V)$           |

| C(N+1) to C(N)                          | 0.3V to +9.0V                       |

| C0 to AGND                              | 0.3V to +4.0V                       |

| SHDN to AGND                            |                                     |

| VAA to AGND                             | 0.3V to +4.0V                       |

| VDDL to GNDL                            |                                     |

| VDDU to GNDU                            | 0.3V to +6.0V                       |

| GNDU to GNDL                            | 0.3V to +80V                        |

| AGND to GNDL                            | 0.3V to +0.3V                       |

| AUXIN1, AUXIN2, THRM to AGND            | 0.3V to +6.0V                       |

| REF to AGND                             | $-0.3V$ to $(VAA + 0.3V)$           |

| SCLL, SDAL, ALRML to GNDL               | 0.3V to (VDD <sub>L</sub> + 0.3V)   |

| SCLU, SDAU, ALRMU to GNDU               | 0.3V to (VDD <sub>U</sub> + 0.3V)   |

| CP+ to AGND(GNDU -                      | -1.0V) to (VDD <sub>U</sub> + 1.0V) |

| CP- to AGND                             | $0.3V \text{ to } (GND_U + 0.3V)$   |

|                                         |                                     |

| GPIO0, GPIO1, GPIO20.3V to (VDD <sub>L</sub> + 0.3V)<br>ESD Rating (HBM, Note 1)±2kV              |

|---------------------------------------------------------------------------------------------------|

| C0-C12, AUXIN1, AUXIN2, REF, VAA, VDDIJ, GNDIJ.                                                   |

| VDDL, GNDL, DCIN, SHDN, CP+, CP-, HV, SCLU, SDAU,                                                 |

| ALRM <sub>U</sub> , SCL <sub>L</sub> , SDA <sub>L</sub> , ALRM <sub>L</sub> , GPIO0, GPIO1, GPIO2 |

| Maximum Continuous Current into Any Pin20mA                                                       |

| ESD Diode Maximum Average                                                                         |

| Power Dissipation for Hot Plug (Note 2)14.4/ $\sqrt{\tau}$ W                                      |

| Continuous Power: Multilayer Board1269.8mW                                                        |

| Continuous Power: Single-Layer Board                                                              |

| (derating 15.9mW/°C above +70°C)1095.9mW                                                          |

| Operating Temperature Range40°C to +105°C                                                         |

| Storage Temperature Range55°C to +150°C                                                           |

| Junction Temperature (continuous)+150°C                                                           |

| Lead Temperature (soldering, 10s)+300°C                                                           |

| Soldering Temperature (reflow)+260°C                                                              |

|                                                                                                   |

Note 1: Human Body Model to Specification MIL-STD-883 Method 3015.7.

Note 2: Maximum average power dissipation for time period τ. Peak current must never exceed 2A. τ is one time constant (in μs) of hot-plug current waveform through a given diode. For example, if τ is 330μs, the maximum average diode power dissipation is 0.793W. Actual average power dissipation must be calculated from current waveform for the application circuit.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } V_{GNDU} = V_{DCIN} = 18V \text{ to } +60V, \text{ typical values are at } T_A = +25^{\circ}C, \text{ unless otherwise specified from } -40^{\circ}C \text{ to } +105^{\circ}C \text{ per the application circuit in Figure 4.})$

| PARAMETER                                        | SYMBOL         | CONDITIONS                                                        | MIN   | TYP   | MAX   | UNITS   |

|--------------------------------------------------|----------------|-------------------------------------------------------------------|-------|-------|-------|---------|

| C0-C12 INPUTS                                    |                |                                                                   |       |       |       |         |

| Differential Cell Input-Voltage<br>Range         | VCELLXIN       | Any 2 inputs<br>CN+1 to CN for C12–C0 (Note 2)                    |       |       | 4.7   | V       |

|                                                  |                | Input C1 referred to AGND                                         | 0.7   |       | 7.0   |         |

| Cell Input Common-Mode Voltage<br>Range (Note 5) | VCXIN          | Inputs C2 through C[TOP] referred to AGND                         | 0.7   |       |       | V       |

| hange (Note 3)                                   |                | C[TOP] referred to AGND                                           |       | GNDu  |       |         |

|                                                  |                | C0 referred to AGND                                               | -0.05 |       | +0.05 |         |

| Input Lookago Current                            | la             | ADC off; $C(N)$ to $C(N+1) = 5V$                                  | -1.0  |       | +1.0  | μA      |

| Input-Leakage Current                            | ICXIN          | ADC ON; $C(N)$ to $C(N+1) = 3V$                                   |       | ±10.0 |       | μΑ      |

| ADC Resolution                                   | <b>ADCBITS</b> | LSB size is +1.22mV                                               | 12    |       |       | Bits    |

| Channel- Conversion Time                         | to.            | Highest enabled input                                             |       | 11.34 |       | μs/     |

| Charmer- Conversion Time                         | ts             | Enabled inputs except highest                                     |       | 7.66  |       | Channel |

|                                                  |                | TA = +25°C (Note 4); VCELL = 3.0V                                 | -5    |       | +5    |         |

| Channel Aggurgay                                 |                | -10°C < T <sub>A</sub> < +50°C; V <sub>CELL</sub> = 3.0V (Note 3) | -10   |       | +10   | mV      |

| Channel Accuracy                                 |                | -40°C < TA < +85°C; VCELL = 3.0V<br>(Note 3)                      | -15   |       | +15   | 1110    |

|                                                  |                | -40°C < T <sub>A</sub> < +105°C; V <sub>CELL</sub> = 3.0V         | -20   |       | +20   |         |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } V_{GNDU} = V_{DCIN} = 18V \text{ to } +60V, \text{ typical values are at } T_A = +25^{\circ}C, \text{ unless otherwise specified from } -40^{\circ}C \text{ to } +105^{\circ}C \text{ per the application circuit in Figure 4.})$

| PARAMETER                          | SYMBOL                      | CONDITIONS                               | MIN           | TYP   | MAX   | UNITS                |

|------------------------------------|-----------------------------|------------------------------------------|---------------|-------|-------|----------------------|

| Differential Nonlinearity          | DNL                         | No missing codes at 12 bits              |               | ±1.0  |       | LSB                  |

| Channel Offset Error               | CELLVOS                     | Cells 1 through 12                       | -5            |       | +5    | mV                   |

| Channel Gain Error                 | CELLAV                      | Cells 1 through 12                       | -1.0          |       | +1.0  | %                    |

| Cell-Balancing Switch Resistance   |                             | RSWITCH from C(N) to C(N+1) when enabled |               | 6     | 20    | Ω                    |

| AUXIN1, AUXIN2 INPUTS              |                             |                                          |               |       |       |                      |

| Absolute Differential Input Range  | VAUXINXIN                   | AUXIN1, AUXIN2 to AGND; ADC REF = THRM   | 0             |       | VTHRM | V                    |

| Common-Mode Input-Voltage<br>Range |                             | Inputs AUXIN1/2 referred to AGND         | 0             |       | VTHRM | V                    |

| Input-Leakage Current              | lauxin                      | ADC off; input voltage = 3.3V            | -1.0          |       | +1.0  | μΑ                   |

| ADC Resolution                     |                             |                                          | 12            |       |       | Bits                 |

| Conversion Time                    | ts                          |                                          |               | 10    |       | μs/<br>AUX_<br>Input |

| A · · · · - · · ·                  |                             | $T_A = +25^{\circ}C$                     | -0.5          |       | +0.5  | 0/                   |

| Accuracy                           |                             | -40°C < T <sub>A</sub> < +105°C          | -1.0          |       | +1.0  | %                    |

| Differential Nonlinearity          | DNL                         | No missing codes at 12 bits              |               | ±1.0  |       | LSB                  |

| Offset Error                       | AUXVos                      | AUXIN1, AUXIN2                           | -8            |       | +8    | mV                   |

| Gain Error AUXAv                   |                             | AUXIN1, AUXIN2                           | -1.0          |       | +1.0  | %                    |

| THRM Switch Resistance             | RTHRM                       | THRM to VAA (Note 3)                     | 5             | 18    | 28    | Ω                    |

| VOLTAGE REFERENCE                  |                             |                                          |               |       |       |                      |

| Output REF Voltage                 | REFVout                     | $T_A = +25^{\circ}C$                     | 2.45          | 2.50  | 2.55  | V                    |

| REF Output Short-Circuit Current   | I <sub>REF-SC</sub>         |                                          |               | ±12.5 |       | mA                   |

| Temperature Coefficient            | ΔREF/<br>ΔTEMP              |                                          |               | ±25   |       | ppm/°C               |

| Initial Drift                      | Change after 1000hr burn-in |                                          |               | 120   |       | ppm                  |

| LOGIC INPUTS AND OUTPUTS (         | GPIO AND SHD                | N)                                       |               |       |       |                      |

| SHDN Voltage High                  |                             |                                          | 1.8           |       |       | V                    |

| SHDN Voltage Low                   |                             |                                          |               |       | 0.5   | V                    |

|                                    |                             | VSHDN = 3.4V                             |               |       | 1     |                      |

| SHDN Input Leakage Current         |                             | VSHDN = 30V                              |               | 5.15  | 18    | μΑ                   |

|                                    |                             | VSHDN = 56V                              |               | 12.6  | 45    |                      |

| GPIO Input Voltage Low             |                             |                                          |               |       | 0.8   | V                    |

| GPIO Input Voltage High            |                             |                                          | 2.4           |       |       | V                    |

| I/O Leakage Current                |                             | I/O pins programmed to high impedance    | -1            | +2    | +6.2  | μΑ                   |

| GPIO Output Voltage Low            |                             | ISINK = 3mA                              |               |       | 0.4   | V                    |

| GPIO Output Voltage High           |                             | ISOURCE = 3mA                            | VDDL -<br>0.5 |       |       | V                    |

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } V_{GNDU} = V_{DCIN} = 18V \text{ to } +60V, \text{ typical values are at } T_A = +25^{\circ}C, \text{ unless otherwise specified from } -40^{\circ}C \text{ to } +105^{\circ}C \text{ per the application circuit in Figure 4.})$

| PARAMETER                                                         | SYMBOL                      | CONDITIONS                                                                  | MIN            | TYP            | MAX            | UNITS            |

|-------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------|----------------|----------------|----------------|------------------|

| LINEAR REGULATOR +3.4V (VA                                        | A)                          |                                                                             |                |                |                |                  |

| Input Voltage Range                                               | VDCIN                       | 0 < I <sub>LOAD</sub> < 8mA                                                 | 6.0            |                | 70             | V                |

| Output Voltage                                                    | VVAA                        | 0 < I <sub>LOAD</sub> < 8mA;<br>6V < V <sub>DCIN</sub> < 70V                |                | 3.4            | 3.55           | V                |

| Short-Circuit Current                                             |                             | VAA = 0V, 6V < VDCIN < 30V                                                  |                |                | 60             | mA               |

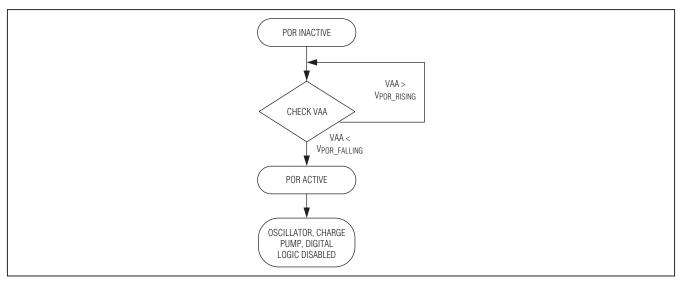

|                                                                   |                             | Falling VAA                                                                 | 2.85           | 2.95           | 3.05           | V                |

| Power-On Reset Threshold (Note 3)                                 |                             | Rising VAA                                                                  | 2.9            | 3.0            | 3.1            | V                |

| (Note 3)                                                          |                             | POR threshold hysteresis                                                    | 0.01           | 40             | 80             | mV               |

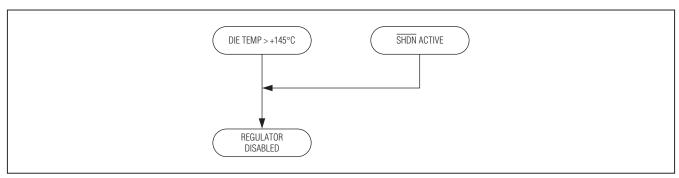

| Thermal Shutdown                                                  |                             | Rising temperature                                                          |                | +145           |                | °C               |

| Thermal-Shutdown Hysteresis                                       |                             |                                                                             |                | 15             |                | °C               |

| CHARGE PUMP +3.4V                                                 |                             |                                                                             |                |                |                |                  |

| Output Voltage                                                    | Vvddu - Vgndu               | ILOAD = 0 at 0.1µF CP+ to CP-                                               | 3.2            | 3.4            | 3.55           | V                |

| Output Voltage                                                    | VVDDU - VGNDU               | 1mA = ILOAD at 0.1µF CP+ to CP-                                             | 3.2            | 2.5            | 3.55           | V                |

| Charge-Pump Efficiency                                            |                             | IVDDU/IGNDU - IVDDU at 2.7V,<br>VDDU - GNDU                                 | 60             | 89             | 99             | %                |

| Charge-Pump Undervoltage<br>Threshold                             | VCPUV                       |                                                                             | 2.0            | 2.7            | 3.2            | V                |

| INTERNAL OSCILLATORS (32.76                                       | 88kHz, 6.0MHz)              |                                                                             | 1              |                |                |                  |

| Internal 32.768kHz Oscillator<br>Frequency                        | fwD-OSC                     |                                                                             | 32.113         | 32.768         | 33.423         | kHz              |

| Internal 6.0MHz Oscillator<br>Frequency                           | fHF-OSC                     |                                                                             | 5.82           | 6.0            | 6.18           | MHz              |

| I <sup>2</sup> C LOWER PORT SCL <sub>L</sub> , SDA <sub>L</sub> , | ALRM <sub>L</sub> (Relative | to GND <sub>L</sub> , VDD <sub>L</sub> = Nominal 3.4V)                      |                |                |                |                  |

| SDAL, SCLL Input Voltage Low                                      |                             |                                                                             |                |                | 0.3 x<br>VVDDL | V                |

| SDAL, SCLL Input Voltage High                                     |                             |                                                                             | 0.7 x<br>VVDDL |                |                | V                |

| SDA <sub>L</sub> , SCL <sub>L</sub> Input Hysteresis              |                             |                                                                             | 0.2            | 0.1 x<br>VVDDL | 0.5            | V                |

| SDAL, ALRML Output Voltage Low                                    |                             | At sink = 3mA                                                               |                |                | 0.4            | V                |

| SDA <sub>L</sub> , SCL <sub>L</sub> Leakage Current               |                             | VSDAL = VSCLL = 1.5V                                                        |                |                | 1.0            | μΑ               |

|                                                                   | RACTIVE_EDGE                | Active edge                                                                 | 0.5            | 1              | 3              | l <sub>1</sub> O |

| CDA, Managed Desistance                                           |                             | Managed passive state                                                       | 35             | 50             | 75             | kΩ               |

| SDAL, Managed Resistance                                          |                             | Off passive state                                                           |                | 1              |                | ΜΩ               |

|                                                                   | tone_shot                   | tone_shot (active edge pulse)                                               | 150            | 250            | 380            | ns               |

| SDA <sub>L</sub> 1-TAU Capacitance                                | C <sub>1_TAU</sub>          | SDAL rises to 70% within active edge time when loaded with this capacitance | 120            | 280            | 550            | рF               |

| ALRM <sub>L</sub> Output High Voltage                             |                             | At source = 3mA                                                             | VDDL -<br>0.4  |                |                | V                |

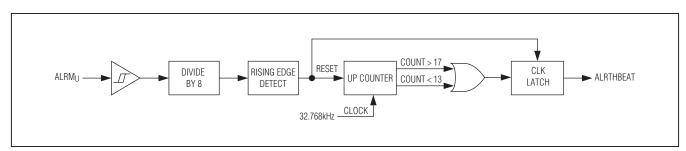

| ALRM <sub>L</sub> Heartbeat Frequency                             |                             | OSC = 32.768kHz ±2.0%                                                       | 16,000         | 16,384         | 16,711         | kHz              |

| Lower Port Input Capacitance                                      |                             | SCLL, SDAL, ALRML                                                           |                | 15             |                | pF               |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } V_{GNDU} = V_{DCIN} = 18V \text{ to } +60V, \text{ typical values are at } T_A = +25^{\circ}C, \text{ unless otherwise specified from } -40^{\circ}C \text{ to } +105^{\circ}C \text{ per the application circuit in Figure 4.})$

| PARAMETER                                                           | SYMBOL           | CONDITIONS                                                                                                                              |                            | TYP                        | MAX                        | UNITS     |  |

|---------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-----------|--|

| I <sup>2</sup> C UPPER PORT SCL <sub>U</sub> , SDA <sub>U</sub> , A | LRMu (Relative   | to GND <sub>U</sub> , VDD <sub>U</sub> )                                                                                                |                            |                            |                            |           |  |

| SDAU, ALRMU Input Voltage Low                                       |                  |                                                                                                                                         |                            |                            | 0.3 x<br>V <sub>VDDU</sub> | V         |  |

| SDAU, ALRMU Input Voltage High                                      |                  |                                                                                                                                         | 0.7 x<br>V <sub>VDDU</sub> |                            |                            | V         |  |

| SDA <sub>U</sub> , ALRM <sub>U</sub> Input Hysteresis               |                  |                                                                                                                                         | 0.05                       | 0.1 x<br>V <sub>VDDU</sub> | 0.4                        | V         |  |

| SDAU, SCLU Output Voltage Low                                       |                  | At sink = 3mA                                                                                                                           |                            |                            | 0.4                        | V         |  |

| SDAU, SCLU Leakage Current                                          |                  | VSDAU = VSCLU = 1.5V                                                                                                                    | -1                         | ±1.0                       | +1                         | μΑ        |  |

|                                                                     |                  | Active edge                                                                                                                             | 0.5                        | 1                          | 3                          | kΩ        |  |

| SDALL Managed Posistance                                            |                  | Managed passive state                                                                                                                   | 30                         | 50                         | 75                         | kΩ        |  |

| SDA <sub>U</sub> , Managed Resistance                               |                  | Off passive state                                                                                                                       |                            | 1                          |                            | $M\Omega$ |  |

|                                                                     | tone_shot        | tone_shot (active edge pulse)                                                                                                           | 150                        | 250                        | 480                        | ns        |  |

| SDA <sub>U</sub> 1-TAU Capacitance                                  |                  | SDA <sub>U</sub> rises to 70% within active edge time when loaded with this capacitance, i.e., choose 100pF to guarantee 3τ rising edge | 120                        | 280                        | 550                        | рF        |  |

| ALDM OL O                                                           |                  | VALRMU = VDDU + 0.15V                                                                                                                   |                            |                            | 1                          | ^         |  |

| ALRMU Clamp Current                                                 |                  | VALRMU = GNDU - 0.15V                                                                                                                   |                            |                            | 1                          | μΑ        |  |

| ALDM: Classes Voltage                                               |                  | 250μA current pulling below GNDU                                                                                                        | GNDU<br>-0.49              |                            |                            | V         |  |

| ALRM∪ Clamp Voltage                                                 |                  | 250μA current pulling above VDDU                                                                                                        |                            |                            | VDDU +<br>0.49             | V         |  |

| Upper Port Input Capacitance                                        |                  | SCL <sub>U</sub> , SDA <sub>U</sub> , ALRM <sub>U</sub>                                                                                 |                            | 8                          |                            | рF        |  |

| Port-to-Port Level Delay                                            |                  |                                                                                                                                         |                            |                            | 1                          | μs        |  |

| Interface Startup                                                   |                  | From SHDN or from POR                                                                                                                   |                            | 3                          |                            | ms        |  |

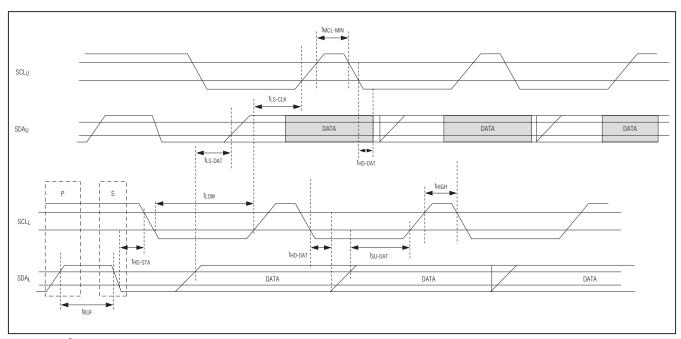

| I <sup>2</sup> C TIMING CHARACTERISTICS                             |                  |                                                                                                                                         |                            |                            |                            |           |  |

| I <sup>2</sup> C Clock Frequency                                    | f <sub>I2C</sub> |                                                                                                                                         | 10                         |                            | 200                        | kHz       |  |

| Bus Timeout Period                                                  | ttimeout         | Timeout for maximum clock low/high time                                                                                                 |                            | 27.4                       |                            | ms        |  |

| Bus Free Time                                                       | tBUF             | Master to slave delay from a STOP to the next START command                                                                             | 500                        |                            |                            | μs        |  |

| Bus Hold Time                                                       | tHD-STA          | Master hold time after a START command                                                                                                  | 350                        |                            |                            | μs        |  |

| Bus START Command Setup Time                                        | tsu-sta          | Repeated START setup time                                                                                                               | 1                          |                            |                            | μs        |  |

| Bus STOP Command Setup Time                                         | tsu-stop         | STOP condition setup time                                                                                                               | 100                        |                            |                            | ns        |  |

|                                                                     | SLAVE PORT       | Transmit                                                                                                                                | 500                        |                            |                            |           |  |

| SDA Data Hold Time                                                  | thd-dat          | Receive                                                                                                                                 | -30                        |                            |                            | ns        |  |

| DA Data Floid TITLE                                                 | MASTER PORT      | Transmit                                                                                                                                | 400                        |                            |                            | 115       |  |

|                                                                     | thd-dat          | Receive (Note 7)                                                                                                                        | 400                        |                            |                            |           |  |

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } V_{GNDU} = V_{DCIN} = 18V \text{ to } +60V, \text{ typical values are at } T_A = +25^{\circ}C \text{ otherwise specified from } -40^{\circ}C \text{ to } +105^{\circ}C \text{ per the application circuit in Figure 4.})$

| PARAMETER                                                                      | SYMBOL CONDITIONS                   |                                                                               | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------|------|------|------|-------|

|                                                                                | SLAVE PORT                          | Transmit (Note 7)                                                             | 250  |      |      |       |

| SDA Data Setup Time                                                            | tsu-dat                             | Receive                                                                       | 250  |      |      | ns    |

| John Data Setup Time                                                           | MASTER PORT                         | Transmit (Note 7)                                                             | 250  |      |      | 115   |

|                                                                                | tsu-dat                             | Receive                                                                       | 1000 |      |      |       |

| SCL <sub>L</sub> Low Time                                                      | tLOW                                |                                                                               | 1.25 |      |      | μs    |

| SCL <sub>L</sub> High Time                                                     | tHIGH                               |                                                                               | 1.25 |      |      | μs    |

| Remastered Clock Minimum High Time                                             | tMCL-MIN                            |                                                                               | 1    |      |      | us    |

| LEVEL-SHIFT TIMING                                                             |                                     |                                                                               |      |      |      |       |

| Level Shift Delay (SDAL to SDAU or SDAU to SDAL)                               | tLS-DAT                             | Rising or falling edge at 1.5V threshold; pin-to-pin delay with 100pF loading | 400  |      | 1100 | ns    |

| Level Shift Delay (SCLL to SCLU)                                               | tLS-CLK                             | Rising or falling edge at 1.5V threshold; pin-to-pin delay with 100pF loading | 600  |      | 800  | ns    |

| POWER-SUPPLY REQUIREMENT                                                       | TS DCIN                             |                                                                               |      |      |      |       |

|                                                                                | IDCIN<br>Acquisition<br>Mode        | High-voltage mux enabled, ADC converting 12 channels; VDCIN = 30V             |      | 3.0  | 6    | mA    |

|                                                                                | I <sub>HV</sub> Acquisition<br>Mode |                                                                               |      | 4.1  | 9.6  |       |

| Current Consumption                                                            | IDCIN<br>Cell-Balancing<br>Mode     | Cell balancing enabled for four switches, LDO, REF, and OSC running; VDCIN =  |      | 70   |      |       |

| ( <b>Note:</b> IDDQ testing is done in production test with a coverage of 71%) | IGNDU<br>Cell-Balancing<br>Mode     | VGNDU = 6V                                                                    |      | 63   |      |       |

|                                                                                | IDCIN<br>Standy Mode                | No conversions or cell balancing; LDO,                                        |      | 55   | 150  | μΑ    |

|                                                                                | IGNDU<br>Standby Mode               | REF, and OSC running, SHDN = 1                                                |      | 20   | 130  |       |

|                                                                                | I <sub>DCIN</sub><br>Shutdown Mode  | SHDN = 0                                                                      |      | 0.25 | 2    |       |

|                                                                                | IGNDU<br>Shutdown Mode              |                                                                               |      | 0.3  | 2    |       |

Note 3: Guaranteed by design and not production tested.

Note 4: Differential input voltage range for which channel gain and offset error applies.

Note 5: Common-mode level at each pin required for specified operation of the high-voltage mux.

Note 6: Offset and gain error are calibrated at +25°C and 3.0V per cell at the factory, assuming that VCXIN is met.

Note 7: This is a derived specification. No characterization required. These specifications involve the clock low time and clock high time used.

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

#### **Pin Configuration**

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                       |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

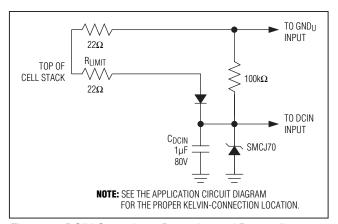

| 1   | DCIN | DC Power-Supply Input. DCIN supplies the internal 3.4V regulator, which provides low-voltage power to the device. Bypass DCIN to GND with a 1µF capacitor.                                                                                                                     |

| 2   | CP+  | Charge-Pump Capacitor Plus Input for the Internal Charge Pump. Connect a 0.1µF high-voltage capacitor between CP+ and CP                                                                                                                                                       |

| 3   | CP-  | Charge-Pump Capacitor Minus Input for the Internal Charge Pump. Connect a 0.1µF high-voltage capacitor between CP+ and CP                                                                                                                                                      |

| 4   | VDDu | Level-Shifted Upper I <sup>2</sup> C Port Digital Supply for Use in Communicating with an Upper, Neighboring Battery Module. This is a regulated output voltage from the internal charge pump that is level shifted above the DCIN pin voltage level.                          |

| 5   | GNDu | Level-Shifted Upper I <sup>2</sup> C Port Ground. This pin is the reference level and ground return for VDD <sub>U</sub> and also the supply input for the charge pump. It should be tied to the DCIN takeoff point on the battery stack as shown in the application diagrams. |

| 6   | SCLU | Level-Shifted Upper Port I <sup>2</sup> C Clock Line. SCL <sub>U</sub> is the I <sup>2</sup> C clock line communicating with the upper neighboring battery module. This pin swings between VDD <sub>U</sub> and GND <sub>U</sub> .                                             |

| 7   | SDAU | Level-Shifted Upper Port I <sup>2</sup> C Bidirectional Serial Data Line. SDA <sub>U</sub> is the I <sup>2</sup> C data line communicating with the upper neighboring battery module. This pin swings between VDD <sub>U</sub> and GND <sub>U</sub> .                          |

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

## Pin Description (continued)

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

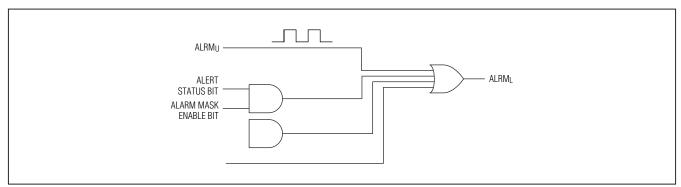

| 8   | ALRMu  | Upper Port Alarm Input. Overvoltage, undervoltage, over/undertemperature, cell mismatch, and communication fault. The alarm signal is laddered. This signal is referenced to VDDU and GNDU. Connect this signal to VDDU through a pullup resistor.                                                                                                                                                                                                                                                                                                                      |

| 9   | N.C.   | Not Internally Connected/Test I/O. Leave open; do not connect any external circuit to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10  | GPIO2  | General-Purpose I/O 2. This pin swings between VDDL and GNDL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11  | GPIO1  | General-Purpose I/O 1. This pin swings between VDDL and GNDL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12  | GPI00  | General-Purpose I/O 0. This pin swings between VDDL and GNDL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 13  | VDDL   | Lower Port I <sup>2</sup> C + 3.4V Digital Supply Input. Connect to VAA and decouple to GND <sub>L</sub> with a 0.47µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14  | GNDL   | Lower Port I <sup>2</sup> C Common or Ground. A star ground connection to AGND is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15  | SCLL   | Lower Port I <sup>2</sup> C Clock. SCL <sub>L</sub> is the I <sup>2</sup> C clock line communicating with the lower neighboring battery module. This pin swings between VDD <sub>L</sub> and GND <sub>L</sub> .                                                                                                                                                                                                                                                                                                                                                         |

| 16  | SDAL   | Lower Port I <sup>2</sup> C Data I/O. SDAL is the I <sup>2</sup> C serial data line communicating with the lower neighboring battery module. This pin swings between VDDL and GNDL.                                                                                                                                                                                                                                                                                                                                                                                     |

| 17  | ALRML  | Lower Port Alarm Output. Overvoltage, undervoltage, over/undertemperature, cell mismatch, and communication faults. The alarm signal is laddered and driven from the highest module down to the lowest. The alarm output is nominally a clocked heartbeat signal that provides a 16kHz clock when no alarm is present and is held at logic-high during an alarm. This signal swings between VDDL and GNDL.                                                                                                                                                              |

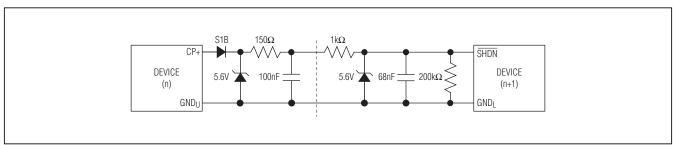

| 18  | SHDN   | Active-Low Shutdown/Input. This pin completely shuts down the MAX11068 internal regulators and oscillators when the pin is less than +0.6V as referenced to AGND. The I <sup>2</sup> C bus is nonresponsive when shutdown is asserted. SHDN for the first pack should be driven by the host controller through the recommended interface circuit. SHDN for laddered modules should be tied to the lower neighboring battery module through the recommended interface circuit. The shutdown pin is 60V tolerant for connection directly to the top of the battery stack. |

| 19  | AUXIN2 | Auxiliary Analog Input 2. A low-voltage analog input pin with a full-scale range of AGND to VAA that can be used for monitoring an external NTC or general-purpose measurements. This channel uses the VAA voltage as the reference voltage for the ADC conversion. When used with the THRM pin and a resistor-divider, ratiometric measurements can be made.                                                                                                                                                                                                           |

| 20  | THRM   | External Thermistor Bias Output. This is a switched connection for supplying a bias voltage from the internal +3.4V regulator (VAA) to an external NTC device for measuring the temperature of the battery module. This pin can supply up to 2mA from the VAA regulator.                                                                                                                                                                                                                                                                                                |

| 21  | AUXIN1 | Auxiliary Analog Input 1. A low-voltage analog input pin with a full-scale range of AGND to VAA that can be used for monitoring an external NTC or general-purpose measurements. This channel uses the VAA voltage as the reference voltage for the ADC conversion. When used with the THRM pin, ratiometric measurements can be made.                                                                                                                                                                                                                                  |

| 22  | REF    | +2.5V Voltage Reference. Bypass REF to AGND with a 1µF capacitor placed close to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 23  | AGND   | Analog Ground. Should be tied to the negative terminal of cell 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 24  | VAA    | +3.4V Analog Supply Output. Connect to VDDL and bypass with a 1.0µF capacitor to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 25  | C0     | Cell 1 Minus Connection. Bypass to AGND with a 1.0µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 26  | C1     | Cell 2 Minus Connection and Cell 1 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27  | C2     | Cell 3 Minus Connection and Cell 2 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28  | C3     | Cell 4 Minus Connection and Cell 3 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 29  | C4     | Cell 5 Minus connection and Cell 4 Plus Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                            |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | C5   | Cell 6 Minus Connection and Cell 5 Plus Connection                                                                                                                                  |

| 31  | C6   | Cell 7 Minus Connection and Cell 6 Plus Connection                                                                                                                                  |

| 32  | C7   | Cell 8 Minus Connection and Cell 7 Plus Connection                                                                                                                                  |

| 33  | C8   | Cell 9 Minus Connection and Cell 8 Plus Connection                                                                                                                                  |

| 34  | C9   | Cell 10 Minus Connection and Cell 9 Plus Connection                                                                                                                                 |

| 35  | C10  | Cell 11 Minus Connection and Cell 10 Plus Connection                                                                                                                                |

| 36  | C11  | Cell 12 Minus Connection and Cell 11 Plus Connection                                                                                                                                |

| 37  | C12  | Cell 12 Plus Connection. Top of battery module stack.                                                                                                                               |

| 38  | HV   | High-Voltage Bias Pin. HV is biased through a diode connection to the charge pump. It is used internally to supply the high-voltage mux. Connect to DCIN through a 3.3µF capacitor. |

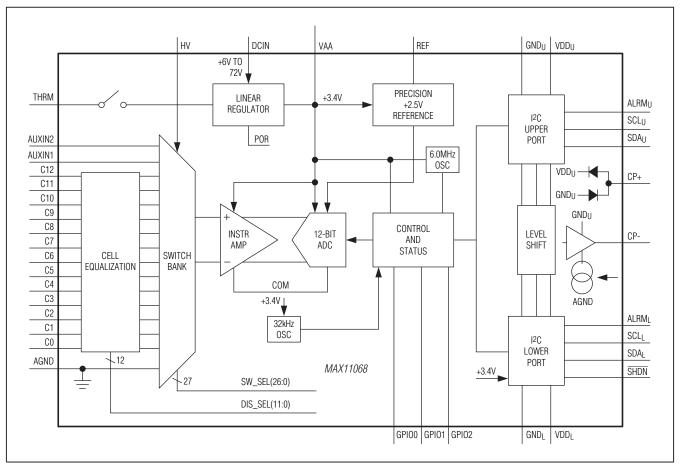

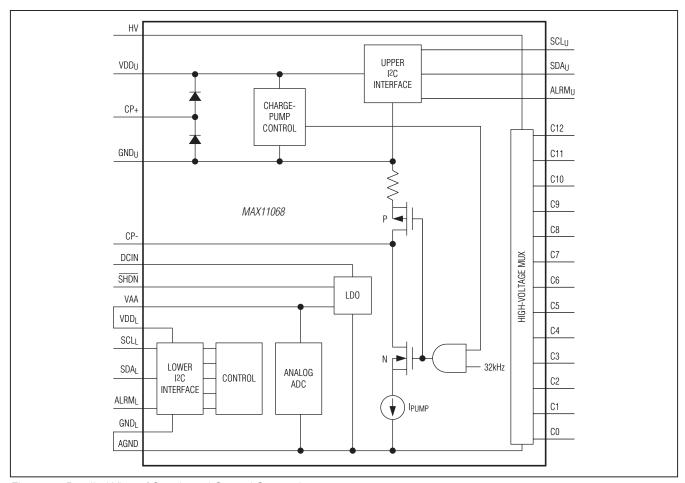

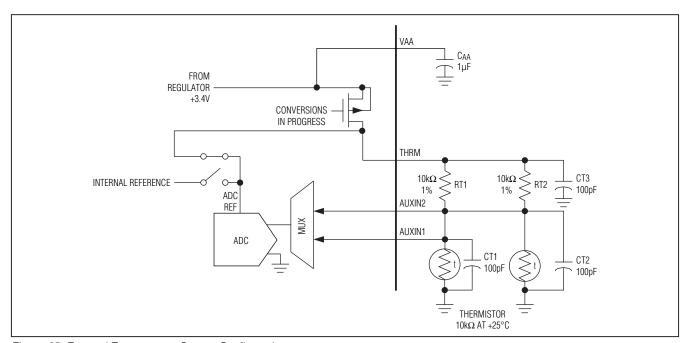

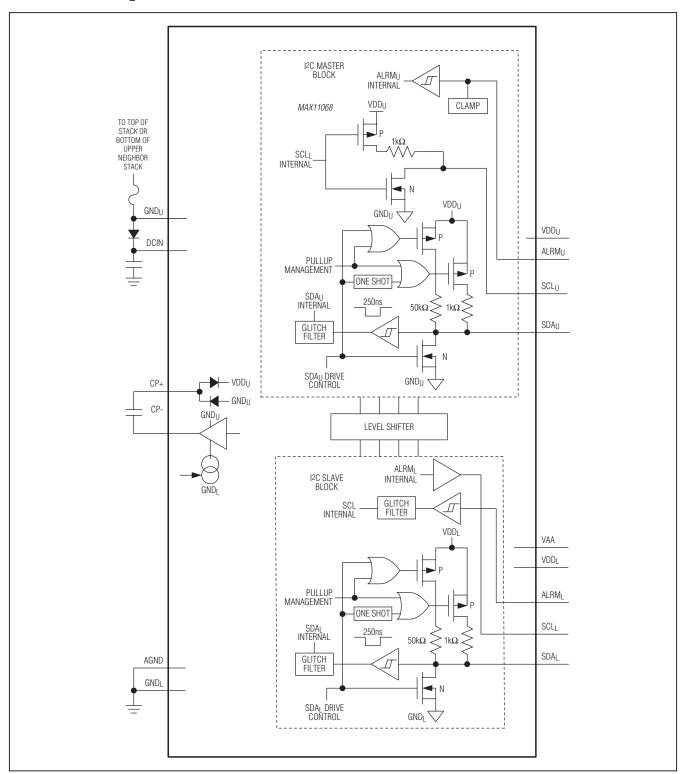

Figure 1. Functional Diagram

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

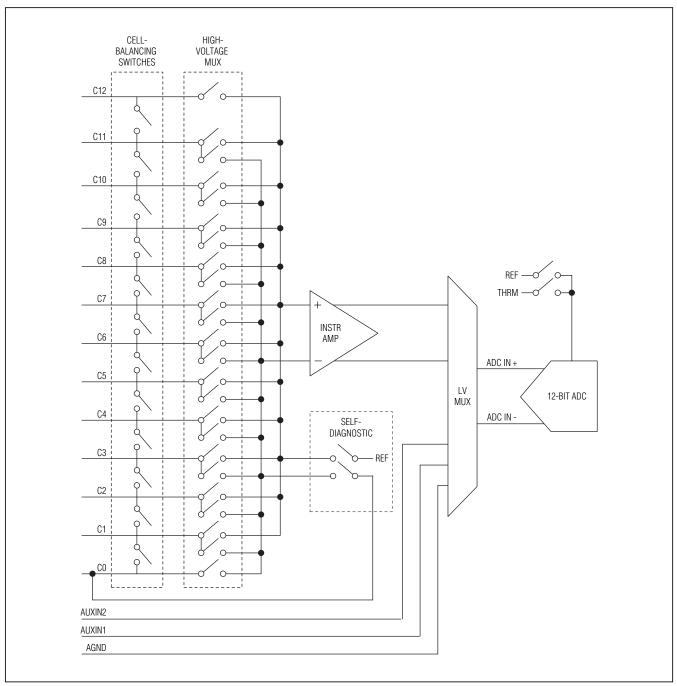

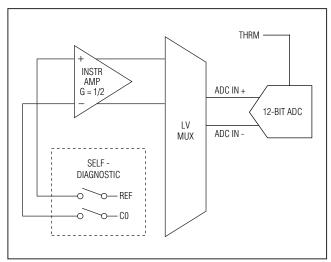

Figure 2. Analog Front-End Block Diagram

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

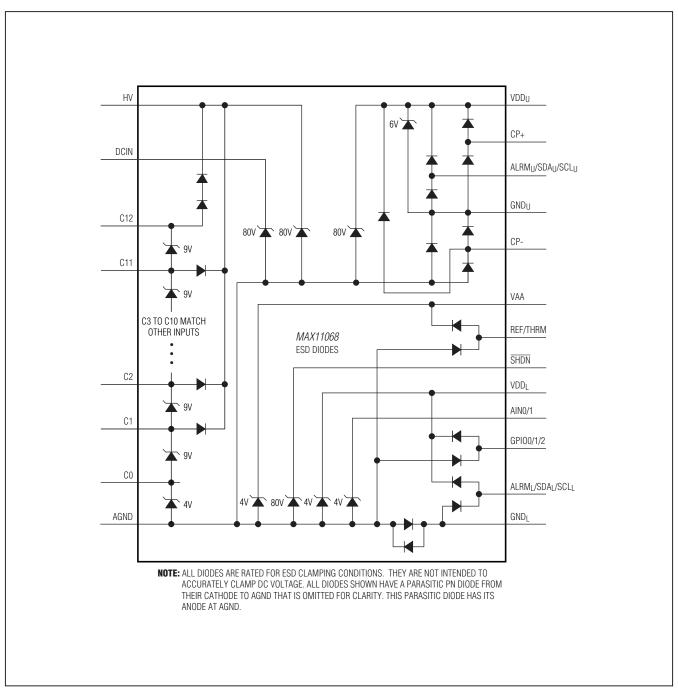

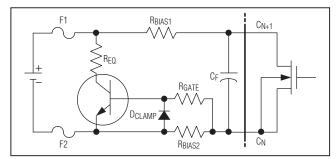

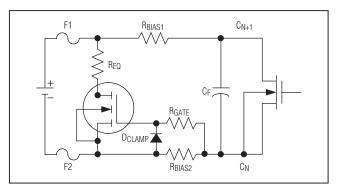

Figure 3. MAX11068 ESD Diode Diagram

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

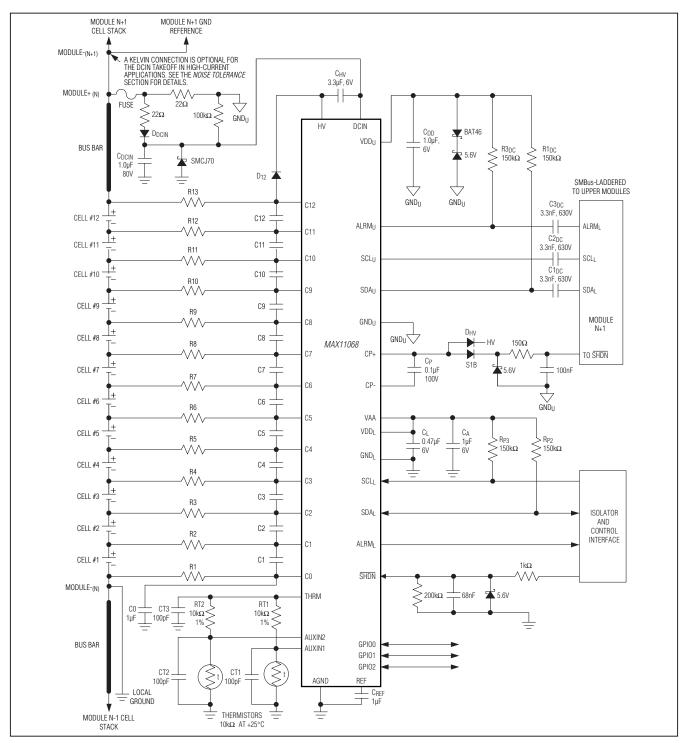

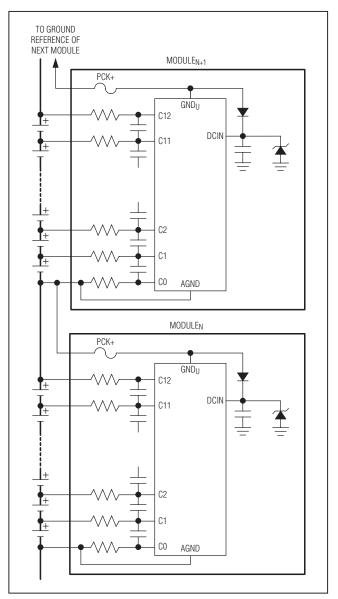

## **Typical Operating Circuit Diagrams**

Figure 4. Operating Circuit Diagram for a 12-Cell System

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

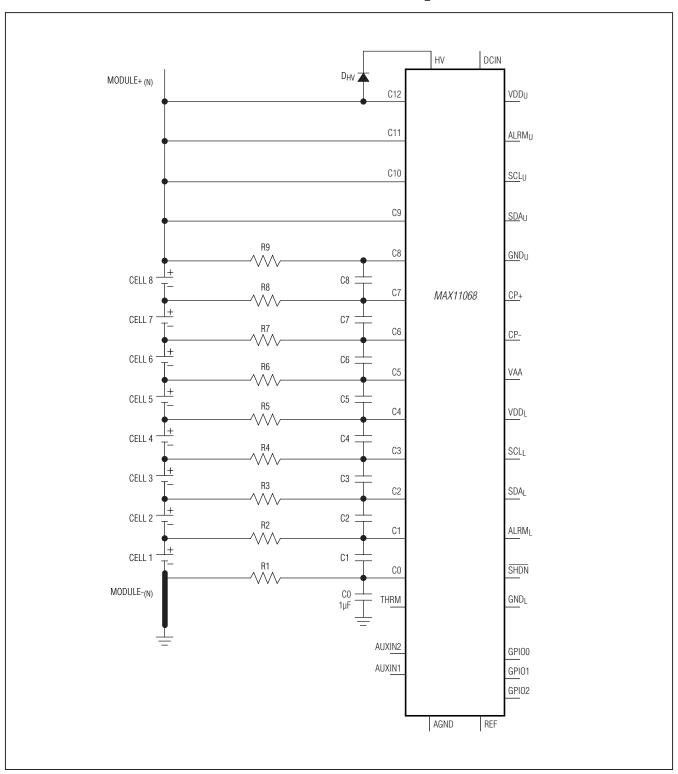

Figure 5. Simplified Operating Circuit Diagram for an 8-Cell System

## 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

#### **Detailed Description**

The MAX11068 has two auxiliary analog inputs that can be used to measure external resistance temperature detector (RTD) components. A negative temperature coefficient (NTC) RTD can be configured with the AUXIN1 or AUXIN2 analog inputs to accurately monitor module or battery-cell temperature. An internal temperature monitor on the die is used to detect thermal overload and disables the MAX11068 cell-balancing switches and linear regulator should the +145°C thermal limit be exceeded.

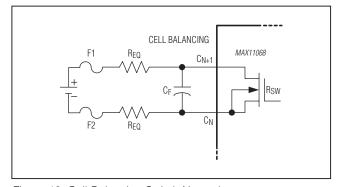

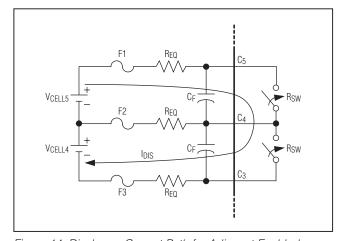

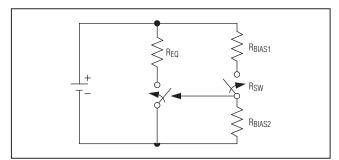

The MAX11068 has 12 built-in cell-balancing/discharge switches that can support up to 200mA cell discharge currents. The MAX11068 package can support up to 1.2W of power dissipation, which limits the number of balancing/discharge switches that can be enabled when using a 200mA set current to three nonconsecutive cells at no more than +75°C ambient temperature. With a 110mA cell set current, all 12 internal cell switches can be enabled at the same time. The balancing switches can also be used to detect an open circuit on any of the cell sense wire connections.

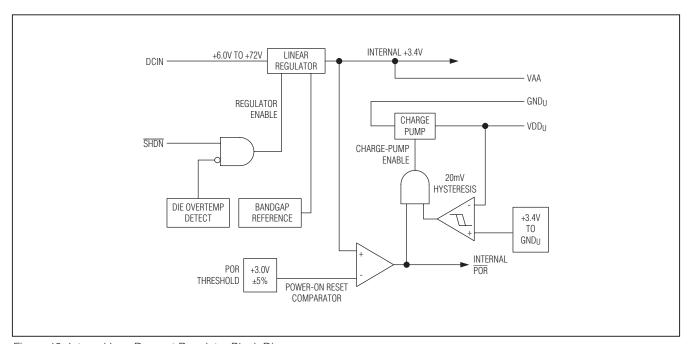

The MAX11068 contains a 25ppm/°C precision bandgap reference and an internal regulator that creates the supply for the analog front end and the interchip, level-shifted, communication bus. The regulator can operate from a 6.0V to 72V supply input. The external shutdown pin can be used to reset the MAX11068.

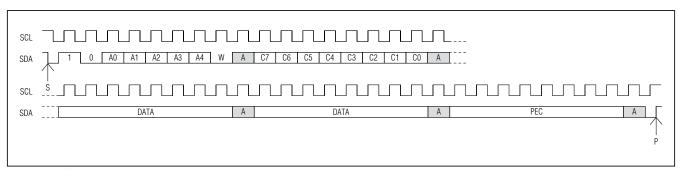

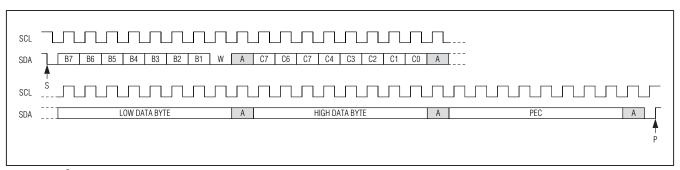

The MAX11068 incorporates an I<sup>2</sup>C physical interface for interchip communication and control. The I<sup>2</sup>C bus system is designed to allow SMBus laddering of up to 31 devices without the need for any interchip isolation.

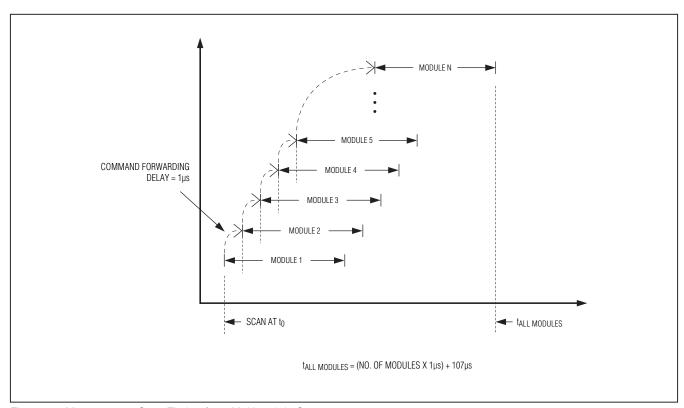

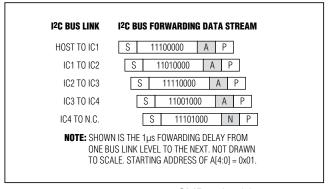

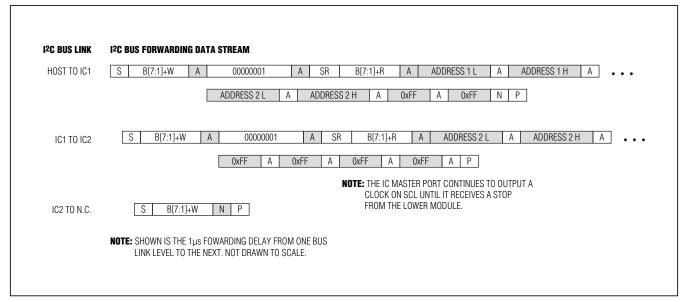

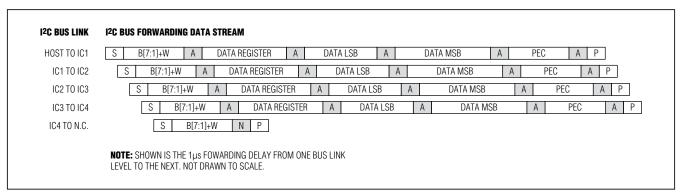

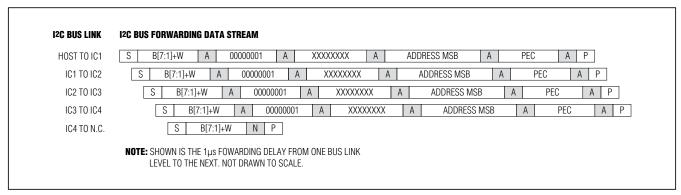

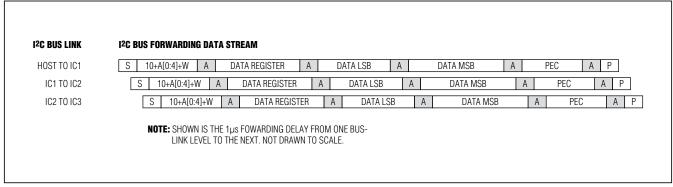

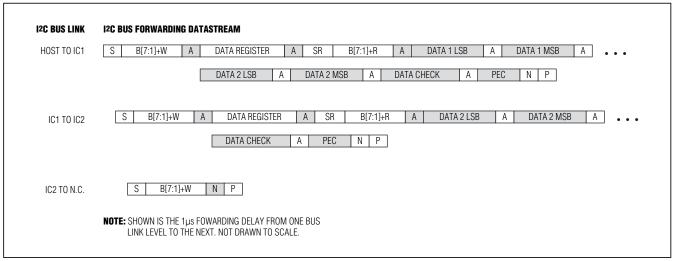

These bidirectional serial buses can withstand large differences in interchip grounds and system noise. The built-in level-shifting and predefined command protocol provide a low-cost, flexible, and reliable communication bus. Command-up forwarding relays communication along the bus from chip to chip for fast response. A 1µs delay is incurred in relaying command messages. bounding the maximum delay in response to a command to 1µs multiplied by the number of chips used in the stack minus 1. For a 31-chip stack, a maximum 30µs delay is incurred before the top module responds. This means that up to 372 cells can be measured with an elapsed measurement time from start to finish of 137µs. For a 16-chip stack, a 15µs delay is incurred. This allows measurement of up to 192 cells with an elapsed measurement time from start to finish of 122µs.

The MAX11068 incorporates an internal oscillator that generates a 6.0MHz system clock with  $\pm 3.0\%$  accuracy.

#### **Architectural Overview**

The MAX11068 is a complete data-acquisition system on a chip designed for rugged, high-voltage measurement applications. It can measure up to 12 channels of voltages from batteries or SuperCaps with a high-accuracy, high-speed SAR ADC. Two auxiliary input channels may be configured for general-purpose measurements or as specialized temperature conversion inputs when used with RTD devices. Simple, yet fast and powerful digital command and control is implemented through unique, high-performance, level-shifted I<sup>2</sup>C communication ports. This allows SMBus laddering the communication and control bus on up to 31 battery modules using the MAX11068.

#### **Battery Pack Architectures**

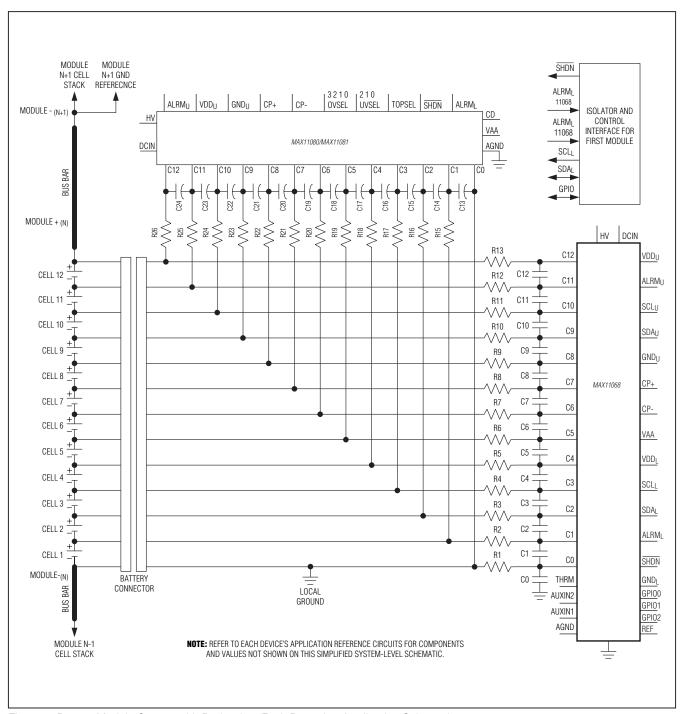

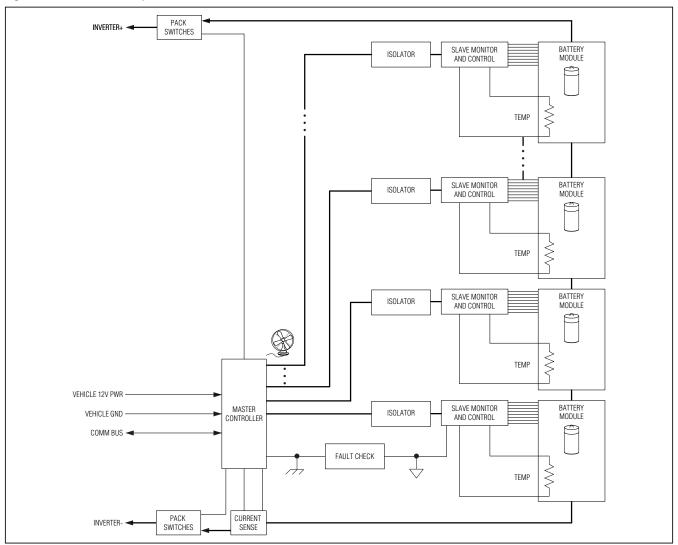

Battery packs are designed in a modular fashion to allow for multiple configurations, and fast and flexible assembly. This reduces cost by streamlining the build or repair process. The definition of a battery pack is a system comprising one or more battery modules connected in either a series or matrix configuration to create a highvoltage power source. Transportation or high-power battery-backup-system applications typically use many series-connected battery modules to generate voltages of up to several hundred volts. This voltage can then be inverted and transformed to levels suitable for the given load. A battery module is a series of cells configured as a subsystem that can be combined with other modules to build a high-voltage pack. For the MAX11068, the minimum cell count per module is limited by the 6.0V input requirement of the regulator, while the maximum cell count is 12. The 6.0V minimum requirement usually limits configurations to at least two lithium-ion (Li+), six NiMH, or six SuperCap cells per module. Figure 6 is the module system with redundant fault-detection application schematic.

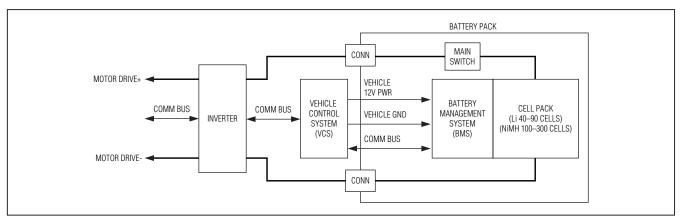

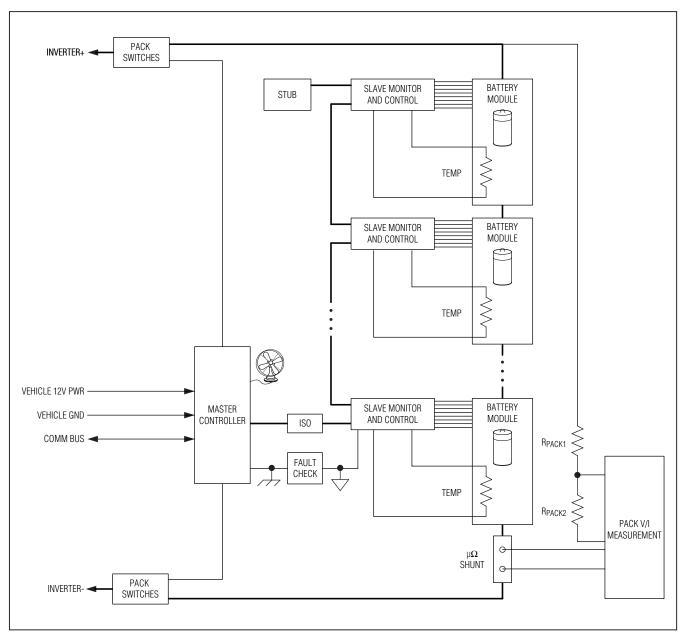

Battery packs used in transportation applications may be composed of various battery technologies (NiMH, Li+, SuperCap, or lead acid) and typically include an electronic battery-management system (BMS), environment control, and several safety features. Figure 7 shows the electric vehicle system (EVS).

In hybrid electric vehicles (HEVs), plug-in hybrid electric vehicles (PHEVs), electric vehicles (EVs), or fuel-cell vehicles (FCVs), cell counts can range from 36 cells to 200 cells using Li+ batteries and up to as high as 200 to 500 cells using NiMH batteries. SuperCaps are typically used in fast-charge holding applications such as regenerative braking energy storage.

There are two fundamental battery-pack management architectures that can be realized with the MAX11068:

- Distributed module communication

- SMBus-laddered module communication

A distributed module system deploys a point-to-point connection from each battery module back to a master microcontroller in the BMS. Because the battery modules operate from the high-voltage battery stack, galvanic isolation must be used when communicating with the master microcontroller. Figure 8 shows the distributed communication battery pack.

An SMBus-laddered module system deploys a serial communication bus that travels through each battery module and is then accessed at one entry point in the system by the master microcontroller in the BMS. The SMBus ladder method reduces cost and requires at most a single galvanic isolator between the high-voltage batteries and the main power net. Galvanic isolation may not be required in certain low-voltage applications. See Figure 9.

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

Figure 6. Battery Module System with Redundant Fault-Detection Application Schematic

Figure 7. Electric Vehicle System

Figure 8. Distributed Communication Battery Pack

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

Figure 9. SMBus-Laddered Battery Module Communication

#### Battery-Management System (BMS)

The BMS in an electric vehicle monitors cell voltage, pack current, and temperature. The BMS is composed of two components. The first is the master controller of the system that handles all communication with the VCS. It also handles state of charge, state of health, and fault-management features of the battery pack. The second component is the data-monitoring function, which gathers information on the conditions of the battery cells, takes voltage/current/temperature measurements, and signals safety faults.

The slave monitor controller (SLC) is directly connected to the series stack battery cells. The SLC measures cell voltages and module temperature, as well as controls the cell-charge equalization feature that keeps all cells balanced to equal states of charge. The SLCs are also designed to report alarm conditions such as cell overvoltage or undervoltage, sense wire-open circuits, and in the case of Li+ battery chemistries, overtemperature situations. The SLCs are managed by the master controller. The master controller orchestrates all data acquisition and cell-balancing tasks in the slaves. The master also measures the pack current coincident to voltage measurements so that state of health of the battery pack can be determined. Measurement of the current through the pack is made across a low-value shunt resistor or hall sensor.

#### Cell Inputs C0-C12

The MAX11068 contains 13 analog inputs that are used for the differential measurement of as many as 12 battery cells. Each differential cell input can withstand up to 9.0V and can be included in the measurement cycle through the cell-channel scan-enable bits of the CELLEN register (address 0x09). Cell inputs are measured differentially and level shifted down to the internal ADC by a high-voltage mux and ADC preamp. The common-mode range of the cell inputs from C2 to C12 is 0.5V to VHV - 2.9V. Common-mode range for C1 is limited to 7.0V and for C0 it is limited to voltages within 50mV of AGND for proper measurements. The absolute maximum differential input between two inputs must always be observed, which is 9.0V.

The application circuit shows RC filtering for each cell input. The values of the resistors are chosen in large part depending on the cell-balancing functionality that is desired. The capacitor value chosen complements the

resistor values to provide lowpass filtering of the ADC measurement. Capacitor values should be in the 100nF to 1µF range.

The first cell position between C1 and C0 must be populated for all applications with a voltage of at least 500mV. This ensures accurate measurements for all other cell positions as defined by the ADC specifications. When implementing a module configuration with fewer than 12 cells, the first cell position should always be used, and then other cell positions may be used in any configuration. Any unused cell positions should have their inputs shorted together. Random connection of cells or the high-voltage supplies during module configuration does not cause adverse effects.

#### **Measurement Scanning**

When a cell is enabled for acquisition by setting the associated scan-enable bits in the CELLEN register (address 0x09), the appropriate cell differential input is scheduled for conversion. The auxiliary input channels along with the self-diagnostic channel may be similarly enabled using their enable bits in the ADCCFG register (address 0x08).

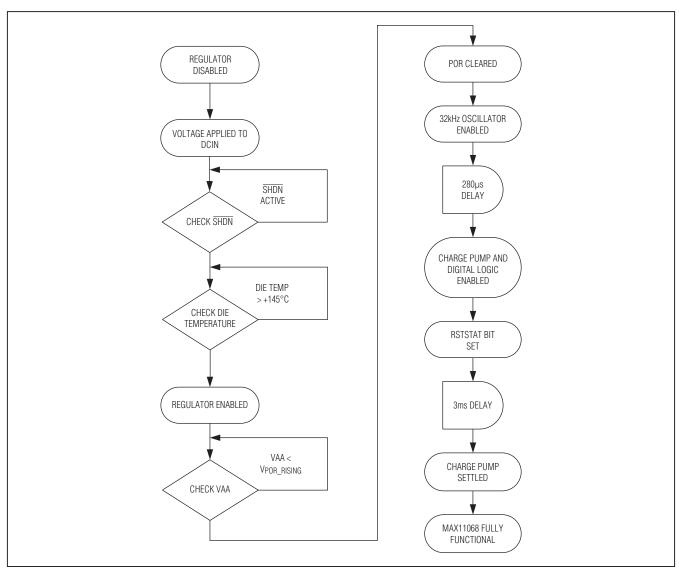

Conversion begins with the setting of the SCAN bit in the SCANCTRL register. The setting of the SCAN bit may be accomplished using either the WRITEALL command or the WRITEDEVICE command, depending on whether all devices are expected to perform the conversion. If the ADC is still busy from a previous acquisition scan, the scan command is ignored. Each module in a system begins the measurement scan cycle as soon as it receives the scan signal. The measurement order of the inputs during a cycle is as follows:

- 1) All enabled cell inputs phase 1, descending order (12-1)

- 2) All enabled cell inputs phase 2, descending order (12–1)

- 3) Self-diagnostic measurement phase 1, if enabled

- 4) Self-diagnostic measurement phase 2, if enabled

- All enabled auxiliary inputs phase 1, ascending order (AUXIN1, AUXIN2)

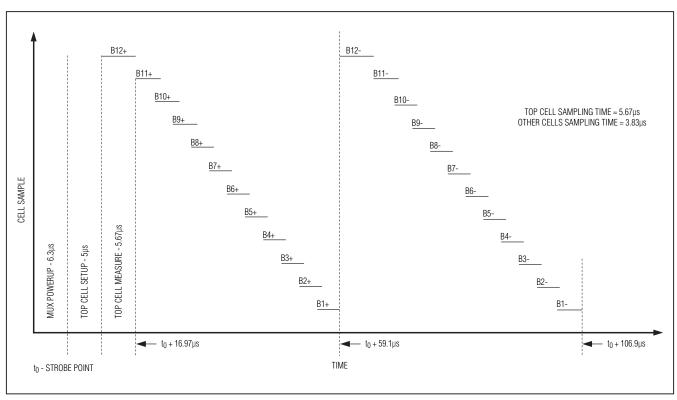

The complete acquisition of the cell voltages takes place in two phases, which is shown in Figure 10. The first phase is the raw cell-voltage acquisition. In this stage, the ADC scans through all the enabled cell input channels, starting with the highest cell.

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

Figure 10. Cell-Scanning Timing

The second stage in the channel-scanning process is the correction phase, where the front-end amplifier chops out any offset and reference-induced errors. This provides a high-accuracy cell voltage result. In this stage, the channels are converted in the same highest to lowest order as the initial measurement. The module-to-module sampling points differ by the communication forwarding delay from the I<sup>2</sup>C command. With the measurements from the two scan phases complete, the ADC data is then offset corrected, averaged, and updated in the cell data registers.

After the cell-measurement cycle is complete, the self-diagnostic channel is acquired when enabled. It is a two-phase measurement as described for the cell-voltage inputs, with each phase measured one immediately after the other. Finally, the enabled auxiliary inputs are measured. They are measured in a single conversion, with results reported in the AIN1 and AIN2 registers. The auxiliary channels have a configurable option to increase settling time that is set in the lower byte of the ACQCFG register (address 0x0C). The configured extra settling time is implemented just before the conversion for each AUXIN channel that is enabled for measure-

ment. So, when both auxiliary channels are measured, the extra settling time occurs twice. Extra settling time is not needed by the MAX11068 ADC; it is only for the benefit of the external application circuit.

#### **Calculating Measurement Time**

The first requirement for performing a measurement conversion is setting the SCAN bit. This can be done by using the WRITEALL or WRITEDEVICE commands. The write commands require 5 full bytes of data, plus 5 acknowledge bits and the start and stop bits. This totals 47 bits of data sent by the host, which would require 235µs at a 200kHz I<sup>2</sup>C clock rate.

The timing of the cell measurements is shown in Figure 10. At the start of the measurement cycle, there is a measurement setup time prior to the measurement of the highest cell totaling 11.3µs. The highest cell measured requires a sampling time of 5.67µs, while the rest of the inputs are sampled at 3.83µs per channel. When all 12 channels are enabled, the 12-cell voltages for one phase are acquired in 47.8µs, not including the measurement setup time. The total acquisition time for 12 cells is 106.9µs

For every module in the battery pack, a 1µs communication delay is incurred while the scan command is forwarded up the SMBus ladder. Therefore, the difference in the scan completion time from the first module to the last module in a chain is no more than 1µs x (no. of modules in the chain - 1) as shown in Figure 11.

Taking the module conversion time and combining it with the communication delay, the overall sampling window of the system can be calculated:

Sampling window = 11.3µs + (5.67µs + (no. of cells enabled per module -1) x 3.83µs) x 2 phases + ((no. of modules per pack - 1) x 1µs per module)

So, for a battery pack that uses 12 cells per module and a system with four modules (total cell count = 48), the sampling window would be:

Sampling Window =  $11.3 + (5.67 + 11 \times 3.83 \mu s) \times 2 + ((4 \text{ Modules } -1) \times 1 \mu s)$

Sampling Window =  $(106.9 \mu s) + (3 \mu s) = 109.9 \mu s$

Thus, from the time the first device receives the scan command until the last device completes its measurement conversion, 109.9µs elapse.

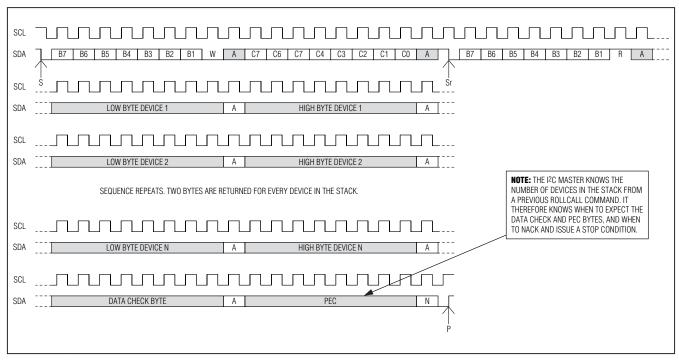

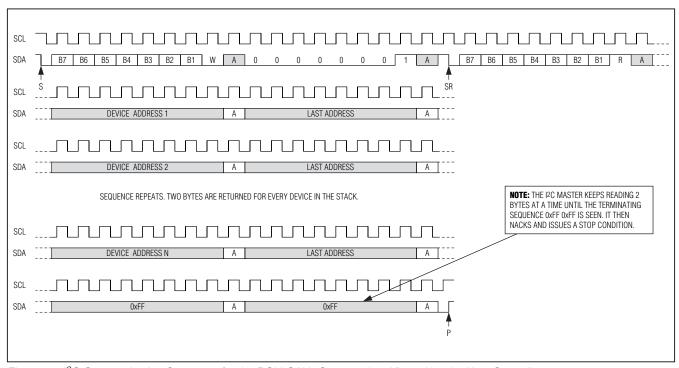

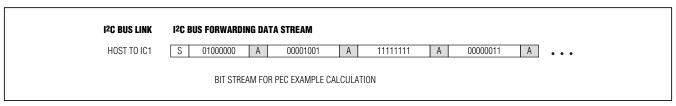

The final aspect of the measurement conversion is the retrieval of data from all devices. A READALL command is the only way to transfer data from each device. Since up to 12 cells are measured, the READALL command must be performed for each cell whose data must be transferred. For each READALL command, there are 5 total bytes of overhead. These include the broadcast address byte, the command code byte (register address to be read), the I2C address byte, the data check byte, and the packet-error check (PEC) byte. Each of these bytes has an acknowledge bit associated with it. The register data from each device consists of 2 more bytes plus 2 acknowledge bits. Finally, the overall data stream consists of 3 more bits, start, stop, and repeated start. Thus, for a read of a single register from all modules, the total bit count is:

READALL bit count =  $3 + 5 \times 8 + 5 + \text{no. of modules } \times (2 \times 8 + 2) = 120$

Figure 11. Measurement Scan Timing for a Multimodule System

# 12-Channel, High-Voltage Sensor, Smart Data-Acquisition Interface

For the example with four modules and 12 cells per module, the total READALL bit count would be 120 bits per cell or 1440 bits for all 12 cells. At a 200kHz I<sup>2</sup>C clock rate, the total time for this command would be 7.2ms.

The overall time from the host issuing the scan command to the last data being received by the host includes the write time for the scan command, the measurement conversion time, and the time for the READALL command. For this 12-cell, four-module, 200kHz I<sup>2</sup>C example the total is:

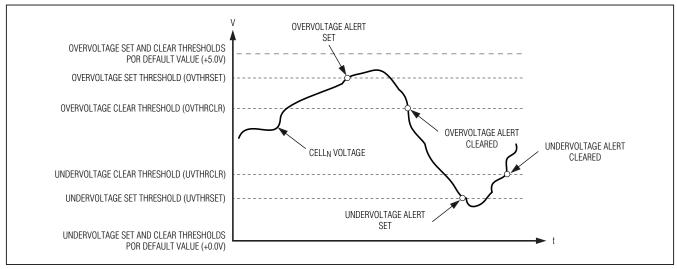

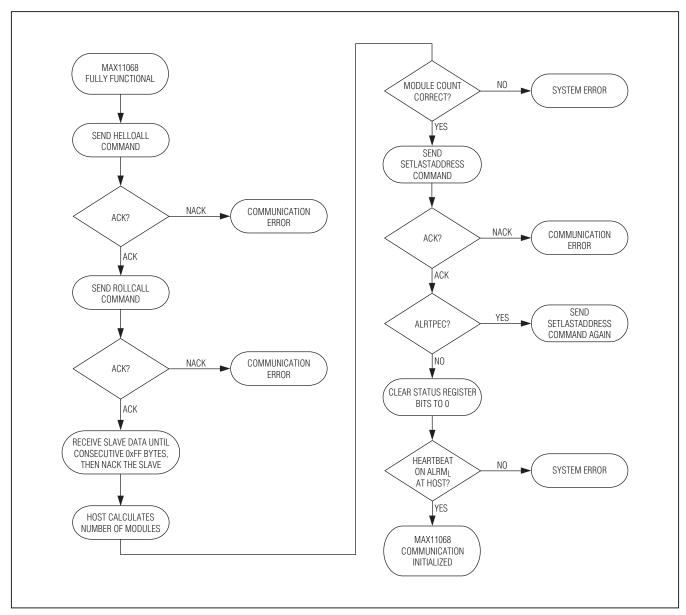

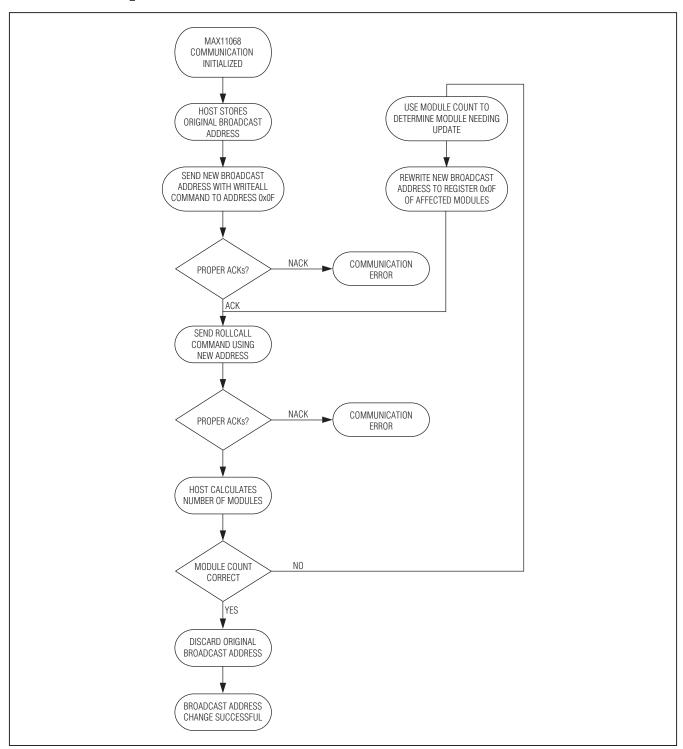

$$235\mu s + 106.9\mu s + 7200\mu s = 7.542ms$$