### **RV-8803-C7 Application Manual**

## Application Manual

RV-8803-C7

# DTCXO Temp. Compensated Real-Time Clock Module with I<sup>2</sup>C-Bus Interface

May 2019 1/74 Rev. 1.6

### **TABLE OF CONTENTS**

| 1. | 0           | VERVIEW                                        | 5  |

|----|-------------|------------------------------------------------|----|

|    | 1.1.        | GENERAL DESCRIPTION                            | 5  |

|    | 1.2.        | APPLICATIONS                                   | 6  |

|    | 1.3.        | ORDERING INFORMATION                           | 7  |

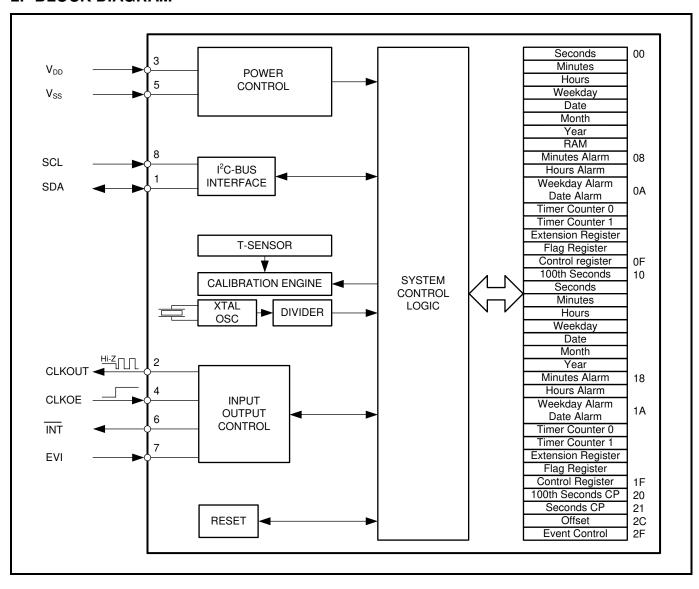

| 2. | В           | LOCK DIAGRAM                                   | 8  |

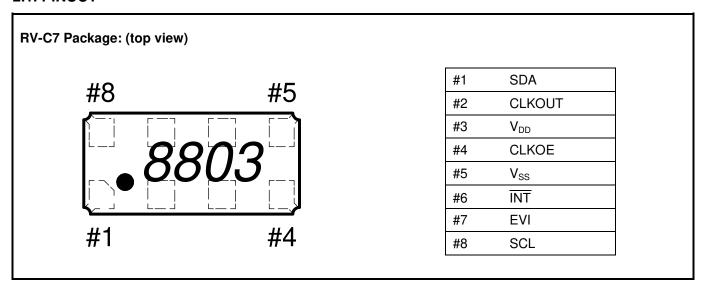

|    | 2.1.        | PINOUT                                         | 9  |

|    | 2.2.        | PIN DESCRIPTION                                | 9  |

|    | 2.3.        | FUNCTIONAL DESCRIPTION                         | 10 |

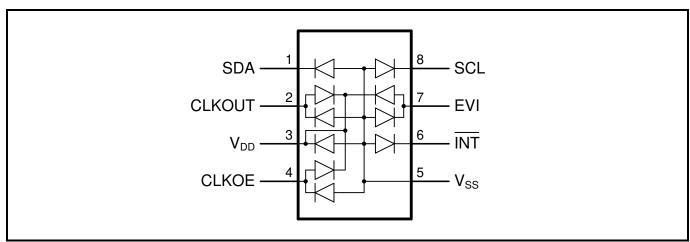

|    | 2.4.        | DEVICE PROTECTION DIAGRAM                      | 10 |

| 3. | RI          | EGISTER ORGANIZATION                           | 11 |

|    | 3.1.        | REGISTER OVERVIEW                              | 11 |

|    | <i>3.2.</i> | CLOCK REGISTERS                                | 13 |

|    | <i>3.3.</i> | CALENDAR REGISTERS                             | 14 |

|    | 3.4.        | ALARM REGISTERS                                | 16 |

|    | 3.5.        | PERIODIC COUNTDOWN TIMER CONTROL REGISTERS     | 18 |

|    | 3.6.        | EXTENSION REGISTER                             | 19 |

|    | <i>3.7.</i> | FLAG REGISTER                                  | 20 |

|    | <i>3.8.</i> | CONTROL REGISTER                               | 21 |

|    | 3.9.        | OFFSET REGISTER                                | 22 |

|    | 3.10.       | CAPTURE BUFFER/EVENT CONTROL REGISTERS         | 23 |

|    | 3.11.       | REGISTER RESET VALUES SUMMARY                  | 25 |

| 4. | DI          | ETAILED FUNCTIONAL DESCRIPTION                 | 26 |

|    | 4.1.        | POWER ON RESET (POR)                           | 26 |

|    | 4.2.        | POWER MANAGEMENT                               | 26 |

|    | 4.3.        | CLOCK SOURCE                                   | 26 |

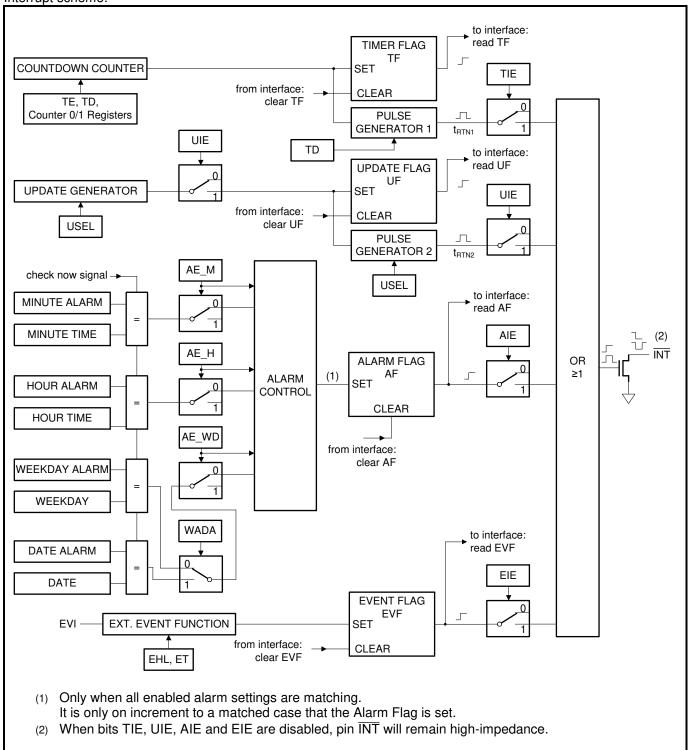

|    | 4.4.        | INTERRUPT OUTPUT                               | 27 |

|    | 4.          | 4.1. SERVICING INTERRUPTS                      | 28 |

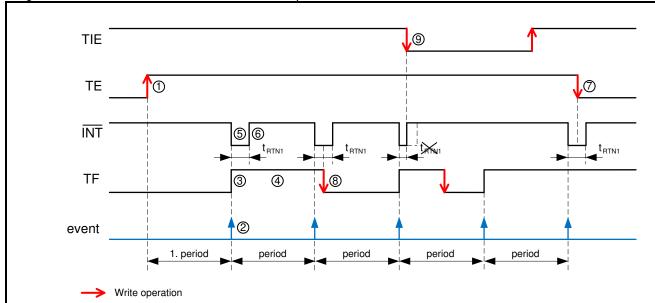

|    | 4.5.        | PERIODIC COUNTDOWN TIMER INTERRUPT FUNCTION    | 29 |

|    | 4.          | 5.1. PERIODIC COUNTDOWN TIMER DIAGRAM          | 29 |

|    | 4.          | 5.2. USE OF THE PERIODIC COUNTDOWN TIMER       | 30 |

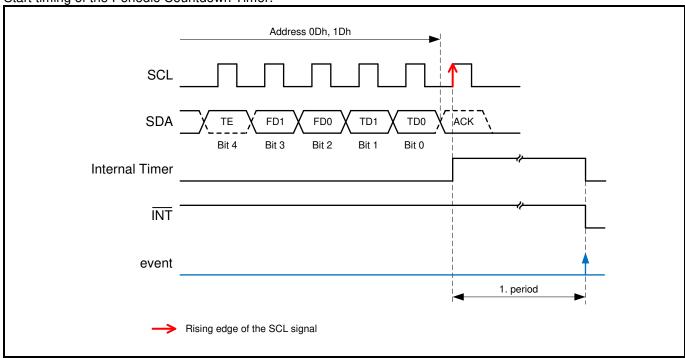

|    | 4.          | 5.3. FIRST PERIOD DURATION                     | 31 |

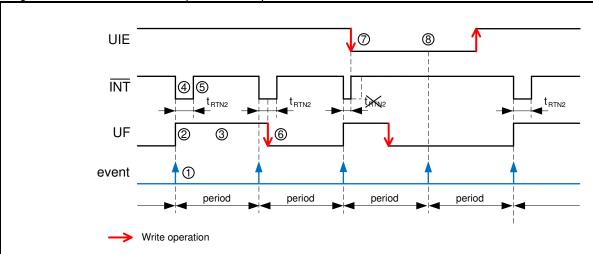

|    | 4.6.        | PERIODIC TIME UPDATE INTERRUPT FUNCTION        | 32 |

|    | 4.          | 6.1. PERIODIC TIME UPDATE DIAGRAM              | 32 |

|    | 4.          | 6.2. USE OF THE PERIODIC TIME UPDATE INTERRUPT | 33 |

|    | 4.7.        | ALARM INTERRUPT FUNCTION                       | 34 |

|    | 4.          | 7.1. ALARM DIAGRAM                             | 34 |

|    | 4.          | 7.2. USE OF THE ALARM INTERRUPT                | 35 |

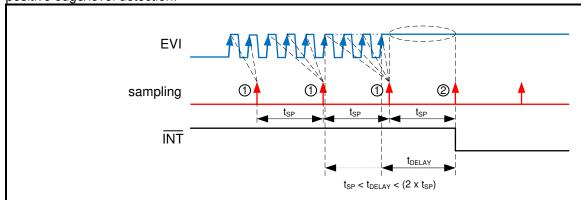

|    | 4.8.        | EXTERNAL EVENT FUNCTION                        | 36 |

| DTCXO Temp. Compensated Real-Time Clock Module with I <sup>2</sup> C-Bus Interface | e RV-8803-C7   |

|------------------------------------------------------------------------------------|----------------|

| 4.8.1. EXTERNAL EVENT DIAGRAM                                                      | 37             |

| 4.8.2. USE OF THE EXTERNAL EVENT FUNCTION                                          | 38             |

| 4.9. CLKOUT FREQUENCY SELECTION                                                    | 39             |

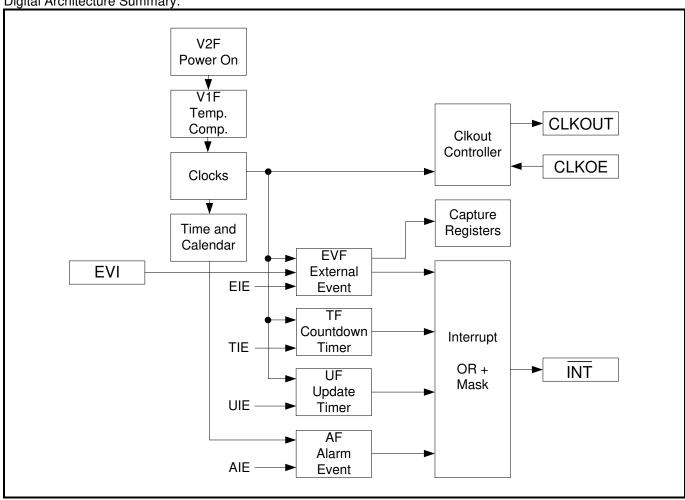

| 4.10. DIGITAL ARCHITECTURE SUMMARY                                                 | 40             |

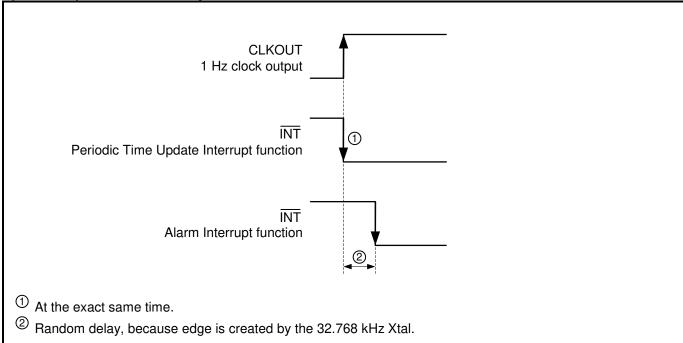

| 4.11. SYNCHRONICITY BETWEEN INT SIGNALS AND 1 HZ CLKOUT                            | 41             |

| 4.12. TIME DATA READ-OUT                                                           | 42             |

| 4.12.1. PROCEDURE                                                                  | 42             |

| 4.12.2. METHODE TO CONFIRM CORRECT TIME AND CALENDAR REA                           | D-OUT42        |

| 4.13. RESET BIT FUNCTION                                                           | 43             |

| 4.14. ERST BIT FUNCTION                                                            | 43             |

| 5. TEMPERATURE COMPENSATION                                                        | 44             |

| 5.1. FREQUENCIES                                                                   | 44             |

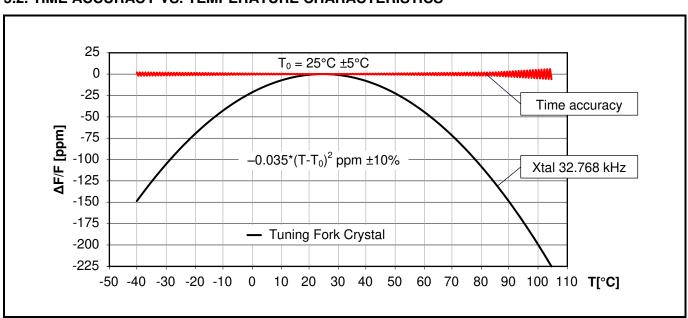

| 5.2. TIME ACCURACY VS. TEMPERATURE CHARACTERISTICS                                 | 44             |

| 5.3. COMPENSATION VALUES                                                           | 45             |

| 5.4. AGING CORRECTION                                                              | 45             |

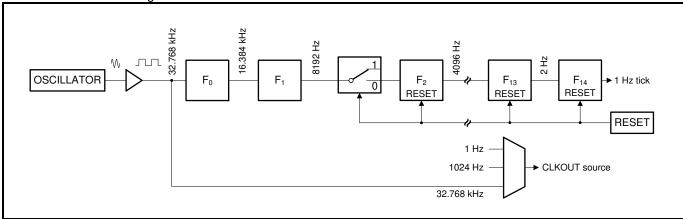

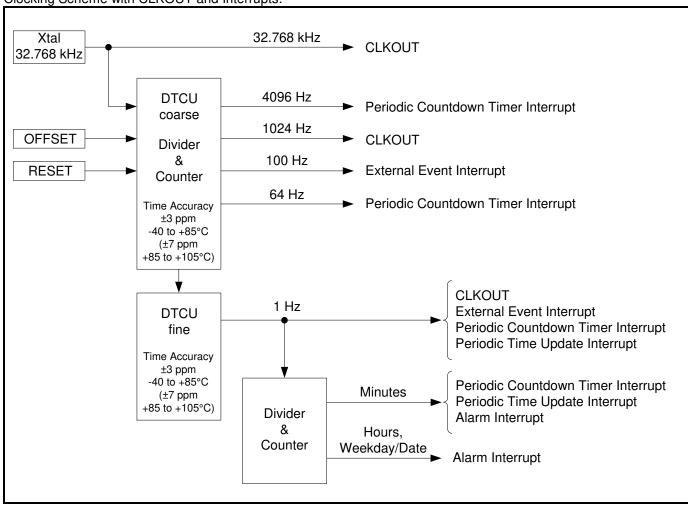

| 5.5. CLOCKING SCHEME                                                               | 46             |

| 5.6. MEASURING TIME ACCURACY AT CLKOUT PIN                                         | 47             |

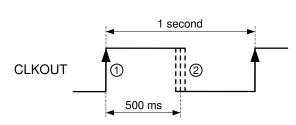

| 5.6.1. MEASURING 1 HZ AT CLKOUT PIN                                                | 47             |

| 5.7. MEASURING TIME ACCURACY AT INT PIN                                            | 48             |

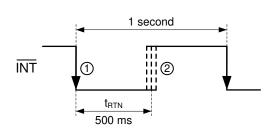

| 5.7.1. MEASURING 1 HZ WITH THE PERIODIC TIME UPDATE INTERRU                        | JPT FUNCTION48 |

| 6. I <sup>2</sup> C INTERFACE                                                      | 49             |

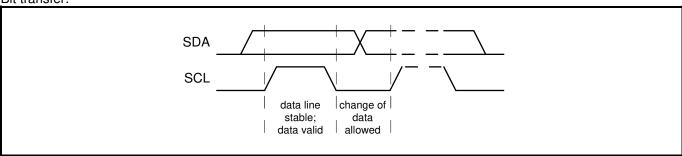

| 6.1. BIT TRANSFER                                                                  | 49             |

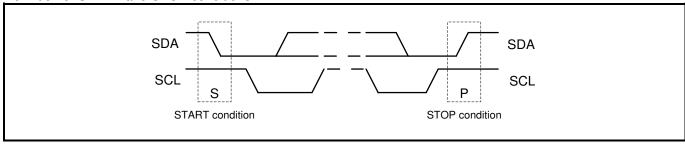

| 6.2. START AND STOP CONDITIONS                                                     | 49             |

| 6.3. DATA VALID                                                                    | 50             |

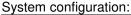

| 6.4. SYSTEM CONFIGURATION                                                          | 50             |

| 6.5. ACKNOWLEDGE                                                                   | 51             |

| 6.6. SLAVE ADDRESS                                                                 | 52             |

| 6.7. WRITE OPERATION                                                               | 52             |

| 6.8. READ OPERATION AT SPECIFIC ADDRESS                                            | 53             |

| 6.9. READ OPERATION                                                                | 54             |

| 6.10. FREE-CLOCKING L'C-BUS                                                        | 54             |

| 7. ELECTRICAL SPECIFICATIONS                                                       | 55             |

| 7.1. ABSOLUTE MAXIMUM RATINGS                                                      | 55             |

| 7.2. OPERATING PARAMETERS                                                          | 56             |

| 7.2.1. TEMPERATURE COMPENSATION AND CURRENT CONSUMPTION                            |                |

| 7.2.2. 32.768 KHZ ENABLE/DISABLE TIMING                                            | 58             |

| 7.3. OSCILLATOR PARAMETERS                                                         | 59             |

| 7.3.1. TIME ACCURACY 1 HZ EXAMPLES                                                 |                |

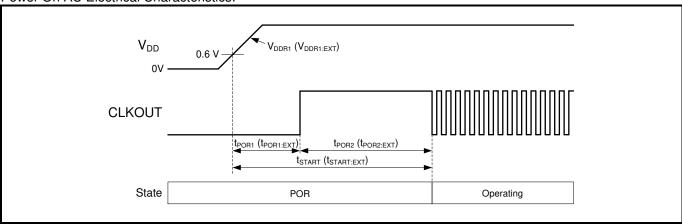

| 7.4. POWER ON AC ELECTRICAL CHARACTERISTICS                                        | 61             |

| DTC | CXO Temp. Compensated Real-Time Clock Module with I <sup>2</sup> C-Bus Interface | RV-8803-C7 |

|-----|----------------------------------------------------------------------------------|------------|

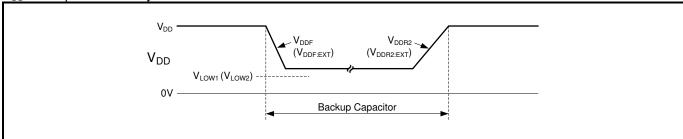

| 7   | 7.5. BACKUP AND RECOVERY                                                         | 62         |

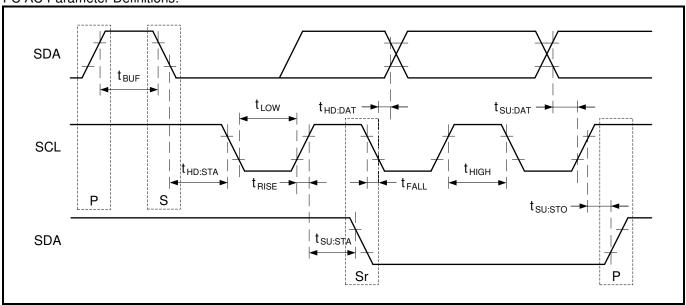

| 7   | 7.6. fC-BUS CHARACTERISTICS                                                      | 63         |

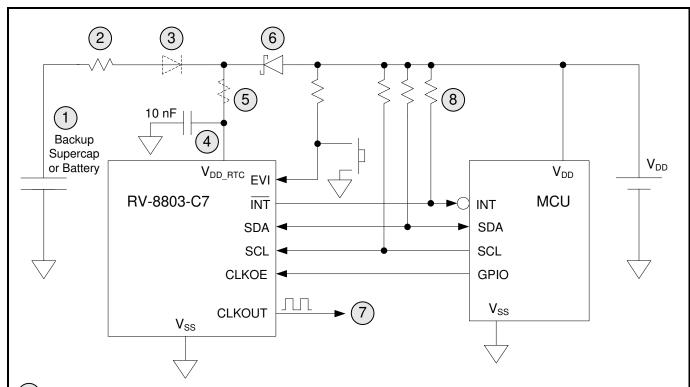

| 8.  | TYPICAL APPLICATION CIRCUIT                                                      | 64         |

| 8   | 3.1. OPERATING RV-8803-C7 WITH BACKUP CAPACITOR                                  |            |

| 9.  | PACKAGE                                                                          | 65         |

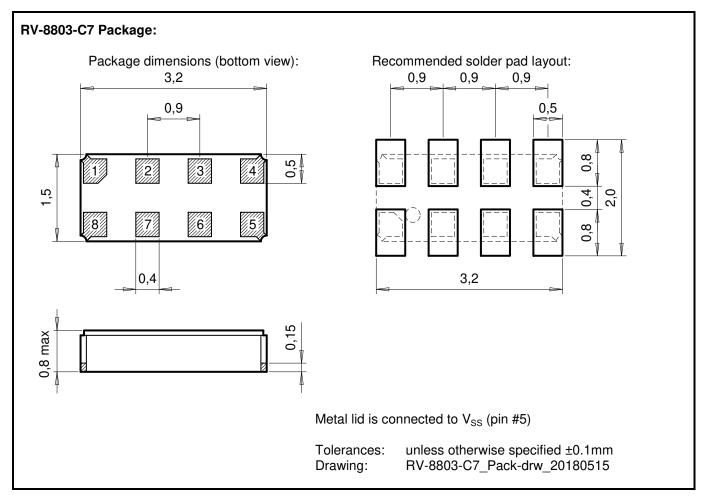

| 9   | 0.1. DIMENSIONS AND SOLDER PAD LAYOUT                                            | 65         |

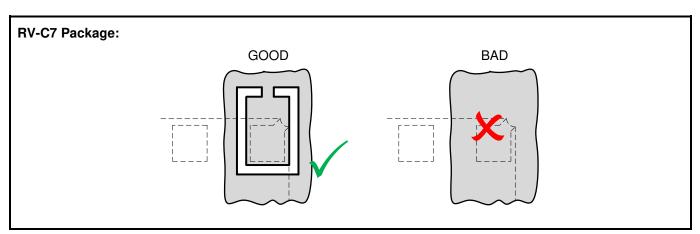

|     | 9.1.1. RECOMMENDED THERMAL RELIEF                                                | 65         |

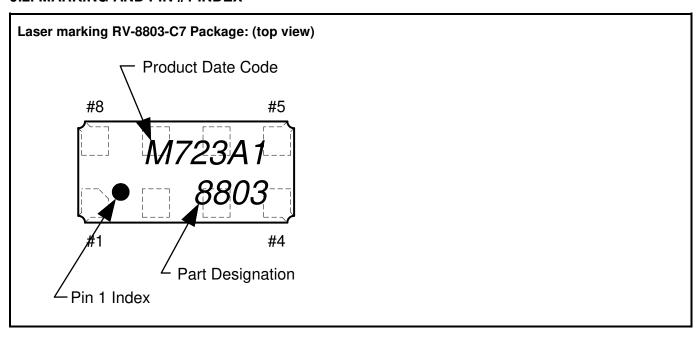

| 9   | 0.2. MARKING AND PIN #1 INDEX                                                    | 66         |

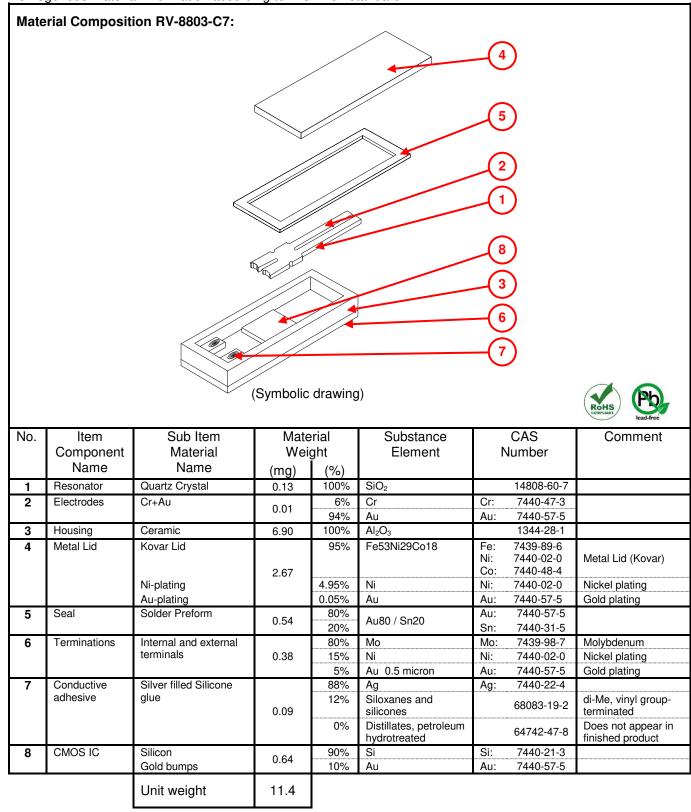

| 10. | MATERIAL COMPOSITION DECLARATION & ENVIRONMENTAL INFORMATION                     | 67         |

| 1   | 0.1. HOMOGENOUS MATERIAL COMPOSITION DECLARATION                                 | 67         |

| 1   | 0.2. MATERIAL ANALYSIS & TEST RESULTS                                            | 68         |

| 1   | 0.3. RECYCLING MATERIAL INFORMATION                                              | 69         |

| 1   | 0.4. ENVIRONMENTAL PROPERTIES & ABSOLUTE MAXIMUM RATINGS                         | 70         |

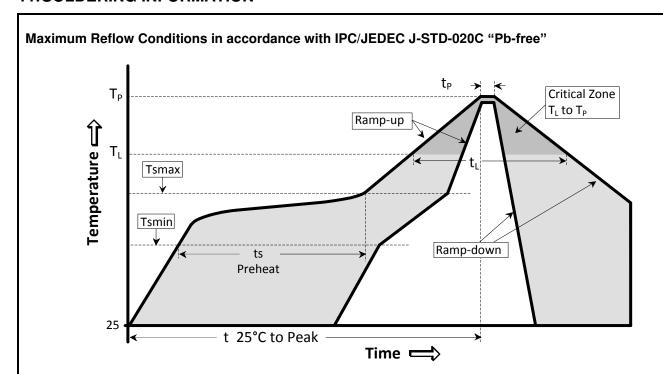

| 11. | SOLDERING INFORMATION                                                            | 71         |

| 12. | HANDLING PRECAUTIONS FOR MODULES WITH EMBEDDED CRYSTALS                          | 72         |

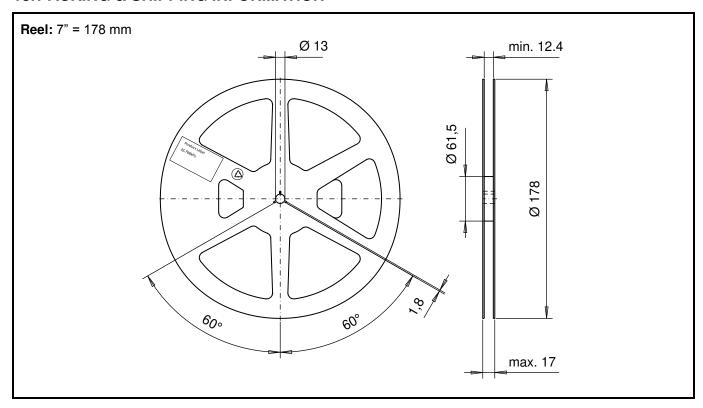

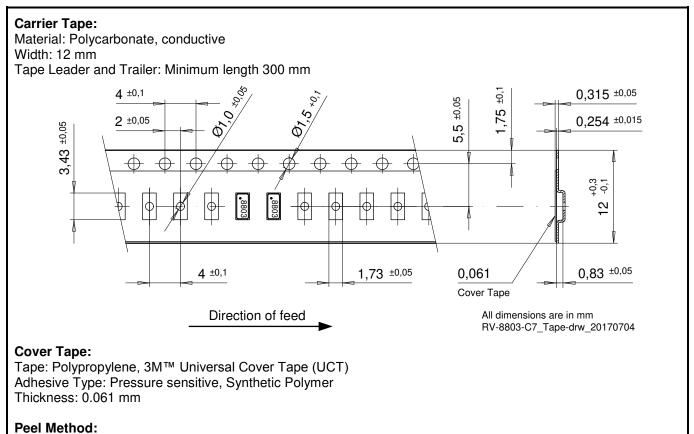

| 13. | PACKING & SHIPPING INFORMATION                                                   | 73         |

| 14. | COMPLIANCE INFORMATION                                                           | 74         |

| 15. | DOCUMENT REVISION HISTORY                                                        | 74         |

### DTCXO Temp. Compensated Real-Time Clock Module with I<sup>2</sup>C-Bus Interface

### 1. OVERVIEW

- RTC module with built-in "Tuning Fork" crystal oscillating at 32.768 kHz

- Counters for hundredths of seconds, seconds, minutes, hours, date, month, year and weekday

- Factory calibrated temperature compensation

- Very high Time Accuracy

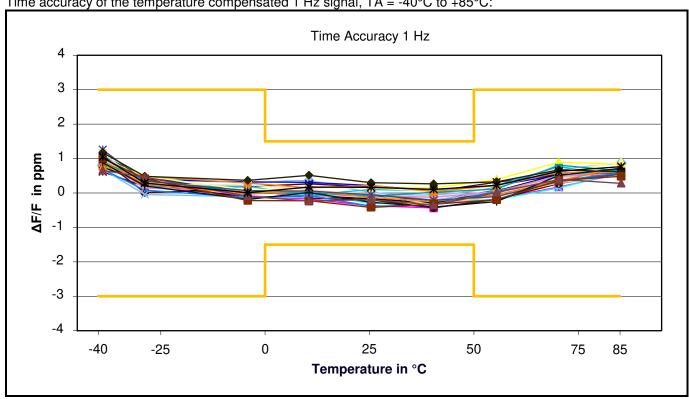

- ±1.5 ppm 0 to +50°C

- o ±3.0 ppm -40 to +85°C

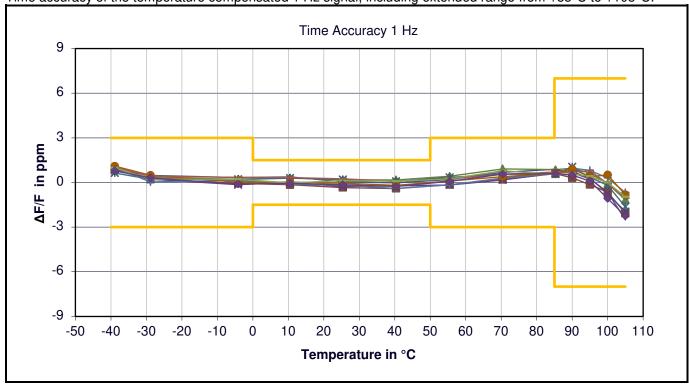

- o ±7.0 ppm +85 to +105°C

- o Aging compensation with OFFSET value

- I<sup>2</sup>C-bus interface (up to 400 kHz)

- Periodic Countdown Timer Interrupt function

- Periodic Time Update Interrupt function (seconds, minutes)

- Alarm Interrupts for weekday or date, hour and minute settings

- External Event Input with Interrupt and Time Stamp function

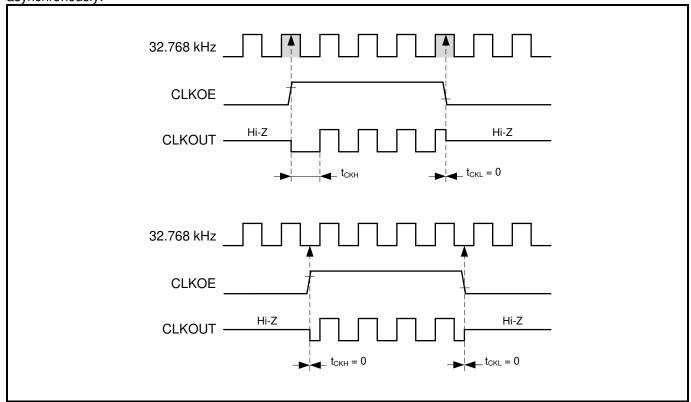

- Programmable Clock Output for peripheral devices (32.768 kHz, 1024 Hz, 1 Hz) with enable/disable function (CLKOE)

- Automatic leap year correction: 2000 to 2099

- Internal Power-On Reset (POR)

- Low voltage detector

- Wide operating voltage range: 1.5 V to 5.5 V

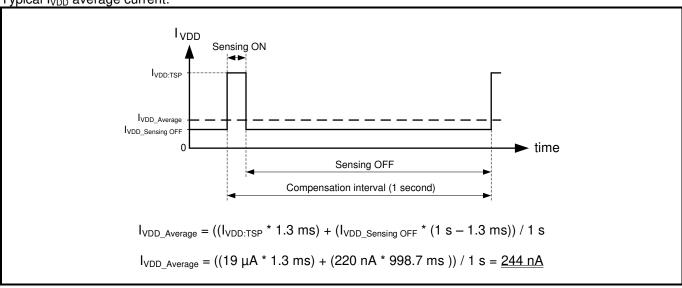

- Very low current consumption: 240 nA (V<sub>DD</sub> = 3.0 V, T<sub>A</sub> = 25°C)

- Operating temperature range: -40 to +85°C

(supports extended range from +85°C to +105°C with limitations)

- Ultra small and compact C7 package size, RoHS-compliant and 100% leadfree: 3.2 x 1.5 x 0.8 mm

- Register compatible with Epson RX-8803SA/LC

- Automotive qualification according to AEC-Q200 available

### 1.1. GENERAL DESCRIPTION

The RV-8803-C7 is a highly accurate real-time clock/calendar module due to its built-in Thermometer and Digital Temperature Compensation circuitry (DTCXO). The Temperature Compensation circuitry is factory calibrated and results in highest time accuracy of ±3.0 ppm across the temperature range from -40 to +85°C and a time accuracy of ±7.0 ppm for the extended range from +85°C to +105°C, and additionally offers an aging offset correction. The RV-8803-C7 has the smallest package and the lowest current consumption among all temperature compensated RTC modules. Due to its special architecture the RV-8803-C7 provides a very low current consumption of 240 nA.

### 1.2. APPLICATIONS

The RV-8803-C7 RTC module combines key functions with outstanding performance in an ultra-small ceramic package:

- Factory calibrated Temperature Compensation with temperature measuring every second

- Ultra-Low Power consumption

- Smallest RTC module (embedded XTAL) in an ultra-small 3.2 x 1.5 x 0.8 mm leadfree ceramic package.

These unique features make this product perfectly suitable for many applications:

• Communication: IoT / Wearables / Wireless Sensors and Tags / Handsets

Automotive: M2M / Navigation & Tracking Systems / Dashboard / Tachometers / Engine Controller

Car Audio & Entertainment Systems

Metering: E-Meter / Heating Counter / Smart Meters / PV Converter/ Utility metering

Outdoor: ATM & POS systems / Surveillance & Safety systems / Ticketing Systems

Medical: Glucose Meter / Health Monitoring Systems

Safety: Security & Camera Systems / Door Lock & Access Control / Tamper Detection

Consumer: Gambling Machines / TV & Set Top Boxes / White Goods

Automation: PLC / Data Logger / Home & Factory Automation / Industrial and Consumer Electronics

### DTCXO Temp. Compensated Real-Time Clock Module with ${\rm I}^2{\rm C-Bus}$ Interface

RV-8803-C7

### 1.3. ORDERING INFORMATION

Example: RV-8803-C7 TA QC

| Code          | Operating temperature range |

|---------------|-----------------------------|

| TA (Standard) | -40 to +85°C 1)             |

<sup>1)</sup> Supports extended range from +85°C to 105°C with limitations.

| Code          | Qualification             |

|---------------|---------------------------|

| QC (Standard) | Commercial Grade          |

| QA            | Automotive Grade AEC-Q200 |

### 2. BLOCK DIAGRAM

### **2.1. PINOUT**

### 2.2. PIN DESCRIPTION

| Symbol          | Pin# | Description                                                                                                                                                                                                                                                        |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA             | 1    | I <sup>2</sup> C Serial Data Input-Output; open-drain; requires pull-up resistor.                                                                                                                                                                                  |

| CLKOUT          | 2    | Clock Output; push-pull; controlled by CLKOE. If CLKOE is HIGH (V <sub>DD</sub> ), the CLKOUT pin drives the square wave of 32.768 kHz, 1024 Hz or 1 Hz (Default value is 32.768 kHz). When CLKOE is tied to Ground, the CLKOUT pin is high impedance (tri-state). |

| $V_{DD}$        | 3    | Power Supply Voltage.                                                                                                                                                                                                                                              |

| CLKOE           | 4    | Input to enable the CLKOUT pin. If CLKOE is HIGH, the CLKOUT pin is in output mode. When CLKOE is tied to Ground, the CLKOUT pin is stopped and is high impedance (tri-state). This pin should not be left floating.                                               |

| V <sub>SS</sub> | 5    | Ground.                                                                                                                                                                                                                                                            |

| ĪNT             | 6    | Interrupt Output; open-drain; active LOW; requires pull-up resistor; Used to output Alarm, Periodic Countdown Timer, Periodic Time Update and External Event Interrupt signals.                                                                                    |

| EVI             | 7    | External Event Interrupt Input with Time Stamp function. This pin should not be left floating.                                                                                                                                                                     |

| SCL             | 8    | I <sup>2</sup> C Serial Clock Input; requires pull-up resistor.                                                                                                                                                                                                    |

### 2.3. FUNCTIONAL DESCRIPTION

The RV-8803-C7 is a high accurate, ultra-low power CMOS based Real-Time-Clock Module with embedded 32.768 kHz Crystal. The Xtal 32.768 kHz clock itself is not temperature compensated.

The very high Time Accuracy and stability of  $\pm 3.0$  ppm over the temperature range from  $-40^{\circ}$ C to  $+85^{\circ}$ C and of  $\pm 7.0$  ppm for the extended range from  $+85^{\circ}$ C to  $+105^{\circ}$ C is achieved by the built-in Digital Temperature Compensation circuitry (DTCXO). The factory calibrated correction values are located in the EEPROM and are not accessible for the user. Additionally, there is an Offset Register customer use for aging correction.

The RV-8803-C7 provides standard Clock & Calendar function including seconds, minutes, hours (24), weekdays, date, months, years (with leap year correction) and interrupt functions for an External Event, Periodic Countdown Timer, Periodic Time Update and Alarm. Beside the standard RTC functions, it includes an integrated Temperature Sensor, a Time Stamp function for the External Event Input and 1 Byte of User RAM and offers an I<sup>2</sup>C-bus (2-wire Interface). Further 2 Bytes can be used as User RAM when the Periodic Countdown Timer is not used (Timer Counter registers 0Bh, 1Bh and 0Ch, 1Ch) and further 3 Bytes when the Alarm function is not used (Alarm registers 08h, 18h; 09h, 19h and 0Ah, 1Ah).

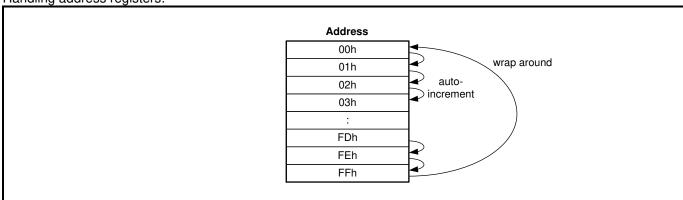

The registers are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte. When address is automatically incremented, wrap around occurs from the address FFh to the address 00h (see figure below).

Handling address registers:

### 2.4. DEVICE PROTECTION DIAGRAM

### 3. REGISTER ORGANIZATION

Registers are accessed by selecting a register address and then performing read or write operations. Multiple reads or writes may be executed in a single access, with the address automatically incrementing after each byte. The following tables Register Definitions (00h to 0Fh), (10h to 1Fh) and (20h to 2Fh) summarize the function of each register. In the table Register Definitions (00h to 0Fh) and (10h to 1Fh) the GPx bits (where x is between 0 and 5) are 6 register bits which may be used as general purpose storage. These bits are not described in the sections below. All of the GPx bits are cleared when the RV-8803-C7 powers up, and they can therefore be used to allow software to determine if a true Power On Reset has occurred, or to hold other initialization data.

Address 00h to 0Fh: Basic time and calendar register

Adds RAM

Address 10h to 1Fh: Extension register ①

Adds 100<sup>th</sup> Seconds counter

Capture buffer and Event control

Note: When writing or reading a specific function value into/from the Address range 00h to 0Fh the value will be automatically updated in the Address range 10h to 1Fh and vice versa.

In order to not corrupt the accuracy of the temperature compensation and the Time Stamp (Capture) function on the highest 100<sup>th</sup> Seconds resolution, it is not possible to freeze the clock and calendar register during read-out process, as it is common practice for other RTC's.

Since the time and calendar registers cannot be frozen, there might be a condition that the time registers are incremented while read-out. To avoid reading corrupted (partially incremented) data, special measures and procedures need to be applied (see TIME DATA READ).

### 3.1. REGISTER OVERVIEW

After reset, all registers are set according to Table in section REGISTER RESET VALUES SUMMARY.

### Register Definitions, Address 00h to 0Fh (Basic time and calendar register):

| Address | Function           | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------------|-----------|-------|-------|-------|-------|-------|-------|-------|

| 00h     | Seconds            | 0         | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 01h     | Minutes            | 0         | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 02h     | Hours              | 0         | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 03h     | Weekday            | 0         | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| 04h     | Date               | 0         | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 05h     | Month              | 0         | 0     | 0     | 10    | 8     | 4     | 2     | 1     |

| 06h     | Year               | 80        | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 07h     | RAM                |           |       |       | RAM   | data  |       |       | •     |

| 08h     | Minutes Alarm      | AE_M      | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 09h     | Hours Alarm        | AE_H      | GP0   | 20    | 10    | 8     | 4     | 2     | 1     |

| 0.4 h   | Weekday Alarm      | A.F. W.D. | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| 0Ah     | Date Alarm         | AE_WD     | GP1   | 20    | 10    | 8     | 4     | 2     | 1     |

| 0Bh     | Timer Counter 0    | 128       | 64    | 32    | 16    | 8     | 4     | 2     | 1     |

| 0Ch     | Timer Counter 1    | GP5       | GP4   | GP3   | GP2   | 2048  | 1024  | 512   | 256   |

| 0Dh     | Extension Register | TEST      | WADA  | USEL  | TE    | F     | D     | Т     | D     |

| 0Eh     | Flag Register      | 0         | 0     | UF    | TF    | AF    | EVF   | V2F   | V1F   |

| 0Fh     | Control Register   | RESE      | RVED  | UIE   | TIE   | AIE   | EIE   | 0     | RESE  |

### ${\tt DTCXO\ Temp.\ Compensated\ Real-Time\ Clock\ Module\ with\ I^2C-Bus\ Interface}$

RV-8803-C7

### Register Definitions, Address 10h to 1Fh (Extension register ①):

| Address             | Function                              | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------------|---------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 10h                 | 100 <sup>th</sup> Seconds (Read Only) | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 11h                 | Seconds                               | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 12h                 | Minutes                               | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 13h                 | Hours                                 | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 14h                 | Weekday                               | 0     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| 15h                 | Date                                  | 0     | 0     | 20    | 10    | 8     | 4     | 2     | 1     |

| 16h                 | Month                                 | 0     | 0     | 0     | 10    | 8     | 4     | 2     | 1     |

| 17h                 | Year                                  | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 18h                 | Minutes Alarm                         | AE_M  | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 19h                 | Hours Alarm                           | AE_H  | GP0   | 20    | 10    | 8     | 4     | 2     | 1     |

| 1Ah                 | Weekday Alarm                         | ΛΕ WD | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| TAIT                | Date Alarm                            | AE_WD | GP1   | 20    | 10    | 8     | 4     | 2     | 1     |

| 1Bh                 | Timer Counter 0                       | 128   | 64    | 32    | 16    | 8     | 4     | 2     | 1     |

| 1Ch                 | Timer Counter 1                       | GP5   | GP4   | GP3   | GP2   | 2048  | 1024  | 512   | 256   |

| 1Dh                 | Extension Register                    | TEST  | WADA  | USEL  | TE    | F     | D     | T     | D     |

| 1Eh                 | Flag Register                         | 0     | 0     | UF    | TF    | AF    | EVF   | V2F   | V1F   |

| 1Fh                 | Control Register                      | RESE  | RVED  | UIE   | TIE   | AIE   | EIE   | 0     | RESET |

| o Read only. Always | s 0.                                  |       |       |       |       |       |       |       |       |

### Register Definitions, Address 20h to 2Fh (Extension register 2):

| Address            | Function                                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------------|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 20h                | 100 <sup>th</sup> Seconds CP (Read Only) | 80    | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 21h                | Seconds CP (Read Only)                   | 0     | 40    | 20    | 10    | 8     | 4     | 2     | 1     |

| 2Ch                | Offset                                   | 0     | 0     |       |       | OFF   | SET   |       |       |

| 2Fh                | Event Control                            | ECP   | EHL   | E     | T     | 0     | 0     | 0     | ERST  |

| o Read only. Alway | /s 0.                                    | •     |       |       |       |       | •     | •     | •     |

### 3.2. CLOCK REGISTERS

### 10h - 100<sup>th</sup> Seconds (Read Only)

This register holds the count of hundredths of seconds, in two binary coded decimal (BCD) digits. Values will be from 00 to 99.

| Address | Function                              | Bit 7    | Bit 6                            | Bit 5                     | Bit 4         | Bit 3                                                     | Bit 2        | Bit 1        | Bit 0 |

|---------|---------------------------------------|----------|----------------------------------|---------------------------|---------------|-----------------------------------------------------------|--------------|--------------|-------|

| 10h     | 100 <sup>th</sup> Seconds (Read Only) | 80       | 40                               | 20                        | 10            | 8                                                         | 4            | 2            | 1     |

| TON     | Reset                                 | Х        | Х                                | Χ                         | Х             | Х                                                         | Х            | Χ            | Χ     |

| Bit     | Symbol                                | Value    | Description                      |                           |               |                                                           |              |              |       |

| 7:0     | 100 <sup>th</sup> Seconds (Read Only) | 00 to 99 | The 100 <sup>th</sup> register o | Seconds re<br>r when sett | egister is cl | of seconds,<br>eared to 00<br>SET bit to 1<br>tion on EVI | when writing | ng to the Se |       |

### 00h, 11h - Seconds

This register holds the count of seconds, in two binary coded decimal (BCD) digits. Values will be from 00 to 59.

| Addresses               | Function | Bit 7    | Bit 6                | Bit 5                                                                                                                                                                                                                                     | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|

| 00h, 11h <sup>(1)</sup> | Seconds  | 0        | 40                   | 20                                                                                                                                                                                                                                        | 10    | 8     | 4     | 2     | 1     |

| 0011, 1111              | Reset    | 0        | Χ                    | Χ                                                                                                                                                                                                                                         | Χ     | Χ     | X     | X     | X     |

| Bit                     | Symbol   | Value    | Description          |                                                                                                                                                                                                                                           |       |       |       |       |       |

| 7                       | 0        | 0        | Read only. Always 0. |                                                                                                                                                                                                                                           |       |       |       |       |       |

| 6:0                     | Seconds  | 00 to 59 | When wri             | Holds the count of seconds, coded in BCD format.  When writing to the Seconds register the 100 <sup>th</sup> Seconds register is cleared to 00. When RESET bit is 1 the Seconds register value remains unchanged (1 Hz clock is stopped). |       |       |       |       |       |

### 01h, 12h - Minutes

This register holds the count of minutes, in two binary coded decimal (BCD) digits. Values will be from 00 to 59.

| Addresses               | Function | Bit 7    | Bit 6                                            | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|--------------------------------------------------|-------|-------|-------------|-------|-------|-------|

| 01h, 12h <sup>(1)</sup> | Minutes  | 0        | 40                                               | 20    | 10    | 8           | 4     | 2     | 1     |

| 0111, 1211              | Reset    | 0        | Χ                                                | Χ     | Х     | Χ           | Χ     | Х     | Χ     |

| Bit                     | Symbol   | Value    |                                                  |       | I     | Description | 1     |       |       |

| 7                       | 0        | 0        | Read only. Always 0.                             |       |       |             |       |       |       |

| 6:0                     | Minutes  | 00 to 59 | Holds the count of minutes, coded in BCD format. |       |       |             |       |       |       |

### 02h, 13h - Hours

This register holds the count of hours, in two binary coded decimal (BCD) digits. Values will be from 00 to 23.

| Addresses               | Function | Bit 7    | Bit 6                                          | Bit 5       | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|------------------------------------------------|-------------|-------|-------|-------|-------|-------|

| 02h, 13h <sup>(1)</sup> | Hours    | 0        | 0                                              | 20          | 10    | 8     | 4     | 2     | 1     |

| 0211, 1311              | Reset    | 0        | 0                                              | Χ           | Χ     | Χ     | Χ     | Χ     | Χ     |

| Bit                     | Symbol   | Value    |                                                | Description |       |       |       |       |       |

| 7:6                     | 0        | 0        | Read only                                      | y. Always 0 |       |       |       |       |       |

| 5:0                     | Hours    | 00 to 23 | Holds the count of hours, coded in BCD format. |             |       |       |       |       |       |

This specific function accessed in Address range 00h to 0Fh is automatically updated in Address range 10h to 1Fh and vice versa.

### 3.3. CALENDAR REGISTERS

### 03h, 14h - Weekday

This register holds the current day of the week. Each bit represents one weekday that is assigned by the user. Values will range from 1 to 7. Do not set 1 to more than one bit.

| Addresses               | Function | Bit 7  | Bit 6     | Bit 5       | Bit 4       | Bit 3       | Bit 2        | Bit 1        | Bit 0 |

|-------------------------|----------|--------|-----------|-------------|-------------|-------------|--------------|--------------|-------|

| 03h, 14h <sup>(1)</sup> | Weekday  | 0      | 7         | 6           | 5           | 4           | 3            | 2            | 1     |

| 0311, 1411              | Reset    | 0      | Х         | Х           | Χ           | Х           | X            | X            | Х     |

| Bit                     | Symbol   | Value  |           |             |             | Description | า            |              |       |

| 7                       | 0        | 0      | Read only | y. Always 0 |             |             |              |              |       |

| 6:0                     | Weekday  | 1 to 7 | Holds the | weekday c   | ounter valu | e. Do not s | et 1 to more | e than one b | oit.  |

| Weekday                 |          | Bit 7  | Bit 6     | Bit 5       | Bit 4       | Bit 3       | Bit 2        | Bit 1        | Bit 0 |

| Weekday 1               |          |        | 0         | 0           | 0           | 0           | 0            | 0            | 1     |

| Weekday 2               |          | 1      | 0         | 0           | 0           | 0           | 0            | 1            | 0     |

| Weekday 3               |          | 1      | 0         | 0           | 0           | 0           | 1            | 0            | 0     |

| Weekday 4               |          | 0      | 0         | 0           | 0           | 1           | 0            | 0            | 0     |

| Weekday 5               |          | 1      | 0         | 0           | 1           | 0           | 0            | 0            | 0     |

| Weekday 6               |          | 1      | 0         | 1           | 0           | 0           | 0            | 0            | 0     |

| Weekday 7               |          | 1      | 1         | 0           | 0           | 0           | 0            | 0            | 0     |

### 04h, 15h - Date

This register holds the current day of the month, in two binary coded decimal (BCD) digits. Values will range from 00 to 31. The Reset value XX after POR has to be replaced by a valid initial value (01 to 31). Leap years are correctly handled from 2000 to 2099.

| Addresses               | Function | Bit 7    | Bit 6       | Bit 5                    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|-------------|--------------------------|-------|-------|-------|-------|-------|

| 04h, 15h <sup>(1)</sup> | Date     | 0        | 0           | 20                       | 10    | 8     | 4     | 2     | 1     |

| 0411, 1511              | Reset    | 0        | 0           | Х                        | Х     | Χ     | Х     | Х     | Х     |

| Bit                     | Symbol   | Value    | Description |                          |       |       |       |       |       |

| 7:6                     | 0        | 0        | Read only   | y. Always 0              |       |       |       |       |       |

| 5:0                     | Date     | 00 to 31 |             | current dat<br>after POR |       |       |       |       |       |

### 05h, 16h - Month

This register holds the current month, in two binary coded decimal (BCD) digits. Values will range from 01 to 12.

| Addresses               | Function | Bit 7    | Bit 6     | Bit 5       | Bit 4      | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|-----------|-------------|------------|-------------|-------|-------|-------|

| 05h, 16h <sup>(1)</sup> | Month    | 0        | 0         | 0           | 10         | 8           | 4     | 2     | 1     |

| USH, TOH                | Reset    | 0        | 0         | 0           | Х          | Х           | Х     | Х     | Х     |

| Bit                     | Symbol   | Value    |           |             |            | Description | า     |       |       |

| 7:5                     | 0        | 0        | Read only | y. Always 0 |            |             |       |       |       |

| 4:0                     | Month    | 01 to 12 | Holds the | current mo  | nth, coded | in BCD forr | mat.  |       |       |

This specific function accessed in Address range 00h to 0Fh is automatically updated in Address range 10h to 1Fh and vice versa.

### DTCXO Temp. Compensated Real-Time Clock Module with I<sup>2</sup>C-Bus Interface

RV-8803-C7

### 06h, 17h - Year

This register holds the current year, in two binary coded decimal (BCD) digits. Values will range from 00 to 99. Leap years are correctly handled from 2000 to 2099.

| Addresses               | Function | Bit 7    | Bit 6                                        | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|----------|----------|----------------------------------------------|-------|-------|-------------|-------|-------|-------|

| 06h, 17h <sup>(1)</sup> | Year     | 80       | 40                                           | 20    | 10    | 8           | 4     | 2     | 1     |

| 0611, 1711              | Reset    | X        | Χ                                            | Х     | Х     | Χ           | Х     | Х     | Х     |

| Bit                     | Symbol   | Value    |                                              |       |       | Description | 1     |       |       |

| 7:0                     | Year     | 00 to 99 | Holds the current year, coded in BCD format. |       |       |             |       |       |       |

### 07h - RAM

This register holds the bits for general purpose use.

| Address | Function | Bit 7         | Bit 6    | Bit 5 | Bit 4 | Bit 3       | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|---------------|----------|-------|-------|-------------|-------|-------|-------|

| 07h     | RAM      |               |          |       | RAM   | data        |       |       |       |

| 0711    | Reset    | 0             | 0        | 0     | 0     | 0           | 0     | 0     | 0     |

| Bit     | Symbol   | Value         |          |       | ı     | Description | 1     |       |       |

| 7:0     | RAM      | 00h to<br>FFh | User RAM | 1     |       |             |       |       |       |

This specific function accessed in Address range 00h to 0Fh is automatically updated in Address range 10h to 1Fh and vice versa.

### 3.4. ALARM REGISTERS

### 08h, 18h - Minutes Alarm

This register holds the Minutes Alarm Enable bit AE\_M and the alarm value for minutes, in two binary coded decimal (BCD) digits. Values will range from 00 to 59.

| Addresses               | Function      | Bit 7    | Bit 6                      | Bit 5        | Bit 4        | Bit 3        | Bit 2    | Bit 1     | Bit 0 |  |

|-------------------------|---------------|----------|----------------------------|--------------|--------------|--------------|----------|-----------|-------|--|

| 08h, 18h <sup>(1)</sup> | Minutes Alarm | AE_M     | 40                         | 20           | 10           | 8            | 4        | 2         | 1     |  |

| Uon, Ton                | Reset         | 0        | 0                          | 0            | 0            | 0            | 0        | 0         | 0     |  |

| Bit                     | Symbol        | Value    | Value Description          |              |              |              |          |           |       |  |

| _                       |               | Mir      | nutes Alarm                |              | Enables al   |              |          | H and AE_ | WD    |  |

| 7                       | AE_M          | 0        | Minutes A                  | Alarm is ena | abled. – Det | ault value   |          |           |       |  |

|                         |               | 1        | Minutes Alarm is disabled. |              |              |              |          |           |       |  |

| 6:0                     | Minutes Alarm | 00 to 59 | Holds the                  | alarm valu   | e for minute | es, coded ir | BCD form | at.       |       |  |

### 09h, 19h - Hours Alarm

This register holds the Hours Alarm Enable bit AE\_H and the alarm value for hours, in two binary coded decimal (BCD) digits. Values will range from 00 to 23.

| Addresses               | Function    | Bit 7    | Bit 6                                                                                                | Bit 5        | Bit 4       | Bit 3     | Bit 2 | Bit 1 | Bit 0 |  |

|-------------------------|-------------|----------|------------------------------------------------------------------------------------------------------|--------------|-------------|-----------|-------|-------|-------|--|

| 09h, 19h <sup>(1)</sup> | Hours Alarm | AE_H     | GP0                                                                                                  | 20           | 10          | 8         | 4     | 2     | 1     |  |

| ugn, Ign                | Reset       | 0        | 0                                                                                                    | 0            | 0           | 0         | 0     | 0     | 0     |  |

| Bit                     | Symbol      | Value    | lue Description                                                                                      |              |             |           |       |       |       |  |

|                         |             | Ho       | Hours Alarm Enable bit. Enables alarm together with AE_M and AE_WD (see USE OF THE ALARM INTERRUPT). |              |             |           |       |       |       |  |

| 7                       | AE_H        | 0        | Hours Ala                                                                                            | arm is enab  | led. – Defa | ult value |       |       |       |  |

|                         |             | 1        | Hours Ala                                                                                            | arm is disab | oled.       |           |       |       |       |  |

| 6                       | GP0         | 0 or 1   | Register bit for general purpose use.                                                                |              |             |           |       |       |       |  |

| 5:0                     | Hours Alarm | 00 to 23 | Holds the alarm value for hours, coded in BCD format.                                                |              |             |           |       |       |       |  |

<sup>&</sup>lt;sup>(1)</sup> This specific function accessed in Address range 00h to 0Fh is automatically updated in Address range 10h to 1Fh and vice versa.

### 0Ah, 1Ah - Weekday/Date Alarm

This register holds the Weekday/Date Alarm Enable bit AE\_WD. If the WADA bit is 0 (Bit 6 in Register 0Dh, 1Dh), it holds the alarm value for the day of the week (weekdays assigned by the user). Multiple weekdays can be selected. Values will range from 0000001 to 11111111. If the WADA bit is 1, it holds the alarm value for the date, in two binary coded decimal (BCD) digits. Values will range from 01 to 31. Leap years are correctly handled from 2000 to 2099.

Weekday Alarm when WADA = 0 (Bit 6 in Register 0Dh, 1Dh)

| Addresses               | Function             | Bit 7                    | Bit 6                                                         | Bit 5                   | Bit 4        | Bit 3                    | Bit 2 | Bit 1    | Bit 0 |

|-------------------------|----------------------|--------------------------|---------------------------------------------------------------|-------------------------|--------------|--------------------------|-------|----------|-------|

| 0Ah, 1Ah <sup>(1)</sup> | Weekday Alarm        | AE_WD                    | 7                                                             | 6                       | 5            | 4                        | 3     | 2        | 1     |

| UAN, TAN                | Reset                | 0                        | 0                                                             | 0                       | 0            | 0                        | 0     | 0        | 0     |

| Bit                     | Symbol               | Value                    |                                                               |                         | ı            | Description              | n     |          |       |

| _                       |                      | Week                     | day/Date A                                                    | larm Enable<br>(see USE |              | es alarm to<br>LARM INTI |       | AE_M and | AE_H  |

| 7                       | AE_WD                | 0                        | Weekday                                                       | /Date Alarn             | n is enable  | d. – Default             | value |          |       |

|                         |                      | 1                        | Weekday                                                       | /Date Alarn             | n is disable | d.                       |       |          |       |

| 6:0                     | Weekday Alarm        | 0000000<br>to<br>1111111 | Holds the weekday alarm value. Multiple days can be selected. |                         |              |                          |       |          |       |

| Weekday Alarm           |                      | Bit 7                    | Bit 6                                                         | Bit 5                   | Bit 4        | Bit 3                    | Bit 2 | Bit 1    | Bit 0 |

| Any weekday selec       | ted. – Default value |                          | 0                                                             | 0                       | 0            | 0                        | 0     | 0        | 0     |

| Weekday 1 Alarm         |                      |                          | 0                                                             | 0                       | 0            | 0                        | 0     | 0        | 1     |

| Weekday 2 Alarm         |                      |                          | 0                                                             | 0                       | 0            | 0                        | 0     | 1        | 0     |

| Weekday 3 Alarm         |                      | 0.511                    | 0                                                             | 0                       | 0            | 0                        | 1     | 0        | 0     |

| Weekday 4 Alarm         |                      | 0 or 1                   |                                                               |                         |              |                          |       | 0        | 0     |

| Weekday 5 Alarm         |                      |                          | 0                                                             | 0                       | 1            | 0                        | 0     | 0        | 0     |

| Weekday 6 Alarm         |                      |                          | 0                                                             | 1                       | 0            | 0                        | 0     | 0        | 0     |

| Weekday 7 Alarm         |                      |                          | 1                                                             | 0                       | 0            | 0                        | 0     | 0        | 0     |

Date Alarm when WADA = 1 (Bit 6 in Register 0Dh, 1Dh)

| Addresses               | Function   | Bit 7                                                                                                    | Bit 6                                 | Bit 5       | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0     |

|-------------------------|------------|----------------------------------------------------------------------------------------------------------|---------------------------------------|-------------|--------------|--------------|-------|-------|-----------|

| 0Ah, 1Ah <sup>(1)</sup> | Date Alarm | AE_WD                                                                                                    | GP1                                   | 20          | 10           | 8            | 4     | 2     | 1         |

| UAII, TAII              | Reset      | 0                                                                                                        | 0                                     | 0           | 0            | 0            | 0     | 0     | 0         |

| Bit                     | Symbol     | Value                                                                                                    |                                       |             |              | Description  | 1     |       |           |

| _                       |            | Weekday/Date Alarm Enable bit. Enables alarm together with AE_M and AE (see USE OF THE ALARM INTERRUPT). |                                       |             |              |              |       |       | AE_H      |

| /                       | AE_WD      | 0                                                                                                        | Weekday                               | /Date Alarn | n is enabled | d. – Default | value |       |           |

|                         |            | 1                                                                                                        | Weekday                               | /Date Alarn | n is disable | d.           |       |       |           |

| 6                       | GP1        | 0 or 1                                                                                                   | Register bit for general purpose use. |             |              |              |       |       |           |

| 5:0                     | Date Alarm | 01 to 31                                                                                                 |                                       |             | e for the da |              |       |       | set value |

<sup>&</sup>lt;sup>(1)</sup> This specific function accessed in Address range 00h to 0Fh is automatically updated in Address range 10h to 1Fh and vice versa.

### 3.5. PERIODIC COUNTDOWN TIMER CONTROL REGISTERS

### 0Bh, 1Bh - Timer Counter 0

This register is used to set the lower 8 bits of the Timer Value (preset value) for the Periodic Countdown Timer.

| Addresses               | Function        | Bit 7         | Bit 6                                                                                                                                                                                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------------|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| 0Bh, 1Bh <sup>(1)</sup> | Timer Counter 0 | 128           | 64                                                                                                                                                                                          | 32    | 16    | 8     | 4     | 2     | 1     |

| UDII, IDII\             | Reset           | 0             | 0                                                                                                                                                                                           | 0     | 0     | 0     | 0     | 0     | 0     |

| Bit                     | Symbol          | Value         | Description                                                                                                                                                                                 |       |       |       |       |       |       |

| 7:0                     | Timer Counter 0 | 00h to<br>FFh | Description  The Timer Value for the Periodic Countdown Timer (lower 8 bit) (see US OF THE PERIODIC COUNTDOWN TIMER). When read, only the preservalue is returned and not the actual value. |       |       |       |       |       |       |

### 0Ch, 1Ch - Timer Counter 1

This register is used to set the upper 4 bits of the Timer Value (preset value) for the Periodic Countdown Timer.

| Addresses               | Function        | Bit 7       | Bit 6                                 | Bit 5        | Bit 4       | Bit 3    | Bit 2 | Bit 1                         | Bit 0 |  |

|-------------------------|-----------------|-------------|---------------------------------------|--------------|-------------|----------|-------|-------------------------------|-------|--|

| 0Ch, 1Ch <sup>(1)</sup> | Timer Counter 1 | GP5         | GP4                                   | GP3          | GP2         | 2048     | 1024  | 512                           | 256   |  |

| UCH, TCH                | Reset           | 0           | 0                                     | 0            | 0           | 0        | 0     | 0                             | 0     |  |

| Bit                     | Symbol          | Value       | Description                           |              |             |          |       |                               |       |  |

| 7                       | GP5             | 0 or 1      | Register bit for general purpose use. |              |             |          |       |                               |       |  |

| 6                       | GP4             | 0 or 1      | Register bit for general purpose use. |              |             |          |       |                               |       |  |

| 5                       | GP3             | 0 or 1      | Register I                            | bit for gene | ral purpose | use.     |       |                               |       |  |

| 4                       | GP2             | 0 or 1      | Register I                            | bit for gene | ral purpose | use.     |       |                               |       |  |

| 3:0                     | Timer Counter 1 | 0h to<br>Fh | OF THE I                              | PERIODIC     |             | WN TIMER |       | pper 4 bit) (<br>ad, only the |       |  |

<sup>&</sup>lt;sup>(1)</sup> This specific function accessed in Address range 00h to 0Fh is automatically updated in Address range 10h to 1Fh and vice versa.

Countdown Period in seconds:

Countdown Period =

$$\frac{\text{Timer Value}}{\text{Timer Clock Frequency}}$$

### 3.6. EXTENSION REGISTER

### 0Dh, 1Dh - Extension Register

This register is used to specify the target for the Alarm Interrupt function and the Periodic Time Update Interrupt function and to select or set operations for the Periodic Countdown Timer.

| Addresses               | Function                | Bit 7                                                                                                                                                                                                                                                                                                                                                                        | Bit 6                                 | Bit 5                    | Bit 4                             | Bit 3       | Bit 2 | Bit 1              | Bit 0                      |

|-------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------|-----------------------------------|-------------|-------|--------------------|----------------------------|

| 0Dh, 1Dh <sup>(1)</sup> | Extension Register      | TEST                                                                                                                                                                                                                                                                                                                                                                         | WADA                                  | USEL                     | TE                                | F           | D     | 7                  | ΓD                         |

| ODN, TDN                | Reset                   | 0                                                                                                                                                                                                                                                                                                                                                                            | 0                                     | 0                        | 0                                 | 0           | 0     | 0                  | 0                          |

| Bit                     | Symbol                  | Value                                                                                                                                                                                                                                                                                                                                                                        |                                       |                          |                                   | Description | n     |                    |                            |

| 7                       | TEST                    | 0                                                                                                                                                                                                                                                                                                                                                                            |                                       |                          | er's test bit.<br>vriting in this |             |       |                    |                            |

| 6                       | WADA                    | Weekday Alarm / Date Alarm selection bit. This bit is used to specify either the Weekday or Date as the source for the Alarm Interrupt function (see USE OF THE ALARM INTERRUPT).  Weekday is the source for the Alarm Interrupt function. – Default value  Date is the source for the Alarm Interrupt function.                                                             |                                       |                          |                                   |             |       |                    | ner the                    |

| 5                       | USEL                    | Update Interrupt Select bit. Specifies either Second or Minute update for the Periodic Time Update Interrupt function. If the RESET bit = 1, the interrupt function is stopped (see PERIODIC TIME UPDATE INTERRUPT FUNCTION).  0 Second update (Auto reset time t <sub>RTN2</sub> = 500 ms). – Default value  1 Minute update (Auto reset time t <sub>RTN2</sub> = 15.6 ms). |                                       |                          |                                   |             |       |                    |                            |

| 4                       | TE                      | Periodic Countdown Timer Enable bit. This bit controls the start/stop setting for the Periodic Countdown Timer Interruption function (see PERIODIC COUNTDOWN TIMER INTERRUPT FUNCTION).  Stops the Periodic Countdown Timer Interrupt function. – Default value  Starts the Periodic Countdown Timer Interrupt function (a countdown starts)                                 |                                       |                          |                                   |             |       | value              |                            |

|                         |                         | CLK<br>00                                                                                                                                                                                                                                                                                                                                                                    | from a pre<br>OUT freque<br>32.768 kH | ncy selecti<br>(see CLK0 | on. Sets the                      |             |       |                    | JT pin                     |

| 3:2                     | FD                      | 01                                                                                                                                                                                                                                                                                                                                                                           | 1024 Hz                               | iz Boladi                | it value                          |             |       |                    |                            |

|                         |                         | 11                                                                                                                                                                                                                                                                                                                                                                           | 32.768 kH                             | lz                       |                                   |             |       |                    |                            |

| 1:0                     | TD                      | Timer Clock Frequency selection. Sets the countdown source clock for the Periodic Countdown Timer Interrupt function. With this setting the Auto reset time $t_{RTN1}$ is also defined. If RESET bit = 1, the interrupt function is stopped. See table below (see also PERIODIC COUNTDOWN TIMER INTERRUPT FUNCTION).                                                         |                                       |                          |                                   |             |       | e Auto<br>ction is |                            |

| TD Value                | Timer Clock Frequency   | ncy Countdown period t <sub>RTN1</sub> RESET bit                                                                                                                                                                                                                                                                                                                             |                                       |                          |                                   |             |       | bit                |                            |

| 00                      | 4096 Hz – Default value |                                                                                                                                                                                                                                                                                                                                                                              |                                       |                          |                                   |             |       |                    |                            |

| 01                      | 64 Hz                   | 15.625 m                                                                                                                                                                                                                                                                                                                                                                     | S                                     |                          |                                   |             |       |                    | Γ bit = 1, the function is |

| 10                      | 1 Hz                    | 1 s                                                                                                                                                                                                                                                                                                                                                                          |                                       | 7.                       | 813 ms                            |             | stopp |                    |                            |

| 11                      | 1/60 Hz                 | 60 s                                                                                                                                                                                                                                                                                                                                                                         |                                       |                          |                                   |             |       |                    |                            |

This specific function accessed in Address range 00h to 0Fh is automatically updated in Address range 10h to 1Fh and vice versa.

### 3.7. FLAG REGISTER

### 0Eh, 1Eh - Flag Register

This register holds a variety of status bits. The register may be written at any time to clear any status flag.

| Addresses                                                                                                                                                                                                                                                                   | Function                                | Bit 7                                                                                                                                                                                                                                                                     | Bit 6                                                                                                                                                                                                                                                                                                                                             | Bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit 4                 | Bit 3                    | Bit 2            | Bit 1        | Bit 0      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|------------------|--------------|------------|--|

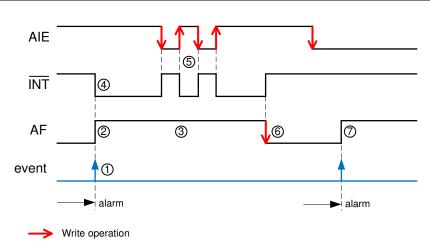

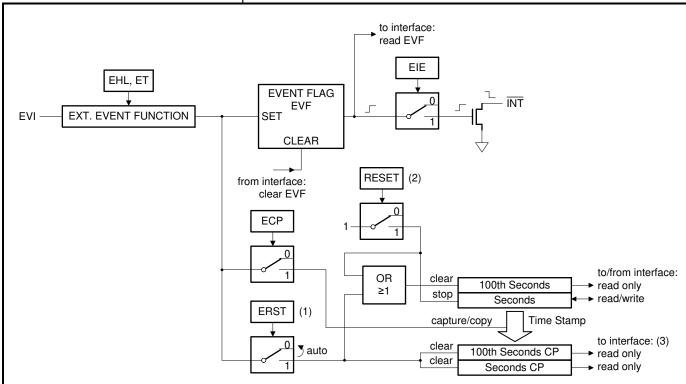

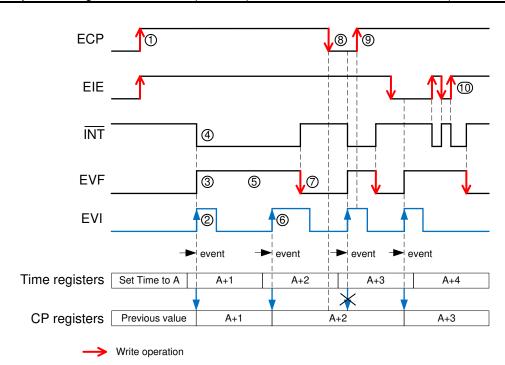

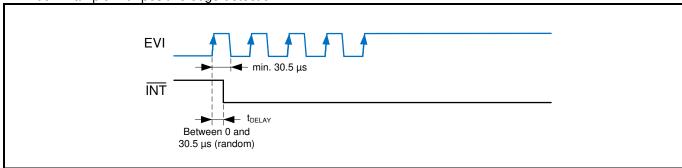

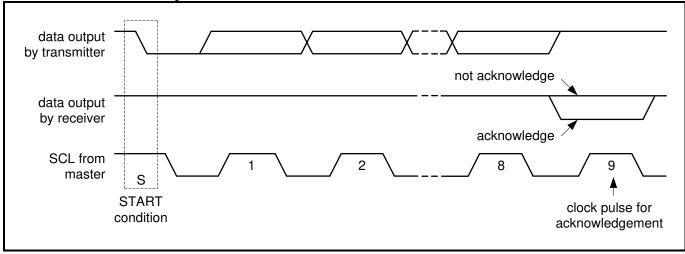

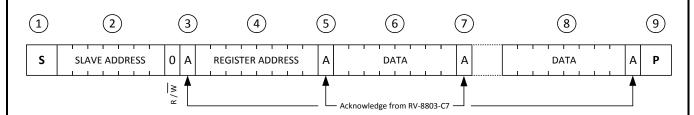

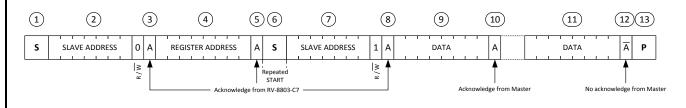

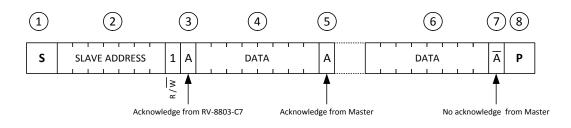

| 0Eh, 1Eh <sup>(1)</sup>                                                                                                                                                                                                                                                     | Flag Register                           | 0                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                 | UF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TF                    | AF                       | EVF              | V2F          | V1F        |  |